(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2011년09월16일

(11) 등록번호 10-1065407

(24) 등록일자 2011년09월08일

(51) Int. Cl.

*H01L 51/50* (2006.01) *H01L 29/786* (2006.01)

(21) 출원번호 10-2009-0078946

(22) 출원일자 2009년08월25일

심사청구일자 2009년08월25일

(65) 공개번호 10-2011-0021259

(43) 공개일자 2011년03월04일

(56) 선행기술조사문현

KR1020050067055 A

(73) 특허권자

삼성모바일디스플레이주식회사

경기도 용인시 기흥구 농서동 산24번지

(72) 발명자

최종현

경기 용인시 기흥구 공세동 428-5

이준우

경기도 오산시 오산동 대동아파트 106동 1801호

(뒷면에 계속)

(74) 대리인

팬코리아특허법인

전체 청구항 수 : 총 25 항

심사관 : 김주승

(54) 유기 발광 표시 장치 및 그 제조 방법

**(57) 요약**

본 발명은 유기 발광 표시 장치 및 그 제조 방법에 관한 것으로서, 본 발명의 실시예에 따른 유기 발광 표시 장치는 기판 본체와, 상기 기판 본체 상에 형성된 제1 게이트 전극 및 제2 반도체층과, 상기 제1 게이트 전극 및 상기 제2 반도체층 위에 형성된 게이트 절연막과, 상기 게이트 절연막을 사이에 두고 상기 제1 게이트 전극 및 상기 제2 반도체층 상에 각각 형성된 제1 반도체층 및 제2 게이트 전극과, 상기 제1 반도체층과 적어도 일부가 맞닿아 포개진 복수의 에칭 스토퍼층들과, 상기 복수의 에칭 스토퍼층들을 각각 드러내는 복수의 접촉 구멍들을 가지고 상기 제1 반도체층 및 상기 제2 게이트 전극 위에 형성된 층간 절연막과, 상기 층간 절연막 상에 형성되어 상기 복수의 에칭 스토퍼층들을 통해 상기 제1 반도체층과 각각 직간접적으로 연결된 제1 소스 전극 및 제1 드레인 전극, 그리고 상기 층간 절연막 상에 형성되어 상기 제2 반도체층과 연결된 제2 소스 전극 및 제2 드레인 전극을 포함한다.

**대 표 도** - 도3

101

(72) 발명자

김광해

경기 용인시 기흥구 공세동 428-5

김경보

경기 용인시 기흥구 공세동 428-5

## 특허청구의 범위

### 청구항 1

제1 박막 트랜지스터와 제2 박막 트랜지스터를 포함하는 유기 발광 표시 장치에 있어서,

기판 본체;

상기 기판 본체 상에 형성된 상기 제1 박막 트랜지스터의 제1 게이트 전극 및 상기 제2 박막 트랜지스터의 제2 반도체층;

상기 제1 게이트 전극 및 상기 제2 반도체층 위에 형성된 게이트 절연막;

상기 게이트 절연막을 사이에 두고 상기 제1 게이트 전극 및 상기 제2 반도체층 상에 각각 형성된 상기 제1 박막 트랜지스터의 제1 반도체층 및 상기 제2 박막 트랜지스터의 제2 게이트 전극;

상기 제1 반도체층과 적어도 일부가 맞닿아 포개진 복수의 에칭 스토퍼층(etching stopper layer)들;

상기 복수의 에칭 스토퍼층들을 각각 드러내는 복수의 접촉 구멍들을 가지고 상기 제1 반도체층 및 상기 제2 게이트 전극 위에 형성된 충간 절연막;

상기 충간 절연막 상에 형성되어 상기 복수의 에칭 스토퍼층들을 통해 상기 제1 반도체층과 각각 직간접적으로 연결된 상기 제1 박막 트랜지스터의 제1 소스 전극 및 제1 드레인 전극; 그리고

상기 충간 절연막 상에 형성되어 상기 제2 반도체층과 연결된 상기 제2 박막 트랜지스터의 제2 소스 전극 및 제2 드레인 전극

을 포함하는 유기 발광 표시 장치.

### 청구항 2

제1항에서,

상기 제1 반도체층은 산화물 반도체층인 유기 발광 표시 장치.

### 청구항 3

제2항에서,

상기 제1 반도체층은 갈륨(Ga), 인듐(In), 아연(Zn), 및 주석(Sn) 중에서 하나 이상의 원소와 산소(O)를 포함하는 유기 발광 표시 장치.

### 청구항 4

제2항에서,

상기 에칭 스토퍼층은 알루미늄(Al), 몰리브덴(Mo), 니켈(Ni), 은(Ag), 크롬(Cr), 티타늄(Ti), 및 탄탈(Ta) 중에서 어느 하나의 금속이나 하나 이상의 금속을 포함하는 합금으로 형성된 유기 발광 표시 장치.

### 청구항 5

제4항에서,

상기 에칭 스토퍼층은 상기 제1 반도체층의 외곽에 위치하는 유기 발광 표시 장치.

### 청구항 6

제2항에서,

상기 제2 반도체층은 상기 제2 게이트 전극과 중첩된 채널 영역과 상기 채널 영역의 양측에 형성된 소스 영역 및 드레인 영역으로 구분된 유기 발광 표시 장치.

### 청구항 7

제6항에서,

상기 제2 반도체층의 상기 채널 영역은 불순물이 도핑되지 않은 다결정 규소층이며,

상기 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역은 불순물이 도핑된 다결정 규소층인 유기 발광 표시 장치.

#### 청구항 8

제7항에서,

상기 제1 게이트 전극은 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역과 동일하게 형성된 유기 발광 표시 장치.

#### 청구항 9

제7항에서,

상기 불순물은 P형 불순물인 유기 발광 표시 장치.

#### 청구항 10

제6항에서,

상기 충간 절연막과 상기 게이트 절연막은 함께 상기 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역의 일부를 각각 드러내는 추가의 접촉 구멍을 더 포함하는 유기 발광 표시 장치.

#### 청구항 11

제1항 내지 제10항 중 어느 한 항에서,

상기 에칭 스토퍼층은 상기 제1 반도체층의 일부 영역 바로 위에 형성된 유기 발광 표시 장치.

#### 청구항 12

제11항에서,

상기 제2 게이트 전극은 상기 제1 반도체층과 동일한 물질로 형성된 제1 전극층과 상기 에칭 스토퍼층과 동일한 물질로 형성된 제2 전극층을 포함하는 유기 발광 표시 장치.

#### 청구항 13

제1항 내지 제10항 중 어느 한 항에서,

상기 에칭 스토퍼층의 일부가 상기 제1 반도체층 바로 아래에 위치하는 유기 발광 표시 장치.

#### 청구항 14

제13항에서,

상기 제2 게이트 전극은 상기 에칭 스토퍼층과 동일한 물질로 형성된 유기 발광 표시 장치.

#### 청구항 15

제1 박막 트랜지스터 및 제2 박막 트랜지스터를 포함하는 유기 발광 표시 장치 제조 방법에 있어서,

기판 본체 상에 다결정 규소층으로 만들어진 제1 게이트 전극 중간체 및 제2 반도체층 중간체를 형성하는 단계;

상기 제1 게이트 전극 중간체 및 상기 제2 반도체층 중간체 상에 게이트 절연막을 형성하는 단계;

상기 게이트 절연막 상에 산화물 반도체층과 금속층을 차례로 형성하는 단계;

상기 산화물 반도체층과 상기 금속층을 패터닝(patterning)하여 상기 제2 박막 트랜지스터의 제2 게이트 전극과, 상기 제1 박막 트랜지스터의 제1 반도체층, 그리고 상기 제1 반도체층의 일부 영역 바로 위에 형성된 복수의 에칭 스토퍼층(etching stopper layer)들을 형성하는 단계;

상기 제1 게이트 전극 중간체 및 상기 제2 반도체층 중간체에 불순물을 도핑하여 상기 제1 박막 트랜지스터의 제1 게이트 전극 및 상기 제2 박막 트랜지스터의 제2 반도체층을 형성하는 단계;

상기 제2 게이트 전극, 상기 제1 반도체층, 및 상기 에칭 스토퍼층 위에 충간 절연막을 형성하는 단계; 그리고 상기 충간 절연막을 식각하여 상기 복수의 에칭 스토퍼층들을 각각 드러내는 제1 소스 접촉 구멍 및 제1 드레인 접촉 구멍과, 상기 충간 절연막과 상기 게이트 절연막을 함께 식각하여 상기 제2 반도체층의 일부를 드러내는 제2 소스 접촉 구멍 및 제2 드레인 접촉 구멍을 형성하는 단계

를 포함하는 유기 발광 표시 장치 제조 방법.

### 청구항 16

제15항에서,

상기 제2 게이트 전극은 상기 산화물 반도체층과 상기 금속층이 적층된 이중층의 구조를 가지며,

상기 제1 반도체층은 상기 산화물 반도체층으로 만들어지고, 상기 에칭 스토퍼층은 상기 금속층으로 만들어진 유기 발광 표시 장치 제조 방법.

### 청구항 17

제1 박막 트랜지스터와 제2 박막 트랜지스터를 포함하는 유기 발광 표시 장치 제조 방법에 있어서,

기판 본체 상에 다결정 규소층으로 만들어진 제1 게이트 전극 중간체 및 제2 반도체층 중간체를 형성하는 단계;

상기 제1 게이트 전극 중간체 및 상기 제2 반도체층 중간체 상에 게이트 절연막을 형성하는 단계;

상기 게이트 절연막 상에 금속층을 형성한 후 패터닝(patterning)하여 상기 제2 박막 트랜지스터의 제2 게이트 전극과 복수의 에칭 스토퍼층(etching stopper layer)들을 형성하는 단계;

상기 제1 게이트 전극 중간체 및 상기 제2 반도체층 중간체에 불순물을 도핑하여 상기 제1 박막 트랜지스터의 제1 게이트 전극 및 상기 제2 박막 트랜지스터의 제2 반도체층을 형성하는 단계;

상기 복수의 에칭 스토퍼들 위에 산화물 반도체층을 형성한 후 패터닝하여 상기 복수의 에칭 스토퍼들과 일부가 중첩된 상기 제1 박막 트랜지스터의 제1 반도체층을 형성하는 단계;

상기 제2 게이트 전극, 상기 에칭 스토퍼층, 및 상기 제1 반도체층 위에 충간 절연막을 형성하는 단계; 그리고

상기 충간 절연막을 식각하여 상기 복수의 에칭 스토퍼층들을 각각 드러내는 제1 소스 접촉 구멍 및 제1 드레인 접촉 구멍과, 상기 충간 절연막과 상기 게이트 절연막을 함께 식각하여 상기 제2 반도체층의 일부를 드러내는 제2 소스 접촉 구멍 및 제2 드레인 접촉 구멍을 형성하는 단계

를 포함하는 유기 발광 표시 장치 제조 방법.

### 청구항 18

제15항 내지 제17항 중 어느 한 항에서,

상기 충간 절연막 상에 상기 제1 박막 트랜지스터의 제1 소스 전극 및 제1 드레인 전극과, 상기 제2 박막 트랜지스터의 제2 소스 전극 및 제2 드레인 전극을 형성하는 단계를 더 포함하며,

상기 제1 소스 전극 및 상기 제1 드레인 전극은 각각 상기 제1 소스 접촉 구멍 및 상기 제1 드레인 접촉 구멍과 상기 에칭 스토퍼층을 통해 상기 제1 반도체층과 직간접적으로 연결되고,

상기 제2 소스 전극 및 상기 제2 드레인 전극은 각각 상기 제2 소스 접촉 구멍 및 상기 제2 드레인 접촉 구멍을 통해 상기 제2 반도체층과 연결되는 유기 발광 표시 장치 제조 방법.

### 청구항 19

제18항에서,

상기 제1 반도체층은 갈륨(Ga), 인듐(In), 아연(Zn), 및 주석(Sn) 중에서 하나 이상의 원소와 산소(O)를 포함하는 유기 발광 표시 장치 제조 방법.

**청구항 20**

제18항에서,

상기 예칭 스토퍼층은 알루미늄(Al), 몰리브덴(Mo), 니켈(Ni), 은(Ag), 크롬(Cr), 티타늄(Ti), 및 탄탈(Ta) 중에서 어느 하나의 금속이나 하나 이상의 금속을 포함하는 합금으로 형성된 유기 발광 표시 장치 제조 방법.

**청구항 21**

제20항에서,

상기 예칭 스토퍼층은 상기 제1 반도체층의 외곽에 위치하는 유기 발광 표시 장치 제조 방법.

**청구항 22**

제18항에서,

상기 제2 반도체층은 상기 제2 게이트 전극과 중첩된 채널 영역과 상기 채널 영역의 양측에 형성된 소스 영역 및 드레인 영역으로 구분된 유기 발광 표시 장치 제조 방법.

**청구항 23**

제22항에서,

상기 제2 반도체층의 상기 채널 영역은 불순물이 도핑되지 않은 다결정 규소층이며,

상기 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역은 불순물이 도핑된 다결정 규소층인 유기 발광 표시 장치 제조 방법.

**청구항 24**

제23항에서,

상기 제1 게이트 전극은 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역과 동일하게 형성된 유기 발광 표시 장치 제조 방법.

**청구항 25**

제23항에서,

상기 불순물은 P형 불순물인 유기 발광 표시 장치 제조 방법.

**명세서****발명의 상세한 설명****기술 분야**

[0001]

본 발명은 유기 발광 표시 장치에 관한 것으로, 보다 상세하게는 산화물 반도체층과 다결정 규소 반도체층을 함께 사용한 유기 발광 표시 장치에 관한 것이다.

**배경 기술**

[0002]

유기 발광 표시 장치(organic light emitting diode display)는 빛을 방출하는 유기 발광 소자(organic light emitting diode)를 가지고 화상을 표시하는 자발광형 표시 장치이다. 유기 발광 표시 장치는 액정 표시 장치(liquid crystal display)와 달리 별도의 광원을 필요로 하지 않으므로 상대적으로 두께와 무게를 줄일 수 있다. 또한, 유기 발광 표시 장치는 낮은 소비 전력, 높은 휙도 및 높은 반응 속도 등의 고품위 특성을 나타내므로 휴대용 전자 기기의 차세대 표시 장치로 주목받고 있다.

[0003]

근래에는, 산화물 박막 트랜지스터(oxide thin film transistor)를 구비한 유기 발광 표시 장치가 특히 주목받고 있다. 산화물 박막 트랜지스터는 산화물 반도체를 사용한 박막 트랜지스터를 말한다. 산화물 박막 트랜지스터는 비정질 규소를 사용한 박막 트랜지스터와 비교하여 상대적으로 높은 전자 이동도와 신뢰성을 가질 뿐만

아니라 종합적으로 우수한 성능을 갖는다. 또한, 산화물 박막 트랜지스터를 구비한 유기 발광 표시 장치는 투명한 표시 장치를 구현하는데 유리하다.

[0004] 하지만, 산화물 박막 트랜지스터는 다결정 규소를 사용한 박막 트랜지스터와 비교하여 우수한 균일성을 가지지만 전하 이동도가 다소 떨어진다. 따라서, 유기 발광 표시 장치가 산화물 박막 트랜지스터만을 사용할 경우 전체적인 성능 향상에 한계가 있었다.

## 발명의 내용

### 해결 하고자하는 과제

[0005] 본 발명은 전술한 배경기술의 문제점을 해결하기 위한 것으로서, 상대적으로 단순한 구조를 가지고 안정적으로 산화물 반도체층과 다결정 규소 반도체층을 함께 사용할 수 있는 유기 발광 표시 장치 및 그 제조 방법을 제공하고자 한다.

### 과제 해결手段

[0006] 본 발명의 실시예에 따른 유기 발광 표시 장치는 기판 본체와, 상기 기판 본체 상에 형성된 제1 게이트 전극 및 제2 반도체층과, 상기 제1 게이트 전극 및 상기 제2 반도체층 위에 형성된 게이트 절연막과, 상기 게이트 절연막을 사이에 두고 상기 제1 게이트 전극 및 상기 제2 반도체층 상에 각각 형성된 제1 반도체층 및 제2 게이트 전극과, 상기 제1 반도체층과 적어도 일부가 맞닿아 포개진 복수의 에칭 스토퍼층(etching stopper layer)들과, 상기 복수의 에칭 스토퍼층들을 각각 드러내는 복수의 접촉 구멍들을 가지고 상기 제1 반도체층 및 상기 제2 게이트 전극 위에 형성된 층간 절연막과, 상기 층간 절연막 상에 형성되어 상기 복수의 에칭 스토퍼층들을 통해 상기 제1 반도체층과 각각 직간접적으로 연결된 제1 소스 전극 및 제1 드레인 전극, 그리고 상기 층간 절연막 상에 형성되어 상기 제2 반도체층과 연결된 제2 소스 전극 및 제2 드레인 전극을 포함한다.

[0007] 상기 제1 반도체층은 산화물 반도체층일 수 있다.

[0008] 상기 제1 반도체층은 갈륨(Ga), 인듐(In), 아연(Zn), 및 주석(Sn) 중에서 하나 이상의 원소와 산소(O)를 포함할 수 있다.

[0009] 상기 에칭 스토퍼층은 알루미늄(Al), 몰리브덴(Mo), 니켈(Ni), 은(Ag), 크롬(Cr), 티타늄(Ti), 및 탄탈(Ta) 중에서 어느 하나의 금속이나 하나 이상의 금속을 포함하는 합금으로 형성될 수 있다.

[0010] 상기 에칭 스토퍼층은 상기 제1 반도체층의 외곽에 위치할 수 있다.

[0011] 상기 제2 반도체층은 상기 제2 게이트 전극과 중첩된 채널 영역과 상기 채널 영역의 양측에 형성된 소스 영역 및 드레인 영역으로 구분될 수 있다.

[0012] 상기 제2 반도체층의 상기 채널 영역은 불순물이 도핑되지 않은 다결정 규소층이며, 상기 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역은 불순물이 도핑된 다결정 규소층일 수 있다.

[0013] 상기 제1 게이트 전극은 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역과 동일하게 형성될 수 있다.

[0014] 상기 불순물은 P형 불순물일 수 있다.

[0015] 상기 층간 절연막과 상기 게이트 절연막은 함께 상기 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역의 일부를 각각 드러내는 추가의 접촉 구멍을 더 포함할 수 있다.

[0016] 상기한 유기 발광 표시 장치에 있어서, 상기 에칭 스토퍼층은 상기 제1 반도체층의 일부 영역 바로 위에 형성될 수 있다.

[0017] 상기 제2 게이트 전극은 상기 제1 반도체층과 동일한 물질로 형성된 제1 전극층과 상기 에칭 스토퍼층과 동일한 물질로 형성된 제2 전극층을 포함할 수 있다.

[0018] 상기한 유기 발광 표시 장치에 있어서, 상기 에칭 스토퍼층의 일부가 상기 제1 반도체층 바로 아래에 위치할 수 있다.

[0019] 상기 제2 게이트 전극은 상기 에칭 스토퍼층과 동일한 물질로 형성될 수 있다.

[0020] 또한, 본 발명의 실시예에 따른 유기 발광 표시 장치 제조 방법은 기판 본체 상에 다결정 규소층으로 만들어진

제1 게이트 전극 중간체 및 제2 반도체층 중간체를 형성하는 단계와, 상기 제1 게이트 전극 중간체 및 상기 제2 반도체층 중간체 상에 게이트 절연막을 형성하는 단계와, 상기 게이트 절연막 상에 산화물 반도체층과 금속층을 차례로 형성하는 단계와, 상기 산화물 반도체층과 상기 금속층을 패터닝(patterning)하여 제2 게이트 전극, 제1 반도체층, 및 상기 제1 반도체층의 일부 영역 바로 위에 형성된 복수의 에칭 스토퍼층(etching stopper layer)들을 형성하는 단계와, 상기 제1 게이트 전극 중간체 및 상기 제2 반도체층 중간체에 불순물을 도핑하여 제1 게이트 전극 및 제2 반도체층을 형성하는 단계와, 상기 제2 게이트 전극, 상기 제1 반도체층, 및 상기 에칭 스토퍼층 위에 충간 절연막을 형성하는 단계, 그리고 상기 충간 절연막을 식각하여 상기 복수의 에칭 스토퍼층들을 각각 드러내는 제1 소스 접촉 구멍 및 제1 드레인 접촉 구멍과, 상기 충간 절연막과 상기 게이트 절연막을 함께 식각하여 상기 제2 반도체층의 일부를 드러내는 제2 소스 접촉 구멍 및 제2 드레인 접촉 구멍을 형성하는 단계를 포함한다.

[0021] 상기 제2 게이트 전극은 상기 산화물 반도체층과 상기 금속층이 적층된 이중층의 구조를 가지며, 상기 제1 반도체층은 상기 산화물 반도체층으로 만들어지고, 상기 에칭 스토퍼층은 상기 금속층으로 만들어질 수 있다.

[0022] 또한, 본 발명의 실시예에 따른 다른 유기 발광 표시 장치 제조 방법은 기판 본체 상에 다결정 규소층으로 만들어진 제1 게이트 전극 중간체 및 제2 반도체층 중간체를 형성하는 단계와, 상기 제1 게이트 전극 중간체 및 상기 제2 반도체층 중간체 상에 게이트 절연막을 형성하는 단계와, 상기 게이트 절연막 상에 금속층을 형성한 후 패터닝(patterning)하여 제2 게이트 전극과 복수의 에칭 스토퍼층(etching stopper layer)들을 형성하는 단계와, 상기 제1 게이트 전극 중간체 및 상기 제2 반도체층 중간체에 불순물을 도핑하여 제1 게이트 전극 및 제2 반도체층을 형성하는 단계와, 상기 복수의 에칭 스토퍼들 위에 산화물 반도체층을 형성한 후 패터닝하여 상기 복수의 에칭 스토퍼들과 일부가 중첩된 상기 제1 반도체층을 형성하는 단계와, 상기 제2 게이트 전극, 상기 에칭 스토퍼층, 및 상기 제1 반도체층 위에 충간 절연막을 형성하는 단계, 그리고 상기 충간 절연막을 식각하여 상기 복수의 에칭 스토퍼층들을 각각 드러내는 제1 소스 접촉 구멍 및 제1 드레인 접촉 구멍과, 상기 충간 절연막과 상기 게이트 절연막을 함께 식각하여 상기 제2 반도체층의 일부를 드러내는 제2 소스 접촉 구멍 및 제2 드레인 접촉 구멍을 형성하는 단계를 포함한다.

[0023] 상기한 유기 발광 표시 장치 제조 방법들에 있어서, 상기 충간 절연막 상에 제1 소스 전극, 제1 드레인 전극, 제2 소스 전극, 및 제2 드레인 전극을 형성하는 단계를 더 포함하며, 상기 제1 소스 전극 및 상기 제1 드레인 전극은 각각 상기 제1 소스 접촉 구멍 및 상기 제1 드레인 접촉 구멍과 상기 에칭 스토퍼층을 통해 상기 제1 반도체층과 직간접적으로 연결되고, 상기 제2 소스 전극 및 상기 제2 드레인 전극은 각각 상기 제2 소스 접촉 구멍 및 상기 제2 드레인 접촉 구멍을 통해 상기 제2 반도체층과 연결될 수 있다.

[0024] 상기 제1 반도체층은 갈륨(Ga), 인듐(In), 아연(Zn), 및 주석(Sn) 중에서 하나 이상의 원소와 산소(O)를 포함할 수 있다.

[0025] 상기 에칭 스토퍼층은 알루미늄(Al), 몰리브덴(Mo), 니켈(Ni), 은(Ag), 크롬(Cr), 티타늄(Ti), 및 탄탈(Ta) 중에서 어느 하나의 금속이나 하나 이상의 금속을 포함하는 합금으로 형성될 수 있다.

[0026] 상기 에칭 스토퍼층은 상기 제1 반도체층의 외곽에 위치할 수 있다.

[0027] 상기 제2 반도체층은 상기 제2 게이트 전극과 중첩된 채널 영역과 상기 채널 영역의 양측에 형성된 소스 영역 및 드레인 영역으로 구분될 수 있다.

[0028] 상기 제2 반도체층의 상기 채널 영역은 불순물이 도핑되지 않은 다결정 규소층이며, 상기 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역은 불순물이 도핑된 다결정 규소층일 수 있다.

[0029] 상기 제1 게이트 전극은 제2 반도체층의 상기 소스 영역 및 상기 드레인 영역과 동일하게 형성될 수 있다.

[0030] 상기 불순물은 P형 불순물일 수 있다.

## 효과

[0031] 본 발명의 실시예에 따르면, 유기 발광 표시 장치는 상대적으로 단순한 구조를 가지고 안정적으로 산화물 반도체층과 다결정 규소 반도체층을 함께 사용할 수 있다.

[0032] 또한, 상기한 유기 발광 표시 장치를 효과적으로 제조할 수 있다.

## 발명의 실시를 위한 구체적인 내용

- [0033] 이하, 첨부한 도면을 참고로 하여 본 발명의 여러 실시예들에 대하여 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 상세히 설명한다. 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명하는 실시예들에 한정되지 않는다.

- [0034] 또한, 여러 실시예들에 있어서, 동일한 구성을 가지는 구성요소에 대해서는 동일한 부호를 사용하여 대표적으로 제1 실시예에서 설명하고, 그 외의 제2 실시예에서는 제1 실시예와 다른 구성에 대해서만 설명하기로 한다.

- [0035] 본 발명을 명확하게 설명하기 위해서 설명과 관계없는 부분은 생략하였으며, 명세서 전체를 통하여 동일 또는 유사한 구성요소에 대해서는 동일한 참조 부호를 붙이도록 한다.

- [0036] 또한, 도면에서 나타난 각 구성의 크기 및 두께는 설명의 편의를 위해 임의로 나타내었으므로, 본 발명이 반드시 도시된 바에 한정되지 않는다.

- [0037] 도면에서 여러 층 및 영역을 명확하게 표현하기 위하여 두께를 확대하여 나타내었다. 그리고 도면에서, 설명의 편의를 위해, 일부 층 및 영역의 두께를 과장되게 나타내었다. 층, 막, 영역, 판 등의 부분이 다른 부분 "위에" 또는 "상에" 있다고 할 때, 이는 다른 부분 "바로 위에" 있는 경우뿐 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다.

- [0038] 이하, 도 1 내지 도3을 참조하여 본 발명의 제1 실시예를 설명한다.

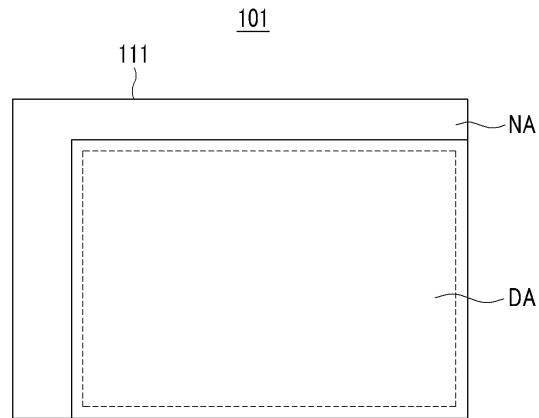

- [0039] 도 1에 도시한 바와 같이, 본 발명의 제1 실시예에 따른 유기 발광 표시 장치(101)는 표시 영역(DA)과 비표시 영역(NA)으로 구분된 기판 본체(111)를 포함한다. 기판 본체(111)의 표시 영역(DA)에는 다수의 화소들(PE)(도 2에 도시)이 형성되어 화상을 표시하고, 비표시 영역(NA)에는 여러 구동 회로가 형성된다.

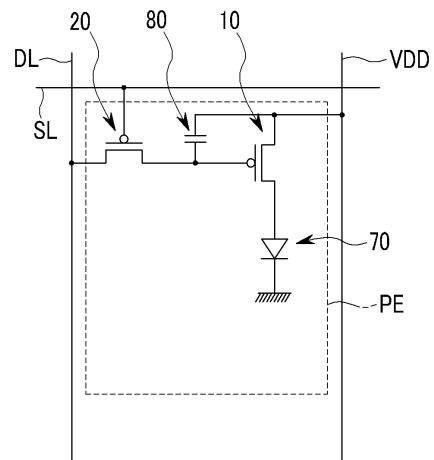

- [0040] 도 2에 도시한 바와 같이 본 발명의 제1 실시예에서는, 하나의 화소(PE)가 유기 발광 소자(organic light emitting diode)(70), 두개의 박막 트랜지스터(thin film transistor, TFT)들(10, 20), 그리고 하나의 축전 소자(capacitor)(80)를 구비하는 2Tr-1Cap 구조를 갖는다. 하지만, 본 발명의 제1 실시예가 이에 한정되는 것은 아니다. 따라서 유기 발광 표시 장치(101)는 하나의 화소(PE)에 세 이상의 박막 트랜지스터와 둘 이상의 축전 소자를 구비할 수 있으며, 별도의 배선이 더 형성되어 다양한 구조를 갖도록 형성할 수도 있다. 이와 같이, 추가로 형성되는 박막 트랜지스터 및 축전 소자는 보상 회로의 구성이 될 수 있다.

- [0041] 보상 회로는 각 화소(PE)마다 형성된 유기 발광 소자(70)의 균일성을 향상시켜 화질(畫質)에 편차가 생기는 것을 억제한다. 일반적으로 보상 회로는 4개 내지 8개의 박막 트랜지스터를 포함한다.

- [0042] 또한, 기판 본체(111)의 비표시 영역(NA) 상에 형성된 구동 회로도 추가의 박막 트랜지스터를 포함할 수 있다.

- [0043] 유기 발광 소자(70)는 정공 주입 전극인 애노드(anode) 전극과, 전자 주입 전극인 캐소드(cathode) 전극, 그리고 애노드 전극과 캐소드 전극 사이에 배치된 유기 발광층을 포함한다.

- [0044] 본 발명의 제1 실시예에 따른 두개의 박막 트랜지스터들은 제1 박막 트랜지스터(10)와 제2 박막 트랜지스터(20)를 포함한다.

- [0045] 제1 박막 트랜지스터(10) 및 제2 박막 트랜지스터(20)는 각각 게이트 전극, 반도체층, 소스 전극, 및 드레인 전극을 포함한다. 그리고 제1 박막 트랜지스터(10)의 반도체층은 산화물 반도체층이고, 제2 박막 트랜지스터(20)의 반도체층은 다결정 규소 반도체층이다. 즉, 제1 박막 트랜지스터(10)는 산화물 박막 트랜지스터고, 제2 박막 트랜지스터(20)는 다결정 규소 박막 트랜지스터이다.

- [0046] 제1 박막 트랜지스터(10)는 유기 발광 소자(70)와 연결되고, 제2 박막 트랜지스터는 스캔 라인(SL) 및 데이터 라인(DL)에 연결된다.

- [0047] 제2 박막 트랜지스터(20)는 발광시키고자 하는 화소(PE)를 선택하는 스위칭 소자로 사용된다. 제2 박막 트랜지스터(20)의 게이트 전극은 스캔 라인(SL)과 연결되며, 제2 박막 트랜지스터(20)의 소스 전극은 데이터 라인(DL)과 연결된다. 제2 박막 트랜지스터(20)는 스캔 라인(SL)에 입력되는 스위칭 전압에 따라 데이터 라인(DL)에서 입력되는 데이터 전압을 제1 박막 트랜지스터(10)로 전달한다.

- [0048] 축전 소자(80)는 제2 박막 트랜지스터(20)와 공통 전원 라인(VDD)에 연결되며, 제2 박막 트랜지스터(20)로부터 전송받은 전압과 공통 전원 라인(VDD)에 공급되는 전압의 차이에 해당하는 전압을 저장한다.

- [0049] 제1 박막 트랜지스터(10)는 선택된 화소(PE) 내의 유기 발광 소자(70)를 발광시키기 위한 구동 전원을 공급한다. 제1 박막 트랜지스터(10)의 게이트 전극은 제2 박막 트랜지스터(20)의 드레인 전극과 연결된 축전

소자(80)의 어느 한 축전판과 연결된다. 그리고 제1 박막 트랜지스터(10)의 소스 전극 및 축전 소자(80)의 다른 한 축전판은 각각 공통 전원 라인(VDD)과 연결된다. 또한, 제1 박막 트랜지스터(10)의 드레인 전극은 유기 발광 소자(70)의 애노드 전극과 연결된다. 이와 같이, 제1 박막 트랜지스터(10)는 공통 전원 라인(VDD)과 축전 소자(80)에 연결되어 축전 소자(80)에 저장된 전압과 문턱 전압의 차이의 제곱에 비례하는 출력 전류( $I_{OLED}$ )를 유기 발광 소자(70)로 공급한다. 유기발광 소자(70)는 제1 박막 트랜지스터(10)로부터 공급받은 출력 전류( $I_{OLED}$ )에 의해 발광한다.

[0050] 이와 같은 화소(PE)의 구성은 전술한 바에 한정되지 않고 다양하게 변형 가능하다.

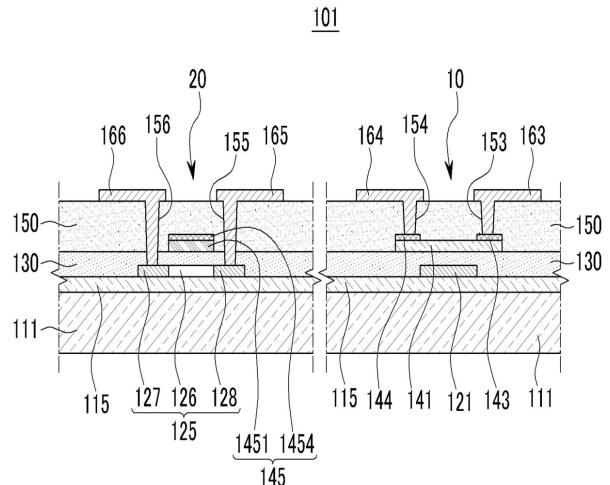

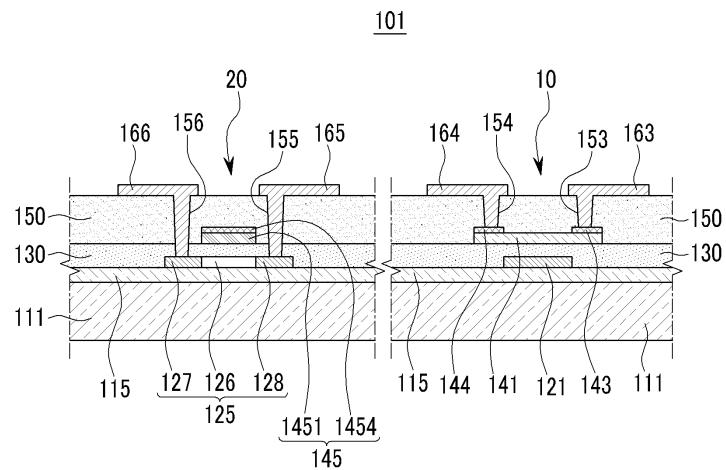

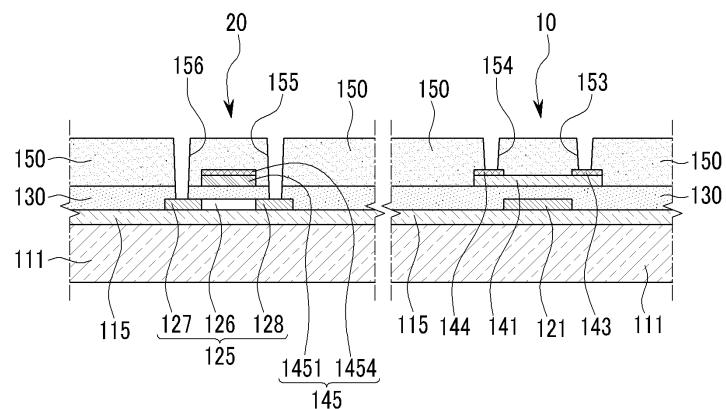

[0051] 도 3에 도시한 바와 같이, 제1 박막 트랜지스터(10)는 제1 게이트 전극(121), 제1 반도체층(141), 제1 소스 전극(163), 및 제1 드레인 전극(164)을 포함한다. 그리고, 제2 박막 트랜지스터(20)는 제2 게이트 전극(145), 제2 반도체층(125), 제2 소스 전극(165), 및 제2 드레인 전극(166)을 포함한다. 여기서, 제1 반도체층(141)은 산화물 반도체층이며, 제2 반도체층(125)은 다결정 규소 반도체층이다. 또한, 제1 박막 트랜지스터(10)는 제1 반도체층(141)과 적어도 일부가 맞닿아 포개진 복수의 에칭 스토퍼층(etching stopper layer)들(143, 144)을 포함한다.

[0052] 이하, 도 3을 참조하여 본 발명의 제1 실시예에 따른 제1 박막 트랜지스터(10) 및 제2 박막 트랜지스터(20)의 구조를 적층 순서를 중심으로 상세히 설명한다.

[0053] 기판 본체(111)는 유리, 석영, 세라믹, 및 플라스틱 등으로 이루어진 절연성 기판으로 형성될 수 있다. 그러나 본 발명의 제1 실시예가 이에 한정되는 것은 아니며, 기판 본체(111)가 스테인리스 강 등으로 이루어진 금속성 기판으로 형성될 수도 있다.

[0054] 기판 본체(111) 상에는 베퍼층(115)이 형성된다. 베퍼층(115)은 다양한 무기막들 및 유기막들 중에서 하나 이상의 막으로 형성될 수 있다. 베퍼층(115)은 불순 원소 또는 수분과 같이 불필요한 성분의 침투를 방지하면서 동시에 표면을 평탄화하는 역할을 한다. 하지만, 베퍼층(115)은 반드시 필요한 구성은 아니며, 기판 본체(111)의 종류 및 공정 조건에 따라 생략될 수도 있다.

[0055] 베퍼층(115) 상에는 제1 게이트 전극(121)과 제2 반도체층(125)이 형성된다.

[0056] 제2 반도체층(125)은 채널 영역(126)과 채널 영역(126)의 양측에 각각 형성된 소스 영역(128) 및 드레인 영역(127)으로 구분된다. 제2 반도체층(125)의 채널 영역(126)은 불순물이 도핑되지 않은 다결정 규소층, 즉 진성 반도체이다. 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)은 불순물이 도핑된 다결정 규소층이다. 이때, 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)에 도핑되는 불순물은 P형 불순물이다. 일례로, 봉소(B) 이온과 같은 물질이 P형 불순물로 사용된다. 하지만, 본 발명의 제1 실시예가 전술한 바에 한정되는 것은 아니다. 따라서, 도핑되는 불순물이 N형 불순물일 수 있다. 이 경우, 인(P) 이온과 같은 물질이 N형 불순물로 사용될 수 있다.

[0057] 제1 게이트 전극(121)은 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)과 동일하게 형성된다. 즉, 제1 게이트 전극(121)은 불순물이 도핑된 다결정 규소층으로 형성된다. 제1 게이트 전극(121)은 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)이 형성될 때 동일한 층에 함께 형성된다.

[0058] 제1 게이트 전극(121) 및 제2 반도체층(125) 상에는 질화 규소(SiNx) 또는 산화 규소(SiOx) 등으로 형성된 게이트 절연막(130)이 형성된다. 하지만, 본 발명의 제1 실시예에서, 게이트 절연막(130)의 소재가 전술한 바에 한정되는 것은 아니다.

[0059] 게이트 절연막(130) 상에는 제2 게이트 전극(145)과 제1 반도체층(141)이 형성된다. 또한, 제1 반도체층(141)의 일부 영역 바로 위에 복수의 에칭 스토퍼층들(143, 144)이 형성된다.

[0060] 제1 반도체층(141)은 적어도 일부 영역이 제1 게이트 전극(121)과 중첩된다. 그리고 제1 반도체층(141)은 산화물 반도체층으로 형성된다. 제1 반도체층(141)은 갈륨(Ga), 인듐(In), 아연(Zn), 및 주석(Sn) 중에서 하나 이상의 원소와 산소(O)를 포함하는 산화물로 형성된다. 예를 들어, 제1 반도체층(141)은 InZnO, InGaO, InSnO, ZnSnO, GaSnO, GaZnO, 및 GaInZnO 등의 혼합 산화물로 만들어질 수 있다.

[0061] 산화물 반도체를 사용하는 제1 박막 트랜지스터(10)는 수소화 비정질 규소를 사용하는 박막 트랜지스터에 비하여 전하의 유효 이동도(effective mobility)가 2 내지 100배 정도 크고, 온/오프 전류비가  $10^5$  내지  $10^8$ 의 값을 갖는다. 즉, 산화물 반도체를 사용한 제1 박막 트랜지스터(10)는 상대적으로 뛰어난 반도체 특성을 갖는다.

또한, 산화물 반도체의 경우, 밴드갭(band gap)이 약 3.0eV 내지 3.5eV 이므로 가시광에 대하여 누설 광전류가 발생하지 않는다. 따라서, 제1 박막 트랜지스터(10)의 순간 잔상을 방지할 수 있다. 또한, 제1 박막 트랜지스터(10)의 특성을 향상시키기 위해, 제1 반도체층(141)에 주기율표상의 3족, 4족, 5족 또는 전이원소가 추가로 포함시킬 수 있다.

[0062] 에칭 스토퍼층(143, 144)은 알루미늄(Al), 몰리브덴(Mo), 니켈(Ni), 은(Ag), 크롬(Cr), 티타늄(Ti), 및 탄탈(Ta) 중에서 어느 하나의 금속이나 하나 이상의 금속을 포함하는 합금 등으로 형성된다.

[0063] 제2 게이트 전극(145)은 제2 반도체층(125)의 채널 영역(126)과 중첩되도록 형성된다. 제2 게이트 전극(145)은 제2 반도체층(125)을 형성하는 과정에서 제2 반도체층(125)의 소스 영역(128)과 드레인 영역(127)에 불순물을 도핑할 때 채널 영역(126)에는 불순물이 도핑되는 것을 차단하는 역할을 한다. 그리고 제2 게이트 전극(145)은 제1 반도체층(141)과 동일한 물질, 즉 산화물 반도체층으로 형성된 제1 전극층(1451)과 제1 전극층(1451) 위에 에칭 스토퍼층(144)과 동일한 물질, 즉 금속층으로 형성된 제2 전극층(1454)을 포함한다. 이와 같이, 제2 전극층(1451)은 제1 반도체층(141)과 함께 형성되고, 제2 전극층(1454)은 에칭 스토퍼층(144)과 함께 형성된다.

[0064] 제1 반도체층(141), 에칭 스토퍼층(143, 144), 및 제2 게이트 전극(145) 상에는 충간 절연막(150)이 형성된다. 충간 절연막(150)은 복수의 에칭 스토퍼층들(143, 144)을 각각 드러내는 제1 소스 접촉 구멍(153)과 제1 드레인 접촉 구멍(154)을 갖는다. 또한, 충간 절연막(150)과 게이트 절연막(130)은 함께 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)의 일부를 각각 드러내는 제2 소스 접촉 구멍(155)과 제2 드레인 접촉 구멍(156)을 갖는다. 충간 절연막(150)은 게이트 절연막(130)과 마찬가지로 질화 규소(SiNx) 또는 산화 규소(SiOx) 등으로 형성될 수 있으나, 이에 한정되는 것은 아니다.

[0065] 충간 절연막(150) 상에는 제1 소스 전극(163), 제1 드레인 전극(164), 제2 소스 전극(165), 및 제2 드레인 전극(166)이 형성된다.

[0066] 제1 소스 전극(163) 및 제1 드레인 전극(164)은 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)을 통해 복수의 에칭 스토퍼층들(143, 144)과 각각 접촉되며 서로 이격된다. 제1 소스 전극(163) 및 제1 드레인 전극(164)은 각각 에칭 스토퍼층들(143, 144)을 통해 제1 반도체층(141)과 간접적으로 연결된다.

[0067] 제2 소스 전극(165) 및 제2 드레인 전극(166)은 제2 소스 접촉 구멍(155) 및 제2 드레인 접촉 구멍(156)을 통해 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)과 각각 접촉되며 서로 이격된다.

[0068] 접촉 구멍들(153, 154, 155, 156)은 동일한 식각 공정을 통해 충간 절연막(150) 또는 충간 절연막(150)과 게이트 절연막(130)을 함께 식각하여 형성된다. 구체적으로, 제2 소스 접촉 구멍(155) 및 제2 드레인 접촉 구멍(156)은 충간 절연막(150)과 게이트 절연막(130)을 함께 식각하여 형성되는 반면, 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)은 충간 절연막(150)만을 식각하여 형성된다. 따라서 제2 소스 접촉 구멍(155) 및 제2 드레인 접촉 구멍(156)을 완성하기 위해 게이트 절연막(130)을 식각하는 과정에서, 제1 소스 접촉 구멍(153) 및 제2 드레인 접촉 구멍(154)은 완성된 후에도 계속 식각액에 노출된다. 이에, 제1 소스 접촉 구멍(153) 및 제2 드레인 접촉 구멍(154)이 불필요하게 깊어지거나 주변의 다른 구성이 손상될 수 있다. 하지만, 본 발명의 제1 실시예에 따른 유기 발광 표시 장치(101)는 별도의 추가 공정을 거치지 않고 제2 게이트 전극(145)을 형성하는 과정에서 함께 형성된 에칭 스토퍼층들(143, 144)은 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)이 안정적으로 형성될 수 있도록 돋는다. 즉, 복수의 에칭 스토퍼층들(143, 144)을 통해 각 접촉 구멍들(153, 154, 155, 156)을 형성하기 위한 식각 환경을 효과적으로 제어할 수 있다.

[0069] 에칭 스토퍼층(143, 144)은 질화 규소(SiNx) 또는 산화 규소(SiOx) 등으로 형성된 충간 절연막(150) 및 게이트 절연막(130)과 상대적으로 식각 선택비가 차이나는 금속층으로 형성된다.

[0070] 또한, 복수의 에칭 스토퍼들(143, 144)은 제1 게이트 전극(121)의 외곽에 위치한다.

[0071] 이와 같은 구성에 의하여, 본 발명의 제1 실시예에 따른 유기 발광 표시 장치(101)는 상대적으로 단순한 구조를 가지고 안정적으로 산화물 박막 트랜지스터인 제1 박막 트랜지스터(10)와 다결정 규소 박막 트랜지스터인 제2 박막 트랜지스터(20)를 함께 사용하여 전체적인 성능을 효율적으로 향상시킬 수 있다.

[0072] 즉, 유기 발광 표시 장치(101)의 전체적인 구조를 단순화시켜 제1 박막 트랜지스터(101)의 에칭 스토퍼층(143, 144)과 제2 박막 트랜지스터(20)의 제2 게이트 전극(145)을 함께 형성하고, 제1 박막 트랜지스터(10)의 제1 게이트 전극(121)과 제2 박막 트랜지스터(20)의 제2 반도체층(125)을 함께 형성할 수 있다. 또한, 에칭 스토퍼층(143, 144)을 통해 안정적으로 유기 발광 표시 장치(101)를 형성할 수 있다.

- [0073] 또한, 유기 발광 소자(70)와 직접 연결되어 유기 발광 소자(70)를 구동하는 제1 박막 트랜지스터(10)로는 균일성이 상대적으로 우수한 산화물 박막 트랜지스터를 사용하고, 비표시 영역(NA)의 구동 회로나 화소(PE)의 스위칭 또는 보상 회로 등에 사용되는 제2 박막 트랜지스터(20)는 전자 이동도가 상대적으로 우수한 다결정 규소 박막 트랜지스터를 사용할 수 있다.

- [0074] 따라서, 유기 발광 표시 장치(101)는 균일성 및 전자 이동도와 같은 박막 트랜지스터의 성능 향상과 함께 안정성 및 생산성을 모두 향상시킬 수 있다.

- [0075] 또한, N형으로 형성된 제1 박막 트랜지스터(10)와 P형으로 형성된 제2 박막 트랜지스터(20)를 조합하여 구동 회로에 사용되는 CMOS 박막 트랜지스터를 형성할 수도 있다.

- [0076] 이하, 도 4 내지 도 7을 참조하여 본 발명의 제1 실시예에 따른 유기 발광 표시 장치(101)의 제조 방법을 제1 박막 트랜지스터(10) 및 제2 박막 트랜지스터(20)의 형성 과정을 중심으로 설명한다.

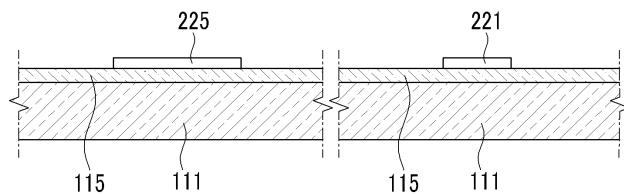

- [0077] 먼저, 도 4에 도시한 바와 같이, 기판 본체(111) 상에 다결정 규소층을 형성한다. 다결정 규소층은 먼저 비정질 규소층을 형성하고 이를 결정화시키는 방법으로 형성할 수 있다. 비정질 규소층을 결정화시키는 방법으로는 해당 기술 분야의 종사자에게 공지된 다양한 방법을 사용할 수 있다. 예를 들어, 비정질 규소층은 열, 레이저, 줄열, 전기장, 또는 촉매 금속 등을 이용하여 결정화시킬 수 있다. 그리고 다결정 규소층을 패터닝(patterning)하여 제1 게이트 전극 중간체(221) 및 제2 반도체층 중간체(225)를 형성한다.

- [0078] 다음, 도 5에 도시한 바와 같이, 제1 게이트 전극 중간체(221)와 제2 반도체층 중간체(225) 상에 게이트 절연막(130)을 형성한다. 게이트 절연막(130)은 질화 규소(SiNx) 또는 산화 규소(SiOx) 등으로 형성될 수 있다.

- [0079] 다음, 게이트 절연막(130) 상에 산화물 반도체층(1401)과 금속층(1402)을 차례로 증착한다. 이때, 산화물 반도체층(1401)과 금속층(1402)은 진공 분위기에서 연속적으로 증착될 수 있다. 이와 같이, 산화물 반도체층(1401)이 증착된 이후 금속층(1402)을 증착하기 전에 추가적으로 거치는 공정을 최소화시켜 산화물 반도체층(1401)이 불필요하게 손상되는 것을 방지할 수 있다.

- [0080] 산화물 반도체층(1401) 또는 금속층(1402)은 산화물 반도체 또는 금속을 스퍼터링(sputtering) 또는 증발법(evaporation) 등과 같은 물리적 기상 증착(physical vapor deposition, PVD) 법 등 해당 기술 분야의 종사자에게 공지된 다양한 방법을 통해 증착된다.

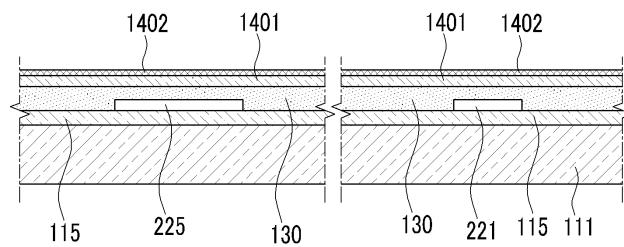

- [0081] 다음, 도 6에 도시한 바와 같이, 적층된 산화물 반도체층(1401) 및 금속층(1402)을 식각 공정을 통해 패터닝하여, 제2 게이트 전극(145), 제1 반도체층(141), 및 복수의 에칭 스토퍼총들(143, 144)을 형성한다. 이때, 식각 공정은 이중 노광 또는 하프톤(halftone) 노광 공정을 포함할 수 있다.

- [0082] 제1 반도체층(141)은 적어도 일부가 제1 게이트 전극 중간체(221)와 중첩되도록 형성되며, 복수의 에칭 스토퍼총들(143, 144)은 각각 제1 반도체층(141)의 일부 영역 위에 형성된다. 또한, 복수의 에칭 스토퍼총들(143, 144)은 제1 게이트 전극 중간체(221)의 외곽에 위치하도록 형성된다. 이때, 복수의 에칭 스토퍼총들(143, 144)은 제1 게이트 전극 중간체(221)와는 가급적 중첩되지 않는 것이 바람직하다. 이는 금속층(1402)으로 형성된 에칭 스토퍼총(143, 144)은 제1 게이트 전극 중간체(221)에 불순물이 도핑되는 것을 차단할 수 있기 때문이다.

- [0083] 제2 게이트 전극(145)은 제2 반도체층 중간체(225)의 일부와 중첩되도록 형성된다. 또한, 제2 게이트 전극(145)은 산화물 반도체층(1401)이 패터닝된 제1 전극층(1451)과 금속층(1402)이 패터닝된 제2 전극층(1454)을 포함한다.

- [0084] 다음, 제1 게이트 전극 중간체(221) 및 제2 반도체층 중간체(225)에 불순물을 도핑하여 제1 게이트 전극(121) 및 제2 반도체층(125)을 형성한다. 이때, 불순물은 제1 반도체층(141)은 투과하여 제1 게이트 전극 중간체(221)에 도핑된다. 반면, 전술한 바와 같이, 불순물은 에칭 스토퍼총(143, 144)을 거의 투과하지 못한다.

- [0085] 제2 반도체층(125)은 제2 게이트 전극(145)에 의해 불순물 도핑이 차단된 채널 영역(126)과, 불순물이 도핑되어 채널 영역(126)의 양측에 형성된 소스 영역(128) 및 드레인 영역(127)으로 구분된다. 그리고, 제1 게이트 전극(121)은 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)과 동일하게 불순물이 도핑된 다결정 규소층으로 형성된다. 도 6에서 화살표는 불순물이 도핑되는 것을 나타낸다.

- [0086] 이와 같이, 본 발명의 제1 실시예에서는 도전성을 갖는 불순물이 도핑된 다결정 규소층을 제1 게이트 전극(121)으로 사용하여, 유기 발광 표시 장치(101)의 전체적인 구조를 간소화시킬 수 있다. 즉, 제1 게이트 전극(121)과 제2 반도체층(125)을 각각 별도로 형성하지 않고, 제2 반도체층(125)을 형성하는 과정에서 제1 게이트

전극(121)을 함께 형성하여 유기 발광 표시 장치의 전체적인 제조 공정을 단순화시킬 수 있다.

[0087] 다음, 도 7에 도시한 바와 같이, 제1 반도체층(141), 에칭 스토퍼층(143, 144), 및 제2 게이트 전극(145) 상에 충간 절연막(150)을 형성한다. 그리고 충간 절연막(150)을 식각하여 복수의 에칭 스토퍼층들(143, 144)의 일부를 각각 드러내는 제1 소스 접촉 구멍(153)과 제1 드레인 접촉 구멍(154)을 형성한다. 또한, 충간 절연막(150)과 게이트 절연막(130)을 함께 식각하여 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)의 일부를 각각 드러내는 제2 소스 접촉 구멍(155)과 제2 드레인 접촉 구멍(156)을 형성한다.

[0088] 다음, 앞서 도 3에 도시한 바와 같이, 충간 절연막(150) 상에 제1 소스 전극(163), 제1 드레인 전극(164), 제2 소스 전극(165), 및 제2 드레인 전극(166)을 형성한다.

[0089] 제1 소스 전극(163) 및 제1 드레인 전극(164)은 각각 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)과 에칭 스토퍼층들(143, 144) 통해 제1 반도체층(141)과 간접적으로 연결된다. 즉, 본 발명의 제1 실시예에서, 에칭 스토퍼층(143, 144)은 제1 소스 전극(163) 및 제1 드레인 전극(164)과 제1 반도체층(141) 사이에 배치되어 이들을 전기적으로 연결시킨다.

[0090] 제2 소스 전극(165) 및 제2 드레인 전극(166)은 각각 제2 소스 접촉 구멍(155)과 제2 드레인 접촉 구멍(156)을 통해 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)과 연결된다.

[0091] 이상과 같은 제조 방법을 통하여, 본 발명의 제1 실시예에 따른 유기 발광 표시 장치(101)를 효과적으로 제조할 수 있다.

[0092] 일반적으로 다결정 규소 박막 트랜지스터와 산화물 박막 트랜지스터를 함께 사용할 경우, 다결정 규소 박막 트랜지스터와 산화물 박막 트랜지스터의 구조 및 사용되는 소재가 서로 사용하여 제조 공정이 복잡해 진다.

[0093] 하지만, 본 발명의 제1 실시예에 따르면, 산화물 박막 트랜지스터인 제1 박막 트랜지스터(10)와 다결정 규소 박막 트랜지스터인 제2 박막 트랜지스터(20)를 효과적으로 형성할 수 있다.

[0094] 구체적으로, 제1 박막 트랜지스터(10)의 제1 게이트 전극(121)과 제2 박막 트랜지스터(20)의 제2 반도체층(125)을 동일층에 함께 형성할 수 있어 유기 발광 표시 장치(101)의 전체적인 제조 공정을 단순화시킬 수 있다.

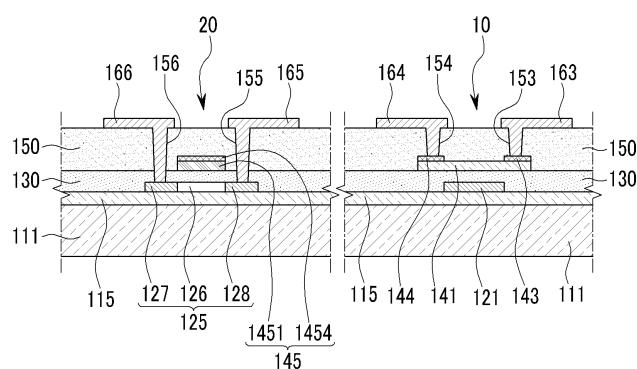

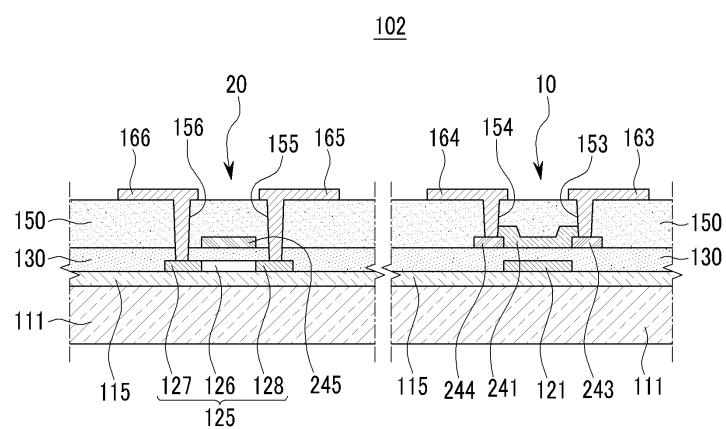

[0095] 이하, 도 8을 참조하여 본 발명의 제2 실시예를 설명한다.

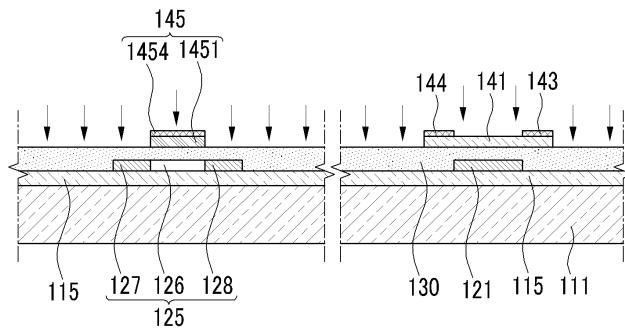

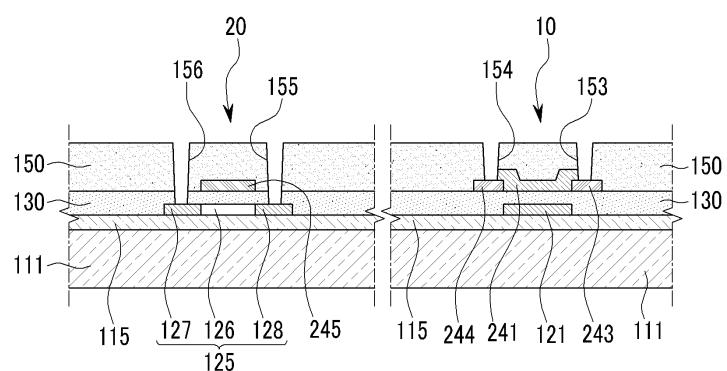

[0096] 도 8에 도시한 바와 같이, 본 발명의 제2 실시예에 따른 유기 발광 표시 장치(102)는 에칭 스토퍼층(243, 244)의 일부가 제1 박막 트랜지스터(10)의 제1 반도체층(241) 바로 아래에 위치한다. 또한, 복수의 에칭 스토퍼들(243, 244)은 제1 게이트 전극(121)의 외곽에 위치한다.

[0097] 충간 절연막(150)의 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)은 각각 복수의 에칭 스토퍼층들(243, 244)의 일부를 드러낸다. 즉, 제1 반도체층(241)과 중첩되지 않은 복수의 에칭 스토퍼층들(243, 244)의 일부가 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)을 통해 드러난다. 그리고 제1 소스 전극(163) 및 제1 드레인 전극(164)은 각각 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)과 복수의 에칭 스토퍼층들(243, 244)을 통해 제1 반도체층(241)과 연결된다.

[0098] 에칭 스토퍼층(243, 244)은 알루미늄(Al), 몰리브덴(Mo), 니켈(Ni), 은(Ag), 크롬(Cr), 티타늄(Ti), 및 탄탈(Ta) 중에서 어느 하나의 금속이나 하나 이상의 금속을 포함하는 합금 등으로 형성된다. 즉, 에칭 스토퍼층(243, 244)은 질화 규소(SiNx) 또는 산화 규소(SiOx) 등으로 형성된 충간 절연막(150) 및 게이트 절연막(130)과 상대적으로 식각 선택비가 차이나는 금속층으로 형성된다.

[0099] 또한, 제2 게이트 전극(245)은 복수의 에칭 스토퍼층들(243, 244)과 동일한 층에 동일한 소재로 함께 형성된다.

[0100] 이와 같이, 본 발명의 제2 실시예에 따른 에칭 스토퍼층(243, 244)도 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)이 안정적으로 형성될 수 있도록 돋는다. 즉, 복수의 에칭 스토퍼층들(243, 244)은 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)이 필요 이상으로 깊어지거나 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154) 주변의 구성이 손상되는 것을 방지할 수 있다.

[0101] 따라서, 본 발명의 제2 실시예에 따른 유기 발광 표시 장치(102)도 상대적으로 단순한 구조를 가지고 안정적으로 산화물 박막 트랜지스터인 제1 박막 트랜지스터(10)와 다결정 규소 박막 트랜지스터인 제2 박막 트랜지스터(20)를 함께 사용하여 전체적인 성능을 효율적으로 향상시킬 수 있다.

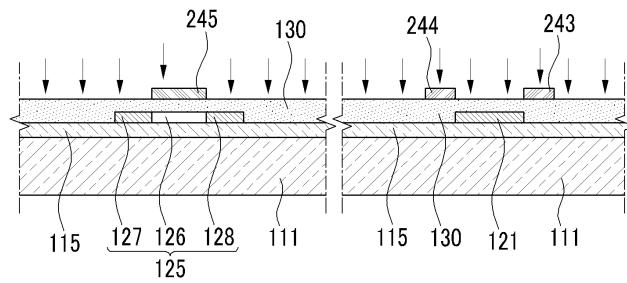

[0102] 이하, 도 9 내지 도 11을 참조하여 본 발명의 제2 실시예에 따른 유기 발광 표시 장치(102)의 제조 방법을 제1

실시예와의 차이점을 중심으로 설명한다.

[0103] 도 9에 도시한 바와 같이, 기판 본체(111) 상에 베퍼층(115)을 형성하고, 베퍼층(115) 위에 제1 게이트 전극 중간체와 제2 반도체층 중간체를 형성한다. 그리고 제1 게이트 전극 중간체와 제2 반도체층 중간체 상에 게이트 절연막(130)을 형성한다.

[0104] 다음, 게이트 절연막(130) 상에 금속층을 증착한 후 이를 패터닝하여 제2 게이트 전극(245)과 복수의 에칭 스토퍼층들(243, 244)을 형성한다. 제2 게이트 전극(245)은 제2 반도체층 중간체의 일부와 중첩되도록 형성된다. 복수의 에칭 스토퍼들(243, 244)은 제1 게이트 전극 중간체의 외곽에 형성되며, 제1 게이트 전극 중간체와는 가급적 중첩되지 않는 것이 바람직하다.

[0105] 다음, 제1 게이트 전극 중간체 및 제2 반도체층 중간체에 불순물을 도핑하여 제1 게이트 전극(121) 및 제2 반도체층(125)을 형성한다. 이때, 불순물은 에칭 스토퍼층(243, 244)을 거의 투과하지 못한다.

[0106] 제2 반도체층(125)은 제2 게이트 전극(245)에 의해 불순물 도핑이 차단된 채널 영역(126)과, 불순물이 도핑되어 채널 영역(126)의 양측에 형성된 소스 영역(128) 및 드레인 영역(127)으로 구분된다. 그리고, 제1 게이트 전극(121)은 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)과 동일하게 불순물이 도핑된 다결정 규소층으로 형성된다. 도 9에서 화살표는 불순물이 도핑되는 것을 나타낸다.

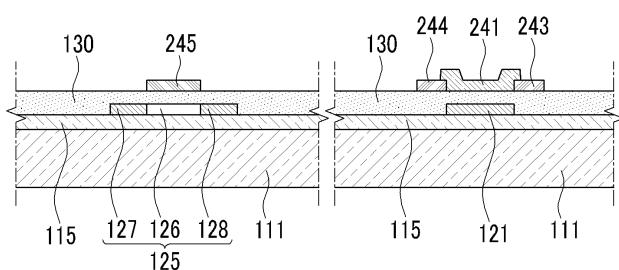

[0107] 다음, 도 10에 도시한 바와 같이, 복수의 에칭 스토퍼들(243, 244) 위에 산화물 반도체층을 형성한 후 이를 패터닝하여 제1 반도체층(241)을 형성한다. 제1 반도체층(241)은 게이트 절연막(130)을 사이에 두고 제1 게이트 전극(121) 상에 위치하며, 복수의 에칭 스토퍼들(243, 244) 바로 위에 일부가 중첩된다.

[0108] 다음, 도 11에 도시한 바와 같이, 제1 반도체층(241), 에칭 스토퍼층(243, 244), 및 제2 게이트 전극(245) 상에 충간 절연막(150)을 형성한다. 그리고 충간 절연막(150)을 식각하여 복수의 에칭 스토퍼층들(243, 244)의 일부를 각각 드러내는 제1 소스 접촉 구멍(153)과 제1 드레인 접촉 구멍(154)을 형성한다. 또한, 충간 절연막(150)과 게이트 절연막(130)을 함께 식각하여 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)의 일부를 각각 드러내는 제2 소스 접촉 구멍(155)과 제2 드레인 접촉 구멍(156)을 형성한다.

[0109] 다음, 앞서 도 3에 도시한 바와 같이, 충간 절연막(150) 상에 제1 소스 전극(163), 제1 드레인 전극(164), 제2 소스 전극(165), 및 제2 드레인 전극(166)을 형성한다.

[0110] 제1 소스 전극(163) 및 제1 드레인 전극(164)은 각각 제1 소스 접촉 구멍(153) 및 제1 드레인 접촉 구멍(154)과 에칭 스토퍼층들(243, 244) 통해 제1 반도체층(141)과 직간접적으로 연결된다. 즉, 본 발명의 제2 실시예에서, 제1 소스 전극(163) 및 제2 드레인 전극(164)은 에칭 스토퍼층(243, 244)을 거쳐 제1 반도체층(241)과 연결되거나 직접 제1 반도체층(241)과 연결될 수 있다.

[0111] 제2 소스 전극(165) 및 제2 드레인 전극(166)은 각각 제2 소스 접촉 구멍(155)과 제2 드레인 접촉 구멍(156)을 통해 제2 반도체층(125)의 소스 영역(128) 및 드레인 영역(127)과 연결된다.

[0112] 이상과 같은 제조 방법을 통하여, 본 발명의 제2 실시예에 따른 유기 발광 표시 장치(102)를 효과적으로 제조할 수 있다.

[0113] 본 발명을 앞서 기재한 바에 따라 바람직한 실시예를 통해 설명하였지만, 본 발명은 이에 한정되지 않으며 다음에 기재하는 특허청구범위의 개념과 범위를 벗어나지 않는 한, 다양한 수정 및 변형이 가능하다는 것을 본 발명이 속하는 기술 분야에 종사하는 자들은 쉽게 이해할 것이다.

### 도면의 간단한 설명

[0114] 도 1은 본 발명의 제1 실시예에 따른 유기 발광 표시 장치의 구조를 개략적으로 나타낸 평면도이다.

[0115] 도 2는 도 1의 유기 발광 표시 장치가 갖는 화소 회로를 나타낸 회로도이다.

[0116] 도 3은 도 1의 유기 발광 표시 장치에 사용된 박막 트랜지스터들을 확대 도시한 부분 단면도이다.

[0117] 도 4 내지 도 7은 도 3의 박막 트랜지스터들의 제조 과정을 순차적으로 나타낸 단면도들이다.

[0118] 도 8은 본 발명의 제2 실시예에 따른 유기 발광 표시 장치에 사용된 박막 트랜지스터들을 확대 도시한 부분 단

면도이다.

[0119] 도 9 내지 도 11은 도 8의 박막 트랜지스터들의 제조 과정을 순차적으로 나타낸 단면도들이다.

## 도면

### 도면1

### 도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

专利名称(译) 有机发光显示器及其制造方法

公开(公告)号 KR101065407B1 公开(公告)日 2011-09-16

申请号 KR1020090078946 申请日 2009-08-25

[标]申请(专利权)人(译) 三星显示有限公司

申请(专利权)人(译) 三圣母工作显示有限公司

当前申请(专利权)人(译) 三圣母工作显示有限公司

[标]发明人 CHOI JONG HYUN

최종현

LEE JUNE WOO

이준우

KIM KWANG HAE

김광해

KIM KYOUNG BO

김경보

发明人 최종현

이준우

김광해

김경보

IPC分类号 H01L51/50 H01L29/786

CPC分类号 H01L27/1251 H01L27/1225 H01L27/3262 H01L21/02579 H01L2251/308

其他公开文献 KR1020110021259A

外部链接 [Espacenet](#)

#### 摘要(译)

目的：提供一种有机发光显示装置及其制造方法，通过配置补偿电路来改善形成在每个像素上的有机发光装置的均匀性，从而防止图像质量的偏差。组成：第一栅电极（121）和第二半导体层（125）形成在基板主体（111）上。栅绝缘层（130）形成在第一栅电极和第二半导体层上。在第一栅电极和第二半导体层上形成半导体层（141）和第二栅电极（145）。