(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0084730

(43) 공개일자 2008년09월19일

(51) Int. Cl.

G09G 3/30 (2006.01) G09G 3/32 (2006.01)

G09G 3/20 (2006.01) H05B 33/12 (2006.01)

(21) 출원번호 10-2008-0023893

(22) 출원일자 2008년03월14일

심사청구일자 없음

(30) 우선권주장

JP-P-2007-00068020 2007년03월16일 일본(JP)

(71) 출원인

소니 가부시끼 가이샤

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

도요무라 나오부미

일본 도쿄도 미나토구 고난 1-7-1 소니 가부시끼

가이샤 내

우찌노 가쓰히데

일본 도쿄도 미나토구 고난 1-7-1 소니 가부시끼

가이샤 내

이이다 유기히또

일본 도쿄도 미나토구 고난 1-7-1 소니 가부시끼

가이샤 내

(74) 대리인

장수길, 이중희

전체 청구항 수 : 총 8 항

## (54) 화소 회로 및 표시 장치와 그 구동 방법

## (57) 요약

이동도 보정 기능을 갖는 유기 EL 표시 장치에서, 영상 신호 진폭을 크게 하여도, 이동도 보정에 기인하는 발광 휘도 저하를 방지할 수 있게 한다. 발광 제어 트랜지스터(122)의 게이트단 G와 구동 트랜지스터(121)의 소스단 S에 용량 소자(129)를 추가한다. 이동도 보정에 따른 게이트-소스간 전압  $V_{gs}$ 의 저하분  $\Delta V$ 를, 이동도 보정 동작의 개시시에, 이동도 보정시에 소비되는 분의 전압  $\Delta V$ 를 발광 제어 트랜지스터(122)에 공급되는 주사 구동 웨尔斯 DS에 의한 커플링에 의해 전압  $V_{DSb}$ 의 분만큼 상승시켜 보충함으로써, 발광 기간에서의 게이트-소스간 전압  $V_{gs}$ 를 넓힌다. 이동도 보정에 기인하는 발광 휘도 저하를 방지할 수 있고, 영상 신호  $V_{sig}$ 의 진폭을 낮출 수 있어, 통상의 영상 신호  $V_{sig}$ 만을 축적 캐패시터(120)에 기입하는 것만으로 충분하여, 저소비 전력화에 기여할 수 있다.

## 대표 도

## 특허청구의 범위

### 청구항 1

구동 전류를 생성하는 구동 트랜지스터, 상기 구동 트랜지스터의 출력단에 접속된 전기 광학 소자, 영상 신호의 신호 전위에 따른 정보를 보유하는 축적 캐패시터, 상기 신호 전위에 따른 정보를 상기 축적 캐패시터에 기입하는 샘플링 트랜지스터, 및 한쪽의 단자가 상기 구동 트랜지스터의 출력단에 접속되고 다른 쪽의 단자에 펄스 신호가 공급되는 용량 소자를 구비하고, 상기 축적 캐패시터에 유지된 정보에 기초하는 구동 전류를 상기 구동 트랜지스터에서 생성하고 상기 구동 전류를 상기 전기 광학 소자에 흘림으로써 상기 전기 광학 소자가 발광하는 화소 회로가 행렬 형상으로 배치되는 화소 어레이부; 및

상기 샘플링 트랜지스터를 수평 주기에서 순차적으로 제어함으로써 상기 화소 회로를 선-순차 주사해서 1행분의 각 축적 캐패시터에 영상 신호의 신호 전위에 따른 정보를 기입하기 위한 기입 주사 펄스를 상기 샘플링 트랜지스터에 출력하는 기입 주사부, 및 상기 샘플링 트랜지스터의 신호 전위의 기입 동작에 따라 1행분의 영상 신호를 영상 신호선에 공급하는 수평 구동부를 포함하는 제어부를 구비하고,

상기 제어부는, 상기 샘플링 트랜지스터를 도통 상태로 설정하고 상기 신호 전위에 따른 정보를 상기 축적 캐패시터에 유지시킨 후에, 상기 샘플링 트랜지스터를 도통 상태로 유지한 채로 상기 구동 트랜지스터의 이동도에 대한 보정량을 상기 축적 캐패시터에 기입되는 정보에 부가하기 위한 이동도 보정 동작을 행하도록 제어하고,

상기 용량 소자의 다른 쪽의 단자에는 상기 이동도 보정 동작을 개시시키는 펄스에 대응하는 정보가 공급되고,

상기 구동 트랜지스터의 출력단에는, 상기 구동 트랜지스터의 제어 입력단과 출력단 사이의 전위차가 커지는 방향의 천이 정보가 상기 용량 소자를 통해서 공급되는 표시 장치.

### 청구항 2

제1항에 있어서,

상기 전기 광학 소자의 발광 기간과 비발광 기간 사이의 뉴티비를 조정하는 발광 제어 트랜지스터를 더 구비하고,

상기 발광 제어 트랜지스터의 제어 입력단에 공급되는 주사 구동 펄스를, 상기 이동도 보정 동작을 개시시키는 펄스로서 설정하는 표시 장치.

### 청구항 3

제1항에 있어서,

n형 및 p형 중 어느 하나의 형의 상기 구동 트랜지스터의 전원 공급단측에 배치되고, 상기 전기 광학 소자의 발광 기간과 비발광 기간 사이의 뉴티비를 조정하는, 상기 n형 및 p형 중 다른 하나의 형의 발광 제어 트랜지스터를 더 구비하고,

상기 용량 소자의 다른 쪽의 단자는 상기 발광 제어 트랜지스터의 제어 입력단에 접속되고,

상기 발광 제어 트랜지스터의 제어 입력단에 공급되는 주사 구동 펄스를, 상기 이동도 보정 동작을 개시시키는 펄스로서 설정하는 표시 장치.

### 청구항 4

제1항에 있어서,

상기 제어부는, 상기 샘플링 트랜지스터에 기준 전위가 공급되는 시간 주기에서 상기 샘플링 트랜지스터를 도통시키고, 상기 구동 트랜지스터의 임계값 전압에 대응하는 전압을 상기 축적 캐패시터에 유지하기 위한 임계값 보정 동작을 행하도록 제어하고, 상기 임계값 보정 동작 후, 상기 구동 트랜지스터의 이동도에 대한 보정량을 상기 축적 캐패시터에 기입되는 정보에 부가하기 위한 이동도 보정 동작을 행하도록 제어하는 표시 장치.

### 청구항 5

제4항에 있어서,

상기 화소 회로는, 상기 구동 트랜지스터 및 상기 샘플링 트랜지스터 외에, 상기 제어부에 의한 상기 임계값 보정 동작 및 상기 이동도 보정 동작시의 제어 펄스에 기초하여 온/오프 동작하는 스위치 트랜지스터를 각각 구비하는 표시 장치.

#### 청구항 6

구동 전류를 생성하는 구동 트랜지스터;

상기 구동 트랜지스터의 출력단에 접속된 전기 광학 소자;

영상 신호의 신호 전위에 따른 정보를 유지하는 축적 캐패시터;

상기 신호 전위에 따른 정보를 상기 축적 캐패시터에 기입하는 샘플링 트랜지스터; 및

한쪽의 단자가 상기 구동 트랜지스터의 출력단에 접속된 용량 소자를 구비하고,

상기 용량 소자의 다른 쪽의 단자에는, 상기 구동 트랜지스터의 이동도에 대한 보정량을 상기 축적 캐패시터에 기입되는 정보에 부가하기 위한 이동도 보정 동작을 개시시키는 펄스에 대응하는, 상기 구동 트랜지스터의 제어 입력단과 출력단 사이의 전위차를 크게 하는 방향의 천이 정보가 공급되는 것을 특징으로 하는 화소 회로.

#### 청구항 7

구동 전류를 생성하는 구동 트랜지스터, 상기 구동 트랜지스터의 출력단에 접속된 전기 광학 소자, 영상 신호의 신호 전위에 따른 정보를 유지하는 축적 캐패시터, 상기 신호 전위에 따른 정보를 상기 축적 캐패시터에 기입하는 샘플링 트랜지스터, 및 한쪽의 단자가 상기 구동 트랜지스터의 출력단에 접속되고 다른 쪽의 단자에 펄스 신호가 공급되는 용량 소자를 구비하고, 상기 구동 트랜지스터가 상기 축적 캐패시터에 유지된 정보에 기초하는 구동 전류를 생성해서 상기 전기 광학 소자에 흘림으로써, 상기 전기 광학 소자가 발광하는 화소 회로의 구동 방법으로서,

상기 샘플링 트랜지스터를 도통 상태로 설정해서 상기 신호 전위에 따른 정보를 상기 축적 캐패시터에 유지시킨 후에, 상기 샘플링 트랜지스터를 도통 상태로 유지한 채로 상기 구동 트랜지스터의 이동도에 대한 보정량을 상기 축적 캐패시터에 기입되는 정보에 부가하기 위한 이동도 보정 동작을 행할 때에, 상기 이동도 보정 동작을 개시시키는 펄스에 대응하는 정보를 상기 용량 소자의 다른 쪽의 단자에 공급하여, 상기 구동 트랜지스터의 제어 입력단과 출력단 사이의 전위차를 크게 하는 구동 방법.

#### 청구항 8

구동 전류를 생성하는 구동 트랜지스터, 상기 구동 트랜지스터의 출력단에 접속된 전기 광학 소자, 영상 신호의 신호 전위에 따른 정보를 보유하는 축적 캐패시터, 상기 신호 전위에 따른 정보를 상기 축적 캐패시터에 기입하는 샘플링 트랜지스터, 및 한쪽의 단자가 상기 구동 트랜지스터의 출력단에 접속되고 다른 쪽의 단자에 펄스 신호가 공급되는 용량 소자를 구비하고, 상기 축적 캐패시터에 유지된 정보에 기초하는 구동 전류를 상기 구동 트랜지스터에서 생성하고 상기 구동 전류를 상기 전기 광학 소자에 흘림으로써 상기 전기 광학 소자가 발광하는 화소 회로가 행렬 형상으로 배치되는 화소 어레이 수단; 및

상기 샘플링 트랜지스터를 수평 주기에서 순차적으로 제어함으로써 상기 화소 회로를 선-순차 주사해서 1행분의 각 축적 캐패시터에 영상 신호의 신호 전위에 따른 정보를 기입하기 위한 기입 주사 펄스를 상기 샘플링 트랜지스터에 출력하는 기입 주사부, 및 상기 샘플링 트랜지스터의 신호 전위의 기입 동작에 따라 1행분의 영상 신호를 영상 신호선에 공급하는 수평 구동부를 포함하는 제어 수단을 구비하고,

상기 제어 수단은, 상기 샘플링 트랜지스터를 도통 상태로 설정하고 상기 신호 전위에 따른 정보를 상기 축적 캐패시터에 유지시킨 후에, 상기 샘플링 트랜지스터를 도통 상태로 유지한 채로 상기 구동 트랜지스터의 이동도에 대한 보정량을 상기 축적 캐패시터에 기입되는 정보에 부가하기 위한 이동도 보정 동작을 행하도록 제어하고,

상기 용량 소자의 다른 쪽의 단자에는 상기 이동도 보정 동작을 개시시키는 펄스에 대응하는 정보가 공급되고,

상기 구동 트랜지스터의 출력단에는, 상기 구동 트랜지스터의 제어 입력단과 출력단 사이의 전위차가 커지는 방

향의 천이 정보가 상기 용량 소자를 통해서 공급되는 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 기술분야

<1> 관련 출원의 상호 참조

<2> 본 발명은 2007년 3월 16일부로 일본특허청에 제출된 일본 특허 출원 제2007-068020호에 관한 기술 내용을 포함하며, 그 전체 내용은 이하 참조된다.

<3> 본 발명은 전기 광학 소자(표시 소자나 발광 소자라고도 칭해짐)를 구비하는 화소 회로(화소라고도 칭해짐)와, 이 화소 회로가 행렬 형상으로 배열된 화소 어레이부를 갖는 표시 장치와, 표시 장치의 구동 방법에 관한 것으로, 보다 상세하게는, 구동 신호의 대소에 의해 휘도가 변화되는 전기 광학 소자를 표시 소자로서 갖는 화소 회로와, 이 화소 회로가 행렬 형상으로 배치되어 이루어지고, 화소 회로마다 능동 소자를 가지고 해당 능동 소자에 의해 화소 단위로 표시 구동이 행해지는 액티브 행렬형의 표시 장치와, 액티브 행렬형의 표시 장치의 구동 방법에 관한 것이다.

#### 배경기술

<4> 화소의 표시 소자로서, 인가되는 전압이나 흐르는 전류에 의해 휘도가 변화되는 전기 광학 소자를 이용한 표시 장치가 있다. 예를 들면, 인가되는 전압에 의해 휘도가 변화되는 전기 광학 소자로서는 액정 표시 소자가 대표적이며, 흐르는 전류에 의해 휘도가 변화되는 전기 광학 소자로서는, 유기 일렉트로 루미네센스(유기 EL이라고 기재함) 소자(유기 발광 다이오드(OLED) 소자가 대표예이다. 후자의 유기 EL 소자를 이용한 유기 EL 표시 장치는, 화소의 표시 소자로서 자발광 전기 광학 소자를 이용한 소위 자발광형의 표시 장치이다.

<5> 유기 EL 소자는 유기 박막에 전계를 걸면 발광하는 현상을 이용한 전기 광학 소자이다. 유기 EL 소자는 비교적 낮은 인가 전압(예를 들면 10V 이하)으로 구동될 수 있기 때문에, 저소비 전력이다. 또한, 유기 EL 소자는 스스로 광을 발하는 자발광 소자이기 때문에, 액정 표시 장치에서는 필요로 되는 백라이트 등의 보조 조명 부재를 필요로 하지 않는다. 따라서, 유기 EL 소자는 경량화 및 박형화가 용이하다. 또한, 유기 EL 소자는 매우 빠른 응답 속도(예를 들면 수  $\mu s$  정도)를 갖기 때문에, 동화상 표시시의 잔상이 발생하지 않는다. 유기 EL 소자는 이를 이점을 갖기 때문에, 전기 광학 소자로서 유기 EL 소자를 이용한 평면 자발광형의 표시 장치의 개발이 최근 왕성해지고 있다.

<6> 유기 EL 소자를 대표예로 하는 전류 구동형의 전기 광학 소자에서는, 구동 전류값이 서로 다르면 발광 휘도도 서로 다르다는 것을 의미한다. 따라서, 안정된 휘도로 발광시키기 위해서는, 안정된 구동 전류를 전기 광학 소자에 공급하는 것이 중요하다. 예를 들면, 유기 EL 소자에 구동 전류를 공급하는 구동 방식은 정전류 구동 방식과 정전압 구동 방식으로 대별될 수 있다(이 방식들은 주지의 기술이기 때문에, 여기에서는 공지 문헌의 제시는 하지 않음).

<7> 유기 EL 소자의 전압-전류 특성은 가파른 기울기를 갖기 때문에, 정전압 구동이 행해지면, 약간의 전압의 변동이나 소자 특성의 변동이 큰 전류의 변동을 생기게 하여 큰 휘도 변동을 가져온다. 따라서, 일반적으로는, 구동 트랜지스터가 포화 영역에서 사용되는 정전류 구동이 이용된다. 물론, 정전류 구동에서도, 전류 변동이 있으면 휘도 변동을 초래한다. 그러나, 작은 전류 변동이면 작은 휘도 변동만 생긴다.

<8> 반대로 말하면, 정전류 구동 방식이어도, 전기 광학 소자의 발광 휘도가 불변이기 위해서는, 입력 화상 신호에 따라서 축적 캐패시터에 기입되고 이 축적 캐패시터에 유지되는 구동 신호가 일정한 것이 중요하다. 예를 들면, 유기 EL 소자의 발광 휘도가 불변이기 위해서는, 입력 화상 신호에 따른 구동 전류가 일정한 것이 중요하다.

<9> 그러나, 프로세스 변동에 의해 전기 광학 소자를 구동하는 능동 소자(구동 트랜지스터)의 임계값 전압이나 이동도가 변동된다. 또한, 유기 EL 소자 등의 전기 광학 소자의 특성이 경시적으로 변동된다. 이러한 구동용의 능동 소자의 특성 변동이나 전기 광학 소자의 특성 변동이 있으면, 정전류 구동 방식이어도, 발광 휘도에 영향을 준다.

<10> 이 때문에, 표시 장치의 화면 전체에 걸쳐서 발광 휘도를 균일하게 제어하기 위해서, 각 화소 회로 내에서 전술한 구동용의 능동 소자나 전기 광학 소자의 특성 변동에 기인하는 휘도 변동을 보정하기 위한 다양한 구조가 검토된다.

<11> 예를 들면, 일본특허공개 제2006-215213호 공보(이하 특허 문헌 1이라고 지칭함)에 기재된 구조는 유기 EL 소자용의 화소 회로로서, 구동 트랜지스터의 임계값 전압에 변동이나 경시 변화가 있는 경우라도 구동 전류를 일정하게 하기 위한 임계값 보정 기능이나, 구동 트랜지스터의 이동도에 변동이나 경시 변화가 있는 경우라도 구동 전류를 일정하게 하기 위한 이동도 보정 기능이나, 유기 EL 소자의 전류-전압 특성에 경시 변화가 있는 경우라도 구동 전류를 일정하게 하기 위한 부트스트랩 기능을 갖는다.

## 발명의 내용

### 해결 하고자하는 과제

<12> 그러나, 특허 문헌 1에 기재된 구조에서는, 샘플링 트랜지스터를 턴온시켜서 영상 신호에 대응하는 구동 전위를 축적 캐패시터에 유지시킨 후에 샘플링 트랜지스터를 턴온시킨 채로 이동도 보정 기간에 들어간다. 이 때문에, 구동 트랜지스터의 게이트 전위가 고정된 상태에서 이동도 보정 동작이 행해지고, 이동도 보정에 의해 게이트-소스간 전압이 감소하고, 게이트-소스간 전압의 감소에 대해 취해지는 조치가 없으면 발광 휘도가 저하하게 되는 폐해가 있다.

<13> 이동도 보정에 기인하는 발광 휘도 저하를 방지하는 한 방법으로서, 예를 들면, 이동도 보정에 의한 게이트-소스간 전압의 감소분을 보충하도록, 보다 큰 영상 신호를 공급해서 축적 캐패시터에 구동 전위를 기입하는 것이 생각된다. 그러나 이 방법으로는, 이동도 보정을 행하지 않는 경우에 비하여 영상 신호 진폭을 크게 할 필요가 있다. 따라서, 전원 전압이나 기입 구동 펄스를 크게 할 필요가 생겨서, 소비 전압의 증대로 연결되게 된다.

<14> 본 발명은, 상기 사정을 감안하여 이루어진 것으로, 영상 신호 진폭을 크게 하지 않아도, 이동도 보정에 기인하는 발광 휘도 저하를 방지할 수 있는 구조를 제공하는 것을 목적으로 한다.

### 과제 해결수단

<15> 본 발명에 따른 표시 장치의 일 실시예는, 영상 신호에 기초하여 화소 회로 내의 전기 광학 소자를 발광시키는 표시 장치로서, 우선, 화소 어레이부에 행렬 형상으로 배치되는 각각의 화소 회로는 적어도 구동 전류를 생성하는 구동 트랜지스터, 구동 트랜지스터의 출력단에 접속된 전기 광학 소자, 영상 신호의 신호 전위에 따른 정보(구동 전위)를 유지하는 축적 캐패시터, 및 축적 캐패시터에 영상 신호의 신호 전위에 따른 정보를 기입하는 샘플링 트랜지스터를 구비한다. 이 화소 회로에서는, 축적 캐패시터에 유지된 정보에 기초하는 구동 전류를 구동 트랜지스터에서 생성해서 전기 광학 소자에 흘림으로써, 전기 광학 소자를 발광시킨다.

<16> 샘플링 트랜지스터가 축적 캐패시터에 신호 전위에 따른 정보를 구동 전위로서 기입한다. 따라서, 샘플링 트랜지스터는 그 입력단(소스단 혹은 드레인단의 한쪽)에서 신호 전위를 수신하고, 그 출력단(소스단 혹은 드레인단의 다른 쪽)에 접속된 축적 캐패시터에 신호 전위에 따른 정보를 기입한다. 물론, 샘플링 트랜지스터의 출력단은, 구동 트랜지스터의 제어 입력단에도 접속된다.

<17> 여기에서 나타낸 화소 회로의 접속 구성은, 가장 기본적인 구성을 나타낸 것으로, 화소 회로는, 적어도 전술한 각 구성 요소를 포함하는 것이면 되고, 이들 구성 요소 이외(즉 다른 구성 요소)가 포함되어 있어도 된다. 또한, "접속"은, 직접적 접속에 한하지 않고, 다른 구성 요소를 개재해서 접속되는 경우라도 된다.

<18> 예를 들면, 접속간에는, 필요에 따라서 스위칭용의 트랜지스터나, 임의의 기능을 갖은 기능부 등을 개재시키는 등의 변경이 가해지는 경우가 있다. 전형적으로는, 표시 기간(환연하면 발광 기간)을 동적으로 제어하기 위해서 스위칭용의 트랜지스터(발광 제어 트랜지스터)를, 구동 트랜지스터의 출력단과 전기 광학 소자 사이에, 혹은 구동 트랜지스터의 전원 공급단(드레인단이 전형예)과 전원 공급용의 배선인 전원선 사이에 배치하는 경우가 있다.

<19> 이러한 변형 양태의 화소 회로이어도, 본항(과제를 해결하기 위한 수단)에서 설명하는 구성이나 작용을 실현할 수 있는 것인 한, 본 발명에 따른 표시 장치의 일 실시예를 실현하는 화소 회로이다.

<20> 여기에서, 본 발명에 따른 화소 회로 및 표시 장치의 일 실시예에서의 특징적인 사항으로서, 전술한 구성의 화소 회로를 베이스로 하여, 화소 회로마다, 한쪽의 단자가 구동 트랜지스터의 출력단에 접속되고 다른 쪽의 단자

에 펄스 신호가 공급되는 용량 소자를 형성한다. 그리고, 용량 소자의 다른 쪽의 단자에는, 이동도 보정 동작을 개시시키는 펄스 신호를 공급한다. 이에 의해, 구동 트랜지스터의 출력단은, 구동 트랜지스터의 제어 입력단과 출력단의 전위차가 커지는 방향의 천이 정보가 용량 소자를 통해서 공급되도록 한다. 이렇게 함으로써, 이동도 보정 개시 시에 구동 트랜지스터의 제어 입력단과 출력단의 전위차를 넓혀 두고 나서 이동도 보정을 행할 수 있다.

<21> 용량 소자의 다른 쪽의 단자에 공급하는, 이동도 보정 동작을 개시시키는 펄스 신호는, 화소 회로의 구성이나 구동 타이밍에 따라서 다양한 것이 생각된다. 예를 들면, 구동 트랜지스터 및 샘플링 트랜지스터 외에, 임계값 보정 동작이나 이동도 보정 동작시의 제어 펄스에 기초하여 온/오프 동작하는 2개의 스위치 트랜지스터를 구비하고, 또한 발광 기간의 뉘티를 조정하는 발광 제어 트랜지스터를 구비하는 특히 문헌 1에 기재와 같은 5TR 구성인 경우에서, 샘플링 트랜지스터에 공급하는 기입 구동 펄스와 발광 제어 트랜지스터에 공급하는 주사 구동 펄스 모두가 액티브로 되는 기간에서 이동도 보정 동작을 행하는 경우, 발광 제어 트랜지스터의 제어 입력단에 공급되는 주사 구동 펄스를, 이동도 보정 동작을 개시시키는 펄스로 하는 것이 좋다.

<22> 또한 이 경우에서, n형 및 p형 중 어느 한쪽의 형의 구동 트랜지스터의 전원 공급단측에 n형 및 p형의 다른 쪽의 형의 발광 제어 트랜지스터를 구비하는 구성인 경우에는, 용량 소자의 다른 쪽의 단자를 발광 제어 트랜지스터의 제어 입력단에 접속하고, 다른 쪽의 단자에 주사 구동 펄스를 공급하도록 하면 된다.

<23> 물론 이것은 일례이며, 구동 트랜지스터의 전기 광학 소자측인 출력단에 용량 소자의 한쪽의 단자를 접속하고, 다른 쪽의 단자에 이동도 보정 동작을 개시하는 펄스에 대응하는 정보를 공급함으로써, 그 펄스의 천이 정보(특히 이동도 보정 개시시의 구동 트랜지스터의 게이트-소스간 전압을 넓히는 방향의 정보)를 구동 트랜지스터의 출력단에 공급하는 것으면 된다.

## 효과

<24> 본 발명의 일 실시예에 따르면, 용량 소자를 추가하고, 그 용량 소자의 한쪽의 단자를 구동 트랜지스터의 출력단에 접속하고, 다른 쪽의 단자에 이동도 보정 동작을 개시시키는 펄스에 대응하는 정보를 공급하여, 구동 트랜지스터의 제어 입력단과 출력단의 전위차를 크게 하도록 했다.

<25> 샘플링 트랜지스터를 도통 상태로 해서 신호 전위에 따른 정보를 축적 캐패시터에 유지시킨 후에 샘플링 트랜지스터를 도통 상태로 한 채로 이동도 보정 동작을 행할 때에, 이동도 보정 개시시에 구동 트랜지스터의 제어 입력단과 출력단의 전위차를 미리 넓혀 두고 나서 이동도 보정을 행할 수 있기 때문에, 구동 트랜지스터의 제어 입력단과 출력단의 전위차의 이동도 보정에 수반하는 감소분을 보충할 수 있다.

<26> 그 결과, 발광 기간에서의 구동 전위를 넓힐 수 있기 때문에, 영상 신호 진폭을 크게 하지 않아도, 이동도 보정에 기인하는 발광 휘도 저하를 방지할 수 있다. 영상 신호 진폭을 크게 하지 않아도 되기 때문에, 저소비 전력화에 기여할 수도 있다.

## 발명의 실시를 위한 구체적인 내용

<27> 이하, 도면을 참조하여 본 발명의 실시예에 대해서 상세하게 설명한다.

<28> <표시 장치의 전체 개요>

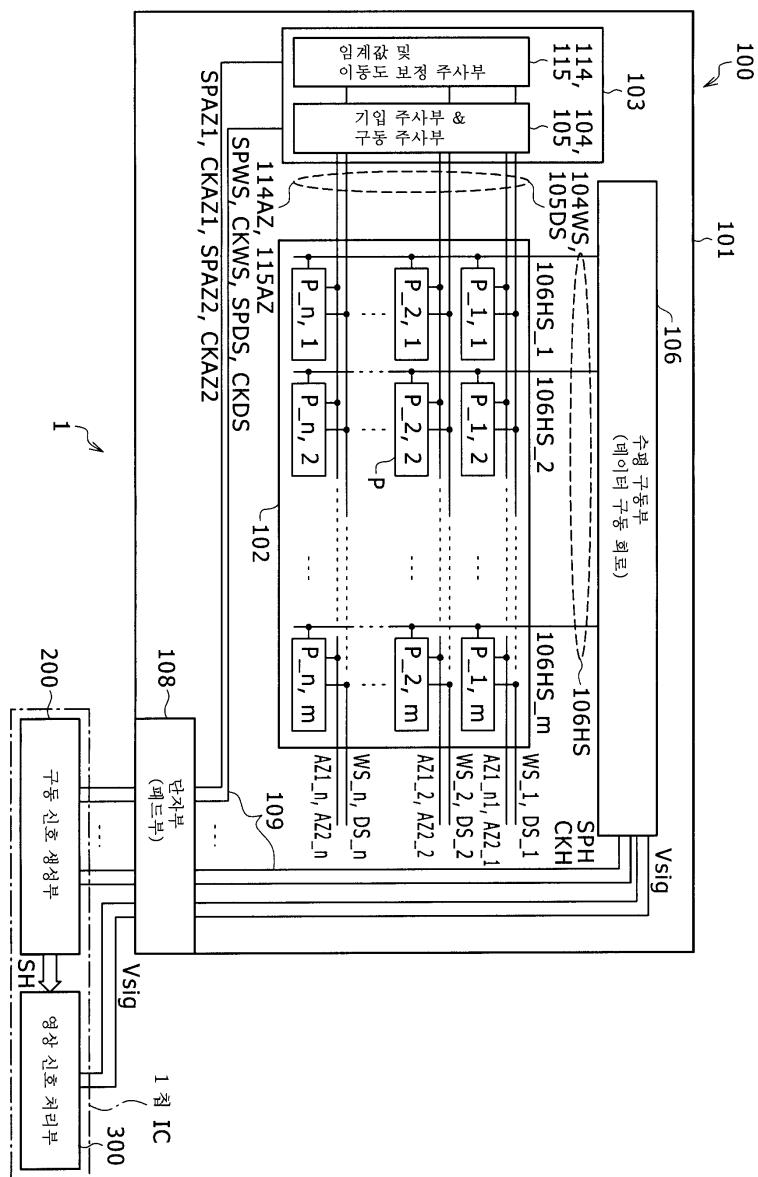

<29> 도 1은, 본 발명에 따른 표시 장치의 일 실시예인 액티브 행렬형 표시 장치의 구성을 개략적으로 도시하는 블록도이다. 본 실시예에서는, 예를 들면 화소의 표시 소자로서 유기 EL 소자를, 능동 소자로서 폴리실리콘 박막 트랜지스터(TFT)를 이용하여, 박막 트랜지스터를 형성한 반도체 기판 위에 유기 EL 소자를 형성해서 이루어지는 액티브 행렬형 유기 EL 디스플레이(이하 유기 EL 표시 장치라고 칭함)에 적용한 경우를 예로서 채용해서 설명한다.

<30> 또한, 이하에서는, 화소의 표시 소자로서 유기 EL 소자를 예로서 구체적으로 설명하지만, 유기 EL 소자는 일례이며, 대상으로 되는 표시 소자는 유기 EL 소자에 한하지 않는다. 일반적으로 전류 구동에 의해 발광하는 발광 소자의 모두에, 후술하는 모든 실시예를 마찬가지로 적용할 수 있다.

<31> 도 1에 도시하는 바와 같이, 유기 EL 표시 장치(1)는, 복수의 표시 소자로서의 유기 EL 소자(도시 생략)를 갖는 화소 회로(화소라고도 칭해짐)(110)가 표시 어스팩트비인 종횡비가 X:Y(예를 들면 9:16)의 유효 영상 영역을 구성하도록 배치된 표시 패널부(100)와, 이 표시 패널부(100)를 구동 및 제어하는 다양한 펄스 신호를 전송하는 패널 제어부의 일례인 구동 신호 생성부(200)와, 영상 신호 처리부(300)를 구비한다. 구동 신호 생성부(200)와

영상 신호 처리부(300)는, 1칩의 IC(Integrated Circuit)에 내장된다.

- <32> 제품 형태로서는, 도 1에 도시와 같이, 표시 패널부(100), 구동 신호 생성부(200), 및 영상 신호 처리부(300) 모두를 구비한 모듈(복합 부품) 형태의 유기 EL 표시 장치(1)가 제공되는 것에 한하지 않는다. 예를 들면, 유기 EL 표시 장치(1)로서 표시 패널부(100)만을 제공하는 것도 가능하다. 이러한 유기 EL 표시 장치(1)는, 반도체 메모리나 미니 디스크(MD)나 카세트 테이프 등의 기록 매체를 이용한 휴대형 음악 플레이어나 그 밖의 전자 기기의 표시부로서 이용된다.

- <33> 표시 패널부(100)는, 예를 들어 화소 회로 P가  $n$ 행  $\times m$ 열의 행렬 형상으로 배열된 화소 어레이부(102)와, 화소 회로 P를 수직 방향으로 주사하는 수직 구동부(103)와, 화소 회로 P를 수평 방향으로 주사하는 수평 구동부(수평 셀렉터 혹은 데이터선 구동부라고도 칭해짐)(106)와, 외부 접속용의 단자부(패드부)(108)를 포함한다. 여기서, 화소 어레이부(102), 수직 구동부(103), 수평 구동부(106), 및 단자부(패드부)(108)는 기판(101) 위에 접적 방식으로 형성된다. 즉, 수직 구동부(103)나 수평 구동부(106)등의 주변 구동 회로가, 화소 어레이부(102)와 동일한 기판(101) 위에 형성된 구성으로 된다.

- <34> 수직 구동부(103)는 예를 들면, 기입 주사부(라이트 스캐너 WS; Write Scan)(104)나 구동 주사부(드라이브 스캐너 DS; Drive Scan)(105)(도면에서는 양자를 일체적으로 도시하고 있음)와, 2개의 임계값 & 이동도 보정 주사부(114, 115)(도면에서는 양자를 일체적으로 도시하고 있음)를 포함한다.

- <35> 화소 어레이부(102)는 일례로서, 도 1의 수평 방향의 한쪽측 혹은 양측으로부터 기입 주사부(104), 구동 주사부(105), 임계값 & 이동도 보정 주사부(114, 115)로 구동되고, 도 1의 수직 방향의 한쪽측 혹은 양측으로부터 수평 구동부(106)로 구동된다. 단자부(108)에는 유기 EL 표시 장치(1)의 외부에 배치된 구동 신호 생성부(200)로부터 다양한 펄스 신호가 공급된다. 마찬가지로, 단자부(108)에는 영상 신호 처리부(300)로부터 영상 신호 Vsig가 공급된다.

- <36> 예를 들어, 수직 구동용의 펄스 신호로서, 수직 방향의 기입 개시 펄스의 일례인 시프트 개시 펄스 SPDS, SPWS나 수직 주사 클럭 CKDS, CKWS 등의 필요한 펄스 신호가 공급된다. 또한, 임계값이나 이동도를 보정하기 위한 펄스 신호로서, 수직 방향의 임계값 검지 개시 펄스의 일례인 시프트 개시 펄스 SPAZ1, SPAZ2나 수직 주사 클럭 CKAZ1, CKAZ2 등의 필요한 펄스 신호가 공급된다. 또한, 수평 구동용의 펄스 신호로서, 수평 방향의 기입 개시 펄스의 일례인 수평 개시 펄스 SPH나 수평 주사 클럭 CKH 등의 필요한 펄스 신호가 공급된다.

- <37> 단자부(108)의 각 단자는, 배선(109)을 통해서, 수직 구동부(103)나 수평 구동부(106)에 접속된다. 예를 들면, 단자부(108)에 공급된 각 펄스는, 필요에 따라서 도시되지 않은 레벨 시프터부에서 전압 레벨을 내부적으로 조정한 후, 버퍼를 통해서 수직 구동부(103)의 각 부나 수평 구동부(106)에 공급된다.

- <38> 화소 어레이부(102)는, 도시하지 않지만(상세한 것은 후술함), 표시 소자로서의 유기 EL 소자에 대하여 화소 트랜지스터가 형성된 각각의 화소 회로 P가 행렬 형상으로 2차원 배치되고, 이 화소 배열에 대하여 행마다 주사선이 배선되며, 이 화소 배열에 대하여 열마다 신호선이 배선된 구성을 갖는다.

- <39> 예를 들면, 화소 어레이부(102)에는, 주사선(케이트선)(104WS, 105DS)이나 임계값 & 이동도 보정 주사선(114AZ, 115AZ)과 신호선(데이터선)(106HS)이 형성된다. 주사선과 신호선이 교차하는 부분에는 도 1에서 도시를 생략한, 유기 EL 소자와 유기 EL 소자를 구동하는 박막 트랜지스터(TFT)가 형성된다. 유기 EL 소자와 박막 트랜지스터의 조합으로 화소 회로 P가 형성된다.

- <40> 구체적으로는, 행렬 형상으로 배열된 각 화소 회로 P에 대해서는, 기입 주사부(104)에 의해 기입 구동 펄스 WS로 구동되는  $n$ 행분의 기입 주사선(104WS\_1 ~ 104WS\_n) 및 구동 주사부(105)에 의해 주사 구동 펄스 DS로 구동되는  $n$ 행분의 구동 주사선(105DS\_1 ~ 105DS\_n), 또한 제1 임계값 & 이동도 보정 주사부(114)에 의해 임계값 & 이동도 보정 펄스 AZ1로 구동되는  $n$ 행분의 임계값 & 이동도 보정 주사선(114AZ\_1 ~ 114AZ\_n) 및 제2 임계값 & 이동도 보정 주사부(115)에 의해 임계값 & 이동도 보정 펄스 AZ2로 구동되는  $n$ 행분의 임계값 & 이동도 보정 주사선(115AZ\_1 ~ 115AZ\_n)이 화소 행마다 배선된다.

- <41> 기입 주사부(104) 및 구동 주사부(105)는 구동 신호 생성부(200)로부터 공급되는 수직 구동계의 펄스 신호에 기초하여, 각 주사선(105DS, 104WS)을 통해서 각 화소 회로 P를 순차적으로 선택한다. 수평 구동부(106)는 구동 신호 생성부(200)로부터 공급되는 수평 구동계의 펄스 신호에 기초하여, 선택된 화소 회로 P에 대하여 신호선(106HS)을 통해서 화상 신호를 기입한다.

- <42> 수직 구동부(103)의 각 부는 선 순차적으로 화소 어레이부(102)를 주사함과 함께, 이 주사에 동기해서, 수평 구

동부(106)가 화상 신호를 1수평 라인분에 대해서 수평 방향으로 순서대로(즉, 화소마다), 혹은 1수평 라인분의 화상 신호를 동시에, 화소 어레이부(102)에 기입한다. 전자는 전체적으로 점-순차 구동으로 되는 반면, 후자는 전체적으로 선-순차 구동으로 된다.

- <43> 점-순차 구동에 대응하는 경우, 수평 구동부(106)는 시프트 레지스터나 샘플링 스위치(수평 스위치) 등을 포함한다. 영상 신호 처리부(300)로부터 입력되는 화소 신호를, 수직 구동부(103)의 각 부에 의해 선택된 행의 각 화소 회로 P에 대하여, 화소 단위로 기입한다. 즉, 수직 주사에 의한 선택 행의 각 화소 회로 P에 대하여 영상 신호를 화소 단위로 기입하는 점-순차 구동을 행한다.

- <44> 한편, 선-순차 구동에 대응하는 경우, 수평 구동부(106)는 전체 열의 신호선(106HS) 상에 형성된 도시하지 않은 스위치를 동시에 턴온시키는 드라이버 회로를 포함한다. 수평 구동부(106)는 영상 신호 처리부(300)로부터 출력되는 화소 신호를, 수직 구동부(103)에 의해 선택된 행의 1라인분의 모든 화소 회로 P에 동시에 기입하기 위해서, 전체 열의 신호선(106HS) 상에 형성된 도시를 생략한 스위치를 동시에 턴온시킨다.

- <45> 수직 구동부(103)의 각 부는, 논리 게이트의 조합(래치를 포함함)에 의해 구성되고, 화소 어레이부(102)의 각 화소 회로 P를 행 단위로 선택한다. 또한, 도 1에서는, 화소 어레이부(102)의 한쪽측에만 수직 구동부(103)를 배치하는 구성을 도시하지만, 화소 어레이부(102)를 사이에 두고 좌우 양측에 수직 구동부(103)를 배치하는 것도 가능하다.

- <46> 마찬가지로, 도 1에서는, 화소 어레이부(102)의 한쪽측에만 수평 구동부(106)를 배치하는 구성을 도시하지만, 화소 어레이부(102)를 사이에 두고 상하 양측에 수평 구동부(106)를 배치하는 것도 가능하다.

- <47> <화소 회로; 비교예>

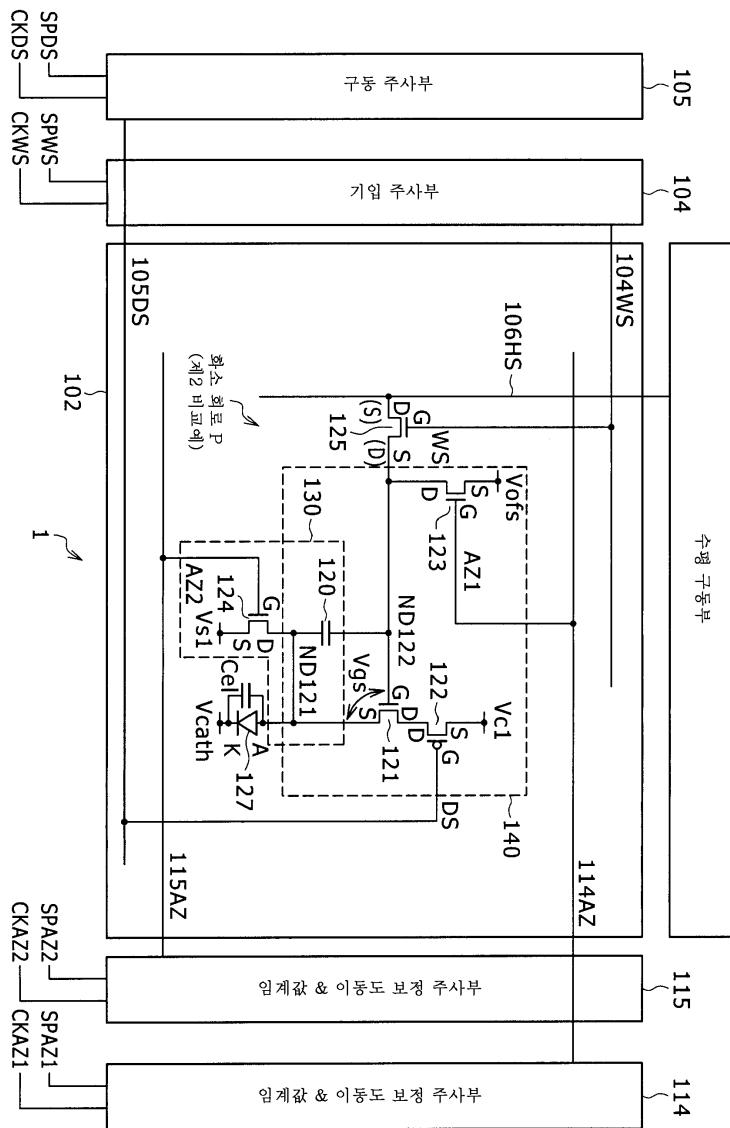

- <48> 도 2는 도 1에 도시한 유기 EL 표시 장치(1)를 구성하는 본 실시예에 따른 화소 회로 P에 대한 비교예를 도시하는 도면이다. 또한, 도 2는 표시 패널부(100)의 기판(101) 위에서 화소 회로 P의 주변부에 형성된 수직 구동부(103)와 수평 구동부(106)도 아울러 도시한다.

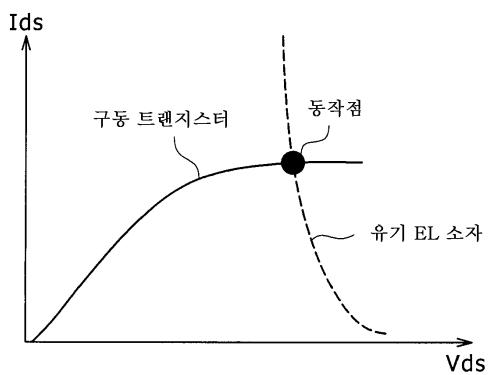

- <49> 도 3은 유기 EL 소자나 구동 트랜지스터의 동작점을 설명하는 도면이다. 도4a 내지 도 4c는, 유기 EL 소자나 구동 트랜지스터의 특성 변동이 구동 전류 Ids에 끼치는 영향을 설명하는 도면이다. 도 5 및 도 6a 내지 도 6d는 그 개선 방법의 개념을 설명하는 도면이다.

- <50> 도 2에 도시하는 비교예나 후술하는 본 실시예에 따른 화소 회로 P는, 기본적으로 n채널형의 박막 전계 효과 트랜지스터로 구동 트랜지스터가 구성되는 점에 특징을 갖는다. 도 2에 도시하는 비교예나 후술하는 본 실시예에 따른 화소 회로 P는, 유기 EL 소자의 경시 열화에 의한 해당 유기 EL 소자에 공급되는 구동 전류 Ids의 변동을 억제하기 위한 회로, 즉 전기 광학 소자의 일례인 유기 EL 소자의 전류-전압 특성의 변화를 보정해서 구동 전류 Ids를 일정하게 유지하는 임계값 보정 기능이나 이동도 보정 기능을 실현하는 구동 신호 일정화 회로 (1)를 구비한 점에 특징을 갖는다. 또한, 도 2에 도시하는 비교예나 후술하는 본 실시예에 따른 화소 회로 P는, 유기 EL 소자의 전류-전압 특성에 경시 변화가 있는 경우라도 구동 전류를 일정하게 하는 부트스트랩 기능을 실현하는 구동 신호 일정화 회로 (2)를 구비한 점에 특징을 갖는다.

- <51> 모든 스위치 트랜지스터를 p채널형의 트랜지스터가 아니라, n채널형의 트랜지스터로 구성할 수 있으면, 트랜지스터 제조에서 종래의 아몰퍼스 실리콘(a-Si) 프로세스를 이용할 수 있다. 이에 의해, 트랜지스터 기판의 저코스트화가 가능해지고, 이러한 구성의 화소 회로 P의 개발이 기대된다. 도 2에 도시하는 비교예나 후술하는 본 실시예에 따른 화소 회로 P는, 발광 제어 트랜지스터로서 p형을 이용하며, 이는 단점일 수 있다.

- <52> 구동 트랜지스터를 포함하는 각 트랜지스터로서 MOS 트랜지스터를 사용한다. 이 경우, 구동 트랜지스터의 게이트단을 제어 입력단으로서 취급하고, 그 소스단 및 드레인단 중 어느 한쪽(여기에서는 소스단)을 출력단으로서 취급하고, 다른 쪽을 전원 공급단(여기서는 드레인단)으로서 취급한다.

- <53> 우선, 본 실시예에 따른 화소 회로 P의 특징을 설명하는 비교예로서, 도 2에 도시하는 비교예의 화소 회로 P에 대해서 설명한다.

- <54> 비교예의 화소 회로 P는, 축적 캐페시터(화소 용량으로도 칭해짐)(120), n채널형 구동 트랜지스터(121), 액티브-L의 구동 펄스(주사 구동 펄스 DS)가 제어 입력단인 게이트단 G에 공급되는 p채널형 발광 제어 트랜지스터(122), 액티브-H의 구동 펄스(기입 구동 펄스 WS)가 제어 입력단인 게이트단 G에 공급되는 n채널형 샘플링 트랜지스터(125), 및 소자를 통해서 전류가 흐름으로써 발광하는 전기 광학 소자(발광 소자)의 일례인 유기 EL 소자

(127)를 갖는다.

<55> 샘플링 트랜지스터(125)는 구동 트랜지스터(121)의 게이트단 G(제어 입력단)측에 형성된 스위칭 트랜지스터이다. 발광 제어 트랜지스터(122)도 스위칭 트랜지스터이다.

<56> 일반적으로, 유기 EL 소자(127)는 정류성을 갖기 때문에 다이오드의 기호로 나타낸다. 또한, 유기 EL 소자(127)는 기생 용량(등가 용량) Cel을 구비한다. 도 2에서, 이 기생 용량 Cel을 유기 EL 소자(127)와 병렬로 나타낸다.

<57> 비교예의 화소 회로 P는 구동 트랜지스터(121)의 드레인단 D측에 발광 제어 트랜지스터(122)를 배치하고, 축적 캐패시터(120)를 구동 트랜지스터(121)의 게이트-소스간에 접속하여, 화소 회로 P가 부트스트랩 회로(130)와 임계값 & 이동도 보정 회로(140)를 구비하는 점에 특징을 갖는다.

<58> 유기 EL 소자(127)는 전류 발광 소자이기 때문에, 유기 EL 소자(127)에 흐르는 전류량을 제어함으로써 색 계조 (color gradation)가 얻어진다. 이 때문에, 구동 트랜지스터(121)의 게이트단 G에 인가되는 전압을 변화시킴으로써, 유기 EL 소자(127)에 흐르는 전류값을 제어한다.

<59> 이때, 부트스트랩 회로(130)나 임계값 & 이동도 보정 회로(140)는 유기 EL 소자(127)의 경시 변화나 구동 트랜지스터(121)의 특성 변동의 영향을 받지 않도록 한다. 이 때문에, 화소 회로 P를 구동하는 수직 구동부(103)는, 기입 주사부(104) 및 구동 주사부(105)에 부가하여, 2개의 임계값 & 이동도 보정 주사부(114, 115)를 구비한다.

<60> 도 2에서는, 1개의 화소 회로 P만을 나타내지만, 도 1에서도 설명한 바와 같이, 마찬가지의 구성의 화소 회로 P가 행렬 형상으로 배열된다. 행렬 형상으로 배열된 화소 회로 P에 대해서는, 기입 주사부(104)에 의해 기입 구동 펄스 WS로 구동되는 n행분의 기입 주사선(104WS\_1~104WS\_n) 및 구동 주사부(105)에 의해 주사 구동 펄스 DS로 구동되는 n행분의 구동 주사선(105DS\_1~105DS\_n) 외에, 제1 임계값 & 이동도 보정 주사부(114)에 의해 임계값 & 이동도 보정 펄스 AZ1로 구동되는 n행분의 임계값 & 이동도 보정 주사선(114AZ\_1~114AZ\_n) 및 제2 임계값 & 이동도 보정 주사부(115)에 의해 임계값 & 이동도 보정 펄스 AZ2로 구동되는 n행분의 임계값 & 이동도 보정 주사선(115AZ\_1~115AZ\_n)이 화소 행마다 배선된다.

<61> 부트스트랩 회로(130)는, 유기 EL 소자(127)와 병렬로 접속되고 액티브-H의 임계값 & 이동도 보정 펄스 AZ2가 공급되는 n채널형 검지 트랜지스터(124)를 구비하고, 이 검지 트랜지스터(124)와 구동 트랜지스터(121)의 게이트-소스간에 접속된 축적 캐패시터(120)로 구성된다. 축적 캐패시터(120)는 부트스트랩 용량으로서도 기능한다.

<62> 임계값 & 이동도 보정 회로(140)는, 구동 트랜지스터(121)의 게이트단 G와 제2 전원 전위 Vc2 사이에 액티브-H의 임계값 & 이동도 보정 펄스 AZ1이 공급되는 n채널형 검지 트랜지스터(123)를 구비하고, 검지 트랜지스터(123), 구동 트랜지스터(121), 발광 제어 트랜지스터(122), 및 구동 트랜지스터(121)의 게이트-소스간에 접속된 축적 캐패시터(120)로 구성된다. 축적 캐패시터(120)는 검지한 임계값 전압 Vth를 유지하는 임계값 전압 유지 용량으로서도 기능한다.

<63> 구동 트랜지스터(121)는 드레인단 D가 발광 제어 트랜지스터(122)의 드레인단 D에 접속된다. 발광 제어 트랜지스터(122)의 소스단 S는 제1 전원 전위 Vc1에 접속된다. 구동 트랜지스터(121)는 소스단 S가 직접 유기 EL 소자(127)의 애노드단 A에 접속된다. 구동 트랜지스터(121)의 소스단 S와 유기 EL 소자(127)의 애노드단 A 사이의 접속점을 노드 ND(121)로 설정한다. 유기 EL 소자(127)의 캐소드단 K는 기준 전위를 공급하는 전체 화소 공통의 접지 배선 Vcath(GND)에 접속되어, 캐소드 전위 Vcath가 공급된다.

<64> 샘플링 트랜지스터(125)는, 게이트단 G가 기입 주사부(104)로부터의 기입 주사선(104WS)에 접속되고, 드레인단 D가 영상 신호선(106HS)에 접속되고, 소스단 S가 구동 트랜지스터(121)의 게이트단 G에 접속된다. 샘플링 트랜지스터(125)의 소스단 S와 구동 트랜지스터(121)의 게이트단 G 사이의 접속점을 노드 ND(122)로 설정한다. 샘플링 트랜지스터(125)의 게이트단 G에는, 기입 주사부(104)로부터 액티브-H의 기입 구동 펄스 WS가 공급된다. 샘플링 트랜지스터(125)는 소스단 S와 드레인단 D를 반전시킨 접속 모드일 수도 있다. 축적 캐패시터(120)는 한쪽의 단자가 구동 트랜지스터(121)의 소스단 S에 접속되고, 다른 쪽의 단자가 동일한 구동 트랜지스터(121)의 게이트단 G에 접속된다.

<65> 검지 트랜지스터(123)는 구동 트랜지스터(121)의 게이트단 G(제어 입력단)측에 형성된 스위칭 트랜지스터이다. 검지 트랜지스터(123)는 소스단 S가 오프셋 전압의 일례인 접지 전위 Vofs에 접속되고, 드레인단 D가 구동 트랜

지스터(121)의 게이트단 G(노드 ND(122))에 접속되고, 제어 입력단인 게이트단 G가 임계값 & 이동도 보정 주사선(114AZ)에 접속된다. 겸지 트랜지스터(123)를 턴온시킴으로써, 구동 트랜지스터(121)의 게이트단 G의 전위를 겸지 트랜지스터(123)를 통해서 고정 전위인 접지 전위 Vofs에 접속한다.

<66> 겸지 트랜지스터(124)는 스위칭 트랜지스터이다. 겸지 트랜지스터(124)는 드레인단 D가 구동 트랜지스터(121)의 소스단 S와 유기 EL 소자(127)의 애노드단 A 사이의 접속점인 노드 ND(121)에 접속되고, 소스단 S가 기준 전위의 일례인 접지 전위 Vs1에 접속되고, 제어 입력단인 게이트단 G가 임계값 & 이동도 보정 주사선(115AZ)에 접속된다.

<67> 구동 트랜지스터(121)의 게이트-소스간에 축적 캐패시터(120)를 접속하고, 겸지 트랜지스터(124)를 턴온시킴으로써, 구동 트랜지스터(121)의 소스단 S의 전위를 겸지 트랜지스터(124)를 통해서 고정 전위인 접지 전위 Vs1에 접속한다.

<68> 샘플링 트랜지스터(125)는 기입 주사선(104WS)에 의해 선택되었을 때 동작한다. 샘플링 트랜지스터(125)는 신호선(106HS)으로부터 화소 신호 Vsig(화소 신호 Vsig의 신호 전위 Vin)를 샘플링하고, 노드 ND(112)를 통해 축적 캐패시터(120)에 신호 전위 Vin에 대응하는 크기의 전압을 유지한다. 축적 캐패시터(120)에 의해 유지되는 전위는 이상적으로는 신호 전위 Vin과 동일한 크기이지만, 실제로는 신호 전위 Vin보다 작다.

<69> 구동 트랜지스터(121)는, 발광 제어 트랜지스터(122)가 주사 구동 펄스 DS하에서 온일 때에, 축적 캐패시터(120)에 의해 유지된 구동 전위(그 시점에서의 구동 트랜지스터(121)의 게이트-소스간 전압 Vgs)에 따라서 유기 EL 소자(127)를 전류로 구동한다. 발광 제어 트랜지스터(122)는 구동 주사선(105DS)에 의해 선택될 때에 도통해서, 제1 전원 전위 Vc1로부터 구동 트랜지스터(121)에 전류를 공급한다.

<70> 이렇게, 구동 트랜지스터(121)의 전원 공급단인 드레인단 D측을 발광 제어 트랜지스터(122)를 통해서 제1 전원 전위 Vc1에 접속하고, 발광 제어 트랜지스터(122)의 온 기간을 제어함으로써, 유기 EL 소자(127)의 발광 기간과 비발광 기간을 조정하여, 뉴티(Duty) 구동을 행하는 것이 가능하다.

<71> 겸지 트랜지스터(123, 124)는 임계값 & 이동도 보정 주사부(114, 115)로부터의 액티브-H의 임계값 & 이동도 보정 펄스 AZ1, AZ2를 임계값 & 이동도 보정 주사선(114AZ, 115AZ)에 공급함으로써 각각을 선택 상태로 설정할 때 동작한다. 겸지 트랜지스터(123, 124)는 미리 결정된 보정 동작(여기서는 임계값 전압 Vth나 이동도  $\mu$ 의 변동을 보정하는 동작)을 행한다.

<72> 예를 들면, 유기 EL 소자(127)의 전류 구동에 앞서 구동 트랜지스터(121)의 임계값 전압 Vth를 겸지하고, 미리 임계값 전압 Vth의 영향을 없애기 위해서, 겸지한 전위를 축적 캐패시터(120)에 유지한다.

<73> 이러한 구성의 화소 회로 P의 정상 동작을 보증하기 위한 조건으로서, 접지 전위 Vs1은 접지 전위 Vofs로부터 구동 트랜지스터(121)의 임계값 전압 Vth를 감산한 레벨보다도 낮게 설정된다. 즉, "Vs1 < Vofs - Vth"이다.

<74> 또한, 유기 EL 소자(127)의 캐소드단 K의 전위 Vcath에 유기 EL 소자(127)의 임계값 전압 VthEL을 가산하여 얻어진 레벨은, 접지 전위 Vs1로부터 구동 트랜지스터(121)의 임계값 전압 Vth를 감산한 레벨보다도 높게 설정된다. 즉, "Vcath + VthEL > Vs1 - Vth"이다. 바람직하게는, 접지 전위 Vofs의 레벨은 신호선(106HS)으로부터 공급되는 화소 신호 Vsig 중 최저 레벨의 근방으로(최저 레벨 이하의 범위에서) 설정된다.

<75> 이러한 구성을 갖는 비교예의 화소 회로 P에서, 샘플링 트랜지스터(125)는, 소정의 신호 기입 기간(샘플링 기간)에 기입 주사선(104WS)으로부터 공급되는 기입 구동 펄스 WS에 따라서 도통하여, 신호선(106HS)으로부터 공급된 영상 신호 Vsig를 축적 캐패시터(120)에 샘플링한다. 축적 캐패시터(120)는, 샘플링된 영상 신호 Vsig에 따라 구동 트랜지스터(121)의 게이트-소스간에 입력 전압(게이트-소스간 전압 Vgs)을 인가한다.

<76> 구동 트랜지스터(121)는 소정의 발광 기간 동안에 게이트-소스간 전압 Vgs에 따른 출력 전류를 구동 전류 Ids로서 유기 EL 소자(127)에 공급한다. 또한, 이 구동 전류 Ids는 구동 트랜지스터(121)의 채널 영역의 캐리어 이동도  $\mu$  및 구동 트랜지스터(121)의 임계값 전압 Vth에 대하여 의존성을 갖는다. 유기 EL 소자(127)는, 구동 트랜지스터(121)로부터 공급된 구동 전류 Ids에 기초하여 영상 신호 Vsig(특히 신호 전위 Vin)에 따른 휘도로 발광한다.

<77> 비교예의 화소 회로 P에서는, 스위칭 트랜지스터(발광 제어 트랜지스터(122) 및 겸지 트랜지스터(123, 124))로 구성되는 보정 수단을 구비한다. 캐리어 이동도  $\mu$ 에 대한 구동 전류 Ids의 의존성을 없애기 위해서, 미리 발광 기간의 개시시에 축적 캐패시터(120)에 유지된 게이트-소스간 전압 Vgs를 보정한다.

- <78> 구체적으로는, 이 보정 수단(스위칭 트랜지스터(122, 123, 124))은, 기입 주사선(104WS) 및 구동 주사선(105D S)으로부터 공급되는 기입 구동 펄스 WS 및 주사 구동 펄스 DS에 따라서 신호 기입 기간의 일부(예를 들면 후반 측)에서 동작하고, 영상 신호 Vsig가 샘플링되는 상태에서 구동 트랜지스터(121)로부터 구동 전류 Ids를 취출하고, 이 구동 전류 Ids를 축적 캐패시터(120)에 부귀환해서 게이트-소스간 전압 Vgs를 보정한다. 또한 이 보정 수단(스위칭 트랜지스터(122, 123, 124))은, 임계값 전압 Vth에 대한 구동 전류 Ids의 의존성을 없애기 위해서, 미리 신호 기입 기간에 앞서 구동 트랜지스터(121)의 임계값 전압 Vth를 검출하고, 또한 검출된 임계값 전압 Vth를 게이트-소스간 전압 Vgs에 부가한다.

- <79> 특히, 비교예의 화소 회로 P에서는, 구동 트랜지스터(121)는 n채널형 트랜지스터이며 그 드레인을 플러스 전원 측에 접속하는 한편, 소스가 유기 EL 소자(127)측에 접속된다. 이 경우, 전술한 보정 수단은 신호 기입 기간의 뒤 부분에 겹치는 발광 기간의 개시 부분에서 구동 트랜지스터(121)로부터 구동 전류 Ids를 취출하고, 이 구동 전류 Ids를 축적 캐패시터(120)측에 부귀환한다.

- <80> 이때, 보정 수단은 발광 기간의 개시 부분에서 구동 트랜지스터(121)의 소스단 S측으로부터 취출한 구동 전류 Ids가, 유기 EL 소자(127)의 기생 용량 Cel에 유입되도록 한다. 구체적으로는, 유기 EL 소자(127)는 애노드단 A 및 캐소드단 K를 구비한 다이오드형 발광 소자이다. 애노드단 A측이 구동 트랜지스터(121)의 소스단 S에 접속되는 한편, 캐소드단 K측이 접지측(본 예에서는 캐소드 전위 Vcath)에 접속된다.

- <81> 이 구성에서, 보정 수단(스위칭 트랜지스터(122, 123, 124))은, 미리 유기 EL 소자(127)의 애노드와 캐소드간을 역바이어스 상태로 설정하고, 따라서 구동 트랜지스터(121)의 소스단 S측으로부터 취출한 구동 전류 Ids가 유기 EL 소자(127)에 유입될 때, 다이오드형의 유기 EL 소자(127)를 용량성 소자로서 기능시킨다.

- <82> 또한, 보정 수단은 신호 기입 기간 내에 구동 트랜지스터(121)로부터 구동 전류 Ids를 취출하는 시간 폭 (duration) t를 조정 가능하다. 이에 의해, 보정 수단은 축적 캐패시터(120)에 대한 구동 전류 Ids의 부귀환량을 최적화한다.

- <83> 여기에서, "부귀환량을 최적화한다"란, 영상 신호 전위의 흑(black) 레벨로부터 백(white) 레벨까지의 범위에서, 어느 레벨에서도 적절하게 이동도 보정을 행할 수 있도록 하는 것을 의미한다. 게이트-소스간 전압 Vgs에 인가되는 부귀환량은, 구동 전류 Ids의 취출 시간에 의존한다. 취출 시간을 길게 취할수록, 부귀환량이 커진다.

- <84> 예를 들면, 영상선 신호 전위인 신호선(106HS)의 전압의 상승 에지 혹은 기입 주사선(104WS)의 기입 구동 펄스 WS의 천이 특성에 경사를 줌으로써, 이동도 보정 기간 t를 영상선 신호 전위에 자동적으로 추종시켜서, 최적화 시킨다. 즉, 이동도 보정 기간 t는 기입 주사선(104WS)과 신호선(106HS)간의 위상차로 결정할 수 있고, 또한 신호선(106HS)의 전위에 의해서도 결정할 수 있다. 이동도 보정 파라미터  $\Delta V$ 는  $\Delta V = Ids \cdot Cel/t$ 이다.

- <85> 이 식으로부터 분명한 바와 같이, 구동 트랜지스터(121)의 드레인-소스간 전류인 구동 전류 Ids가 클수록, 이동도 보정 파라미터  $\Delta V$ 는 커진다. 반대로, 구동 트랜지스터(121)의 구동 전류 Ids가 작을 때, 이동도 보정 파라미터  $\Delta V$ 는 작아진다. 이렇게, 이동도 보정 파라미터  $\Delta V$ 는 구동 전류 Ids에 따라 결정된다.

- <86> 이때, 이동도 보정 기간 t는 반드시 일정할 필요는 없고, 반대로 구동 전류 Ids에 따라 이동도 보정 기간 t를 조정하는 것이 바람직한 경우가 있다. 예를 들면, 구동 전류 Ids가 큰 경우, 이동도 보정 기간 t는 짧게 설정하고, 반대로 구동 전류 Ids가 작아지면, 이동도 보정 기간 t는 길게 설정하는 것이 바람직하다.

- <87> 따라서, 영상 신호선 전위(신호선(106HS)의 전위)의 상승 에지 혹은 기입 주사선(104WS)의 기입 구동 펄스 WS의 천이 특성에 경사를 줌으로써, 신호선(106HS)의 전위가 높을 때(구동 전류 Ids가 클 때) 보정 기간 t가 짧아지고, 신호선(106HS)의 전위가 낮을 때(구동 전류 Ids가 작을 때) 보정 기간 t는 길어지도록 자동적으로 조정한다. 이렇게 함으로써, 영상 신호 전위(영상 신호 Vsig의 신호 전위 Vin)를 추종하는 방식으로, 적절한 보정 기간을 자동적으로 설정할 수 있다. 따라서, 화상의 희도나 패턴에 상관없이 최적의 이동도 보정이 가능하다.

- <88> <기본 동작>

- <89> 우선, 도 2나 후술하는 본 실시예에 따른 화소 회로 P의 특징을 설명하는 비교예로서, 발광 제어 트랜지스터(122), 겹지 트랜지스터(123), 및 겹지 트랜지스터(124)를 구비하고 있지 않고, 축적 캐패시터(120)는, 한쪽의 단자가 노드 ND(122)에 접속되고, 다른 쪽의 단자가 전체 화소 공통인 겹지 배선 Vcath(GND)에 접속되는 경우의 동작에 대해서 설명한다. 이하, 이러한 화소 회로 P를 제1 비교예의 화소 회로 P라고 칭하고, 제1 비교예의 화

소 회로 P와의 구별을 위해서, 도 2에 도시하는 화소 회로 P를 제2 비교예의 화소 회로 P라고 칭한다. 제2 비교예의 화소 회로 P를 화소 어레이부(102)에 구비하는 유기 EL 표시 장치(1)를 제2 비교예의 유기 EL 표시 장치(1)라고 칭한다.

<90> 제1 비교예의 화소 회로 P에서는, 구동 트랜지스터(121)의 소스단 S의 전위(소스 전위 Vs)는, 구동 트랜지스터(121)와 유기 EL 소자(127)의 동작점에 의해 결정되고, 그 전압값은 구동 트랜지스터(121)의 게이트 전위 Vg에 따라 상이하다.

<91> 일반적으로, 도 3에 도시하는 바와 같이, 구동 트랜지스터(121)는 포화 영역에서 구동된다. 따라서, 포화 영역에서 동작하는 트랜지스터의 드레인단과 소스간에 흐르는 전류를  $Ids$ , 이동도를  $\mu$ , 채널 폭(게이트 폭)을  $W$ , 채널 길이(게이트 길이)를  $L$ , 게이트 용량(단위 면적당의 게이트 산화막 용량)을  $Cox$ , 트랜지스터의 임계값 전압을  $V_{th}$ 로 하면, 구동 트랜지스터(121)는 하기의 수학식 1에 나타낸 값을 갖는 정전류원이다. 또한, " $^2$ "는 거듭제곱(power)을 나타낸다. 수학식 1로부터 분명한 바와 같이, 포화 영역에서는 트랜지스터의 드레인 전류  $Ids$ 는 게이트-소스간 전압  $Vgs$ 에 의해 제어되고, 구동 트랜지스터(121)는 정전류원으로서 동작한다.

### 수학식 1

$$Ids = \frac{1}{2} \mu \frac{W}{L} Cox (Vgs - V_{th})^2$$

<92> <발광 소자의  $I_{el}$ - $V_{el}$  특성과 I-V 특성>

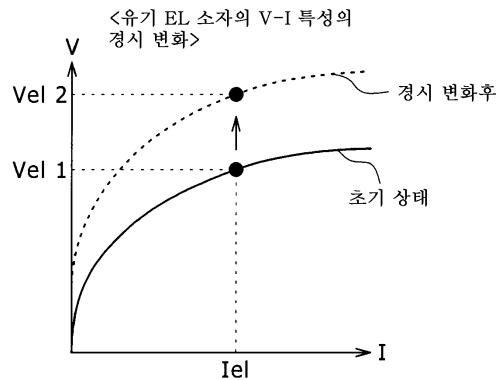

<93> 도 4a 내지 도 4c의 (1)에 나타내는 유기 EL 소자로 대표되는 전류 구동형의 발광 소자의 전류-전압( $I_{el}$ - $V_{el}$ ) 특성에서, 실선으로 나타내는 곡선이 초기 상태시의 특성을 나타내고, 파선으로 나타내는 곡선이 경시 변화후의 특성을 나타낸다. 일반적으로, 유기 EL 소자를 구비하는 전류 구동형의 발광 소자의 I-V 특성은, 그래프에 나타내는 바와 같이 시간이 경과하면 열화한다.

<94> 예를 들면, 발광 소자의 일례인 유기 EL 소자(127)에 발광 전류  $I_{el}$ 이 흐를 때, 유기 EL 소자(127)의 애노드-캐소드간 전압  $V_{el}$ 은 일의적으로 결정된다. 도 4a 내지 도 4c의 (1)에 나타내는 바와 같이, 발광 기간 중에는, 유기 EL 소자(127)의 애노드단 A를 통해서 구동 트랜지스터(121)의 드레인-소스간 전류  $Ids$ (=구동 전류  $Ids$ )로 결정되는 발광 전류  $I_{el}$ 이 흐르고, 이에 의해 유기 EL 소자(127)의 애노드단 A는 애노드-캐소드간 전압  $V_{el}$ 분만큼 상승한다.

<95> 제1 비교예의 화소 회로 P에서는, 유기 EL 소자(127)의 I-V 특성의 경시 변화의 결과로서 동일한 발광 전류  $I_{el}$ 에 대한 애노드-캐소드간 전압  $V_{el}$ 이  $V_{el1}$ 로부터  $V_{el2}$ 로 변화한다. 따라서, 구동 트랜지스터(121)의 동작점이 변화한다. 동일한 게이트 전위  $Vg$ 를 인가해도, 구동 트랜지스터(121)의 소스 전위  $Vs$ 는 변화한다. 그 결과로서, 구동 트랜지스터(121)의 게이트-소스간 전압  $Vgs$ 는 변화한다.

<96> 구동 트랜지스터(121)로서 n채널형을 사용한 단순한 회로에서는, 구동 트랜지스터(121)의 소스단 S가 유기 EL 소자(127)측에 접속되기 때문에, 이 단순 회로는 유기 EL 소자(127)의 I-V 특성의 경시 변화의 영향을 받는다. 따라서, 유기 EL 소자(127)에 흐르는 전류량(발광 전류  $I_{el}$ )이 변화한다. 그 결과, 발광 휘도는 변화한다.

<97> 구체적으로는, 제1 비교예의 화소 회로 P에서는, 유기 EL 소자(127)의 I-V 특성의 경시 변화에 의해 동작점이 변화한다. 동일한 게이트 전위  $Vg$ 를 인가해도, 구동 트랜지스터(121)의 소스 전위  $Vs$ 는 변화한다. 이에 의해, 구동 트랜지스터(121)의 게이트-소스간 전압  $Vgs$ 는 변화한다. 특성 수학식 1로부터 분명한 바와 같이, 게이트-소스간 전압  $Vgs$ 가 변동하면, 게이트 전위  $Vg$ 가 일정하여도 구동 전류  $Ids$ 가 변동하고, 동시에 유기 EL 소자(127)에 흐르는 전류값도 변화된다. 이렇게, 유기 EL 소자(127)의 I-V 특성이 변화되면, 제1 비교예의 화소 회로 P에서는, 유기 EL 소자(127)의 발광 휘도의 경시 변화를 초래한다.

<98> 구동 트랜지스터(121)로서 n채널형을 사용한 단순한 회로에서는, 구동 트랜지스터(121)의 소스단 S가 유기 EL 소자(127)측에 접속되게 되기 때문에, 유기 EL 소자(127)의 경시 변화와 함께 게이트-소스간 전압  $Vgs$ 가 변화한다. 따라서, 유기 EL 소자(127)에 흐르는 전류량이 변화한다. 그 결과, 발광 휘도가 변화한다.

<99> 발광 소자의 일례인 유기 EL 소자(127)의 특성의 경시 변동에 의한 유기 EL 소자(127)의 애노드 전위 변동은, 구동 트랜지스터(121)의 게이트-소스간 전압  $Vgs$ 의 변동으로서 나타나, 드레인 전류(구동 전류  $Ids$ )의 변동을 야기한다. 이 원인에 의한 구동 전류의 변동은 화소 회로 P마다의 발광 휘도의 변동으로서 나타나, 화질의 열화를 야기한다.

- <101> 반면에, 상세한 것은 후술하지만, 축적 캐퍼시터(120)에 신호 전위  $V_{in}$ 에 대응하는 정보가 기입된 시점에서 샘플링 트랜지스터(125)를 비도통 상태로 설정함으로써(또한 그 후의 유기 EL 소자(127)의 발광 기간 동안 계속적으로 샘플링 트랜지스터(125)를 비도통 상태로 유지함으로써), 구동 트랜지스터(121)의 소스단 S의 전위  $V_s$ 의 변동에 구동 트랜지스터(121)의 게이트단 G의 전위  $V_g$ 가 연동하도록 하는 부트스트랩 기능을 실현하는 회로 구성 및 구동 타이밍으로 설정하는 부트스트랩 동작을 수행한다.

- <102> 이에 의해, 유기 EL 소자(127)의 특성의 경시 변동에 의한 유기 EL 소자(127)의 애노드 전위 변동(즉, 소스 전위 변동)이 있어도, 그 변동을 없애도록 게이트 전위  $V_g$ 를 변동시킨다. 따라서, 화면 휙도의 균일성(uniformity)을 확보할 수 있다. 부트스트랩 기능에 의해, 유기 EL 소자를 대표로 하는 전류 구동형의 발광 소자의 경시 변동 보정 능력을 향상시킬 수 있다.

- <103> 이 부트스트랩 기능은, 기입 구동 펄스  $WS$ 를 인액티브-L 상태로 변경해서 샘플링 트랜지스터(125)를 턴오프시킨 발광 개시 시점에서 개시시킬 수 있고, 그 후, 유기 EL 소자(127)에 발광 전류  $I_{el}$ 이 흐르기 시작하고, 발광 전류  $I_{el}$ 이 흐르기 시작함과 함께 애노드-캐소드간 전압  $V_{el}$ 이 안정될 때까지 상승해 가는 과정에서, 애노드-캐소드간 전압  $V_{el}$ 의 변동에 수반하여 구동 트랜지스터(121)의 소스 전위  $V_s$ 가 변동할 때에도 기능한다.

- <104> <구동 트랜지스터의  $V_{gs}$ - $Ids$  특성>

- <105> 또한, 구동 트랜지스터(121)의 제조 프로세스의 변동에 의해, 화소 회로 P마다 임계값 전압이나 이동도 등의 특성 변동이 있다. 구동 트랜지스터(121)를 포화 영역에서 구동하고 구동 트랜지스터(121)에 동일한 게이트 전위를 부여하는 경우에도, 이 특성 변동에 의해 화소 회로 P마다 드레인 전류(구동 전류  $Ids$ )가 변동하여, 발광 휙도의 비균일성으로서 나타난다.

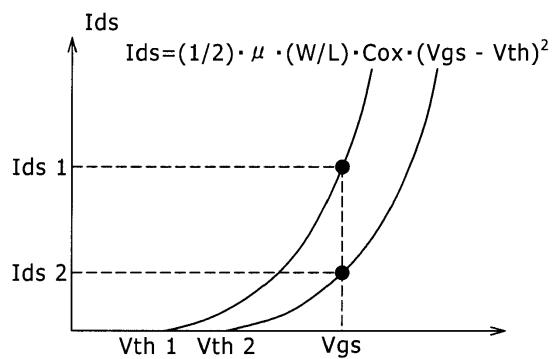

- <106> 예를 들면, 도 4a 내지 도 4c의 (2)는, 구동 트랜지스터(121)의 임계값 변동에 주목한 전압-전류( $V_{gs}$ - $Ids$ ) 특성을 나타내는 도면이다. 임계값 전압이  $V_{th1}$ 과  $V_{th2}$ 에서 서로 다른 2개의 구동 트랜지스터(121)에 대해서 각각 특성 곡선을 예를 들고 있다.

- <107> 전술한 바와 같이, 구동 트랜지스터(121)가 포화 영역에서 동작하고 있을 때의 드레인 전류  $Ids$ 는 특성 수학식 1로 나타낸다. 특성 수학식 1로부터 분명한 바와 같이, 임계값 전압  $V_{th}$ 가 변동하면, 게이트-소스간 전압  $V_{gs}$ 가 일정하여도 드레인 전류  $Ids$ 가 변동한다. 즉, 임계값 전압  $V_{th}$ 의 변동에 대하여 아무런 조치를 실시하지 않으면, 도 4a 내지 도 4c의 (2)에 나타내는 바와 같이, 임계값 전압이  $V_{th1}$ 일 때 게이트 전압  $V_{gs}$ 에 대응하는 구동 전류가  $Ids1$ 인 반면에, 임계값 전압이  $V_{th2}$ 일 때의 동일한 게이트 전압  $V_{gs}$ 에 대응하는 구동 전류  $Ids2$ 는  $Ids1$ 과 서로 다르게 된다.

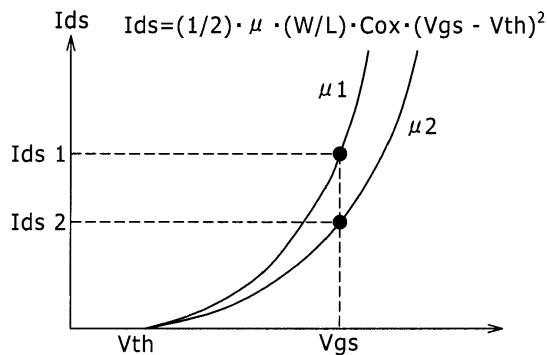

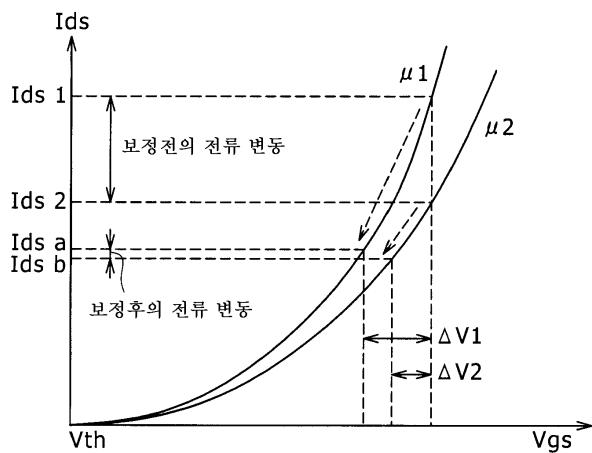

- <108> 또한, 도 4a 내지 도 4c의 (3)은, 구동 트랜지스터(121)의 이동도 변동에 주목한 전압-전류( $V_{gs}$ - $Ids$ ) 특성을 나타내는 도면이다. 이동도가  $\mu_1$ 과  $\mu_2$ 로 서로 다른 2개의 구동 트랜지스터(121)에 대해서 각각 특성 곡선을 예를 들고 있다.

- <109> 특성 수학식 1로부터 분명한 바와 같이, 이동도  $\mu$ 가 변동하면, 게이트-소스간 전압  $V_{gs}$ 가 일정하여도 드레인 전류  $Ids$ 가 변동한다. 즉, 이동도  $\mu$ 의 변동에 대하여 아무런 조치를 실시하지 않으면, 도 4a 내지 도 4c의 (3)에 도시하는 바와 같이, 이동도가  $\mu_1$ 일 때 게이트 전압  $V_{gs}$ 에 대응하는 구동 전류가  $Ids1$ 인 반면에, 이동도가  $\mu_2$ 일 때의 동일한 게이트 전압  $V_{gs}$ 에 대응하는 구동 전류가  $Ids2$ 이어서,  $Ids1$ 과 서로 다르게 된다.

- <110> 도 4a 내지 도 4c의 (2)나 도 4a 내지 도 4c의 (3)에 나타내는 바와 같이, 임계값 전압  $V_{th}$ 나 이동도  $\mu$ 의 차이로  $V_{in}$ - $Ids$  특성에 큰 차이가 나타나면, 동일한 신호 전위  $V_{in}$ 을 부여해도, 구동 전류  $Ids$ , 즉, 발광 휙도가 서로 다르게 된다. 따라서, 화면 휙도의 균일성이 얻어지지 않을 수 있다.

- <111> <임계값 보정 및 이동도 보정의 개념>

- <112> 반면에, 임계값 보정 기능 및 이동도 보정 기능을 실현하는 구동 타이밍(상세한 것은 후술함)으로 설정함으로써, 이들 변동의 영향을 억제할 수 있어, 화면 휙도의 균일성을 확보할 수 있다.

- <113> 제2 비교예나 본 실시예에 따른 임계값 보정 동작 및 이동도 보정 동작에서는, 상세한 것은 후술하지만, 발광시의 게이트-소스간 전압  $V_{gs}$ 가 " $V_{in}+V_{th}-\Delta V$ "로 나타낸다. 이에 의해, 드레인-소스간 전류  $Ids$ 가 임계값 전압  $V_{th}$ 의 변동이나 변화에 의존하지 않도록 함과 함께, 이동도  $\mu$ 의 변동이나 변화에 의존하지 않도록 한다. 결과로서, 임계값 전압  $V_{th}$ 나 이동도  $\mu$ 가 제조 프로세스나 경시에 의해 변동해도, 구동 전류  $Ids$ 는 변동하지 않고, 유기 EL 소자(127)의 발광 휙도도 변동하지 않는다.

- <114> 예를 들면, 도 5는 이동도 보정시의 구동 트랜지스터(121)의 동작점을 설명하는 그래프이다. 제조 프로세스나 경시에서 발생하는 이동도  $\mu_1$ ,  $\mu_2$ 의 변동에 대하여, 발광시의 게이트-소스간 전압  $V_{gs}$ 가 " $V_{in}+V_{th}-\Delta V$ "로 나타내도록 하는 임계값 보정 및 이동도 보정을 인가하면, 우선 이동도의 관점으로부터는, 이동도  $\mu_1$ 에 대해서는 이동도 보정 파라미터  $\Delta V_1$ 이 결정되고, 또한 이동도  $\mu_2$ 에 대해서는 이동도 보정 파라미터  $\Delta V_2$ 가 결정된다.

- <115> 이에 의해, 각각의 이동도에 대해서 적정한 이동도 보정 파라미터가 결정된다. 따라서, 구동 트랜지스터(121)의 이동도  $\mu_1$ 일 때의 구동 전류  $I_{dsA}$  및 이동도  $\mu_2$ 일 때의 구동 전류  $I_{dsB}$ 가 결정된다. 이동도 보정 전에는 큰 전류 변동이 있지만, 이동도 보정에 의해 전류 변동은 작아져, 이동도  $\mu$ 의 차이가 억제된다. 최적의 상태 " $I_{dsA}=I_{dsB}$ "에서는, 이동도  $\mu$ 의 차이를 제거(소거)할 수 있다.

- <116> 도 4a 내지 도 4c의 (3)에도 나타내지만, 이동도 보정을 인가하지 않으면, 게이트-소스간 전압  $V_{gs}$ 에 대하여 이동도가  $\mu_1$ ,  $\mu_2$ 로 서로 다르면, 구동 전류  $I_{ds}$ 도  $I_{ds1}$ ,  $I_{ds2}$ 로 크게 다르게 된다. 이에 대처하기 위해서, 이동도  $\mu_1$ ,  $\mu_2$ 에 대하여 각각 적절한 이동도 보정 파라미터  $\Delta V_1$ ,  $\Delta V_2$ 를 곱함으로써, 구동 전류  $I_{ds}$ 가 구동 전류  $I_{dsA}$ ,  $I_{dsB}$ 로 된다. 각 이동도 보정 파라미터  $\Delta V_1$ ,  $\Delta V_2$ 를 최적화함으로써, 이동도 보정후의 구동 전류  $I_{dsA}$ ,  $I_{dsB}$ 를 서로 가까이 할 수 있어, 이 구동 전류  $I_{dsA}$ ,  $I_{dsB}$ 를 최적 상태에서 동일 레벨로 설정할 수 있다.

- <117> 이동도 보정시에는, 도 5의 그래프로부터 분명한 바와 같이, 큰 이동도  $\mu_1$ 에 대해서는 이동도 보정 파라미터  $\Delta V_1$ 이 커지도록 하는 한편, 작은 이동도  $\mu_2$ 에 대해서는 이동도 보정 파라미터  $\Delta V_2$ 도 작아지도록 부귀환을 곱한다. 이러한 의미에서, 이동도 보정 파라미터  $\Delta V$ 를 부귀환량  $\Delta V$ 라고도 칭한다.

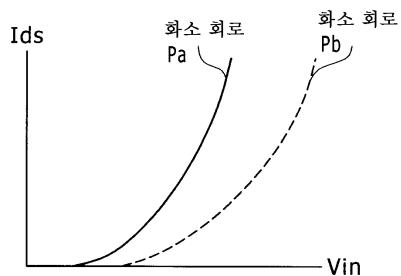

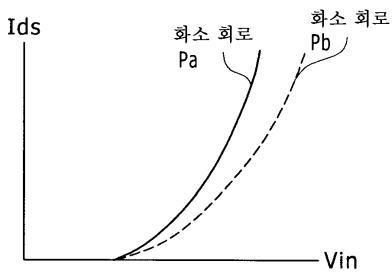

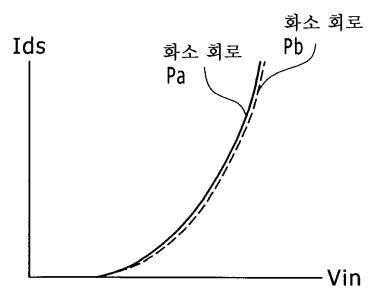

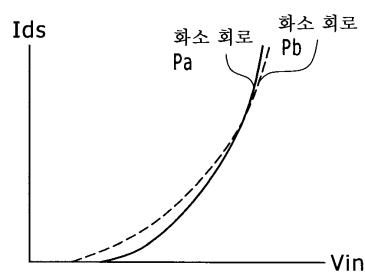

- <118> 도 6a 내지 도 6d의 각 도면은 임계값 보정의 관점으로부터, 신호 전위  $V_{in}$ 과 구동 전류  $I_{ds}$ 간의 관계를 나타낸다. 예를 들면, 구동 트랜지스터(121)의 전류-전압 특성을 나타내는 도 6a 내지 도 6d의 각 도면에서는, 횡축에 신호 전위  $V_{in}$ 을 표시하고, 종축에 구동 전류  $I_{ds}$ 를 표시하며, 임계값 전압  $V_{th}$ 가 비교적 낮고 이동도  $\mu$ 가 비교적 큰 구동 트랜지스터(121)로 구성된 화소 회로  $Pa$ (실선의 곡선)와, 반대로 임계값 전압  $V_{th}$ 가 비교적 높고 이동도  $\mu$ 가 비교적 작은 구동 트랜지스터(121)로 구성된 화소 회로  $Pb$ (점선의 곡선)에 대해서, 각각 특성 곡선을 예를 들고 있다.

- <119> 도 6a 내지 도 6d의 (1)은, 임계값 보정 및 이동도 보정 모두 실행하지 않는 경우이다. 이때, 화소 회로  $Pa$  및 화소 회로  $Pb$ 에서 임계값 전압  $V_{th}$  및 이동도  $\mu$ 의 보정이 전혀 실행되지 않기 때문에, 임계값 전압  $V_{th}$ 나 이동도  $\mu$ 의 차이로  $V_{in}-I_{ds}$  특성에 큰 차이가 나게 된다. 따라서, 동일한 신호 전위  $V_{in}$ 을 부여해도, 구동 전류  $I_{ds}$ , 즉, 발광 휘도가 서로 다르게 되어, 화면 휘도의 균일성이 얻어지지 않을 수 있다.

- <120> 도 6a 내지 도 6d의 (2)는, 임계값 보정을 실행하지만, 이동도 보정은 실행하지 않은 경우이다. 이때, 화소 회로  $Pa$ 와 화소 회로  $Pb$ 에서 임계값 전압  $V_{th}$ 의 차이는 제거된다. 그러나, 이동도  $\mu$ 의 차이는 그대로 나타난다. 따라서, 신호 전위  $V_{in}$ 이 높은 영역(즉, 휘도가 높은 영역)에서, 이동도  $\mu$ 의 차이가 현저히 나타나, 동일한 계조에 대해 휘도가 다르게 된다. 구체적으로는, 동일한 계조(동일한 신호 전위  $V_{in}$ )에서, 이동도  $\mu$ 가 큰 화소 회로  $Pa$ 의 휘도(구동 전류  $I_{ds}$ )는 높고, 이동도  $\mu$ 가 작은 화소 회로  $Pb$ (구동 전류  $I_{ds}$ )의 휘도는 낮아진다.

- <121> 도 6a 내지 도 6d의 (3)은, 임계값 보정 및 이동도 보정 모두 실행하는 경우이다. 임계값 전압  $V_{th}$  및 이동도  $\mu$ 의 차이는 완전하게 보정된다. 그 결과, 화소 회로  $Pa$ 와 화소 회로  $Pb$ 의  $V_{in}-I_{ds}$  특성은 서로 일치한다. 따라서, 모든 계조(신호 전위  $V_{in}$ )에 대해 휘도( $I_{ds}$ )가 동일 레벨로 되어, 화면 휘도의 균일성이 현저히 개선된다.

- <122> 도 6a 내지 도 6d의 (4)는, 임계값 보정 및 이동도 보정 모두 실행하지만, 임계값 전압  $V_{th}$ 의 보정이 불충분한 경우이다. 예를 들면, 1회의 임계값 보정 동작에서는 구동 트랜지스터(121)의 임계값 전압  $V_{th}$ 에 상당하는 전압을 충분히 축적 캐패시터(120)에 유지시킬 수 없는 경우이다. 이때에는, 임계값 전압  $V_{th}$ 의 차가 제거되지 않기 때문에, 화소 회로  $Pa$ 와 화소 회로  $Pb$ 에서는 저계조의 영역에서 휘도(구동 전류  $I_{ds}$ )에 차가 나타난다. 따라서, 임계값 전압  $V_{th}$ 의 보정이 불충분한 경우에는, 저계조에서 휘도의 얼룩짐(non-uniformity)이 나타나, 화질을 손상시킨다.

- <123> <화소 회로의 동작; 비교예>

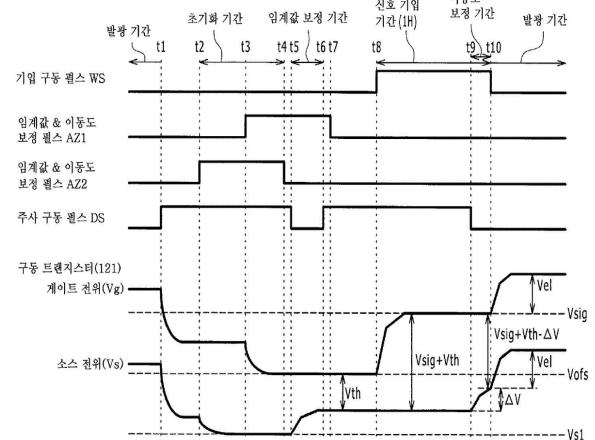

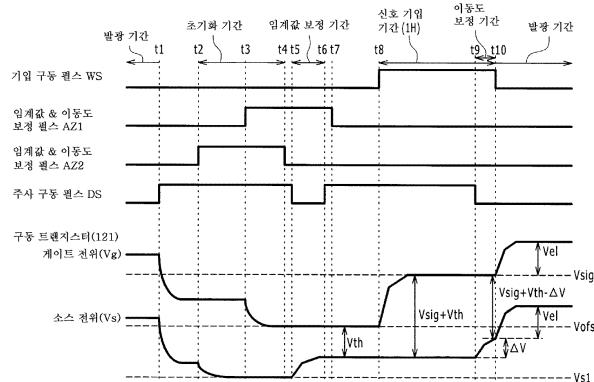

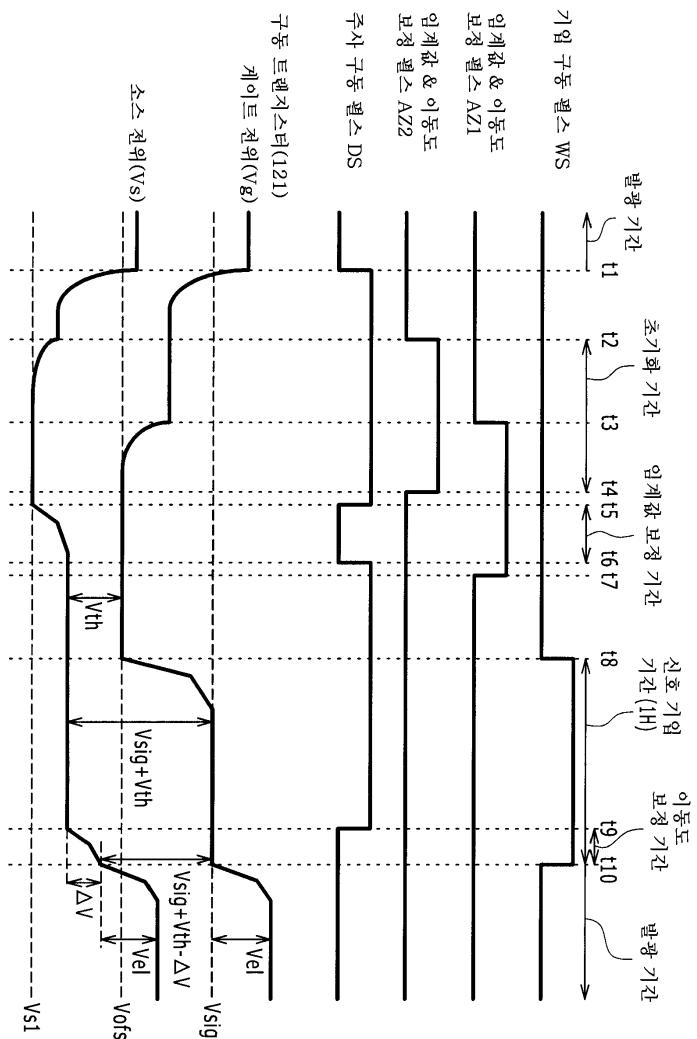

- <124> 도 7은 제2 비교예의 화소 회로 P의 동작을 설명하는 타이밍차트이다. 후술하는 본 실시예의 구동 타이밍에서의 각 구동 펄스 자체는, 기본적으로 도 7의 타이밍차트에 나타내는 것과 동일하다. 사실상, 본 실시예에 따른 화소 회로 P의 구동 타이밍을 나타내는 타이밍차트를 도 7의 타이밍차트가 포함한다.

- <125> 도 7에서는 시간 축 t를 따라서, 기입 구동 펄스 WS, 임계값 & 이동도 보정 펄스 AZ1, AZ2, 및 주사 구동 펄스

DS의 파형을 나타낸다. 전술한 설명으로부터 이해되는 바와 같이, 스위칭 트랜지스터(123, 124, 125)는 n채널 형이기 때문에, 각 펄스 AZ1, AZ2, WS가 각각 하이(H) 레벨일 때에 온되고, 로우(L) 레벨일 때에는 오프된다. 한편, 발광 제어 트랜지스터(122)는 p채널형이기 때문에, 주사 구동 펄스 DS가 하이 레벨일 때에 오프되고, 로우 레벨일 때에 온된다. 또한, 이 타이밍차트는 각 펄스 WS, AZ1, AZ2, DS의 파형과 함께 구동 트랜지스터(121)의 게이트단 G의 전위 변화 및 소스단 S의 전위 변화도 나타낸다.

<126> 비교예의 화소 회로 P에서, 통상의 발광 상태에서는, 구동 주사부(105)로부터 출력되는 주사 구동 펄스 DS만이 액티브-L 상태이고, 다른 펄스, 즉, 기입 주사부(104) 및 임계값 & 이동도 보정 주사부(114, 115)로부터 각각 출력되는 기입 구동 펄스 WS 및 임계값 & 이동도 보정 펄스 AZ1, AZ2가 인액티브-L 상태이다. 따라서, 발광 제어 트랜지스터(122)만이 온 상태이다.

<127> 1 필드 동안에 화소 어레이부(102)의 각 행이 일회 순차적으로 주사된다. 해당 필드가 시작되기 전의 기간(t1 이전)에, 모든 펄스 WS, AZ1, AZ2, DS가 로우 레벨에 있다. 따라서, n채널형의 스위칭 트랜지스터(123, 124, 125)는 오프 상태에 있는 한편, p채널형의 발광 제어 트랜지스터(122)만이 온 상태이다.

<128> 따라서, 구동 트랜지스터(121)는 온 상태의 발광 제어 트랜지스터(122)를 통해서 제1 전원 전위 Vc1에 접속하기 때문에, 소정의 게이트-소스간 전압 Vgs에 따라서 구동 전류 Ids를 유기 EL 소자(127)에 공급한다. 따라서, 타이밍 t1 이전에 유기 EL 소자(127)는 발광한다. 이때, 구동 트랜지스터(121)에 인가되는 게이트-소스간 전압 Vgs는 게이트 전위 Vg와 소스 전위 Vs의 차로 나타낸다.

<129> 이때, 구동 트랜지스터(121)는 포화 영역에서 동작하도록 설정된다. 따라서, 포화 영역에서 동작하는 트랜지스터의 드레인단과 소스간에 흐르는 전류를 Ids, 이동도를  $\mu$ , 채널 폭을 W, 채널 길이를 L, 게이트 용량을 Cox, 트랜지스터의 임계값 전압을 Vth로 하면, 원리적으로는, 구동 트랜지스터(121)는 수학식 1에 나타낸 값을 갖는 정전류원이다.

<130> 새로운 필드가 시작되는 타이밍 t1에서, 주사 구동 펄스 DS가 로우 레벨로부터 하이 레벨로 절환된다(t1). 따라서, 타이밍 t1에서, 모든 스위칭 트랜지스터(122~125)가 오프 상태이다. 이에 의해 발광 제어 트랜지스터(122)가 턴오프되고, 구동 트랜지스터(121)는 제1 전원 전위 Vc1로부터 접속해제된다. 따라서, 게이트 전압 Vg나 소스 전압 Vs가 저하되고, 유기 EL 소자(127)의 발광이 정지되어, 비발광 기간이 시작된다.

<131> 다음으로, 임계값 & 이동도 보정 펄스 AZ1, AZ2를 순서대로 액티브-H 상태로 설정함으로써, 검지 트랜지스터(123, 124)를 턴온한다. 또한, 검지 트랜지스터(123, 124)는 어느 쪽이 먼저 턴온되어도 된다. 따라서, 유기 EL 소자(127)에 전류가 흐르지 않도록 하여, 유기 EL 소자(127)를 비발광 상태로 설정한다. 도 7에 도시한 예에서는, 우선 임계값 & 이동도 보정 펄스 AZ2를 액티브-H 상태로 설정해서 검지 트랜지스터(124)를 턴온시키고(t2), 그 후에 임계값 & 이동도 보정 펄스 AZ1을 액티브-H 상태로 설정해서 검지 트랜지스터(123)를 턴온시킨다(t3).

<132> 이때, 구동 트랜지스터(121)는 소스단 S에 검지 트랜지스터(124)를 통해서 접지 전위 Vs1이 공급됨으로써, 구동 트랜지스터(121)의 소스 전위 Vs가 초기화된다.(t2~t3) 또한, 구동 트랜지스터(121)의 게이트단 G에는 검지 트랜지스터(123)를 통해서 접지 전위 Vofs가 공급됨으로써, 구동 트랜지스터(121)의 게이트 전위 Vg가 초기화된다(t3~t4).

<133> 이에 의해, 구동 트랜지스터(121)의 게이트-소스간에 접속된 축적 캐패시터(120)의 양끝의 전위차가 구동 트랜지스터(121)의 임계값 전압 Vth 이상으로 설정된다. 이때, 구동 트랜지스터(121)의 게이트-소스간 전압 Vgs는 "Vofs-Vs1"의 값을 취한다. "Vs1<Vofs-Vth"로 설정되기 때문에, 구동 트랜지스터(121)는 온 상태를 유지하고, 그것에 따른 전류 Ids1이 흐른다.

<134> 여기에서, 유기 EL 소자(127)를 비발광 상태로 설정하기 위해서는,  $V_{cath}+V_{thEL}>V_{s1}-V_{th}$ 의 관계에 있는 것, 즉, 유기 EL 소자(127)의 애노드단 A에 인가된 전압  $V_{el}(=V_{s1}-V_{th})$ 을 유기 EL 소자(127)의 임계값 전압  $V_{thEL}$ 과 캐소드 전압  $V_{cath}$ 의 합보다도 작도록 접지 전위 Vofs와 접지 전위 Vs1의 전압을 설정할 필요가 있다. 이렇게 하면, 유기 EL 소자(127)는, 역바이어스 상태로 설정되어, 유기 EL 소자(127)에 전류가 흐르지 않아, 비발광 상태로 된다.

<135> 따라서, 구동 트랜지스터(121)의 드레인 전류 Ids1은 제1 전원 전위 Vc1로부터 온 상태에 있는 검지 트랜지스터(124)를 통해서 접지 전위 Vs1에 흐른다. 또한,  $V_{ofs}-V_{s1}=V_{gs}>V_{th}$ 로 설정함으로써, 후속하는 타이밍 t5에서 행해지는 임계값 전압 Vth의 변동 보정의 준비를 행한다. 환연하면, 기간 t2~t5는, 구동 트랜지스터(121)의 리

세트 기간(초기화 기간)이나 이동도 보정의 준비 기간에 상당한다.

<136> 유기 EL 소자(127)의 임계값 전압  $V_{thEL}$ 에 관해서는,  $V_{thEL} > V_s$ 로 설정된다. 이에 의해, 유기 EL 소자(127)에는 마이너스 바이어스가 인가되어, 유기 EL 소자(127)는 소위 역바이어스 상태로 설정된다. 이 역바이어스 상태는, 이후에 행하는 임계값 전압  $V_{th}$ 의 변동 보정 및 캐리어 이동도  $\mu$ 의 변동 보정의 동작을 정상적으로 동작시키기 위해서 필요하다.

<137> 다음으로, 임계값 & 이동도 보정 펄스 AZ2를 인액티브-L 상태로 설정하고(t4), 그와 거의 동시에(약간 늦게) 주사 구동 펄스 DS를 액티브-L 상태로 설정한다(t5). 이에 의해, 검지 트랜지스터(124)가 턴오프되는 한편, 발광 제어 트랜지스터(122)가 턴온된다. 이 결과, 구동 전류  $I_{ds}$ 가 축적 캐패시터(120)에 유입된다. 구동 트랜지스터(121)의 임계값 전압  $V_{th}$ 를 보정(소거)하는 임계값 보정 기간이 시작된다.

<138> 구동 트랜지스터(121)의 게이트단 G는 접지 전위  $V_{ofs}$ 에 유지된다. 구동 트랜지스터(121)의 소스 전위  $V_s$ 가 상승해서, 구동 트랜지스터(121)가 컷오프할 때까지 구동 전류  $I_{ds}$ 가 흐른다. 구동 트랜지스터(121)가 컷오프하면, 구동 트랜지스터(121)의 소스 전위  $V_s$ 는 " $V_{ofs}-V_{th}$ "로 된다.

<139> 즉, 유기 EL 소자(127)의 등가 회로는 다이오드와 기생 용량  $C_{el}$ 의 병렬 회로로 나타내기 때문에, " $V_{el} \leq V_{cath} + V_{thEL}$ "인 한, 즉, 유기 EL 소자(127)의 누설 전류가 구동 트랜지스터(121)에 흐르는 전류보다도 상당히 작은 한, 구동 트랜지스터(121)의 전류는 축적 캐패시터(120)와 기생 용량  $C_{el}$ 을 충전하기 위해서 사용된다.

<140> 이 결과, 구동 트랜지스터(121)를 흐르는 드레인 전류  $I_{ds}$ 의 전류 경로가 차단되면, 유기 EL 소자(127)의 애노드단 A의 전압  $V_{el}$ , 즉, 노드 ND(121)의 전위는 시간과 함께 상승한다. 그리고, 노드 ND(121)의 전위(소스 전압  $V_s$ )와 노드 ND(122)의 전압(게이트 전압  $V_g$ ) 사이의 전위차가 정확하게 임계값 전압  $V_{th}$ 로 될 때, 구동 트랜지스터(121)는 온 상태로부터 오프 상태로 되어, 드레인 전류가 흐르지 않게 된다. 이에 의해, 임계값 보정 기간이 종료한다. 즉, 일정 시간 경과 후, 구동 트랜지스터(121)의 게이트-소스간 전압  $V_{gs}$ 는 임계값 전압  $V_{th}$ 의 값을 취한다.

<141> 이때, " $V_{el} = V_{ofs} - V_{th} \leq V_{cath} + V_{thEL}$ "이다. 즉, 노드 ND(121)와 노드 ND(122) 사이에 나타난 전위차=임계값 전압  $V_{th}$ 는 축적 캐패시터(120)에 의해 유지된다. 이렇게, 검지 트랜지스터(123, 124)는 임계값 & 이동도 보정 주사선(114AZ, 115AZ)에 의해 각각 적절한 타이밍에 선택되었을 때 동작하고, 구동 트랜지스터(121)의 임계값 전압  $V_{th}$ 를 검지하여, 이것을 축적 캐패시터(120)에 유지시킨다.

<142> 주사 구동 펄스 DS를 인액티브-H 상태로 설정하고(t6), 임계값 & 이동도 보정 펄스 AZ1을 인액티브-L 상태로 설정하며(t7), 이 순서대로 함으로써 발광 제어 트랜지스터(122)와 검지 트랜지스터(123)를 이 순서대로 턴오프하여, 임계값 제거 동작을 종료시킨다. 발광 제어 트랜지스터(122)를 검지 트랜지스터(123)보다도 먼저 턴오프함으로써, 구동 트랜지스터(121)의 게이트단 G의 전압  $V_g$ 의 변동을 억제하는 것이 가능하다.

<143> 또한, 임계값 제거( $V_{th}$  보정 기간) 경과 후에도, 검지한 구동 트랜지스터(121)의 임계값 전압  $V_{th}$ 를 축적 캐패시터(120)에 보정용 전위로서 유지시킨다.

<144> 이렇게, 타이밍 t5~t6의 기간은 구동 트랜지스터(121)의 임계값 전압  $V_{th}$ 를 검출하는 기간이다. 여기에서 이 검출 기간 t5~t6을 임계값 보정 기간이라고 칭한다.

<145> 다음으로, 기입 구동 펄스 WS를 액티브-H 상태로 설정해서 샘플링 트랜지스터(125)를 턴온하여, 축적 캐패시터(120)에 화소 신호  $V_{sig}$ 를 기입한다(화소 신호  $V_{sig}$ 의 기입을 샘플링이라고도 칭함)(t8~t10). 이러한 영상 신호  $V_{sig}$ 의 샘플링은, 기입 구동 펄스 WS가 인액티브-L 상태로 되돌아가는 타이밍 t10까지 행해진다. 즉, 타이밍 t8~t10의 기간은 신호 기입 기간(이하 샘플링 기간이라고도 칭함)이라고 칭한다. 통상적으로, 샘플링 기간은, 1 수평 기간(1H)으로 설정된다.

<146> 이 샘플링 기간(t8~t10)에, 구동 트랜지스터(121)의 게이트단 G에 화소 신호  $V_{sig}$ 의 신호 전위  $V_{in}$ 을 공급함으로써, 게이트 전압  $V_g$ 를 신호 전위  $V_{in}$ 에 대응하는 구동 전위로 설정한다. 신호 전위  $V_{in}$ 에 대응하고 축적 캐패시터(120)에 기입되는 정보의 크기의 비율을 기입 계인  $G_{input}$ 이라고 칭한다. 이때, 화소 신호  $V_{sig}$ 는 구동 트랜지스터(121)의 임계값 전압  $V_{th}$ 에 부가되는 형태로 유지된다. 이 결과, 구동 트랜지스터(121)의 임계값 전압  $V_{th}$ 의 변동은 통상적으로 제거되며, 이는 임계값 보정을 행해지는 것을 의미한다.

<147> 구동 트랜지스터(121)의 게이트-소스간 전압  $V_{gs}$ , 즉, 축적 캐패시터(120)에 기입되는 구동 전위는, 축적 캐패시터(120)(용량값  $C_s$ )와 유기 EL 소자(127)의 기생 용량  $C_{el}$ (용량값  $C_{el}$ )과 게이트-소스간의 기생 용량(용량값

$C_{gs}$ )에 의해, 수학식 2와 같이 결정된다.

## 수학식 2

$$V_{gs} = \frac{C_{el}}{C_{el} + C_s + C_{gs}} (V_{sig} - V_{ofs}) + V_{th}$$

&lt;148&gt;

그러나, 일반적으로, 기생 용량  $C_{el}$ 은 축적 캐패시터(120)의 용량값  $C_s$  및 게이트-소스간의 기생 용량값  $C_{gs}$ 에 비하여 훨씬 크다. 즉, 유기 EL 소자(127)의 기생 용량(등가 용량)  $C_{el}$ 에 비하여 축적 캐패시터(120)는 충분히 작다. 이 결과, 영상 신호  $V_{sig}$ 의 거의 대부분이 축적 캐패시터(120)에 기입된다. 정확하게는, 접지 전위  $V_{ofs}$ 에 대한 영상 신호  $V_{sig}$ 의 차분, 즉, " $V_{sig}-V_{ofs}$ "가 축적 캐패시터(120)에 기입된다.

&lt;150&gt;

따라서, 구동 트랜지스터(121)의 게이트-소스간의 전압  $V_{gs}$ 는, 앞에서 검출 유지된 임계값 전압  $V_{th}$ 와 금회 샘플링된 " $V_{sig}-V_{ofs}$ "를 더하여 얻어진 레벨 " $V_{sig}-V_{ofs}+V_{th}$ "과 동일하다. 이때, 접지 전위  $V_{ofs}$ 를 화소 신호  $V_{sig}$ 의 혹 레벨 부근에 설정해 두면, 접지 전위  $V_{ofs}$ 는  $V_{ofs}=0V$ 로 설정할 수 있다. 따라서, 게이트-소스간 전압  $V_{gs}$ (=구동 전위)는 거의 " $V_{sig}+V_{th}$ "와 동일하게 된다.

&lt;151&gt;

신호 기입 기간이 종료하는 타이밍  $t_{10}$ 보다 전에 주사 구동 펄스 DS를 액티브-L 상태로 하여 발광 제어 트랜지스터(122)를 턴온시킨다( $t_9$ ). 이에 의해, 구동 트랜지스터(121)의 드레인단 D가 발광 제어 트랜지스터(122)를 통해서 제1 전원 전위  $V_{c1}$ 에 접속되기 때문에, 화소 회로 P는 비발광 기간으로부터 발광 기간으로 진행한다.

&lt;152&gt;

이렇게, 샘플링 트랜지스터(125)가 아직 온 상태이고 또한 발광 제어 트랜지스터(122)가 온 상태로 설정된 기간  $t_9 \sim t_{10}$  동안, 구동 트랜지스터(121)의 이동도 보정을 행한다. 기입 구동 펄스 WS와 주사 구동 펄스 DS의 액티브 기간이 서로 겹치는 기간(이동도 보정 기간이라고 칭함)을 조정함으로써, 각 화소의 구동 트랜지스터(121)의 이동도의 보정을 최적화한다. 즉, 신호 기입 기간의 뒤 부분과 발광 기간의 개시 부분이 서로 겹치는 기간  $t_9 \sim t_{10}$  동안 이동도 보정을 적절하게 실행한다.

&lt;153&gt;

또한, 이동도 보정을 실행하는 발광 기간의 개시시에는, 유기 EL 소자(127)는 실제로는 역바이어스 상태에 있기 때문에 발광하지 않는다. 이동도 보정 기간  $t_9 \sim t_{10}$  동안, 구동 트랜지스터(121)의 게이트단 G가 영상 신호  $V_{sig}$ (보다 정확하게는 신호 전위  $V_{in}$ )에 대응하는 전위로 고정된 상태에서, 구동 트랜지스터(121)에 구동 전류  $Ids$ 가 흐른다.

&lt;154&gt;

여기에서, " $V_{ofs}-V_{th}<V_{thEL}$ "로 설정함으로써, 유기 EL 소자(127)는 역바이어스 상태로 설정되기 때문에, 다이오드 특성이 아니라 단순한 용량 특성을 나타낸다. 따라서, 구동 트랜지스터(121)에 흐르는 구동 전류  $Ids$ 는 축적 캐패시터(120)의 용량값  $C_s$ 와 유기 EL 소자(127)의 기생 용량(등가 용량)  $C_{el}$ 의 용량값  $C_{el}$ 의 양자를 결합하여 얻어진 용량 " $C=C_s+C_{el}$ "에 기입된다. 이에 의해 구동 트랜지스터(121)의 소스 전위  $V_s$ 는 상승한다.

&lt;155&gt;

도 7의 타이밍차트에서는, 이 상승분을  $\Delta V$ 로 나타낸다. 이 상승분, 즉, 이동도 보정 파라미터인 부귀환량  $\Delta V$ 는 결국, 축적 캐패시터(120)에 유지된 게이트-소스간 전압  $V_{gs}$ 로부터 차감되게 되기 때문에, 부귀환이 곱해진다. 이렇게, 구동 트랜지스터(121)의 구동 전류  $Ids$ 를 동일한 구동 트랜지스터(121)의 게이트-소스간 전압  $V_{gs}$ 에 부귀환함으로써, 이동도  $\mu$ 을 보정하는 것이 가능하다. 또한, 부귀환량  $\Delta V$ 는 이동도 보정 기간  $t_9 \sim t_{10}$ 의 시간 폭  $t$ 를 조정함으로써 최적화 가능하다.

&lt;156&gt;

본 예의 경우, 영상 신호  $V_{sig}$ 의 레벨이 높을수록, 구동 전류  $Ids$ 는 커지고,  $\Delta V$ 의 절대값도 커진다. 따라서, 발광 휘도 레벨에 따른 이동도 보정을 행할 수 있다. 또한, 이동도가 높은 구동 트랜지스터(121)와 낮은 구동 트랜지스터(121)를 생각하는 경우, 영상 신호  $V_{sig}$ 를 일정하게 하면, 구동 트랜지스터(121)의 이동도  $\mu$ 가 클수록,  $\Delta V$ 의 절대값도 커진다.

&lt;157&gt;

환연하면, 이동도 보정 기간에 이동도가 높은 구동 트랜지스터(121)는 낮은 구동 트랜지스터(121)에 비하여 소스 전위가 크게 상승한다. 또한, 소스 전위가 크게 상승할수록, 게이트와 소스간의 전위차가 작아져, 전류가 흐르기 어려워지도록 부귀환이 곱해진다. 이동도  $\mu$ 가 클수록, 부귀환량  $\Delta V$ 가 커지기 때문에, 화소마다 이동도  $\mu$ 의 변동을 제거하는 것이 가능하다. 이동도가 상이한 구동 트랜지스터(121)이어도, 동일한 구동 전류  $Ids$ 를 유기 EL 소자(127)에 흘릴 수 있다. 이동도 보정 기간을 조정함으로써, 그 부귀환량  $\Delta V$ 를 최적화할 수 있다.

&lt;158&gt;

다음으로, 기입 주사부(104)는 기입 구동 펄스 WS를 인액티브-L 상태로 절환한다( $t_{10}$ ). 이에 의해, 샘플링 트

랜지스터(125)가 비도통(오프) 상태로 설정되어, 발광 기간이 시작된다. 이 후, 다음 프레임(혹은 필드)으로 옮기고, 임계값 보정 준비 동작, 임계값 보정 동작, 이동도 보정 동작, 및 발광 동작이 반복된다.

<159> 이 결과, 구동 트랜지스터(121)의 게이트단 G는 영상 신호선(106HS)으로부터 접속해제된다. 구동 트랜지스터(121)의 게이트단 G에의 신호 전위 Vin의 인가가 해제되기 때문에, 구동 트랜지스터(121)의 게이트 전위 Vg는 상승 가능하게 된다.

<160> 이때, 구동 트랜지스터(121)에 흐르는 구동 전류 Ids는 유기 EL 소자(127)에 흐르고, 유기 EL 소자(127)의 애노드 전위는 구동 전류 Ids에 따라서 상승한다. 이 상승분을 Vel로 한다. 이때, 구동 트랜지스터(121)의 게이트-소스간 전압 Vgs는 축적 캐패시터(120)의 효과에 의해 일정하기 때문에, 구동 트랜지스터(121)는 일정 전류(구동 전류 Ids)를 유기 EL 소자(127)에 흘린다. 그 결과, 전압 강하가 발생하고, 유기 EL 소자(127)의 애노드단 A의 전위 Vel(=노드 ND(121)의 전위)은, 유기 EL 소자(127)에 전류 또는 구동 전류 Ids가 흐를 수 있는 전압까지 상승한다. 반면에, 축적 캐패시터(120)에 의해 유지된 게이트-소스간 전압 Vgs는 "Vsigt+Vth-ΔV"의 값을 유지한다.

<161> 결국, 소스 전위 Vs의 상승에 수반하여, 유기 EL 소자(127)의 역바이어스 상태는 해소되기 때문에, 구동 전류 Ids가 유기 EL 소자(127)에 유입됨으로써, 유기 EL 소자(127)는 실제로 발광을 개시한다. 이때의 유기 EL 소자(127)의 애노드 전위의 상승(Vel)은 구동 트랜지스터(121)의 소스 전위 Vs의 상승임에 틀림없다. 구동 트랜지스터(121)의 소스 전위 Vs는 "-Vth+ΔV+Vel"이다.

<162> 발광시의 구동 전류 Ids와 게이트 전압 Vgs의 관계는, 전술한 트랜지스터 특성을 나타낸 수학식 1의 Vgs에 "Vsigt+Vth-ΔV"를 대입함으로써, 수학식 3과 같이 나타낼 수 있다.

### 수학식 3

$$Ids = k \mu (Vgs - Vth)^2 = k \mu (Vsigt - \Delta V)^2$$

<163> 수학식 3에서,  $k=(1/2)(W/L)Cox$ 이다. 수학식 3은, 임계값 전압 Vth의 항이 삭제되고, 유기 EL 소자(127)에 공급되는 구동 전류 Ids는 구동 트랜지스터(121)의 임계값 전압 Vth에 의존하지 않는 것을 나타낸다. 기본적으로 구동 전류 Ids는 영상 신호의 신호 전압 Vsigt에 의해 결정된다. 환연하면, 유기 EL 소자(127)는 영상 신호 Vsigt에 따른 휘도로 발광한다.

<165> 이때, 신호 전위 Vin은 귀환량 ΔV로 보정된다. 보정량 ΔV는 정확하게는 수학식 3의 계수부에 위치하는 이동도 μ의 효과를 없애도록 기능한다. 따라서, 구동 전류 Ids는 실질적으로 신호 전위 Vin에만 의존한다. 구동 전류 Ids는 임계값 전압 Vth에 의존하지 않기 때문에, 임계값 전압 Vth가 제조 프로세스에 의해 변동해도, 드레인-소스간의 구동 전류 Ids는 변동하지 않으므로, 유기 EL 소자(127)의 발광 휘도도 변동하지 않는다.

<166> 구동 트랜지스터(121)의 게이트단 G와 소스단 S 사이에는 축적 캐패시터(120)가 접속된다. 그 축적 캐패시터(120)의 효과에 의해, 발광 기간의 개시시 부트스트랩 동작이 행해지고, 구동 트랜지스터(121)의 게이트-소스간 전압 "Vgs=Vin-ΔV+Vth"를 일정하게 유지한 채, 이 동작에서 구동 트랜지스터(121)의 게이트 전위 Vg 및 소스 전위 Vs가 상승한다. 구동 트랜지스터(121)의 소스 전위 Vs가 "-Vth+ΔV+Vel"로 됨으로써, 게이트 전위 Vg는 "Vin+Vel"로 된다.

<167> 여기에서, 유기 EL 소자(127)는, 발광 시간이 길어지면 그 I-V 특성이 변화한다. 그 때문에, 노드 ND(121)의 전위도 변화된다. 그러나, 축적 캐패시터(120)의 효과 때문에, 노드 ND(121)의 전위 상승에 연동하는 방식으로 노드 ND(122)의 전위도 상승한다. 이리하여, 구동 트랜지스터(121)의 게이트-소스간 전위 Vgs는 노드 ND(121)의 전위 상승에 불구하고, 항상 거의 "Vsigt+Vth-ΔV"로 유지된다. 따라서, 유기 EL 소자(127)에 흐르는 전류는 변화되지 않는다. 따라서, 유기 EL 소자(127)의 I-V 특성이 열화해도, 일정 전류 Ids가 항상 계속해서 흐른다. 따라서, 유기 EL 소자(127)는 화소 신호 Vsigt에 따른 휘도로 발광을 계속하여, 휘도는 변화되지 않는다.

<168> 이 후, 다음 필드의 타이밍 t1에서, 주사 구동 필스 DS가 인액티브-H 상태로 설정되어 발광 제어 트랜지스터(122)가 턴오프된다. 이에 의해, 발광이 종료됨과 함께 해당 필드가 종료된다. 이 후, 전술한 바와 마찬가지로, 다음 필드의 동작으로 옮겨서, 임계값 전압 보정 동작, 이동도 보정 동작, 및 발광 동작이 반복된다.

<169> 이렇게, 제2 비교예의 화소 회로 P에서는, 부트스트랩 회로(130)는 전기 광학 소자의 일례인 유기 EL 소자(127)의 전류-전압 특성의 변화를 보정함으로써 구동 전류를 일정하게 유지하는 구동 신호 일정화 회로로서 기능한

다.

<170> 또한, 제2 비교예의 화소 회로 P는 임계값 & 이동도 보정 회로(140)를 구비한다. 임계값 보정 기간에서의 검지 트랜지스터(123, 124)의 작용에 의해, 구동 트랜지스터(121)의 임계값 전압 Vth를 소거하여, 그 임계값 전압 Vth의 변동의 영향을 받지 않는 일정 전류 Ids를 훌릴 수 있다. 따라서, 입력 화소 신호에 대응하는 안정된 계조로 표시할 수 있어, 고화질의 화상을 얻을 수 있다.

<171> 또한, 샘플링 트랜지스터(125)에 의한 영상 신호 Vsig의 기입 동작과 연동한 발광 제어 트랜지스터(122)의 이동도 보정 기간 동안의 작용에 의해, 구동 트랜지스터(121)의 캐리어 이동도  $\mu$ 을 반영시킨 게이트-소스간 전압 Vgs가 설정되고, 해당 캐리어 이동도  $\mu$ 의 변동의 영향을 받지 않는 일정 전류 Ids를 훌릴 수 있다. 따라서, 입력 화소 신호에 대응하는 안정된 계조로 표시할 수 있어, 고화질의 화상을 얻을 수 있다.

<172> 즉, 임계값 & 이동도 보정 회로(140)는, 구동 트랜지스터(121)의 특성 변동(본 예에서는 임계값 전압 Vth 및 캐리어 이동도  $\mu$ 의 변동)에 의한 구동 전류 Ids에 끼치는 영향을 방지하기 위해서, 임계값 전압 Vth 및 캐리어 이동도  $\mu$ 에 의한 영향을 보정해서 구동 전류를 일정하게 유지하는 구동 신호 일정화 회로로서 기능한다.

<173> 제2 비교예에서 나타낸 부트스트랩 회로(130)나 임계값 & 이동도 보정 회로(140)의 회로 구성은, 구동 트랜지스터(121)로서 n채널형을 이용하여 유기 EL 소자(127)를 구동하기 위한 구동 신호를 일정하게 유지하는 구동 신호 일정화 회로의 일례에 지나지 않는다. 유기 EL 소자(127)의 경시 열화나 n채널형의 구동 트랜지스터(121)의 특성 변동(예를 들면 임계값 전압이나 이동도 등의 변동이나 변화)에 의한 구동 전류 Ids에 끼치는 영향을 방지하기 위한 구동 신호 일정화 회로로서는, 그 밖의 공지의 다양한 회로를 적용할 수 있다.

<174> <이동도 보정의 폐해에 대해서>

<175> 여기에서, 도 5와 도 7을 참조하여, 이동도 보정의 효과와 이동도 보정에 의한 폐해에 대해서 고찰해 본다. 도 5를 참조하여 설명한 바와 같이, 제조 프로세스나 경시에서 발생하는 이동도  $\mu_1$ ,  $\mu_2$ 의 변동에 대하여, 발광시의 게이트-소스간 전압 Vgs가 "Vin+Vth- $\Delta V$ "로 나타내도록 하는 임계값 보정 및 이동도 보정을 곱함으로써, 이동도  $\mu$ 의 차이를 억제할 수 있다. 이동도 보정 기간을 조정하고 각각의 이동도 보정 파라미터  $\Delta V_1$ ,  $\Delta V_2$ ( $\Delta V=Ids \cdot t/Cel$ )를 최적화함으로써, 이동도  $\mu$ 의 차이를 제거할 수 있다.

<176> 그러나, 도 7에 나타낸 구동 타이밍에서는, 기입 구동 펄스 WS를 액티브-H 상태로 하여 샘플링 트랜지스터(125)를 턴온시켜서 축적 캐페시터(120)에 신호 전위 Vin에 대응하는 정보(구동 전위)를 기입한 후의, 기입 구동 펄스 WS와 주사 구동 펄스 DS의 각 액티브 기간(즉, 발광 제어 트랜지스터(122)와 샘플링 트랜지스터(125)의 각각의 온 기간)의 오버랩 기간을 이동도 보정 기간( $t_9 \sim t_{10}$ )으로 설정한다. 이동도 보정 기간 동안, 구동 트랜지스터(121)에 영상 신호 Vsig(신호 전위 Vin)가 지속적으로 공급된다. 게이트 전위 Vg가 고정된 채로, 이동도 보정량인 이동도 보정 파라미터  $\Delta V$ 의 분만큼 구동 트랜지스터(121)의 소스 전위 Vs가 상승한다.

<177> 이동도 보정 기간 동안의 소스 전위 Vs의 상승  $\Delta V$ 는, 그 시점의 구동 트랜지스터(121)의 게이트-소스간 전압 Vgs( $=Vsigt+Vth$ )에 영향을 준다. 소스 전위 Vs에서의  $\Delta V$ 의 상승분만큼, 게이트-소스간 전압 Vgs가 감소한다. 그 때문에, 발광 기간에서의 구동 전류 Ids에 기여하는 게이트-소스간 전압 Vgs(즉, 구동 전위)가 작아진다. 따라서, 발광 회로는 이동도 보정을 행하지 않는 경우에 비하여 저하한다.

<178> 이동도 보정에 기인하는 발광 회로 저하를 방지하는 한 방법으로서, 예를 들면, 샘플링 기간( $t_8 \sim t_9$ )에, 원하는 회로의 발광에 필요한 영상 신호 Vsig(보다 정확하게는 신호 전위 Vin)에  $\Delta V$ 를 더하여 얻어진 전압을 기입할 수 있다. 즉, 이동도 보정에 의한 게이트-소스간 전압 Vgs의 감소분을 보충하도록, 보다 큰 영상 신호 Vsig를 화소 회로 P에 공급해서 축적 캐페시터(120)에 큰 구동 전위를 기입할 수 있다. 그러나, 이 방법으로는, 이동도 보정을 행하지 않는 경우에 비하여 신호 전위 Vin의 진폭이 대폭 상승하는 결과로 된다. 따라서, 전원 전압이나 기입 구동 펄스 WS를 증가시켜, 소비 전압의 증대로 연결될 필요가 있다.

<179> 따라서, 본 실시예에서는, 이동도 보정에 기인하는 게이트-소스간 전압 Vgs의 저하를 방지함에 있어서, 영상 신호 Vsig(보다 정확하게는 신호 전위 Vin)에 이동도 보정 파라미터  $\Delta V$ 의 분을 더하지 않아도, 이동도 보정에 기인하는 게이트-소스간 전압 Vgs의 저하를 방지할 수 있는 구조를 구비한다. 이하, 구체적으로 설명한다.

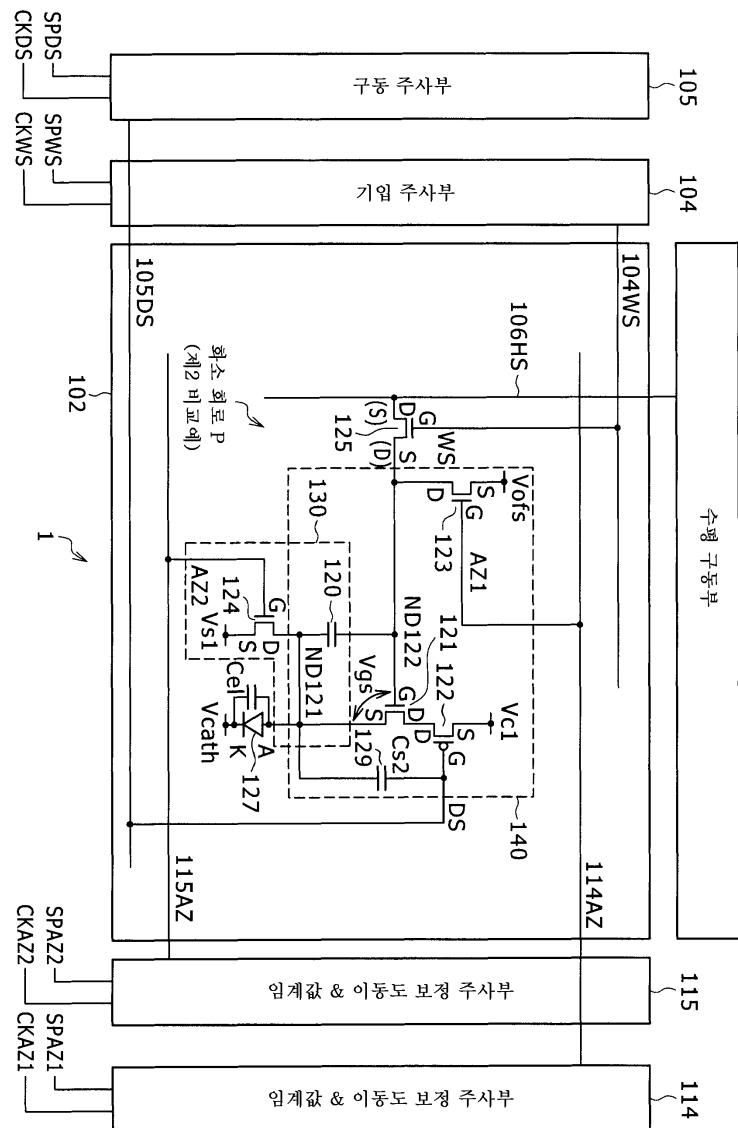

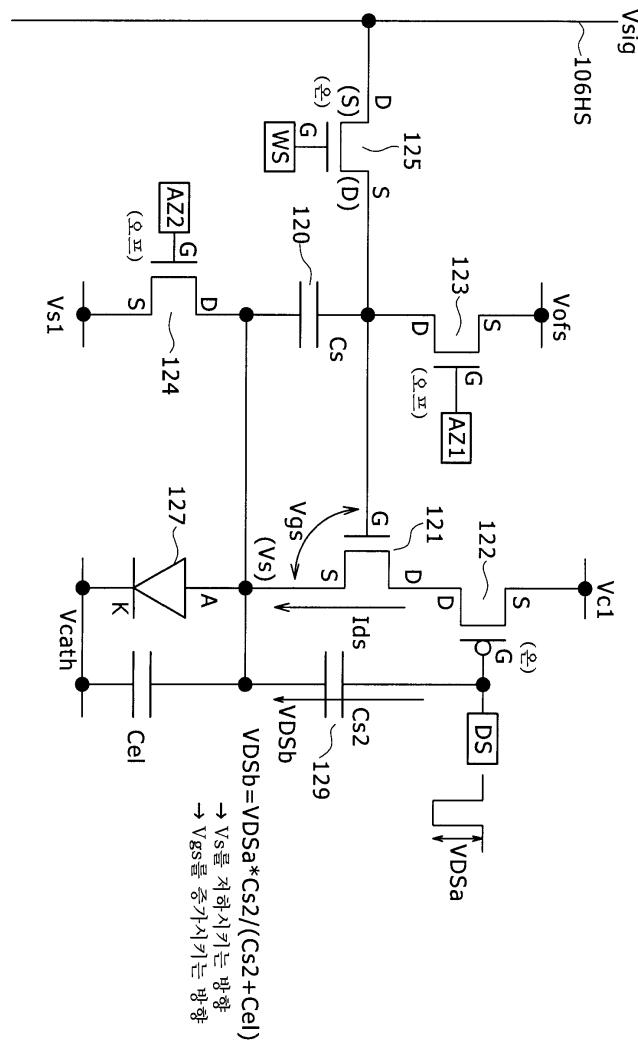

<180> <화소 회로: 본 실시예>

<181> 도 8은 영상 신호 Vsig에 이동도 보정 파라미터  $\Delta V$ 의 분을 더하지 않고 이동도 보정에 기인하는 게이트-소스간 전압 Vgs의 저하를 방지하는 것을 가능하게 하는 본 실시예에 따른 화소 회로 P와, 화소 회로 P를 구비한 유기 EL 표시 장치의 일 실시예를 도시하는 도면이다. 본 실시예에 따른 화소 회로 P를 화소 어레이부(102)에 구비

하는 유기 EL 표시 장치를 본 실시예에 따른 유기 EL 표시 장치(1)라고 칭한다.

<182> 본 실시예에 따른 유기 EL 표시 장치(1)는, 도 2에 도시한 제2 비교예의 화소 회로 P와 마찬가지의 기능 요소를 갖는 복수의 화소 회로 P를 행렬 형상으로 배치한 화소 어레이부(102)를 구비하고, 예를 들면, 유기 EL 소자(1)가 유기 EL 소자(127)의 경시 열화에 의한 구동 전류 변동을 방지하는 회로(부트스트랩 회로)를 탑재하고, 또한 유기 EL 소자(1)가 구동 트랜지스터(121)의 특성 변동(임계값 전압 변동이나 이동도 변동)에 의한 구동 전류 변동을 방지하는 구동 방식을 채용하는 점에 특징을 갖는다. 그 때문에, 구동 타이밍으로서는, 기본적으로는 도 7에 도시한 제2 비교예와 동일한 것이 적용된다.

<183> 또한, 본 실시예에 따른 유기 EL 표시 장치(1)에서는, 화소 회로 P마다, 발광 제어 트랜지스터(122)의 게이트단 G와 노드 ND(121)(구동 트랜지스터(121)의 소스단 S 및 축적 캐패시터(120)의 한쪽 단자와 유기 EL 소자(127)의 애노드단 A의 접속점)에 용량값 Cs2의 용량 소자(129)를 추가하고, 용량 소자(129)를 통해서 발광 제어 트랜지스터(122)의 게이트단 G에 공급되는 주사 구동 펄스 DS의 천이 정보(특히 이동도 보정 개시시의 소스 전위에 대하여 게이트-소스간 전압 Vgs를 넓히는 방향의 정보)를 노드 ND(121)에 공급함으로써, 발광 기간에서의 게이트-소스간 전압 Vgs를 넓히는 점에 특징을 갖는다.

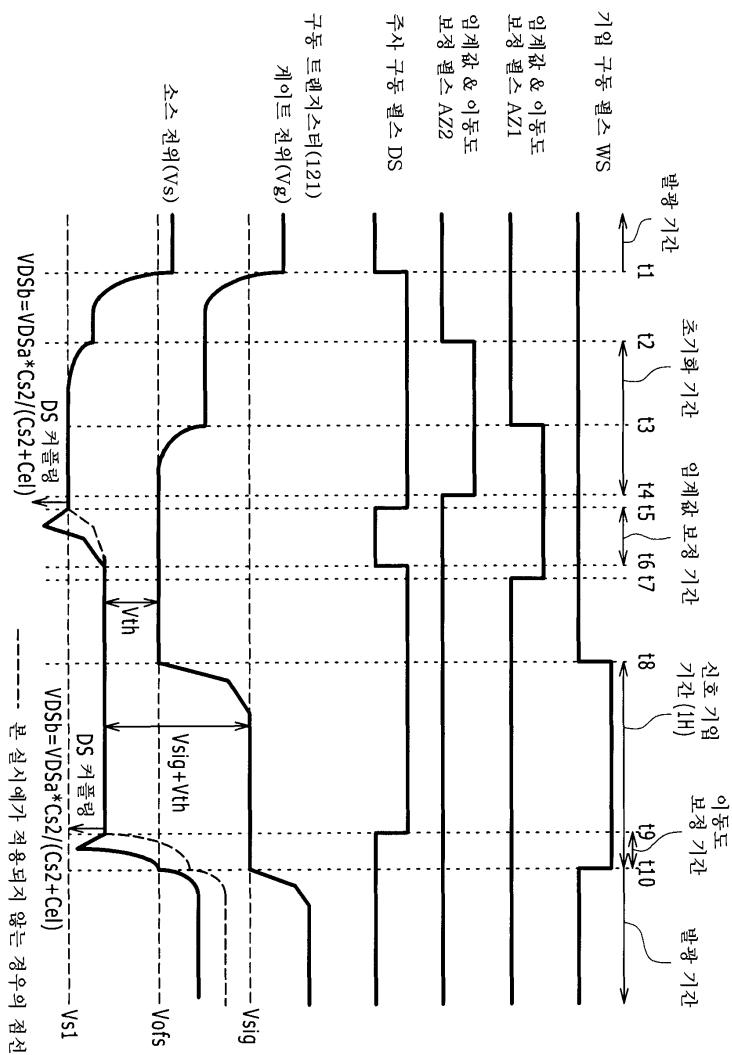

<184> <화소 회로의 동작; 본 실시예>

<185> 도 9는 본 실시예에 따른 화소 회로의 동작을 설명하는 타이밍차트이다. 도 10은 이동도 보정에 의한 게이트-소스간 전압 Vgs의 감소분을 보정하는 동작을 설명하는 도면이다.

<186> 제2 비교예의 화소 회로 P를 구동하는, 도 7의 타이밍차트와의 비교로부터 추측되는 바와 같이, 각 스위치 트랜지스터(122, 123, 124, 125)에 대한 구동 펄스 자체에는 다르지 않다.

<187> 그러나, 본 실시예에 따른 화소 회로 P에서는, p채널형의 발광 제어 트랜지스터(122)의 게이트단 G와 노드 ND(121), 즉, 구동 트랜지스터(121)의 소스단 사이에, 용량 소자(129)를 구비한다. 주사 구동 펄스 DS의 천이 정보가 노드 ND(121)의 전위(소스 전위 Vs)에 더해진다. 또한, 샘플링 트랜지스터(125)가 오프될 때에는, 게이트 전위 Vg도 축적 캐패시터(120)의 효과에 의해 약간 상승한다.

<188> 따라서, 예를 들면, 주사 구동 펄스 DS가 액티브-L 상태로부터 인액티브-H 상태로 천이하는 발광 제어 트랜지스터(122)의 턴오프의 동작시(타이밍 t1, t6)에서는, 발광 제어 트랜지스터(122)의 게이트단 G의 전압 변동이 용량 소자(129)를 통해서 구동 트랜지스터(121)의 소스에 플러스의 커플링 VDS(VDS는 주사 구동 펄스 DS의 진폭임)가 입력된다. 따라서, 구동 트랜지스터(121)의 소스 전위 Vs나 게이트 전위 Vg가 약간 상승한다.

<189> 한편, 주사 구동 펄스 DS가 인액티브-H 상태로부터 액티브-L 상태로 천이하는 발광 제어 트랜지스터(122)의 턴온의 동작시(타이밍 t5, t9)에는, 발광 제어 트랜지스터(122)의 게이트단 G의 전압 변동이 용량 소자(129)를 통해서 구동 트랜지스터(121)의 소스에 마이너스의 커플링 VDS로서 입력된다. 따라서, 구동 트랜지스터(121)의 소스 전위 Vs나 게이트 전위 Vg가 약간 하강한다.

<190> 주사 구동 펄스 DS의 진폭 VDS를 VDSA(V: 볼트)로 하면, 용량 소자(129)를 통해서 구동 트랜지스터(121)의 소스 단 S측에 커플링하는 전압 VDSb(V: 볼트)는 수학식 4로 나타낸다.

## 수학식 4

$$VDSb = VDSA * Cs2 / (Cs2 + Cel)$$

<191> 예를 들면, 커플링은 발광 제어 트랜지스터(122)가 턴온되는 타이밍(t9)이기 때문에, 구동 트랜지스터(121)의 게이트-소스간 전압 Vgs는 "Vth+VDSb"로 된다. 그 후, 샘플링 트랜지스터(125)의 턴온에 의해 원하는 발광에 필요한 신호 전위(영상 신호 Vsig에 대응하는 값)를 축적 캐패시터(120)에 기입하여, "Vgs=Vth+VDSb+Vsig"이 된다. 발광 제어 트랜지스터(122)의 온 주기가 샘플링 트랜지스터(125)의 온 주기와 오버랩됨으로써, 이동도 보정 기간이 시작된다. 여기에서, VDSb의 커플링량이 이동도 보정으로 소비하는 전압과 동일하면, 이동도 보정후의 게이트-소스간 전압 Vgs는 "Vth+Vsig"이고, 샘플링 트랜지스터(125)의 턴오프 후에 발광 기간으로 천이한다.

<192> 이렇게, 본 실시예의 구조에서는, 액티브-L의 주사 구동 펄스 DS가 공급되는 p채널형의 발광 제어 트랜지스터(122)의 게이트단 G와 구동 트랜지스터(121)의 소스단 S(노드 ND(121)) 사이에 용량 소자(129)를 추가하고, 용량 소자(129)를 통해서 주사 구동 펄스 DS의 천이 정보(특히 이동도 보정 개시시의 소스 전위에 대하여 게이트-소스간 전압을 넓히는 방향의 정보)를 노드 ND(121)에 공급한다.

<194> 이동도 보정에 의한 게이트-소스간 전압  $V_{gs}$ 의 저하분  $\Delta V$ 를, 이동도 보정 동작의 개시시에(이동도 보정 전에), 주사 구동 펄스 DS에 의한 커플링 전압  $V_{DSb}$ 의 분만큼 넓힌다. 즉, 이동도 보정시에 소비되는 분의 전압  $\Delta V$ 를 발광 제어 트랜지스터(122)에 공급되는 주사 구동 펄스 DS에 기초한 커플링에 의해 전압  $V_{DSb}$ 의 분만큼 부가하여 보충한다. 따라서, 발광 기간 동안의 게이트-소스간 전압  $V_{gs}$ 를 넓힐 수 있다. 이에 의해, 이동도 보정에 기인하는 발광 휘도 저하를 방지할 수 있고, 영상 신호  $V_{sig}$ (신호 전위  $V_{in}$ )의 진폭을 낮출 수 있어, 통상의 영상 신호  $V_{sig}$ 만을 축적 캐패시터(120)에 기입하는 것만으로 충분하기 때문에, 저소비 전력화에 기여할 수 있다.

<195> 이동도 보정에 기인하는 발광 휘도 저하를 방지함에 있어서, 영상 신호  $V_{sig}$ (보다 정확하게는 신호 전위  $V_{in}$ )에 이동도 보정 파라미터  $\Delta V$ 의 분을 더하지 않아도, 이동도 보정에 기인하는 발광 휘도 저하를 방지할 수 있다. 따라서, 패널의 저소비 전력화에 기여할 수 있다.

<196> 아울러, 부가적인 효과로서, 영상 신호  $V_{sig}$ (보다 정확하게는 신호 전위  $V_{in}$ )의 정보를 축적 캐패시터(120)에 기입할 때의 기입 계인  $G_{input}$ 의 증대도 기대할 수 있다. 예를 들면, 구동 트랜지스터(121)의 게이트단 G에 형성되는 기생 용량을 무시하면, 축적 캐패시터(120)의 용량  $C_s$  및 유기 EL 소자(127)의 기생 용량  $C_{el}$ 을 이용하여, 도 2에 도시한 제2 비교예의 화소 회로 P에서의 기입 계인  $G_{input0}$ 은 수학식 5의 (1)과 같이 나타낼 수 있고, 한편, 도 8에 도시한 본 실시예의 화소 회로 P에서의 기입 계인  $G_{input1}$ 은 수학식 5의 (2)와 같이 나타낼 수 있다.

## 수학식 5

$$G_{input0} = 1 - C_s / (C_s + C_{el}) \quad (1)$$

$$G_{input1} = 1 - C_s / (C_s + C_s + C_{el}) \quad (2)$$

<199> 수학식 5의 (1)과 수학식 5의 (2)의 비교로부터 알 수 있는 바와 같이, 본 실시예의 화소 회로 P에서 기입 계인  $G_{input}$ 의 증가가 예상된다. 이에 의해, 발광 휘도를 종래와 동일하게 만드는 것을 생각한 경우, 보다 작은 신호 전위  $V_{in}$ 이어도 되어, 영상 신호  $V_{sig}$ 의 진폭을 더욱 낮추는 것이 가능하여, 저소비 전력화를 더욱 촉진할 수 있다.

<200> 이렇게, 이동도 보정시에 소비되는 분(이동도 보정 파라미터  $\Delta V$ )의 전압을 발광 제어 트랜지스터(122)의 게이트단과 구동 트랜지스터(121)의 소스단 사이에 배치한 용량 소자(129)를 통해서 관여하는, 이동도 보정 기간 개시를 나타내는 주사 구동 펄스 DS의 하강 정보의 커플링 효과에 의해 보충함으로써, 신호 진폭을 대폭 삭감하여, 저소비 전력화에 크게 기여할 수 있다.

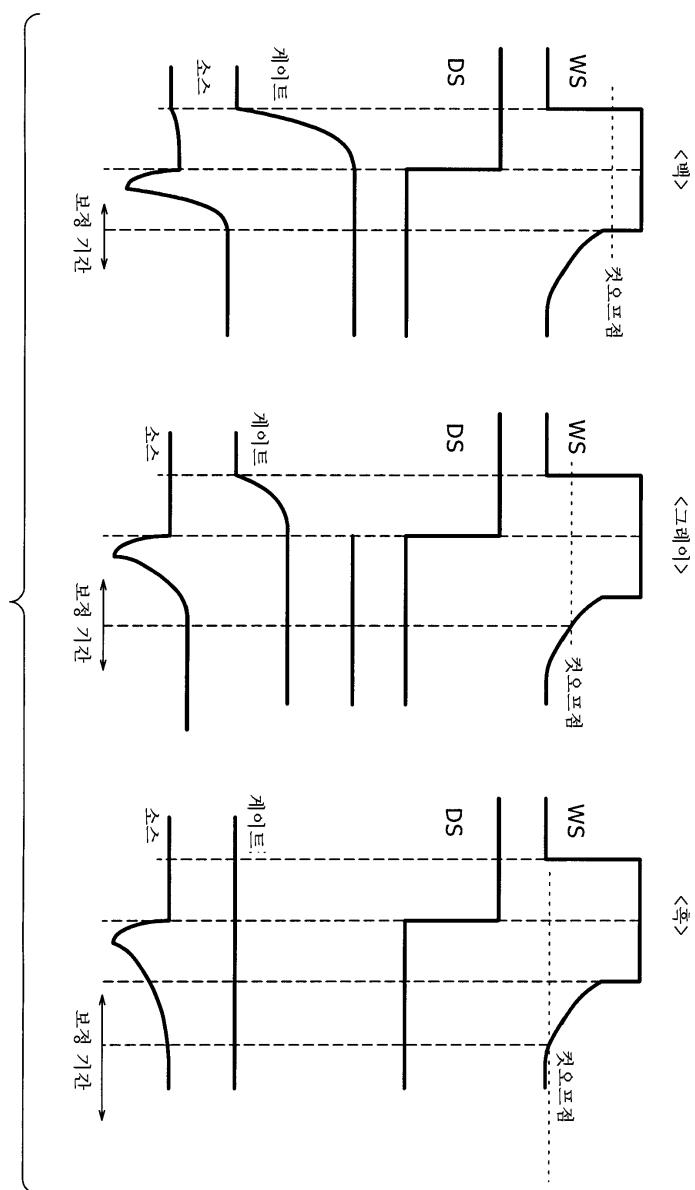

<201> <변형예>

<202> 도 11은 이동도 보정에 의한 게이트-소스간 전압  $V_{gs}$ 의 감소분을 보정하는 변형예의 동작을 설명하는 도면이다. 도 11에서는 기입 구동 펄스 WS를, 하강을 둔하게 하여 계조마다 컷오프 점을 변화시키는 구조와 DS 커플링파의 조합에서, 백, 그레이, 흑의 각 표시시의 DS 커플링시의, 구동 펄스 WS, DS와, 구동 트랜지스터(121)의 게이트 및 소스의 각 전압을 나타낸다.

<203> 전술한 보정의 구조에서는, 실제로는  $V_{gs}$ 의 보완량은 계조에 상관없이 일정하다. 따라서, 예를 들면, 흑이 부유하게 될 수 있다. 한편, 계조마다 최적의 이동도 보정 시간을 위해서, 기입 구동 펄스 WS를 하강을 둔하게 하여 계조마다 컷오프 점을 변화시키는 구조가 있다. 이 구조를 이용함으로써, 백 신호 영역에서는 DS 커플링에 의해 게이트-소스간 전압  $V_{gs}$ 를 넓혀, 신호 전압을 저하시킬 수 있고, 그레이-흑 신호에서는 기입 구동 펄스 WS의 하강을 완만하게 함으로써 이동도 보정량을 많게 하여, 원하는 계조를 실현할 수 있다.

<204> 즉, DS 커플링에 의해 "신호 기입+ $a$ "의 전압을 게이트-소스간 전압  $V_{gs}$ 에 부가한다. 이  $a$ 는 신호 전압에 상관없이 일정하다. 그러나, 여기에서의 문제는 저계조로 원하는 휘도보다 높은 휘도이다. 극단적인 예로서 흑을 기입하는 경우, 임계값 보정후, 0V의 신호 전압이 기입되면 흑 표시로 되지만, DS 커플링에 의해  $+a$ 가 부가된다.  $+a$ 를 제거하기 위해서, 이동도 보정 시간을 길게 취할 필요가 있다. 이동도 보정 시간은 저계조일수록 길게 할 필요가 있기 때문에, 기입 구동 펄스 WS를, 하강 에지를 둔하게 하여 계조마다 컷오프 점을 변화시키는 구조의 파형으로 하고, 이에 의해 이동도 보정 시간을 신호 전압마다 바꿀 필요가 있다.

<205> 이상, 본 발명에 대해서 실시예를 이용하여 설명했지만, 본 발명의 기술적 범위는 상기 실시예에 기재된 범위에는 한정되지 않는다. 발명의 요지를 일탈하지 않는 범위에서 상기 실시예에 다양한 변경 또는 개량을 가할 수

있고, 그러한 변경 또는 개량을 가한 형태도 본 발명의 기술적 범위에 포함된다.

<206> 또한, 상기한 실시예는, 청구항에 따른 발명을 한정하는 것이 아니며, 또한 실시예 중에서 설명되는 특징의 조합의 모두가 발명의 해결 수단에 필수적이다라고는 할 수 없다. 전술한 실시예에는 다양한 단계의 발명이 포함되고, 개시되는 복수의 구성 요건에서의 적절한 조합에 의해 다양한 발명을 추출할 수 있다. 실시예에 나타내지는 전체 구성 요건으로부터 몇 가지의 구성 요건이 삭제되어도, 효과가 얻어지는 한에서, 이 몇 가지의 구성 요건이 삭제된 구성이 발명으로서 추출될 수 있다.

<207> <화소 회로 및 구동 타이밍의 변형예>

<208> 예를 들면, 회로 이론상은 "쌍대 원리(duality principle)"가 성립하기 때문에, 화소 회로 P에 대해서는, 이 관점으로부터의 변형을 가할 수 있다. 이 경우, 도시하지 않지만, 우선, 도 8에 도시한 5TR 구성의 화소 회로 P가 n채널형의 구동 트랜지스터(121)를 포함하며, p채널형의 구동 트랜지스터(이하 p형 구동 트랜지스터(121p)라고 칭함)를 이용하여 화소 회로 P를 구성한다. 따라서, p채널형의 발광 제어 트랜지스터(122)를 액티브-H의 주사 구동 펄스가 공급되는 n채널형의 발광 제어 트랜지스터(이하 n형 발광 제어 트랜지스터(122n)이라고 칭함)로 바꾸고, 또한 영상 신호 Vsig의 신호 전위 Vin의 극성이나 전원 전압의 대소 관계를 역전시키는 등, 쌍대 원리를 따른 변경을 가한다.

<209> 쌍대 원리를 적용해서 구동 트랜지스터를 p형으로 변경한 변형예에 따른 유기 EL 표시 장치에서도, 전술한 n형 구동 트랜지스터를 이용한 기본예에 따른 유기 EL 표시 장치와 마찬가지로, 용량 소자(129)를 n형 발광 제어 트랜지스터(122n)의 게이트단과 p형 구동 트랜지스터(121p)의 소스단에 접속시킨다. 따라서, 이동도 보정 개시시에 p형 구동 트랜지스터(121p)의 게이트-소스간 전압 Vgs를 미리 넓혀 두고 나서 이동도 보정을 행할 수 있다. 따라서, 이동도 보정에 수반하는 p형 구동 트랜지스터(121p)의 게이트-소스간 전압 Vgs의 감소분을 보충할 수 있다.

<210> 전술한 변형예는, 도 8에 도시한 5TR 구성에 대하여 "쌍대 원리"에 따른 변경을 가한 것이지만, 회로 변경의 방법은 이에 한정되는 것이 아니라, 5TR 구성 이외이어도 된다. 샘플링 트랜지스터(125)를 온 상태로 설정하고, 신호 전위 Vin에 따른 정보를 축적 캐페시터(120)에 유지시킨 후에, 샘플링 트랜지스터(125)를 온 상태로 한 채로 이동도 보정 동작을 행하는 화소 회로 P 및 구동 타이밍인 한, 본 실시예의 사상을 적용할 수 있다.

### 도면의 간단한 설명

<211> 도 1은 본 발명에 따른 표시 장치의 일 실시예인 액티브 행렬형 표시 장치의 구성을 개략적으로 도시하는 블록도.

<212> 도 2는 도 1에 도시한 유기 EL 표시 장치를 구성하는 본 실시예의 화소 회로 P에 대한 비교예를 도시하는 도면.

<213> 도 3은 유기 EL 소자나 구동 트랜지스터의 동작점을 설명하는 도면.

<214> 도 4a 내지 도 4c는 유기 EL 소자나 구동 트랜지스터의 특성 변동이 구동 전류 Ids에 끼치는 영향을 설명하는 도면.

<215> 도 5는 구동 트랜지스터의 특성 변동이 구동 전류에 끼치는 영향의 개선 방법의 개념을 설명하는 도면(1).

<216> 도 6은 구동 트랜지스터의 특성 변동이 구동 전류에 끼치는 영향의 개선 방법의 개념을 설명하는 도면(2).

<217> 도 7은 제2 비교예의 화소 회로의 동작을 설명하는 타이밍차트.

<218> 도 8은 본 실시예의 화소 회로 P와 유기 EL 표시 장치의 일 실시예를 도시하는 도면.

<219> 도 9는 본 실시예에 따른 화소 회로의 동작을 설명하는 타이밍차트.

<220> 도 10은 이동도 보정에 의한 게이트-소스간 전압 Vgs의 감소분을 보정하는 동작을 설명하는 도면.

<221> 도 11은 이동도 보정에 의한 게이트-소스간 전압 Vgs의 감소분을 보정하는 변형예의 동작을 설명하는 도면.

<222> [도면의 주요 부분에 대한 부호의 설명]

<223> 1: 유기 EL 표시 장치

<224> 101: 기판

- <225> 102: 화소 어레이부

- <226> 103: 수직 구동부

- <227> 104: 기입 주사부

- <228> 104WS: 기입 주사선

- <229> 105: 구동 주사부

- <230> 106: 수평 구동부

- <231> 106HS: 영상 신호선

- <232> 109: 제어부

- <233> 114, 115: 임계값 & 이동도 보정 주사부

- <234> 114AZ, 115AZ: 임계값 & 이동도 보정 주사선

- <235> 120: 축적 캐패시터

- <236> 121: 구동 트랜지스터

- <237> 122: 발광 제어 트랜지스터

- <238> 123, 124: 검지 트랜지스터

- <239> 125: 샘플링 트랜지스터

- <240> 127: 유기 EL 소자

- <241> 129: 용량 소자

- <242> 130: 부트스트랩 회로

- <243> 140: 임계값 & 이동도 보정 회로

- <244> AZ1, AZ2: 임계값 & 이동도 보정 펄스

- <245> Ce1: 유기 EL 소자의 기생 용량

- <246> DS: 주사 구동 펄스

- <247> P: 화소 회로

- <248> Vsig: 영상 신호

- <249> WS: 기입 구동 펄스

도면

도면1

도면2

도면3

## 도면4a

## 도면4b

## 도면4c

**도면5**

$$I_{ds} = \frac{1}{2} \cdot \mu \cdot \left(\frac{W}{L}\right) \cdot C_{ox} \cdot (V_{gs} - V_{th})^2$$

임계값 보정 및 이동도 보정 :  $V_{in} + V_{th} - \Delta V$

**도면6a****도면6b**

도면6c

도면6d

## 도면7

## 도면8

## 도면9

도면10

도면11

|                |                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路，显示装置及其驱动方法                                                                          |         |            |

| 公开(公告)号        | KR1020080084730A                                                                         | 公开(公告)日 | 2008-09-19 |

| 申请号            | KR1020080023893                                                                          | 申请日     | 2008-03-14 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                     |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                     |         |            |

| [标]发明人         | TOYOMURA NAOBUMI<br>도요무라나오부미<br>UCHINO KATSUHIDE<br>우찌노 가쓰히데<br>IIDA YUKIHITO<br>이이다유끼히또 |         |            |

| 发明人            | 도요무라나오부미<br>우찌노 가쓰히데<br>이이다유끼히또                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/32 G09G3/20 H05B33/12                                                     |         |            |

| CPC分类号         | G09G2300/0842 G09G2300/0861 G09G2320/043 G09G3/3233 G09G2300/0819                        |         |            |

| 代理人(译)         | CHANG, SOO KIL<br>LEE , JUNG HEE                                                         |         |            |

| 优先权            | 2007068020 2007-03-16 JP                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                |         |            |

### 摘要(译)

在具有移动的有机EL显示装置中是校正，视频信号的幅度很大。该运动仍然可以防止由校正引起的发光亮度降低。电容元件(129)被添加到辐射控制晶体管(122)的栅极G和驱动晶体管(121)的源极端S。在运动中，运动是在校正操作开始时根据校正的栅极-源极之间的电压Vgs的劣化 $\Delta V$ ，该运动增加了通过注入的耦合在校正中消耗的分钟的电压 $\Delta V$ 。驱动脉冲DS，其中辐射控制晶体管(122)作为电压VDSb的分钟被提供并且它被补充。以这种方式，电压Vgs在发光时段在栅极-源极之间变宽。该运动可以防止由校正引起的发光亮度降低。可以降低图像信号Vsigt的幅度。仅通过在存储电容器(120)中写入正常图像信号Vsigt就足够了。它可以有助于降低功耗。有机电致发光显示器，写入扫描线，图像信号线，阈值和移动是校正扫描线，存储电容器，自举电路，寄生电容，注入驱动脉冲，内切驱动脉冲。