**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

G09G 3/30 (2006.01)

(45) 공고일자 2006년11월27일

(11) 등록번호 10-0649513

(24) 등록일자 2006년11월17일

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2005-0029920 | (65) 공개번호 | 10-2006-0047168 |

| (22) 출원일자 | 2005년04월11일     | (43) 공개일자 | 2006년05월18일     |

| 심사청구일자    | 2005년04월11일     |           |                 |

|            |                    |             |        |

|------------|--------------------|-------------|--------|

| (30) 우선권주장 | JP-P-2004-00117332 | 2004년04월12일 | 일본(JP) |

|            | JP-P-2005-00092566 | 2005년03월28일 | 일본(JP) |

|            | JP-P-2005-00092588 | 2005년03월28일 | 일본(JP) |

|            | JP-P-2005-00096835 | 2005년03월30일 | 일본(JP) |

(73) 특허권자 산요덴키가부시키가이샤

일본 오사카후 모리구치시 게이한 혼도오리 2쵸메 5반 5고

(72) 발명자 이께다 교지

일본 기후깨 요로궁 요로쪼 오바 835-33

(74) 대리인 장수길

구영창

이중희

(56) 선행기술조사문현

EP1170719 A1 JP2001036822 A

KR1020020056353 A KR1020030001530 A

KR1020040058576 A

\* 심사관에 의하여 인용된 문현

**심사관 : 천대식**

전체 청구항 수 : 총 16 항

**(54) 유기 EL 패널용 화소 회로 및 그 구동 방법**

**(57) 요약**

구동 트랜지스터의 제어단의 전위를 제어함으로써 그 전위에 따른 구동 전류가 유기 EL 소자에 공급된다. 구동 트랜지스터와 상기 유기 EL 소자 사이에 구동 제어 트랜지스터를 삽입 배치하고, 이것에 의해 상기 구동 전류를 온 오프한다. 또한, 단락 트랜지스터를 설치하고, 이 단락 트랜지스터에 의해 구동 트랜지스터를 다이오드 접속할지의 여부를 제어한다. 또한, 선택 트랜지스터에 의해, 데이터 라인으로부터의 데이터 신호를 상기 구동 트랜지스터의 제어단에 공급할지의 여부를 제어한다. 그리고, 이 선택 트랜지스터와, 상기 구동 트랜지스터의 제어단 사이에 용량을 배치함과 함께, 이 용량의 상기 선택 트랜지스터측과, 소정의 전원과의 사이의 접속을 전위 제어 트랜지스터에 의해 온 오프한다.

**대표도**

도 1

## 특허청구의 범위

### 청구항 1.

제어단의 전위에 따른 구동 전류를 유기 EL 소자에 공급하는 구동 트랜지스터와,

소정의 전원과 상기 유기 EL 소자 사이에 삽입 배치되고, 상기 구동 전류를 온 오프하는 구동 제어 트랜지스터와,

상기 구동 트랜지스터를 다이오드 접속할지의 여부를 제어하는 단락 트랜지스터와,

데이터 라인으로부터의 데이터 신호를 상기 구동 트랜지스터의 제어단에 공급할지의 여부를 제어하는 선택 트랜지스터와,

이 선택 트랜지스터와, 상기 구동 트랜지스터의 제어단 사이에 삽입 배치된 용량과,

이 용량의 상기 선택 트랜지스터측과, 상기 소정의 전원과의 사이의 접속을 온 오프하는 전위 제어 트랜지스터

를 갖는 유기 EL 패널에 이용되는 화소 회로.

### 청구항 2.

제1항에 있어서,

상기 구동 트랜지스터는, 2개의 피제어단의 일단이 양의 전원에 접속되고, 타단이 상기 구동 제어 트랜지스터에 접속되어

있는 유기 EL 패널에 이용되는 화소 회로.

### 청구항 3.

제2항에 있어서,

상기 전위 제어 트랜지스터는, 상기 용량의 상기 선택 트랜지스터측과, 상기 양의 전원과의 접속을 온 오프하는 유기 EL

패널에 이용되는 화소 회로.

### 청구항 4.

제2항에 있어서,

상기 구동 트랜지스터는, p 채널 트랜지스터인 유기 EL 패널에 이용되는 화소 회로.

### 청구항 5.

제1항에 있어서,

상기 구동 트랜지스터는, 2개의 피제어단의 일단이 상기 구동 제어 트랜지스터에 접속되고, 타단이 상기 유기 EL 소자에

접속되어 있는 유기 EL 패널에 이용되는 화소 회로.

## 청구항 6.

제5항에 있어서,

상기 전위 제어 트랜지스터는, 상기 용량의 상기 선택 트랜지스터측과, 상기 양의 전원과의 접속을 온 오프하는 유기 EL 패널에 이용되는 화소 회로.

## 청구항 7.

제5항에 있어서,

상기 구동 트랜지스터는 n 채널 트랜지스터인 유기 EL 패널에 이용되는 화소 회로.

## 청구항 8.

제1항에 있어서,

상기 선택 트랜지스터의 제어단에 접속되고, 상기 선택 트랜지스터의 온 오프를 제어하는 제어 라인을 갖고,

이 제어 라인에는, 상기 단락 트랜지스터의 제어단도 접속되고, 또한 상기 선택 트랜지스터와, 상기 단락 트랜지스터는, 동시에 온 오프되는 것을 특징으로 하는 유기 EL 패널용 화소 회로.

## 청구항 9.

제1항에 있어서,

상기 선택 트랜지스터의 제어단에 접속되고, 상기 선택 트랜지스터의 온 오프를 제어하는 제어 라인을 갖고,

이 제어 라인에는, 상기 전위 제어 트랜지스터의 제어단도 접속되고, 또한 상기 선택 트랜지스터와, 상기 전위 제어 트랜지스터는, 한쪽이 온되었을 때에 다른 쪽이 오프되는 것을 특징으로 하는 유기 EL 패널용 화소 회로.

## 청구항 10.

제1항에 있어서,

상기 선택 트랜지스터의 제어단에 접속되고, 상기 선택 트랜지스터의 온 오프를 제어하는 제어 라인을 갖고,

이 제어 라인에는, 상기 단락 트랜지스터 및 상기 전위 제어 트랜지스터의 제어단도 접속되고,

또한, 상기 선택 트랜지스터와, 상기 단락 트랜지스터는, 동시에 온 오프되고, 상기 선택 트랜지스터와, 상기 전위 제어 트랜지스터는, 한쪽이 온되었을 때에 다른 쪽이 오프되는 것을 특징으로 하는 유기 EL 패널용 화소 회로.

## 청구항 11.

유기 EL 패널의 화소 회로의 구동 방법으로서,

상기 화소 회로는,

제어단의 전위에 따른 구동 전류를 유기 EL 소자에 공급하는 구동 트랜지스터와,

소정의 전원과 상기 유기 EL 소자 사이에 삽입 배치되고, 상기 구동 전류를 온 오프하는 구동 제어 트랜지스터와,

상기 구동 트랜지스터를 다이오드 접속할지의 여부를 제어하는 단락 트랜지스터와,

데이터 라인으로부터의 데이터 신호를 상기 구동 트랜지스터의 제어단에 공급할지의 여부를 제어하는 선택 트랜지스터와,

이 선택 트랜지스터와, 상기 구동 트랜지스터의 제어단 사이에 삽입 배치된 용량과,

이 용량의 상기 선택 트랜지스터측과, 상기 소정의 전원과의 사이의 접속을 온 오프하는 전위 제어 트랜지스터를 포함하고,

상기 구동 방법은,

선택 트랜지스터 및 단락 트랜지스터를 온으로 하고, 전위 제어 트랜지스터를 오프함과 함께, 상기 용량의 선택 트랜지스터측의 전압을 데이터 신호의 전압으로 한 상태에서, 구동 트랜지스터의 제어단 전압을 구동 트랜지스터의 피제어단의 한 쪽의 전압에 대하여, 구동 트랜지스터의 임계값 전압만큼 상이한 전압으로 세트하는 리세트 공정과,

선택 트랜지스터, 단락 트랜지스터를 오프로 하고, 전위 제어 트랜지스터를 온하여, 구동 트랜지스터의 제어단 전압을 데이터 신호의 전압과, 구동 트랜지스터의 임계값 전압에 따른 전압으로 세트하고, 구동 제어 트랜지스터를 온하여, 구동 트랜지스터로부터의 구동 전류를 유기 EL 소자에 흘리는 발광 공정

을 갖는 유기 EL 패널 화소 회로의 구동 방법.

## 청구항 12.

제11항에 있어서,

상기 리세트 공정의 전 공정으로서, 상기 선택 트랜지스터 및 단락 트랜지스터를 온으로 하고, 전위 제어 트랜지스터를 오프로 하고, 상기 구동 제어 트랜지스터를 온으로 하여, 상기 구동 트랜지스터의 제어단의 전하를 방출하는 디스챠지 공정을 마련하는 유기 EL 패널 화소 회로의 구동 방법.

## 청구항 13.

제1항에 있어서,

상기 구동 제어 트랜지스터는 발광 세트 라인에 의해 온 오프가 제어되고,

상기 전위 제어 트랜지스터는, 상기 용량의 상기 선택 트랜지스터측과, 상기 발광 세트 라인과의 사이의 접속을 온 오프하는 유기 EL 패널용 화소 회로.

## 청구항 14.

제13항에 있어서,

상기 선택 트랜지스터의 제어단에 접속되고, 상기 선택 트랜지스터의 온 오프를 제어하는 제어 라인을 갖고,

이 제어 라인에는, 상기 전위 제어 트랜지스터의 제어단도 접속되고, 또한 상기 선택 트랜지스터와, 상기 전위 제어 트랜지스터는, 상보적으로 온 오프되는 유기 EL 패널용 화소 회로.

## 청구항 15.

제14항에 있어서,

상기 제어 라인에는, 상기 단락 트랜지스터의 제어단도 접속되고, 또한 상기 선택 트랜지스터와, 상기 단락 트랜지스터는 동시에 온 오프되는 유기 EL 패널용 화소 회로.

## 청구항 16.

제13항에 있어서,

상기 선택 트랜지스터의 제어단에 접속되고, 상기 선택 트랜지스터의 온 오프를 제어하는 제어 라인을 갖고,

상기 발광 세트 라인은, 상기 제어 라인에 의해 선택 트랜지스터가 온된 후에, 발광 제어 트랜지스터를 오프하는 전압으로 세트되고, 상기 제어 라인에 의해 선택 트랜지스터가 오프된 후에, 구동 제어 트랜지스터를 온하는 전압으로 세트되는 유기 EL 패널용 화소 회로.

명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

유기 EL 소자에 공급하는 구동 전류를 데이터 신호에 따라 제어하는 유기 EL 화소 회로에 관한 것이다.

자발광 소자인 일렉트로루미네센스(Electroluminescence : 이하 EL) 소자를 각 화소에 발광 소자로서 이용한 EL 표시 장치는, 자발광형임과 함께 얇고 소비 전력이 적다는 등의 유리한 점이 있어, 액정 표시 장치(LCD)나 CRT 등의 표시 장치를 대신하는 표시 장치로서 주목받고 있다.

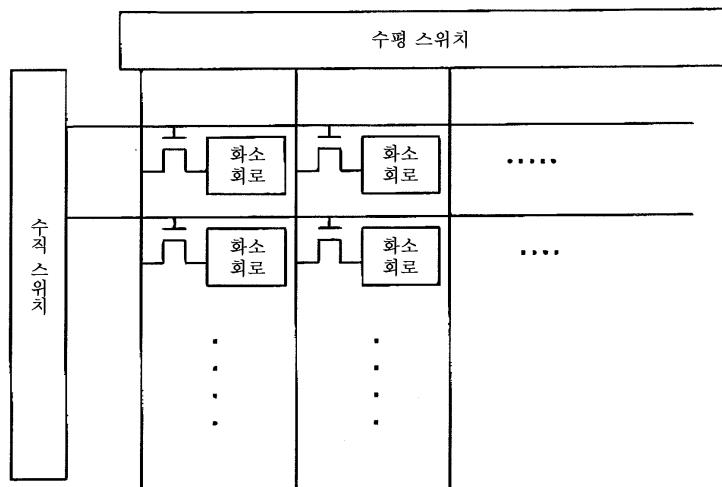

특히, EL 소자를 개별로 제어하는 박막 트랜지스터(TFT) 등의 스위치 소자를 각 화소에 설치하고, 화소마다 EL 소자를 제어하는 액티브 매트릭스형 EL 표시 장치에서는, 고정밀한 표시가 가능하다.

이 액티브 매트릭스형 EL 표시 장치에서는, 기판 상에 복수개의 게이트 라인이 행(수평) 방향으로 연장되고, 복수개의 데이터 라인 및 전원 라인이 열(수직) 방향으로 연장되어 있고, 각 화소는 유기 EL 소자와, 선택 TFT, 구동용 TFT 및 축적 용량을 구비하고 있다. 게이트 라인을 선택함으로써 선택 TFT를 온하여, 데이터 라인 상의 데이터 전압(전압 비디오 신호)을 축적 용량으로 충전하고, 이 전압에 의해 구동 TFT를 온하여 전원 라인으로부터의 전력을 유기 EL 소자에 흘리고 있다.

#### 발명이 이루고자 하는 기술적 과제

그러나, 이러한 화소 회로에서, 매트릭스 형상으로 배치된 화소 회로의 구동 TFT의 임계값 전압이 변동되면, 휘도가 변동되게 되어, 표시 품질이 저하한다고 하는 문제가 있다. 그리고, 표시 패널 전체의 화소 회로를 구성하는 TFT에 대하여, 그 특성을 동일하게 하는 것은 어려우므로, 그 온 오프의 임계값이 변동되는 것을 방지하는 것은 어렵다.

따라서, 구동 TFT에서의 임계값의 변동의 표시에 대한 영향을 방지하는 것이 바람직하다.

여기서, TFT의 임계값의 변동에의 영향을 방지하기 위한 회로에 대해서는, 종래부터 각종 제안이 있다(예를 들면 상기 특허 문헌1).

그러나, 이 제안에서는, 임계값 변동의 보상을 하기 위한 회로를 필요로 한다. 따라서, 이러한 회로를 이용하면, 화소 회로의 소자 수가 증가하고, 개구율이 작아져 버린다고 하는 문제가 있었다. 또한, 보상을 위한 회로를 추가한 경우, 화소 회로를 구동하기 위한 주변 회로에 대해서도 변경이 필요하게 된다고 하는 문제도 있었다.

### 발명의 구성

본 발명은, 효과적으로 구동 트랜지스터의 임계값 전압의 변동을 보상할 수 있는 화소 회로를 제공한다.

본 발명에 따르면, 선택 트랜지스터를 온한 상태에서, 단락 트랜지스터를 온함으로써, 구동 트랜지스터의 제어단 전압을 데이터 전압 및 구동 트랜지스터의 임계값 전압에 따른 것으로 세트하는 것이 가능하다. 따라서, 구동 트랜지스터의 임계값 전압의 변동에 상관없이, 데이터 전압에 따른 구동 전류를 유기 EL 소자에 공급할 수 있다.

또한, 전위 제어 트랜지스터의 일단은, 발광 세트 라인에 접속되어 있다. 발광 세트 라인은, 소정의 전원으로부터의 전압이 세트되기 때문에, 그 전압은 유기 EL 소자에 흐르는 전류 등의 영향을 기본적으로 받지 않아 안정적이다. 따라서, 구동 트랜지스터의 제어단 전압을 정확하게 세트할 수 있다.

또한, 구동 트랜지스터를 n 채널 트랜지스터로 했기 때문에, 트랜지스터의 특성이 우수하며, 그 능동층을 아몰페스 실리콘으로 형성하는 것도 가능하게 된다. 또한, 선택 트랜지스터와 구동 트랜지스터의 제어단 사이에 컨덴서를 삽입해도, 종래의 선택 트랜지스터를 직접 p 채널 구동 트랜지스터의 제어단에 접속한 경우와 동일한 극성의 데이터 신호를 이용할 수 있다.

이하, 본 발명의 실시예에 대하여, 도면에 기초하여 설명한다.

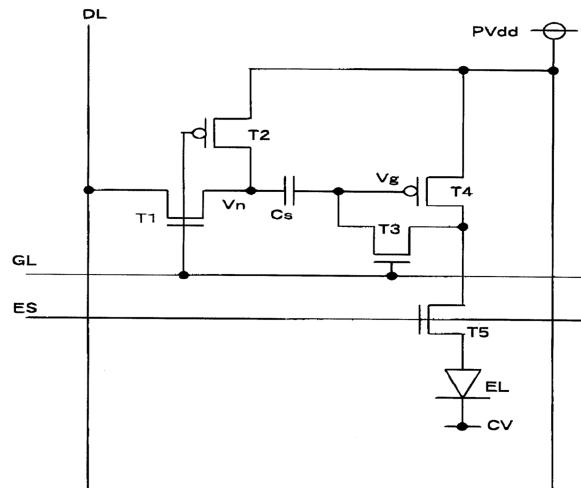

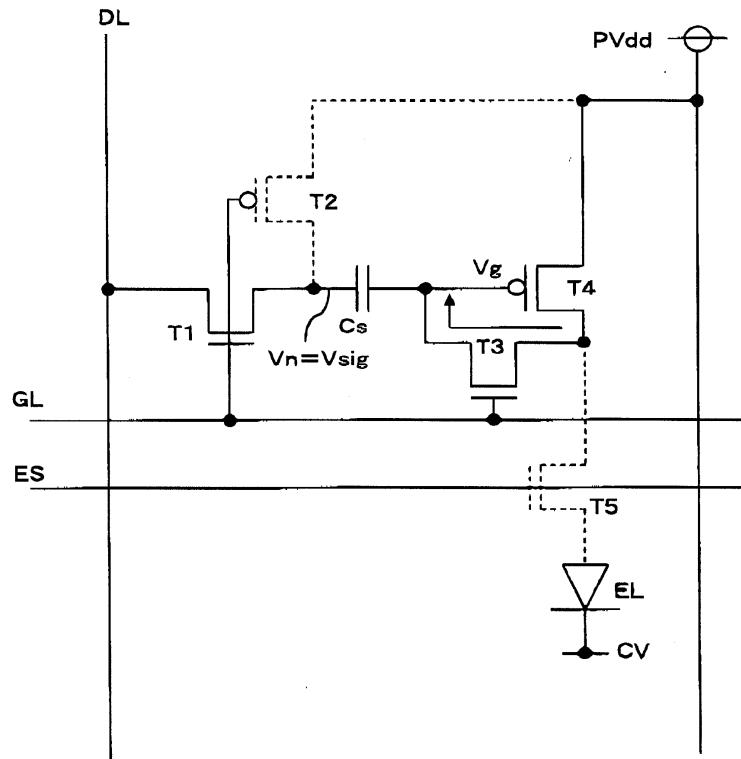

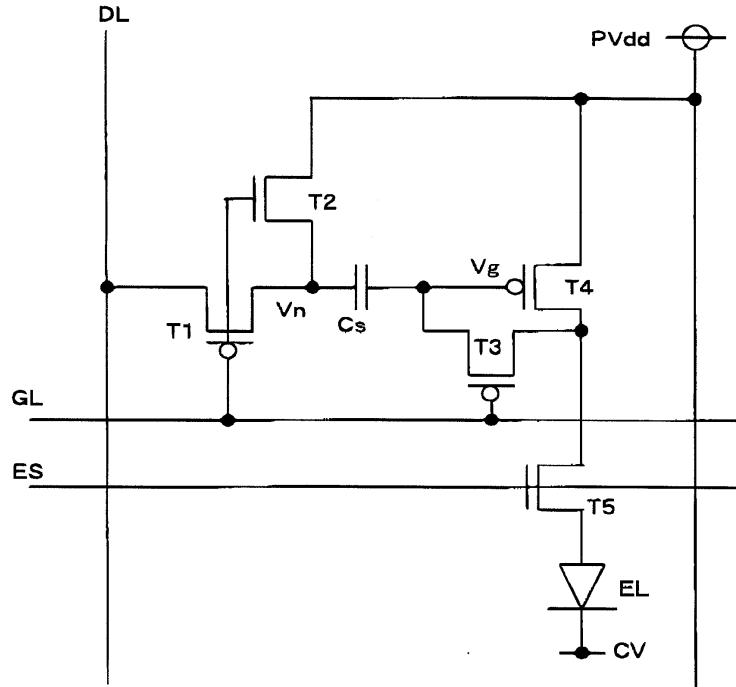

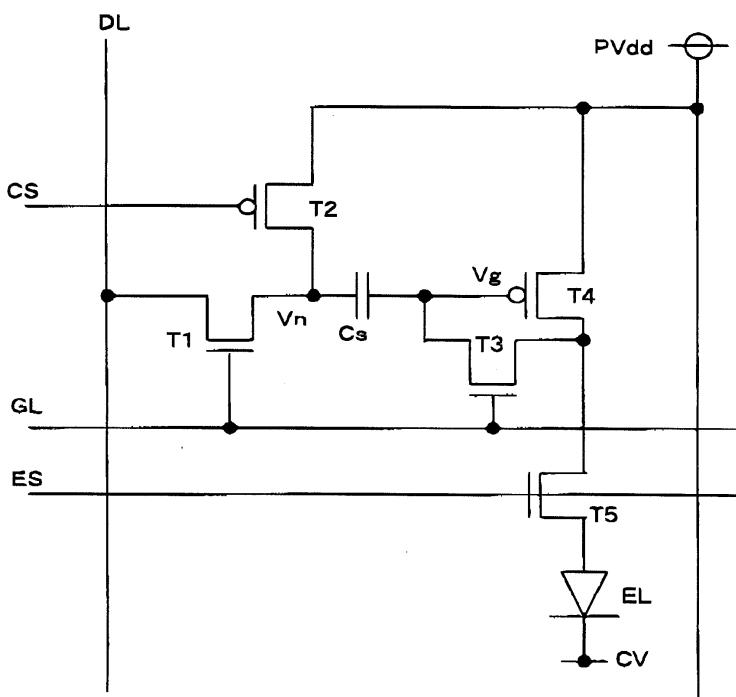

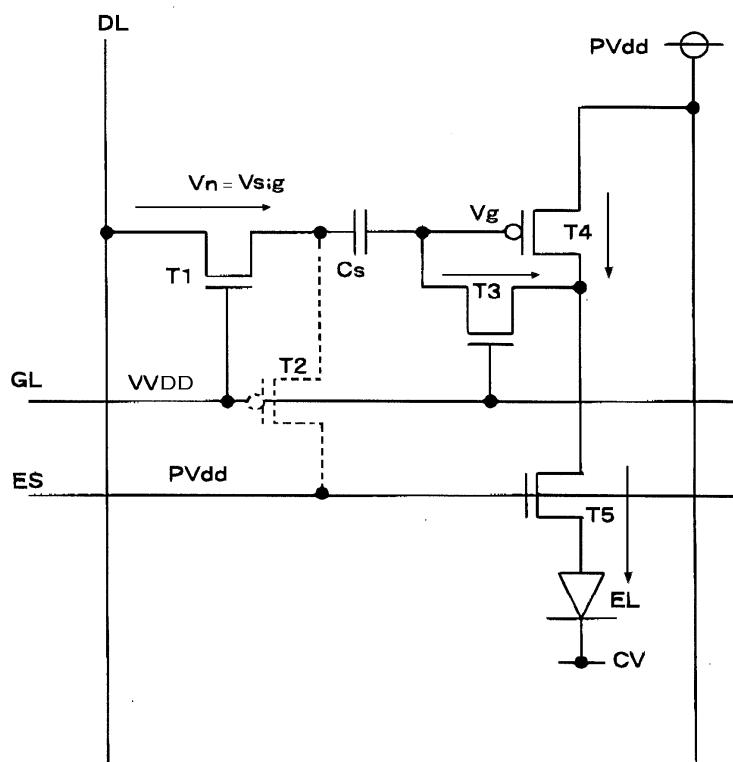

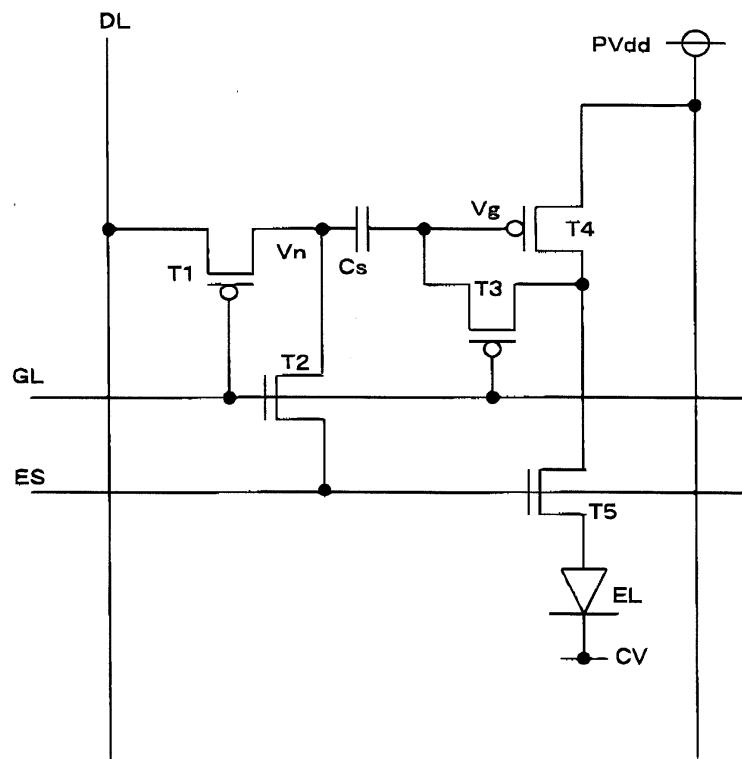

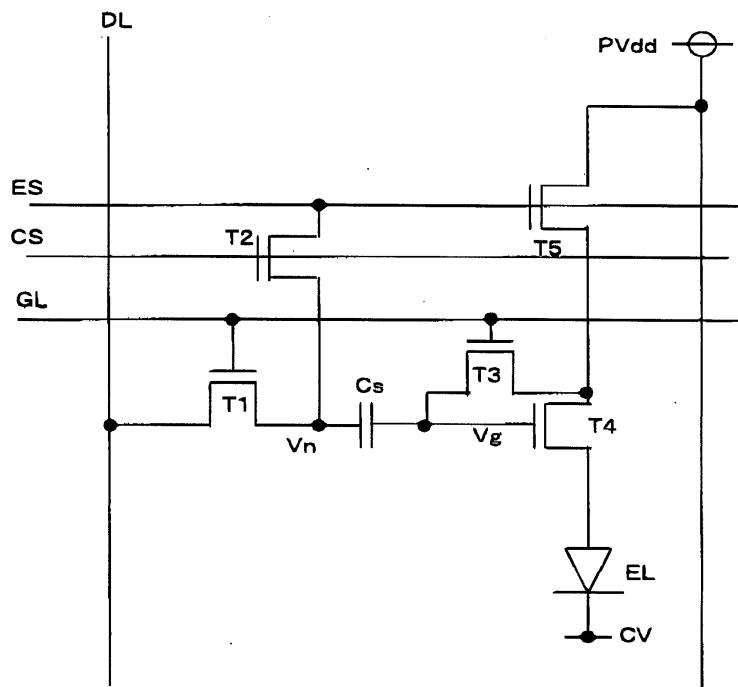

도 1은, 실시예에 따른 화소 회로의 구성을 도시하고 있다. 데이터 라인 DL은, 수직 방향으로 연장되고, 화소의 표시 회로에 대한 데이터 신호(데이터 전압 Vsig)를 화소 회로에 공급한다. 데이터 라인 DL은, 1 열의 화소에 대하여 하나 설치되어 있고, 수직 방향의 화소에 대하여, 그 화소의 데이터 전압 Vsig을 순차적으로 공급한다.

이 데이터 라인 DL에는, n 채널의 선택 트랜지스터 T1의 드레인이 접속되어 있고, 이 선택 트랜지스터 T1의 소스는, 컨덴서 Cs의 일단에 접속되어 있다. 선택 트랜지스터 T1의 게이트는, 수평 방향으로 연장되는 게이트 라인 GL에 접속되어 있다. 이 게이트 라인 GL에는, 수평 방향의 각 화소 회로의 선택 트랜지스터 T1의 게이트가 접속되어 있다.

이 게이트 라인 GL에는, p 채널의 전위 제어 트랜지스터 T2의 게이트가 접속되어 있다. 따라서, 선택 트랜지스터 T1이 온일 때에 전위 제어 트랜지스터 T2가 오프하고, 선택 트랜지스터 T1이 오프일 때에 전위 제어 트랜지스터 T2가 온으로 된다. 전위 제어 트랜지스터 T2의 소스는 전원 라인(양의 전원) PVdd에 접속되고, 드레인은 컨덴서 Cs와 선택 트랜지스터 T1의 소스에 접속되어 있다. 또한, 전원 라인 PVdd도 수직 방향으로 연장되어 있어, 수직 방향의 각 화소에 전원 전압 PVdd를 공급한다.

컨덴서 Cs의 타단은, p 채널의 구동 트랜지스터 T4의 게이트에 접속되어 있다. 구동 트랜지스터 T4의 소스는 전원 라인 PVdd에 접속되고, 드레인은 n 채널의 구동 제어 트랜지스터 T5의 드레인에 접속되어 있다. 구동 제어 트랜지스터 T5의 소스는, 유기 EL 소자 EL의 애노드에 접속되어 있고, 게이트는, 수평 방향으로 연장되는 발광 세트 라인 ES에 접속되어 있다. 또한, 유기 EL 소자 EL의 캐소드는, 저전압의 캐소드 전원(음의 전원) CV에 접속되어 있다.

또한, 구동 트랜지스터 T4의 게이트에는, n 채널의 단락 트랜지스터 T3의 드레인이 접속되어 있고, 이 단락 트랜지스터 T3의 소스는, 구동 트랜지스터 T4의 드레인에 접속되어 있고, 또한 게이트는, 게이트 라인 GL에 접속되어 있다.

이와 같이, 본 실시예에서는, 수직 방향으로 데이터 라인 DL과, 전원 라인 PVdd가 배치되고, 수평 방향으로 게이트 라인 GL과, 발광 세트 라인 ES가 배치되어 있다.

이어서, 이 화소 회로의 동작에 대하여, 설명한다.

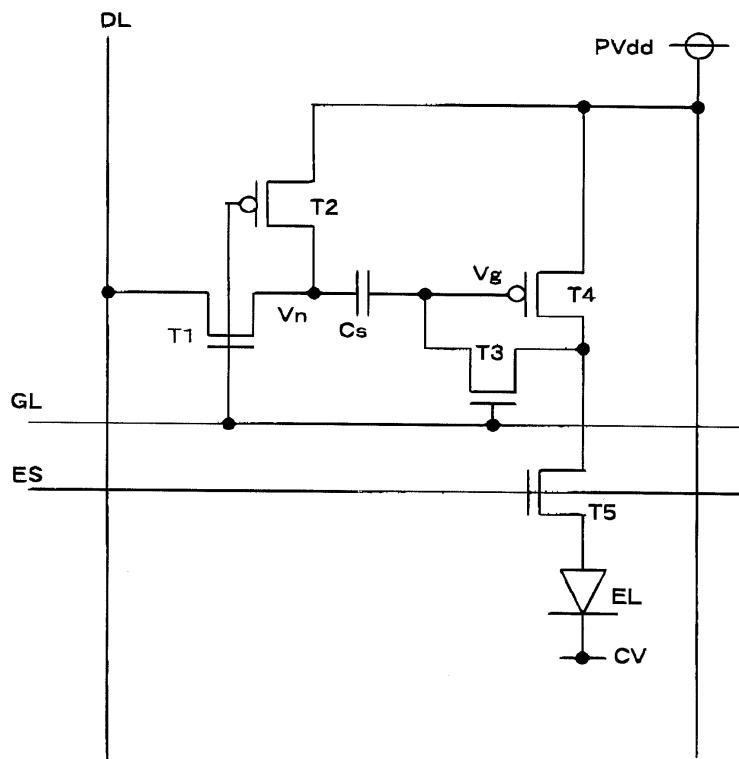

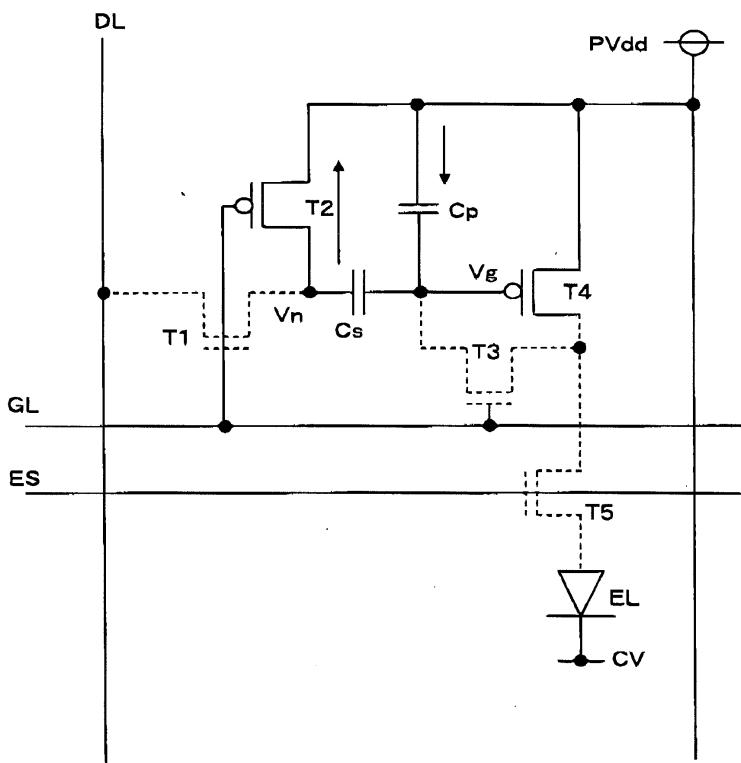

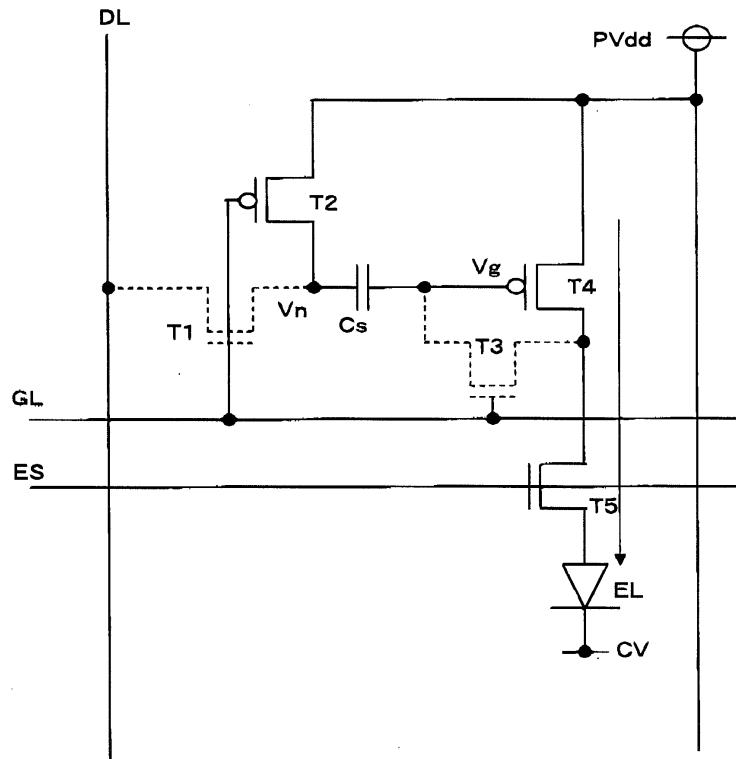

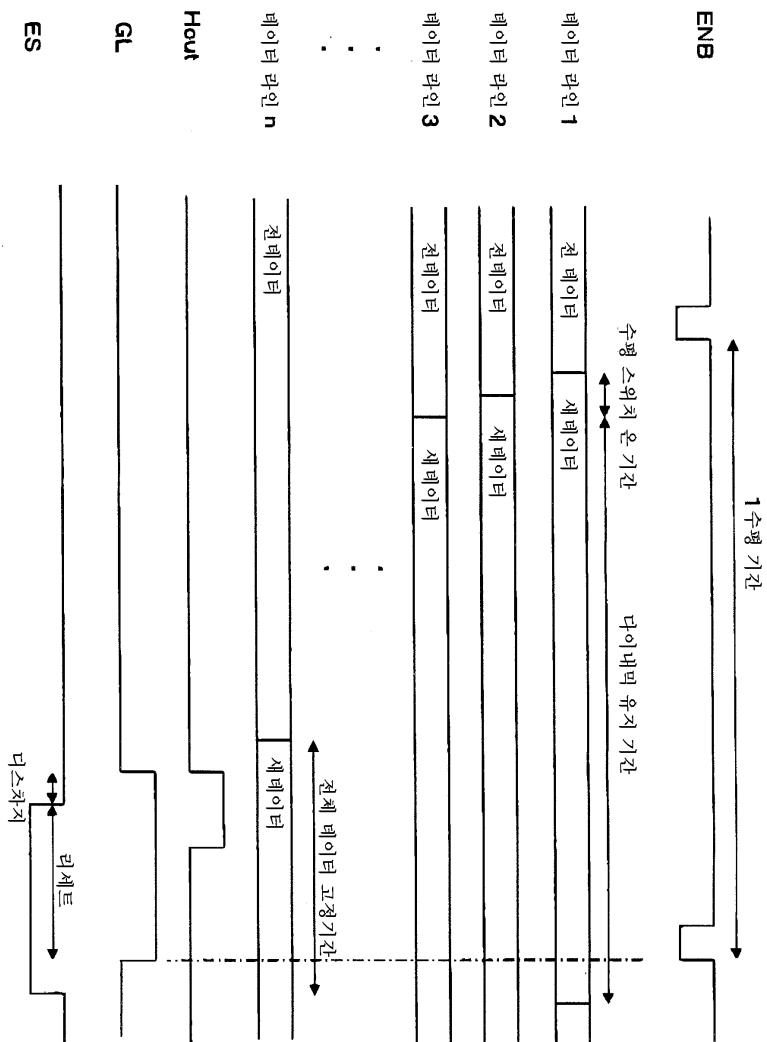

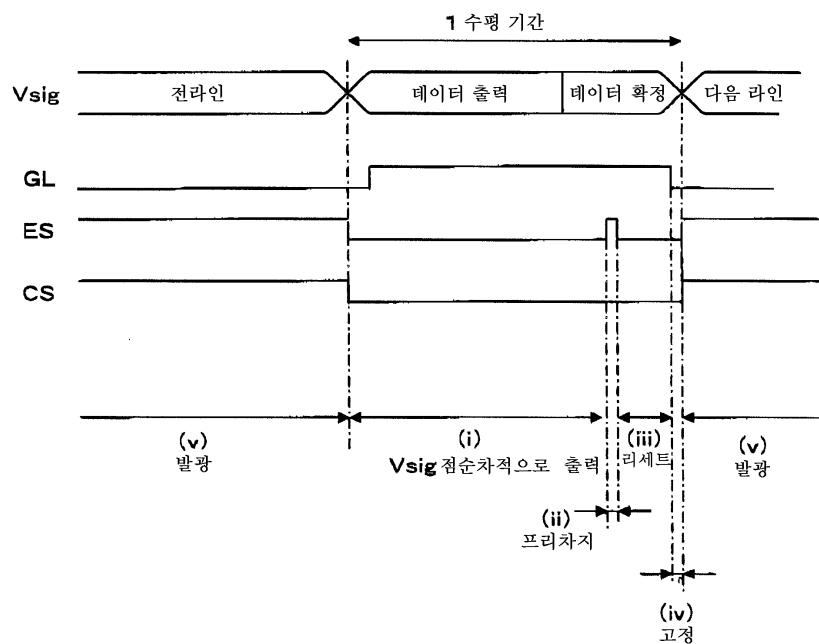

도 2에 도시한 바와 같이, 이 화소 회로는, 게이트 라인 GL, 발광 세트 라인 ES의 상태(H 레벨, L 레벨)에 따라, (i) 디스챠지(GL=H 레벨, ES=H 레벨), (ii) 리세트(GL=H 레벨, ES=L 레벨), (iii) 전위 고정(GL=L 레벨, ES=L 레벨), (iv) 발광(GL=L 레벨, ES=H 레벨)의 4개의 상태가 있으며, 이것을 반복한다. 즉, 데이터 라인 DL의 데이터를 유효하게 한 상태에서, (i) 디스챠지를 행하고, 그 후 (ii) 리세트에 의해, 컨덴서 Cs의 충전 전압을 결정하고, (iii)에서 게이트 전압 Vg을 고정하고, (v) 고정된 게이트 전압에 따른 구동 전류에 의해 유기 EL 소자 EL이 발광한다.

또한, 데이터 라인 DL에서의 데이터는, 도 2에 도시한 바와 같이, (i) 디스챠지 공정 전에 유효로 되고, (iii) 고정 공정 후에 무효로 된다. 따라서, (i) 디스챠지 공정으로부터 (iii) 고정 공정까지는 데이터 라인에 유효한 데이터가 세트되어 있다.

이하, 각각의 상태에 대하여, 설명한다. 또한, 도 3~도 6에서 오프의 트랜지스터에 대해서는, 파선으로 나타내고 있다.

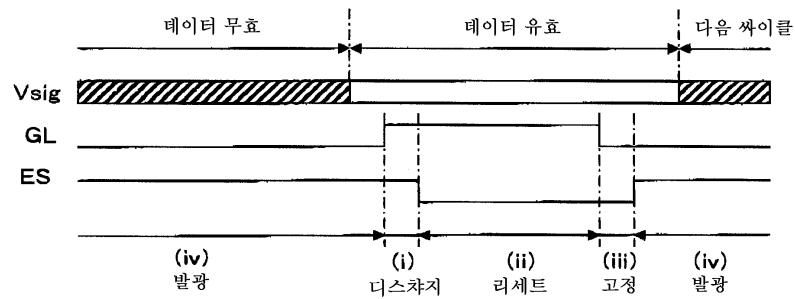

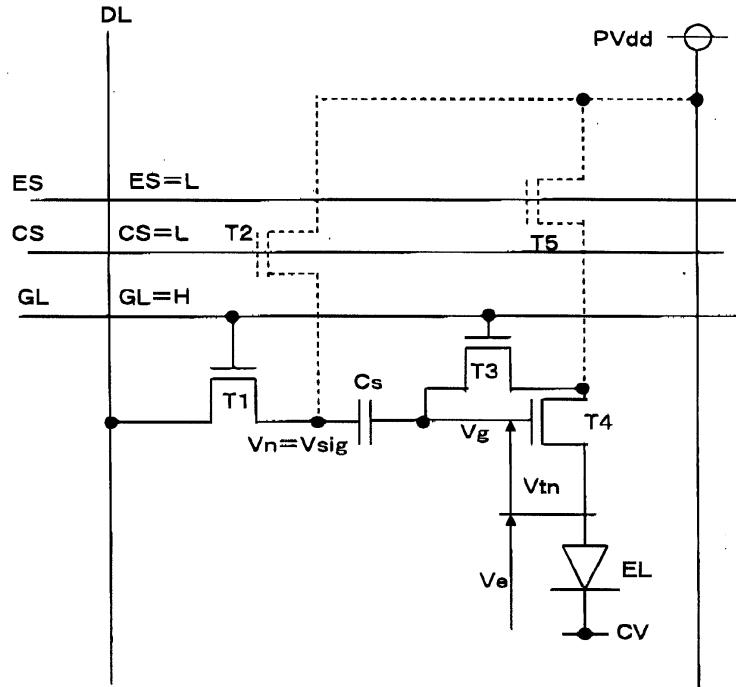

#### (i) 디스챠지(GL=H 레벨, ES=H 레벨)

우선, 데이터 라인 DL에 데이터 전압 Vsig이 공급되고 있는 상태에서, 게이트 라인 GL, 발광 세트 라인 ES의 양방을 H 레벨(고레벨)로 한다. 이에 의해, 선택 트랜지스터 T1, 구동 제어 트랜지스터 T5, 단락 트랜지스터 T3이 온되고, 전위 제어 트랜지스터 T2가 오프로 된다. 따라서, 도 3에 도시한 바와 같이 컨덴서 Cs의 선택 트랜지스터 T1측의 전압 Vn=Vsиг라고 하는 상태에서, 전원 라인 PVdd로부터의 전류가 구동 트랜지스터 T4, 구동 제어 트랜지스터 T5, 유기 EL 소자 EL를 통하여 캐소드 전원 CV에 흐르고, 이에 의해 구동 트랜지스터 T4의 게이트에 유지되어 있던 전하가 방출된다. 이에 의해, 구동 트랜지스터 T4의 게이트 전압 Vg는, 소정의 저전압으로 된다.

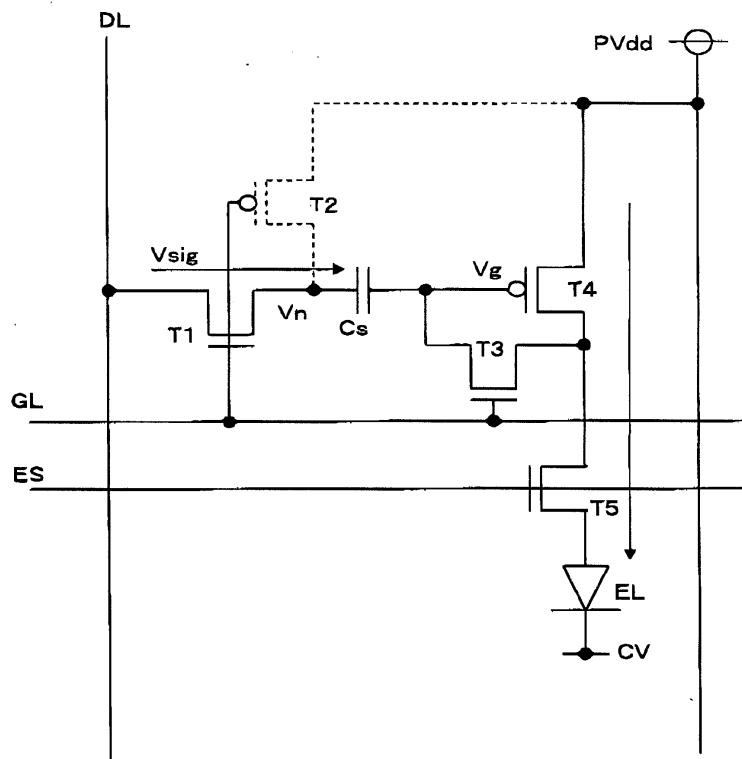

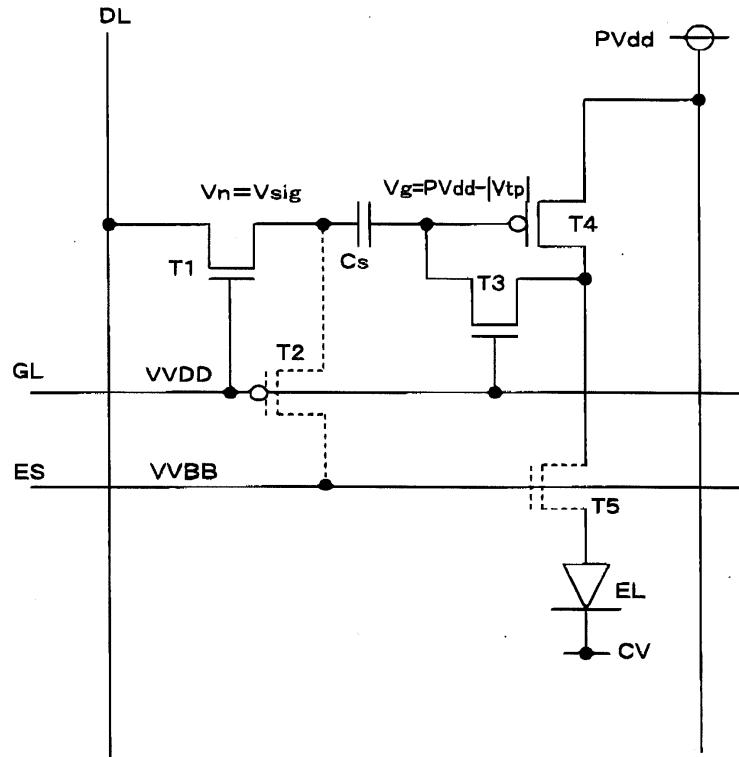

#### (ii) 리세트(GL=H 레벨, ES=L 레벨)

전술한 디스챠지의 상태로부터 발광 세트 라인 ES를 L 레벨(로우 레벨)로 변경한다. 이에 의해, 도 4에 도시한 바와 같이, 구동 제어 트랜지스터 T5가 오프로 되고, 구동 트랜지스터 T4의 게이트 전압 Vg=Vg0=PVdd- | Vtp |로 리세트된다. 여기서, 이 Vtp는, 구동 트랜지스터 T4의 임계값 전압이다. 즉, 구동 트랜지스터 T4는 소스가 전원 PVdd에 접속되어 있는 상태에서, 단락 트랜지스터 T3에 의해, 게이트 드레인 사이가 단락되어 있기 때문에, 그 게이트 전압이, 전원 PVdd보다 구동 트랜지스터 T4의 임계값 전압 | Vtp | 만큼 낮은 전압으로 세트되어 오프된다. 이 때 컨덴서 Cs의 선택 트랜지스터 T1측의 전위 Vn=Vsig이고, 컨덴서 Cs에는 | Vsig-(PVdd- | Vtp |) |의 전압이 충전된다.

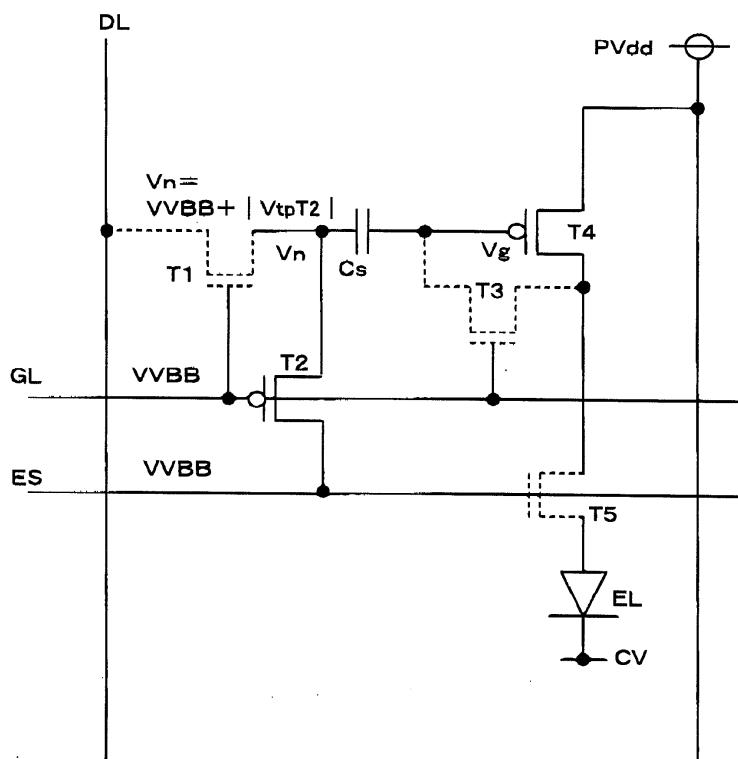

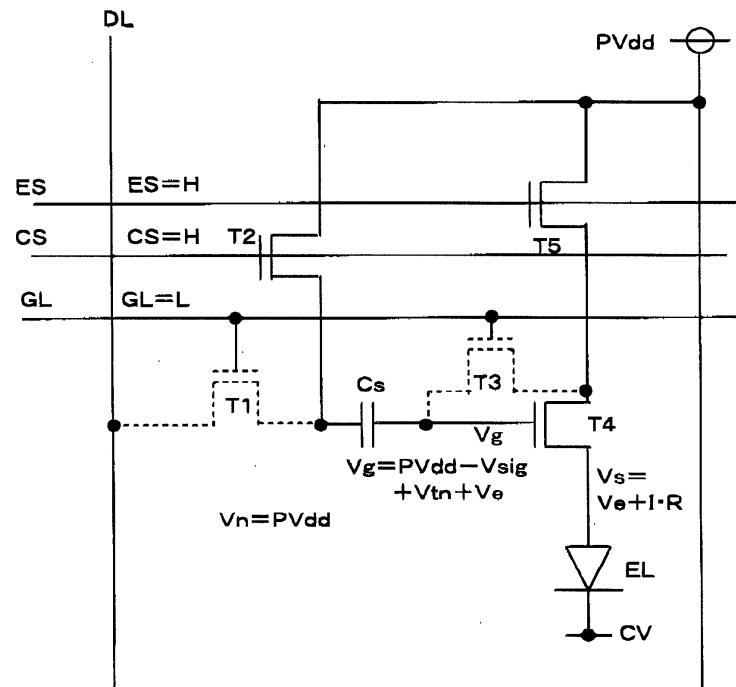

#### (iii) 전위 고정(GL=L 레벨, ES=L 레벨)

이어서, 게이트 라인 GL을 L 레벨로 하고, 선택 트랜지스터 T1, 단락 트랜지스터 T3을 오프로 하고, 전위 제어 트랜지스터 T2를 온한다. 이에 의해, 도 5에 도시한 바와 같이 구동 트랜지스터 T4의 게이트는, 드레인으로부터 분리된다. 그리고, 전위 제어 트랜지스터 T2가 온함으로써, Vn=PVdd로 된다. 따라서, 구동 트랜지스터 T4의 게이트 전위 Vg는, Vn의 변화에 따라 시프트한다. 또한, 구동 트랜지스터 T4의 게이트와 소스 사이에는, 기생 용량 Cp가 존재하기 때문에, 게이트 전위 Vg는, 이 Cp의 영향을 받는다.

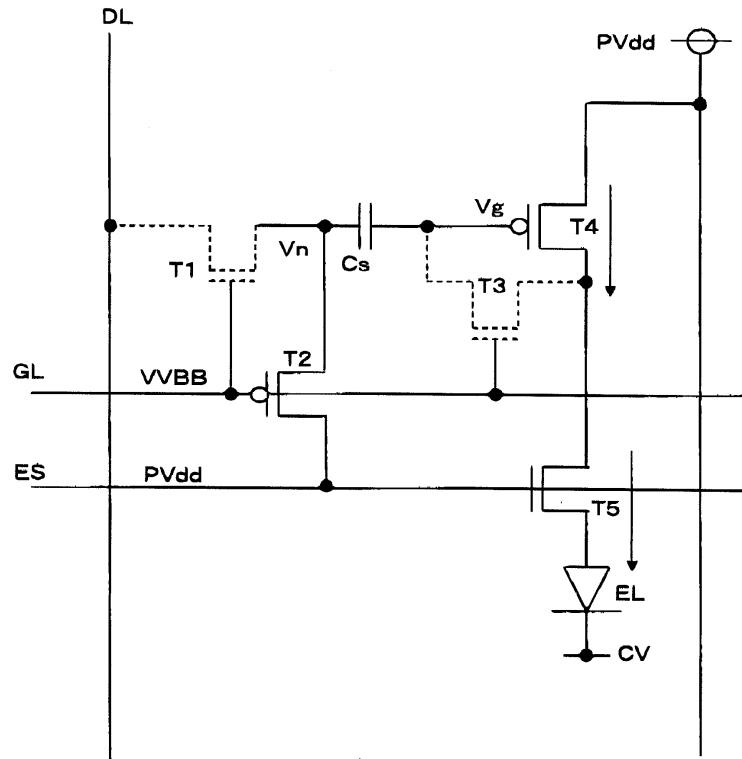

#### (iv) 발광(GL=L 레벨, ES=H 레벨)

이어서, 발광 세트 라인 ES를 H 레벨로 함으로써, 도 6에 도시한 바와 같이 구동 제어 트랜지스터 T5가 온하여, 이에 의해 구동 트랜지스터 T4로부터의 구동 전류가 유기 EL 소자 EL에 흐른다. 이 때의 구동 전류는, 구동 트랜지스터 T4의 게이트 전압에 의해 결정되는, 구동 트랜지스터 T4의 드레인 전류로 되지만, 이 드레인 전류는 구동 트랜지스터 T4의 임계값 전압 Vtp와는 관계없는 것으로 되어, 임계값 전압의 변동에 수반하는 발광량의 변동을 억제할 수 있다.

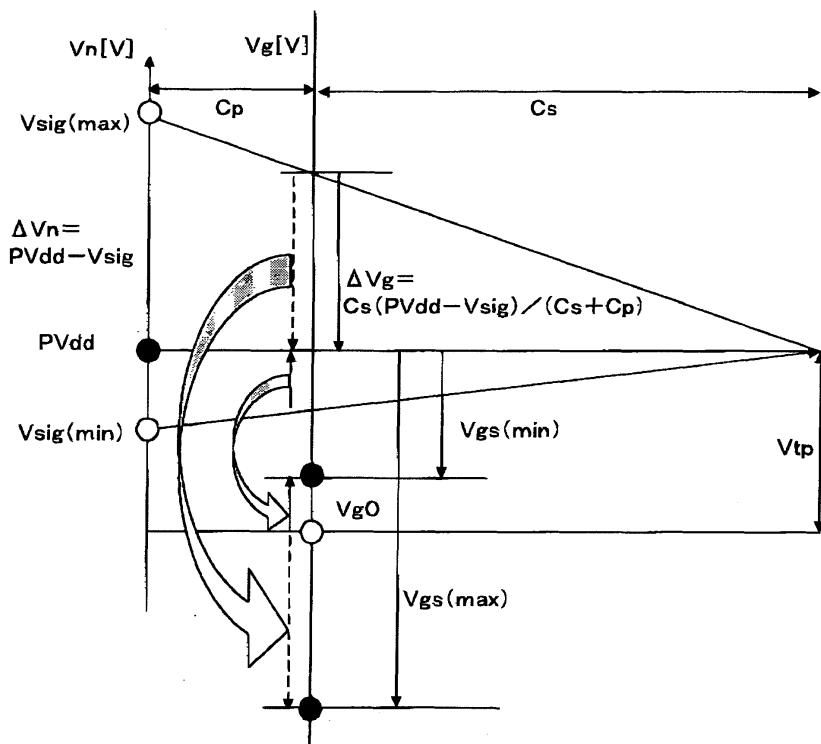

이것에 대하여 도 7에 기초하여 설명한다.

전술된 바와 같이, (ii) 리세트 후에는, 도 7에서, ○로 나타낸 바와 같이, Vn(=Vsig)은, Vsig(max)~Vsig(min) 사이의 값이고, Vg는 PVdd로부터 구동 트랜지스터 T4의 임계값 전압 Vtp만큼 줄어든 전압 Vg0로 된다. 즉, Vg=Vg0=PVdd+Vtp (Vtp<0), Vn=Vsig이다.

그리고, (iii)의 전위 고정으로 들어가면,  $V_n$ 은,  $V_{sig}$ 로부터  $PV_{dd}$ 까지 변화하므로, 그 변화량  $\Delta V_g$ 는,  $C_s$ ,  $C_p$ 의 용량을 고려하여,  $\Delta V_g = PV_{dd} + C_s(PV_{dd} - V_{sig}) / (C_s + C_p)$ 로 표현할 수 있다.

따라서,  $V_n$ ,  $V_g$ 는, 도 7에서 ●로 나타낸 바와 같이,  $V_n = PV_{dd}$ ,  $V_g = V_{tp} + \Delta V_g = PV_{dd} + V_{tp} + C_s(PV_{dd} - V_{sig}) / (C_s + C_p)$ 로 된다.

여기서,  $V_{gs} = V_g - PV_{dd}$ 이므로,  $V_{gs} = V_{tp} + C_s(PV_{dd} - V_{sig}) / (C_s + C_p)$ 로 된다.

한편, 드레인 전류  $I$ 는,  $I = (1/2)\beta(V_{gs} - V_{tp})^2$ 로 표현되고, 상기 식을 대입함으로써, 드레인 전류  $I$ 는 다음과 같이 표현된다.

$$I = (1/2)\beta\{V_{tp} + C_s(PV_{dd} - V_{sig}) / (C_s + C_p) - V_{tp}\}^2$$

$$= (1/2)\beta\{C_s(PV_{dd} - V_{sig}) / (C_s + C_p)\}^2$$

$$= (1/2)\beta\alpha(V_{sig} - PV_{dd})^2$$

여기서,  $\alpha = \{C_s / (C_s + C_p)\}^2$ ,  $\beta$ 는 구동 트랜지스터 T4 증폭율이고,  $\beta = \mu\epsilon G_w / G_l$ 이고,  $\mu$ 는 캐리어의 이동도,  $\epsilon$ 는 유전율,  $G_w$ 는 게이트 폭,  $G_l$ 은 게이트 길이이다.

이와 같이, 드레인 전류  $I$ 의 식에는,  $V_{tp}$ 는 포함되지 않고,  $V_{sig} - PV_{dd}$ 의 제곱에 비례하게 된다. 따라서, 구동 트랜지스터 T4의 임계값 전압의 변동의 영향을 배제하고 데이터 전압  $V_{sig}$ 에 따른 발광을 달성할 수 있다.

전술한 설명에서는, 1 화소에 대한 동작에 대해서만 설명하였다. 실제로는, 표시 패널은, 매트릭스 형상으로 화소가 배치되어 있고, 이들의 각각에 대하여 대응하는 휘도 신호에 따른 데이터 전압  $V_{sig}$ 을 공급하여 각 유기 EL 소자를 발광시킨다. 즉, 도 8에 도시한 바와 같이 표시 패널에는, 수평 스위치 회로 HSR와, 수직 스위치 VSR이 설치되어 있고, 이들의 출력에 의해 데이터 라인 DL, 게이트 라인 GL, 기타 발광 세트 라인 ES 등의 상태가 제어된다. 특히, 수평 방향의 각 화소에는, 하나의 게이트 라인 GL이 대응되어 있고, 이 게이트 라인 GL은 수직 스위치 VSR에 의해, 하나씩 순서대로 활성화된다. 이어서, 하나의 게이트 라인 GL이 활성화되는 1 수평 기간에, 수평 스위치 HSR에 의해 모든 데이터 라인 DL에 데이터 전압이 점차적으로 공급되고, 이들이 1 수평 라인분의 화소 회로에 데이터가 기입된다. 그리고, 각 화소 회로에서 1 수직 기간 후까지 기입된 데이터 전압에 따른 발광이 이루어진다.

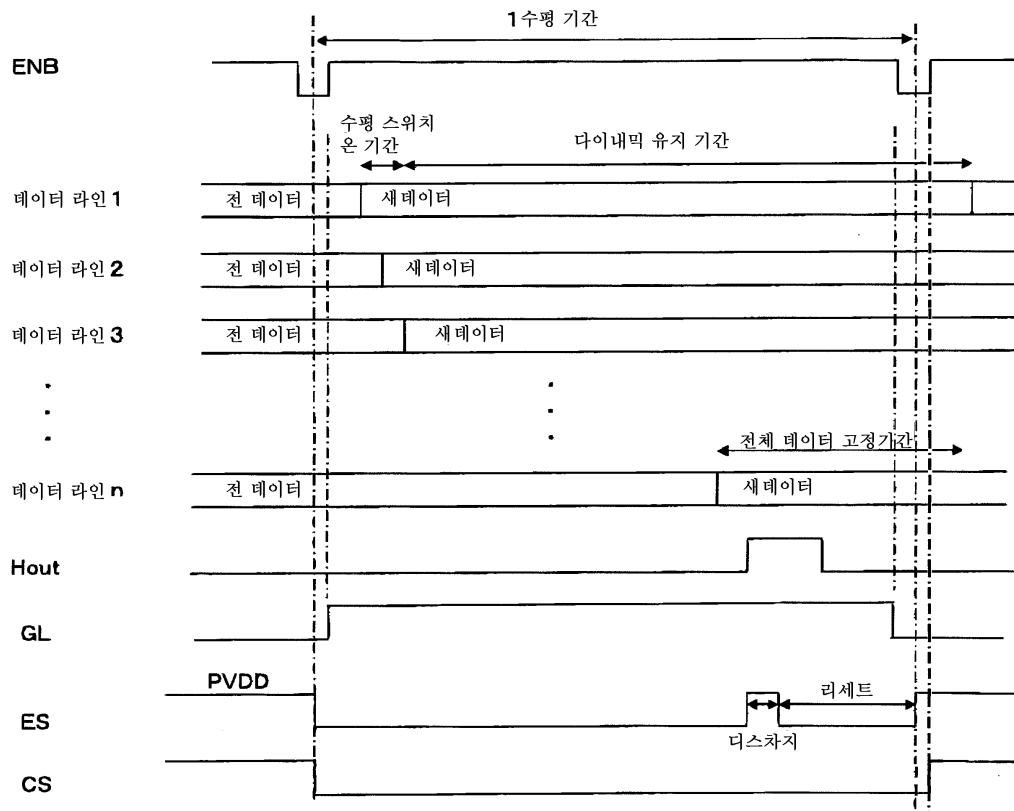

이어서, 1 수평 라인 내의 각 화소에 대한 데이터의 기입 순서에 대하여, 도 9에 기초하여 설명한다.

우선, 1 수평 기간의 개시를 나타내는 인에이블 신호 ENB의 L 레벨 후에, 모든 데이터 라인 DL에 점순차적으로 데이터 전압  $V_{sig}$ 을 기입한다. 즉, 데이터 라인 DL에는, 용량 등이 접속되어 있고, 전압 신호를 세트함으로써, 데이터 라인 DL에 그 데이터 전압  $V_{sig}$ 가 유지된다. 따라서, 각 열의 화소에 대한 데이터 전압  $V_{sig}$ 를 순차적으로 대응하는 데이터 라인 DL에 세트함으로써, 모든 데이터 라인 DL에 데이터 전압  $V_{sig}$ 을 세트한다.

그리고, 이 데이터의 세트가 종료된 단계에서, Hout를 H 레벨로 하고, 게이트 라인 GL을 H 레벨로 하여 활성화하고, 전술한 하나의 수평 방향의 각 화소에 대하여 동작을 행하고, 각 화소에서의 데이터를 기입하여, 발광이 행해진다.

이와 같이 하여, 통상적인 비디오 신호(데이터 전압  $V_{sig}$ )를 순차적으로 데이터 라인 DL에 기입하고, 이것을 화소 회로에 세트하여, 발광시킬 수 있다.

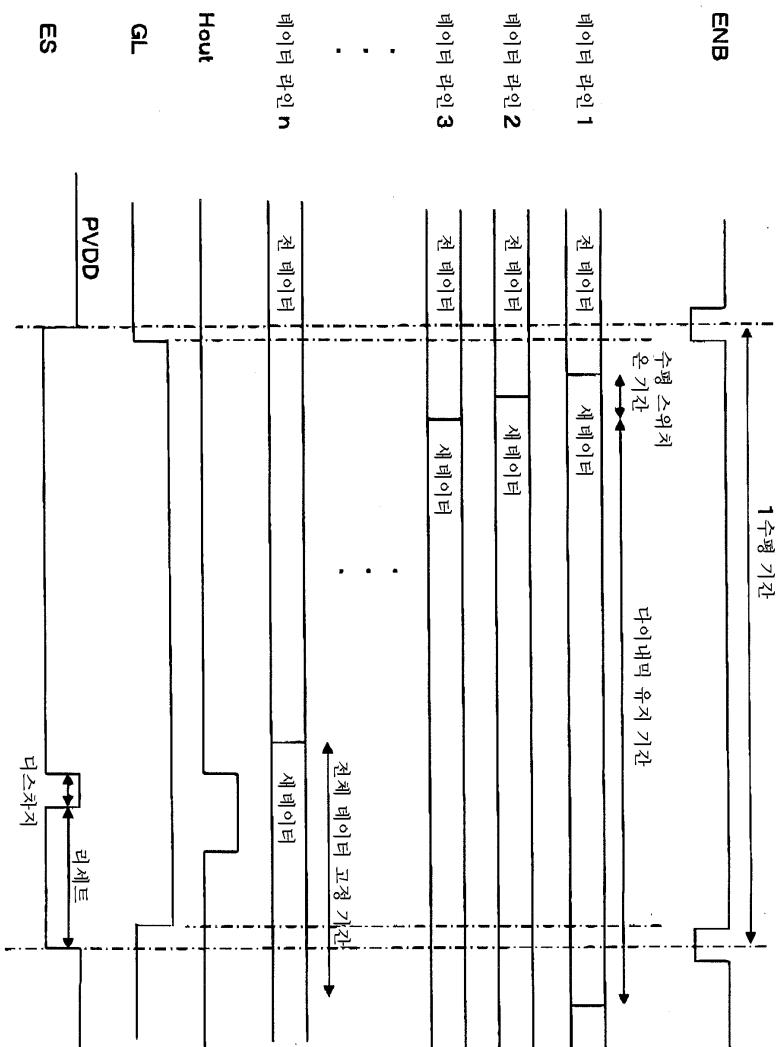

이어서, 다른 방식에 대하여, 도 10에 기초하여 설명한다. 이 예에서는, 인에이블 라인 ENB가 L 레벨인 기간에, 발광 세트 라인 ES를 H 레벨로 하고, 인에이블 라인 ENB가 H 레벨로 상승할 때에 게이트 라인 GL을 H 레벨(활성화)로 한다. 이 상태에서, 데이터 전압  $V_{sig}$ 를 순차적으로 데이터 라인 DL에 세트한다. 그리고, 모든 데이터 라인 DL에 데이터 전압  $V_{sig}$ 을 세트한 경우에는, 발광 세트 라인 ES를 H 레벨로 하여, 전술한 디스챠지를 행하고, 그 후 발광 세트 라인 ES를 L 레벨로 복귀시킨다. 게이트 라인 GL은, 인에이블 라인 ENB의 하강에 동기하여 L 레벨로 복귀되고, 인에이블 라인 ENB가 L 레벨일 때에 인에이블 라인 ENB를 H 레벨로 복귀시킨다. 이에 의해, 전술한 예와 마찬가지의 동작이 행해진다.

이어서, 각종 변형예에 대하여, 설명한다.

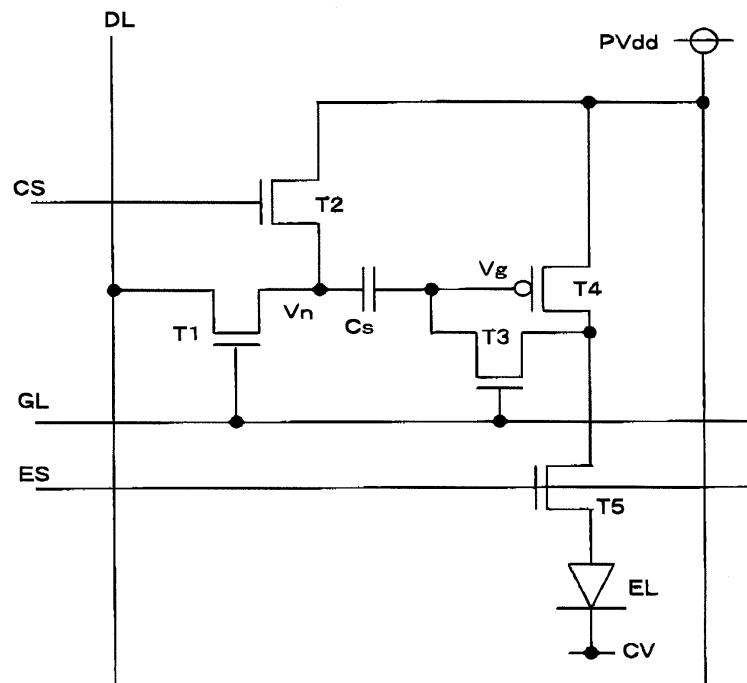

#### (A) 변형예1

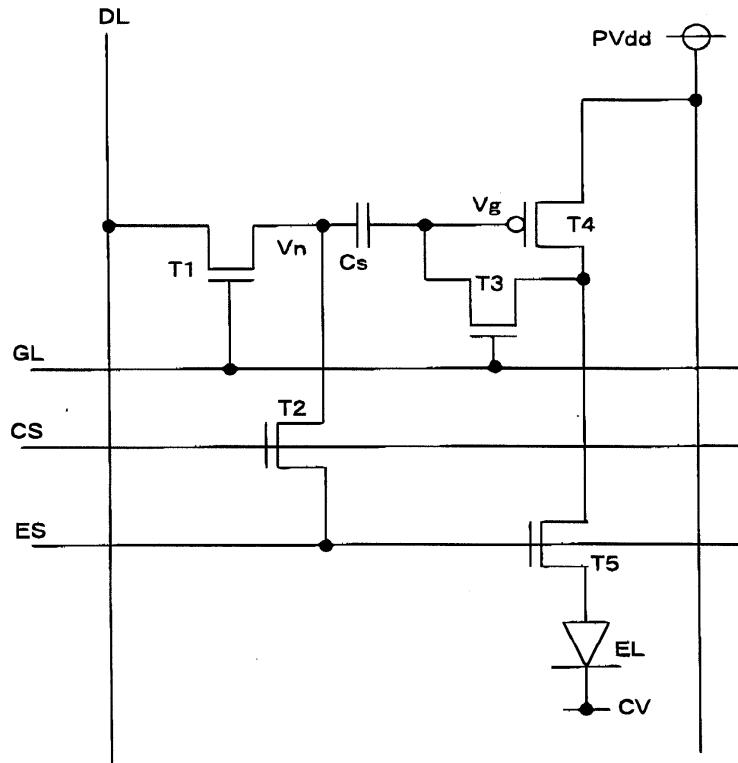

도 11은, 변형예1의 구성을 도시하고 있다. 이 변형예1에서는, 선택 트랜지스터 T1, 단락 트랜지스터 T3을 p 채널로 하고, 전위 제어 트랜지스터 T2를 n 채널로 하고 있다. 이러한 구성에서는, 게이트 라인 GL의 H 레벨, L 레벨을 전술한 실시 예와 반대로 함으로써, 실시예와 마찬가지의 동작을 가능하게 하고 있다.

이 변형예1에서의 게이트 라인 GL, 발광 세트 라인 ES의 제어에 따른 선택 트랜지스터 T1, 구동 제어 트랜지스터 T5의 온 오프는, 도 12에 도시한 바와 같으며, 이것은 전술한 도 2에 도시한 것과 동일하다.

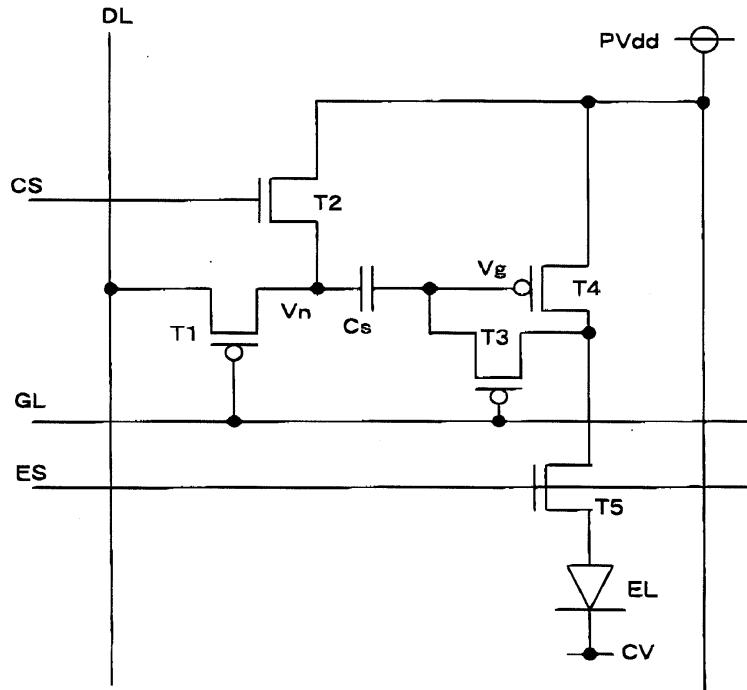

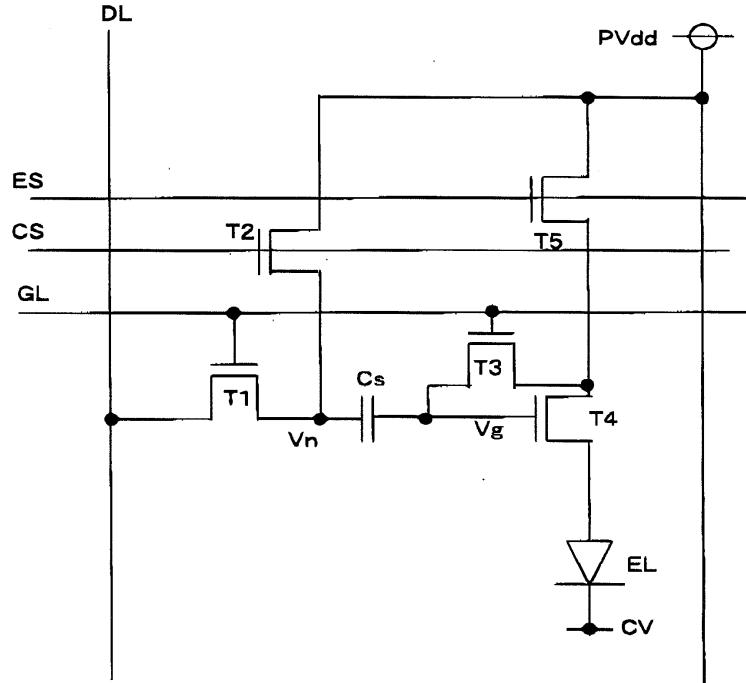

#### (B) 변형예2

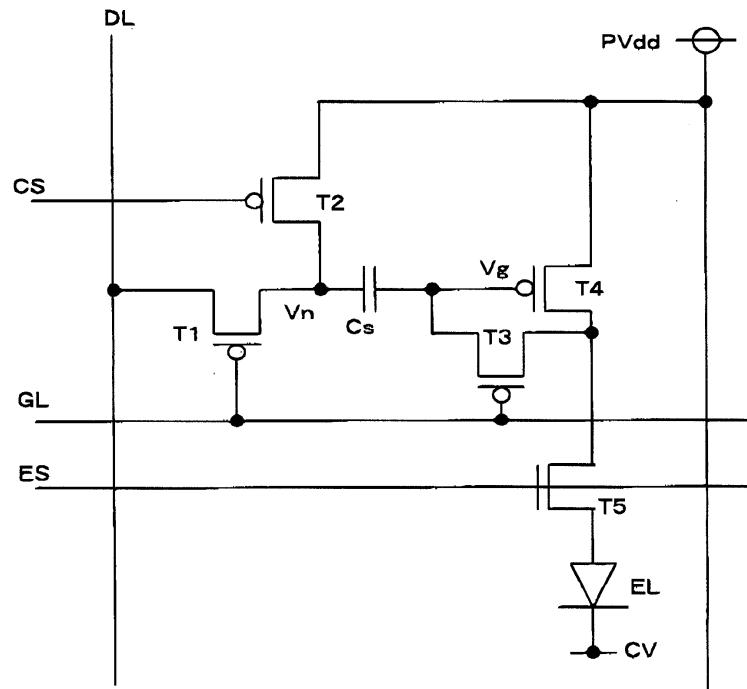

도 13은, 변형예2의 구성을 도시하고 있다. 이 변형예2에서는, 실시예의 화소 회로와 비교하여, 전위 제어 트랜지스터 T2의 제어용으로 전용의 제어 라인 CS를 설치하고 있다. 따라서, 전위 제어 트랜지스터 T2를 제어 라인 CS에 의해 독립하여 제어할 수 있다. 따라서, 도 14에 도시한 바와 같이, 제어 라인 CS에 의해, 선택 트랜지스터 T1이 온하기 전에, 전위 제어 트랜지스터 T2를 오프하고, 선택 트랜지스터 T1이 오프한 후에, 구동 제어 트랜지스터 T5와 함께 전위 제어 트랜지스터 T2를 온할 수 있다.

이러한 구성에 따르면, 수평 방향의 라인이 증가하지만, 전위 제어 트랜지스터 T2를 가장 적절한 타이밍에서 온 오프할 수 있다. 즉, 단락 트랜지스터 T3과, 전위 제어 트랜지스터 T2의 동시 온의 기간을 확실하게 없앨 수 있고, 정확한 게이트 전위 고정을 할 수 있어, 보정 정밀도를 상승시킬 수 있다.

도 15는, 도 13에 대하여 전위 제어 트랜지스터 T2를 n 채널로 한 예이고, 도 16은 선택 트랜지스터 T1, 단락 트랜지스터 T3을 p 채널, 전위 제어 트랜지스터 T2를 n 채널로 한 예이고, 도 17은, 선택 트랜지스터 T1, 단락 트랜지스터 T3, 전위 제어 트랜지스터 T2를 모두 p 채널로 한 예를 도시하고 있다.

#### (C) 변형예3

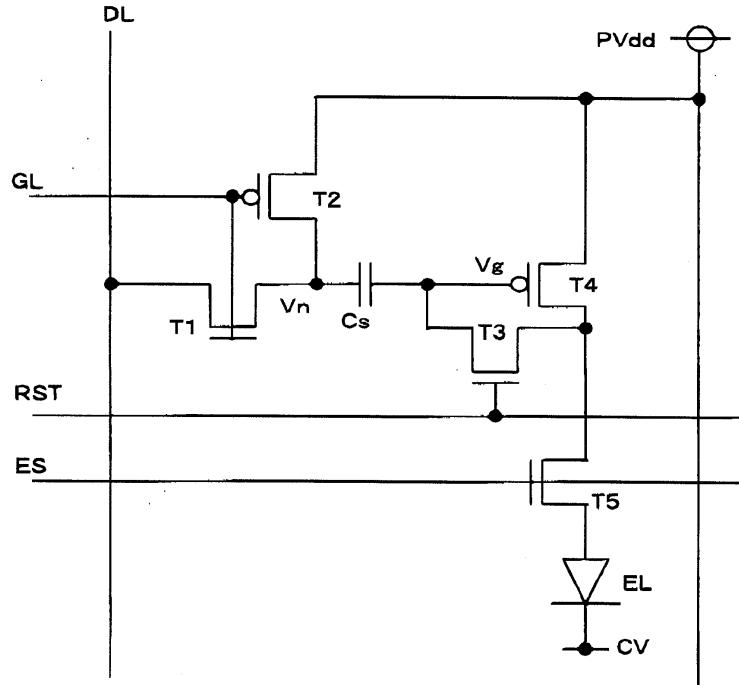

도 18은 다른 변형예이고, 선택 트랜지스터 T1과, 전위 제어 트랜지스터 T2를 게이트 라인 GL에 접속하고, 전용 리세트 라인 RST를 설치하고, 이 리세트 라인 RST에 단락 트랜지스터 T3에 접속하고 있다. 이 구성에서는, 도 19에 도시한 바와 같이, 리세트 라인 RST에 의해, 단락 트랜지스터 T3을, 선택 트랜지스터 T1의 오프 및 구동 제어 트랜지스터 T5의 온에 앞서, 오프할 수 있다.

따라서, 변형예2와 마찬가지로, 전위 제어 T2와, 단락 트랜지스터 T3의 동시 온 기간을 없앨 수 있다. 이러한 구성으로 함으로써, 게이트 라인 GL의 근처에 배치하는 트랜지스터는, 선택 트랜지스터 T1과, 전위 제어 트랜지스터 T2의 2개면 되므로, 화소 회로에서의 트랜지스터의 레이아웃이 용이하게 된다. 그러나, 이 경우에는 선택 트랜지스터 T1과, 단락 트랜지스터 T3의 오프 타이밍이 어긋나는 것으로 되어, 이 때에 Vg에 영향을 주는 노이즈가 발생할 가능성도 있다.

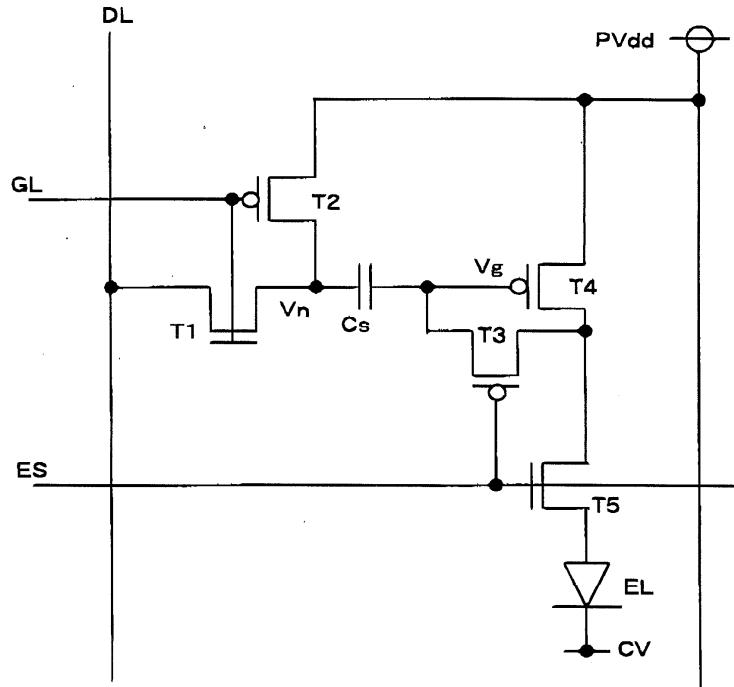

#### (D) 변형예4

도 20은, 또 다른 변형예이다. 이 예에서는, 선택 트랜지스터 T1, 전위 제어 트랜지스터 T2를 게이트 라인 GL에 접속하고, 단락 트랜지스터 T3, 구동 제어 트랜지스터 T5를 발광 세트 라인 ES에 접속하고 있다. 이 예에서는, 도 21에 도시한 바와 같이, 발광 상태로부터, 게이트 라인 GL이 H 레벨로 되고, 전위 제어 트랜지스터 T2가 오프로 되고, 선택 트랜지스터 T1이 온이 되어, 컨덴서 Cs의 일단에 데이터 전압 Vsig가 공급된다. 이 때 단락 트랜지스터 T3은 오프로 되고, 구동 제어 트랜지스터 T5는 온으로 되어 있다. 이어서, 발광 세트 라인 ES가 L 레벨로 되고, 단락 트랜지스터 T3이 온으로 되고, 구동 제어 트랜지스터 T5가 오프로 된다. 직전까지, 유기 EL 소자 EL에 전류가 흐르고 있고, 구동 트랜지스터 T4의 드레인은 비교적 낮은 전압으로 되어 있고, 단락 트랜지스터 T3이 온함으로써, Vg에 PVdd+ Vtp의 합으로 세트하는, 리세트가 행해진다. 그 후, 발광 세트 라인 ES가 H 레벨로 되고, 단락 트랜지스터 T3이 오프로 되고, 구동 제어 트랜지스터 T5가 온으로 된 단계에서, 게이트 라인 GL이 H 레벨로 되어, 전위의 고정 및 발광이 행하여진다.

이 변형예4에 따르면, 게이트 라인 GL의 근처에 선택 트랜지스터 T1, 전위 제어 트랜지스터 T2를 배치하고, 발광 세트 라인 ES의 근처에 단락 트랜지스터 T3, 구동 제어 트랜지스터 T5를 배치함으로써, 배선의 주회가 매우 용이하게 된다. 따라

서, 화소 회로의 레이아웃이 용이하게 된다. 그러나, 선택 트랜지스터 T1과, 단락 트랜지스터 T3의 타이밍이 어긋나기 때문에, 노이즈가 나타나기 쉽다고 하는 단점도 있다. 또한, 다른 구성예와 같은 디스챠지 공정을 마련할 수 없기 때문에, 구동 트랜지스터 T4의 게이트에 대한 전하의 방출을 충분히 행할 수 없는 경우도 발생하기 쉽다.

#### (E) 변형 예5

도 22는, 또 다른 변형예이다. 이 예에서는, 전위 제어 트랜지스터 T2를 전원 PVdd가 아니라, 발광 세트 라인 ES에 접속하고 있다. 즉, 전술한 실시예에서는, 전위 제어 트랜지스터 T2에 의해, 용량 Cs의 선택 트랜지스터 T1 측을 전원 PVdd와 접속했지만, 이 예에서는 용량 Cs의 선택 트랜지스터 T1측을 발광 세트 라인 ES에 접속한다. 이 발광 세트 라인 ES는, L 레벨 시에 VVBB, H 레벨 시에 PVdd에 세트된다. 따라서, 이 회로에서도, 전술한 회로와 마찬가지의 동작이 얻어진다. 또한, 전술한 바와 같은 동작을 달성하기 위해, 전위 제어 트랜지스터 T2가 용량 Cs의 선택 트랜지스터 T1측을 접속하는 곳은, 반드시 전원 PVdd가 아니라도 된다. 즉, 구동 트랜지스터 T4에 대하여, 적합한 시프트량이 얻어지면, 다른 전압의 전원이어도 된다.

이 변형예5에서의 각 상태에 대하여, 이하에 설명한다.

##### (i) 디스챠지(GL=H, ES=H)

우선, 데이터 라인 DL에 데이터 전압 Vsig이 공급되고 있는 상태에서, 게이트 라인 GL, 발광 세트 라인 ES의 양방을 H 레벨(하이 레벨)로 한다. 이에 의해, 선택 트랜지스터 T1, 구동 제어 트랜지스터 T5, 단락 트랜지스터 T3이 온으로 되고, 전위 제어 트랜지스터 T2가 오프로 된다. 따라서, 도 23에 도시한 바와 같이 컨덴서 Cs의 선택 트랜지스터 T1측의 전압  $V_n = V_{sig}$ 라고 하는 상태에서, 전원 라인 PVdd로부터의 전류가 구동 트랜지스터 T4, 구동 제어 트랜지스터 T5, 유기 EL 소자 EL를 통하여 캐소드 전원 CV에 흐르고, 이에 의해 구동 트랜지스터 T4의 게이트에 유지되어 있던 전하가 방출된다. 이에 의해, 구동 트랜지스터 T4의 게이트 전압 Vg는, 소정의 저전압으로 된다.

##### (ii) 리세트(GL=H, ES=L)

전술한 디스챠지의 상태로부터 발광 세트 라인 ES를 L 레벨(로우 레벨)로 변경한다. 이에 의해, 도 24에 도시한 바와 같이, 구동 제어 트랜지스터 T5가 오프로 되고, 구동 트랜지스터 T4의 게이트 전압  $V_g = V_{g0} = PVdd - |V_{tp}|$ 로 리세트된다. 여기서, 이  $V_{tp}$ 는, 구동 트랜지스터 T4의 임계값 전압이다. 즉, 구동 트랜지스터 T4는 소스가 전원 PVdd에 접속되어 있는 상태에서, 단락 트랜지스터 T3에 의해, 게이트 드레인 사이가 단락되어 있기 때문에, 그 게이트 전압이, 전원 PVdd보다 구동 트랜지스터 T4의 임계값 전압  $|V_{tp}|$  만큼 낮은 전압으로 세트되어 오프된다. 이 때 컨덴서 Cs의 선택 트랜지스터 T1 측의 전위  $V_n = V_{sig}$ 이고, 컨덴서 Cs에는  $|V_{sig} - (PVdd - |V_{tp}|)|$ 의 전압이 충전된다.

##### (iii) 전위 고정(GL=L, ES=L)

이어서, 게이트 라인 GL을 L 레벨로 하고, 선택 트랜지스터 T1, 단락 트랜지스터 T3을 오프로 하고, 전위 제어 트랜지스터 T2를 온한다. 이 때, 발광 세트 라인 ES의 전압은, L 레벨이고, 게이트 라인 GL의 L 레벨의 전압 VVBB와 동일한 전압으로 설정되어 있다. 따라서,  $V_{sig} > V_n > VVBB$ 이고, 선택 트랜지스터 T1이 오프로 되지 않으면, 전위 제어 트랜지스터 T2는 온하지 않는다. 이와 같이, 선택 트랜지스터 T1이 오프한 후에, 전위 제어 트랜지스터 T2가 온하기 때문에, 컨덴서 Cs에 충전된 전압은 유지되고, 데이터 전압이 파괴되지는 않는다.

그리고, 선택 트랜지스터 T1이 오프하고, 전위 제어 트랜지스터 T2가 온함으로써 도 25에 도시한 바와 같이 구동 트랜지스터 T4의 게이트는, 드레인으로부터 분리되고, 한쪽 전위 제어 트랜지스터 T2가 온함으로써,  $V_n$ 은, 발광 세트 라인 ES=VVBB+  $|V_{tp}T2|$ 로 된다.

##### (iv) 발광(GL=L, ES=H)

이어서, 발광 세트 라인 ES를 H로 함으로써, 도 26에 도시한 바와 같이 구동 제어 트랜지스터 T5가 온한다. 또한, 발광 세트 라인 ES의 전위가 PVdd에 세트됨으로써, 구동 트랜지스터 T4의 게이트 전위가  $PVdd - VVBB+ |V_{tp}T2|$  만큼, 시프트된다. 또한, 이 때의 전압 시프트량은 구동 트랜지스터 T4의 게이트 용량 Cp의 영향을 받는다.

이와 같이, 전압이 시프트되고, 구동 제어 트랜지스터 T5가 온함으로써 구동 트랜지스터 T4로부터의 구동 전류가 유기 EL 소자 EL에 흐른다. 이 때의 구동 전류는, 구동 트랜지스터 T4의 게이트 전압에 의해 결정되는, 구동 트랜지스터 T4의 드레인 전류로 되지만, 이 드레인 전류는 구동 트랜지스터 T4의 임계값 전압  $V_{tp}$ 와는 관계없는 것으로 되어, 임계값 전압의 변동에 수반하는 발광량의 변동을 억제할 수 있다.

또한, 전위 제어 트랜지스터 T2의 드레인은, 발광 세트 라인 ES에 접속되어 있다. 이 발광 세트 라인 ES는, H 레벨 시에 전원 전압 PVdd에 세트되지만, 이 발광 세트 라인 ES는, 유기 EL 소자 EL에 전류를 공급하는 전원 공급 라인 PVdd와는 독립하여 전원 전압 PVdd의 공급을 받는다. 따라서, 각 화소에서의 유기 EL 소자 EL의 구동 전류에 의해, 발광 세트 라인 ES의 전압이 변동하는 경우는 거의 없다. 따라서, 전위 제어 트랜지스터 T2를 통하여 컨덴서 CS의 일단에 공급되는 시프트용의 전압이 변동되어 표시가 흐트러지는 것을 방지할 수 있다.

예를 들면, 전압 시프트량  $\Delta V_g$ 는 후술한 바와 같이,  $\Delta V_g = CS(V_{sig} - PVdd) / (CS + Cp)$ 로 표현되고, PVdd를 포함하고 있다. 따라서, PVdd가 변동하면,  $\Delta V_g$ 는 변화하지만, 본 실시예에서는 이 변화가 억제된다. 특히, 화소 수가 증가한 경우에는, 이 PVdd의 변화가, 크로스토크나 휘도 구배 발생의 원인으로 되지만, 본 실시예에 따르면, 이들의 표시에의 영향을 억제할 수 있다.

#### (F) 변형 예6

도 27은, 변형 예6의 구성을 도시하고 있다. 이 예는 기본적으로 변형 예5와 마찬가지이지만, 선택 트랜지스터 T1, 단락 트랜지스터 T3을 p 채널로 하고, 전위 제어 트랜지스터 T2를 n 채널로 하고 있다. 이러한 구성에서는, 게이트 라인 GL의 H, L을 전술한 변형 예5와 반대로 함으로써, 실시예와 마찬가지의 동작을 가능하게 하고 있다.

(G) 도 28은, 변형 예7의 구성을 도시하고 있다. 이 변형 예7에서는, 전위 제어 트랜지스터 T2의 게이트에 용량 세트 라인 CS가 접속되어 있다. 그리고, 이 예에서는 전위 제어 트랜지스터 T2를 n 채널 트랜지스터로 하고 있다. 이와 같이, 전위 제어 트랜지스터 T2의 온 오프용으로 전용의 라인인 용량 세트 라인 CS를 갖고 있다. 그리고, 이 용량 세트 라인 CS를, 도 29에 도시한 바와 같이 H 레벨=VVDD, L 레벨=VVBB로 한다. 전압  $V_n$ 의 레벨이 일단 하강하는 것을 방지할 수 있다. 즉, 도 22 등의 실시예에서는, 게이트 라인 GL과 용량 세트 라인 CS가 공통이기 때문에 발광 라인 ES가 L 레벨의 타이밍에서 게이트 라인 GL을 폐쇄해야하며, 전압  $V_n$ 은  $V_{sig} \rightarrow VVBB+ | V_{tp}T2 | \rightarrow PVDD$ 와 같이 변화한다.

변형 예7에서는, 게이트 라인 GL과 용량 세트 라인 CS와 발광 라인 ES의 타이밍을 따로따로 설정할 수 있으므로, 도 29와 같이 발광 라인 ES가 H 레벨로 된 후에 용량 세트 라인 CS를 온으로 하면, 전압  $V_n$ 은 일단 하강하지 않고 PVDD로 직접 변화하고, 보다 안정된 동작이 가능하다.

또한, 상기 실시예에서, 각종 전압은 다음과 같이 설정하는 것이 적합하다. 전원 라인 PVdd는 PVdd, 발광 세트 라인 ES는 H 레벨=PVdd, L 레벨=VVBB, 게이트 라인 GL은 H 레벨=VVDD, L 레벨=VVBB, 용량 세트 라인 CS는 H 레벨=VVDD, L 레벨=VVBB, 캐소드 전원 CV=CV로 하고, PVdd=8V, VVDD=10V, VVBB=-2V, CV=-2V 정도로 설정하면 된다.

#### (H) 변형 예8

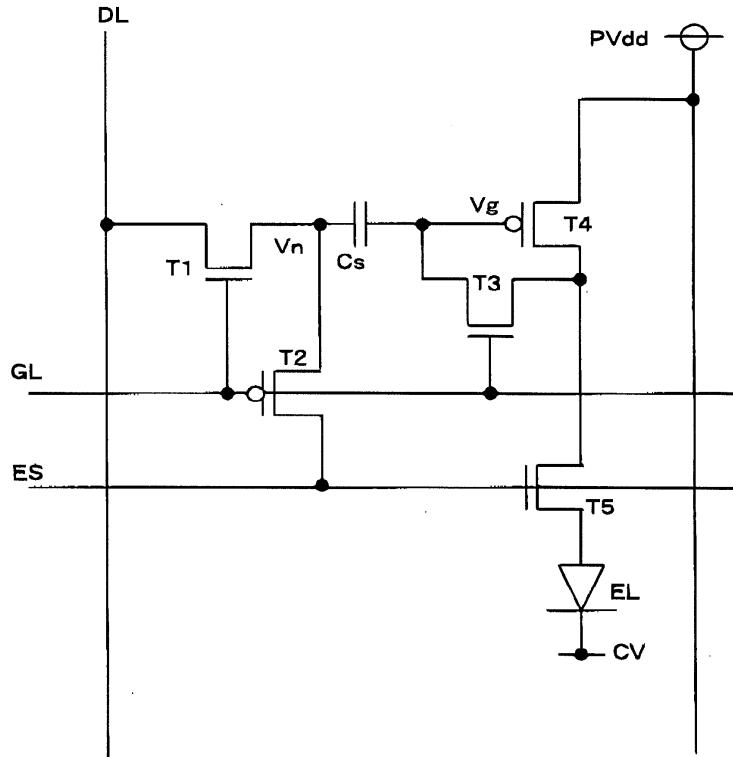

이 변형 예8에서는, 도 30에 도시한 바와 같이 구동 트랜지스터 T4로서, n 채널 트랜지스터를 채용하고 있다. 그리고, 이 구동 트랜지스터 T4의 소스는 유기 EL 소자 EL의 애노드에 접속되고, 드레인은 n 채널의 구동 제어 트랜지스터 T5의 소스에 접속되고, 이 구동 제어 트랜지스터 T5의 드레인이 전원 PVdd에 접속되어 있다.

또한, 게이트 라인 GL과 마찬가지로 수평 방향으로 연장되는 용량 세트 라인 CS가 설치되어 있고, 이 용량 세트 라인 CS에, n 채널의 전위 제어 트랜지스터 T2의 게이트가 접속되어 있다.

또한, 그 밖의 구성은, 기본적으로 도 1의 회로와 마찬가지이다.

이어서, 이 화소 회로의 동작에 대하여, 설명한다.

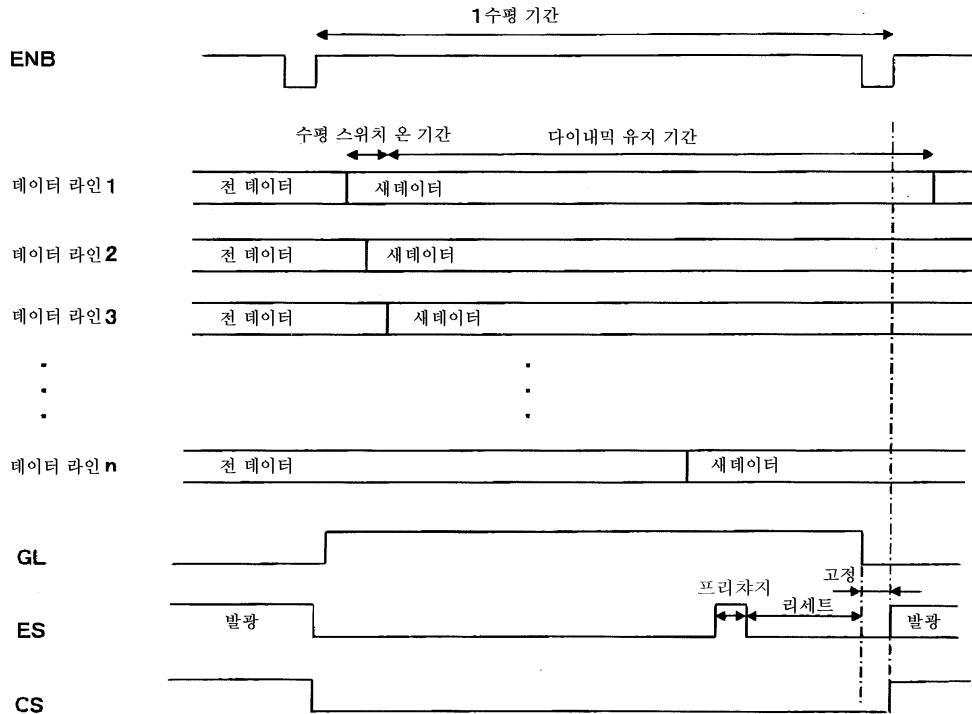

도 31에 도시한 바와 같이 이 화소 회로(데이터 라인 DL을 포함)는, 1 수평 기간에서, 게이트 라인 GL, 발광 세트 라인 ES, 용량 세트 라인 CS의 상태(H, L)에 따라, (i) 데이터 세트(GL=H, ES=L, CS=L), (ii) 프리챠지(GL=H, ES=H, CS=L), (iii) 리세트(GL=H, ES=L, CS=L), (iv) 전위 고정(GL=L, ES=L, CS=L), (v) 발광(GL=L, ES=H, CS=H)의 5개의 상태가 있으며, 이것을 반복한다.

또한, 데이터 라인 DL에서의 데이터는, 도 31에 도시한 바와 같이, 기입 대상의 라인이 선택된 단계에서 그 수평 라인의 각 열의 데이터 라인 DL에 순차적으로 데이터가 세트된다. 즉, 데이터 라인 DL에 대해서는, 데이터가 화소마다 점순차적으로 출력된다. 그리고, 모든 데이터 라인 DL에 데이터가 세트된 후, 각 화소 회로에 그 데이터(데이터 전압)가 취득된다.

이하, 기입의 동작에 대하여, 설명한다.

(i) 데이터 세트(GL=H, ES=L, CS=L)

우선, 발광 세트 라인 ES=L 레벨로 하고, 전원 라인 PVdd로부터의 전류를 차단함과 함께, 용량 세트 라인 CS=L 레벨로 하고, 선택 트랜지스터 T1과 용량 CS의 접속점의 전압을 내린다. 그리고, 이 상태에서 게이트 라인 GL을 H 레벨로 하여, 데이터 라인 DL에 대응하는 각 화소의 데이터 전압을 순차적으로 세트한다. 따라서, 데이터 라인 DL에 데이터가 세트된 전압이 용량 CS에 인가된다. 또한, 데이터 라인 DL에는, 데이터 전압이 점차적으로 세트되지만, 각 데이터 라인 DL은 용량이 접속되어 있어, 일단 인가된 데이터 전압이 유지된다.

(ii) 프리챠지(GL=H, ES=H, CS=L)

각 데이터 라인 DL에의 데이터 세트가 종료된 후, 발광 세트 라인 ES를 H 레벨로 한다. 이에 의해, 구동 트랜지스터 T4의 드레인이 전원 라인 PVdd에 접속되고, 또한 단락 트랜지스터 T3이 온으로 되기 때문에, 구동 트랜지스터 T4의 게이트가 전원 전위 PVdd까지 쳐지된다.

(iii) 리세트(GL=H, ES=L, CS=L)

그 후, 발광 세트 라인 ES를 L 레벨로 복귀시키고, 구동 트랜지스터 T4를 전원 PVdd로부터 분리한다. 이에 의해, 구동 트랜지스터 T4의 게이트 전위는, 그 소스 전위로부터 임계값 전압 Vtn만큼 오프셋이 걸린 전위까지 내려간다. 한편, 유기 EL 소자 EL의 임계값 전압 Ve로 되기 때문에, 구동 트랜지스터 T4의 게이트 전압 Vg=Ve+Vtn로 된다. 또한, 이 때의 컨덴서 Cs의 데이터 라인 DL측은 데이터 라인 DL의 데이터 전압 Vsig로 되어 있다.

(iv) 전위 고정(GL=L, ES=L, CS=L)

이어서, 게이트 라인 GL을 L 레벨로 세트하여, 선택 트랜지스터 T1, 단락 트랜지스터 T3을 오프한다. 이에 의해, 도 32에 도시한 바와 같이 구동 트랜지스터 T4의 게이트 전압 Vg=Ve+Vtn으로 고정된다. 이 때, 컨덴서 Cs의 반대측의 전압은 Vsig이고, 컨덴서 Cs에는, Vsig-Vg=Vsig-(Ve+Vtn)의 전압이 충전된다.

(v) 발광(GL=L, ES=H, CS=H)

전위가 고정된 후, 발광 세트 라인 ES 및 용량 세트 라인 CS를 H 레벨로 한다. 이에 의해, 도 33에 도시한 바와 같이, 컨덴서 Cs의 선택 트랜지스터 T1측의 전압은 PVdd로 되고, 따라서 구동 트랜지스터 T4의 게이트 전압 Vg=PVdd-Vsig+Ve+Vtn로 된다. 그리고, 구동 제어 트랜지스터 T5도 온으로 되기 때문에, 구동 트랜지스터 T4가 그 게이트 소스 간 전압 Vgs에 따른 전류를 흘려, 이것이 유기 EL 소자 EL에 공급된다. 여기서, 구동 트랜지스터 T4의 소스 전위 Vs=Ve+I·R로 된다. 여기서, I는 유기 EL 소자 EL에 흐르는 전류값, R은 유기 EL 소자 EL의 온 저항이다. 따라서, 구동 트랜지스터 T4의 게이트 소스간 전압 Vgs=Vg-Vs=PVdd-Vsig+Vtn-I·R로 된다.

유기 EL 소자 EL의 온 저항 R은, 유기 EL 소자의 면적을 크게 하고, 유기 EL 소자의 유기층을 얇게 함으로써, 꽤 작게 할 수 있다. 그리고, 구동 트랜지스터 T4에서의 드레인 전류 I는,  $I=(1/2)\beta(Vgs-Vtn)^2$ 에 의해 결정되기 때문에, 구동 트랜지스터 T4의 임계값 전압에 의하지 않고, 데이터 전압 Vsig에 따른 전류를 구동 트랜지스터 T4에 흘릴 수 있다. 또한,  $\beta$ 는 구동 트랜지스터 T4 증폭율이고,  $\beta=\mu\epsilon Gw/Gi$ 로 표현되고,  $\mu$ 는 캐리어의 이동도,  $\epsilon$ 는 유전율,  $Gw$ 는 게이트 폭,  $Gi$ 는 게이트 길이이다.

특히, 구동 트랜지스터 T4의 게이트 소스간 전압 Vgs는, PVdd로부터 데이터 전압 Vsig를 감산한 전압에 기초하여 결정된다. 따라서, 데이터 전압 Vsig는, p 채널의 구동 트랜지스터의 게이트에 직접 공급하는 데이터 전압 Vsig와 동일한 것을 이용할 수 있다. 따라서, 데이터 라인 DL을 구동하는 회로를 종래와 마찬가지의 구성으로 할 수 있다.

이어서, 1 수평 라인 내의 각 화소에 대한 데이터의 기입 순서에 대하여, 도 34에 기초하여 설명한다.

우선, 1 수평 기간의 개시를 나타내는 인에이블 신호 ENB의 L 후에, 모든 데이터 라인 DL에 점순차적으로 데이터 전압 Vsig를 기입한다. 즉, 데이터 라인 DL에는, 용량 등이 접속되어 있고, 전압 신호를 세트함으로써, 데이터 라인 DL에 그 데이터 전압 Vsig가 유지된다. 따라서, 각 열의 화소에 대한 데이터 전압 Vsig를 순차적으로 대응하는 데이터 라인 DL에 세트함으로써, 모든 데이터 라인 DL에 데이터 전압 Vsig를 세트한다.

그리고, 이 데이터의 세트가 종료된 단계에서, 발광 세트 라인 ES를 H 레벨로 하여 프리챠지하고, 그 후 발광 세트 라인 ES를 L 레벨로 복귀시켜 리세트를 행한다. 그리고, 게이트 라인 GL을 L 레벨로 복귀시킴으로써, 화소 회로 내의 컨덴서 Cs의 충전 전압이 고정되고, 그 후 용량 세트 라인 CS를 H 레벨로 함으로써 구동 트랜지스터 T4의 게이트가 시프트하여, 해당 수평 라인의 전체 화소에서, 발광이 행하여진다.

이와 같이 하여, 통상적인 비디오 신호(데이터 전압 Vsig)가 순차적으로 데이터 라인 DL에 기입되고, 이것을 화소 회로에 세트하여, 발광시킬 수 있다.

특히, 도 30에 도시한 바와 같이, 화소 회로에 사용하는 트랜지스터(박막 트랜지스터 : TFT)를 모두 n 채널 트랜지스터로 하는 것이 적합하다. n 채널 트랜지스터는, 그 특성이 p 채널 트랜지스터에 비하여 우수하다. 이 때문에, 트랜지스터의 능동충을 아몰퍼스 실리콘으로 해도, 충분히 동작이 가능하게 된다. 따라서, 능동충에 대하여, 폴리실리콘화하는 처리를 불필요하게 하여 수율을 개선할 수 있다.

또한, 선택 트랜지스터 T1과 구동 트랜지스터 T4의 게이트 사이에 컨덴서 Cs를 삽입해도, 종래의 선택 트랜지스터를 직접 p 채널의 구동 트랜지스터의 제어단에 접속한 경우와 동일한 극성의 데이터 신호를 이용할 수 있다.

### ( I ) 변형 예9

도 35에는, 변형 예9의 화소 회로의 구성을 도시한다. 이 예에서는, 전위 제어 트랜지스터 T2의 일단(드레인)이 전원 라인 PVdd가 아니라, 발광 세트 라인 ES에 접속되어 있다. 이 구성에 의해서도, 도 1의 예와 마찬가지의 작용이 얻어진다. 또한, 전원으로서는 동일한 PVdd에 접속되지만, 발광 세트 라인 ES는, 전원 라인 PVdd와는 다른 라인이고, 유기 EL 소자 EL로 구동 공급하는 전원 라인 PVdd에 비하여 그 전압 변동이 없어, 안정된 동작이 얻어진다. 즉, 전위 제어 트랜지스터 T2에 의한 전압 Vn을 설정할 때에, 전원 라인 PVdd의 전압 강하의 영향을 받을 수 없다.

### 발명의 효과

이상, 본 발명에 따르면, 효과적으로 구동 트랜지스터의 임계값 전압의 변동을 보상할 수 있는 화소 회로를 제공할 수 있다.

### 도면의 간단한 설명

도 1은 실시예에 따른 화소 회로의 구성을 도시하는 도면.

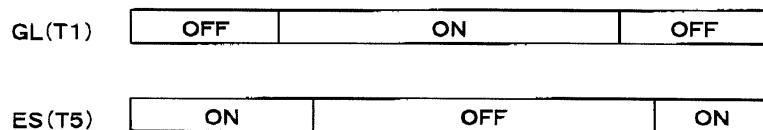

도 2는 동작을 설명하는 차트도.

도 3은 디스챠지 공정을 설명하는 도면.

도 4는 리세트 공정을 설명하는 도면.

도 5는 전위 고정 공정을 설명하는 도면.

도 6은 발광 공정을 설명하는 도면.

도 7은 리세트로부터 전위 고정 공정에서의 전위 변화의 상태를 설명하는 도면.

도 8은 패널의 전체 구성을 도시하는 도면.

도 9는 데이터 세트의 태이밍 예를 도시하는 도면.

도 10은 데이터 세트의 다른 태이밍 예를 도시하는 도면.

도 11은 변형 예1의 구성을 설명하는 도면.

도 12는 변형 예1의 구동 상태를 도시하는 도면.

도 13은 변형 예2의 구성을 설명하는 도면.

도 14는 변형 예2의 구동 상태를 도시하는 도면.

도 15는 변형 예2에 대한 다른 구성을 도시하는 도면.

도 16은 변형 예2에 대한 또 다른 구성을 도시하는 도면.

도 17은 변형 예2에 대한 또 다른 구성을 도시하는 도면.

도 18은 변형 예3에 대한 구성을 도시하는 도면.

도 19는 변형 예3의 구동 상태를 도시하는 도면.

도 20은 변형 예4에 대한 구성을 도시하는 도면.

도 21은 변형 예4의 구동 상태를 도시하는 도면.

도 22는 변형 예5에 따른 화소 회로의 구성을 도시하는 도면.

도 23은 변형 예5의 디스챠지 공정을 설명하는 도면.

도 24는 변형 예5의 리세트 공정을 설명하는 도면.

도 25는 변형 예5의 전위 고정 공정을 설명하는 도면.

도 26은 변형 예5의 발광 공정을 설명하는 도면.

도 27은 변형 예6의 구성을 설명하는 도면.

도 28은 변형 예7의 화소 회로의 구성을 도시하는 도면.

도 29는 변형 예7의 동작을 설명하는 차트도.

도 30은 변형 예8에 따른 화소 회로의 구성을 도시하는 도면.

도 31은 변형 예8의 동작을 설명하는 차트도.

도 32는 변형 예8의 데이터의 기입을 설명하는 도면.

도 33은 변형예8의 발광 시를 설명하는 도면.

도 34는 변형 예8의 데이터 세트의 타이밍 예를 도시하는 도면.

도 35는 변형 예9의 화소 회로의 구성을 도시하는 도면.

### 〈도면의 주요 부분에 대한 부호의 설명〉

GL : 게이트 라인

## DL : 데이터 라인

PVdd : 전원 라인

ES : 발광 세트 라인

도면

## 도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면 10

도면11

도면12

도면13

### 도면14

|        |     |     |     |

|--------|-----|-----|-----|

| GL(T1) | OFF | ON  | OFF |

| CS(T2) | ON  | OFF | ON  |

| ES(T5) | ON  | OFF | ON  |

### 도면 15

도면16

도면17

도면18

도면19

|         |     |     |     |

|---------|-----|-----|-----|

| GL(T1)  | OFF | ON  | OFF |

| RST(T3) | OFF | ON  | OFF |

| ES(T5)  | ON  | OFF | ON  |

도면20

도면21

|        |     |     |     |

|--------|-----|-----|-----|

| GL(T1) | OFF | ON  | OFF |

| ES(T5) | ON  | OFF | ON  |

## 도면22

### 도면23

도면24

도면25

도면26

도면27

도면28

도면29

### 도면30

### 도면31

### 도면32

### 도면33

도면34

도면35

|                |                                                                                                              |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于有机EL面板的像素电路及其驱动方法                                                                                          |         |            |

| 公开(公告)号        | <a href="#">KR100649513B1</a>                                                                                | 公开(公告)日 | 2006-11-27 |

| 申请号            | KR1020050029920                                                                                              | 申请日     | 2005-04-11 |

| [标]申请(专利权)人(译) | 三洋电机株式会社<br>山洋电气株式会社                                                                                         |         |            |

| 申请(专利权)人(译)    | 三洋电机有限公司是分租                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 三洋电机有限公司是分租                                                                                                  |         |            |

| [标]发明人         | IKEDA KYOJI                                                                                                  |         |            |

| 发明人            | IKEDA, KYOJI                                                                                                 |         |            |

| IPC分类号         | G09G3/30 G09F9/30 G09G3/32 H05B33/02 H05B33/08                                                               |         |            |

| CPC分类号         | G09G2300/0842 G09G2300/0861 G09G2320/043 G09G3/3233 G09G2300/0819                                            |         |            |

| 代理人(译)         | CHANG, SOO KIL<br>LEE, JUNG HEE                                                                              |         |            |

| 优先权            | 2004117332 2004-04-12 JP<br>2005092566 2005-03-28 JP<br>2005092588 2005-03-28 JP<br>2005096835 2005-03-30 JP |         |            |

| 其他公开文献         | KR1020060047168A                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                    |         |            |

### 摘要(译)

通过控制驱动晶体管的控制级的电位，将根据电势的驱动电流提供给有机电致发光显示器。驱动控制晶体管插入并设置在驱动晶体管和有机电致发光显示器之间。驱动电流打开和关闭。此外，建立短路晶体管。控制连接二极管的驱动晶体管与该短路晶体管是否相连。而且，使用选择晶体管，控制从数据线向驱动晶体管的控制级提供数据信号的纸张是否被控制。并且在该选择晶体管的控制级和驱动晶体管之间设置容量，并且使用选择晶体管的横向结果，并且利用电位控制晶体管接通和断开预定电源之间的连接。选择晶体管，电位控制晶体管，数据信号，二极管连接。