(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0018106

(43) 공개일자 2008년02월27일

(51) Int. Cl.

G09G 3/30 (2006.01) G09G 3/20 (2006.01)

G09G 3/32 (2006.01)

(21) 출원번호 10-2007-0082202

(22) 출원일자 2007년08월16일

심사청구일자 없음

(30) 우선권주장

JP-P-2006-00226754 2006년08월23일 일본(JP)

(71) 출원인

소니 가부시끼 가이샤

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

유모토 아키라

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시

끼 가이샤 나이

아사노 미쓰루

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시

끼 가이샤 나이

진타 세이이치로

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시

끼 가이샤 나이

(74) 대리인

이화의, 권태복

전체 청구항 수 : 총 8 항

**(54) 화소회로****(57) 요 약**

제어신호를 공급하는 행 방향의 주사선과 영상신호를 공급하는 열 방향의 데이터선이 교차하는 부분에 배치된 화소회로에 대해 기재하고, 상기 화소회로는, 샘플링 트랜지스터와, 드라이브 트랜지스터와, 상기 샘플링 트랜지스터의 전류단과 상기 드라이브 트랜지스터의 게이트 사이에 접속된 용량과, 상기 드라이브 트랜지스터의 전류단에 접속된 발광소자를 포함한다.

**대표도 - 도5**

## 특허청구의 범위

### 청구항 1

제어신호를 공급하는 행 방향의 주사선과 영상신호를 공급하는 열 방향의 데이터선이 교차하는 부분에 배치된 화소회로로서,

샘플링 트랜지스터와,

드라이브 트랜지스터와,

상기 샘플링 트랜지스터의 전류단과 상기 드라이브 트랜지스터의 게이트 사이에 접속된 용량과,

상기 드라이브 트랜지스터의 전류단에 접속된 발광소자를 포함하고,

상기 샘플링 트랜지스터의 게이트는 상기 주사선에 접속되고, 상기 샘플링 트랜지스터의 한쪽 전류단은 상기 데이터선에 접속되고, 다른 한쪽의 전류단은 상기 용량과의 접속점이 되며, 상기 샘플링 트랜지스터는, 소정의 샘플링 기간에 상기 주사선에서 공급되는 제어신호에 따라 도통해서 상기 데이터선에서 공급된 영상신호를 샘플링하고,

상기 드라이브 트랜지스터는, 상기 샘플링된 영상신호에 따라, 출력전류를 상기 발광소자에 공급하고,

상기 발광소자는, 상기 드라이브 트랜지스터로부터 공급된 출력전류에 의해 상기 영상신호에 따른 휘도로 발광하고,

상기 화소회로는, 상기 영상신호의 샘플링 기간 내에 설정된 보정기간 동안 동작하여, 상기 드라이브 트랜지스터의 상기 전류단을, 상기 샘플링 트랜지스터의 상기 접속점에 전기적으로 접속함으로써, 상기 보정기간에 상기 출력전류를 상기 접속점에 부귀환하는 것을 특징으로 하는 화소회로.

### 청구항 2

제 1항에 있어서,

상기 화소회로는 상기 출력전류의 부귀환을 통해 상기 드라이브 트랜지스터의 이동도의 편차를 보정하는 것을 특징으로 하는 화소회로.

### 청구항 3

제 1항에 있어서,

상기 출력전류를 상기 접속점에 부귀환하는 부귀환 수단을 구비한 것을 특징으로 하는 화소회로.

### 청구항 4

제 3항에 있어서,

상기 부귀환 수단은, 상기 드라이브 트랜지스터의 상기 전류단과 상기 샘플링 트랜지스터의 상기 접속점 사이에 접속된 스위칭 트랜지스터를 포함하고,

상기 스위칭 트랜지스터는 상기 보정 기간 동안 그 게이트에 인가되는 제어신호에 따라 도통하여, 상기 드라이브 트랜지스터의 상기 전류단을, 상기 샘플링 트랜지스터의 상기 접속점에 전기적으로 접속하는 것을 특징으로 하는 화소회로.

### 청구항 5

제 3항에 있어서,

상기 부귀환 수단은, 상기 드라이브 트랜지스터의 상기 전류단과 상기 데이터선 사이에 접속된 스위칭 트랜지스터를 포함하고,

상기 스위칭 트랜지스터는 상기 보정 기간 동안 그 게이트에 인가되는 제어신호에 따라 도통하여, 상기 드라이브 트랜지스터의 상기 전류단을, 상기 샘플링 기간 동안 도통상태에 있는 상기 샘플링 트랜지스터를 통해 상기

접속점에 접속하는 것을 특징으로 하는 화소회로.

### 청구항 6

제 1항에 있어서,

상기 드라이브 트랜지스터의 상기 게이트와 상기 전류단 사이에 접속되는 스위칭 트랜지스터를 포함하고,

상기 스위칭 트랜지스터는 상기 영상신호의 샘플링에 앞서 온 상태로 하여, 상기 드라이브 트랜지스터의 역치전 압에 해당하는 전압을 그 게이트에 기록하는 것을 특징으로 하는 화소회로.

### 청구항 7

제어신호를 공급하는 행 방향의 주사선과 영상신호를 공급하는 열 방향의 데이터선이 교차하는 부분에 배치된 화소회로로서,

샘플링 트랜지스터와,

드라이브 트랜지스터와,

상기 드라이브 트랜지스터의 게이트에 접속된 용량과,

상기 드라이브 트랜지스터에 접속된 발광소자를 포함하고,

상기 샘플링 트랜지스터는, 소정의 샘플링 기간에 상기 주사선에서 공급되는 제어신호에 따라 도통해서, 상기 데이터선에서 공급된 영상신호를 상기 용량에 샘플링하고,

상기 드라이브 트랜지스터는, 상기 샘플링된 영상신호에 따라, 출력전류를 상기 발광소자에 공급하고,

상기 발광소자는, 상기 드라이브 트랜지스터로부터 공급된 출력전류에 의해 상기 영상신호에 따른 휘도로 발광하고,

상기 화소회로는, 제1 스위칭 트랜지스터와, 상기 제1 스위칭 트랜지스터와 분리된 제2 스위칭 트랜지스터를 더 포함하고,

상기 제1 스위칭 트랜지스터는, 상기 영상신호의 샘플링에 앞서 온 상태로 하여, 상기 드라이브 트랜지스터의 역치전압에 해당하는 전압을 상기 용량에 기록하고,

상기 제2 스위칭 트랜지스터는, 상기 영상신호의 샘플링 기간 내에 설정된 보정기간에 동작하여, 상기 보정기간에 상기 출력전류를 상기 용량에 부귀화하는 것을 특징으로 하는 화소회로.

### 청구항 8

제어신호를 공급하는 행 방향의 주사선과,

영상신호를 공급하는 열 방향의 데이터선과,

상기 주사선과 상기 데이터선이 교차하는 부분에 배치된 화소회로로서,

샘플링 트랜지스터와,

드라이브 트랜지스터와,

상기 샘플링 트랜지스터의 전류단과 상기 드라이브 트랜지스터의 게이트 사이에 접속된 용량과,

상기 드라이브 트랜지스터의 전류단에 접속된 발광소자를 적어도 포함한 화소회로를 구비한 표시장치로서,

상기 샘플링 트랜지스터의 게이트는 상기 주사선에 접속되고, 상기 샘플링 트랜지스터의 한쪽 전류단은 상기 데이터선에 접속되고, 다른 한쪽의 전류단은 상기 용량과의 접속점이 되며, 상기 샘플링 트랜지스터는, 소정의 샘플링 기간에 상기 주사선에서 공급되는 제어신호에 따라 도통해서 상기 데이터선에서 공급된 영상신호를 샘플링하고,

상기 드라이브 트랜지스터는, 상기 샘플링된 영상신호에 따라, 출력전류를 상기 발광소자에 공급하고,

상기 발광소자는, 상기 드라이브 트랜지스터로부터 공급된 출력전류에 의해 상기 영상신호에 따른 휘도로 발광

하고,

상기 화소회로는, 상기 영상신호의 샘플링 기간 내에 설정된 보정기간 동안 동작하여, 상기 드라이브 트랜지스터의 상기 전류단을, 상기 샘플링 트랜지스터의 상기 접속점에 전기적으로 접속함으로써, 상기 보정기간에 상기 출력전류를 상기 접속점에 부귀환하는 것을 특징으로 하는 표시장치.

## 명세서

### 발명의 상세한 설명

#### 기술분야

- <1> 본 발명은 2006년 8월 23일에 일본 특허청에 출원된 일본 특개 JP 2006-226754에 관한 주제를 포함하고, 그 모든 내용은 여기에 참조로 인용된다.

- <2> 본 발명은 화소마다 배치한 발광소자를 전류 구동하는 화소회로에 관한 것이다. 특히 각 화소회로 내에 설치한 절연 게이트형 전계효과 트랜지스터에 의해, 유기 EL소자 등의 발광소자에 공급하는 전류량을 제어하는 액티브 방식의 화소회로에 관한 것이다. 더욱 자세한 것은, 각 화소회로에 형성한 발광소자의 구동용 트랜지스터의 이동도의 편차를 보정하는 기술에 관한 것이다.

#### 배경기술

- <3> 화상표시장치, 예를 들면 액정 모니터 등에서는 다수의 액정화소를 매트릭스형으로 배열한다. 표시해야 할 화상 정보에 따라 화소마다 입사광의 투과 강도 또는 반사 강도를 제어함으로써 화상을 표시한다. 이것은, 유기 EL소자를 화소에 사용한 유기 EL디스플레이 등에 있어서도 마찬가지지만, 액정화소와 달리 유기 EL소자는 자발광 소자다. 그 때문에, 유기 EL디스플레이에는 액정 모니터에 비해 화상의 시인성이 높고, 백라이트를 필요로 하지 않고, 응답 속도가 높은 등의 이점을 가진다. 또한, 각 발광소자의 휘도 레벨(계조)은 거기에 흐르는 전류치에 의해 제어할 수 있다. 유기 EL디스플레이의 소위 전류제어형이라는 점에서 액정 모니터 등의 전압제어형과는 크게 다르다.

- <4> 유기 EL디스플레이의 구동방식에는, 액정 모니터와 마찬가지로, 단순 매트릭스 방식과 액티브 매트릭스 방식이 있다. 전자는 구조가 단순하지만, 대형이면서 고화질의 디스플레이를 제공하기 어렵다는 점 등의 문제가 있다. 따라서, 현재는 액티브 매트릭스 방식의 개발이 활발히 이루어지고 있다. 이 방식은, 각 화소회로 내부의 발광소자에 흐르는 전류를, 화소회로 내부에 설치한 능동소자(일반적으로는 박막 트랜지스터, TFT)에 의해 제어하는 것이다. 액티브 방식의 화소회로는, 예를 들면 일본국 공개특허공보 특개 평8-234683호(특허문현 1이라 칭함), 특표 2002-514320 공보, 일본국 공개특허공보 특개 2005-173434 공보(각각 특허문현 2, 특허문현 3이라 칭함)에 기재되어 있다.

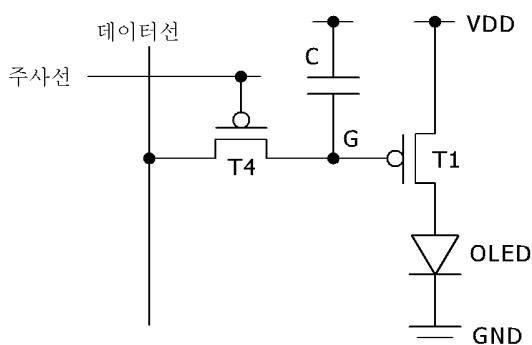

- <5> 도 1은, 종래의 화소회로의 가장 단순한 구성예를 계시하는 회로도다. 도시하는 바와 같이, 이 화소회로는, 제어신호를 공급하는 행 방향의 주사선과 영상신호를 공급하는 열 방향의 데이터선이 교차하는 부분에 배치되어 있다. 이 화소회로는, 샘플링 트랜지스터 T4와 용량 C와 드라이브 트랜지스터 T1과 발광소자 OLED를 포함한다. 이 발광소자 OLED는 예를 들면 유기 EL소자다. 샘플링 트랜지스터 T4는, 주사선에서 공급되는 제어신호에 따라 도통해서 데이터선에서 공급되는 영상신호를 샘플링한다. 용량 C는 샘플링된 영상신호에 따른 입력 전압을 보유한다. 드라이브 트랜지스터 T1은, 용량 C에 보유된 입력 전압에 따라 소정의 발광 기간에 출력전류를 공급한다. 이때 일반적으로, 출력전류는 드라이브 트랜지스터 T1의 채널 영역의 캐리어 이동도  $\mu$  및 역치전압  $V_{th}$ 에 의존성을 가진다. 발광소자 OLED는, 드라이브 트랜지스터 T1로부터 공급된 출력전류에 의해 영상신호에 따른 휘도로 발광한다. 이때 도시한 예에서는, 드라이브 트랜지스터 T1의 한쪽의 전류단(소스)은 전원전위 VDD에 접속되어 있고, 다른 쪽의 전류단(드레인)은 발광소자 OLED의 애노드에 접속되어 있다. 발광소자 OLED의 캐소드는 접지전위 GND에 접속되어 있다.

- <6> 드라이브 트랜지스터 T1은, 용량 C에 보유된 입력 전압이 게이트 G에 인가되면, 소스/드레인간에 출력전류를 흐르게 하여, 발광소자 OLED에 전류를 공급한다. 일반적으로 발광소자 OLED의 발광 휘도는 전류 공급량에 비례한다. 또한, 드라이브 트랜지스터 T1의 출력전류 공급량은 게이트 전압, 즉 용량 C에 기록된 입력 전압에 의해 제어된다. 종래의 화소회로에서는, 드라이브 트랜지스터 T1의 게이트 G에 인가되는 입력 전압을 입력 영상신호에 따라 변화시킴으로써 발광소자 OLED에 공급하는 전류량을 제어하였다.

<7> 여기에서 드라이브 트랜지스터 T1의 동작 특성은 이하의 식 1로 나타낸다.

$$<8> I_{ds} = (1/2) \mu (W/L) Cox (V_{gs}-V_{th})^2 \quad \dots \quad (1)$$

<9> 이 트랜지스터 특성식 1에 있어서,  $I_{ds}$ 는 소스에서 드레인으로 흐르는 드레인 전류를 나타내고, 화소회로에서는 발광소자 OLED에 공급되는 출력전류다.  $V_{gs}$ 는 소스를 기준으로 게이트에 인가되는 게이트 전압을 나타낸다. 화소회로에서  $V_{gs}$ 는 전술한 입력 전압이다.  $V_{th}$ 는 트랜지스터의 역치전압이다. 또  $\mu$ 는 트랜지스터의 채널을 구성하는 반도체 박막의 이동도를 나타내고 있다. 한편,  $W$ 는 채널 폭을 나타내고,  $L$ 은 채널 길이를 나타내고,  $Cox$ 는 게이트 용량을 나타낸다. 이 트랜지스터 특성식 1로부터 명확한 것처럼, 박막 트랜지스터는 포화 영역에서 동작할 때, 게이트 전압  $V_{gs}$ 가 역치전압  $V_{th}$ 를 초과하면, 온 상태가 되어서 드레인 전류  $I_{ds}$ 가 흐른다. 동작 원리로 보면, 상기의 트랜지스터 특성식 1이 나타내는 것처럼, 게이트 전압  $V_{gs}$ 가 일정하면 항상 같은 양의 드레인 전류  $I_{ds}$ 가 발광소자 OLED에 공급된다. 따라서, 화면을 구성하는 각 화소에 모두 동일한 레벨의 영상신호를 공급하면, 전체 화소가 동일 휙도로 발광한다. 이로써 화면의 일양성(유니포머티)이 얻어진다.

<10> 그러나 실제로는, 폴리실리콘 등의 반도체 박막으로 구성된 박막 트랜지스터(TFT)는, 각각의 디바이스 특성에 편차가 있다. 특히, 역치전압  $V_{th}$ 는 일정하지 않고 화소마다 편차가 있다. 전술의 트랜지스터 특성식 1로부터 명확한 것처럼, 각 드라이브 트랜지스터의 역치전압  $V_{th}$ 가 변동하면, 게이트 전압  $V_{gs}$ 가 일정해도, 드레인 전류  $I_{ds}$ 에 편차가 생기고, 화소마다 휙도가 변동되기 때문에, 화면의 유니포머티를 손상한다. 이 때문에 종래부터 드라이브 트랜지스터 T1의 역치전압의 편차를 캔슬하는 기능을 내장한 화소회로가 개발되고 있다. 예를 들면, 특허문헌 2에 기재되어 있다.

<11> 드라이브 트랜지스터의 역치전압  $V_{th}$ 의 편차를 캔슬하는 기능을 내장한 화소회로는, 화면의 유니포머티나 역치전압의 시간에 따른 변화에 의한 휙도변동을 개선할 수 있다. 그런데 드라이브 트랜지스터를 구성하는 TFT의 특성 편차는,  $V_{th}$ 뿐만 아니라 이동도  $\mu$ 도 화소 사이에서 변동하는 것이 알려져 있다. 역치전압  $V_{th}$ 과 함께 이동도  $\mu$ 의 보정 기능을 갖춘 화소회로도 알려져 있다. 예를 들면, 상기 특허문헌 3에 기재되어 있다.

## 발명의 내용

### 해결 하고자하는 과제

<12> 전술한 이동도  $\mu$ 의 보정 기능을 갖춘 화소회로는, 기본적으로 샘플링 기간의 일부인 소정의 이동도 보정 기간 동안, 드라이브 트랜지스터로부터 공급되는 출력전류를 그 드라이브 트랜지스터의 게이트측에 부귀환하여, 이동도 보정을 행하는 방식이다. 드라이브 트랜지스터의 이동도  $\mu$ 가 클수록 부귀환량이 많아진다. 이에 따라, 드라이브 트랜지스터의 게이트 전압(즉 신호 전위)이 저하되어, 출력전류를 억제하도록 작용한다. 반대로 이동도  $\mu$ 가 작을 경우 부귀환량도 작아진다. 따라서 출력전류는 크게 저하되지 않는다. 이렇게 하여, 화소간의 이동도  $\mu$ 의 편차를 보정한다.

<13> 이와 같이, 종래의 이동도 보정은, 드라이브 트랜지스터의 출력전류를 게이트측에 부귀환함으로써 이루어졌다. 그러나, 부귀환으로 인해 필연적으로 드라이브 트랜지스터의 게이트 전압(신호 전압)이 압축되고, 이 상태로는 휙도의 저하를 초래한다. 부귀환으로 인한 휙도의 저하를 보상하기 위해, 미리 영상신호의 진폭을 크게 설정할 필요가 있다. 그러나 그만큼 소비 전력의 증가를 초래한다.

<14> 또 종래의 화소회로에서, 드라이브 트랜지스터의 게이트측에 접속하는 용량성분은 비교적 작다. 이 때문에, 부귀환에 의해 급속하게 게이트 전압이 압축된다. 이것을 억제하기 위해, 부귀환을 적용하는 이동도 보정기간을 가능한 한 짧게 설정할 필요가 있다. 그러나, 이동도 보정기간을  $\mu s$  단위의 단시간으로 하면, 배선의 지연 등으로 인해 타이밍 제어에 편차가 생기고, 그 결과 안정된 이동도 보정동작을 행하기 어려워진다. 특히 패널이 대형화되면 배선 지연이 현저해져, 단시간에 안정적으로 이동도 보정동작을 행하는 것이 곤란해져, 해결해야 할 과제로 남는다.

### 과제 해결수단

<15> 전술한 종래의 기술의 과제를 감안하여, 본 발명은 부귀환 동작에 의해 드라이브 트랜지스터의 이동도 편차를 보정하는 기능을 안정화시키면서, 충분한 휙도를 확보할 수 있고, 소비 전력이 적은 화상표시장치를 실현할 수 있는 화소회로를 제공하는 것을 목적으로 한다. 이러한 목적을 달성하기 위해 이하의 수단을 강구했다. 즉, 본 발명의 실시예의 화소회로는, 제어신호를 공급하는 행 방향의 주사선과 영상신호를 공급하는 열 방향의 데이터선이 교차하는 부분에 배치된다. 화소회로는, 샘플링 트랜지스터와, 드라이브 트랜지스터와, 상기 샘플링 트랜

지스터의 전류단과 상기 드라이브 트랜지스터의 게이트 사이에 접속된 용량과, 상기 드라이브 트랜지스터의 전류단에 접속된 발광소자를 포함한다. 상기 샘플링 트랜지스터의 게이트는 상기 주사선에 접속된다. 상기 샘플링 트랜지스터의 한쪽 전류단은 상기 데이터선에 접속된다. 다른 한쪽의 전류단은 상기 용량과의 접속점이 된다. 상기 샘플링 트랜지스터는, 소정의 샘플링 기간에 상기 주사선에서 공급되는 제어신호에 따라 도통해서 상기 데이터선에서 공급된 영상신호를 샘플링한다. 상기 드라이브 트랜지스터는, 상기 샘플링된 영상신호에 따라, 소정의 발광 기간 동안 출력전류를 상기 발광소자에 공급한다. 상기 발광소자는, 상기 드라이브 트랜지스터로부터 공급된 출력전류에 의해 상기 영상신호에 따른 휘도로 발광한다. 화소회로는, 상기 영상신호의 샘플링 기간 내에 설정된 보정기간 동안 동작하여, 상기 드라이브 트랜지스터의 상기 전류단을, 상기 샘플링 트랜지스터의 상기 접속점에 전기적으로 접속함으로써, 상기 보정기간에 상기 출력전류를 상기 접속점에 부귀환한다.

<16> 화소회로는 출력전류의 부귀환을 통해 드라이브 트랜지스터의 이동도의 편차를 보정한다. 화소회로는 출력전류를 접속점에 부귀환하는 부귀환 수단을 구비한다. 바람직하게는, 상기 부귀환 수단은, 상기 드라이브 트랜지스터의 상기 전류단과 상기 샘플링 트랜지스터의 상기 접속점 사이에 접속된 스위칭 트랜지스터를 포함한다. 스위칭 트랜지스터는 상기 보정 기간 동안 그 게이트에 인가되는 제어신호에 따라 도통하여, 상기 드라이브 트랜지스터의 상기 전류단을, 상기 샘플링 트랜지스터의 상기 접속점에 전기적으로 접속한다. 또는, 상기 부귀환 수단은, 상기 드라이브 트랜지스터의 상기 전류단과 상기 데이터선 사이에 접속된 스위칭 트랜지스터를 포함한다. 스위칭 트랜지스터는 상기 보정 기간 동안 그 게이트에 인가되는 제어신호에 따라 도통하여, 상기 드라이브 트랜지스터의 상기 전류단을, 상기 샘플링 기간 동안 도통상태에 있는 상기 샘플링 트랜지스터를 통해 상기 접속점에 접속한다. 화소회로는 상기 드라이브 트랜지스터의 상기 게이트와 상기 전류단 사이에 접속되는 스위칭 트랜지스터를 포함한다. 스위칭 트랜지스터는 상기 영상신호의 샘플링에 앞서 온 하여, 상기 드라이브 트랜지스터의 역치전압에 해당하는 전압을 그 게이트에 기록한다.

<17> 본 발명의 실시예의 화소회로는, 제어신호를 공급하는 행 방향의 주사선과 영상신호를 공급하는 열 방향의 데이터선이 교차하는 부분에 배치된다. 화소회로는, 샘플링 트랜지스터와, 드라이브 트랜지스터와, 상기 드라이브 트랜지스터의 게이트에 접속된 용량과, 상기 드라이브 트랜지스터에 접속된 발광소자를 포함한다. 상기 샘플링 트랜지스터는, 소정의 샘플링 기간에 상기 주사선에서 공급되는 제어신호에 따라 도통해서, 상기 데이터선에서 공급된 영상신호를 상기 용량에 샘플링한다. 상기 드라이브 트랜지스터는, 상기 샘플링된 영상신호에 따라, 출력전류를 상기 발광소자에 공급한다. 상기 발광소자는, 상기 드라이브 트랜지스터로부터 공급된 출력전류에 의해 상기 영상신호에 따른 휘도로 발광한다. 상기 화소회로는, 제1 스위칭 트랜지스터와, 이것과는 다른 제2 스위칭 트랜지스터를 포함한다. 상기 제1 스위칭 트랜지스터는, 상기 영상신호의 샘플링에 앞서 온 하여, 상기 드라이브 트랜지스터의 역치전압에 해당하는 전압을 상기 용량에 기록한다. 상기 제2 스위칭 트랜지스터는, 상기 영상신호의 샘플링 기간 내에 설정된 보정기간에 동작하여, 상기 보정기간에 상기 출력전류를 상기 용량에 부귀환한다.

## 효과

<18> 본 발명의 실시예에 의하면, 영상신호의 샘플링 후에, 드라이브 트랜지스터의 전류단(예를 들면 드레인)과, 샘플링 트랜지스터의 전류단과 용량의 접속점(이하 입력측 노드라고 부르는 경우가 있다)이, 부귀환 수단을 구성하는 스위칭 트랜지스터에 의해 접속된다. 이 스위칭 트랜지스터의 동작에 의해, 드라이브 트랜지스터에 흐르는 출력전류가, 입력측 노드에 부귀환되어, 그 전위변화를 초래한다. 이 입력측 노드와 드라이브 트랜지스터의 게이트는, 용량에 의해 교류 방식으로 결합한다. 그 결과, 드라이브 트랜지스터의 게이트 전위도 변화된다. 입력측 노드의 전위변화는, 드라이브 트랜지스터의 게이트 전압  $V_{gs}$ 의 절대치를 감소시키도록 작용한다. 드라이브 트랜지스터 출력전류가 클수록, 이 작용은 현저해진다. 따라서 화소간에서 드라이브 트랜지스터의 구동 능력(즉 이동도  $\mu$ )에 차이가 있으면, 구동전류를 축소하도록 작용한다. 이에 따라, 드라이브 트랜지스터의 이동도  $\mu$ 의 편차를 보정할 수 있어, 휘도의 균일성이 우수한 화상표시장치를 제공할 수 있다.

<19> 특히 본 발명에서는, 부귀환 수단으로서 전용 스위칭 트랜지스터를 설치한다. 이 스위칭 트랜지스터에 의해, 드라이브 트랜지스터의 전류단(예를 들면 드레인 노드)과, 용량의 입력측 노드가 전기적으로 접속된다. 이 스위칭 트랜지스터는 샘플링 기간 동안 온 하도록 제어되기 때문에, 샘플링 트랜지스터도 도통상태에 있다. 결과적으로 이동도 보정시에는, 드라이브 트랜지스터의 전류단과 데이터선이, 도통상태에 있는 샘플링 트랜지스터를 통해 전기적으로 접속된 상태에 있다. 데이터선은 일반적으로 패널의 상하에 걸쳐 설치된다. 그 결과, 이 선들은 비교적 큰 기생용량을 가진다. 따라서 입력 노드의 용량성분이 비교적 크기 때문에, 이동도 보정 기간 동안 입력 노드의 전위가 상승하는 속도는 비교적 느린다. 즉 드라이브 트랜지스터의 게이트 전압  $V_{gs}$ 의 압축이 비교적 천

천히 발생하기 때문에, 그만큼 이동도 보정기간의 타이밍 제어도 천천히 행할 수 있다. 따라서 패널이 대형화되어 배선 지연이 증가한 경우에도, 안정된 이동도  $\mu$ 의 편차 보정동작을 행할 수 있다.

### 발명의 실시를 위한 구체적인 내용

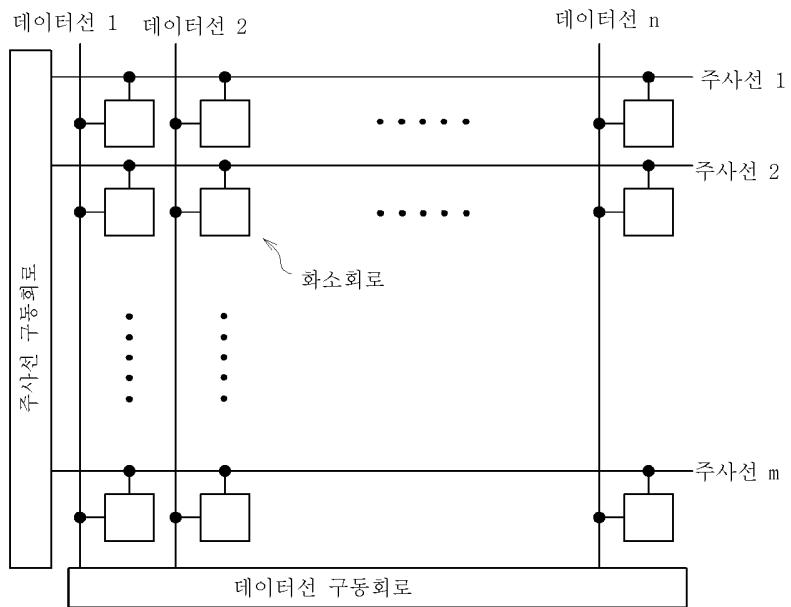

- <20> 이하 도면을 참조해서 본 발명의 실시예를 상세하게 설명한다. 도 2는, 본 발명의 실시예에 따른 화소회로를 집적한 화상표시장치의 전체 구성을 나타내는 블럭도다. 도시하는 것처럼, 이 화상표시장치는, 중앙의 화소 어레인부와, 그 주변에 위치하는 데이터선 구동회로 및 주사선 구동회로로 구성되어 있다. 화소 어레이부는, 행 방향의 주사선 1~m과, 열 방향의 데이터선 1~n과, 각 주사선과 각 데이터선이 교차하는 부분에 배치된 화소회로로 구성되어 있다. 주사선 구동회로는, 각 주사선 1~m에 접속되어 있고, 화소회로를 선 순차 주사하기 위한 제어신호를 순차 공급한다. 데이터선 구동회로는 열 방향의 데이터선 1~n에 접속되어 있고, 각 화소회로에 영상신호를 공급한다.

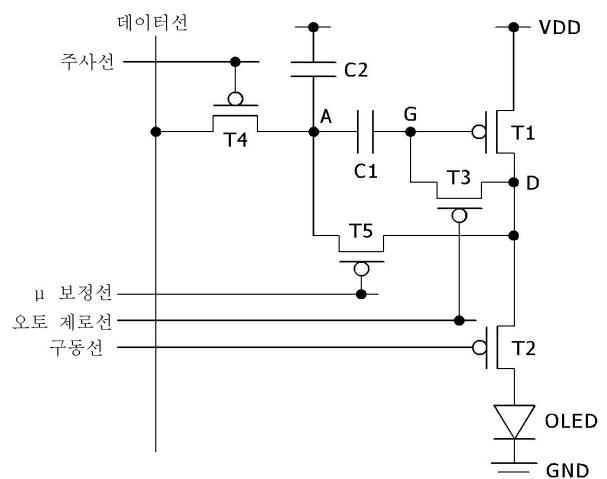

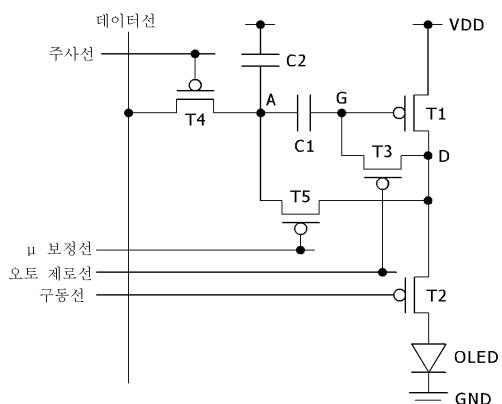

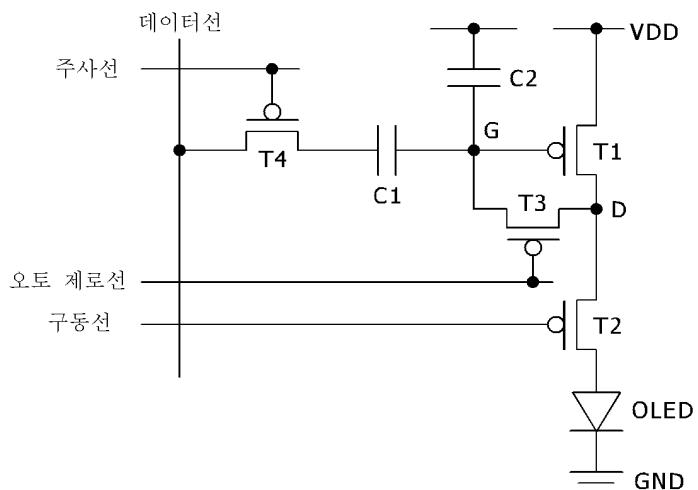

- <21> 도 3은, 도 2에 나타낸 화소회로의 구성예를 게시하는 회로도다. 단, 이 화소회로는 본 발명의 원인이 된 참고예다. 본 발명의 배경을 밝히기 위해서 유용하므로, 이 참고예를 간단하게 설명한다. 이 화소회로는, 4개의 P 채널형 트랜지스터 T1~T4와, 2개의 용량 C1 및 C2와, 발광소자 OLED로 구성되어 있다. 4개의 트랜지스터 T1~T4 중에서, T1은 드라이브 트랜지스터, T2 및 T3은 스위칭 트랜지스터, T4는 샘플링 트랜지스터다. 드라이브 트랜지스터 T1의 한쪽의 전류단(소스)은 전원전위 VDD에 접속되고, 다른 쪽의 전류단(드레인 D)은 스위칭 트랜지스터 T2를 통해 발광소자 OLED의 애노드에 접속된다. 발광소자 OLED의 캐소드는 접지전위 GND에 접속된다. 스위칭 트랜지스터 T2의 게이트는 주사선과 평행하게 배치된 구동선에 접속된다. 드라이브 트랜지스터 T1의 드레인 D는 다른 1개의 스위칭 트랜지스터 T3을 통해 드라이브 트랜지스터 T1의 게이트 G에 접속된다. 용량 C2는 이 게이트 G와 소정의 전원전위 사이에 접속된다. 스위칭 트랜지스터 T3의 게이트에는 주사선과 평행하게 배치된 오토 제로선이 접속된다. 샘플링 트랜지스터 T4의 한쪽 전류단은 용량 C1의 일단과 접속된다. 본 명세서에서는 이 접속점을 입력 노드라고 부르는 경우가 있다. 용량 C1의 다른 쪽의 단부는 드라이브 트랜지스터 T1의 게이트 G에 접속된다. 샘플링 트랜지스터 T4의 다른 쪽의 전류단은 데이터선에 접속된다. 따라서, 샘플링 트랜지스터 T4의 전류단과 드라이브 트랜지스터 T1의 제어단(게이트 G)은, 결합 용량 C1에 의해 교류 방식으로 접속된다. 샘플링 트랜지스터 T4의 게이트에는 주사선이 접속된다.

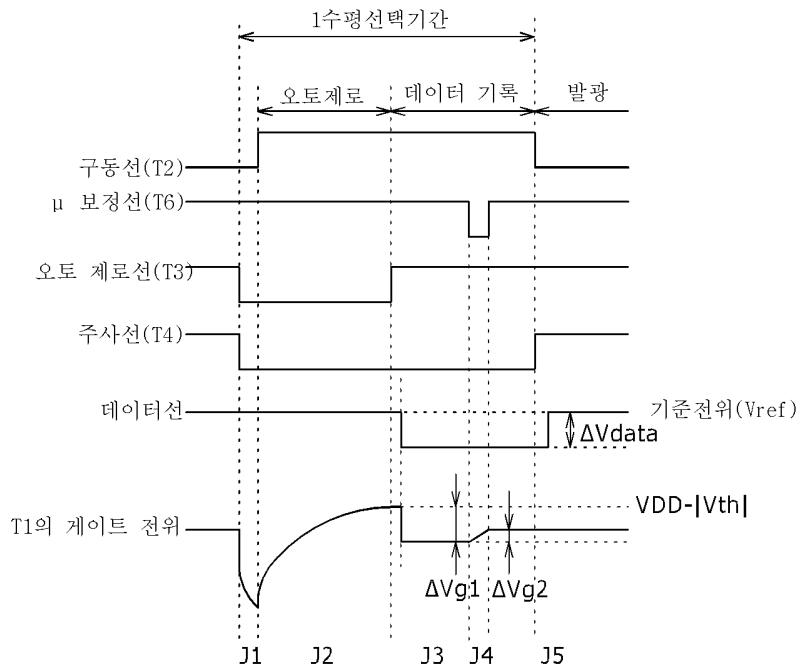

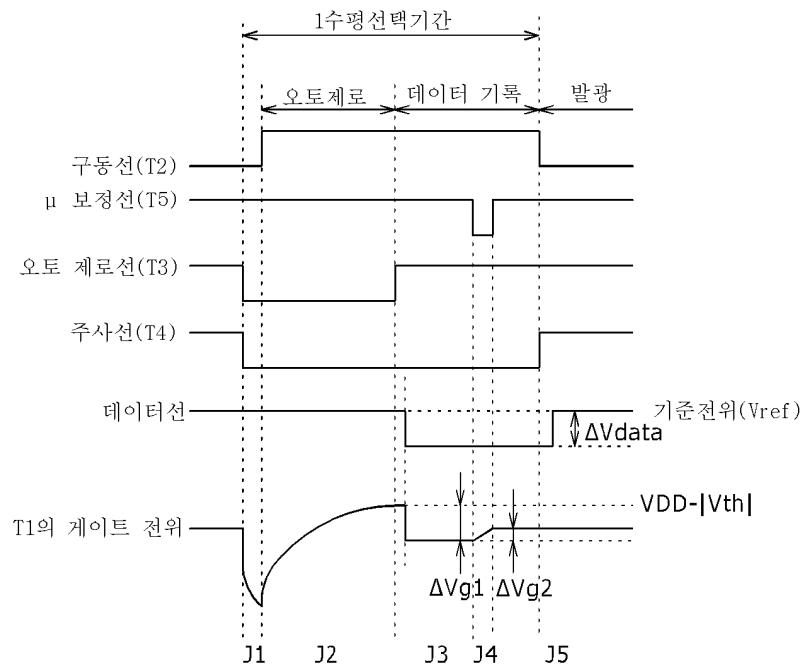

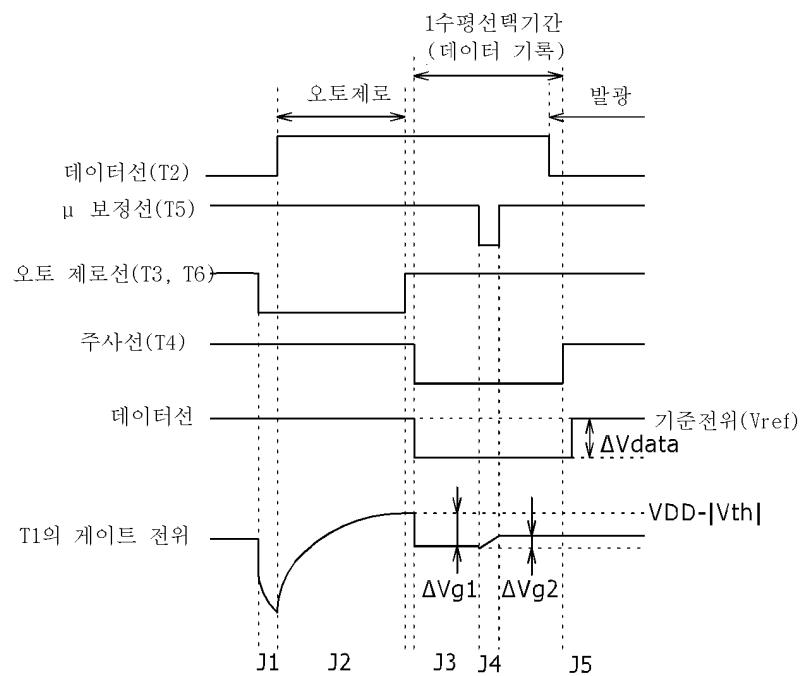

- <22> 도 4는, 도 3에 나타낸 화소회로의 동작 설명에 제공하는 타이밍 차트다. 각 트랜지스터 T2, T3, T4의 제어단(게이트)에 접속된 구동선, 오토 제로선 및 주사선의 전위변화(즉, 제어신호 파형)뿐만 아니라, 데이터선상의 신호 전위의 변화도 나타낸다. 또한, 드라이브 트랜지스터 T1의 게이트 전위의 변화 파형도 나타낸다.

- <23> 우선 준비 기간 J1에, 구동선 및 오토 제로선을 저레벨로 함으로써, 트랜지스터 T2 및 T3을 도통상태로 한다. 이때 드라이브 트랜지스터 T1은 다이오드 접속된 상태에서 발광소자 OLED와 접속하기 때문에, 드라이브 트랜지스터 T1에 드레인 전류가 흐른다.

- <24> 다음의 오토 제로 기간 J2에, 구동선을 고레벨로 함으로써, 스위칭 트랜지스터 T2를 비도통으로 한다. 이때 주사선은 저레벨이기 때문에 샘플링 트랜지스터 T4가 도통상태로 되고, 데이터선에는 기준전위 Vref가 주어진다. 드라이브 트랜지스터 T1에 흐르는 전류가 차단되기 때문에, 드라이브 트랜지스터 T1의 게이트 전위는 상승하지만, 그 전위가  $VDD - |Vth|$ 까지 상승한 시점에서 드라이브 트랜지스터 T1은 비도통상태가 되고, 전위가 안정된다. 이 동작을 이후 「오토 제로 동작」이라고 부르는 경우가 있다. 이 오토 제로 동작에 의해, 드라이브 트랜지스터 T1의 역치전압  $Vth$ 에 해당하는 전압을 그 게이트 G에 기록할 수 있다.

- <25> 이어서 데이터 기록 기간 J3에, 오토 제로선을 고레벨로 전환함으로써, 스위칭 트랜지스터 T3을 비도통으로 한다. 또 데이터선의 전위를  $Vref$ 에서 신호 전압  $\Delta Vdata$ 만큼 낮은 전위로 한다. 이 데이터선 전위의 변화로 인해 용량 C1을 통해 드라이브 트랜지스터 T1의 게이트 전위가  $\Delta Vg1$ 만큼 하강한다.

- <26> 데이터 기록 기간 J3 내에 설정된 이동도 보정기간 J4에, 오토 제로선을 단기간 동안 저레벨로 함으로써, 스위칭 트랜지스터 T3을 일시적으로 도통상태로 한다. 이때 드라이브 트랜지스터 T1은 도통상태에 있기 때문에, 드라이브 트랜지스터 T1의 소스로부터 드레인 D를 향해 전류가 흐르고, 스위칭 트랜지스터 T3을 통해 드라이브 트랜지스터 T1의 게이트 G측에 부귀화된다. 이 부귀화 동작에 의해, 드라이브 트랜지스터 T1의 게이트 전위가 상승한다. 게이트 전위가  $\Delta Vg2$ 만큼 상승한 시점에서 오토 제로선이 고레벨로 되돌아오고, 스위칭 트랜지스터 T3이 오프(비도통)가 된다.

- <27> 발광 기간 J5에는, 주사선을 고레벨로 함으로써, 샘플링 트랜지스터 T4를 비도통으로 한다. 구동선은 저레벨로 함으로써, 스위칭 트랜지스터 T2를 도통상태로 한다. 그 결과, 드라이브 트랜지스터 T1 및 발광소자 OLED에 출

력전류가 흐르고, 이에 따라 발광소자 OLED가 발광을 시작한다.

<28> 전술한 데이터 기록 기간 J3에 있어서의 데이터 기록에서는, 기생 용량을 무시하면,  $\Delta Vg1$  및 드라이브 트랜지스터 T1의 게이트 전위  $Vg$ 는 각각 이하의 식 2 및 3으로 나타낸다.

$$<29> \Delta Vg1 = \Delta Vdata \times C1 / (C1+C2) \quad \dots \quad (2)$$

$$<30> Vg = VDD - |Vth| - \Delta Vdata \times C1 / (C1+C2) \quad \dots \quad (3)$$

<31> 여기에서 이동도 보정기간 J4에 이동도 보정동작을 행하지 않을 경우에 대해서 생각한다. 이 경우, 데이터 기록 기간 J3이 종료되면 그대로 발광 기간 J5에 진행되게 된다. 발광 기간 J5에 발광소자 OLED에 흐르는 전류를  $Ioled$ 라고 하면, 이것은 발광소자 OLED와 직렬로 접속되어 있는 드라이브 트랜지스터 T1에 의해 그 전류치가 제어된다. 드라이브 트랜지스터 T1이 포화 영역에서 동작한다고 가정하면, 잘 알려진 MOS 트랜지스터의 특성식 1 및 상기 두 식을 사용하여,  $Ioled$ 는 이하의 식 4와 같이 나타낸다.

$$<32> Ioled = \mu \cdot Cox(W/L)(1/2)(VDD - Vg - |Vth|)^2$$

$$<33> = \mu \cdot Cox(W/L)(1/2)(\Delta Vdata \times C1 / (C1+C2))^2 \quad \dots \quad (4)$$

<34> 여기에서  $\mu$ 는 드라이브 트랜지스터 T1의 다수 캐리어의 이동도,  $Cox$ 는 단위면적당 게이트 용량,  $W$ 는 게이트 폭,  $L$ 은 게이트 길이다. 상기 식 4에 의하면,  $Ioled$ 는 드라이브 트랜지스터 T1의 역치전압  $Vth$ 에 상관없이, 외부에서 주어지는 신호 전압  $\Delta Vdata$ 에 의해 제어된다. 다시 말하면, 도 3의 화소회로는, 화소마다 변동하는 드라이브 트랜지스터의 역치전압  $Vth$ 의 영향을 받지 않고, 전류의 균일성, 나아가서는 휘도의 균일성이 비교적 높은 표시장치를 실현할 수 있다.

<35> 그러나, 상기 식 4에 의하면, 이동도  $\mu$ 가 화소 사이에서 변동한 경우에는, 그것이 즉시 출력전류  $Ioled$ 의 편차가 된다는 것을 알 수 있다. 따라서, 도 4의 타이밍 차트에서는, 데이터 기록 기간 J3 내에 설정된 이동도 보정 기간 J4에, 이동도  $\mu$ 의 편차 보정을 행하고 있다. 보정기간 J4에 단기간 동안 오토 제로선을 저레벨로 하면, 드라이브 트랜지스터 T1 자신을 흐르는 전류에 의해, 드라이브 트랜지스터 T1의 게이트 전위가  $\Delta Vg2$ 만큼 상승한다. 이에 따라, 발광 기간 J5에 드라이브 트랜지스터 T1로부터 발광소자 OLED에 흐르는 전류치가 작아진다. 본 명세서에서는 이 게이트 전위를 압축하는 작용을 부귀환 동작이라고 표현하고 있다. 드라이브 트랜지스터 T1의 이동도  $\mu$ 가 클수록, 이 부귀환 동작에 의해 드라이브 트랜지스터 T1의 게이트 전압  $Vgs$ (게이트/소스간의 전위차)는 더욱 축소된다. 따라서 도 4의 타이밍 차트에 나타낸 이동도 보정동작을 행함으로써 이동도  $\mu$ 의 편차가 보정된다는 것을 알 수 있다.

<36> 상기 부귀환 동작을 지나치게 길게 설정하면, 드라이브 트랜지스터 T1로부터 발광소자 OLED에 흐르는 전류치가 작아지기 때문에, 원하는 휘도를 얻을 수 없게 된다. 따라서, 부귀환 시간은 특정 한계치 이내로 유지해야 한다. 한편, 드라이브 트랜지스터 T1은, OLED를 구동하기 위해서 어느 정도 전류 구동 능력이 큰 것이 보통이다. 용량  $C1$ 이나  $C2$ 는 작은 화소 내에 형성할 필요가 있다. 따라서 용량값에는 한계가 있다. 이로 인해, 전술한 부귀환 동작시에 T1의 게이트 전위의 상승 속도가 커지기 쉽다. 구체적으로는, T1의 전류치는  $1\text{uA}$ ,  $C2$ 의 값은  $500\text{fF}$  정도로 하는 것이 패널 설계상 현실적이다. 이 경우, 부귀환의 시간을  $3\text{us}$ 로 취하면, 게이트 전위의 상승 폭은,

$$<37> \Delta Vg2 = 1\text{uA} \times 3\text{us} / 500\text{fF} = 6[\text{V}]$$

<38> 이 된다. 즉, 부귀환 동작에 의해  $Vgs$ 가  $6\text{V}$ 나 압축되어 버린다. 이 경우, 미리  $Vgs$ 의 압축보다 충분히 큰 진폭으로 데이터선을 구동할 필요가 있다. 그러나, 이것은 소비 전력이나, 데이터선을 구동하는 드라이버의 비용 등의 측면에서 현실적으로 허용되기 어렵다. 이것을 완화하기 위해서 부귀환의 시간을 짧게 할 수 있다. 그러나, 부귀환의 시간을 제어하는 오토 제로선에는 배선 지연이 있다. 그 결과, 특히 패널이 대형화되면, 단시간에 선택·비선택의 동작을 행하는 것은 곤란해진다.

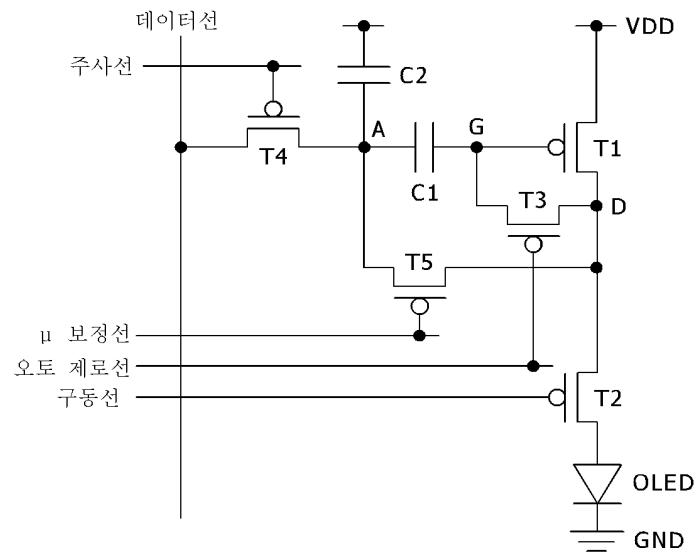

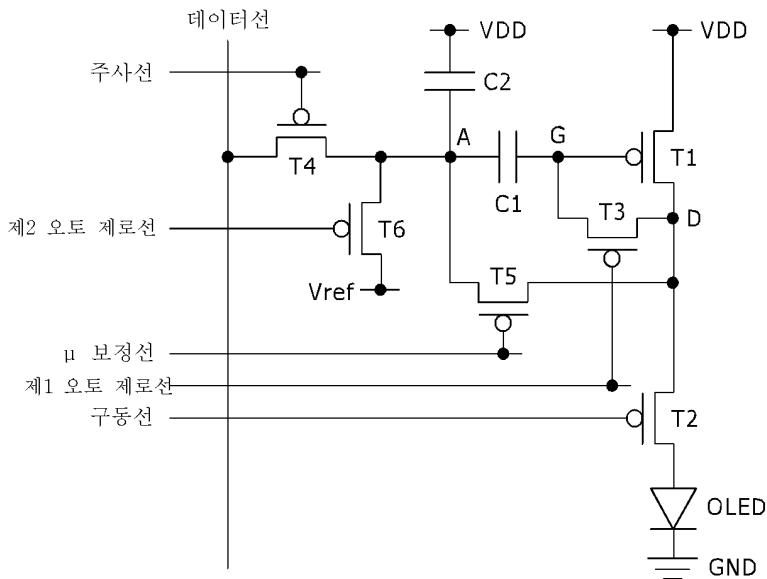

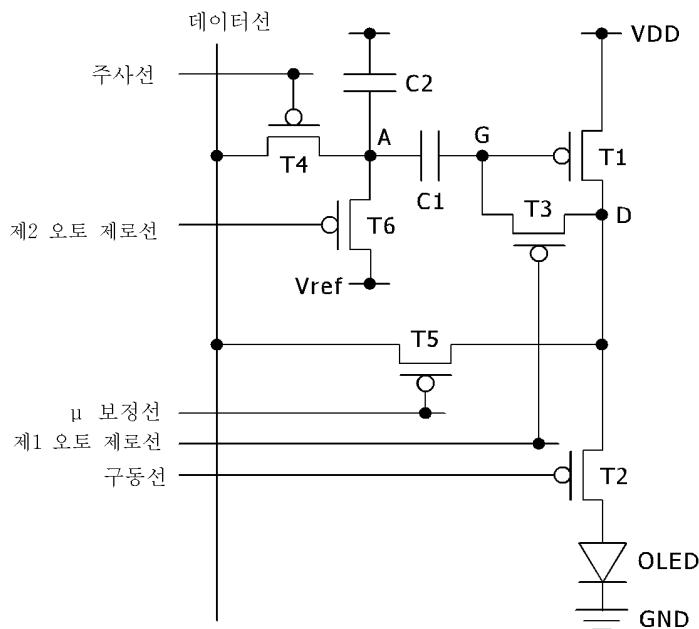

<39> 도 5는, 본 발명의 실시예에 따른 화소회로의 제1 실시예를 나타내는 회로도다. 이해를 쉽게 하기 위해서, 도 3에 나타낸 참고예에 관련된 화소회로와 대응하는 부분에는 대응하는 참조번호를 부여한다. 도시하는 것처럼, 이 화소회로는 5개의 트랜지스터 T1~T5와, 2개의 용량  $C1$  및  $C2$ 와 1개의 발광소자 OLED로 구성되어 있다. 도 4에 나타낸 참고예와 비교하면 분명한 것처럼, 스위칭 트랜지스터 T5가 1개 증가하였다. 이 스위칭 트랜지스터 T5는 부귀환 수단을 구성하고 있고, 오로지 부귀환 동작을 행하기 위해 부가된 디바이스다. 이때, 도 5의 제1 실시예에서는 트랜지스터 T1~T5로서 모두 PMOS를 사용하지만, 본 발명이 이것에 한정되는 것은 아니다. 특히 트랜지

스터 T2~T5는 단순한 스위치이기 때문에, 이것들 모두 또는 일부를 NMOS트랜지스터 혹은 다른 스위칭 디바이스로 대체할 수도 있다.

<40> 이 화소회로는, 기본적으로 제어신호를 공급하는 행 방향의 주사선과 영상신호를 공급하는 열 방향의 데이터선이 교차하는 부분에 배치되어 있다. 화소회로는 적어도 샘플링 트랜지스터 T4와, 드라이브 트랜지스터 T1과, 샘플링 트랜지스터 T4의 전류단과 드라이브 트랜지스터 T1의 게이트 G 사이에 접속된 용량 C1을 포함한다. 화소회로는 또한 이 용량 C1의 일단과 소정의 전원전위 사이에 접속된 용량 C2와, 드라이브 트랜지스터 T1의 전류단(드레인 D)에 접속된 발광소자 OLED를 포함한다. 샘플링 트랜지스터 T4의 게이트는 주사선에 접속된다. 그 샘플링 트랜지스터 T4의 한쪽의 전류단은 데이터선에 접속되고, 다른 한쪽의 전류단은 용량 C1과의 접속점 A가 된다. 샘플링 트랜지스터 T4는 소정의 샘플링 기간에 주사선에서 공급되는 제어신호에 따라 도통해서 데이터선에서 공급된 영상신호를 샘플링한다. 드라이브 트랜지스터 T1은, 샘플링된 영상신호에 따라, 소정의 발광 기간 동안 출력전류를 발광소자 OLED에 공급한다. 발광소자 OLED는, 드라이브 트랜지스터 T1로부터 공급된 출력전류에 의해 영상신호에 따른 휘도로 발광한다. 특징사항으로서, 이 화소회로는 부귀환 수단을 구비하고 있다. 이 부귀환 수단은, 영상신호의 샘플링 기간 내에 설정된 보정기간에 동작하고, 드라이브 트랜지스터 T1의 드레인 D를 샘플링 트랜지스터 T4의 접속점 A에 전기적으로 접속함으로써, 보정기간에 출력전류를 접속점 A에 부귀환해서 드라이브 트랜지스터 T1의 이동도  $\mu$ 의 편차를 보정한다.

<41> 본 실시예에서는 스위칭 트랜지스터 T5가 상기 부귀환 수단을 구성한다. 그 스위칭 트랜지스터 T5는 드라이브 트랜지스터 T1의 드레인 D와, 샘플링 트랜지스터 T4의 접속점 A 사이에 개재한다. 이 스위칭 트랜지스터 T5는, 보정 기간 동안 그 게이트에 인가되는 제어신호에 따라 도통하여, 드라이브 트랜지스터 T1의 드레인 D를, 샘플링 트랜지스터 T4의 접속점 A에 전기적으로 접속한다. 이 화소회로는 드라이브 트랜지스터 T1의 게이트 G와 드레인 D 사이에 접속되어 있는 별도의 스위칭 트랜지스터 T3을 포함하고 있다. 이 스위칭 트랜지스터 T3은 영상 신호의 샘플링에 앞서 온 하여, 드라이브 트랜지스터 T1의 역치전압 Vth에 해당하는 전압을 그 게이트 G에 기록해 둔다.

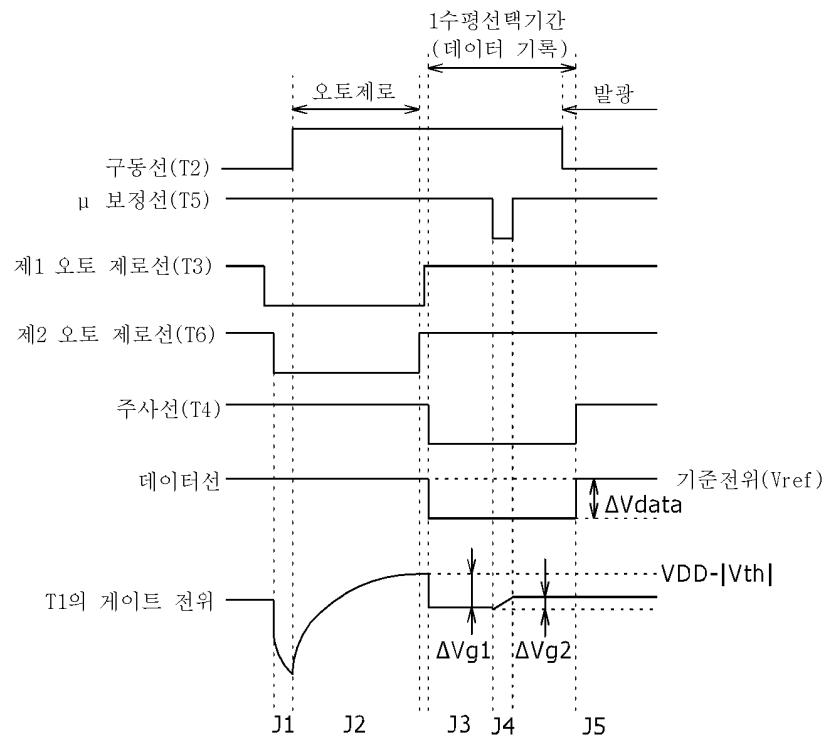

<42> 도 6은, 도 5에 나타낸 화소회로의 동작 설명에 제공하는 타이밍 차트다. 이해를 쉽게 하기 위해서, 도 4에 나타낸 타이밍 차트와 같은 표기를 채용하고 있다. 우선 준비 기간 J1에, 구동선 및 오토 제로선을 저레벨로 함으로써, 스위칭 트랜지스터 T2 및 T3을 도통상태로 한다. 이때 드라이브 트랜지스터 T1은 다이오드 접속된 상태에서 발광소자 OLED와 접속하기 때문에, 드라이브 트랜지스터 T1에 전류가 흐른다.

<43> 다음의 오토 제로 기간 J2에 구동선을 고레벨로 함으로써, 스위칭 트랜지스터 T2를 비도통으로 한다. 이때 주사선은 저레벨이기 때문에, 샘플링 트랜지스터 T4는 도통상태가 되고, 데이터선에는 기준전위 Vref가 주어진다. 드라이브 트랜지스터 T1에 흐르는 전류는 차단되기 때문에, 드라이브 트랜지스터 T1의 게이트 전위는 상승한다. 그러나, 그 전위가  $VDD - |Vth|$ 까지 상승한 시점에 드라이브 트랜지스터 T1은 비도통상태가 되기 때문에, 전위가 안정된다.

<44> 이어서, 데이터 기록 기간 J3에는, 오토 제로선을 고레벨로 해서, 스위칭 트랜지스터 T3을 비도통으로 한다. 또한, 데이터선의 전위를 Vref로부터  $\Delta Vdata$ 만큼 낮은 전위로 한다. 이 데이터선 전위의 변화로 인해 용량 C1을 통해 드라이브 트랜지스터 T1의 게이트 전위가  $\Delta Vg1$ 만큼 하강한다.

<45> 데이터 기록 기간 J3 내에 특별히 설정된 보정기간 J4에는, 스위칭 트랜지스터 T5의 게이트에 접속된  $\mu$ 보정선을 단기간 동안 저레벨로 해서, 스위칭 트랜지스터 T5를 도통상태로 한다. 이때, 전술한 데이터 기록 동작에 의해 드라이브 트랜지스터 T1은 도통상태에 있기 때문에, 드라이브 트랜지스터 T1의 소스로부터 드레인 D를 향해 전류가 흐른다. 이 전류는 스위칭 트랜지스터 T5를 통해 용량 C1의 접속점 A에 부귀환된다. 이에 따라 용량 C1의 입력측 전위가 상승하고, 그 결과 드라이브 트랜지스터 T1의 게이트 전위도 상승한다. 게이트 전위가  $\Delta Vg2$ 만큼 상승한 시점에서,  $\mu$ 보정선은 고레벨이 되어, 스위칭 트랜지스터 T5가 비도통이 된다.

<46> 발광 기간 J5에는, 주사선을 고레벨로 해서 샘플링 트랜지스터 T4를 비도통으로 한다. 구동선은 저레벨로 해서 스위칭 트랜지스터 T2를 도통상태로 한다. 그 결과, 드라이브 트랜지스터 T1 및 발광소자 OLED에 출력전류가 흘러, 발광소자 OLED가 발광을 시작한다. 이때, 전술한 준비 기간 J1, 오토 제로 기간 J2 및 보정기간 J4를 포함한 데이터 기록 기간 J3은, 모두 그 화소에 할당된 1수평선택기간(1H) 내에 할당되어 있다.

<47> 도 5 및 도 6에 나타낸 제1 실시예는, 도 3 및 도 4에 나타낸 참고예와 마찬가지로  $Vth$  편차 캔슬 기능과 이동도  $\mu$  편차 보정 기능을 갖추고 있다. 여기에서, 제1 실시예는 이동도  $\mu$ 의 편차 보정시에, 드라이브 트랜지스터 T1의 전류단(드레인 노드)과, 용량 C1의 입력측 노드가 스위칭 트랜지스터 T5에 의해 전기적으로 접속된다는

점이 큰 특징이다. 이때 샘플링 트랜지스터 T4도 도통상태에 있다. 결과적으로 드라이브 트랜지스터 T1의 드레인과 데이터선이 전기적으로 접속된 상태가 된다. 데이터선은 일반적으로 패널의 상하에 걸쳐 설치되기 때문에, 비교적 큰 기생용량을 가진다. 따라서 이동도  $\mu$ 의 편차 보정시에 드라이브 트랜지스터 T1로부터 흘러나온 전류를 데이터선측에 부귀환할 때, 데이터선 전위가 상승할 때의 속도가 비교적 느린다. 따라서 이 부귀환 동작에서는  $V_{gs}$ 의 압축이 천천히 발생하기 때문에, 그만큼  $\mu$ 보정선에 대한 타이밍 제어도 천천히 행할 수 있다. 따라서 패널이 대형화되어  $\mu$ 보정선의 배선 지연이 증가한 경우에도 안정된  $\mu$  편차 보정동작을 행할 수 있다.

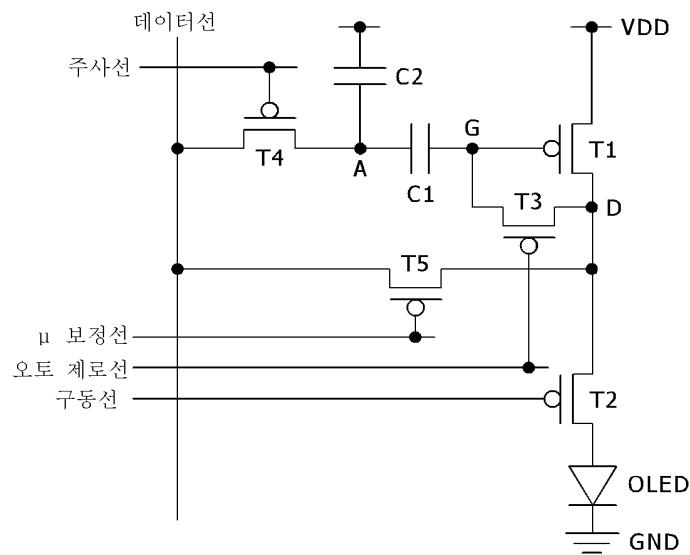

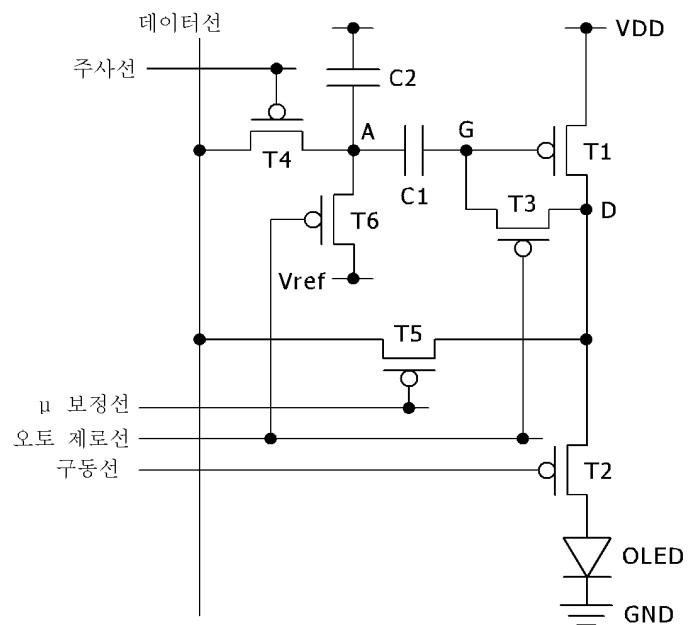

<48> 도 7은, 본 발명의 실시예에 따른 화소회로의 제2 실시예를 나타내는 회로도다. 이해를 쉽게 하기 위해서, 도 5에 나타낸 제1 실시예와 대응하는 부분에는 대응하는 참조번호를 부여한다. 실시예 2는, 부귀환 수단을 구성하는 스위칭 트랜지스터 T5가 드라이브 트랜지스터 T1의 전류단(드레인 D)과 데이터선 사이에 접속된다는 점이 실시예 1과 다르다. 이 스위칭 트랜지스터 T5의 제어단(게이트)은 주사선과 평행하게 배치된  $\mu$ 보정선에 접속되어 있다. 이 스위칭 트랜지스터 T5는, 보정 기간 동안 그 게이트에 인가되는 제어신호에 따라 도통하여, 드라이브 트랜지스터 T1의 드레인 D를, 데이터선을 통해, 또한 샘플링 기간 동안 도통상태에 있는 샘플링 트랜지스터 T4를 통해, 접속점 A에 접속한다. 결과적으로, 접속점 A가 데이터선에 도통한 상태에서 부귀환 동작이 이루어지기 때문에, 제1 실시예와 완전히 같은 효과가 얻어진다.

<49> 도 8은, 도 7에 나타낸 제2 실시예의 동작 설명에 제공하는 타이밍 차트다. 제2 실시예의 동작은 제1 실시예의 동작과 같다. 즉, 데이터 기록 기간 J3 내에 설정된 보정기간 J4에 들어가면,  $\mu$ 보정선을 단기간 동안 저레벨로 해서 스위칭 트랜지스터 T5를 도통상태로 한다. 이때 드라이브 트랜지스터 T1은 온 상태에 있기 때문에, 그 소스로부터 드레인을 향해 전류가 흐른다. 이 전류는 스위칭 트랜지스터 T5를 통해 데이터선에 흘러나간다. 그 결과 데이터선 전위가 상승한다. 또한, 도통상태에 있는 샘플링 트랜지스터 T4를 통해 용량 C1의 입력측 전위도 상승한다. 이에 따라 드라이브 트랜지스터 T1의 게이트 전위가 상승한다. 그 게이트 전위가  $\Delta V_{g2}$ 만큼 상승하면,  $\mu$ 보정선이 고레벨이 되어, 샘플링 트랜지스터 T5는 비도통이 된다.

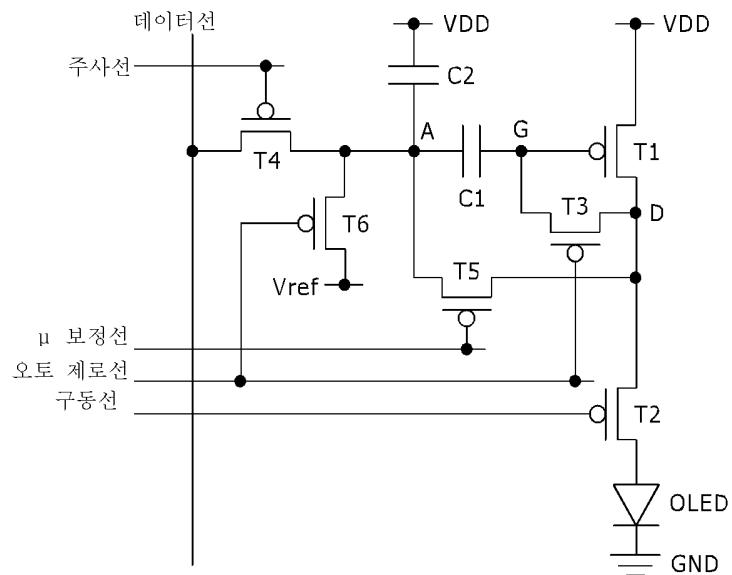

<50> 도 9는, 본 발명의 실시예에 따른 화소회로의 제3 실시예를 나타내는 회로도다. 제3 실시예는 제1 실시예와 기본적으로 유사하다. 제1 실시예와 유사하고, 대응하는 부분에는 대응하는 참조번호를 부착해서 이해를 쉽게 하고 있다. 제3 실시예는, 스위칭 트랜지스터 T6이 부가되어 있다는 점이 실시예 1과 다르다. 이 스위칭 트랜지스터 T6의 한쪽의 전류단은 접속점 A에 접속되고, 다른 쪽의 전류단은 기준전위  $V_{ref}$ 에 접속된다. 스위칭 트랜지스터 T6의 게이트는 제2 오토 제로선에 접속된다. 이때, 이 제2 오토 제로선과 구별하기 위해서, 스위칭 트랜지스터 T3의 게이트에 접속되어 있는 오토 제로선을, 도 9에서는 특별히 제1 오토 제로선이라고 나타낸다.

<51> 도 10은, 도 9에 나타낸 제3 실시예의 동작 설명에 제공하는 타이밍 차트다. 이해를 쉽게 하기 위해서, 도 6에 나타낸 제1 실시예의 타이밍 차트와 같은 표기를 채용하고 있다. 도 5 및 도 6에 나타낸 제1 실시예에서는, 1수평선택기간(1H) 내에 오토 제로 동작 및 데이터 기록 동작을 행할 필요가 있다. 즉, 데이터선의 전위는 기준전위  $V_{ref}$ 와 신호 전위  $V_{data}$  사이에서 전환된다. 따라서, 오토 제로 동작과 데이터 기록 동작을 1수평기간 내에 완료할 필요가 있었다. 반면에, 본 실시예에서는, 데이터선과는 개별적으로 기준전위  $V_{ref}$ 를 접속점 A에 설정하기 위한 스위칭 트랜지스터 T6을 부가하고 있다. 이 스위칭 트랜지스터 T6에 의해, 데이터 기록에 앞서 오토 제로 동작을 행할 수 있다. 따라서 데이터선상의 신호 파형을 단순화할 수 있고, 오토 제로 동작이나 데이터 기록 동작의 시간에 여유가 생긴다. 도 10의 타이밍 차트로부터 분명한 것처럼, 데이터 기록 기간 J3으로서 1수평선택기간(1H)을 모두 이용할 수 있다. 오토 제로 기간 J2는 수평선택기간 이전이면 그 타이밍이나 길이를 자유롭게 설정할 수 있다.

<52> 도 11은, 본 발명의 실시예에 따른 화소회로의 제4 실시예를 나타내는 회로도다. 본 제4 실시예는 기본적으로 도 9에 나타낸 제3 실시예와 유사하고, 그 개량판이다. 본 실시예에서, 스위칭 트랜지스터 T3의 게이트에 접속되는 제1 오토 제로선과, 스위칭 트랜지스터 T6의 게이트에 접속되는 제2 오토 제로선을 공통의 오토제로선으로 통합한다. 이 공통의 오토 제로선으로 스위칭 트랜지스터 T3 및 T6을 동시에 온/오프 제어한다. 이에 따라 주사선과 평행하게 설치하는 제어선의 개수를 줄일 수 있다.

<53> 도 12는, 도 11에 나타낸 제4 실시예의 동작 설명에 제공하는 타이밍 차트다. 오토 제로 기간 J2에, 오토 제로선은 저레벨로 전환된다. 이에 따라 스위칭 트랜지스터 T3과 T6은 같은 타이밍으로 도통상태가 되고, 소정의 오토 제로 동작을 실행한다.

<54> 도 13은, 본 발명의 실시예에 따른 화소회로의 제5 실시예를 나타내는 회로도다. 제5 실시예는 기본적으로 도 7에 나타낸 제2 실시예와 유사하다. 제5 실시예는, 기준전위  $V_{ref}$ 와 접속점 A 사이에 오토 제로용 스위칭 트랜지스터 T6을 추가한다는 점이 제2 실시예와 다르다. 이 점에서 제5 실시예는, 도 9에 나타낸 제3 실시예와 유사한

구성으로 되어 있다. 본 실시예의 동작 타이밍 차트는, 도 10의 동작 타이밍 차트와 같다. 제3 실시예와 마찬가지로, 본 실시예는 데이터 기록에 앞서 오토 제로 동작을 행할 수 있다. 따라서, 데이터선상의 신호 파형을 단순화할 수 있고, 오토 제로 동작이나 데이터 기록 동작의 시간에 여유가 생긴다.

<55> 도 14는, 본 발명의 실시예에 따른 화소회로의 제6 실시예를 나타내는 회로도다. 제6 실시예는, 도 13에 나타낸 제5 실시예와 기본적으로 유사하다. 제6 실시예는, 스위칭 트랜지스터 T3과 T6으로 오토 제로선을 공용화한 점이 제5 실시예와 다르다. 그 점에서 본 제6 실시예는 상기 제4 실시예와 유사하다. 본 실시예에서는 오토 제로선 1개로 오토 제로 제어를 행할 수 있어, 전체적으로 제어선의 개수를 줄일 수 있다.

<56> 첨부된 청구항이나 그 동등 범위에 있는 한, 설계 요구 및 다른 요소에 따라 다양한 변형, 조합, 하부 조합, 변경을 행할 수 있다는 것은 당업자에게 이해된다.

### 도면의 간단한 설명

<57> 도 1은 종래의 화소회로의 일례를 게시하는 회로도다.

<58> 도 2는 본 발명의 실시예에 따른 화소회로를 내장한 화상표시장치의 전체 구성을 나타내는 블럭도다.

<59> 도 3은 화소회로의 참고예를 게시하는 회로도다.

<60> 도 4는 도 3에 나타낸 화소회로의 동작 설명에 제공하는 타이밍 차트다.

<61> 도 5는 본 발명의 실시예에 따른 화소회로의 제1 실시예를 나타내는 회로도다.

<62> 도 6은 제1 실시예의 동작 설명에 제공하는 타이밍 차트다.

<63> 도 7은 본 발명의 실시예에 따른 화소회로의 제2 실시예를 나타내는 회로도다.

<64> 도 8은 제2 실시예의 동작 설명에 제공하는 타이밍 차트다.

<65> 도 9는 본 발명의 실시예에 따른 화소회로의 제3 실시예를 나타내는 화소회로다.

<66> 도 10은 제3 실시예의 동작 설명에 제공하는 타이밍 차트다.

<67> 도 11은 본 발명의 실시예에 따른 화소회로의 제4 실시예를 나타내는 회로도다.

<68> 도 12는 제4 실시예의 동작 설명에 제공하는 타이밍 차트다.

<69> 도 13은 본 발명의 실시예에 따른 화소회로의 제5 실시예를 나타내는 회로도다.

<70> 도 14는 본 발명의 실시예에 따른 화소회로의 제6 실시예를 나타내는 회로도다.

### 도면

#### 도면1

## 도면2

## 도면3

**도면4****도면5**

## 도면6

도면7

## 도면8

## 도면9

## 도면10

## 도면11

## 도면12

## 도면13

## 도면14

|                |                                                                                                                      |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">KR1020080018106A</a>                                                                                     | 公开(公告)日 | 2008-02-27 |

| 申请号            | KR1020070082202                                                                                                      | 申请日     | 2007-08-16 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                                 |         |            |

| [标]发明人         | YUMOTO AKIRA<br>유모토 아키라<br>ASANO MITSURU<br>아사노 미쓰루<br>JINTA SEIICHIRO<br>진타 세이이치로                                   |         |            |

| 发明人            | 유모토 아키라<br>아사노 미쓰루<br>진타 세이이치로                                                                                       |         |            |

| IPC分类号         | G09G3/30 G09G3/20 G09G3/32                                                                                           |         |            |

| CPC分类号         | G09G3/3291 G09G2300/0852 G09G2300/0861 G09G2330/021 G09G2310/06 G09G3/3233 G09G2300/0417 G09G2300/0819 G09G2300/0426 |         |            |

| 代理人(译)         | LEE HWA我                                                                                                             |         |            |

| 优先权            | 2006226754 2006-08-23 JP                                                                                             |         |            |

| 其他公开文献         | <a href="#">KR101413198B1</a>                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                            |         |            |

### 摘要(译)

并且，设置在用于提供控制信号的行方向上的扫描线和用于提供视频信号的列方向上的数据线的部分的像素电路相互交叉，该像素电路包括采样晶体管，驱动晶体管，连接在驱动晶体管的电流端和驱动晶体管的栅极之间的电容器，以及连接到驱动晶体管的电流端的发光元件。