(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) Int. Cl.

H05B 33/22 (2006.01)

(11) 공개번호

10-2007-0041347

(43) 공개일자

2007년04월18일

(21) 출원번호 10-2006-0099204

(22) 출원일자 2006년10월12일

심사청구일자 2006년10월12일

(30) 우선권주장 JP-P-2005-00298943 2005년10월13일 일본(JP)

(71) 출원인 산요덴키가부시키가이샤

일본 오사카후 모리구치시 게이한 혼도오리 2쵸메 5반 5고

(72) 발명자 이케다 교지

일본 기후켄 요로궁 요로쵸 오바 835-33

나카이 신고

일본 아이찌켄 이찌노미야시 오꾸쵸 미나미메구사 43-17

오가와 다까시

일본 기후켄 안파찌궁 안파찌쵸 미나미이마가부찌 556-1 202

우에스기 겐야

일본 기후켄 호즈미시 요꼬야 36-19

(74) 대리인 장수길

구영창

이중희

전체 청구항 수 : 총 11 항

(54) 박막 트랜지스터 및 유기 일렉트로루미네센스 표시 장치

## (57) 요약

본 발명은 외광에 의한 광전류의 발생을 억제함과 함께, 박막 트랜지스터의 특성(예를 들면 임계값)의 변동을 작게 한다. 절연 기판(1)에 아몰퍼스 실리콘을 레이저 어닐에 의해 다결정화해서 이루어지는 능동층(2)(반도체층)이 형성되고, 이 능동층(2) 내에, 서로 대향해서 드레인 영역(2d)과 소스 영역(2s)이 형성되어 있다. 드레인 영역(2d)과 소스 영역(2s)은, 각각 n<sup>-</sup>층과 n<sup>+</sup>층이 인접해서 형성되어 있는 구조를 갖고 있다. 드레인 영역(2d)의 n<sup>-</sup>층과 소스 영역(2s)의 n<sup>-</sup>층 사이에 p형의 채널 영역(2c)이 형성되어 있다. 드레인 영역(2d)의 n<sup>-</sup>층과 채널 영역(2c)의 경계 영역만을 피복해서 형성되고, 절연 기판(1)을 통하여 경계 영역에 입사하는 외광을 차광하기 위한 차광층(3d)이 형성되어 있다.

대표도

도 1

특허청구의 범위

## 청구항 1.

절연 기판 상에 형성된 반도체층과,

상기 반도체층 중에 형성된 제1 도전형의 소스 영역 및 드레인 영역과,

상기 소스 영역과 상기 드레인 영역 사이에 형성된 채널 영역과,

상기 드레인 영역과 상기 채널 영역의 경계 영역만을 피복해서 형성되고, 상기 절연 기판을 통하여 상기 경계 영역에 입사하는 외광을 차광하기 위한 차광층과,

상기 반도체층을 피복해서 형성된 게이트 절연막과,

상기 게이트 절연막 상에 형성된 게이트 전극

을 구비하는 것을 특징으로 하는 박막 트랜지스터.

## 청구항 2.

제1항에 있어서,

상기 차광층은 상기 절연 기판과 상기 반도체층 사이에 형성되고, 또한 상기 차광층과 상기 반도체층 사이에 절연막이끼워져 있는 것을 특징으로 하는 박막 트랜지스터.

## 청구항 3.

제1항 또는 제2항에 있어서,

상기 차광층이 일정 전위로 고정되는 것을 특징으로 하는 박막 트랜지스터.

## 청구항 4.

제1항에 있어서,

상기 드레인층은 저농도 영역과 고농도 영역으로 이루어지고, 상기 차광층은 저농도 영역과 상기 채널 영역의 경계 영역을 피복하고 있는 것을 특징으로 하는 박막 트랜지스터.

## 청구항 5.

제1항에 있어서,

상기 차광층은 크롬 또는 몰리브덴으로 이루어지는 것을 특징으로 하는 박막 트랜지스터.

## 청구항 6.

절연 기판 상에 형성된 반도체층과,

상기 반도체층 중에 형성된 제1 도전형의 소스 영역 및 드레인 영역과,

상기 소스 영역과 상기 드레인 영역 사이에 형성된 채널 영역과,

상기 드레인 영역과 상기 채널 영역의 경계 영역만을 피복해서 형성되고, 상기 절연 기판을 통하여 상기 경계 영역에 입사하는 외광을 차광하기 위한 제1 차광층과,

상기 소스 영역과 상기 채널 영역의 경계 영역만을 피복해서 형성되고, 상기 절연 기판을 통하여 상기 경계 영역에 입사하는 외광을 차광하기 위한 제2 차광층과,

상기 반도체층을 피복해서 형성된 게이트 절연막과,

상기 게이트 절연막 상에 형성된 게이트 전극

을 구비하는 것을 특징으로 하는 박막 트랜지스터.

#### 청구항 7.

제6항에 있어서,

상기 제1 및 제2 차광층은 상기 절연 기판과 상기 반도체층 사이에 형성되고, 또한 상기 제1 및 제2 차광층과 상기 반도체층 사이에 절연막이 끼워져 있는 것을 특징으로 하는 박막 트랜지스터.

#### 청구항 8.

제6항 또는 제7항에 있어서,

상기 제1 및 제2 차광층이 일정 전위로 고정되어 있는 것을 특징으로 하는 박막 트랜지스터.

#### 청구항 9.

제6항에 있어서,

상기 제1 차광층 및 상기 제2 차광층은 크롬 또는 몰리브덴으로 이루어지는 것을 특징으로 하는 박막 트랜지스터.

#### 청구항 10.

절연 기판 상에 형성되고, 상기 절연 기판을 통하여 광을 방사하는 유기 일렉트로루미네센스 소자와,

상기 유기 일렉트로루미네센스 소자를 구동하는 구동 트랜지스터

를 구비하고,

상기 구동 트랜지스터는, 상기 절연 기판 상에 형성된 반도체층과, 상기 반도체층 중에 형성된 제1 도전형의 소스 영역 및 드레인 영역과, 상기 소스 영역과 상기 드레인 영역 사이에 형성된 채널 영역과, 상기 드레인 영역과 상기 채널 영역의 경계 영역만을 피복해서 형성되고, 상기 절연 기판을 통하여 상기 경계 영역에 입사하는 외광을 차광하기 위한 차광층과, 상기 반도체층을 피복해서 형성된 게이트 절연막과, 상기 게이트 절연막 상에 형성된 게이트 전극을 구비하는

것을 특징으로 하는 유기 일렉트로루미네센스 표시 장치.

## 청구항 11.

제10항에 있어서,

상기 차광층은 상기 절연 기판과 상기 반도체층 사이에 형성되고, 또한 상기 차광층과 상기 반도체층 사이에 절연막이 끼워져 있는 것을 특징으로 하는 유기 일렉트로루미네센스 표시 장치.

명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 박막 트랜지스터 및 유기 일렉트로루미네센스 표시 장치에 관한 것이다.

최근, CRT나 LCD를 대신하는 표시 장치로서, 자발광 소자인 유기 일렉트로루미네센스 소자(이하, 「유기 EL 소자」라고 약칭함)를 이용한 유기 EL 표시 장치가 개발되고 있다. 특히, 비디오 신호에 따라 유기 EL 소자를 구동하는 구동 트랜지스터를 화소마다 구비한 액티브 매트릭스형의 유기 EL 표시 장치가 개발되고 있다.

이 구동 트랜지스터는, 클래스 기판 상에 형성된 박막 트랜지스터로 이루어진다. 이 때문에, 이 클래스 기판을 통하여 유기 EL 소자로부터의 광이 방사되는 보텀 에미션형의 유기 EL 표시 장치에서는, 클래스 기판을 통하여 외광이 박막 트랜지스터의 능동층에 입사한다. 그렇게 하면, 이 외광이 능동층 내에서 캐리어를 여기하여, 소스 드레인 간에 광전류(리크 전류)가 흘러, 표시 콘트라스트가 열화된다고 하는 문제가 있었다.

따라서, 특히 문헌 1에 기재되어 있는 바와 같이, 박막 트랜지스터의 능동층에 입사하는 외광을 차광하는 차광층을 형성함으로써, 광전류의 생성을 억지하도록 한 기술이 알려져 있다.

#### 발명이 이루고자 하는 기술적 과제

그러나, 종래의 박막 트랜지스터에서는, 차광층의 전위가 박막 트랜지스터의 특성(예를 들면, 임계값 전압)에 큰 영향을 미친다. 따라서, 차광층의 전위를 고정하는 것이 생각되지만, 그와 같이 하여도, 트랜지스터에 부수되는 pn접합의 순방향 전류나 킥백 전류(드레인으로부터 게이트로의 리크 전류)의 영향을 받게 된다. 한편, 차광층의 전위를 고정하지 않으면, 대전에 의해, 차광층의 전위가 불안정해져, 트랜지스터 특성이 더 불안정하게 된다고 하는 문제가 있었다. 또한, 이러한 박막 트랜지스터를 유기 EL 표시 장치의 구동 트랜지스터로서 이용하면, 그 표시 품위가 열화된다고 하는 문제가 있었다.

#### 발명의 구성

본 발명의 박막 트랜지스터는, 절연 기판 상에 형성된 반도체층과, 상기 반도체층 중에 형성된 제1 도전형의 소스 영역 및 드레인 영역과, 상기 소스 영역과 상기 드레인 영역 사이에 형성된 채널 영역과, 상기 드레인 영역과 상기 채널 영역의 경계 영역만을 피복해서 형성되고, 상기 절연 기판을 통하여 상기 경계 영역에 입사하는 외광을 차광하기 위한 차광층과, 상기 반도체층을 피복해서 형성된 게이트 절연막과, 상기 게이트 절연막 상에 형성된 게이트 전극을 구비하는 것을 특징으로 하는 것이다.

본 발명은, 외광의 영향에 의해 광전류가 생성되는 주된 영역은, 역바이어스 상태로 되는 드레인 영역과 채널 영역의 경계 영역인 것에 주목하여, 그 경계 영역만을 피복하는 차광층을 형성한 것이다. 이에 의해, 광전류의 발생이 억지됨과 함께, 박막 트랜지스터의 특성(예를 들면 임계값)의 변동을 작게 할 수 있다.

또한, 본 발명의 유기 일렉트로루미네센스 표시 장치는, 절연 기판 상에 형성되어, 상기 절연 기판을 통하여 광을 방사하는 유기 일렉트로루미네센스 소자와, 상기 유기 일렉트로루미네센스 소자를 구동하는 박막 트랜지스터를 구비하고, 상기 박막 트랜지스터는, 상기 절연 기판 상에 형성된 반도체층과, 상기 반도체층 내에 형성된 제1 도전형의 소스 영역 및 드레인 영역과, 상기 소스 영역과 상기 드레인 영역 사이에 형성된 채널 영역과, 상기 드레인 영역과 상기 채널 영역의 경계영역만을 피복해서 형성되고, 상기 절연 기판을 통하여 상기 경계 영역에 입사하는 외광을 차광하기 위한 차광층과, 상기 반도체층을 피복해서 형성된 게이트 절연막과, 상기 게이트 절연막 상에 형성된 게이트 전극을 구비하는 것을 특징으로 하는 것이다.

### <실시예>

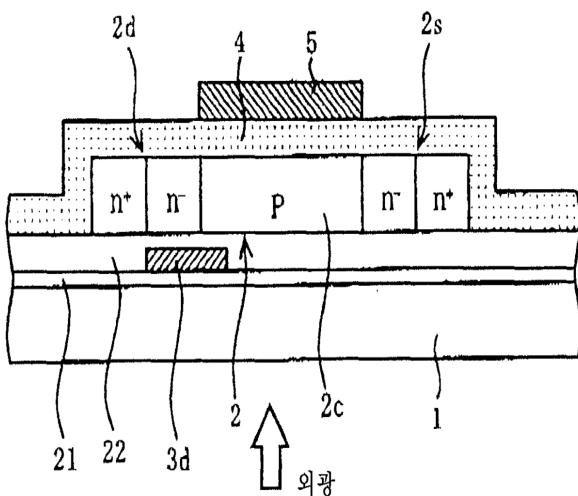

다음으로, 본 발명의 제1 실시예에 따른 박막 트랜지스터에 대해서 도면을 참조하여 설명한다. 도 1은 제1 실시예에 따른 박막 트랜지스터의 단면도이다. 석영 글래스, 무알칼리 글래스 등으로 이루어지는 절연 기판(1)에 아몰퍼스 실리콘을 레이저 어닐에 의해 다결정화해서 이루어지는 능동층(2)(반도체층)이 형성되고, 이 능동층(2) 내에, 서로 대향해서 드레인 영역(2d)과 소스 영역(2s)이 형성되어 있다. 드레인 영역(2d)과 소스 영역(2s)는 소위 LDD(Lightly doped drain) 구조를 갖고 있고, 즉, 각각  $n^-$ 층과  $n^+$ 층이 인접해서 형성되어 있는 구조를 갖고 있다. 드레인 영역(2d)의  $n^-$ 층과 소스 영역(2s)의  $n^-$ 층 사이에 p형의 채널 영역(2c)이 형성되어 있다.

그리고, 드레인 영역(2d)의  $n^-$ 층과 채널 영역(2c)의 경계 영역만을 피복해서 형성되고, 절연 기판(1)을 통하여 경계 영역에 입사하는 외광을 차광하기 위한 차광층(3d)이 형성되어 있다. 차광층(3d)은 절연 기판(1)과 능동층(2) 사이에 끼워져 형성되어 있고, 크롬이나 몰리브덴과 같은 금속으로 이루어진다. 또한, 차광층(3d)은 절연 기판(1) 상의 버퍼 절연막(21)에 형성되고, 또한, 차광층(3d)과 능동층(2) 사이에는 절연막(22)이 끼워져 있다. 또한, 능동층(2)을 피복해서  $\text{SiO}_2$  등의 절연물로 이루어지는 게이트 절연막(4)이 형성되고, 이 절연막 상에 크롬이나 몰리브덴 등으로 이루어지는 게이트 전극(5)이 형성되어 있다.

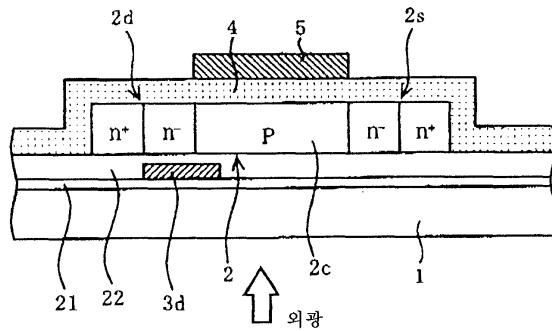

도 2은 본 실시예의 박막 트랜지스터와 대비되는 박막 트랜지스터의 단면도이다. 도 1의 본 실시예의 박막 트랜지스터의 차광층(3d)이 드레인 영역(2d)과 채널 영역(2c)의 경계 영역만을 피복하도록 형성되어 있는 것에 대해서, 도 2의 박막 트랜지스터의 차광층(3a)은 능동층(2)을 실질적으로 전면 차광하도록 형성되어 있다. 이하에서는, 제1 실시예의 박막 트랜지스터를 「드레인 차광」의 박막 트랜지스터, 이와 대비되는 도 2의 박막 트랜지스터를 「전면 차광」의 박막 트랜지스터라고 칭하는 것으로 한다.

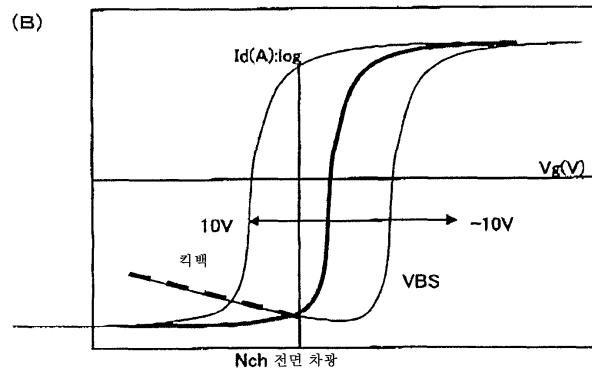

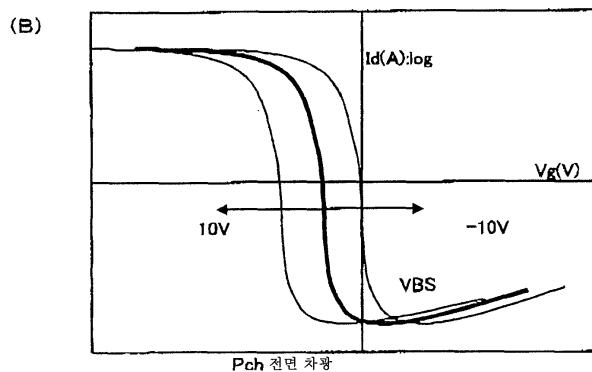

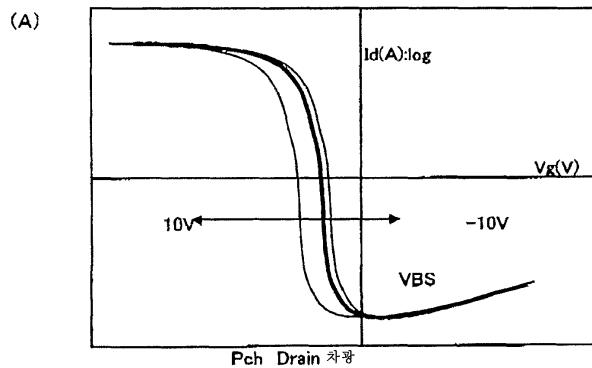

도 4는, 상술한 2개의 박막 트랜지스터의 드레인 전류대 게이트 전압 특성을 대비한 도면으로, 도 4의 (A)는 드레인 차광의 박막 트랜지스터의 특성, 도 4의 (B)는 전면 차광의 박막 트랜지스터의 특성을 도시하고 있다. 도 4에서,  $Id(A)$ 는 드레인 전류,  $Vg(V)$ 은 게이트 전압, VBS는 차광층(3d, 3a)과 소스 영역(2s) 간에 걸친 전압이다. VBS는  $-10V \sim 10V$  사이에서 변화시키고 있다. VBS가 마이너스일 때에는 드레인 영역(2d) 또는 소스 영역(2s)의  $n^-$ 층과 p형의 채널 영역(2c)의 pn 접합이 역바이어스로 되고, VBS가 플러스일 때에는 상기 pn 접합은 순바이어스되는 것으로 된다.

도 4의 (B)로부터 명확해지는 바와 같이, 전면 차광의 박막 트랜지스터의 드레인 전류대 게이트 전압 곡선은 VBS가 마이너스 방향으로 변화되면 우측으로 크게 시프트하고, 플러스 방향으로 변화되면 좌측으로 크게 시프트한다. VBS가 플러스인 영역에서는, pn 접합이 순바이어스되기 때문에 순방향 전류가 흐른다. 즉, VBS에 의해 임계값이 흙들리게 된다. 또한,  $VBS < -8V$ 의 영역에서는, 트랜지스터가 오프의 영역( $Vg(V) < 0V$ )에서 킥백 전류가 흐르게 된다.

이에 대하여, 드레인 차광 박막 트랜지스터는, 도 4의 (A)로부터 명확해지는 바와 같이, 드레인 전류쌍 게이트 전압 곡선의 VBS의 변화에 의한 시프트는 매우 작다. 또한, VBS가 마이너스 방향으로 변화되면 임계값은 약간 커지지만, 킥백 전류는 흐르지 않는다. VBS가 마이너스 방향으로 변화되어도 임계값은 거의 변화하지 않아, 순방향 전류도 흐르지 않는다.

이와 같이, 전면 차광의 박막 트랜지스터의 특성은 차광층(3a)의 전위가 변화되면 크게 변동되게 되는 것에 대해서, 본 발명의 드레인 차광의 박막 트랜지스터에서는, 차광층(3d)의 전위가 변화되어도 그 특성 변동이 억제된다.

또한, 외광의 영향에 의해 광전류가 생성되는 주된 영역은, 트랜지스터의 사용상, pn접합이 역바이어스 상태로 되는 드레인 영역(2d)과 채널 영역(2c)의 경계영역이기 때문에, 이 영역만을 피복하는 차광층(3d)에 의해 광전류의 발생을 충분히 억지할 수 있다. 또한, 차광층(3d)의 전위는 일정 전위, 예를 들면 접지 전위V<sub>SS</sub>로 고정해 두는 것이, VBS의 변화를 가능한 만큼 억제하여, 트랜지스터의 특성 변동을 억제하기 위해 바람직하다.

본 실시예에서, 박막 트랜지스터의 바이어스 상태로서, 드레인 영역(2d)에 부수되는 pn접합이 역바이어스되고, 소스 영역(2s)에 부수된 pn접합은 역바이어스되지 않는 것을 전제로 하고 있다. 따라서, 그 역의 바이어스 상태도 발생하는 경우, 즉, 소스 영역(2s)에 부수되는 pn접합이 역바이어스되는 경우에는 거기서 광전류가 발생해버리기 때문에, 드레인 차광에서는, 광전류의 억제 효과는 얻어지지 않는다.

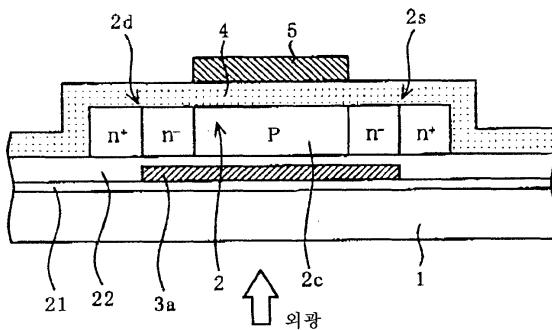

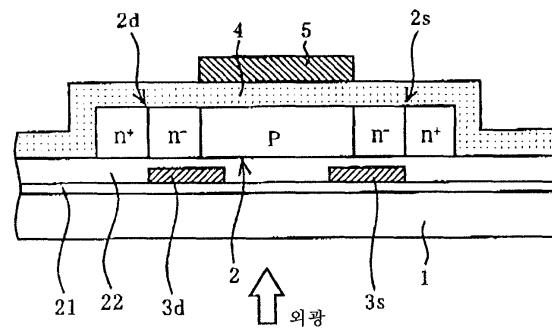

따라서, 제2 실시예의 박막 트랜지스터에서는, 도 3에 도시한 바와 같이, 드레인 영역측의 차광층(3d)(제1 차광층) 외에, 소스 영역(2s)측에도, 마찬가지로, 소스 영역(2s)과 채널 영역(2c)의 경계 영역만을 피복하는 차광층(3s)(제2 차광층)을 형성하였다. 이 차광층(3s)과 능동층(2) 사이에도 절연막(22)이 끼워져 있다.

이 박막 트랜지스터에 의하면, 드레인 영역(2d)에 부수되는 pn접합이 역바이어스되는 경우와, 소스 영역(2s)에 부수된 pn접합은 역바이어스되는 경우의 양방에 대해, 광전류의 발생을 억지하는 효과를 발휘한다. 또한, 전면 차광하고 있지 않기 때문에, 차광층(3d), 차광층(3s)의 전위의 변화에 대한 특성 변동도 어느 정도 억제된다.

상술한 제1 및 제2 실시예는, N채널형의 박막 트랜지스터에 관한 것인데, P채널형의 박막 트랜지스터에 대해서도 마찬가지의 차광층을 형성함으로써, 트랜지스터의 특성 변동을 억지할 수 있다. 즉, 도 5에 도시한 바와 같이, 드레인 차광의 박막 트랜지스터(도 5의 (A) 쪽이), 전면 차광의 박막 트랜지스터(도 5의 (B))에 비해, VBS에 의한 드레인 전류대 계이트 전압 특성 커프의 시프트량이 작게 억제되어 있다.

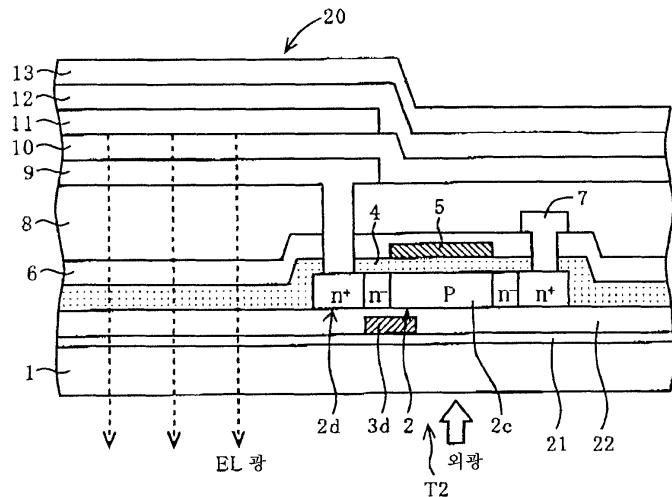

다음으로, 본 발명의 박막 트랜지스터를 이용한 유기 EL 표시 장치에 대해 설명한다. 도 6은, 보텀 에미션형의 유기 EL 표시 장치의 화소의 단면도이다. 제1 실시예의 드레인 차광의 박막 트랜지스터가 유기 EL 소자(20)의 구동 트랜지스터 T2로서 이용되어 있다. 이하, 이 유기 EL 표시 장치의 화소의 구조에 대해 자세히 설명한다.

절연 기판(1) 상에 드레인 차광의 구동 트랜지스터 T2가 형성되고, 이것을 피복해서 SiO<sub>2</sub>막, SiN막 및 SiO<sub>2</sub>막의 순으로 적층된 층간 절연막(6)이 형성되어 있다. 소스 영역(2d)에 대응해서 형성한 컨택트홀에 Al 등의 금속을 충전해서 구동 전원 전위 PVdd에 접속된 구동 전원선(7)이 배치되어 있다. 또한, 전면에 예를 들면 유기 수지로 이루어져 표면을 평탄하게 하는 평탄화 절연막(8)이 형성되어 있다.

또한, 평탄화 절연막(8)에 소스 영역(2s)에 대응한 위치에 컨택트홀이 형성되고, 이 컨택트홀을 통하여 소스 영역(2s)과 컨택트한 ITO(Indium Tin Oxide) 또는, IZO(Indium Zinc Oxide)로 이루어지는 투명 전극, 즉 유기 EL 소자(20)의 애노드층(9)이 평탄화 절연막(8) 상에 형성되어 있다. 이 애노드층(9)은 각 화소마다 섬 형상으로 분리 형성되어 있다.

유기 EL 소자(20)는, 상기 애노드층(9), MYDATA(4, 4-bis(3-methylphenylphenylamino)biphenyl)로 이루어지는 제1 홀 수송층, TPD(4, 4, 4-tris(3-methylphenylphenylamino)triphenylamine)로 이루어지는 제2 홀 수송층으로 이루어지는 홀 수송층(10), 퀴나크리돈(Quinacridone) 유도체를 포함하는 Bebq2(10-멘조 [h] 퀴놀리놀-베릴륨 작체)로 이루어지는 발광층(11) 및 Bebq로 이루어지는 전자 운송층(12), 마그네슘 인듐 합금 혹은 알루미늄, 혹은 알루미늄 합금으로 이루어지는 캐소드층(13)이, 이 순서로 적층 형성된 구조이다.

캐소드층(13)은, 발광층(11)을 피복하여, 화소 영역 전체로 연장되고 있다. 유기 EL 소자(20)는, 애노드층(9)으로부터 주입된 홀과, 캐소드층(13)으로부터 주입된 전자가 발광층(11)의 내부에서 재결합하여, 발광층(11)을 형성하는 유기 분자를 여기해서 여기자가 발생한다. 여기자가 방사해서 비활성화하는 과정에서 발광층(11)으로부터 광이 방출되고, 이 광이 투명한 애노드층(9)으로부터 투명, 혹은 반투명의 절연 기판(1)을 투과해서 외부로 방사되어 발광한다.

상술한 유기 EL 표시 장치에 의하면, 박막 트랜지스터의 드레인 영역에 차광층(3d)이 형성되어 있기 때문에, 외광에 의한 광전류(오프 리크 전류)의 발생을 억지하여, 표시 콘트라스트를 향상할 수 있음과 함께, 박막 트랜지스터의 특성 변동(예를 들면, 임계치의 변동)을 작게 할 수 있다.

도 7은, 이 유기 EL 표시 장치의 1화소의 회로도이다. 이 회로에서는, 구동 트랜지스터 T2 외에 화소 선택 트랜지스터 T1이 도시되어 있다. 화소 선택 트랜지스터 T1은, 게이트 라인 CL의 게이트 신호에 따라 온 상태로 되고, 비디오 신호 Vsig를 구동 트랜지스터 T1의 게이트에 전달한다. Cs는 비디오 신호 Vsig를 유지하기 위한 축적 용량이다. 이 예에서는, 화소 선택 트랜지스터 T1은 N채널형, 구동 트랜지스터 T2는 P채널형이다.

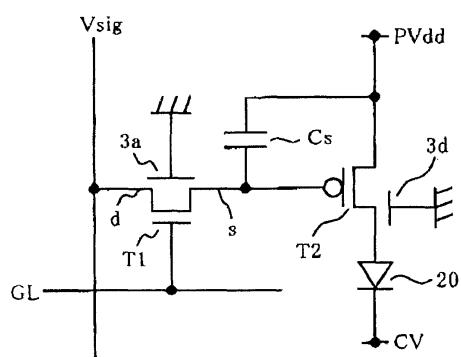

10만 룹스 정도의 외광이 닿으면, 화소 선택 트랜지스터 T1에도 광전류(오프 리크 전류)가 발생하여, 구동 트랜지스터 T2의 게이트에 유지된 전하가 누설되어버린다. 이 때문에, 화소의 세로 방향 간섭, 즉 크로스 토크에 의한 표시 불량이 발생한다. 그 때문에, 화소 선택 트랜지스터 T1에 대해서도 차광층을 형성할 필요가 있다. 화소 선택 트랜지스터 T1에서는, 드레인 d에 부수되는 pn접합이 역바이어스되는 경우와, 소스 s에 부수된 pn접합은 역바이어스되는 경우의 양방이 발생하므로, 드레인 d와 소스 s의 한쪽만을 차광했다는 것으로는 외광의 차광 효과가 얻어지지 않는다. 따라서, 도 7의 회로에서는, 전면 차광의 차광층(3a)을 형성하고 있다. 전면 차광에서는, 상술된 바와 같이 임계값의 변동이 커지지만, 게이트 신호의 하이 레벨의 전압이 임계값에 대하여 상당히 높은 경우에는, 그 변동의 영향은 작다.

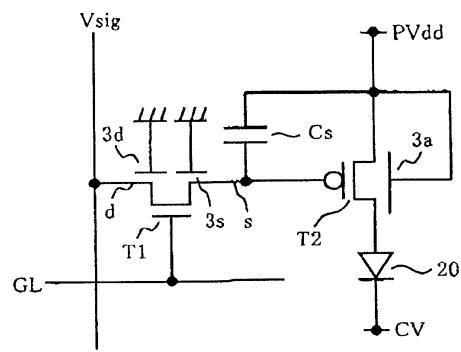

또한, 도 8과 같이, 제2 실시예에 따라, 드레인 차광의 차광층(3d)과 소스 차광의 차광층(3s)(도3 참조)을 형성하여도 된다. 도 8의 회로에서는, 구동 트랜지스터 T2에 전면 차광의 차광층(3a)이 형성되어 있다. 이 경우에도, 구동 트랜지스터 T2의 임계값의 변동은 커지지만, 비디오 신호 Vsig의 하이 레벨의 전압이 임계값에 대하여 상당히 높은 경우에는 그 변동의 영향은 작다.

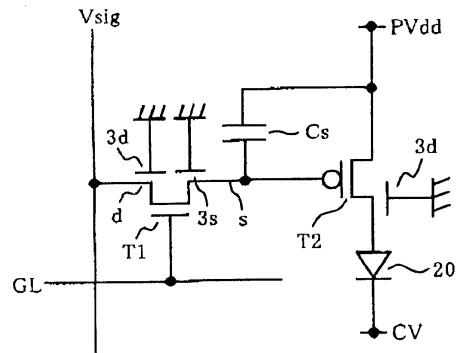

가장 바람직한 회로로서는, 도 9에 도시한 바와 같이, 구동 트랜지스터 T2에 대해서는, 드레인 차광의 차광층(3d)을 형성하고, 화소 선택 트랜지스터 T1에 대해서는, 드레인 차광의 차광층(3d)과 소스 차광의 차광층(3s)(도 3 참조)을 형성하는 것이다. 이에 의해, 구동 트랜지스터 T2와 화소 선택 트랜지스터 T1의 양방에 대해, 외광에 의한 광 전류(오프 리크 전류)의 발생을 억지하여, 표시 콘트라스트를 향상할 수 있음과 함께, 게이트 신호나 비디오 신호 Vsig의 레벨에 관계없이, 트랜지스터의 특성 변동(예를 들면, 임계값의 변동)을 작게 할 수 있다고 하는 효과가 얻어진다.

### 발명의 효과

본 발명의 박막 트랜지스터에 의하면, 외광에 의한 광전류의 발생을 억지할 수 있음과 함께, 박막 트랜지스터의 특성(예를 들면 임계값)의 변동을 작게 할 수 있다. 특히, 킥백 전류를 억지할 수 있음과 함께, 순방향 전류에 관해서도 억지할 수 있다.

또한, 본 발명의 일렉트로루미네센스 표시 장치에 의하면, 상기 박막 트랜지스터에서 유기 일렉트로루미네센스 소자를 구동하고 있기 때문에, 그 표시 콘트라스트를 향상할 수 있다.

### 도면의 간단한 설명

도 1은 본 발명의 제1 실시예에 따른 박막 트랜지스터의 단면도.

도 2는 본 발명의 박막 트랜지스터와 대비되는 박막 트랜지스터의 단면도.

도 3은 본 발명의 제2 실시예에 따른 박막 트랜지스터의 단면도.

도 4는 N채널형의 박막 트랜지스터의 드레인 전류대 게이트 전압의 특성 곡선을 도시하는 도면.

도 5는 P채널형의 박막 트랜지스터의 드레인 전류대 게이트 전압의 특성 곡선을 도시하는 도면.

도 6은 본 발명의 실시예에 따른 유기 EL 표시 장치의 화소의 단면도.

도 7은 본 발명의 실시예에 따른 박막 트랜지스터를 이용한 유기 EL 표시 장치의 1화소의 제1 회로도.

도 8은 본 발명의 실시예에 따른 박막 트랜지스터를 이용한 유기 EL 표시 장치의 1화소의 제2 회로도.

도 9는 본 발명의 실시예에 따른 박막 트랜지스터를 이용한 유기 EL 표시 장치의 1화소 제3 회로도.

<도면의 주요 부분에 대한 부호의 설명>

1: 절연 기판

2: 능동층

2d: 드레인 영역

2s: 소스 영역

2c: 채널 영역

3d, 3s: 차광층

4: 게이트 절연막

5: 게이트 전극

6: 층간 절연막

7: 구동 전원선

8: 평탄화 절연막

9: 애노드층

10: 홀 수송층

11: 발광층

12: 전자 수송층

13: 캐소드층

20: 유기 EL 소자

21: 벼파 절연막

22: 절연막

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

## 도면9

|                |                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管和有机电致发光显示装置                                                                                   |         |            |

| 公开(公告)号        | <a href="#">KR1020070041347A</a>                                                                   | 公开(公告)日 | 2007-04-18 |

| 申请号            | KR1020060099204                                                                                    | 申请日     | 2006-10-12 |

| [标]申请(专利权)人(译) | 三洋电机株式会社<br>山洋电气株式会社                                                                               |         |            |

| 申请(专利权)人(译)    | 三洋电机有限公司是分租                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 三洋电机有限公司是分租                                                                                        |         |            |

| [标]发明人         | IKEDA KYOJI<br>이케다교지<br>NAKAI SHINGO<br>나카이신고<br>OGAWA TAKASHI<br>오가와다까시<br>UESUGI KENYA<br>우에스기겐야 |         |            |

| 发明人            | 이케다교지<br>나카이신고<br>오가와다까시<br>우에스기겐야                                                                 |         |            |

| IPC分类号         | H05B33/22                                                                                          |         |            |

| CPC分类号         | H01L27/3272 H01L29/78621 H01L51/5284 H01L29/78633                                                  |         |            |

| 代理人(译)         | LEE , JUNG HEE<br>CHANG, SOO KIL                                                                   |         |            |

| 优先权            | 2005298943 2005-10-13 JP                                                                           |         |            |

| 其他公开文献         | KR100742494B1                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                          |         |            |

## 摘要(译)

用途：提供薄膜晶体管和有机电致发光显示装置，以防止外部光产生光电流，并减少薄膜晶体管的特性变化。