(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2009년03월19일

(11) 등록번호 10-0889681

(24) 등록일자 2009년03월12일

(51) Int. Cl.

G09G 3/30 (2006.01) G09G 3/32 (2006.01)

G09G 3/20 (2006.01) G01R 19/00 (2006.01)

(21) 출원번호 10-2007-0075430

(22) 출원일자 2007년07월27일

심사청구일자 2007년07월27일

(65) 공개번호 10-2009-0011638

(43) 공개일자 2009년02월02일

(56) 선행기술조사문현

JP2005309230 A

KR1020060029062 A

JP2005258427 A

JP2005128272 A

전체 청구항 수 : 총 36 항

심사관 : 조기덕

(54) 유기전계발광 표시장치 및 그의 구동방법

**(57) 요약**

본 발명은 유기 발광 다이오드의 열화를 보상할 수 있도록 한 유기전계발광 표시장치에 관한 것이다.

본 발명의 유기전계발광 표시장치는 유기 발광 다이오드 및 상기 유기 발광 다이오드로 전류의 공급유무를 제어하는 화소회로를 포함하는 화소들과; 센싱 기간 동안 상기 화소들 각각에 포함되는 유기 발광 다이오드로 제 1전류를 공급하면서 상기 유기 발광 다이오드에 인가되는 전압을 디지털 값으로 변환하고, 샘플링 기간 동안 상기 디지털 값에 대응하여 상기 유기 발광 다이오드가 보상될 수 있는 제 2전류를 상기 화소로부터 성크하기 위한 센싱부를 구비하며; 상기 제 2전류는 1(1은 자연수)개의 전류값 중 데이터의 비트에 대응하여 선택된 전류값과 상기 유기 발광 다이오드의 열화가 보상될 수 있는 전류를 포함하는 전류이다.

**대표도** - 도4

## 특허청구의 범위

### 청구항 1

유기 발광 다이오드 및 상기 유기 발광 다이오드로 전류의 공급유무를 제어하는 화소회로를 포함하는 화소들과;

센싱 기간 동안 상기 화소들 각각에 포함되는 유기 발광 다이오드로 제 1전류를 공급하면서 상기 유기 발광 다이오드에 인가되는 전압을 디지털 값으로 변환하고, 샘플링 기간 동안 상기 디지털 값에 대응하여 상기 유기 발광 다이오드가 보상될 수 있는 제 2전류를 상기 화소로부터 싱크하기 위한 센싱부를 구비하며;

상기 제 2전류는 1(1은 자연수)개의 전류값 중 데이터의 비트에 대응하여 선택된 전류값과 상기 유기 발광 다이오드의 열화가 보상될 수 있는 전류를 포함하는 전류인 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 2

제 1항에 있어서,

상기 센싱부는

상기 제 1전류를 공급하기 위한 전류 소스부와,

상기 제 2전류를 싱크하기 위한 전류 디지털-아날로그 변환부와,

상기 전류 소스부 및 전류 디지털-아날로그 변환부를 상기 화소와 접속되는 피드백선과 선택적으로 접속시키기 위한 스위칭부와,

상기 전류 소스부와 접속되어 상기 유기 발광 다이오드에 인가되는 전압을 상기 디지털 값으로 변환하기 위한 아날로그-디지털 변환부와,

상기 디지털 값을 저장하기 위한 메모리와,

상기 메모리에 저장되는 디지털 값에 대응하여 상기 유기 발광 다이오드의 열화가 보상될 수 있도록 상기 전류 디지털-아날로그 변환부를 제어하기 위한 제어부를 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 3

제 2항에 있어서,

상기 전류 소스부, 스위칭부 및 전류 디지털-아날로그 변환부는 채널마다 위치되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 4

제 2항에 있어서,

상기 스위칭부는

상기 피드백선과 상기 전류 소스부 사이에 위치되는 제 1스위치와,

상기 피드백선과 상기 전류 디지털-아날로그 변환부 사이에 위치되는 제 2스위치를 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 5

제 4항에 있어서,

상기 제 1스위치는 상기 센싱 기간 동안 턴-온되고, 상기 제 2스위치는 상기 샘플링 기간 동안 턴-온되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 6

제 2항에 있어서,

상기 전류 디지털-아날로그 변환부는

상기 데이터의 계조에 대응하여 나누어진 상기 1개의 전류값 중 제일 낮은 계조에 대응하는 제 3전류를 생성하기 위한 제 1전류 생성부와,

상기 제 1전류 생성부로부터 공급되는 제 3전류에 대응하여 제 2전류 생성부로부터 상기 제 3전류를 싱크하기 위한 제 1전류 싱크부와,

상기 제 1전류 생성부로부터 공급되는 상기 제 3전류에 대응하여 상기 유기 발광 다이오드의 열화가 보상될 수 있는 제 4전류를 상기 제 2전류 생성부로부터 싱크하기 위한 제 2전류 싱크부와,

상기 제 1전류 싱크부 및 제 2전류 싱크부에서 싱크되는 상기 제 3전류 및 제 4전류에 대응하는 제 5전류를 생성하기 위한 제 2전류 생성부와,

상기 제 2전류 생성부로부터 공급되는 제 5전류를 상기 데이터의 계조에 대응하여  $\beta$  ( $\beta$ 는 1, 2, 3, ...)배로 상승하여 상기 제 2전류를 생성하고, 상기 제 2전류를 상기 피드백선으로부터 싱크하기 위한 제 3전류 싱크부를 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 7

제 6항에 있어서,

상기 제 1전류 싱크부는

다이오드 형태로 접속되어 상기 제 3전류를 공급받는 적어도 하나의 제 1트랜지스터들과,

상기 제 1트랜지스터들과 전류 미러로 접속되어 상기 제 3전류를 싱크하기 위한 적어도 하나의 제 2트랜지스터들을 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 8

제 7항에 있어서,

상기 제 2전류 싱크부는

상기 제 2전류 생성부와 접속되며, 상기 제어부의 제어에 의하여 턴-온 및 턴-오프되는 다수의 제 3스위치들과,

상기 제 3스위치들 각각에 접속되는 적어도 하나 이상의 제 3트랜지스터들과,

상기 제 3트랜지스터들과 전류 미러로 접속되며 상기 제 3전류를 공급받는 제 4트랜지스터들을 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 9

제 8항에 있어서,

상기 제 3스위치들과 접속되는 상기 제 3트랜지스터들의 수는  $2^k$  ( $k=0, 1, 2, \dots$ )의 비율로 증가되도록 설정되는 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 10

제 8항에 있어서,

상기 제 3트랜지스터들의 수와 상기 제 4트랜지스터들의 수는 동일하게 설정되는 것을 특징으로 하는 유기전계 발광 표시장치.

#### 청구항 11

제 8항에 있어서,

상기 제어부는 상기 제 4전류가 상기 제 2전류 생성부로부터 싱크될 수 있도록 상기 제 3스위치들의 턴-온 및 턴-오프를 제어하는 것을 특징으로 하는 유기전계발광 표시장치.

#### 청구항 12

제 6항에 있어서,

상기 제 2전류 생성부는

상기 제 3전류 및 제 4전류가 상기 제 1전류 싱크부 및 제 2전류 싱크부로 싱크되도록 다이오드 형태로 접속되는 적어도 하나의 제 1트랜지스터들과;

상기 제 1트랜지스터들과 전류 미러로 접속되어 상기 제 3전류 및 제 4전류를 합한 전류에 해당하는 제 5전류를 상기 제 3전류 싱크부로 공급하기 위한 적어도 하나의 제 2트랜지스터들을 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 13

제 6항에 있어서,

상기 제 3전류 싱크부는

상기 스위칭부와 접속되며, 데이터 구동부의 제어에 의하여 턴-온 및 턴-오프되는 다수의 제 3스위치들과,

상기 제 3스위치들 각각에 접속되는 적어도 하나 이상의 제 1트랜지스터들과,

상기 제 3트랜지스터들과 전류 미러로 접속되며 상기 제 5전류를 공급받는 제 2트랜지스터를 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 14

제 13항에 있어서,

상기 데이터 구동부는 상기 데이터의 상위 비트들을 이용하여 상기 제 3스위치들의 턴-온 및 턴-오프를 제어하면서 상기 제 5전류를  $\beta$  배 상승하여 상기 제 2전류를 생성하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 15

제 2항에 있어서,

상기 전류 디지털-아날로그 변환부는

상기 데이터의 계조에 대응하여 나누어진 상기 1개의 전류값 중 제일 낮은 계조에 대응하는 제 3전류를 생성하기 위한 제 1전류 생성부와;

상기 제 1전류 생성부로부터 공급되는 제 3전류를 공급받고, 상기 데이터의 계조에 대응하여 상기 제 3전류를  $\beta$  ( $\beta$ 는 1, 2, 3, ...)배로 상승하여 생성되는 제 4전류를 제 2전류 생성부로부터 싱크하기 위한 제 1전류 싱크부와;

상기 제 1전류 싱크부에서 싱크되는 상기 제 4전류에 대응하여 상기 제 4전류를 생성하고, 생성된 제 4전류를 제 2전류 싱크부 및 제 3전류 싱크부로 공급하기 위한 제 2전류 생성부와;

상기 제 4전류에 대응하여 상기 화소로부터 상기 제 4전류를 싱크하기 위한 상기 제 2전류 싱크부와;

상기 제 4전류에 대응하여 상기 유기 발광 다이오드의 열화가 보상될 수 있는 제 5전류를 상기 화소로부터 싱크하기 위한 제 3전류 싱크부를 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 16

제 15항에 있어서,

상기 제 1전류 싱크부는

다이오드 형태로 접속되어 상기 제 3전류를 공급받는 적어도 하나의 제 1트랜지스터와;

상기 제 2전류 생성부와 접속되며, 데이터 구동부의 제어에 의하여 턴-온 및 턴-오프되는 다수의 제 3스위치들과;

상기 제 3스위치들 각각에 접속되며, 상기 제 1트랜지스터와 전류 미러로 접속되는 적어도 하나 이상의 제 2트

랜지스터들을 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 17

제 16항에 있어서,

상기 데이터 구동부는 상기 제 4전류가 상기 제 2전류 생성부로부터 싱크되도록 상기 데이터의 상위 비트들을 이용하여 상기 제 3스위치들의 턴-온 및 턴-오프를 제어하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 18

제 15항에 있어서,

상기 제 2전류 싱크부는

다이오드 형태로 접속되어 상기 제 4전류를 공급받는 적어도 하나의 제 1트랜지스터들과,

상기 제 1트랜지스터들과 전류 미러로 접속되어 상기 제 4전류를 상기 화소로부터 싱크하기 위한 적어도 하나의 제 2트랜지스터들을 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 19

제 18항에 있어서,

상기 제 3전류 싱크부는

상기 스위칭부와 접속되며, 상기 제어부의 제어에 의하여 턴-온 및 턴-오프되는 다수의 제 3스위치들과,

상기 제 3스위치들 각각에 접속되는 적어도 하나 이상의 제 3트랜지스터들과,

상기 제 3트랜지스터들과 전류 미러로 접속되며 상기 제 4전류를 공급받는 제 4트랜지스터들을 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 20

제 19항에 있어서,

상기 제 3스위치들과 접속되는 상기 제 3트랜지스터들의 수는  $2^k$ ( $k=0, 1, 2, \dots$ )의 비율로 증가되도록 설정되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 21

제 19항에 있어서,

상기 제 3트랜지스터들의 수와 상기 제 4트랜지스터들의 수는 동일하게 설정되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 22

제 19항에 있어서,

상기 제어부는 상기 제 5전류가 상기 화소로부터 싱크될 수 있도록 상기 제 3스위치들의 턴-온 및 턴-오프를 제어하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 23

제 2항에 있어서,

한 프레임은 복수의 서브 프레임으로 나누어 구동되며, 상기 샘플링 기간은 상기 한 프레임의 초기에 위치되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 24

제 2항에 있어서,

상기 센싱 기간은 상기 유기전계발광 표시장치로 전원이 공급되는 순간에 위치되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 25

제 2항에 있어서,

상기 화소들과 접속된 데이터선들로 상기 화소들이 발광될 수 있는 제 1데이터신호 또는 상기 화소들이 비발광 되는 제 2데이터신호를 공급하기 위한 데이터 구동부와,

상기 화소들과 접속된 제 1주사선들로 제 1주사신호를 공급하고, 제 2주사선들로 제 2주사신호를 공급하기 위한 주사 구동부와,

상기 화소들과 접속된 제어선들로 제어신호를 공급하기 위한 제어선 구동부를 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 26

제 25항에 있어서,

상기 데이터 구동부는

샘플링 신호를 순차적으로 생성하기 위한 쉬프트 레지스터부와,

상기 샘플링 신호에 대응하여 상기 데이터들을 순차적으로 저장하기 위한 샘플링 래치부와,

상기 샘플링 래치부에 저장된 데이터들을 저장하기 위한 훌딩 래치부와,

상기 훌딩 래치부로부터 상기 데이터들의 하위비트들을 공급받아 상기 제 1데이터신호 또는 제 2데이터신호를 생성하기 위한 신호 생성부를 구비하며,

상기 데이터의 하위비트들을 제외한 상위비트들은 상기 센싱부로 공급되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 27

제 25항에 있어서,

상기 화소들 각각은

제 1전극이 상기 피드백선과 접속되며, 상기 제 1주사선으로 주사신호가 공급될 때 턴-온되는 제 2트랜지스터와;

제 1트랜지스터의 게이트전극이 상기 제 2트랜지스터의 제 2전극에 접속되며, 상기 유기 발광 다이오드로 전류를 공급하기 위한 제 1트랜지스터와;

상기 제 1트랜지스터의 게이트전극 및 제 1전극 사이에 접속되며, 상기 제 2전류에 대응하는 전압을 충전하기 위한 제 1커패시터와;

상기 제 1트랜지스터의 제 2전극과 상기 피드백선 사이에 접속되며, 상기 제 1주사선으로 주사신호가 공급될 때 턴-온되는 제 3트랜지스터와;

제 1전극이 상기 제 1트랜지스터의 제 2전극에 접속되고, 제 2전극이 상기 유기 발광 다이오드의 애노드전극에 접속되는 제 4트랜지스터와;

상기 제 4트랜지스터의 게이트전극과 상기 제 1트랜지스터의 제 1전극 사이에 접속되며, 상기 제 1데이터신호 또는 제 2데이터신호에 대응하는 전압을 충전하기 위한 제 2커패시터와;

상기 제 4트랜지스터의 게이트전극과 상기 데이터선 사이에 접속되며, 상기 제 2주사선으로 주사신호가 공급될 때 턴-온되는 제 5트랜지스터와;

상기 유기 발광 다이오드의 애노드전극과 상기 피드백선 사이에 접속되며, 상기 제어선으로 제어신호가 공급될 때 턴-온되는 제 6트랜지스터를 구비하는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 28

제 27항에 있어서,

상기 제 5트랜지스터는 상기 센싱 기간 및 샘플링 기간 동안 턴-온되어 상기 데이터선으로부터 제 2데이터신호를 공급받는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 29

제 27항에 있어서,

상기 제 6트랜지스터는 상기 센싱 기간 동안 턴-온되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 30

제 27항에 있어서,

상기 제 2트랜지스터 및 제 3트랜지스터는 상기 샘플링 기간에 턴-온되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 31

제 27항에 있어서,

한 프레임은 복수의 서브 프레임을 포함하며, 상기 서브 프레임 기간 동안 상기 제 2주사신호가 순차적으로 공급되면서 상기 제 2커패시터에 상기 제 1데이터신호 또는 제 2데이터신호에 대응하는 전압이 충전되는 것을 특징으로 하는 유기전계발광 표시장치.

### 청구항 32

센싱 기간 동안 화소들에 포함되는 유기 발광 다이오드들로 제 1전류를 공급하는 단계와,

상기 제 1전류에 대응하여 상기 유기 발광 다이오드들에 인가되는 전압을 디지털 값들로 변환하여 메모리에 저장하는 단계와,

샘플링 기간 동안 상기 메모리에 저장된 디지털 값을 이용하여 상기 유기 발광 다이오드의 열화가 보상될 수 있도록 상기 화소로부터 싱크되는 제 2전류값을 조절하는 단계와,

상기 제 2전류를 싱크하면서 상기 화소들에 상기 제 2전류에 대응하는 전압을 충전하는 단계를 포함하며,

상기 제 2전류는 1(1은 자연수)개의 전류값 중 데이터의 비트에 대응하여 선택된 전류값과 상기 유기 발광 다이오드의 열화가 보상될 수 있는 전류를 포함하는 전류인 것을 특징으로 하는 유기전계발광 표시장치의 구동방법.

### 청구항 33

제 32항에 있어서,

상기 센싱 기간 동안 상기 메모리에는 모든 화소를 각각의 디지털 값들이 저장되는 것을 특징으로 하는 유기전계발광 표시장치의 구동방법.

### 청구항 34

제 32항에 있어서,

상기 센싱 기간은 상기 유기전계발광 표시장치로 전월이 공급되는 시점에 위치되는 것을 특징으로 하는 유기전계발광 표시장치의 구동방법.

### 청구항 35

제 32항에 있어서,

한 프레임은 복수의 서브 프레임으로 나뉘며, 상기 샘플링 기간은 상기 프레임의 초기에 위치되는 것을 특징으로 하는 유기전계발광 표시장치의 구동방법.

## 청구항 36

제 35항에 있어서,

상기 서브 프레임의 주사기간 동안 상기 화소들 각각에 상기 화소들이 발광하는 제 1데이터신호 또는 상기 화소들이 비발광하는 제 2데이터신호를 공급하는 단계와,

상기 서브 프레임의 발광기간 동안 상기 제 1데이터신호를 공급받은 화소들 각각의 유기 발광 다이오드로 상기 제 2전류를 공급하는 단계를 포함하는 것을 특징으로 하는 유기전계발광 표시장치의 구동방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <24> 본 발명은 유기전계발광 표시장치 및 그의 구동방법에 관한 것으로, 특히 유기 발광 다이오드의 열화를 보상할 수 있도록 한 유기전계발광 표시장치 및 그의 구동방법에 관한 것이다.

- <25> 최근, 음극선관(Cathode Ray Tube)의 단점인 무게와 부피를 줄일 수 있는 각종 평판 표시장치들이 개발되고 있다. 평판 표시장치로는 액정 표시장치(Liquid Crystal Display), 전계방출 표시장치(Field Emission Display), 플라즈마 표시패널(Plasma Display Panel) 및 유기전계발광 표시장치(Organic Light Emitting Display) 등이 있다.

- <26> 평판표시장치 중 유기전계발광 표시장치는 전자와 정공의 재결합에 의하여 빛을 발생하는 유기 발광 다이오드(Organic Light Emitting Diode : OLED)를 이용하여 화상을 표시한다. 이러한, 유기전계발광 표시장치는 빠른 응답속도를 가짐과 동시에 낮은 소비전력으로 구동되는 장점이 있다.

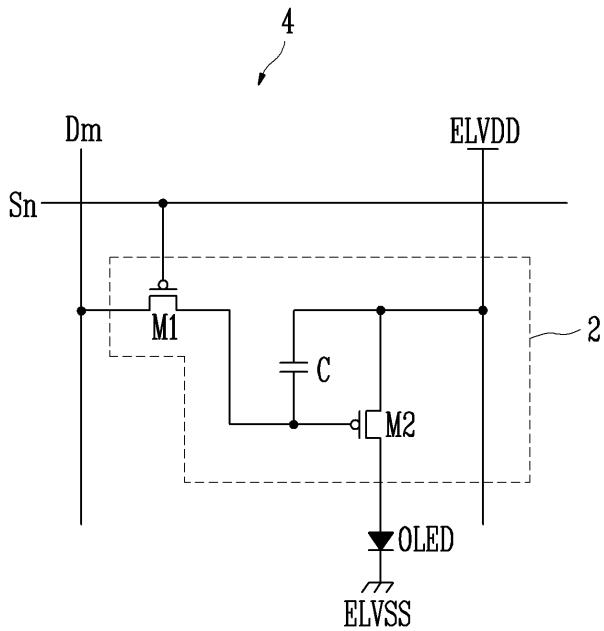

- <27> 도 1은 종래의 유기전계발광 표시장치의 화소를 나타내는 회로도이다.

- <28> 도 1을 참조하면, 종래의 유기전계발광 표시장치의 화소(4)는 유기 발광 다이오드(OLED)와, 데이터선(Dm) 및 주사선(Sn)에 접속되어 유기 발광 다이오드(OLED)를 제어하기 위한 화소회로(2)를 구비한다.

- <29> 유기 발광 다이오드(OLED)의 애노드전극은 화소회로(2)에 접속되고, 캐소드전극은 제 2전원(ELVSS)에 접속된다. 이와 같은 유기 발광 다이오드(OLED)는 화소회로(2)로부터 공급되는 전류에 대응되어 소정 휙도의 빛을 생성한다.

- <30> 화소회로(2)는 주사선(Sn)에 주사신호가 공급될 때 데이터선(Dm)으로 공급되는 데이터신호에 대응되어 유기 발광 다이오드(OLED)로 공급되는 전류량을 제어한다. 이를 위해, 화소회로(2)는 제 1전원(ELVDD)과 유기 발광 다이오드(OLED) 사이에 접속된 제 2트랜지스터(M2)와, 제 2트랜지스터(M2), 데이터선(Dm) 및 주사선(Sn)의 사이에 접속된 제 1트랜지스터(M1)와, 제 2트랜지스터(M2)의 게이트전극과 제 1전극 사이에 접속된 스토리지 커퍼시터(C)를 구비한다.

- <31> 제 1트랜지스터(M1)의 게이트전극은 주사선(Sn)에 접속되고, 제 1전극은 데이터선(Dm)에 접속된다. 그리고, 제 1트랜지스터(M1)의 제 2전극은 스토리지 커퍼시터(C)의 일측단자에 접속된다. 여기서, 제 1전극은 소오스전극 및 드레인전극 중 어느 하나로 설정되고, 제 2전극은 제 1전극과 다른 전극으로 설정된다. 예를 들어, 제 1전극이 소오스전극으로 설정되면 제 2전극은 드레인전극으로 설정된다. 주사선(Sn) 및 데이터선(Dm)에 접속된 제 1트랜지스터(M1)는 주사선(Sn)으로부터 주사신호가 공급될 때 텐-온되어 데이터선(Dm)으로부터 공급되는 데이터신호를 스토리지 커퍼시터(C)로 공급한다. 이때, 스토리지 커퍼시터(C)는 데이터신호에 대응되는 전압을 충전한다.

- <32> 제 2트랜지스터(M2)의 게이트전극은 스토리지 커퍼시터(C)의 일측단자에 접속되고, 제 1전극은 스토리지 커퍼시터(C)의 다른측단자 및 제 1전원(ELVDD)에 접속된다. 그리고, 제 2트랜지스터(M2)의 제 2전극은 유기 발광 다이오드(OLED)의 애노드전극에 접속된다. 이와 같은 제 2트랜지스터(M2)는 스토리지 커퍼시터(C)에 저장된 전압 값에 대응하여 제 1전원(ELVDD)으로부터 유기 발광 다이오드(OLED)를 경유하여 제 2전원(ELVSS)으로 공급되는 전류량을 제어한다. 이때, 유기 발광 다이오드(OLED)는 제 2트랜지스터(M2)로부터 공급되는 전류량에 대응되는

빛을 생성한다.

<33> 실제로, 종래의 유기 발광 표시장치의 화소(4)는 상술한 과정을 반복하면서 소정 휙도의 화상을 표시한다. 한편, 제 2트랜지스터(M2)가 스위치로 동작하는 디지털 구동에서는 제 1전원(ELVDD)과 제 2전원(ELVSS)이 유기 발광 다이오드(OLED)에 그대로 공급되고, 이에 따라 유기 발광 다이오드(OLED)는 정전압 구동으로 발광한다. 즉, 디지털 구동에서는 유기 발광 다이오드(OLED)로 일정 전류를 공급하면서 유기 발광 다이오드(OLED)의 발광 시간을 이용하여 계조를 표현한다. 하지만, 디지털 구동 방식에서는 유기 발광 다이오드(OLED)가 정전압으로 구동되기 때문에 유기 발광 다이오드(OLED)의 열화 진행 속도가 빠르고, 이에 따라 원하는 휙도의 영상을 표시할 수 없는 문제점이 발생한다.

<34> 실제로, 유기 발광 다이오드(OLED)가 열화되면 유기 발광 다이오드(OLED)의 저항이 증가하고, 이에 따라 동일 전압에 대응하여 유기 발광 다이오드(OLED)로 흐르는 전류가 감소되어 휙도가 낮아지는 문제점이 발생한다.

### 발명이 이루고자 하는 기술적 과제

<35> 따라서, 본 발명의 목적은 유기 발광 다이오드의 열화를 보상할 수 있도록 한 유기전계발광 표시장치 및 그의 구동방법을 제공하는 것이다.

### 발명의 구성 및 작용

<36> 상기 목적을 달성하기 위하여, 본 발명의 실시 예에 따른 유기전계발광 표시장치는 유기 발광 다이오드 및 상기 유기 발광 다이오드로 전류의 공급유무를 제어하는 화소회로를 포함하는 화소들과; 센싱 기간 동안 상기 화소들 각각에 포함되는 유기 발광 다이오드로 제 1전류를 공급하면서 상기 유기 발광 다이오드에 인가되는 전압을 디지털 값으로 변환하고, 샘플링 기간 동안 상기 디지털 값에 대응하여 상기 유기 발광 다이오드가 보상될 수 있는 제 2전류를 상기 화소로부터 싱크하기 위한 센싱부를 구비하며; 상기 제 2전류는 1(1은 자연수)개의 전류값 중 데이터의 비트에 대응하여 선택된 전류값과 상기 유기 발광 다이오드의 열화가 보상될 수 있는 전류를 포함하는 전류이다.

<37> 바람직하게, 상기 센싱부는 상기 제 1전류를 공급하기 위한 전류 소스부와, 상기 제 2전류를 싱크하기 위한 전류 디지털-아날로그 변환부와, 상기 전류 소스부 및 전류 디지털-아날로그 변환부를 상기 화소와 접속되는 피드백선과 선택적으로 접속시키기 위한 스위칭부와, 상기 전류 소스부와 접속되어 상기 유기 발광 다이오드에 인가되는 전압을 상기 디지털 값으로 변환하기 위한 아날로그-디지털 변환부와, 상기 디지털 값을 저장하기 위한 메모리와, 상기 메모리에 저장되는 디지털 값에 대응하여 상기 유기 발광 다이오드의 열화가 보상될 수 있도록 상기 전류 디지털-아날로그 변환부를 제어하기 위한 제어부를 구비한다.

<38> 상기 전류 디지털-아날로그 변환부는 상기 데이터의 계조에 대응하여 나누어진 상기 1개의 전류값 중 제일 낮은 계조에 대응하는 제 3전류를 생성하기 위한 제 1전류 생성부와, 상기 제 1전류 생성부로부터 공급되는 제 3전류에 대응하여 제 2전류 생성부로부터 상기 제 3전류를 싱크하기 위한 제 1전류 싱크부와, 상기 제 1전류 생성부로부터 공급되는 상기 제 3전류에 대응하여 상기 유기 발광 다이오드의 열화가 보상될 수 있는 제 4전류를 상기 제 2전류 생성부로부터 싱크하기 위한 제 2전류 싱크부와, 상기 제 1전류 싱크부 및 제 2전류 싱크부에서 싱크되는 상기 제 3전류 및 제 4전류에 대응하는 제 5전류를 생성하기 위한 제 2전류 생성부와, 상기 제 2전류 생성부로부터 공급되는 제 5전류를 상기 데이터의 계조에 대응하여  $\beta$  ( $\beta$ 는 1, 2, 3, ...)배로 상승하여 상기 제 2전류를 생성하고, 상기 제 2전류를 상기 피드백선으로부터 싱크하기 위한 제 3전류 싱크부를 구비한다.

<39> 상기 전류 디지털-아날로그 변환부는 상기 데이터의 계조에 대응하여 나누어진 상기 1개의 전류값 중 제일 낮은 계조에 대응하는 제 3전류를 생성하기 위한 제 1전류 생성부와; 상기 제 1전류 생성부로부터 공급되는 제 3전류를 공급받고, 상기 데이터의 계조에 대응하여 상기 제 3전류를  $\beta$  ( $\beta$ 는 1, 2, 3, ...)배로 상승하여 생성되는 제 4전류를 제 2전류 생성부로부터 싱크하기 위한 제 1전류 싱크부와; 상기 제 1전류 싱크부에서 싱크되는 상기 제 4전류에 대응하여 상기 제 4전류를 생성하고, 생성된 제 4전류를 제 2전류 싱크부 및 제 3전류 싱크부로 공급하기 위한 제 2전류 생성부와; 상기 제 4전류에 대응하여 상기 화소로부터 상기 제 4전류를 싱크하기 위한 상기 제 2전류 싱크부와; 상기 제 4전류에 대응하여 상기 유기 발광 다이오드의 열화가 보상될 수 있는 제 5전류를 상기 화소로부터 싱크하기 위한 제 3전류 싱크부를 구비한다.

<40> 상기 제 1전류 싱크부는 다이오드 형태로 접속되어 상기 제 3전류를 공급받는 적어도 하나의 제 1트랜지스터와; 상기 제 2전류 생성부와 접속되며, 데이터 구동부의 제어에 의하여 턴-온 및 턴-오프되는 다수의 제 3스위치들과; 상기 제 3스위치들 각각에 접속되며, 상기 제 1트랜지스터와 전류 미러로 접속되는 적어도 하나 이상의 제

2트랜지스터들을 구비한다.

- <41> 상기 제 2전류 싱크부는 다이오드 형태로 접속되어 상기 제 4전류를 공급받는 적어도 하나의 제 1트랜지스터들과, 상기 제 1트랜지스터들과 전류 미러로 접속되어 상기 제 4전류를 상기 화소로부터 싱크하기 위한 적어도 하나의 제 2트랜지스터들을 구비한다.

- <42> 상기 제 3전류 싱크부는 상기 스위칭부와 접속되며, 상기 제어부의 제어에 의하여 턴-온 및 턴-오프되는 다수의 제 3스위치들과, 상기 제 3스위치들 각각에 접속되는 적어도 하나 이상의 제 3트랜지스터들과, 상기 제 3트랜지스터들과 전류 미러로 접속되며 상기 제 4전류를 공급받는 제 4트랜지스터들을 구비한다.

- <43> 본 발명의 실시예에 의한 유기전계발광 표시장치의 구동방법은 센싱 기간 동안 화소들에 포함되는 유기 발광 다이오드들로 제 1전류를 공급하는 단계와, 상기 제 1전류에 대응하여 상기 유기 발광 다이오드들에 인가되는 전압을 디지털 값들로 변환하여 메모리에 저장하는 단계와, 샘플링 기간 동안 상기 메모리에 저장된 디지털 값을 이용하여 상기 유기 발광 다이오드의 열화가 보상될 수 있도록 상기 화소로부터 싱크되는 제 2전류값을 조절하는 단계와, 상기 제 2전류를 싱크하면서 상기 화소들에 상기 제 2전류에 대응하는 전압을 충전하는 단계를 포함하며, 상기 제 2전류는 1(1은 자연수)개의 전류값 중 데이터의 비트에 대응하여 선택된 전류값과 상기 유기 발광 다이오드의 열화가 보상될 수 있는 전류를 포함한다.

- <44> 바람직하게, 상기 센싱 기간 동안 상기 메모리에는 모든 화소들 각각의 디지털 값들이 저장된다. 상기 센싱 기간은 상기 유기전계발광 표시장치로 전원이 공급되는 시점에 위치된다. 한 프레임은 복수의 서브 프레임으로 나뉘며, 상기 샘플링 기간은 상기 프레임의 초기에 위치된다. 상기 서브 프레임의 주사기간 동안 상기 화소들 각각에 상기 화소들이 발광하는 제 1데이터신호 또는 상기 화소들이 비발광하는 제 2데이터신호를 공급하는 단계와, 상기 서브 프레임의 발광기간 동안 상기 제 1데이터신호를 공급받은 화소들 각각의 유기 발광 다이오드로 상기 제 2전류를 공급하는 단계를 포함한다.

- <45> 이하, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자가 본 발명을 용이하게 실시할 수 있는 바람직한 실시 예를 첨부된 도 2 내지 도 11을 참조하여 상세히 설명하면 다음과 같다.

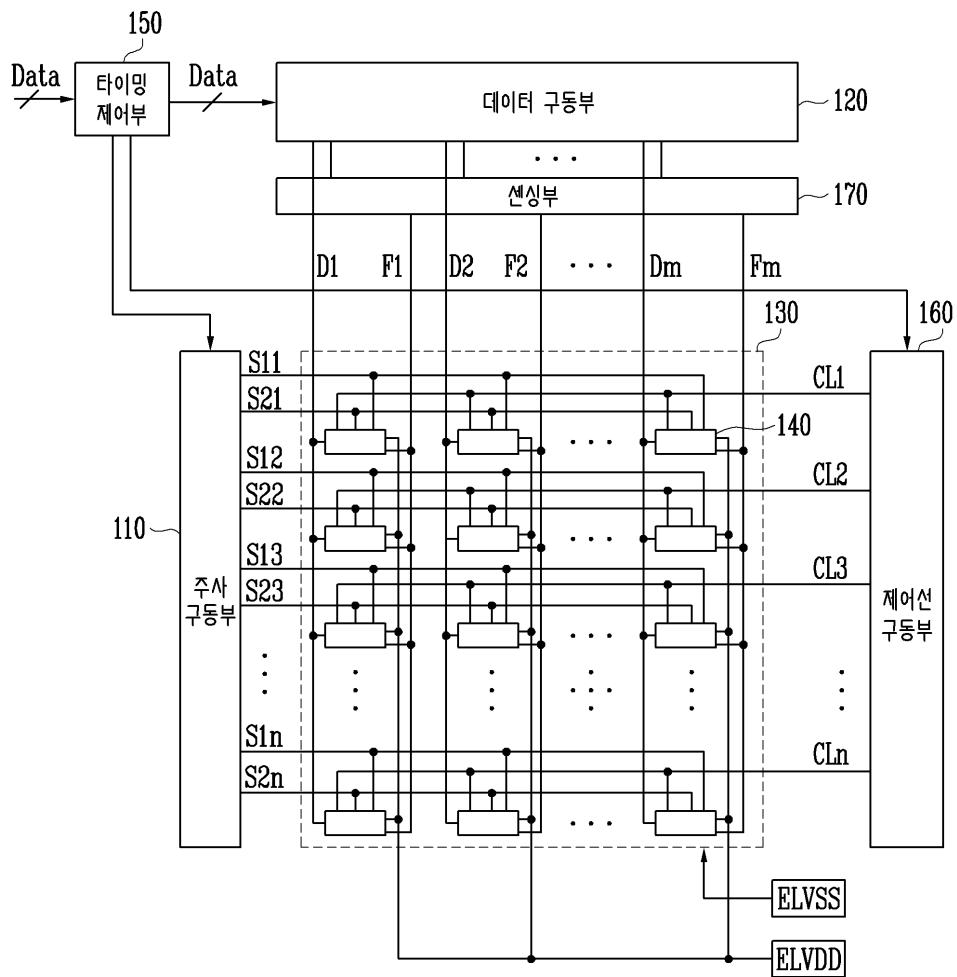

- <46> 도 2는 본 발명의 실시예에 의한 유기전계발광 표시장치를 나타내는 도면이다.

- <47> 도 2를 참조하면, 본 발명의 실시예에 의한 유기전계발광 표시장치는 제 1주사선들(S11 내지 S1n), 제 2주사선들(S21 내지 S2n), 데이터선들(D1 내지 Dm), 피드백선들(F1 내지 Fm) 및 제어선들(CL1 내지 CLn)과 접속되는 화소들(140)을 포함하는 화소부(130)와, 제 1 및 제 2주사선들(S11 내지 S1n, S21 내지 S2n)을 구동하기 위한 주사 구동부(110)와, 제어선들(CL1 내지 CLn)을 구동하기 위한 제어선 구동부(160)와, 데이터선들(D1 내지 Dm)을 구동하기 위한 데이터 구동부(120)와, 주사 구동부(110), 제어선 구동부(160) 및 데이터 구동부(120)를 제어하기 위한 타이밍 제어부(150)를 구비한다.

- <48> 또한, 본 발명의 실시예에 의한 유기전계발광 표시장치는 피드백선들(F1 내지 Fm)을 이용하여 화소들(140) 각각에 포함되는 유기 발광 다이오드의 열화정보를 센싱하고, 센싱된 정보에 대응하여 유기 발광 다이오드의 열화가 보상될 수 있는 전압을 화소들(140)에 충전하는 센싱부(170)를 더 구비한다.

- <49> 화소부(130)는 제 1주사선들(S11 내지 S1n), 제 2주사선들(S21 내지 S2n), 데이터선들(D1 내지 Dm), 피드백선들(F1 내지 Fm) 및 제어선들(CL1 내지 CLn)의 교차부에 위치되는 화소들(140)을 구비한다. 화소들(140)은 외부로부터 제 1전원(ELVDD) 및 제 2전원(ELVSS)을 공급받는다. 이와 같은 화소들(140)은 데이터신호에 대응하여 제 1전원(ELVDD)과 유기 발광 다이오드의 전기적 접속을 제어한다.

- <50> 여기서, 화소들(140)에 유기 발광 다이오드로 공급되는 전류는 계조에 대응하여 적어도 2가지 이상의 전류값을 갖는다. 즉, 본 발명에서는 유기 발광 다이오드의 발광시간 및 전류값을 이용하여 계조를 구현한다.

- <51> 주사 구동부(110)는 제 1주사선들(S11 내지 S1n)로 제 1주사신호를 공급하고, 제 2주사선들(S21 내지 S2n)로 제 2주사신호를 공급한다. 주사 구동부(110)에서 공급되는 제 1주사신호 및 제 2주사신호에 대한 상세한 설명은 후술하기로 한다.

- <52> 제어선 구동부(160)는 센싱기간 동안 제어선들(CL1 내지 CLn)로 제어신호를 공급한다. 여기서, 센싱기간은 유기전계발광 표시장치로 전원이 공급되는 시점 또는 사용자에 의하여 미리 설정된 시점에 위치되는 기간으로 화소들(140) 각각에 포함되는 유기 발광 다이오드의 열화정보를 추출하는 기간이다.

- <53> 데이터 구동부(120)는 센싱 기간 및 샘플링 기간 동안 데이터선들(D1 내지 Dm)로 제 2데이터신호를 공급한다.

그리고, 데이터 구동부(120)는 정상 구동기간 동안 데이터선들(D1 내지 Dm)로 제 1데이터신호 또는 제 2데이터신호를 공급한다. 여기서, 제 1데이터신호는 화소들(140)이 발광할 수 있는 전압으로 설정되고, 제 2데이터신호는 화소들(140)이 비발광되는 전압으로 설정된다.

<54> 센싱부(170)는 센싱기간 동안 유기 발광 다이오드의 열화정보를 추출하고, 추출된 열화정보가 보상될 수 있도록 전류 디지털-아날로그 변환부(Current Digital Analog Converter : 이하 "전류 DAC"라 함)(미도시)에서 싱크(sink)되는 전류값을 조절한다. 그리고, 센싱부(170)는 한 프레임 기간 중 샘플링 기간 동안 전류 DAC를 이용하여 화소들(140)의 전압을 충전함으로써 유기 발광 다이오드의 열화가 보상되도록 한다.

<55> 여기서, 전류 DAC에서 싱크되는 전류는 데이터(Data)의 계조에 대응하여 적어도 2가지 이상의 전류값을 갖는다. 즉, 전류 DAC에서 싱크되는 전류는 유기 발광 다이오드의 열화가 보상됨과 아울러 데이터(Data)의 계조에 대응하여 전류값으로 결정된다. 이와 같은 센싱부(170)에 대한 상세한 설명은 후술하기로 한다.

<56> 타이밍 제어부(150)는 주사 구동부(110), 데이터 구동부(120), 제어선 구동부(160)를 제어한다. 그리고, 타이밍 제어부(150)는 외부로부터 공급되는 데이터(Data)를 데이터 구동부(120)로 전달한다.

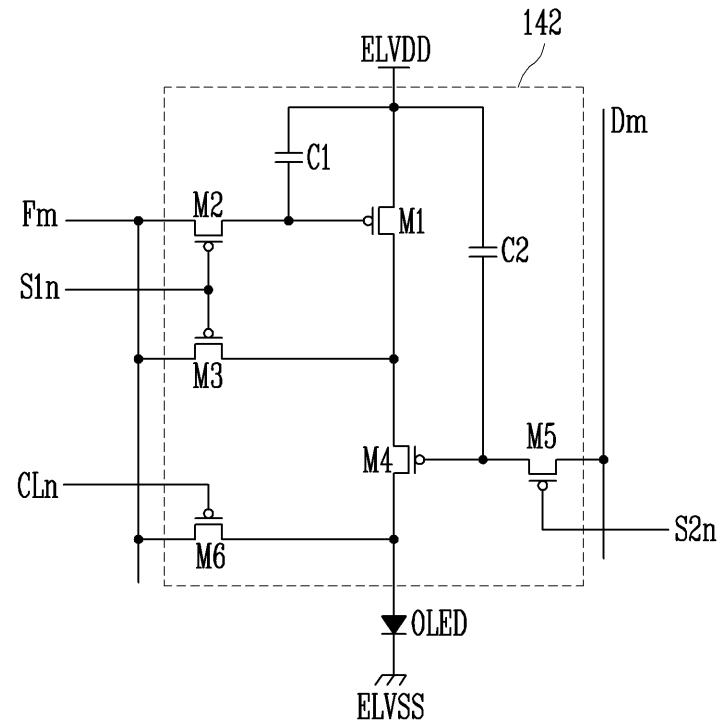

<57> 도 3은 도 2에 도시된 화소의 실시예를 나타내는 도면이다. 도 3에서는 설명의 편의성을 위하여 제 m데이터선(Dm) 및 제 1n주사선(S1n)에 접속된 화소를 도시하기로 한다.

<58> 도 3을 참조하면, 본 발명의 실시예에 의한 화소(140)는 유기 발광 다이오드(OLED)와, 유기 발광 다이오드(OLED)로 전류를 공급하기 위한 화소회로(142)를 구비한다.

<59> 유기 발광 다이오드(OLED)의 애노드전극은 화소회로(142)에 접속되고, 캐소드전극은 제 2전원(ELVSS)에 접속된다. 이와 같은 유기 발광 다이오드(OLED)는 화소회로(142)로부터 공급되는 전류에 대응하여 발광 또는 비발광된다.

<60> 화소회로(142)는 제 1주사선(S1n)으로 제 1주사신호가 공급될 때 피드백선(Fm)으로부터 싱크되는 전류에 대응하여 소정의 전압을 제 1커패시터(C1)에 충전한다. 그리고, 화소회로(142)는 제 2주사선(S2n)으로 제 2주사신호가 공급될 때 제 2커패시터(C2)에 데이터신호에 대응되는 전압을 충전한다. 여기서, 제 1데이터신호가 공급된 경우 제 2커패시터(C2)에는 제 4트랜지스터(M4)가 턴-온되는 전압이 충전되고, 제 2데이터신호가 공급되는 경우 제 2커패시터(C2)에는 제 4트랜지스터(M4)가 턴-오프되는 전압이 충전된다. 화소회로(142)는 제 1데이터신호가 공급되는 경우 제 1커패시터(C1)에 충전된 전압에 대응하는 전류를 소정 시간 동안 유기 발광 다이오드(OLED)로 공급한다. 이를 위해, 화소회로(142)는 6개의 트랜지스터(M1 내지 M6), 제 1커패시터(C1) 및 제 2커패시터(C2)를 구비한다.

<61> 제 2트랜지스터(M2)의 게이트전극은 제 1주사선(S1n)에 접속되고, 제 1전극은 피드백선(Fm)에 접속된다. 그리고, 제 2트랜지스터(M2)의 제 2전극은 제 1트랜지스터(M1)의 게이트전극 및 제 1커패시터(C1)의 제 1단자에 접속된다. 이와 같은 제 2트랜지스터(M2)는 제 1주사선(S1n)으로 제 1주사신호가 공급될 때 턴-온된다.

<62> 제 1트랜지스터(M1)의 게이트전극은 제 2트랜지스터(M2)의 제 2전극에 접속되고, 제 1전극은 제 1전원(ELVDD) 및 제 1커패시터(C1)의 제 2단자에 접속된다. 그리고, 제 1트랜지스터(M1)의 제 2전극은 제 4트랜지스터(M4)의 제 1전극에 접속된다. 이와 같은 제 1트랜지스터(M1)는 제 1커패시터(C1)에 충전된 전압에 대응하는 전류를 제 4트랜지스터(M4)로 공급한다.

<63> 제 3트랜지스터(M3)의 게이트전극은 제 1주사선(S1n)에 접속되고, 제 1전극은 제 1트랜지스터(M1)의 제 2전극에 접속된다. 그리고, 제 3트랜지스터(M3)의 제 2전극은 피드백선(Fm)에 접속된다. 이와 같은 제 3트랜지스터(M3)는 제 1주사선(S1n)으로 제 1주사신호가 공급될 때 턴-온된다.

<64> 제 4트랜지스터(M4)의 게이트전극은 제 5트랜지스터(M5)의 제 2전극에 접속되고, 제 1전극은 제 1트랜지스터(M1)의 제 2전극에 접속된다. 그리고, 제 4트랜지스터(M4)의 제 2전극은 유기 발광 다이오드(OLED)의 애노드전극에 접속된다. 이와 같은 제 4트랜지스터(M4)는 제 2커패시터(C2)에 충전된 전압에 대응하여 턴-온 또는 턴-오프된다.

<65> 제 5트랜지스터(M5)의 게이트전극은 제 2주사선(S2n)에 접속되고, 제 1전극은 데이터선(Dm)에 접속된다. 그리고, 제 5트랜지스터(M5)의 제 2전극은 제 4트랜지스터(M4)의 게이트전극에 접속된다. 이와 같은 제 5트랜지스터(M5)는 제 2주사선(S2n)으로 제 2주사신호가 공급될 때 턴-온된다.

<66> 제 6트랜지스터(M6)의 게이트전극은 제어선(CLn)에 접속되고, 제 1전극은 피드백선(Fm)에 접속된다. 그리고,

제 6트랜지스터(M6)의 제 2전극은 유기 발광 다이오드(OLED)의 애노드전극에 접속된다. 이와 같은 제 6트랜지스터(M6)는 제어선(CL<sub>n</sub>)으로 제어신호가 공급될 때 턴-온된다.

<67> 제 1커패시터(C1)는 제 1트랜지스터(M1)의 게이트전극 및 제 1전극 사이에 위치된다. 이와 같은 제 1커패시터(C1)는 피드백선(F<sub>m</sub>)으로 싱크되는 전류에 대응하여 제 1트랜지스터(M1)의 게이트전극에 인가되는 전압을 충전한다.

<68> 제 2커패시터(C2)는 제 1전원(ELVDD)과 제 4트랜지스터(M4)의 게이트전극 사이에 위치된다. 이와 같은 제 2커패시터(C2)는 데이터신호에 대응되는 전압을 충전한다. 여기서, 제 2커패시터(C2)는 제 1데이터신호가 공급되는 경우 제 4트랜지스터(M4)가 턴-온될 수 있는 전압을 충전하고, 제 2데이터신호가 공급되는 경우 제 4트랜지스터(M4)가 턴-오프될 수 있는 전압을 충전한다.

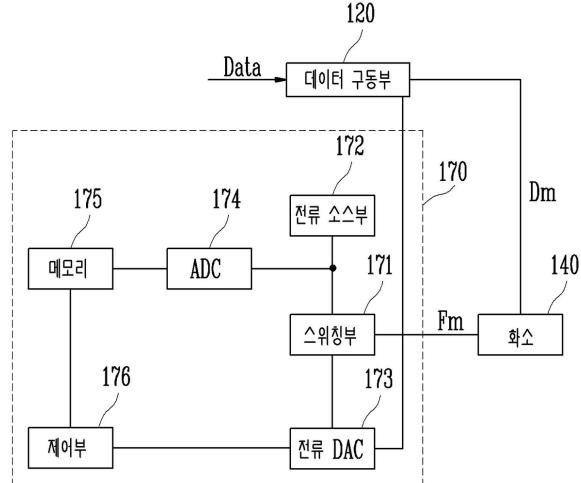

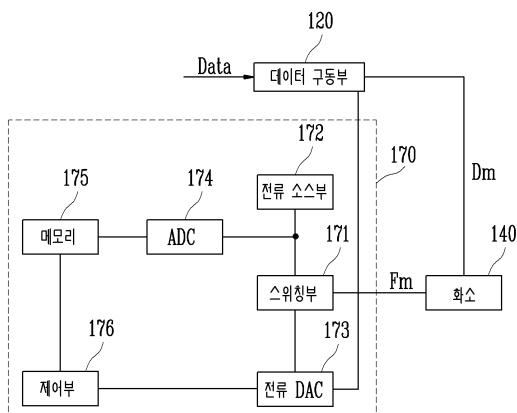

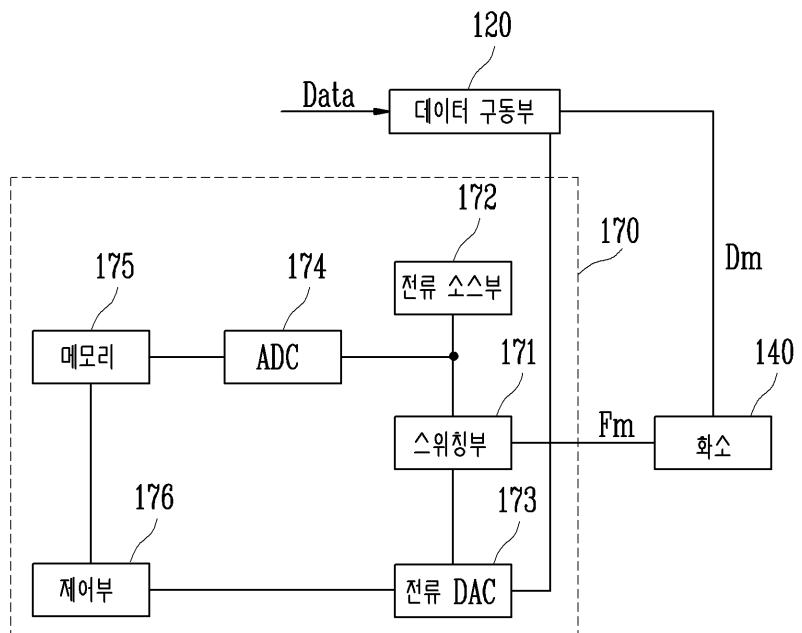

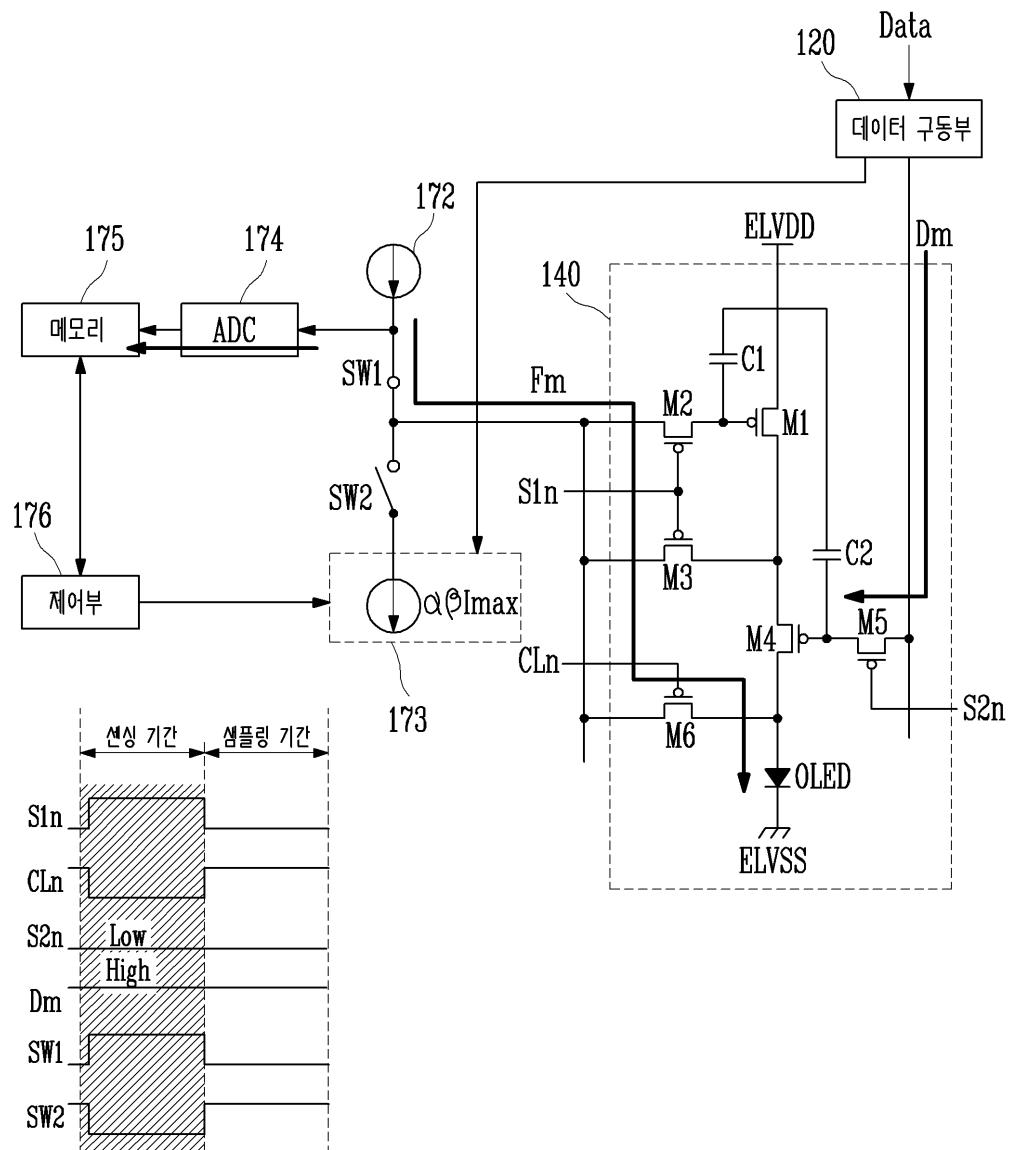

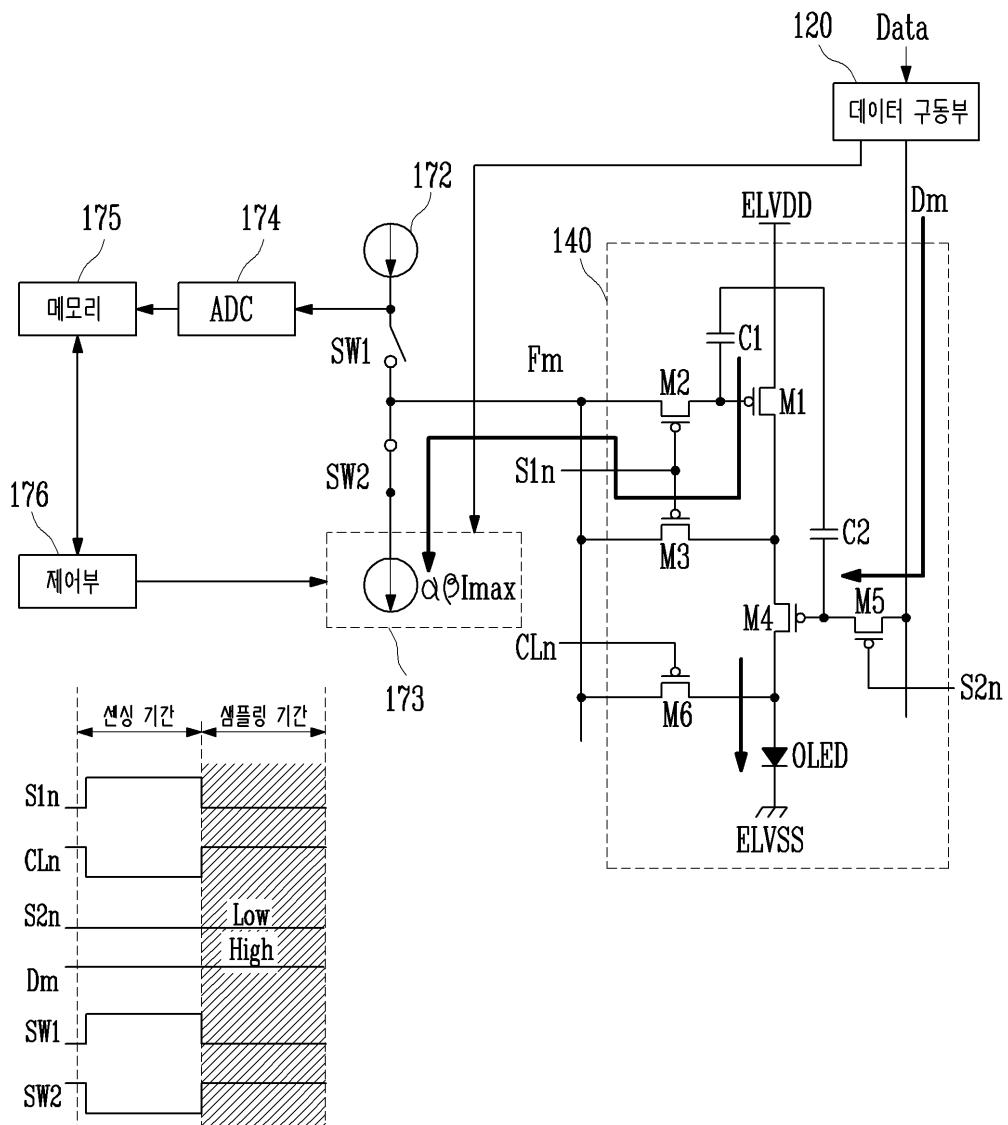

<69> 도 4는 도 2에 도시된 센싱부를 상세히 나타내는 도면이다. 도 4에는 설명의 편의성을 위하여 제 m피드백선(F<sub>m</sub>)과 접속되는 구성을 도시하기로 한다.

<70> 도 4를 참조하면, 센싱부(170) 각각의 채널에는 스위칭부(171), 전류 소스부(172) 및 전류 DAC(173)가 포함된다. 그리고, 센싱부(170)에는 각각의 채널에 포함되는 스위칭부(171)와 공통적으로 접속되는 아날로그 디지털 컨버터(Analog Digital Converter : 이하 "ADC"라 함)(174), 메모리(175) 및 제어부(176)가 구비된다. 여기서, ADC(174)가 각각의 채널에 공통적으로 접속된다고 가정하였지만 본 발명이 이에 한정되는 것은 아니다. 예를 들어, 본 발명에서는 적색 화소, 녹색 화소 및 청색 화소와 각각 접속되도록 3개의 ADC(174)가 포함될 수도 있다.

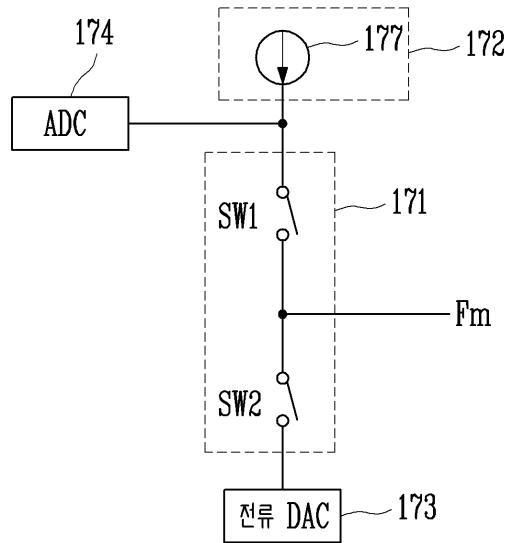

<71> 스위칭부(171)는 도 5에 도시된 바와 같이 전류 소스부(172)와 피드백선(F<sub>m</sub>) 사이에 위치되는 제 1스위치(SW1)와, 전류 DAC(173)와 피드백선(F<sub>m</sub>) 사이에 위치되는 제 2스위치(SW2)를 구비한다.

<72> 제 1스위치(SW1)는 센싱기간 동안 턴-온된다. 제 1스위치(SW1)가 턴-온되면 피드백선(F<sub>m</sub>)과 전류 소스부(172), 피드백선(F<sub>m</sub>)과 ADC(174)가 전기적으로 접속된다.

<73> 제 2스위치(SW2)는 샘플링 기간 동안 턴-온된다. 제 2스위치(SW2)가 턴-온되면 피드백선(F<sub>m</sub>)과 전류 DAC(173)가 전기적으로 접속된다. 여기서, 샘플링 기간은 한 프레임 기간 중 초기 기간 동안 위치된다. 샘플링 기간의 위치에 대한 상세한 설명은 후술하기로 한다.

<74> 전류 소스부(172)는 피드백선(F<sub>m</sub>)으로 정전류를 공급한다. 이를 위해, 전류 소스부(172)는 전류원(177)을 포함한다. 전류원(177)은 소정의 전류를 피드백선(F<sub>m</sub>)으로 공급한다. 여기서, 전류원(177)의 전류값은 열화정보에 대응하는 전압이 유기 발광 다이오드(OLED)에 인가될 수 있도록 설정된다. 실제로, 전류원(177)의 전류는 유기 발광 다이오드(OLED)에 소정의 전압이 인가될 수 있도록 실험적으로 다양하게 설정될 수 있다.

<75> ADC(174)는 전류 소스부(172)로부터 화소(140)로 전류가 공급될 때 유기 발광 다이오드에 인가되는 전압을 디지털값으로 변경한다.

<76> 메모리(175)는 ADC(174)로부터 공급되는 디지털값을 저장한다. 여기서, 메모리(175)는 화소부(130)에 포함되는 모든 화소들(140)의 디지털값이 포함될 수 있도록 그 용량이 설정된다.

<77> 제어부(176)는 메모리(175)에 저장되는 디지털값을 이용하여 화소들(140) 각각에 포함되는 유기 발광 다이오드(OLED)의 열화정보를 파악하고, 파악된 열화정보가 보상될 수 있도록 전류 DAC(173)를 제어한다.

<78> 상세히 설명하면, 전류 소스부(172)로부터 화소(140)로 전류가 공급될 때 유기 발광 다이오드(OLED)에는 소정의 전압이 인가된다. 여기서, 유기 발광 다이오드(OLED)가 열화 될수록 유기 발광 다이오드(OLED)에 인가되는 전압값은 증가한다. 따라서, 메모리(175)에 저장된 디지털값에는 유기 발광 다이오드(OLED)의 열화정보가 포함된다. 예를 들어, 유기 발광 다이오드(OLED)가 열화되지 않는 경우 메모리(175)에는 "0000"의 값이 저장된다면, 유기 발광 다이오드(OLED)가 열화되는 경우 메모리(175)에는 "0010"의 값이 저장될 수 있다. 이 경우, 제어부(176)는 디지털값에 대응하여 유기 발광 다이오드(OLED)의 열화가 보상될 수 있도록 전류 DAC(173)를 제어한다.

<79> 전류 DAC(173)는 화소(140)로부터 소정의 전류를 싱크한다. 여기서, 전류 DAC(173)에서 싱크되는 전류는 데이터 구동부(120) 및 제어부(176)의 제어에 의하여 그 값이 결정된다.

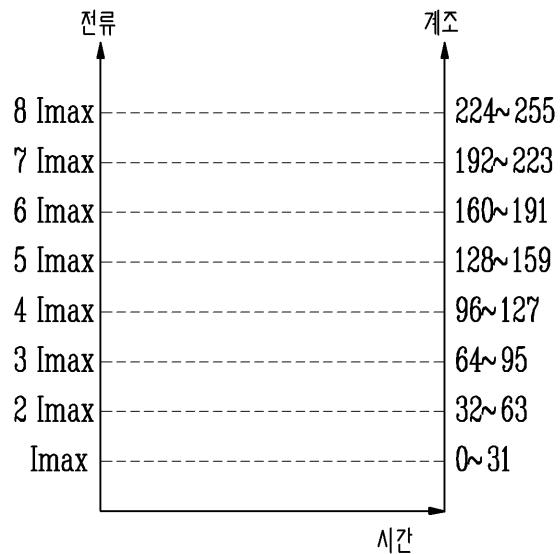

<80> 상세히 설명하면, 본 발명에서 전류 DAC(173)는 데이터(Data)의 비트(즉, 계조)에 대응하여 도 6과 같이 1(1은 자연수)개의 전류값 중 어느 하나의 전류를 싱크한다. 일례로, 전류 DAC(173)는 데이터(Data)의 상위 비트들에 대응하여 8개의 전류(I<sub>max</sub> 내지 8I<sub>max</sub>) 중 어느 하나의 전류를 화소(140)로부터 싱크한다. 여기서, 8개의 전류

(Imax 내지 8Imax) 중 어느 하나의 전류가 싱크된 후 화소들(140)의 발광 시간을 제어하여 세부계조를 표현한다. 예를 들어, 데이터(Data)의 계조가 "100"으로 설정되는 경우 전류 DAC(173)는 4Imax의 전류를 싱크한다. 그리고, 4Imax의 전류가 싱크된 화소(140)의 발광시간을 제어하여 "100"의 계조를 표현한다. 이 경우, 데이터(Data)의 상위비트들을 이용하여 4Imax의 전류가 싱크되고, 데이터(Data)의 하위비트들을 이용하여 발광시간이 제어된다.

<81> 한편, 전류 DAC(173)는 유기 발광 다이오드(OLED)의 열화가 보상될 수 있도록 추가적으로 전류를 싱크한다. 예를 들어, 데이터(Data)의 계조가 "100"을 설정되는 경우 전류 DAC(173)는  $\alpha$  4Imax의 전류를 싱크한다. 여기서,  $\alpha$ 는 유기 발광 다이오드(OLED)의 열화가 보상될 수 있도록 추가되는 전류를 의미한다. 그리고, 도 6에서 Imax는 데이터(Data)의 비트에 대응하여 전류 DAC(173)에서 싱크되는 가장 낮은 전류를 의미한다.

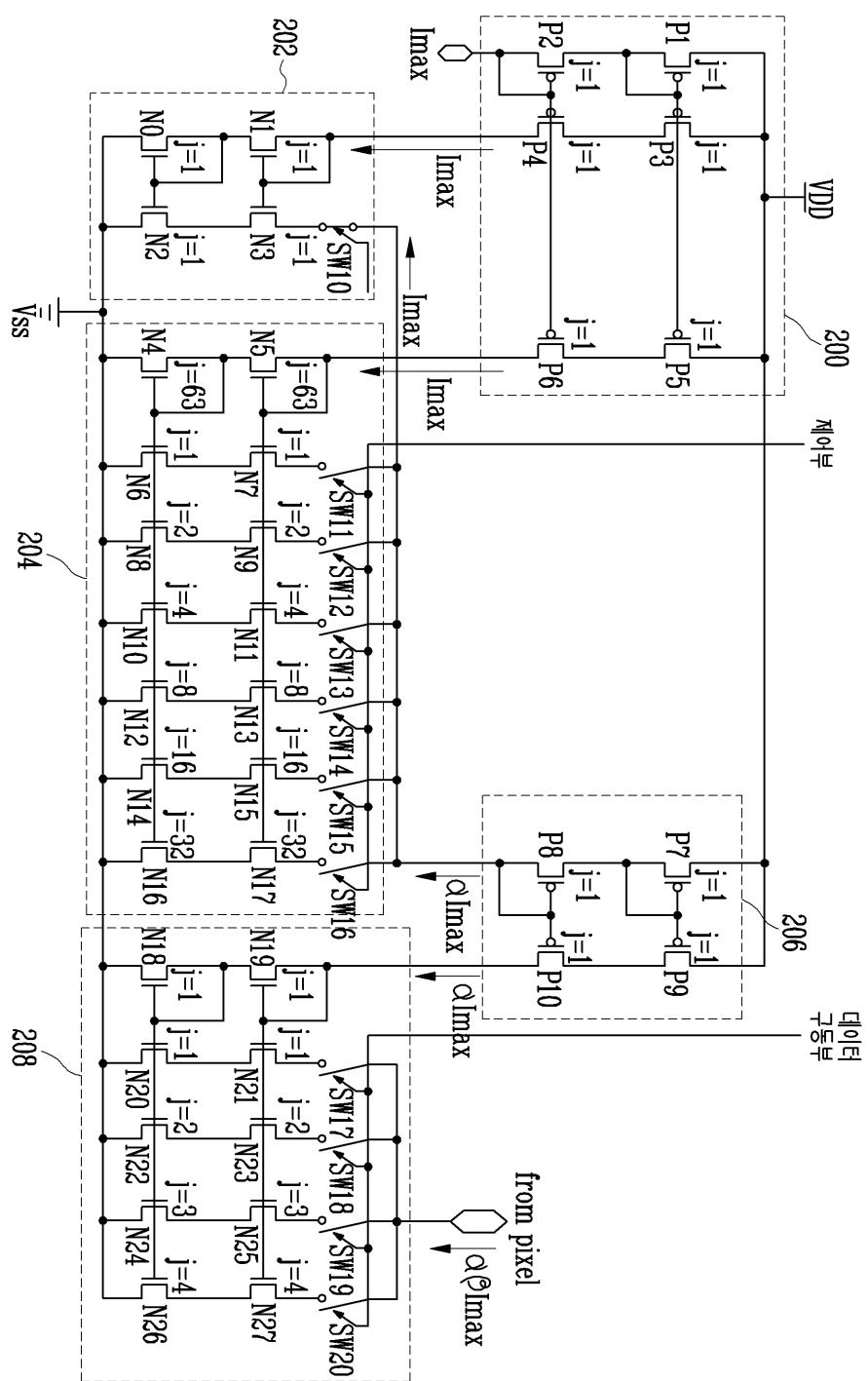

<82> 도 7은 도 4에 도시된 전류 DAC의 제 1실시예를 나타내는 도면이다. 도 7에서 j는 트랜지스터의 숫자를 의미한다. 그리고, 도 7에서  $\beta$ 는 데이터(Data)의 계조에 의하여 선택되는 전류를 의미한다. 예를 들어,  $\beta$ 는 도 6과 같이 1, 2, 3, 4, 5, 6, 7, 8중 어느 하나로 선택될 수 있다.

<83> 도 7을 참조하면, 본 발명의 제 1실시예에 의한 전류 DAC(173)는 Imax의 전류를 생성하기 위한 제 1전류 생성부(200)와, 제 1전류 생성부(200)와 접속되어 Imax의 전류를 싱크하기 위한 제 1전류 싱크부(202)와, 전류 생성부(200)와 접속되어  $\alpha$ 의 전류를 싱크하기 위한 제 2전류 싱크부(204)와, 제 1전류 싱크부(202)와 제 2전류 싱크부(204)와 접속되어  $\alpha$  Imax의 전류를 생성하기 위한 제 2전류 생성부(206)와, 제 2전류 생성부(206)와 접속되어 화소(140)로부터  $\beta$   $\alpha$  Imax의 전류를 싱크하기 위한 제 3전류 싱크부(208)를 구비한다.

<84> 제 1전류 생성부(200)는 Imax의 전류를 생성한다. 이를 위하여, 제 1전류 생성부(200)는 P1 내지 P6 트랜지스터를 구비한다. P1 트랜지스터 및 P2 트랜지스터는 다이오드 형태로 접속되어 제 3전원(VDD)으로부터 Imax의 전류가 흐를 수 있도록 채널폭이 설정된다.

<85> P3 트랜지스터 및 P4 트랜지스터는 제 3전원(VDD)과 제 1전류 싱크부(202) 사이에 직렬로 접속된다. 여기서, P3 트랜지스터는 P1 트랜지스터와 전류 미러로 접속되고, P4 트랜지스터는 P2 트랜지스터와 전류 미러로 접속된다. 이와 같은 P3 및 P4 트랜지스터는 Imax 전류를 제 1전류 싱크부(202)로 공급한다.

<86> P5 및 P6 트랜지스터는 제 3전원(VDD)과 제 2전류 싱크부(204)에 직렬로 접속된다. P5 트랜지스터는 P1 트랜지스터와 전류 미러로 접속되고, P6 트랜지스터는 P2 트랜지스터와 전류 미러로 접속된다. 이와 같은 P5 및 P6 트랜지스터는 Imax 전류를 제 2전류 싱크부(204)로 공급한다.

<87> 제 1전류 싱크부(202)는 제 2전류 생성부(206)로부터 Imax의 전류를 싱크한다. 이를 위하여, 제 1전류 싱크부(202)는 N0 내지 N3 트랜지스터를 구비한다. N0 및 N1 트랜지스터는 제 1전류 생성부(200)의 P4 트랜지스터와 제 4전원(VSS) 사이에서 다이오드 형태로 접속된다. 이와 같은 N0 및 N1 트랜지스터는 제 1전류 생성부(200)로부터 공급되는 Imax의 전류를 제 4전원(VSS)으로 공급한다.

<88> N2 및 N3 트랜지스터는 제 2전류 생성부(206)와 제 4전원(VSS) 사이에 접속된다. N3 트랜지스터는 N1 트랜지스터와 전류 미러로 접속되고, N2 트랜지스터는 N0 트랜지스터와 전류 미러로 접속된다. 따라서, N2 및 N3 트랜지스터는 제 2전류 생성부(206)로부터 Imax에 대응하는 전류를 싱크한다.

<89> 한편, N3 트랜지스터와 제 2전류 생성부(206) 사이에는 제 10스위치(SW10)가 설치된다. 제 10스위치(SW10)는 항상 턴-온 상태를 유지한다. 이와 같은 제 10스위치(SW10)는 제 2전류 싱크부(204)에 포함되는 스위치들(SW11 내지 SW16)과 저항을 맞추기 위하여 사용된다.

<90> 제 2전류 싱크부(204)는 제 2전류 생성부(206)로부터  $\alpha$ 의 전류를 싱크한다. 상세히 설명하면, 제 2전류 싱크부(204)는 제 1전류 생성부(200)와 제 4전원(VSS) 사이에는 직렬로 형성되는 N5 트랜지스터들 및 N4 트랜지스터들을 구비한다. 여기서, N5 트랜지스터들은 서로 병렬로 접속된다. 예를 들어, N5 트랜지스터들은 서로 병렬로 접속되는 63개의 트랜지스터로 구성된다. 그러면, 63개의 N5 트랜지스터 각각으로 Imax의 1/63에 해당하는 전류가 흐른다. 마찬가지로, N4 트랜지스터들은 서로 병렬로 접속되는 63개의 트랜지스터로 구성된다. 그러면, 63개의 N4 트랜지스터 각각으로 Imax의 1/63에 해당하는 전류가 흐른다. 실제로, N5 및 N4 트랜지스터들의 수는 다양하게 설정될 수 있다. 다만, N5 및 N4 트랜지스터들의 수는 스위치들(SW11 내지 SW16)과 접속되는 트랜지스터들(N6 내지 N17)의 수와 동일하게 설정된다.

<91> 또한, 제 2전류 싱크부(204)는 제 2전류 생성부(206)와 접속되는 제 11스위치(SW11) 내지 제 16스위치(SW16)와, 제 11스위치(SW11) 내지 제 16스위치(SW16) 각각과 제 4전원(VSS) 사이에 접속되는 트랜지스터들(N6 내지 N17)

을 구비한다.

- <92> 여기서, 제 11스위치(SW11) 내지 제 16스위치(SW16) 각각에 접속되는 트랜지스터의 수는  $2^k$ ( $k=0, 1, 2, 3, \dots$ )의 비율로 증가하도록 설정된다. 상세히 설명하면, 제 11스위치(SW11)와 제 4전원(VSS) 사이에는 각각 하나씩의 N7 트랜지스터 및 N6 트랜지스터가 형성된다. N7 트랜지스터는 N5 트랜지스터들과 전류 미러로 형성된다. N6 트랜지스터는 N4 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 11스위치(SW11)가 턴-온되는 경우 제 2전류 생성부(206)로부터  $I_{max}$ 의  $1/63$ 에 해당하는 전류가 추가적으로 싱크된다. 한편, 제 11스위치(SW11)와 제 4전원(VSS) 사이에는 N7 트랜지스터만이 형성될 수 있다.(즉, N6 제거) 이 경우, N4, N8, N10, N12, N14, N16, N2, N0 트랜지스터들도 제거된다. 본 발명에서는 안정성을 위하여 스위치들(SW11 내지 SW16)과 제 4전원(VSS) 사이에 직렬로 접속되도록 트랜지스터들을 형성하였지만 이에 한정되는 것은 아니다.

- <93> 제 12스위치(SW12)와 제 4전원(VSS) 사이에는 직렬로 각각 2개의 N9 트랜지스터 및 N8 트랜지스터가 형성된다. (여기서, N9 트랜지스터들 각각은 서로 병렬로 접속되고, N8 트랜지스터들 각각도 서로 병렬로 접속된다.) N9 트랜지스터들은 N5 트랜지스터들과 전류 미러로 형성된다. N8 트랜지스터들은 N4 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 12스위치(SW12)가 턴-온되는 경우 제 2전류 생성부(206)로부터  $I_{max}$ 의  $2/63$ 에 해당하는 전류가 추가적으로 싱크된다.

- <94> 제 13스위치(SW13)와 제 4전원(VSS) 사이에는 직렬로 각각 4개의 N11 트랜지스터 및 N10 트랜지스터가 형성된다. N11 트랜지스터들은 N5 트랜지스터들과 전류 미러로 형성된다. N10 트랜지스터들은 N4 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 13스위치(SW13)가 턴-온되는 경우 제 2전류 생성부(206)로부터  $I_{max}$ 의  $4/63$ 에 해당하는 전류가 추가적으로 싱크된다.

- <95> 제 14스위치(SW14)와 제 4전원(VSS) 사이에는 직렬로 각각 8개의 N13 트랜지스터 및 N12 트랜지스터가 형성된다. N13 트랜지스터들은 N5 트랜지스터들과 전류 미러로 형성된다. N12 트랜지스터들은 N4 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 14스위치(SW14)가 턴-온되는 경우 제 2전류 생성부(206)로부터  $I_{max}$ 의  $8/63$ 에 해당하는 전류가 추가적으로 싱크된다.

- <96> 제 15스위치(SW15)와 제 4전원(VSS) 사이에는 직렬로 각각 16개의 N15 트랜지스터 및 N14 트랜지스터가 형성된다. N15 트랜지스터들은 N5 트랜지스터들과 전류 미러로 형성된다. N14 트랜지스터들은 N4 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 15스위치(SW15)가 턴-온되는 경우 제 2전류 생성부(206)로부터  $I_{max}$ 의  $16/63$ 에 해당하는 전류가 추가적으로 싱크된다.

- <97> 제 16스위치(SW16)와 제 4전원(VSS) 사이에는 직렬로 각각 32개의 N17 트랜지스터 및 N16 트랜지스터가 형성된다. N17 트랜지스터들은 N5 트랜지스터들과 전류 미러로 형성된다. N16 트랜지스터들은 N4 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 16스위치(SW16)가 턴-온되는 경우 제 2전류 생성부(206)로부터  $I_{max}$ 의  $32/63$ 에 해당하는 전류가 추가적으로 싱크된다.

- <98> 한편, 제 11스위치(SW11) 내지 제 16스위치(SW16)는 제어부(176)에 의하여 턴-온 및 턴-오프가 제어된다. 제어부(176)는 제 2전류 생성부(206)로부터 유기 발광 다이오드(OLED)의 열화정보가 보상될 수 있는  $\alpha$ 의 전류가 흐를 수 있도록 제 11스위치(SW11) 내지 제 16스위치(SW16)를 제어한다.

- <99> 제 2전류 생성부(206)는  $\alpha I_{max}$ 의 전류를 제 3전류 싱크부(208)로 공급한다. 이를 위하여, 제 2전류 생성부(206)는 P7 내지 P10 트랜지스터를 구비한다. P7 트랜지스터는 제 3전원(VDD)과 접속되도록 형성되고, P8 트랜지스터는 제 1전류 싱크부(202)와 제 2전류 싱크부(204)와 접속되도록 형성된다. 그리고, P7 및 P8 트랜지스터는 서로 직렬로 접속됨과 아울러 다이오드 형태로 접속된다. 따라서, P7 및 P8 트랜지스터에서는 제 1전류 싱크부(202) 및 제 2전류 싱크부(204)로부터 싱크되는  $\alpha I_{max}$ 의 전류가 흐른다.

- <100> P9 트랜지스터 및 P10 트랜지스터는 제 3전원(VDD)과 제 3전류 싱크부(208) 사이에 직렬로 접속된다. 여기서, P9 트랜지스터는 P7 트랜지스터와 전류 미러로 접속되고, P10 트랜지스터는 P8 트랜지스터와 전류 미러로 접속된다. 이와 같은 P9 및 P10 트랜지스터는  $\alpha I_{max}$ 의 전류를 제 3전류 싱크부(208)로 공급한다.

- <101> 제 3전류 싱크부(208)는 화소(140)로부터  $\beta \alpha I_{max}$ 의 전류를 싱크한다. 제 3전류 싱크부(208)는 제 2전류 생성부(206)와 제 4전원(VSS) 사이에 직렬로 접속되는 N19 및 N18 트랜지스터를 구비한다. N19 및 N18 트랜지스터는 다이오드 형태로 접속되어 제 2전류 생성부(206)로부터 공급되는  $\alpha I_{max}$ 를 제 4전원(VSS)으로 공급한다.

- <102> 또한, 제 3전류 싱크부(208)는 스위칭부(171)와 접속되는 제 17스위치(SW17) 내지 제 20스위치(SW20)와, 제 17스위치(SW17) 내지 제 20스위치(SW20) 각각과 제 4전원(VSS) 사이에 접속되는 트랜지스터들(N20 내지 N27)을 구

비한다.

<103> 여기서, 제 17스위치(SW17) 내지 제 20스위치(SW20) 각각에 접속되는 트랜지스터의 수는 원하는  $\beta$ 의 전류가 흐를 수 있도록 설정된다. 예를 들어, 제 17스위치(SW17)와 제 4전원(VSS) 사이에는 각각 하나씩의 N21 트랜지스터 및 N20 트랜지스터가 형성된다. N21 트랜지스터는 N19 트랜지스터들과 전류 미러로 형성된다. N20 트랜지스터는 N18 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 17스위치(SW17)가 턴-온되는 경우  $a I_{max}$ 의 전류가 화소(140)로부터 싱크된다. 한편, 제 17스위치(SW17)와 제 4전원(VSS) 사이에는 N21 트랜지스터만이 형성될 수 있다.(즉, N20 제거) 이 경우, N18, N20, N22, N24, N26 트랜지스터들로 제거된다.

<104> 마찬가지로, 제 18스위치(SW18)와 제 4전원(VSS) 사이에는 각각 2개씩의 N23 및 N22의 트랜지스터가 형성된다. 따라서, 제 18스위치(SW18)가 턴-온되는 경우  $2a I_{max}$ 의 전류가 화소(140)로부터 싱크된다. 제 19스위치(SW19)와 제 4전원(VSS) 사이에는 각각 3개씩의 N25 및 N24 트랜지스터가 형성된다. 따라서, 제 19스위치(SW19)가 턴-온되는 경우  $3a I_{max}$ 의 전류가 화소(140)로부터 싱크된다. 제 20스위치(SW19)와 제 4전원 사이에는 각각 4개씩의 N27 및 N26 트랜지스터가 형성된다. 따라서, 제 20스위치(SW20)가 턴-온되는 경우  $4a I_{max}$ 의 전류가 화소(140)로부터 싱크된다. 여기서, 제 3전류 싱크부(208)에 4개의 스위치(SW17 내지 SW20)가 포함되는 것으로 도시하였지만 본 발명이 이에 한정되는 것은 아니다. 실제로, 원하는  $\beta$ 의 전류가 흐를 수 있도록 제 3전류 싱크부(208)에 포함되는 스위치(SW17 내지 SW20)의 수는 다양하게 설정될 수 있다.

<105> 한편, 제 17스위치(SW17) 내지 제 20스위치(SW20)는 데이터 구동부(120)로부터 공급되는 데이터(Data)의 상위비트들에 의하여 턴-온 및 턴-오프된다. 데이터 구동부(120)는 데이터(Data)의 상위 비트들 대응하여 제 17스위치(SW17) 내지 제 20스위치(SW20)의 턴-온 및 턴-오프를 제어하면서 계조에 대응하는  $\beta a I_{max}$ 의 전류가 화소(140)로부터 싱크되도록 한다.

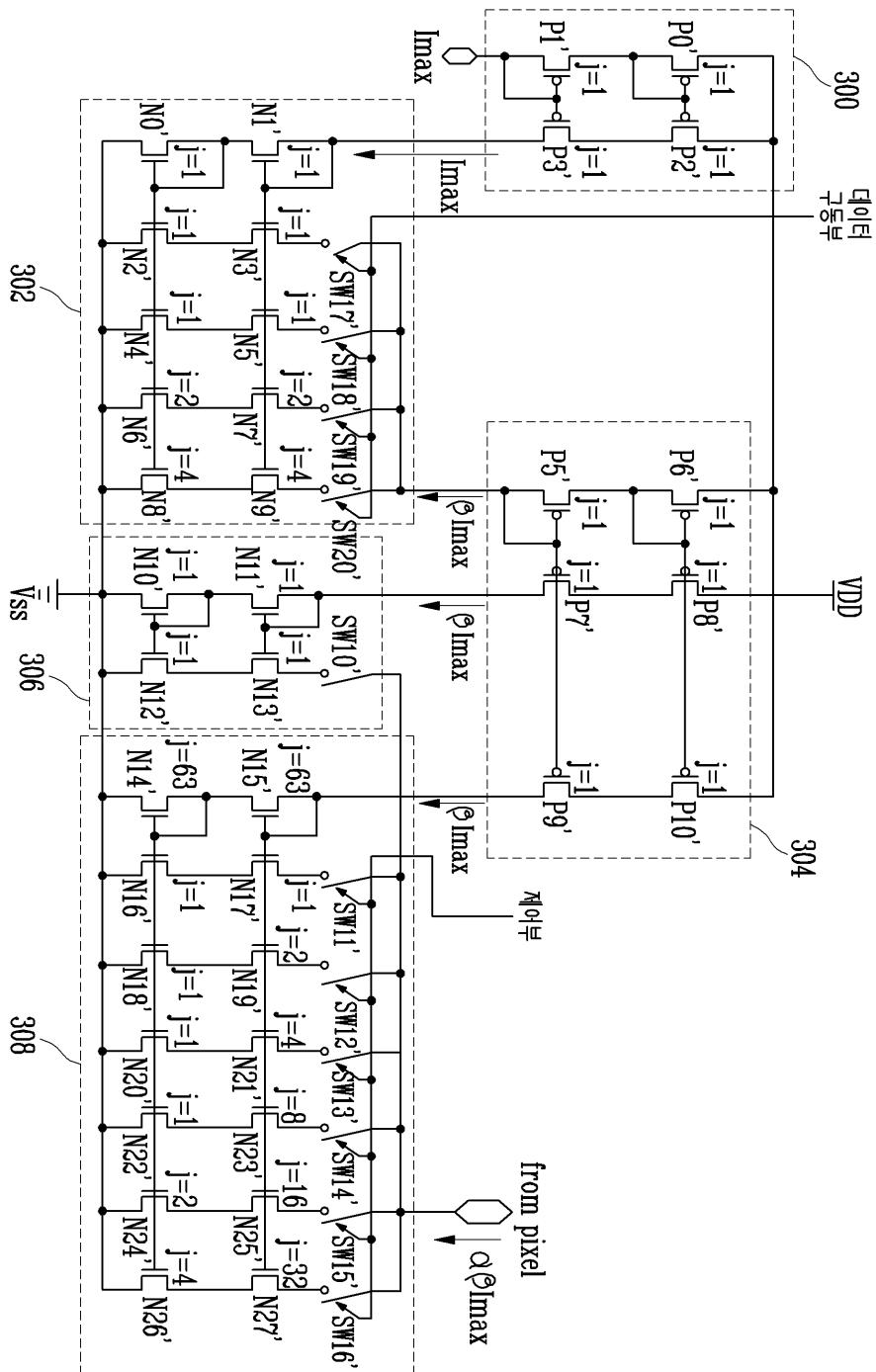

<106> 도 8은 도 4에 도시된 전류 DAC의 제 2실시예를 나타내는 도면이다. 도 8에서는  $\beta I_{max}$ 의 전류를 생성하고, 이후에  $a$ 의 전류를 생성한다는 점에서 도 7과 차이점이 있다.

<107> 도 8을 참조하면, 본 발명의 제 2실시예에 의한 전류 DAC(173)는  $I_{max}$ 의 전류를 생성하기 위한 제 1전류 생성부(300)와, 제 1전류 생성부(300)와 접속되어  $\beta I_{max}$ 의 전류를 싱크하기 위한 제 1전류 싱크부(302)와, 제 1전류 싱크부(302)와 접속되어  $\beta I_{max}$ 의 전류를 생성하기 위한 제 2전류 생성부(304)와, 제 2전류 생성부(304)와 접속되어 화소(140)로부터  $\beta I_{max}$ 의 전류를 싱크하기 위한 제 2전류 싱크부(306)와, 제 2전류 생성부(304)와 접속되어 화소(140)로부터  $a$ 의 전류를 싱크하기 위한 제 3전류 싱크부(308)를 구비한다.

<108> 제 1전류 생성부(300)는  $I_{max}$ 의 전류를 생성한다. 이를 위하여, 제 1전류 생성부(300)는 P0' 내지 P3' 트랜지스터를 구비한다. P0' 트랜지스터 및 P1' 트랜지스터는 다이오드 형태로 접속되어 제 3전원(VDD)으로부터  $I_{max}$ 의 전류가 흐를 수 있도록 채널폭이 설정된다.

<109> P2' 트랜지스터 및 P3' 트랜지스터는 제 3전원(VDD)과 제 1전류 싱크부(302) 사이에 직렬로 접속된다. 여기서, P2' 트랜지스터는 P0' 트랜지스터와 전류 미러로 접속되고, P3' 트랜지스터는 P1' 트랜지스터와 전류 미러로 접속된다. 이와 같은 P2' 및 P3' 트랜지스터는  $I_{max}$  전류를 제 1전류 싱크부(302)로 공급한다.

<110> 제 1전류 싱크부(302)는 제 1전류 생성부(300)로부터  $I_{max}$ 의 전류를 공급받으면서 제 2전류 생성부(304)로부터  $\beta I_{max}$ 의 전류를 싱크한다. 이를 위해, 제 1전류 싱크부(302)는 제 1전류 생성부(300)와 제 4전원(VSS) 사이에 직렬로 접속되는 N1' 및 N0' 트랜지스터를 구비한다. N1' 및 N0' 트랜지스터는 다이오드 형태로 접속되어 제 1전류 생성부(300)로부터 공급되는  $I_{max}$ 의 전류를 제 4전원(VSS)으로 공급한다.

<111> 또한, 제 1전류 싱크부(302)는 제 2전류 생성부(304)와 접속되는 제 17스위치(SW17') 내지 제 20스위치(SW20')와, 제 17스위치(SW17') 내지 제 20스위치(SW20') 각각과 제 4전원(VSS) 사이에 접속되는 트랜지스터들(N2' 내지 N9')을 구비한다.

<112> 여기서, 제 17스위치(SW17) 내지 제 20스위치(SW20) 각각에는  $\beta$ 에 대응하는 전류가 효율적으로 싱크될 수 있도록 접속되는 트랜지스터의 수가 설정된다. 예를 들어, 제 17스위치(SW17) 내지 제 20스위치(SW20) 각각에 접속되는 트랜지스터의 수는  $2^h$ ( $h=0, 1, 2, \dots$ )의 비율로 증가하도록 설정될 수 있다. 상세히 설명하면, 제 17스위치(SW17')와 제 4전원(VSS) 사이에는 각각 하나씩의 N2' 트랜지스터 및 N3' 트랜지스터가 형성된다. N3' 트랜지스터는 N1' 트랜지스터와 전류 미러로 형성된다. N2' 트랜지스터는 N0' 트랜지스터와 전류 미러로 형성된다. 따라서, 제 17스위치(SW17')가 턴-온되는 경우  $I_{max}$ 의 전류가 제 2전류 생성부(304)로부터 싱크된다. 한편, 제 17스위치(SW17')와 제 4전원(VSS) 사이에는 N3' 트랜지스터만이 형성될 수 있다.(즉, N2' 제거) 이

경우, N0', N4', N6', N8' 트랜지스터들도 제거된다.

<113> 마찬가지로, 제 18스위치(SW18')와 제 4전원(VSS) 사이에는 각각 하나씩의 N5' 및 N4'가 트랜지스터가 형성된다. 따라서, 제 18스위치(SW18')가 턴-온되는 경우  $I_{max}$ 의 전류가 제 2전류 생성부(304)로부터 싱크된다. 제 19스위치(SW19')와 제 4전원(VSS) 사이에는 각각 2개씩의 N7' 및 N6' 트랜지스터가 형성된다. 따라서, 제 19스위치(SW19')가 턴-온되는 경우  $2I_{max}$ 의 전류가 전류 생성부(304)로부터 싱크된다. 제 20스위치(SW20')와 제 4전원 사이에는 각각 4개씩의 N9' 및 N8' 트랜지스터가 형성된다. 따라서, 제 20스위치(SW20')가 턴-온되는 경우  $4I_{max}$ 의 전류가 제 2전류 생성부(304)로부터 싱크된다. . .

<114> 한편, 제 17스위치(SW17') 내지 제 20스위치(SW20')는 데이터 구동부(120)로부터 공급되는 데이터(Data)의 상위 비트들에 대응하여 턴-온 및 턴-오프 된다. 데이터 구동부(120)는 데이터(Data)의 상위비트들에 대응하여 제 17스위치(SW17') 내지 제 20스위치(SW20')의 턴-온 및 턴-오프를 제어하면서 계조에 대응하는  $\beta I_{max}$ 의 전류가 제 2전류 생성부(304)로부터 싱크되도록 한다.

<115> 제 2전류 생성부(304)는  $\beta I_{max}$ 의 전류를 제 2전류 싱크부(306) 및 제 3전류 싱크부(308)로 공급한다. 이를 위하여, 제 2전류 생성부(304)는 P5' 내지 P10' 트랜지스터를 구비한다.

<116> P6' 트랜지스터는 제 3전원(VDD)과 접속되도록 형성되고, P5' 트랜지스터는 제 1전류 싱크부(302)와 접속되도록 형성된다. 그리고, P6' 및 P5' 트랜지스터는 서로 직렬로 접속됨과 아울러 다이오드 형태로 접속된다. 따라서, P6' 및 P5' 트랜지스터에서는 제 1전류 싱크부(302)로부터 싱크되는  $\beta I_{max}$ 의 전류가 흐른다.

<117> P8' 및 P7' 트랜지스터는 제 3전원(VDD)과 제 2전류 싱크부(306) 사이에 직렬로 접속된다. 여기서, P8' 트랜지스터는 P6' 트랜지스터와 전류 미러로 접속되고, P7' 트랜지스터는 P5' 트랜지스터와 전류 미러로 접속된다. 이와 같은 P8' 및 P7' 트랜지스터는  $\beta I_{max}$ 의 전류를 제 2전류 싱크부(306)로 공급한다.

<118> P10' 및 P9' 트랜지스터는 제 3전원(VDD)과 제 3전류 싱크부(308) 사이에 직렬로 접속된다. 여기서, P10' 트랜지스터는 P6' 트랜지스터와 전류 미러로 접속되고, P9' 트랜지스터는 P5' 트랜지스터와 전류 미러로 접속된다. 이와 같은 P10' 및 P9' 트랜지스터는  $\beta I_{max}$ 의 전류를 제 3전류 싱크부(308)로 공급한다.

<119> 제 2전류 싱크부(306)는 스위칭부(171) 및 피드백선(Fm)을 경유하여 화소(140)로부터  $\beta I_{max}$ 의 전류를 싱크한다. 이를 위하여, 제 2전류 싱크부(306)는 N10' 내지 N13' 트랜지스터를 구비한다. N10' 및 N11' 트랜지스터는 제 2전류 생성부(304)의 P7' 트랜지스터와 제 4전원(VSS) 사이에 다이오드 형태로 접속된다. 이와 같은 N10' 및 N11' 트랜지스터는 다이오드 형태로 접속되어 제 2전류 생성부(304)로부터 공급되는  $\beta I_{max}$ 의 전류를 제 4전원(VSS)으로 공급한다.

<120> N13' 및 N12' 트랜지스터는 스위칭부(171)와 제 4전원(VSS) 사이에 접속된다. N13' 트랜지스터는 N11' 트랜지스터와 전류 미러로 접속되고, N12' 트랜지스터는 N10' 트랜지스터와 전류 미러로 접속된다. 따라서, N13' 및 N12' 트랜지스터는 화소(140)로부터  $\beta I_{max}$ 의 전류를 싱크한다.

<121> 한편, N13' 트랜지스터와 스위칭부(171) 사이에는 제 10스위치(SW10')가 설치된다. 제 10스위치(SW10')는 항상 턴-온 상태를 유지한다. 이와 같은 제 10스위치(SW10')는 제 3전류 싱크부(308)에 포함되는 스위치들(SW11' 내지 SW16')과 저항을 맞추기 위하여 사용된다.

<122> 제 3전류 싱크부(308)는 화소(140)로부터  $\alpha$ 의 전류를 싱크한다. 상세히 설명하면, 제 3전류 싱크부(308)는 제 2전류 생성부(304)와 제 4전원(VSS) 사이에 직렬로 형성되는 N15' 트랜지스터들 및 N14' 트랜지스터들을 구비한다. 여기서, N15' 트랜지스터들은 서로 병렬로 접속된다. 예를 들어, N15' 트랜지스터들은 서로 병렬로 접속되는 63개의 트랜지스터로 구성된다. 그러면, 63개의 N15' 트랜지스터 각각으로  $\beta I_{max}$ 의  $1/63$ 에 해당하는 전류가 흐른다. 마찬가지로, N14' 트랜지스터들은 서로 병렬로 접속되는 63개의 트랜지스터로 구성된다. 그러면, 63개의 N14' 트랜지스터 각각으로  $\beta I_{max}$ 의  $1/63$ 에 해당하는 전류가 흐른다. 실제로, N15' 및 N14' 트랜지스터들의 수는 다양하게 설정될 수 있다. 다만, N15' 및 N14' 트랜지스터들의 수는 스위치들(SW11' 내지 SW16')과 접속되는 트랜지스터들(N16' 내지 N27')의 수와 동일하게 설정된다.

<123> 또한, 제 3전류 싱크부(308)는 스위칭부(171)와 접속되는 제 11스위치(SW11') 내지 제 16스위치(SW16')와, 제 11스위치(SW11') 내지 제 16스위치(SW16') 각각과 제 4전원(VSS) 사이에 접속되는 트랜지스터들(N16' 내지 N27')을 구비한다.

<124> 여기서, 제 11스위치(SW11') 내지 제 16스위치(SW16') 각각에 접속되는 트랜지스터의 수는  $2^k$ ( $k=0, 1, 2, 3$ ,

...)의 비율로 증가하도록 설정된다. 상세히 설명하면, 제 11스위치(SW11')와 제 4전원(VSS) 사이에는 각각 하나씩의 N17' 트랜지스터 및 N16' 트랜지스터가 형성된다. N17' 트랜지스터는 N15' 트랜지스터들과 전류 미러로 형성된다. N16' 트랜지스터는 N14' 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 11스위치(SW11')가 턴-온되는 경우 화소(140)로부터  $\beta I_{max}$ 의 1/63에 해당하는 전류가 추가적으로 성크된다. 한편, 제 11스위치(SW11')와 제 4전원(VSS) 사이에는 N17' 트랜지스터만이 형성될 수 있다.(즉, N16' 제거) 이 경우, N14', N16', N18', N20', N22', N24', N26' 트랜지스터들도 제거된다.

<125> 제 12스위치(SW12')와 제 4전원(VSS) 사이에는 직렬로 각각 2개의 N19' 트랜지스터 및 N18' 트랜지스터가 형성된다.(여기서, N19' 트랜지스터들 각각은 서로 병렬로 접속되고, N18' 트랜지스터들 각각도 서로 병렬로 접속된다.) N19' 트랜지스터들은 N15' 트랜지스터들과 전류 미러로 형성된다. N18' 트랜지스터들은 N14' 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 12스위치(SW12')가 턴-온되는 경우 화소(140)로부터  $\beta I_{max}$ 의 2/63에 해당하는 전류가 추가적으로 성크된다.

<126> 제 13스위치(SW13')와 제 4전원(VSS) 사이에는 직렬로 각각 4개의 N21' 트랜지스터 및 N20' 트랜지스터가 형성된다. N21' 트랜지스터들은 N15' 트랜지스터들과 전류 미러로 형성된다. N20' 트랜지스터들은 N14' 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 13스위치(SW13')가 턴-온되는 경우 화소(140)로부터  $\beta I_{max}$ 의 4/63에 해당하는 전류가 추가적으로 성크된다.

<127> 제 14스위치(SW14')와 제 4전원(VSS) 사이에는 직렬로 각각 8개의 N23' 트랜지스터 및 N22' 트랜지스터가 형성된다. N23' 트랜지스터들은 N15' 트랜지스터들과 전류 미러로 형성된다. N22' 트랜지스터들은 N14' 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 14스위치(SW14')가 턴-온되는 경우 화소(140)로부터  $\beta I_{max}$ 의 8/63에 해당하는 전류가 추가적으로 성크된다.

<128> 제 15스위치(SW15')와 제 4전원(VSS) 사이에는 직렬로 각각 16개의 N25' 트랜지스터 및 N24' 트랜지스터가 형성된다. N25' 트랜지스터들은 N15' 트랜지스터들과 전류 미러로 형성된다. N24' 트랜지스터들은 N14' 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 15스위치(SW15')가 턴-온되는 경우 화소(140)로부터  $\beta I_{max}$ 의 16/63에 해당하는 전류가 추가적으로 성크된다.

<129> 제 16스위치(SW16')와 제 4전원(VSS) 사이에는 직렬로 각각 32개의 N27' 트랜지스터 및 N26' 트랜지스터가 형성된다. N27' 트랜지스터들은 N15' 트랜지스터들과 전류 미러로 형성된다. N26' 트랜지스터들은 N14' 트랜지스터들과 전류 미러로 형성된다. 따라서, 제 16스위치(SW16')가 턴-온되는 경우 화소(140)로부터  $\beta I_{max}$ 의 32/63에 해당하는 전류가 추가적으로 성크된다.

<130> 한편, 제 11스위치(SW11') 내지 제 16스위치(SW16')는 제어부(176)에 의하여 턴-온 및 턴-오프가 제어된다. 제어부(176)는 화소(140)로부터 유기 발광 다이오드(OLED)의 열화정보가 보상될 수 있는  $\alpha$ 의 전류가 흐를 수 있도록 제 11스위치(SW11') 내지 제 16스위치(SW16')를 제어한다.

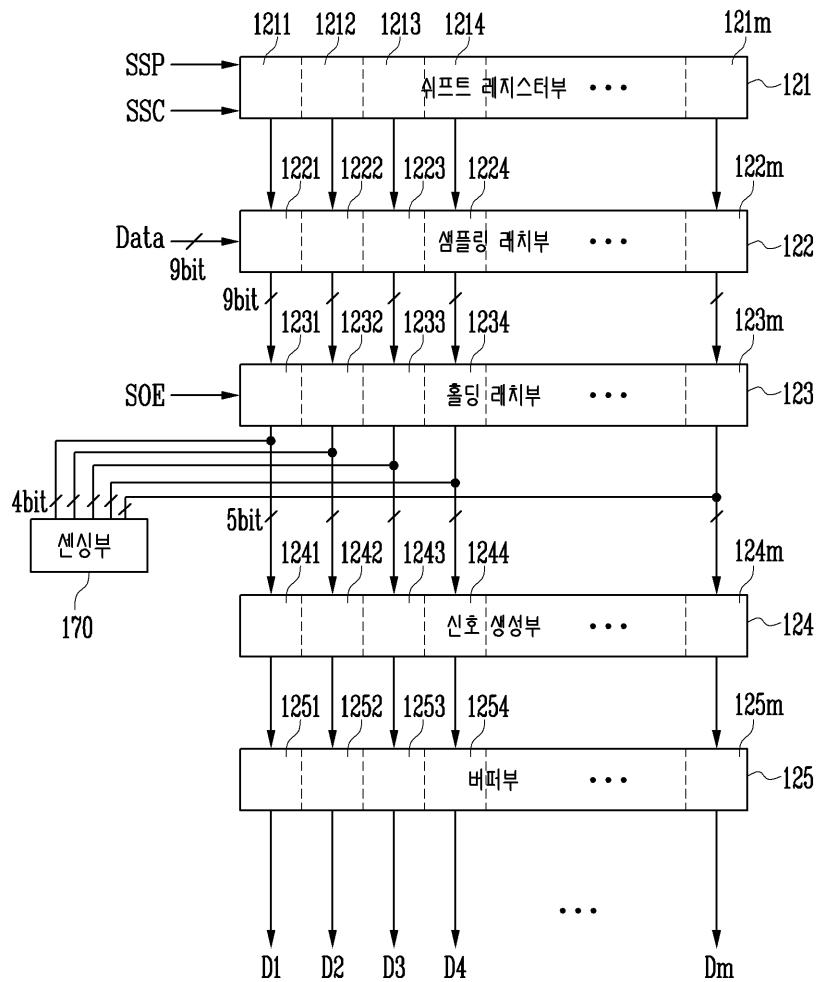

<131> 도 9는 도 2에 도시된 데이터 구동부를 나타내는 도면이다.

<132> 도 9를 참조하면, 데이터 구동부(120)는 쉬프트 레지스터부(121), 샘플링 래치부(122), 훌딩 래치부(123), 신호 생성부(124) 및 버퍼부(125)를 구비한다.

<133> 쉬프트 레지스터부(121)는 타이밍 제어부(150)로부터 소스 스타트 펄스(SSP) 및 소스 쉬프트 클럭(SSC)을 공급받는다. 소스 쉬프트 클럭(SSC) 및 소스 스타트 펄스(SSP)를 공급받은 쉬프트 레지스터(121)는 소스 쉬프트 클럭(SSC)의 1주기마다 소스 스타트 펄스(SSP)를 쉬프트 시키면서 순차적으로  $m$ 개의 샘플링 신호를 생성한다. 이를 위해, 쉬프트 레지스터부(121)는  $m$ 개의 쉬프트 레지스터(1211 내지 121m)를 구비한다.

<134> 샘플링 래치부(122)는 쉬프트 레지스터부(121)로부터 순차적으로 공급되는 샘플링 신호에 응답하여 데이터(Data)를 순차적으로 저장한다. 이를 위하여, 샘플링 래치부(122)는  $m$ 개의 데이터(Data)를 저장하기 위하여  $m$ 개의 샘플링 래치(1221 내지 122m)를 구비한다.

<135> 훌딩 래치부(123)는 타이밍 제어부(150)로부터 소스 출력 인에이블(SOE) 신호를 공급받는다. 소스 출력 인에이블(SOE) 신호를 공급받은 훌딩 래치부(123)는 샘플링 래치부(122)로부터 데이터(Data)를 입력 받아 저장한다. 그리고, 훌딩 래치부(123)는 자신에게 저장된 데이터(Data)를 센싱부(170) 및 신호 생성부(124)로 공급한다.

<136> 예를 들어, 데이터(Data)가 9비트인 경우 훌딩 래치부(123)는 상위 4비트를 센싱부(170)로 공급하고, 하위 5비트를 신호 생성부(124)로 공급할 수 있다. 여기서, 훌딩 래치들(1231 내지 123m) 각각은 채널들 각각에 위치되

는 전류 DAC(173)들로 상위 비트들을 공급한다.

<137> 신호 생성부(124)는 홀딩 래치부(123)로부터 데이터(Data)들의 하위비트들을 입력받고, 입력받은 데이터(Data)들에 대응하여  $m$ 개의 데이터신호를 생성한다. 이를 위하여, 신호 생성부(124)는  $m$ 개의 펠스 생성부(1241 내지 124m)를 구비한다. 즉, 신호 생성부(124)는 각각의 채널마다 위치되는 펠스 생성부들(1241 내지 124m)을 이용하여  $m$ 개의 데이터신호를 생성하고, 생성된 데이터신호를 버퍼부(125)로 공급한다.

<138> 버퍼부(125)는 신호 생성부(124)로부터 공급되는  $m$ 개의 데이터신호를  $m$ 개의 데이터선(D1 내지 Dm) 각각으로 공급한다. 이를 위해, 버퍼부(125)는  $m$ 개의 버퍼들(1251 내지 125m)을 구비한다.

<139> 도 10a 내지 도 10b는 센싱부의 동작과정을 나타내는 도면이다. 도 10a 및 도 10b를 설명할 때 설명의 편의성을 위하여 제  $m$ 데이터선(Dm) 및 제 1n주사선(S1n)과 접속된 화소를 도시하기로 한다.

<140> 도 10a 내지 도 10b를 참조하면, 먼저 센싱 기간 동안 제 2주사선(S2n)으로 제 2주사신호가 공급되고, 제어선(CL<sub>n</sub>)으로 제어신호가 공급된다. 그리고, 센싱 기간 동안 제 1스위치(SW1)가 터-온됨과 동시에 데이터선(Dm)으로 제 2데이터신호가 공급된다.

<141> 제 2주사선(S2n)으로 제 2주사신호가 공급되면 제 5트랜지스터(M5)가 터-온된다. 제 5트랜지스터(M5)가 터-온되면 데이터선(Dm)으로 공급되는 제 2데이터신호에 대응되는 전압이 제 2커패시터(C2)에 충전된다. 따라서, 센싱 기간 동안 제 4트랜지스터(M4)는 터-오프 상태를 유지한다.

<142> 제어선(CL<sub>n</sub>)으로 제어신호가 공급되면 제 6트랜지스터(M6)가 터-온된다. 이때, 제 1스위치(SW1)가 터-온되기 때문에 전류 소스부(172)로부터 공급되는 전류가 피드백선(Fm) 및 제 6트랜지스터(M6)를 경유하여 유기 발광 다이오드(OLED)로 공급된다. 이때, 유기 발광 다이오드(OLED)에는 전류 소스부(172)로부터 공급되는 전류에 대응하여 소정의 전압이 인가된다. 유기 발광 다이오드(OLED)에 인가된 전압은 ADC(174)에서 디지털 값으로 변경되어 메모리(175)에 저장된다.

<143> 실제로, 센싱 기간 동안에는 상술한 과정을 반복하면서 모든 화소들(140)의 디지털 값이 메모리(175)에 저장된다.

<144> 한편, ADC(174)가 모든 채널에 공통적으로 접속되는 경우 채널별로 위치되는 제 1스위치(SW1)는 순차적으로 터-온된다. 상세히 설명하면, 제어신호는 수평라인 단위로 순차적으로 공급된다. 예를 들어, j(j는 자연수)번째 제어선(CL<sub>j</sub>)으로 제어신호가 공급된다면 j번째 수평라인에 위치되는 화소들(140)에 각각 포함되는 제 6트랜지스터(M6)가 터-온된다. 이후, 제 1피드백선(F1)으로부터 제  $m$ 피드백선(Fm)과 접속된 제 1스위치(SW1)들이 순차적으로 터-온된다. 그러면, 제 1피드백선(F1)과 접속된 화소(140)로부터 제  $m$ 피드백선(Fm)과 접속된 화소(140)들의 디지털 값이 메모리(175)에 순차적으로 저장된다.

<145> 이후, 도 10b에 도시된 바와 같은 샘플링 기간 동안 제 1주사선(S1n)으로 제 1주사신호가 공급되고, 제 2주사선(S2n)으로 제 2주사신호가 공급된다. 그리고, 샘플링 기간 동안 제 2스위치(SW2)가 터-온됨과 동시에 데이터선(Dm)으로 제 2데이터신호가 공급된다.

<146> 제 2주사선(S2n)으로 제 2주사신호가 공급되면 제 5트랜지스터(M5)가 터-온된다. 제 5트랜지스터(M5)가 터-온되면 데이터선(Dm)으로 공급되는 제 2데이터신호에 대응되는 전압이 제 2커패시터(C2)에 충전된다. 따라서, 샘플링 기간 동안 제 4트랜지스터(M4)는 터-오프 상태를 유지한다.

<147> 제 1주사선(S1n)으로 제 1주사신호가 공급되면 제 2트랜지스터(M2) 및 제 3트랜지스터(M3)가 터-온된다. 따라서, 피드백선(Fm)과 제 1트랜지스터(M1)의 게이트전극 및 제 2전극이 전기적으로 접속된다.

<148> 한편, 샘플링 기간 동안 제어부(176)는 메모리(175)로부터 피드백선(Fm)과 접속된 화소(140)에 대응하는 디지털 값을 추출한다. 이후, 제어부(176)는 화소(140)의 열화가 보상될 수 있도록 제 11스위치(SW11) 내지 제 16스위치(SW16)의 터-온 및 터-오프를 제어한다. 그리고, 샘플링 기간 동안 데이터 구동부(120)는 데이터(Data)의 계조에 대응하는 전압이 싱크될 수 있도록 전류 DAC(173)를 제어한다.

<149> 그러면, 전류 DAC(173)에서 유기 발광 다이오드(OLED)의 열화가 보상됨과 아울러 데이터(Data)의 계조에 대응하는  $\alpha \beta I_{max}$ 의 전류가 싱크된다. 전류 DAC(173)에서 싱크되는  $\alpha \beta I_{max}$ 의 전류는 제 1전원(ELVDD), 제 1트랜지스터(M1), 제3트랜지스터(M3), 피드백선(Fm) 및 제 2스위치(SW2)를 경유하여 전류 DAC(173)로 공급된다. 따라서, 제 1트랜지스터(M1)의 게이트전극에는  $\alpha \beta I_{max}$ 의 전류가 흐를 수 있는 전압이 인가되고, 이 전압은 제 1커패시터(C1)에 충전된다.

- <150> 실제로, 샘플링 기간 동안에는 상술한 과정을 반복하면서 모든 화소들(140)의 제 1커패시터(C1) 각각에 소정의 전압을 충전한다. 상세히 설명하면, 샘플링 기간 동안 제 1주사선(S11 내지 S1n)으로 제 1주사신호가 순차적으로 공급되고, 제 2주사선(S11 내지 S2n)으로 제 2주사신호가 순차적으로 공급된다.

- <151> 이때, 제어부(176) 및 타이밍 제어부(150)는 각각의 채널에 위치되는 전류 DAC(173)를 제어하면서 유기 발광 다이오드(OLED)의 열화가 보상됨과 동시에 데이터(Data)의 계조에 대응하는 전류를 각각의 화소들(140)로부터 성크한다.

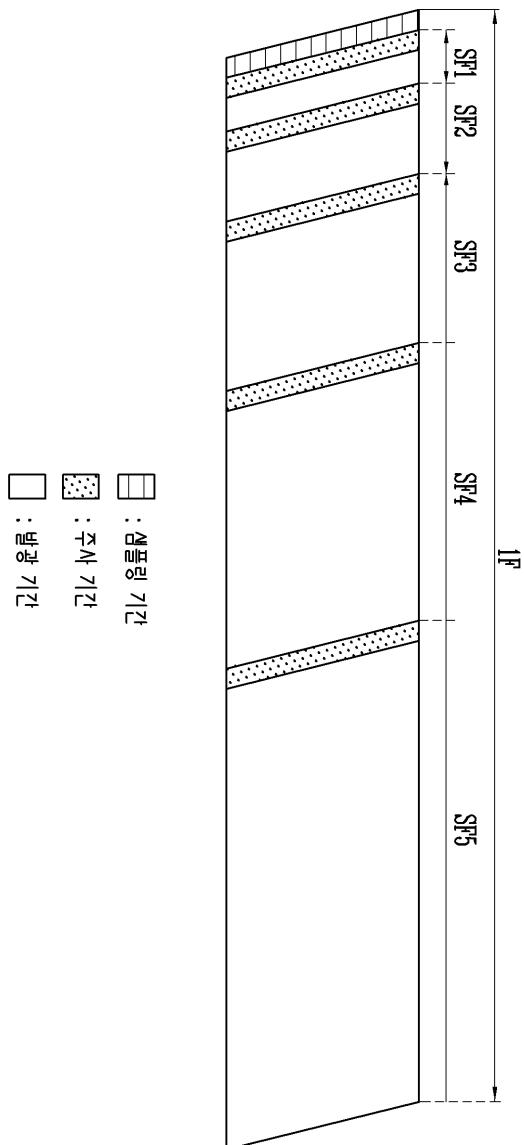

- <152> 도 11은 본 발명에 의한 한 프레임의 실시예를 나타내는 도면이다.

- <153> 도 11을 참조하면, 먼저 각각의 프레임은 샘플링 기간과 다수의 서브 프레임(SF1 내지 SF5)으로 이루어진다. 샘플링 기간은 서브 프레임(SF1 내지 SF5) 이전에 위치되어 각각의 화소들(140)에 포함되는 제 1커패시터(C1)에 소정의 전압을 충전한다. 여기서, 제 1커패시터(C1)에 충전되는 전압은 데이터(Data)의 계조에 대응하여 서로 다르게 설정된다. 도한, 제 1커패시터(C1)에 충전되는 전압은 유기 발광 다이오드(OLED)의 열화가 보상될 수 있도록 설정된다.

- <154> 서브 프레임(SF1 내지 SF5)은 주사기간 및 발광기간으로 나누어 구동된다. 주사기간 동안 제 2주사선(S21 내지 S2n)으로 제 2주사신호가 순차적으로 공급된다. 그리고, 제 2주사신호와 동기되도록 데이터선들(D1 내지 Dm)로 데이터신호가 공급된다. 그러면, 화소들(140) 각각에 포함되는 제 2커패시터(C2)에 제 1데이터신호 또는 제 2데이터신호에 대응하는 전압이 충전된다.

- <155> 발광 기간에는 제 2커패시터(C2)에 대응되는 전압에 대응하여 제 4트랜지스터(M4)가 턠-온 또는 턠-오프된다. 제 4트랜지스터(M4)가 턠-오프되는 경우 해당 서브 프레임 기간 동안 화소(140)는 비발광 상태로 설정된다. 제 4트랜지스터(M4)가 턠-온되는 경우 제 1커패시터(C1)에 충전된 전압에 대응하는 전류가 제 1트랜지스터(M1)로부터 유기 발광 다이오드(OLED)로 공급되고, 이에 따라 유기 발광 다이오드(OLED)가 발광 상태로 설정된다.

- <156> 한편, 제 1커패시터(C1)에 충전되는 전압은 도 6과 같이 데이터(Data)의 일부 계조에 대응하는 전압이기 때문에 발광기간의 시간을 이용하여 미세한 계조를 표현한다. 또한, 제 1커패시터(C1)에 충전되는 전압은 유기 발광 다이오드(OLED)의 열화가 보상될 수 있도록 설정되기 때문에 유기 발광 다이오드(OLED)에서 원하는 휘도의 빛을 생성할 수 있다. 또한, 제 1트랜지스터(M1)를 경유하여 싱크된 전류에 대응하는 전압이 제 1커패시터(C1)에 충전되기 때문에 제 1트랜지스터(M1)의 문턱전압 불균일 및 이동도 편차와 무관하게 균일한 휘도의 영상을 표시할 수 있다.

- <157> 상기 발명의 상세한 설명과 도면은 단지 본 발명의 예시적인 것으로서, 이는 단지 본 발명을 설명하기 위한 목적에서 사용된 것이지 의미 한정이나 특허청구범위에 기재된 본 발명의 범위를 제한하기 위하여 사용된 것은 아니다. 따라서, 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 보호 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허청구범위에 의해 정하여 져야만 할 것이다.

### 발명의 효과

- <158> 상술한 바와 같이, 본 발명의 실시 예에 따른 유기전계발광 표시장치 및 그의 구동방법에 의하면 유기 발광 다이오드로 전류를 공급하면서 유기 발광 다이오드에 인가되는 전압을 디지털 값에 변경하여 메모리에 저장한다. 이후, 메모리에 저장된 디지털 값에 대응하여 유기 발광 다이오드의 열화가 보상될 수 있도록 화소로부터 싱크되는 전류량을 조절한다. 그러면, 유기 발광 다이오드의 열화가 보상되고, 이에 따라 원하는 휘도의 영상을 표시할 수 있는 장점이 있다. 또한, 본 발명에서는 데이터의 계조(비트값)에 대응하여 싱크되는 전류를 몇개의 전류로 분할하기 때문에 계조 표현력을 향상시킬 수 있다.

### 도면의 간단한 설명

- <1> 도 1은 일반적인 유기전계발광 표시장치의 화소를 나타내는 도면이다.

- <2> 도 2는 본 발명의 실시예에 의한 유기전계발광 표시장치를 나타내는 도면이다.

- <3> 도 3은 도 2에 도시된 화소의 실시예를 나타내는 도면이다.

- <4> 도 4는 도 2에 도시된 센싱부를 나타내는 도면이다.

- <5> 도 5는 도 4에 도시된 스위칭부를 나타내는 도면이다.

- <6> 도 6은 도 4에 도시된 전류 DAC에서 싱크되는 전류 레벨을 나타내는 도면이다.

- <7> 도 7은 도 4에 도시된 전류 DAC의 제 1실시예를 나타내는 도면이다.

- <8> 도 8은 도 4에 도시된 전류 DAC의 제 2실시예를 나타내는 도면이다.

- <9> 도 9는 도 2에 도시된 데이터 구동부를 나타내는 도면이다.

- <10> 도 10a 및 도 10b는 센싱부의 동작과정을 나타내는 도면이다.

- <11> 도 11은 본 발명의 한 프레임 실시예를 나타내는 도면이다.

## &lt;도면의 주요 부분에 대한 부호의 설명&gt;

|      |                                  |                          |

|------|----------------------------------|--------------------------|

| <13> | 2,142 : 화소회로                     | 4,140 : 화소               |

| <14> | 110 : 주사 구동부                     | 120 : 데이터 구동부            |

| <15> | 121 : 쉬프트 레지스터부                  | 122 : 샘플링 래치부            |

| <16> | 123 : 훌딩 래치부                     | 124 : 신호 생성부             |

| <17> | 125 : 베틀부                        | 130 : 화소부                |

| <18> | 150 : 타이밍 제어부                    | 160 : 제어선 구동부            |

| <19> | 170 : 센싱부                        | 171 : 스위칭부               |

| <20> | 172 : 전류 소스부                     | 173 : 전류 DAC             |

| <21> | 174 : ADC                        | 175 : 메모리                |

| <22> | 176 : 제어부                        | 200,206,300,304 : 전류 생성부 |

| <23> | 202,204,208,302,306,308 : 전류 싱크부 |                          |

**도면****도면1**

## 도면2

## 도면3

140

## 도면4

도면5

도면6

## 도면7

## 도면8

## 도면9

120

도면10a

도면10b

도면11

|                |                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光显示装置及其驱动方法                                                            |         |            |

| 公开(公告)号        | <a href="#">KR100889681B1</a>                                               | 公开(公告)日 | 2009-03-19 |

| 申请号            | KR1020070075430                                                             | 申请日     | 2007-07-27 |

| [标]申请(专利权)人(译) | 三星显示有限公司<br>汉阳大学校产学协力团                                                      |         |            |

| 申请(专利权)人(译)    | 三圣母工作显示有限公司<br>汉阳大学产学合作基金会                                                  |         |            |

| 当前申请(专利权)人(译)  | 三圣母工作显示有限公司<br>汉阳大学产学合作基金会                                                  |         |            |

| [标]发明人         | OHKYONG KWON                                                                |         |            |

| 发明人            | OHKYONG KWON                                                                |         |            |

| IPC分类号         | G09G3/30 G09G3/32 G09G3/20 G01R19/00                                        |         |            |

| CPC分类号         | G09G2300/0852 G09G2320/0295 G09G2320/043 G09G3/3233 G09G3/3283 G09G2320/045 |         |            |

| 代理人(译)         | SHIN , YOUNG MOO                                                            |         |            |

| 其他公开文献         | KR1020090011638A                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                   |         |            |

## 摘要(译)

一种有机发光显示器，其包括像素，每个像素包括有机发光二极管和用于控制向有机发光二极管的电流供应的像素电路；感测单元，其用于在采样时段期间的感测时段期间将施加到有机发光二极管的电压转换为数字值，并且用于从与数字值相对应的像素吸收第二电流以补偿有机光的劣化。在一个采样周期内发光二极管。