# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) Int. Cl.

**G09G 3/30** (2006.01)

(21) 출원번호 10-2002-7008789

(22) 출원일자 2002년07월06일 심사청구일자 2006년10월20일

번역문제출일자 **2002년07월06일**

(65) 공개번호10-2002-0069241(43) 공개일자2002년08월29일

(86) 국제출원번호 PCT/JP2001/009735

국제출원일자 **2001년11월07일** (87) 국제공개번호 **WO 2002/39420**

(87) 국제공개번호 **WO 2002/39420** 국제공개일자 **2002년05월16일**

(30) 우선권주장

JP-P-2000-00338688 2000년11월07일 일본(JP) (뒷면에 계속)

(56) 선행기술조사문헌 KR1020010031766 A KR1020020018264 A (45) 공고일자 2008년05월20일

(11) 등록번호 10-0830772 (24) 등록일자 2008년05월13일

(73) 특허권자

소니 가부시끼 가이샤

일본국 도쿄도 미나토쿠 코난 1-7-1

(72) 발명자

유모또, 아끼라

일본141-0001도꾜도시나가와꾸기따시나가와6 쪼메7-35소니가부시끼가이샤내

(74) 대리인

구영창, 장수길

전체 청구항 수 : 총 60 항 심사관 : 김남인

## (54) 액티브 매트릭스형 표시 장치 및 액티브 매트릭스형 유기일렉트로 루미네센스 표시 장치

#### (57) 요 약

전류 기입형의 화소 회로를 채용한 경우에는, 각 화소에의 데이터의 기입을 선순차로 행할 필요가 있다. 전류 기입형 화소 회로(11)를 매트릭스 형상으로 배치하여 이루어지는 액티브 매트릭스형 표시 장치에 있어서, 데이터 선(13-1~13-m)의 각각에 대응하여 설치된 m개의 전류 드라이버 회로(CD)(15-1~15-m)로 이루어지는 데이터선 드라이버 회로(15)를 설치하고, 이 데이터선 드라이버 회로(15)에서 화상 데이터(본 예에서는 휘도 데이터)를 일단 유지하고, 그런 후 이것을 전류의 형태로 데이터선(13-1~13-m)의 각각에 제공함으로써 각 화소 회로(11)에 대한 화상 정보의 기입 구동을 행하도록 한다.

## **대표도** - 도1

## (81) 지정국

국내특허: 대한민국, 미국, 중국, 싱가포르 EP 유럽특허: 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투 칼, 스웨덴, 핀란드, 사이프러스, 터어키

# (30) 우선권주장

JP-P-2001-00231807 2001년07월31일 일본(JP) JP-P-2001-00320936 2001년10월18일 일본(JP) JP-P-2001-00339772 2001년11월05일 일본(JP)

#### 특허청구의 범위

#### 청구항 1

액티브 매트릭스형 표시 장치에 있어서.

화상 정보가 전류의 형태로 주어지는 화소 회로가 매트릭스 형상으로 배치됨과 함께, 이들 각 화소 회로를 선택하는 복수개의 주사선 및 각 화소 회로에 화상 정보를 공급하는 복수개의 데이터선이 배선되어 이루어지는 표시부와,

화상 정보를 일단 유지한 후 전류의 형태로 상기 복수개의 데이터선의 각각에 제공함으로써 각 화소 회로에 대한 화상 정보의 기입 구동을 행하는 구동 회로를 구비한 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 2

제1항에 있어서,

상기 화소 회로의 각각은 흐르는 전류에 의해서 휘도가 변화하는 전기 광학 소자를 구비하고,

상기 구동 회로는 휘도에 따른 크기의 전류를, 상기 복수개의 데이터선을 통해 상기 화소 회로의 각각에 흘림으로써 화상 정보의 기입을 행하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 3

제1항에 있어서,

상기 구동 회로는 상기 복수개의 데이터선마다 설치되고, 상기 화상 정보를 전압의 형태로 유지하는 유지부와, 상기 유지부에서 유지한 전압을 전류로 변환하여 상기 복수개의 데이터선의 각각에 공급하는 구동부를 갖는 것 을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 4

제3항에 있어서.

상기 구동 회로는 상기 화상 정보가 전류의 형태로 주어지고, 이 전류를 전압으로 변환하는 변환부를 구비하고, 이 변환부에서 변환한 전압을 상기 유지부에서 유지하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 5

제4항에 있어서,

상기 구동 회로에 있어서,

상기 변환부는 드레인과 게이트가 전기적으로 단락된 상태에 있을 때, 상기 화상 정보가 전류의 형태로 공급됨으로써 그 게이트·소스 사이에 전압을 발생하는 제1 전계 효과 트랜지스터를 포함하고,

상기 유지부는 상기 제1 전계 효과 트랜지스터의 게이트·소스 사이에서 발생하는 전압을 유지하는 캐패시터를 포함하고,

상기 구동부는 상기 캐피시터의 유지 전압에 기초하여 상기 복수개의 데이터선의 각각을 구동하는 제2 전계 효과 트랜지스터를 포함하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 6

액티브 매트릭스형 표시 장치에 있어서,

화상 정보가 전류의 형태로 주어지는 화소 회로가 매트릭스 형상으로 배치됨과 함께, 이들 각 화소 회로를 선택하는 복수개의 주사선 및 각 화소 회로에 화상 정보를 공급하는 복수개의 데이터선이 배선되어 이루어지는 표시부와,

화상 정보를 일단 유지한 후 전류의 형태로 상기 복수개의 데이터선의 각각에 제공함으로써 각 화소 회로에 대한 화상 정보의 기입 구동을 행하는 구동 회로를 구비하고,

상기 구동 회로는 상기 화상 정보가 전류의 형태로 주어지고, 이 전류를 전압으로 변환하는 변환부와, 이 변환부에서 변환한 전압을 유지하는 유지부와, 해당 유지부에서 유지한 전압을 전류로 변환하여 상기 복수개의 데이터선의 각각에 공급하는 구동부를 구비하고,

상기 변환부와 상기 구동 회로에 상기 화상 정보를 공급하는 전류원과의 사이에, 상기 화상 정보의 기입 시에 포화 영역에서 동작하는 임피던스 변환용 트랜지스터를 구비하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 7

제6항에 있어서,

상기 변환부는, 드레인과 게이트가 전기적으로 단락된 상태에 있을 때, 상기 화상 정보가 전류의 형태로 공급됨으로써 그 게이트·소스 사이에 전압을 발생하는 제1 전계 효과 트랜지스터를 포함하고,

상기 유지부는 상기 제1 전계 효과 트랜지스터의 게이트·소스 사이에 발생하는 전압을 유지하는 캐패시터를 포함하고,

상기 구동부는 상기 캐패시터의 유지 전압에 기초하여 상기 복수개의 데이터선의 각각을 구동하는 제2 전계 효과 트랜지스터를 포함하며.

상기 제1 전계 효과 트랜지스터와 상기 구동 회로에 상기 화상 정보를 공급하는 전류원과의 사이에, 상기 화상 정보의 기입 시에 포화 영역에서 동작하는 임피던스 변환용 트랜지스터를 갖는 것을 특징으로 하는 액티브 매트 릭스형 표시 장치.

#### 청구항 8

제7항에 있어서,

상기 임피던스 변환용 트랜지스터는, 상기 제1 전계 효과 트랜지스터와 도전형이 다른 트랜지스터이고, 상기 구동 회로마다 설치되어 있는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 9

제7항에 있어서,

상기 복수개의 데이터선마다 설치된 상기 구동 회로가 블록화되어 있고,

상기 임피던스 변환용 트랜지스터는 블록 내의 복수의 구동 회로에 대하여 공통으로 설치되어 있는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 10

제5항에 있어서,

상기 구동 회로는, 상기 제1, 제2 전계 효과 트랜지스터로서 동일한 트랜지스터를 이용하고,

상기 제1 전계 효과 트랜지스터에 의한 전류-전압의 변환과, 그것에 기초하는 상기 제2 전계 효과 트랜지스터에 의한 데이터선의 구동을 시분할적으로 행하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 11

제5항에 있어서,

상기 구동 회로는, 상기 화상 정보를 입력하는 신호 입력선과 상기 제1 전계 효과 트랜지스터를 접속 또는 차단하는 제1 스위치 소자와, 상기 제1 전계 효과 트랜지스터의 드레인과 게이트를 접속 또는 차단하는 제2 스위치소자를 구비하고,

상기 화상 정보의 취득 시에는 상기 제1 및 제2 스위치 소자를 접속 상태로 하고, 그 취득 종료 시에는 상기 제2 스위치 소자를 차단 상태로 하고, 그런 후 상기 제1 스위치 소자를 차단 상태로 하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 12

제5항에 있어서,

상기 구동 회로는, 상기 제1, 제2 전계 효과 트랜지스터로서 동일한 특성을 갖는 트랜지스터를 이용하고,

상기 제1, 제2 전계 효과 트랜지스터는, 전류 미러 회로를 형성하고 있는 것을 특징으로 하는 액티브 매트릭스 형 표시 장치.

#### 청구항 13

제12항에 있어서,

상기 구동 회로는, 상기 화상 정보를 입력하는 신호 입력선과 상기 제1 전계 효과 트랜지스터를 접속 또는 차단하는 제1 스위치 소자와, 상기 제1 전계 효과 트랜지스터의 게이트와 상기 제2 전계 효과 트랜지스터의 게이트 를 접속 또는 차단하는 제2 스위치 소자를 구비하고,

상기 화상 정보의 취득 시에는 상기 제1 및 상기 제2 스위치 소자를 접속 상태로 하고, 그 취득 종료 시에는 상기 제2 스위치 소자를 차단 상태로 하고, 그런 후 상기 제1 스위치 소자를 차단 상태로 하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 14

제13항에 있어서,

상기 구동 회로에서 상기 제1 전계 효과 트랜지스터의 채널 폭/채널 길이가, 상기 제2 전계 효과 트랜지스터의 채널 폭/채널 길이보다도 큰 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 15

제11항에 있어서,

상기 구동 회로는, 상기 제1 스위치 소자와 상기 제1 전계 효과 트랜지스터와의 사이에 접속된 제3 전계 효과 트랜지스터와, 상기 제3 전계 효과 트랜지스터의 드레인과 게이트와의 사이를 접속 또는 차단하는 제3 스위치 소자와, 상기 제3 전계 효과 트랜지스터의 게이트에 접속된 제2 캐패시터를 구비하고,

상기 제1 전계 효과 트랜지스터가 상기 제2 스위치 소자에 의해, 또한 상기 제3 전계 효과 트랜지스터가 상기 제3 스위치 소자에 의해, 함께 드레인과 게이트가 접속된 상태에 있을 때, 이들 트랜지스터의 드레인·소스 사이에 상기 제1 스위치 소자를 통해서 상기 화상 정보가 전류의 형태로 공급되는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 16

제3항에 있어서,

상기 복수개의 데이터선마다 설치된 복수개의 상기 구동 회로는 동일한 신호 입력선을 공유하고, 이것을 시분할 적으로 사용하면서 화상 정보의 취득을 행하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 17

제3항에 있어서,

상기 구동 회로는 상기 화상 정보가 전압의 형태로 주어지고, 이 전압을 상기 유지부에서 유지하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 18

제17항에 있어서,

상기 구동 회로에서,

상기 유지부는 상기 화상 정보에 따른 전압을 유지하는 유지 캐패시터를 포함하고,

상기 구동 회로는, 상기 유지 캐패시터의 유지 전압에 기초하여 상기 복수개의 데이터선의 각각을 구동하는 전계 효과 트랜지스터를 포함하고.

상기 전계 효과 트랜지스터는, 그 게이트·드레인이 전기적으로 단락되는 동작 후에, 그 게이트와 신호 입력선이 기입 캐패시터를 통해 용량 결합된 상태에서 화상 정보가 제공되는 것을 특징으로 하는 액티브 매트릭스형표시 장치.

#### 청구항 19

제18항에 있어서,

상기 구동 회로는 상기 기입 캐패시터의 신호 입력선측 노드와 소정의 전위점과의 사이에 접속된 스위치 소자를 구비하고,

상기 전계 효과 트랜지스터가 그 게이트·드레인 사이가 전기적으로 접속되는 동작이 행해지고 있는 동안에, 상기 스위치 소자가 단락됨으로써 상기 기입 캐패시터의 신호 입력선측 노드가 상기 소정의 전위가 되는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 20

제3항에 있어서,

상기 구동 회로는, 1개의 데이터선에 대하여 복수계통씩 설치되어 있는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 21

제20항에 있어서,

상기 구동 회로는, 1개의 데이터선에 대하여 2계통씩 설치되고, 한쪽의 계통의 구동 회로가 데이터선을 구동하는 동안에 다른 쪽의 계통의 구동 회로가 화상 정보의 취득을 행하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 22

제20항에 있어서,

상기 구동 회로는, 1개의 데이터선에 대하여 3계통씩 설치되고, 임의의 주사 사이클에서 1계통의 구동 회로가 리세트 동작을, 다른 1계통의 구동 회로가 데이터 피(被)기입 동작을, 남은 1계통이 데이터선 구동 동작을 행하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 23

제1항에 있어서,

상기 구동 회로를 구성하는 트랜지스터는, 상기 화소 회로를 구성하는 트랜지스터와 동시에 형성되는 박막 트랜 지스터인 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 24

제1항에 있어서,

상기 화상 정보를 입력하는 신호 입력선과 소정의 전위점과의 사이에 누설 소자를 갖는 것을 특징으로 하는 액 티브 매트릭스형 표시 장치.

#### 청구항 25

제1항에 있어서,

상기 화상 정보를 입력하는 신호 입력선과 소정의 전위점과의 사이에, 상기 신호 입력선을 통해서 상기 구동 회로에 상기 화상 정보를 공급하는 데 앞서서 상기 신호 입력선의 전위를 소정의 값으로 설정하는 초기치 설정용소자를 갖는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 26

화소 회로가 매트릭스 형상으로 배치됨과 함께, 이들 각 화소 회로를 선택하는 복수개의 주사선 및 각 화소 회로에 화상 정보를 공급하는 복수개의 데이터선이 배선되어 이루어지는 표시부와,

상기 복수개의 데이터선 각각을 통해 상기 화소 회로의 각각에 대한 화상 정보의 기입 구동을 행하는 구동 회로를 구비하는 액티브 매트릭스형 표시 장치에 있어서.

상기 화소 회로는 흐르는 전류에 의해서 휘도가 변화하는 전기 광학 소자와, 소스 또는 드레인이 상기 데이터선에 접속되고, 또한 게이트가 상기 주사선에 접속된 제1 전계 효과 트랜지스터와, 드레인과 게이트가 접속된 상태에 있을 때, 상기 제1 전계 효과 트랜지스터를 통해 상기 데이터선으로부터 전류가 공급됨으로써 그 게이트·소스 사이에 전압을 발생하는 제2 전계 효과 트랜지스터와, 상기 제2 전계 효과 트랜지스터에서 발생하는 전압을 유지하는 캐패시터와, 상기 캐패시터에서의 전압 유지의 상태를 유지하는 제3 전계 효과 트랜지스터와, 상기 캐패시터에서 유지한 전압을 구동 전류로 변환하여 상기 전기 광학 소자에 흘리는 제4 전계 효과 트랜지스터를 구비하고,

상기 구동 회로는 드레인과 게이트가 전기적으로 단락된 상태에 있을 때, 상기 화상 정보가 전류의 형태로 공급됨으로써 그 게이트·소스 사이에 전압을 발생하는 제5 전계 효과 트랜지스터와, 상기 제5 전계 효과 트랜지스터의 게이트·소스 사이에서 발생하는 전압을 유지하는 캐패시터와, 상기 캐패시터에서 유지한 전압을 전류로 변환하여 상기 복수개의 데이터선의 각각에 공급하는 제6 전계 효과 트랜지스터를 구비하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 27

제26항에 있어서,

상기 구동 회로에서의 상기 제5 전계 효과 트랜지스터와 해당 구동 회로에 상기 화상 정보를 공급하는 전류원과의 사이에, 상기 화상 정보의 기입 시에 포화 영역에서 동작하는 임피던스 변환용 트랜지스터를 갖는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

# 청구항 28

제27항에 있어서,

상기 임피던스 변환용 트랜지스터는 상기 제5 전계 효과 트랜지스터와 도전형이 다른 트랜지스터인 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 29

제27항에 있어서,

상기 임피던스 변환용 트랜지스터는 상기 구동 회로마다 설치되어 있는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 30

제27항에 있어서,

상기 복수개의 데이터선마다 설치된 상기 구동 회로가 블록화되어 있고,

상기 임피던스 변환용 트랜지스터는 블록 내의 복수의 구동 회로에 대하여 공통으로 설치되어 있는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

## 청구항 31

제26항에 있어서,

상기 구동 회로는 상기 제5, 제6 전계 효과 트랜지스터로서 동일한 트랜지스터를 이용하고,

상기 제5 전계 효과 트랜지스터에 의한 전류-전압의 변환과, 그것에 기초하는 상기 제6 전계 효과 트랜지스터에 의한 데이터선의 구동을 시분할적으로 행하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 32

제26항에 있어서,

상기 구동 회로는, 상기 화상 정보를 입력하는 신호 입력선과 상기 제5 전계 효과 트랜지스터를 접속 또는 차단하는 제1 스위치 소자와, 상기 제5 전계 효과 트랜지스터의 드레인과 게이트를 접속 또는 차단하는 제2 스위치소자를 구비하고,

상기 화상 정보의 취득 시에는 상기 제1 및 제2 스위치 소자를 접속 상태로 하고, 그 취득 종료 시에는 상기 제2 스위치 소자를 차단 상태로 하며, 그런 후 상기 제1 스위치 소자를 차단 상태로 하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 33

제26항에 있어서,

상기 구동 회로는 상기 제5, 제6 전계 효과 트랜지스터로서 동일한 특성을 갖는 트랜지스터를 이용하고,

상기 제5, 제6 전계 효과 트랜지스터는, 전류 미러 회로를 형성하고 있는 것을 특징으로 하는 액티브 매트릭스 형 표시 장치.

#### 청구항 34

제33항에 있어서,

상기 구동 회로는, 상기 화상 정보를 입력하는 신호 입력선과 상기 제5 전계 효과 트랜지스터를 접속 또는 차단하는 제1 스위치 소자와, 상기 제5 전계 효과 트랜지스터의 게이트와 상기 제6 전계 효과 트랜지스터의 게이트를 접속 또는 차단하는 제2 스위치 소자를 구비하고,

상기 화상 정보의 취득 시에는 상기 제1 및 상기 제2 스위치 소자를 접속 상태로 하고, 그 취득 종료 시에는 상기 제2 스위치 소자를 차단 상태로 하며, 그런 후 상기 제1 스위치 소자를 차단 상태로 하는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 35

제34항에 있어서,

상기 구동 회로에서, 상기 제5 전계 효과 트랜지스터의 채널 폭/채널 길이가, 상기 제6 전계 효과 트랜지스터의 채널 폭/채널 길이보다도 큰 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 36

제32항에 있어서,

상기 구동 회로는, 상기 제1 스위치 소자와 상기 제5 전계 효과 트랜지스터와의 사이에 접속된 제7 전계 효과 트랜지스터와, 상기 제7 전계 효과 트랜지스터의 드레인과 게이트 사이를 접속 또는 차단하는 제3 스위치 소자와, 상기 제7 전계 효과 트랜지스터의 게이트에 접속된 제2 캐패시터를 구비하고,

상기 제5 전계 효과 트랜지스터가 상기 제2 스위치 소자에 의해, 또한 상기 제7 전계 효과 트랜지스터가 상기 제3 스위치 소자에 의해, 함께 드레인과 게이트가 접속된 상태에 있을 때, 이들 트랜지스터의 드레인·소스 사이에 상기 제1 스위치 소자를 통해서 상기 화상 정보가 전류의 형태로 공급되는 것을 특징으로 하는 액티브 매트릭스형 표시 장치.

#### 청구항 37

액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치에 있어서,

제1, 제2 전극 및 이들 전극 사이에 발광층을 포함하는 유기층을 갖는 유기 일렉트로 루미네센스 소자를 표시 소자로서 이용하고, 화상 정보가 전류의 형태로 주어지는 화소 회로가 매트릭스 형상으로 배치됨과 함께, 이들 각 화소 회로를 선택하는 복수개의 주사선 및 각 화소 회로에 휘도 정보를 공급하는 복수개의 데이터선이 배선 되어 이루어지는 표시부와, 화상 정보를 일단 유지한 후 전류의 형태로 상기 복수개의 데이터선의 각각에 제공함으로써 각 화소 회로에 대한 화상 정보의 기입 구동을 행하는 구동 회로

를 구비한 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 38

제37항에 있어서,

상기 구동 회로는, 상기 복수개의 데이터선마다 설치되고, 상기 화상 정보를 전압의 형태로 유지하는 유지부와, 상기 유지부에서 유지한 전압을 전류로 변환하여 상기 복수개의 데이터선의 각각에 공급하는 구동부를 갖는 것 을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 39

제38항에 있어서,

상기 구동 회로는 상기 화상 정보가 전류의 형태로 주어지고, 이 전류를 전압으로 변환하는 변환부를 구비하고, 이 변환부에서 변환한 전압을 상기 유지부에서 유지하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 40

제39항에 있어서,

상기 구동 회로에 있어서,

상기 변환부는 드레인과 게이트가 전기적으로 단락된 상태에 있을 때, 상기 화상 정보가 전류의 형태로 공급됨으로써 그 게이트·소스 사이에 전압을 발생하는 제1 전계 효과 트랜지스터를 포함하고

상기 유지부는 상기 제1 전계 효과 트랜지스터의 게이트·소스 사이에서 발생하는 전압을 유지하는 캐패시터를 포함하고,

상기 구동부는 상기 캐패시터의 유지 전압에 기초하여 상기 복수개의 데이터선의 각각을 구동하는 제2 전계 효과 트랜지스터를 포함하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 41

액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치에 있어서,

제1, 제2 전극 및 이들 전극 사이에 발광층을 포함하는 유기층을 갖는 유기 일렉트로 루미네센스 소자를 표시 소자로서 이용하며, 화상 정보가 전류의 형태로 주어지는 화소 회로가 매트릭스 형상으로 배치됨과 함께, 이들 각 화소 회로를 선택하는 복수개의 주사선 및 각 화소 회로에 휘도 정보를 공급하는 복수개의 데이터선이 배선 되어 이루어지는 표시부와,

화상 정보를 일단 유지한 후 전류의 형태로 상기 복수개의 데이터선의 각각에 제공함으로써 각 화소 회로에 대한 화상 정보의 기입 구동을 행하는 구동 회로를 구비하고,

상기 구동 회로는, 상기 화상 정보가 전류의 형태로 주어지고, 이 전류를 전압으로 변환하는 변환부와, 이 변환 부에서 변환한 전압을 유지하는 유지부와, 해당 유지부에서 유지한 전압을 전류로 변환하여 상기 복수개의 데이 터선의 각각에 공급하는 구동부를 구비하고,

상기 변환부와 상기 구동 회로에 상기 화상 정보를 공급하는 전류원과의 사이에, 상기 화상 정보의 기입 시에 포화 영역에서 동작하는 임피던스 변환용 트랜지스터를 구비하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

## 청구항 42

제41항에 있어서,

상기 변환부는 드레인과 게이트가 전기적으로 단락된 상태에 있을 때, 상기 화상 정보가 전류의 형태로 공급됨으로써 그 게이트·소스 사이에 전압을 발생하는 제1 전계 효과 트랜지스터를 포함하고,

상기 유지부는, 상기 제1 전계 효과 트랜지스터의 게이트·소스 사이에 발생하는 전압을 유지하는 캐패시터를 포함하고.

상기 구동부는, 상기 캐패시터의 유지 전압에 기초하여 상기 복수개의 데이터선의 각각을 구동하는 제2 전계 효과 트랜지스터를 포함하고

상기 제1 전계 효과 트랜지스터와 상기 구동 회로에 상기 화상 정보를 공급하는 전류원과의 사이에, 상기 화상 정보의 기입 시에 포화 영역에서 동작하는 임피던스 변환용 트랜지스터를 포함하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 43

제42항에 있어서,

상기 임피던스 변환용 트랜지스터는 상기 제1 전계 효과 트랜지스터와 도전형이 다른 트랜지스터이고, 상기 구동 회로마다 설치되어 있는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 44

제42항에 있어서,

상기 복수개의 데이터선마다 설치된 상기 구동 회로가 블록화되어 있고,

상기 임피던스 변환용 트랜지스터는, 블록 내의 복수의 구동 회로에 대하여 공통으로 설치되어 있는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 45

제40항에 있어서,

상기 구동 회로는 상기 제1, 제2 전계 효과 트랜지스터로서 동일한 트랜지스터를 이용하고,

상기 제1 전계 효과 트랜지스터에 의한 전류-전압의 변환과, 그것에 기초하는 상기 제2 전계 효과 트랜지스터에 의한 데이터선의 구동을 시분할적으로 행하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 46

제40항에 있어서,

상기 구동 회로는 상기 화상 정보를 입력하는 신호 입력선과 상기 제1 전계 효과 트랜지스터를 접속 또는 차단하는 제1 스위치 소자와, 상기 제1 전계 효과 트랜지스터의 드레인과 게이트를 접속 또는 차단하는 제2 스위치소자를 구비하고.

상기 화상 정보의 취득 시에는 상기 제1 및 상기 제2 스위치 소자를 접속 상태로 하고, 그 취득 종료 시에는 상기 제2 스위치 소자를 차단 상태로 하며, 그런 후 상기 제1 스위치 소자를 차단 상태로 하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

## 청구항 47

제40항에 있어서,

상기 구동 회로는 상기 제1, 상기 제2 전계 효과 트랜지스터로서 동일한 특성을 갖는 트랜지스터를 이용하고,

상기 제1, 제2 전계 효과 트랜지스터는 전류 미러 회로를 형성하고 있는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 48

제47항에 있어서,

상기 구동 회로는 상기 화상 정보를 입력하는 신호 입력선과 상기 제1 전계 효과 트랜지스터를 접속 또는 차단하는 제1 스위치 소자와, 상기 제1 전계 효과 트랜지스터의 게이트와 상기 제2 전계 효과 트랜지스터의 게이트

를 접속 또는 차단하는 제2 스위치 소자를 구비하고,

상기 화상 정보의 취득 시에는 상기 제1 및 상기 제2 스위치 소자를 접속 상태로 하고, 그 취득 종료 시에는 상기 제2 스위치 소자를 차단 상태로 하며, 그런 후 상기 제1 스위치 소자를 차단 상태로 하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

## 청구항 49

제48항에 있어서,

상기 제1, 상기 제2 전계 효과 트랜지스터에 있어서, 상기 제1 전계 효과 트랜지스터의 채널 폭/채널 길이가, 상기 제2 전계 효과 트랜지스터의 채널 폭/채널 길이보다도 큰 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 50

제46항에 있어서,

상기 구동 회로는 상기 제1 스위치 소자와 상기 제1 전계 효과 트랜지스터 사이에 접속된 제3 전계 효과 트랜지스터와, 상기 제3 전계 효과 트랜지스터의 드레인과 게이트와의 사이를 접속 또는 차단하는 제3 스위치 소자와, 상기 제3 전계 효과 트랜지스터의 게이트에 접속된 제2 캐패시터를 구비하고,

상기 제1 전계 효과 트랜지스터가 상기 제2 스위치 소자에 의해, 또한 상기 제3 전계 효과 트랜지스터가 상기 제3 스위치 소자에 의해, 함께 드레인과 게이트가 접속된 상태에 있을 때, 이들 트랜지스터의 드레인·소스 사이에 상기 제1 스위치 소자를 통해서 상기 화상 정보가 전류의 형태로 공급되는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 51

제37항에 있어서,

상기 복수개의 데이터선마다 설치된 복수개의 상기 구동 회로는 동일한 신호 입력선을 공유하고, 이것을 시분할 적으로 사용하면서 화상 정보의 취득을 행하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센 스 표시 장치.

#### 청구항 52

제37항에 있어서,

상기 구동 회로는, 상기 화상 정보가 전압의 형태로 주어지고, 이 전압을 상기 유지부에서 유지하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 53

제52항에 있어서,

상기 구동 회로에 있어서,

상기 유지부는 상기 화상 정보에 따른 전압을 유지하는 유지 캐패시터를 포함하고,

상기 구동 회로는 상기 유지 캐패시터의 유지 전압에 기초하여 상기 복수개의 데이터선의 각각을 구동하는 전계 효과 트랜지스터를 포함하고,

상기 전계 효과 트랜지스터는 그 게이트·드레인이 전기적으로 단락되는 동작 후에, 그 게이트와 신호 입력선이기입 캐패시터를 통해 용량 결합된 상태에서 화상 정보가 주어지는 것을 특징으로 하는 액티브 매트릭스형 유기일렉트로 루미네센스 표시 장치.

#### 청구항 54

제53항에 있어서,

상기 구동 회로는, 상기 기입 캐패시터의 신호 입력선측 노드와 소정의 전위점과의 사이에 접속된 스위치 소자

를 구비하고,

상기 전계 효과 트랜지스터가 그 게이트·드레인 사이가 전기적으로 접속되는 동작이 행해지고 있는 동안에, 상기 스위치 소자가 단락됨으로써 상기 기입 캐패시터의 신호 입력선측 노드가 상기 소정의 전위가 되는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

## 청구항 55

제37항에 있어서,

상기 구동 회로는, 1개의 데이터선에 대하여 복수계통씩 설치되어 있는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 56

제55항에 있어서,

상기 구동 회로는, 1개의 데이터선에 대하여 2계통씩 설치되고, 한쪽의 계통의 구동 회로가 데이터선을 구동하는 동안에 다른 쪽의 계통의 구동 회로가 화상 정보의 취득을 행하는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 57

제55항에 있어서,

상기 구동 회로는 1개의 데이터선에 대하여 3계통씩 설치되고, 임의의 주사 사이클에 있어서 1계통의 구동 회로 가 리세트 동작을, 다른 1계통의 구동 회로가 데이터 피기입 동작을, 남은 1계통이 데이터선 구동 동작을 행하 는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

#### 청구항 58

제37항에 있어서,

상기 구동 회로를 구성하는 트랜지스터는 상기 화소 회로를 구성하는 트랜지스터와 동시에 형성되는 박막 트랜 지스터인 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

## 청구항 59

제37항에 있어서,

상기 화상 정보를 입력하는 신호 입력선과 소정의 전위점과의 사이에 누설 소자를 갖는 것을 특징으로 하는 액 티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

## 청구항 60

제37항에 있어서,

상기 화상 정보를 입력하는 신호 입력선과 소정의 전위점과의 사이에, 상기 신호 입력선을 통해서 상기 구동 회로에 상기 화상 정보를 공급하는 데 앞서서 상기 신호 입력선의 전위를 소정의 값으로 설정하는 초기치 설정용소자를 갖는 것을 특징으로 하는 액티브 매트릭스형 유기 일렉트로 루미네센스 표시 장치.

## 명세서

## 기술분야

본 발명은 각 화소마다 능동 소자를 가지고 해당 능동 소자에 의해 화소 단위로 표시 제어가 행해지는 액티브 매트릭스형 표시 장치에 관한 것으로, 특히 흐르는 전류에 의해서 휘도가 변화하는 전기 광학 소자를 화소의 표시 소자로서 이용하는 액티브 매트릭스형 표시 장치 및 전기 광학 소자로서 유기 재료의 일렉트로 루미네센스 (이하, 유기 EL(electroluminescence)라고 함) 소자를 이용하는 액티브 매트릭스형 유기 EL 표시 장치에 관한 것이다.

### 배경기술

- <2> 표시 장치, 예를 들면 화소의 표시 소자로서 액정 셀을 이용한 액정 디스플레이 등에 있어서는, 다수의 화소를 매트릭스 형상으로 배열하여, 표시하여야 할 화상 정보에 따라서 화소마다 광 강도를 제어함으로써 화상의 표시 구동을 행하고 있다. 이 표시 구동은, 화소의 표시 소자로서 유기 EL 소자를 이용한 유기 EL 디스플레이 등도 마찬가지이다.

- <3> 단, 유기 EL 디스플레이의 경우에는, 화소의 표시 소자로서 발광 소자를 이용한, 소위 자발광형의 디스플레이이 기 때문에, 액정 디스플레이에 비교하여 화상의 시인성이 높고, 백 라이트가 불필요하며, 응답 속도가 빠른 등의 이점을 갖는다. 또한, 각 발광 소자의 휘도는 거기에 흐르는 전류치에 의해서 제어되는, 즉 유기 EL 소자가 전류 제어형이라는 점에서, 액정 셀이 전압 제어형인 액정 디스플레이 등과는 크게 다르다.

- 수> 유기 EL 디스플레이에 있어서는, 액정 디스플레이와 마찬가지로, 그 구동 방식으로서 단순(패시브) 매트릭스 방식과 액티브 매트릭스 방식을 채용할 수 있다. 단, 전자는 구조가 단순하지만, 대형 또한 고정밀의 디스플레이의 실현이 어려운 등의 문제가 있다. 이 때문에, 최근 화소 내부의 발광 소자에 흐르는 전류를, 마찬가지로 화소 내부에 형성한 능동 소자(일반적으로는, 박막 트랜지스터(Thin Film Transistor; TFT)에 의해서 제어하는 액티브 매트릭스 방식의 개발이 활발하게 행해지고 있다.

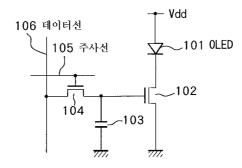

- <5> 도 33에 액티브 매트릭스형의 유기 EL 디스플레이에서의 화소 회로(단위 화소의 회로)의 종래예를 나타낸다(보다 상세하게는, 미국 특허 제5,684,365호 공보, 특개평 8-234683호 공보를 참조).

- <6> 이 종래예에 따른 화소 회로는, 도 33으로부터 명백한 바와 같이, 애노드(양극)가 플러스 전원 Vdd에 접속된 유기 EL 소자(101)와, 드레인이 유기 EL 소자(101)의 캐소드(음극)에 접속되며, 소스가 접지된 TFT(102)와, TFT(102)의 게이트와 접지와의 사이에 접속된 캐패시터(103)와, 드레인이 TFT(102)의 게이트에, 소스가 데이터 선(106)에, 게이트가 주사선(105)에 각각 접속된 TFT(104)를 갖는 구성으로 되어 있다.

- <7> 여기서, 유기 EL 소자는 대부분의 경우 정류성이 있기 때문에, OLED(Organic Light Emitting Diode)라고 불리는 경우가 있다. 따라서, 도 33 및 그 밖의 도면에서는, OLED로서 다이오드의 기호를 이용하여 도시한다. 단, 이하의 설명에 있어서, OLED에 반드시 정류성만이 요구되는 것은 아니다.

- <8> 상기 구성의 화소 회로의 동작은 다음과 같다. 우선, 주사선(105)의 전위를 선택 상태(여기서는, 고레벨)로 하고, 데이터선(106)에 기입 전위 Vw를 인가하면, TFT(104)가 도통하여 캐패시터(103)가 충전 또는 방전되고, TFT(102)의 게이트 전위는 기입 전위 Vw로 된다. 다음에, 주사선(105)의 전위를 비선택 상태(여기서는, 저레벨)로 하면, 주사선(105)과 TFT(102)와는 전기적으로 분리되지만, TFT(102)의 게이트 전위는 캐패시터(103)에 의해서 안정적으로 유지된다.

- <9> 그리고, TFT(102) 및 OLED(101)에 흐르는 전류는 TFT(102)의 게이트·소스 간 전압 Vgs에 따른 값으로 되고, OLED(101)는 그 전류치에 따른 휘도로 계속 발광한다. 여기서, 주사선(105)을 선택하여 데이터선(106)에 주어진 휘도 정보를 화소 내부에 전달하는 동작을, 이하 「기입」이라고 부르는 것으로 한다. 상술된 바와 같이, 도 33에 도시한 화소 회로에서는, 한번 전위 Vw의 기입을 행하면, 다음에 기입이 행해지기까지의 동안에는, OLED(101)는 일정한 휘도로 발광을 계속한다.

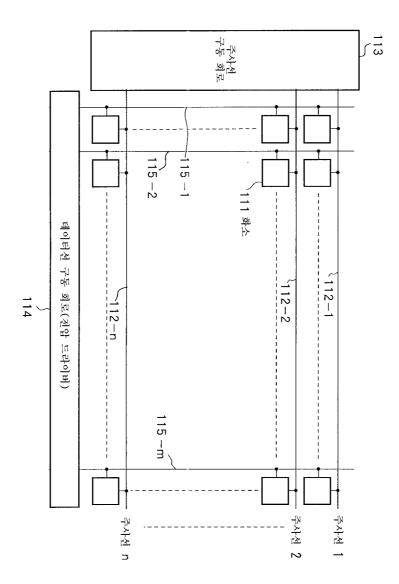

- <10> 이러한 화소 회로(이하, 단순히 화소라고 적는 경우도 있다)(111)를 도 34에 도시한 바와 같이 매트릭스 형상으로 다수 배열하고, 주사선(112-1~112-n)을 주사선 구동 회로(113)에 의해 순차 선택하면서, 전압 구동형의 데이터선 구동 회로(전압 드라이버)(114)로부터 데이터선(115-1~115-m)을 통해서 기입을 반복함으로써, 액티브 매트릭스형 표시 장치(유기 EL 디스플레이)를 구성할 수 있다. 여기서는, m열 n행의 화소 배열을 나타내고 있다. 이 경우, 당연한 것이지만, 데이터선이 m개, 주사선이 n개가 된다.

- <11> 단순 매트릭스형 표시 장치에서는, 각 발광 소자는, 선택된 순간에만 발광하는 데 대하여, 액티브 매트릭스형 표시 장치에서는, 기입 종료 후에도 발광 소자가 발광을 계속한다. 이 때문에, 액티브 매트릭스형 표시 장치는 단순 매트릭스형 표시 장치에 비하여 발광 소자의 피크 휘도, 피크 전류가 감소된다는 점에서, 특히 대형·고정 밀한 디스플레이에서는 유리하게 된다.

- <12> 그런데, 액티브 매트릭스형 유기 EL 디스플레이에 있어서는, 능동 소자로서 일반적으로, 유리 기판 상에 형성된 절연 게이트형 박막 전계 효과 트랜지스터(TFT)가 이용된다. 그런데, 이 TFT의 형성에 사용되는 비정질 실리콘이나 폴리실리콘(다결정 실리콘)은 단결정 실리콘에 비하여 결정성이 나쁘고, 도전 기구의 제어성이 나쁘기 때

문에, 형성된 TFT은 특성의 변동이 큰 것이 잘 알려져 있다.

- <13> 특히, 비교적 대형의 유리 기판 상에 폴리실리콘 TFT를 형성하는 경우에는, 유리 기판의 열 변형 등의 문제를 피하기 위해서, 통상 비정질 실리콘막의 형성 후에, 레이저어닐링법에 의해서 결정화가 행해진다. 그러나, 큰 유리 기판에 균일하게 레이저 에너지를 조사하는 것이 어렵고, 폴리실리콘의 결정화의 상태가 기판 내의 장소에 따라서 변동을 일으킬 가능성을 배제할 수 없다. 이 결과, 동일 기판 상에 형성한 TFT라도, 그 임계치 Vth가 화소에 의해 수백 mV, 경우에 따라서는 1V 이상 변동하는 것도 드문일은 아니다.

- <14> 이 경우, 예를 들면 다른 화소에 대하여 동일한 전위 Vw를 기입하여도, 화소에 따라서는 TFT의 임계치 Vth가 변동되게 된다. 이에 따라, OLED에 흐르는 전류 Ids는 화소마다 크게 변동하여 완전히 원하는 값으로부터 벗어나는 결과가 되어, 디스플레이로서 높은 화질을 기대할 수 없게 된다. 이것은, 임계치 Vth만이 아니라, 캐리어의 이동도 11 등의 변동에 대해서도 마찬가지라고 할 수 있다.

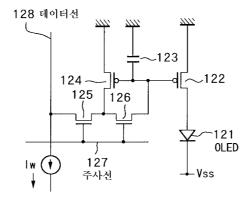

- <15> 이러한 문제를 개선하기 위해서, 본원 발명자는, 일례로서 도 35에 도시하는 전류 기입형의 화소 회로를 제안하고 있다(국제 공개 번호 W001-06484의 공보 참조).

- <16> 이 전류 기입형의 화소 회로는, 도 35로부터 자명한 바와 같이, 캐소드가 마이너스 전원 Vss에 접속된 OLED(121)와, 드레인이 OLED(121)의 애노드에 접속되고, 소스가 기준 전위점인 접지에 접속된 TFT(122)와, 이 TFT(122)의 게이트와 접지와의 사이에 접속된 캐패시터(123)와, 게이트가 TFT(122)의 게이트에 접속되고, 소스가 접지된 TFT(124)와, 드레인이 TFT(124)의 드레인에, 소스가 데이터선(128)에, 게이트가 주사선(127)에 각각 접속된 TFT(125)와, 드레인이 TFT(122, 124)의 각 게이트에, 소스가 TFT(124, 125)의 각 드레인에, 게이트가 주사선(127)에 각각 접속된 TFT(126)를 갖는 구성으로 되어 있다.

- <17> 이 회로예에서는, TFT(122, 124)로서 PMOS(전계 효과 트랜지스터), TFT(125, 126)로서 NMOS를 이용하고 있다. 이 화소 회로를 구동하는 타이밍차트를 도 36(A)~도 36(C)에 도시한다.

- <18> 도 35에 도시하는 화소 회로가, 도 33에 도시하는 화소 회로와 결정적으로 다른 점은 다음과 같다. 즉, 도 33에 도시하는 화소 회로에서는 휘도 데이터가 전압의 형태로 화소에 주어지는 데 대하여, 도 35에 도시하는 화소 회로에서는 전류의 형태로 화소에 주어지는 점에 있다. 그 동작은 다음과 같다.

- <19> 우선, 휘도 정보를 기입할 때는, 주사선(127)을 선택 상태로 하여, 데이터선(128)에, 휘도 정보에 따른 전류 Iw를 흘린다. 이 전류 Iw는 TFT(125)를 통해서 TFT(124)에 흐른다. 이 때, TFT(124)에 생기는 게이트·소스 간 전압을 Vgs로 한다. 기입할 때에는 TFT(126)에 의해 TFT(124)의 게이트·드레인 사이가 단락되어 있기 때문에, TFT(124)는 포화 영역에서 동작한다. .

- <20> 따라서, 잘 알려진 MOS 트랜지스터의 식에 따라서,

# 수학식 1

- $\langle 21 \rangle$  Iw= $\mu$  1Cox1W1/L1/2(Vgs-Vth1)<sup>2</sup>

- <22> 가 성립된다. 수학식 1에 있어서, Vth1은 TFT(124)의 임계치, μ1은 캐리어의 이동도, Cox1은 단위 면적당 게이트 용량, W1은 채널 폭, L1은 채널 길이이다.

- <23> 다음에, OLED(121)에 흐르는 전류를 Idrv로 하면, 이 전류 Idrv는 OLED(121)와 직렬로 접속된 TFT(122)에 의해 전류치가 제어된다. 도 35에 도시하는 화소 회로에서는 TFT(122)의 게이트·소스 간 전압이 수학식 1의 Vgs에 일치하기 때문에, TFT(122)가 포화 영역에서 동작한다고 가정하면,

#### 수학식 2

- <24> Idrv= $\mu$  2Cox2W2/L2/2(Vgs-Vth2)<sup>2</sup>

- <25> 가 된다.

- <26> 덧붙여서 말하면, MOS 트랜지스터가 포화 영역에서 동작하는 조건은, 일반적으로,

## 수학식 3

$\langle 27 \rangle$  |Vds| > |Vgs - Vt|

<28> 인 것이 알려져 있다. 수학식 2, 수학식 3식의 각 파라미터의 의미는 수학식 1과 마찬가지이다. 여기서, TFT(124)와 TFT(122)는, 작은 화소 내부에 근접하여 형성되기 때문에, 사실 상, μ1=μ2, Cox1=Cox2, Vth1=Vth2라고 생각된다. 그러면, 수학식 1과 수학식 2로부터 용이하게,

- <29> Idrv/Iw=(W2/W1)/(L2/L1)

- <30> 이 유도된다.

- <31> 즉, 캐리어의 이동도µ, 단위 면적당의 게이트 용량 Cox, 임계치 Vth의 값 자체가 패널면 내에서, 혹은 패널마다 변동되었다고 해도, OLED(121)에 흐르는 전류 Idrv는 정확하게 기입 전류 Iw에 비례하기 때문에, 결과적으로, OLED(121)의 발광 휘도를 정확하게 제어할 수 있다. 예를 들면, 특히 W2=W1, L2=L1로 설계하면, Idrv/Iw=1, 즉 TFT 특성의 변동에 상관없이, 기입 전류 Iw와 OLED(121)에 흐르는 전류 Idrv와는 동일한 값이 된다

- <32> 일반적으로, 액티브 매트릭스형 표시 장치에 있어서는, 각 화소에의 휘도 데이터의 기입은 기본적으로 주사선 단위로 행해진다. 예를 들면, 비정질 실리콘 TFT를 이용한 액정 디스플레이에 있어서는, 선택된 동일 주사선 상의 화소에 대하여 일괄적으로(동시에) 기입을 행하는 것이 일반적이다. 이와 같이, 주사선 단위로의 기입은 일반적으로, 선순차 기입으로 호칭되어 있다.

- <33> 이 선순차 기입 방식을 채용하는 표시 장치에서는, 통상, 데이터선 드라이버는 표시 패널 내부의 화소 회로를 구성하는 TFT의 제조 공정과는 별도로, 일반적인 모노리식(monolithic) 반도체 기술에 의해 제조된다. 따라서, 특성이 안정적인 것을 얻기 쉽지만, 그 반면에, 표시 장치의 데이터선 개수분의 데이터선 드라이버 개수가 필요 하기 때문에, 시스템 전체로서 대형·고비용이 되는 경향이 있다. 또한, 화소수가 많거나, 혹은 화소 피치가 좁은 표시 장치의 실현에 있어서는, 표시 패널과 패널 외부의 드라이버와의 결선을 위한 배선 개수나 접속 점수 가 방대해지기 때문에, 접속의 신뢰성이나 배선 피치 등의 점에서도 대형·고정밀한 표시 장치의 실현에는 한계 가 있다.

- <34> 여기서, 상기한 「패널 외부의 드라이버」는 문자 그대로 표시 패널(유리 기판)의 외부에 설치되어, 플렉시블 케이블 등에 의해서 패널과 결선되는 경우도 있지만, TAB(Tape Automated Bonding) 기술 등에 의해서 패널(유리 기판) 상에 탑재되는 경우도 있다. 상술한 설명으로서는 양자를 포함해서 편의적으로 「패널 외부」라고 표현 하고 있고, 이하에도 마찬가지로 표현한다.

- <35> 한편, 폴리실리콘 TFT를 이용한 액정 디스플레이에 있어서는, 트랜지스터의 구동 능력이 높고, 단일의 화소에 대한 기입을 단시간에 행할 수 있기 때문에, 점순차 기입으로 불리는 기입 방식이 채용되는 경우도 많다. 이 점순차 기입 방식을 채용하는 표시 장치의 구성예를 도 37에, 그 동작 타이밍차트를 도 38(A)~도 38(F)에 도시한다. 또, 도 37에서, 도 34와 동등 부분에는 동일 부호를 붙여서 도시한다.

- <36> 도 37에 있어서, 데이터선(115-1~115-m)의 각 일단과 신호 입력선(116)과의 사이에 수평 스위치 HSW1~HSWm이 설치되어 있다. 그리고, 이들 수평 스위치 HSW1~HSWm은 수평 스캐너(HSCAN)(117)로부터 순차 출력되는 선택 펼스 we1~wem에 의해서 on/off 제어된다. 수평 스위치 HSW1~HSWm 및 수평 스캐너(117)는 TFT로 구성되며, 화소 회로(11)와 동일한 제조 공정으로 동시에 형성된다.

- <37> 수평 스캐너(117)에는 수평 스타트 펄스 hsp 및 수평 클릭 신호 hck가 입력된다. 수평 스캐너(117)는, 도 38 (A)~(E)에 도시한 바와 같이, 수평 스타트 펄스 hsp의 입력 후, 수평 클릭 신호 hck의 천이(상승 및 하강)에 대응하여, 수평 스위치 HSW1~HSWm을 선택하기 위한 선택 펄스 we1~wem을 순차 발생한다.

- <38> 수평 스위치 HSW1~HSWm 각각은, 선택 펄스 we1~wem이 주어진 기간에 도통 상태가 되어 신호 입력선(116)을 통해 주어지는 화상 데이터(전압치) sin을 데이터선(115-1)~데이터선(115-m)에 전달한다. 이에 따라, 주사선 구동 희로(113)에 의해서 선택된 주사선 상의 화소에의 기입이 점순차로써 행해진다. 데이터선(115-1)~데이터선(115-m)에 주어진 전압은 수평 스위치 HSW1~HSWm이 비도통된 후에도 데이터선(115-1)~데이터선(115-m)의 부유용량 등의 용량 성분에 의해서 유지된다.

- <39> 이와 같이, 수평 클럭 신호 hck가 m 클럭분 제공되면, 선택된 주사선 상의 모든 화소에 데이터가 기입된다. 이점순차 기입 방식의 표시 장치의 경우, 1개의 신호 입력선(116)을 시분할적으로 사용하는 구성이기 때문에, 표시 패널과 패널 외부의 데이터 드라이버(화상 데이터 sin을 공급하는 회로)와의 접속 점수가 적게 되고, 또한

외부 드라이버의 수도 그에 따라 적게 할 수 있다는 등의 이점이 있다.

- <40> 그런데, 화소 회로로서, 상술한 도 35에 도시하는 전류 기입형 화소 회로를 채용한 경우에는, 도 37에 도시한 바와 같은 표시 장치의 구성으로서는 화소(111)에 정상적인 기입을 행할 수 없다. 그 이유를 이하에 설명한다.

- <41> 도 37에 있어서, 특정한 수평 스위치 HSW가 선택되어 도통한 상태에서, 신호 입력선(116)을 전류원에 의해서 구동하면, 수평 스위치 HSW가 선택되어 있는 데이터선 상의 화소에 대해서는 정상적으로 전류 기입이 행해진다. 그 후, 수평 스캐너(117)에 수평 클럭 신호 hck가 입력되고, 다른 데이터선에 대한 기입이 개시되면,그 기입과 동시에 그 때까지 선택되어 있던 수평 스위치 HSW가 비도통이 되기 때문에, 대응하는 데이터선에 흐르는 전류가 제로가 되게 된다.

- <42> 따라서, 정상적으로 기입을 행하기 위해서는, 주사선이 선택 상태에서 비선택 상태로 되는 시점에서, 그 주사선 상의 모든 화소에 소정의 기입 전류가 공급되어 있을 필요가 있다. 즉, 전류 기입형의 화소 회로를 채용한 경 우에는 각 화소에의 데이터의 기입을 선순차로 행할 필요가 있고, 예를 들면 도 39에 도시한 바와 같이, 선택된 주사선 상의 화소에 대하여 표시 패널의 외부에 설치된 데이터선 드라이버(118)로부터 일괄하여 기입을 행하는 구성을 채용할 필요가 있다.

- <43> 이것은 도 34에 도시한 선순차 구동 방식의 표시 장치와 기본적으로 동일한 구성으로 되어 있다. 그 결과로서, 상술한 바와 같이, 패널 외부의 데이터선 드라이버(118)를 구성하는 전류 드라이버 회로 CD1~CDm의 개수나, 이 들과 표시 패널과의 사이의 배선의 접속 점수가 증가한다는 문제가 발생한다.

### 발명의 상세한 설명

- <44> 본 발명은, 상기 과제에 감안하여 이루어진 것으로, 그 목적으로 하는 바는 전류 기입형 화소 회로를 채용한 경우에 있어서, 표시 패널과 외부의 데이터 드라이버 회로와의 접속 점수를 삭감하면서 정상적인 전류 기입 동작을 실현할 수 있는 액티브 매트릭스형 표시 장치 및 액티브 매트릭스형 유기 EL 표시 장치를 제공하는 데 있다.

- 본 발명에 의한 액티브 매트릭스형 표시 장치는, 전류에 의해서 화상 정보의 기입을 행하는 전류 기입형의 화소 회로가 매트릭스 형상으로 배치됨과 함께, 이들 각 화소 회로를 선택하는 복수개의 주사선 및 각 화소 회로에 화상 정보를 공급하는 복수개의 데이터선이 배선되어 이루어지는 표시부와, 화상 정보를 일단 유지한 후 전류의 형태로 복수개의 데이터선의 각각에 제공함으로써 각 화소 회로에 대한 화상 정보의 기입 구동을 행하는 구동 회로를 구비한 구성으로 되어 있다.

- <46> 상기 구성의 액티브 매트릭스형 표시 장치에 있어서, 화소 회로가 전류 기입형의 경우에는 화소 회로 내의 능동소자의 특성이 화소마다 변동되었다고 해도, 표시 소자에 흐르는 전류가 정확하게 기입 전류에 비례하기때문에, 표시 소자의 발광 휘도를 정확하게 제어할 수 있다. 한편, 구동 회로는 화상 정보를 일단 유지하고, 그런 후 데이터선 각각에 화상 정보를 전류의 형태로 제공한다. 이에 따라, 구동 회로에 의한 각 화소 회로에의 화상 정보의 기입이 선순차로써 행해진다.

#### 실시예

- <87> [제1 실시 형태]

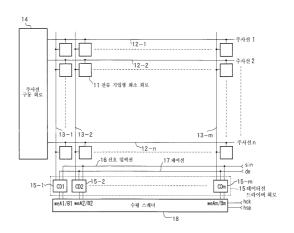

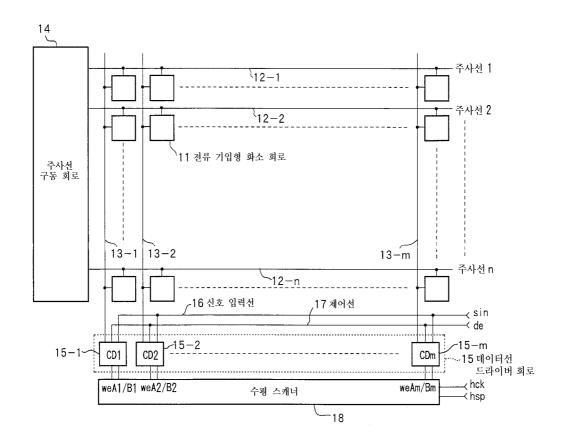

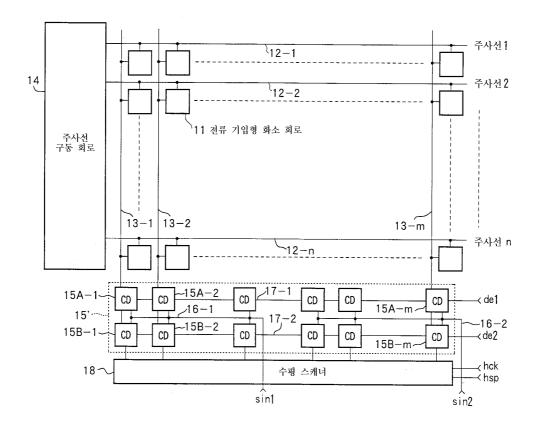

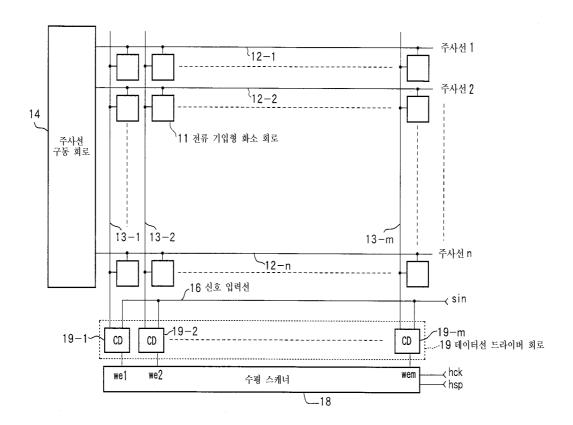

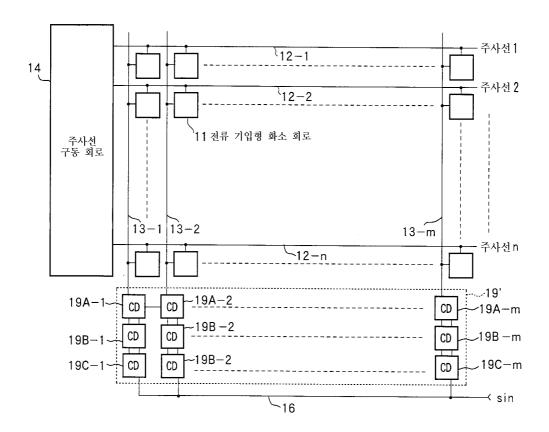

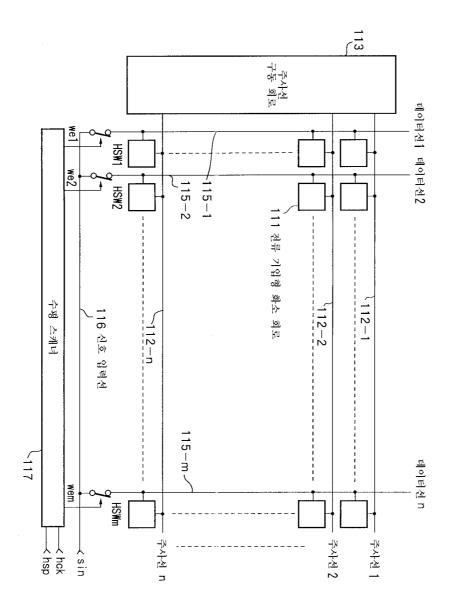

- <88> 도 1은 본 발명의 제1 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도이다. 도 1에 있어서, 화소 회로(11)가 매트릭스 형상으로 다수 배치되어 표시 영역(표시부)를 구성하고 있다. 여기서는, m열 n행의 화소 배열을 예로서 채용하여 나타내고 있다. 이 표시 영역에는 화소 회로(11)의 각각에 대하여, 각화소(화소 회로)를 선택하는 n개의 주사선(12-1~12-n)과, 각 화소에 화상 데이터, 예를 들면 휘도 데이터를 공급하는 m개의 데이터선(13-1~13-m)이 배선되어 있다.

- <89> 상기 표시 영역의 외부에는 주사선(12-1~12-n)을 선택 구동하는 주사선 구동 회로(14)가 설치됨과 함께, 데이 터선(13-1~13-m)을 구동하는 데이터선 드라이버 회로(15)가 설치되어 있다. 주사선 구동 회로(14)는, 예를 들면 시프트 레지스터로 이루어지고, 각 전송단의 출력단이 주사선(12-1~12-n)의 각 일단에 접속되어 있다. 데이터선 드라이버 회로(15)는, 후술하는 바와 같이, m개의 전류 기입형의 전류 드라이버 회로(CD: 15-1~15-m)에 의해 구성되어 있다.

- <90> 전류 기입형의 전류 드라이버 회로(이하, 단순히 「전류 드라이버 회로」라고 적는다)(15-1~15-m)는 각 출력단

이 데이터선(13-1~13-m)의 각 일단에 접속되어 있다.

- <91> 데이터선 드라이버 회로(15)의 전류 드라이버 회로(15-1~15-m)에는 신호 입력선(16)을 통해서 외부로부터 화상 데이터(본 예에서는, 휘도 데이터) sin이 공급됨과 함께, 제어선(17)을 통해 외부로부터 구동 제어 신호 de가 공급된다. 즉, 데이터선(13-1~13-m)마다 설치된 전류 드라이버 회로(15-1~15-m)는 동일한 신호 입력선(16)을 공용하고, 이것을 시분할적으로 사용하면서 화상 데이터의 취득을 행한다. 전류 드라이버 회로(15-1~15-m)에는 또한, 수평 스캐너(HSCAN)(18)로부터, 2계통의 기입 제어 신호 weAl~weAm, weBl~weBm이 공급된다.

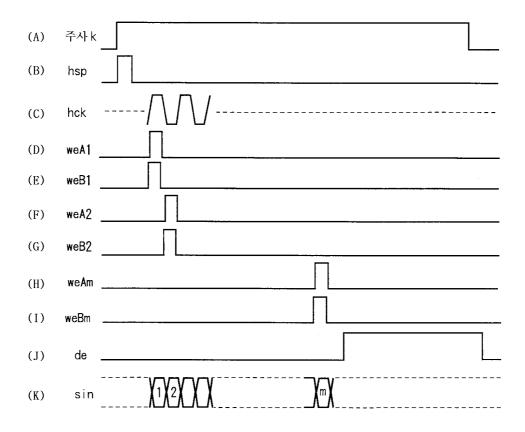

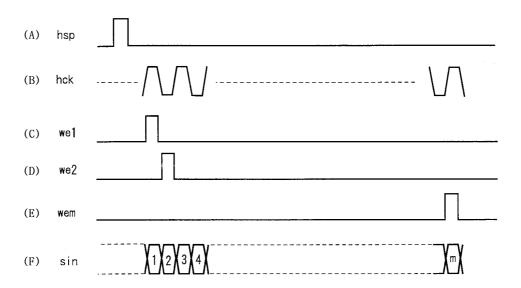

- <92> 수평 스캐너(18)에는 수평 스타트 펄스 hsp 및 수평 클럭 신호 hck가 입력된다. 수평 스캐너(18)는, 예를 들면 시프트 레지스터로 이루어지며, 도 2(A)~도 2(K)의 타이밍차트에 도시한 바와 같이, 수평 스타트 펄스 hsp의 입력 후, 수평 클럭 신호 hck의 천이(상승 및 하강)에 대응하여, 기입 제어 신호 weA1~weAm, weB1~weBm을 순 차 발생한다. 여기서, 예를 들면 기입 제어 신호 weA1~weAm의 각각은, 기입 제어 신호 weB1~weBm의 각각에 대하여 약간 지연된 타이밍 관계에 있다.

- <93> 상기 구성의 제1 실시 형태에 따른 액티브 매트릭스형 표시 장치에 있어서, 화소 회로(11)로서는, 예를 들면 도 35에 도시한 전류 기입형의 화소 회로가 이용된다. 이 전류 기입형 화소 회로는, 상술한 바와 같이, 화소 회로 (11)의 표시 소자로서, 전류치에 의해서 휘도가 제어되는 발광 소자, 예를 들면 유기 EL 소자(OLED)를 이용함과 동시에, 4개의 TFT(절연 게이트형 박막 전계 효과 트랜지스터) 및 하나의 캐패시터를 구비하고, 휘도 데이터가 전류의 형태로 데이터선으로부터 주어지게 된다. 또, 화소 회로(11)로서는, 도 35에 도시한 회로 구성의 것으로 한정되는 것은 아니고, 요컨대 전류 기입형의 화소 회로이면 된다.

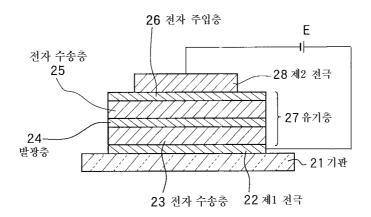

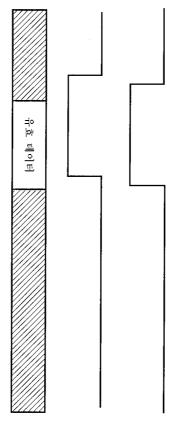

- <94> 여기서, 유기 EL 소자의 구조의 일례에 대하여 설명한다. 도 3에 유기 EL 소자의 단면 구조를 나타낸다. 도 3 으로부터 자명한 바와 같이, 유기 EL 소자는 투명 유리 등으로 이루어지는 기판(21) 상에, 투명 도전막으로 이루어지는 제1 전극(예를 들면, 양극: 22)을 형성하고, 그 위에 다시 정공 수송층(23), 발광층(24), 전자 수송층(25) 및 전자 주입층(26)을 순차 퇴적시켜 유기층(27)을 형성한 후, 이 유기층(27)의 상에 금속으로 이루어지는 제2 전극(예를 들면, 음극)(28)을 형성한 구성으로 되어 있다. 그리고, 제1 전극(22)과 제2 전극(28) 사이에 직류 전압 E를 인가함으로써, 발광층(24)에 있어서 전자와 정공이 재결합할 때에 발광하도록 되어 있다.

- <95> 이 유기 EL 소자(OLED)를 포함하는 화소 회로에서는, 상술한 바와 같이 능동 소자로서 일반적으로 유리 기판 상에 형성된 TFT이 이용된다. 그리고, 이 화소 회로가 생성된 유리 기판(표시 패널) 상에 주사선 구동 회로(14)도 마찬가지로, TFT 등의 회로 소자에 의해 형성된다. 이 때, 전류 드라이버 회로(15-1~15-m)에 대해서도, 동일한 표시 패널(유리 기판) 상에 TFT 등의 회로 소자에 의해서 동시에 형성하도록 해도 된다. 단, 전류 드라이버 회로(15-1~15-m)를 반드시 표시 패널 상에 설치할 필요는 없고, 패널 외부에 설치하는 구성을 채용해도 된다.

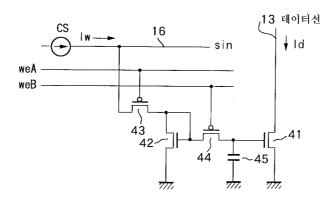

- <96> [제1 회로예]

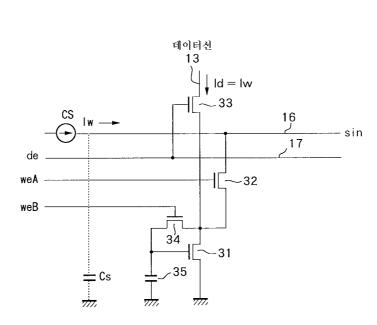

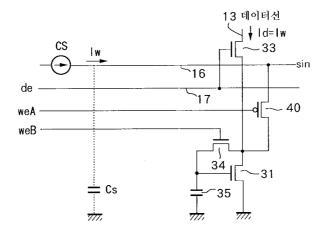

- <97> 도 4는 데이터선 드라이버 회로(15)를 구성하는 전류 드라이버 회로(15-1~15-m)의 구체적인 회로예를 도시하는 회로도이다. 또, 전류 드라이버 회로(15-1~15-m)의 각각은 완전히 동일한 회로 구성으로 되어 있다.

- <98> 도 4로부터 명백한 바와 같이, 본 예에 따른 전류 드라이버 회로는 4개의 TFT(31~34) 및 하나의 캐패시터(35) 로 구성되어 있다. 이 회로예에서는 TFT(31~34)의 전부를 NMOS로 구성하고 있지만, 이것은 일례이고, 이것에 한정되는 것은 아니다.

- <99> 도 4에 있어서, TFT(31)는 그 소스가 접지되어 변환부를 구성하고 있다.

- <100> 이 TFT(31)의 드레인에 TFT(32, 33)의 각 소스 및 TFT(34)의 드레인이 각각 접속되어 있다. TFT(32)는 그 드레인이 신호 입력선(16)에 접속된 제1 스위치 소자이고, 그 게이트에는 제1 기입 제어 신호 weA가 주어진다. TFT(33)는 그 드레인이 데이터선(13)에 접속되어 구동부를 구성하고 있으며, 그 게이트에는 제어선(17)을 통해 구동 제어 신호 de가 주어진다. TFT(34)는 그 소스가 TFT(31)의 게이트에 접속된 제2 스위치 소자로, 그 게이트에는 제2 기입 제어 신호 weB가 주어진다. TFT(31)의 게이트 및 TFT(34)의 소스와 접지 사이에는 유지부를 구성하는 캐패시터(35)가 접속되어 있다.

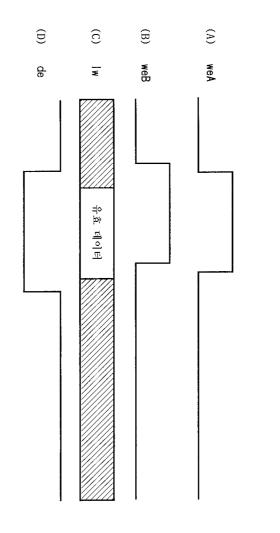

- <101> 다음에, 상기 구성의 전류 드라이버 회로의 회로 동작에 대하여, 도 5(A)~도 5(D)의 구동 파형도를 이용하여 설명한다.

- <102> 본 전류 드라이버 회로에의 기입 시에는 제1 기입 제어 신호 weA 및 제2 기입 제어 신호 weB를 함께 선택 상태로 한다. 여기서는, 양자가 고레벨의 상태를 선택 상태로 하고 있다. 또한, 구동 제어 신호 de를 비선택 상태

(여기서는 저레벨)로 한다. 이 상태에서 신호 입력선(16)에 전류치 Iw의 전류원 CS를 접속함으로써, TFT(32)의 소스를 통해서 TFT(31)에 기입 전류 Iw가 흐른다.

<103> 이 때, TFT(31)의 게이트·드레인 사이는 TFT(34)에 의해서 전기적으로 단락되어 있기 때문에 수학식 3이 성립하고, TFT(31)는 포화 영역에서 동작한다. 따라서, 그 게이트·소스 사이에는,

## 수학식 5

- <104> Iw= $\mu$  CoxW/L/2(vgs-Vth)<sup>2</sup>

- <105> 로 주어지는 전압 Vgs가 생긴다. 여기서, Vth는 TFT(31)의 임계치, μ는 캐리어의 이동도, Cox는 단위 면적당의 게이트 용량, W는 채널폭, L은 채널 길이이다.

- <106> 다음에, 제1, 제2 기입 제어 신호 weA, weB를 비선택 상태로 한다. 상세하게는, 우선 제2 기입 제어 신호 weB를 저레벨로 하여 TFT(34)를 비도통 상태로 한다. 이에 따라, TFT(31)의 게이트·소스 사이에서 생긴 전압 Vgs가 캐패시터(35)에 의해서 유지된다. 계속해서, 제1 기입 제어 신호 weA를 저레벨로 하여 TFT(32)를 비도통 상태로 함으로써, 본 전류 드라이버 회로와 전류원 CS가 전기적으로 차단되기 때문에, 그 후는 전류원 CS에 의해서 다른 전류 드라이버 회로에 대하여 기입을 행할 수 있다. TET(33)는 캐패시터(35)의 유지 전압 Vgs에 기초하여 데이터선(13)을 구동한다.

- <107> 이와 같이, 본 전류 드라이버 회로에의 기입 종료 시에, 우선 TFT(34)를 비도통 상태로 하고, 그런 후 TFT(32)를 비도통 상태로 한다, 즉 TFT(32)에 앞서서 TFT(34)를 비도통 상태로 함으로써, 휘도 데이터의 기입을 확실하게 행할 수 있다. 여기서, 전류원 CS가 구동하는 데이터는, 제2 기입 제어 신호 WeB가 비선택이 되는 시점에서는 유효할 필요가 있지만, 그 후는 임의의 값(예를 들면, 다음의 전류 드라이버 회로에의 기입 데이터)으로 되어도 된다.

- <108> 다음에, 구동 제어 신호 de를 선택 상태(여기서는 고레벨)로 하면, TFT(31)이 포화 영역에서 동작하고 있으면, TFT(31)를 흐르는 전류는,

- <109> Id= $\mu$  CoxW/L/2(vgs-Vth)<sup>2</sup>

- <110> 로 주어진다. 이것이 데이터선(13)에 흐르는 전류가 되지만, 이것은 상술한 기입 전류 Iw와 일치한다.

- <111> 즉, 도 4에 도시하는 회로는 전류치의 형태로 기입된 휘도 데이터 sin을 일단 전압치로 변환하여 캐패시터(35)에 유지하고, 기입 종료 후에도 캐패시터(35)의 전압치에 기초하여, 기입된 전류치와 거의 같은 전류치로 데이터선(13)을 구동하는 기능을 갖는다. 또한 이 동작에 있어서, 수학식 5, 수학식 6 중 캐리어의 이동도 μ나 임계치 Vth 등의 절대치는 문제가 되지 않는다. 즉, 도 4에 도시한 회로는 TFT의 특성 변동에 상관없이, 기입된 전류치와 정확하게 같은 전류치로 데이터선(13)을 구동할 수 있다.

- <112> 계속해서, 도 1에 도시한 제1 실시 형태에 따른 액티브 매트릭스형 표시 장치에 있어서, 화소 회로(11)로서 도 35의 전류 기입형 화소 회로를 이용하고, 또한 전류 드라이버 회로(15-1~15-m)로서 도 4의 전류 기입형 전류 드라이버 회로를 이용한 경우의 동작에 대하여, 도 2(A)~도 2(K)의 타이밍차트에 기초하여 설명한다.

- <113> 수평 스캐너(18)는, 상술한 바와 같이, 수평 스타트 필스 hsp의 입력 후에, 수평 클럭 신호 hck의 천이에 대응하여, 제1, 제2 기입 제어 신호 weA1~weAm, weB1~weBm을 순차 발생한다. 여기서, 기입 제어 신호 weA1~weAm 각각은 기입 제어 신호 weB1~weBm의 각각에 대하여 약간 타이밍이 지연되고 있다. 휘도 데이터 sin은 이들의 기입 제어 신호 weA1~weAm, weB1~weBm에 동기하여, 신호 입력선(16)으로부터 전류치의 형태로 입력된다.

- <114> 그리고, 수평 클럭 hck이 m 클럭 분입력되면, m개의 전류 드라이버 회로(15-1~15-m)에 휘도 데이터 sin이 기입된다. 기입 중에는 구동 제어 신호 de는 비선택 상태라고 되어 있지만, 모든 전류 드라이버 회로(15-1~15-m)에 기입이 종료한 시점에서는 선택 상태로 되어, 따라서 데이터선(13-1)~데이터선(13-m)이 구동된다. 구동제어 신호 de가 선택 상태일 때, k 번째의 주사선(12-k)이 선택되어 있기 때문에, 주사선(12-k)에 접속된 화소(11)에 대하여 선순차 기입이 행해진다.

- <115> 주사선(12-k)을 비선택으로 하면 기입이 종료하지만, 도 2(A)~도 2(K)의 타이밍차트에서는 그 시점에서 구동

제어 신호 de는 선택 상태를 유지하고 있고, 기입 종료까지 유효한 기입 데이터(기입 전류)를 유지하도록 하고 있다. 단, 이 구동 방법에 있어서는, 1 주사선 기간(통상은, 1 프레임 기간 / 주사선 개수)에, 전류 드라이버 회로(15-1~15-m)에의 기입과, 데이터선(13-1~13-m)의 구동이 직렬에 행해지기 때문에, 이들 기입과 데이터선 구동의 양방에 충분한 시간을 확보하는 것이 어려운 경우가 있다.

- <116> [제2 회로예]

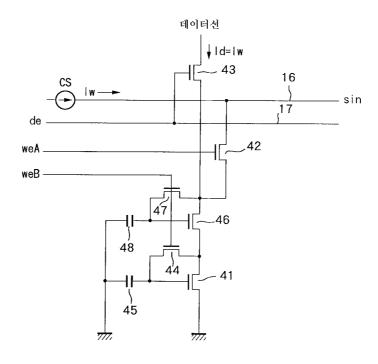

- <117> 도 6은 전류 드라이버 회로(15-1~15-m)의 다른 회로예를 도시하는 회로도로, 도 6 중, 도 4와 동등 부분에는 동일 부호를 붙여서 나타낸다.

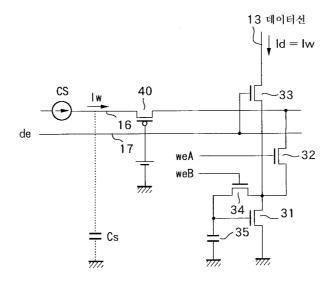

- <118> 도 6으로부터 명백한 바와 같이, 본 예에 따른 전류 드라이버 회로는 도 4의 회로 소자 외에, TFT(31)와 전류원 CS 사이에, 휘도 데이터 sin의 기입 시에 포화 영역에서 동작하는 임피던스 변환용 트랜지스터, 즉 TFT(31)과 도전형이 다른 PMOS의 TFT(40)를, 예를 들면 TFT(32)를 통해 접속한 구성으로 되어 있다. 이 구성에 따르면, 본 전류 드라이버 회로에의 휘도 데이터 sin의 기입을 도 4의 회로예보다도 고속으로 행할 수 있다. 그 이유에 대하여 이하에 순차 설명한다.

- <119> 전류 기입에서는, 일반적으로 기입에 요하는 시간이 길다는 문제가 있다. 도 4의 회로예의 전류 드라이버 회로에 전류치 Iw를 기입하는 경우, 전류원 CS의 출력 저항은 이론 상 무한대이기 때문에, 회로의 저항은 도 4의 TFT(31)에 의해 결정되는 한편, 패널 내부의 TFT는 일반적으로 구동 능력이 작아, 바꿔 말하면 입력 저항이 높기 때문에, 신호 입력선(16)의 전위가 정상 상태로 도달하기까지의 시간이 걸리기 때문이다.

- <120> 여기서 우선, 도 4의 회로예의 경우에 대해서 기입에 필요한 시간을 구한다. 기입 시에, TFT(31)는 게이트·드 레인 사이가 TFT(34)에 의해 단락되고, 따라서 포화 영역에서 동작하는 것을 근거로 하여, MOS 트랜지스터의 수학식 1의 양변을 게이트·소스 간 전압 Vgs로 미분함으로써,

## 수학식 7

- <121> 1/Rn= $\mu$  nCoxWn/Ln(Vgsn-Vth)

- <122> 을 얻는다. 여기서, TFT(31)가 NMOS이기 때문에, 필요한 파라미터에는 첨자 n을 붙여서 나타낸다. Rn은 TFT(31)의 신호 입력선(16)으로부터 본 미분 저항으로, 이것이 신호 입력선(16)의 입력 저항이다. 또, TFT(3 2)는 아날로그 스위치로 저항 특성을 나타내지만, TFT(31)에 비교하여 충분히 작은 저항치가 되도록 설계할 수 있기 때문에, 그 저항치는 무시한다.

- <123> 수학식 1, 수학식 7로부터,

## 수학식 8

- <124> Rn=1/√ (2µ nCoxWn/Ln· Iw)

- <125> 를 얻는다. 즉, TFT(31)의 입력 저항 Rn은 기입 전류 Iw의 평방근에 반비례하고, 특히 기입 전류 Iw가 작은 상 태에서는 매우 큰 값이 된다. 한편, 신호 입력선(16)에 존재하는 용량을 Cs로 하면, 기입 동작의 시상수는 정상 상태 부근에서는,

- <126>  $\tau = Cs \times Rn$

- <127> 으로 주어진다.

- <128> 신호 입력선(16)에 신호 전류를 공급하는 전류원 CS는 통상 패널 외부의 부품으로 구성되기 때문에, 데이터선 드라이버 회로(15)로부터 거리적으로 떨어져 있는 경우가 많고, 용량 Cs는 큰 값이 되기 쉽다. 게다가, 먼저설명한 바와 같이, TFT(31)의 입력 저항 Rn은 기입 전류 Iw가 작아짐에 따라 증대하기 때문에, 작은 전류의 기입에 요하는 긴 기입 시간은 중대한 문제이다.

- <129> 기입 시간을 단축하기 위해서는, 수학식 9로부터, TFT(31)의 입력 저항 Rn 을 작게 할 필요가 있다. 이를 위해서는, 최대 휘도치에 상당하는 전류치를 보다 큰 값으로 설정함으로써, 작은 휘도치에 있어서도 기입 전류 Iw가 너무 작아지지 않도록 하는 것이 생각되지만, 이것은 소비 전력의 증대를 초래한다. 혹은, TFT(31)의 Wn/Ln을 크게 하는 것이 생각되지만, 그 경우는 보다 작은 게이트 전압 진폭으로 TFT(31)를 사용하게 되기 때문에, 미소

한 노이즈에 의해 구동 전류가 영향받기 쉬워지는 등의 문제가 있다.

<130> 여기서, 도 6의 회로예의 회로 동작에 대하여 생각한다. 신호 입력선(16)에는 전류원 CS가 접속되어 있고, 이 전류원 CS와 본 전류 드라이버 회로 사이에는 비교적 큰 기생 용량 Cs가 존재하고 있다. 지금, 신호 전류 Iw를 기입하는 동작을 생각하여, TFT(40)가 포화 영역에서 동작하고 있다고 한다면, 정상 상태에서는 MOS 트랜지스터의 수학식 1에 따라서,

## 수학식 10

- $|V| = \mu pCoxWp/Lp/2(Vgs-Vtp)^2$

- <132> 가 성립된다. 여기서, TFT(40)가 PMOS이기 때문에, 필요한 파라미터에는 첨자 p를 붙여서 나타낸다.

- <133> 도 6의 회로예에서는, 신호 입력선(16)이 TFT(40)의 소스인 것에 주의하면,

## 수학식 11

- <134> Iw= $\mu$  pCoxWp/Lp/2(Vin-Vg-|Vtp|)<sup>2</sup>

- <135> 가 성립하는 것을 알 수 있다. Vin 및 Vg은 각각, 접지를 기준으로 한 신호 입력선(16)의 전압 및 TFT(40)의 게이트 전압이다.

- <136> 수학식 11의 양변을 신호 입력선(16)의 전압 Vin으로 미분하면,

### 수학식 12

- <137>  $1/Rp=\mu pCoxWp/Lp(Vin-Vg-|Vtp|)$

- <138> 를 얻는다. Rp는 TFT(40)의 신호 입력선(16)으로부터 본 미분 저항으로, 이것이 신호 입력선(16)의 입력 저항이다. 수학식 11, 수학식 12로부터,

## 수학식 13

- <139> Rp=1/ $\sqrt{(2\mu \text{ pCoxWp/Lp} \cdot \text{Iw})}$

- <140> 를 얻는다. 기입 동작의 시상수는 정상 상태 부근에서는,

## 수학식 14

- <141>  $\tau = C_S \times R_P$

- <142> 로 주어진다.

- <143> 여기서 주목해야 하는 것은, 수학식 13, 수학식 14에 따르면, 기입 시상수는 TFT(31)에 관한 파라미터(Wn, Ln 등)에 관계없이, P 채널 TFT(40)에 의해 결정된다는 것이다. 즉, TFT(40)의 Wp/Lp를 크게 설정하면, 수학식 13에 의해서 임의로 신호 입력선(16)의 입력 저항 Rp를 작게 할 수 있고, 수학식 14에 의해서 기입 동작의 시상수가 작아지는 것을 알 수 있다. 즉, 기입 전류 Iw의 크기나 TFT(31)의 파라미터를 변경하지 않고, 즉 먼저 설명한 바와 같은 소비 전력의 증대나 노이즈 내성의 악화를 수반하지 않고 기입을 고속화하는 것이 가능해진다.

- <144> 기입을 고속화하면, 일정한 시간 내에 동일한 신호 입력선(16)을 시분할적으로 사용하여 다수의 데이터를 데이터선 드라이버 열에 기입하는 것이 가능하게 되기 때문에, 패널과 패널 외부의 전류원 CS 사이의 접속 점수나, 전류원 CS의 개수를 삭감할 수 있다.

- <145> 여기서, TFT(40)를 포화 영역에서 동작시키기 위한 방법에 대하여 이하에 나타낸다. MOS 트랜지스터가 포화 영역에서 동작하기 위한 조건은 상술한 바와 같이 수학식 3으로 주어지지만, PMOS의 경우에는,

## 수학식 15

<146> Vd < Vg + |Vtp|

- <147> 로 표현해도 된다. 여기서, Vd, 및 Vg는 각각, 접지를 기준으로 한 드레인 전위 및 게이트 전위이다.

- <148> 기입 시간이 문제가 되는 것은, 앞서 설명한 것처럼 기입 전류 Iw가 작은 경우 이다. 그래서, 기입 전류 Iw가 제로에 가까운 기입 상태를 생각하면, TFT(31)는 그 게이트·드레인이 TFT(34)에 의해 전기적으로 단락되어 있고, 흐르는 전류가 제로에 가깝다. 이것으로부터, 그 드레인 전위는 거의 Vtn이지만, 이것은 TFT(40)의 드레인 전위 Vg이기도 하다. 따라서, 수학식 15는,

- <149> Vtn < Vg + |Vtp|

- <150> 로 표현할 수 있다.

- <151> 따라서, TFT(40)를 포화 영역에서 동작시키기 위해서는, 수학식 16이 성립하는 것, 구체적으로는, 예를 들면 게이트 전위 Vg=0으로 사용하는 경우에는 Vtn<|Vtp|로 하거나, 혹은 Vg을 0V가 아니고, 0V보다도 높은 전위로 사용하면 된다.

- <152> 상술한 바와 같이, TFT(31)와 전류원 CS 사이에, 휘도 데이터 sin의 기입 시에 포화 영역에서 동작하는 임피던 스 변환용 트랜지스터(본 예에서는, P 채널 TFT(40))를 접속함으로써, 본 전류 드라이버 회로에의 휘도 데이터 sin의 기입을 도 4의 회로예보다도 고속으로 행할 수 있다. 이에 따라, 일정한 시간 내에 동일한 신호 입력선 (16)을 시분할적으로 사용하여 다수의 데이터를 데이터선 드라이버 열에 기입하는 것이 가능하게 되기 때문에, 패널과 패널 외부의 전류원 CS 사이의 접속 점수나, 전류원 CS의 개수를 삭감할 수 있다.

- <153> 또, 본 회로예에서는 P 채널 TFT(40)를 TFT(31)과 전류원 CS 사이에 TFT(32)를 통해 접속하는 회로 구성으로 하였지만, 도 7에 도시한 바와 같이, 휘도 데이터 sin의 기입 시에 포화 영역에서 동작하는 P 채널 TFT(40)을 N 채널 TFT(32) 대신에 설치하고, 이 P 채널 TFT(40)에 임피던스 변환과 스위치(도 6의 TFT(32))의 양 기능을 갖게 하도록 해도, 상기한 경우와 마찬가지의 작용 효과를 얻을 수 있다. 이 변형예의 경우에는 전류 드라이버 회로마다 트랜지스터를 1개 삭감할 수 있기 때문에, 그 만큼만 회로 구성의 간략화, 저비용화를 도모할 수 있다는 이점이 있다.

- <154> [제2 실시 형태]

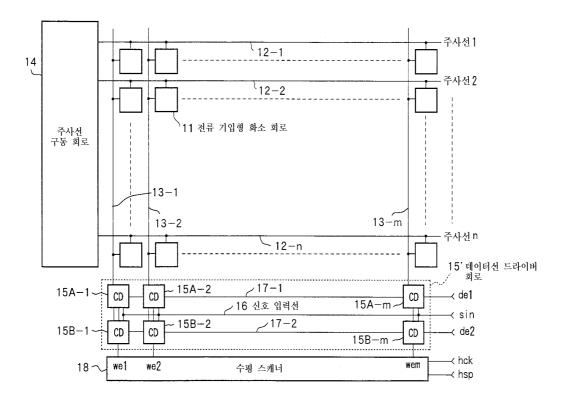

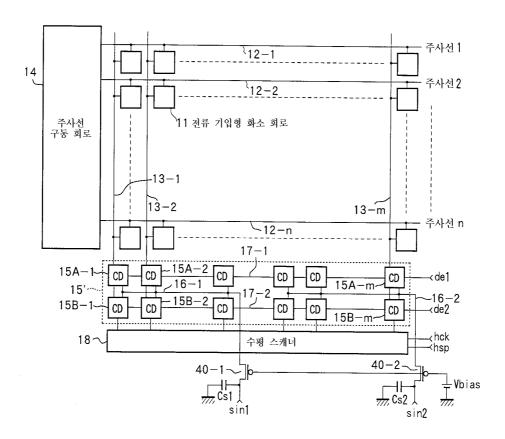

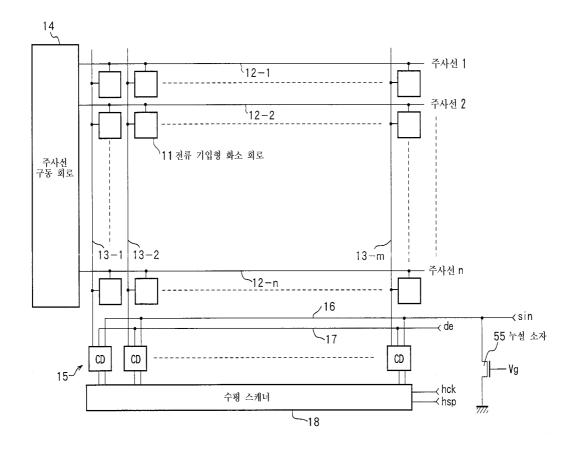

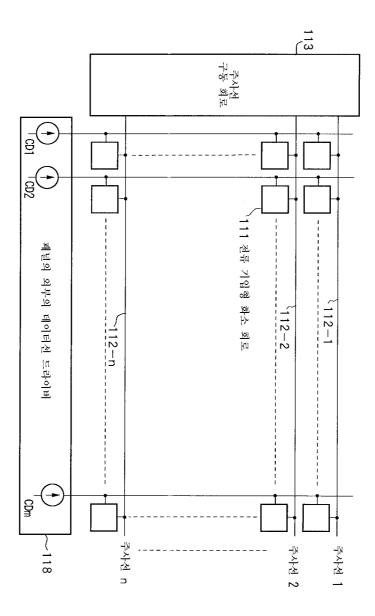

- <155> 도 8은 본 발명의 제2 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도로, 도 8 중, 도 1과 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 실시 형태에 따른 액티브 매트릭스형 표시 장치에 있어서, 제1 실시 형태에 따른 액티브 매트릭스형 표시 장치와의 차이는 데이터선 드라이버 회로(15')의 구성에 있다.

- <156> 즉, 제1 실시 형태에서는 데이터선 드라이버 회로(15)를 1열분의 전류 드라이버 회로(15-1~15-m)로 구성하고 있는 데 대하여, 본 실시 형태에서는 데이터선 드라이버 회로(15')를 2 열분의 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)로 구성하고 있다. 이들 2 열분의 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)에는 신호 입력선(16)을 통해서 외부로부터 화상 데이터(본 예에서는, 휘도 데이터) sin이 공급된다.

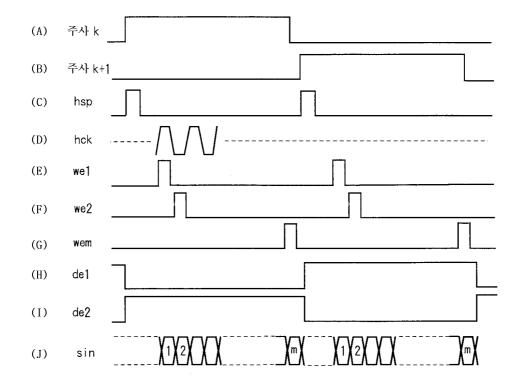

- <157> 2열분의 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)에는 또한, 2개의 제어선(17-1, 17-2)을 통해서 외부로부터 2계통의 구동 제어 신호 de1, de2가 공급된다. 이들의 구동 제어 신호 de1, de2는 도 9의 타이밍차트에 도시한 바와 같이, 1 주사선 기간의 주기로 극성이 반전하고, 또한 상호 역상의 신호로 되어 있다.

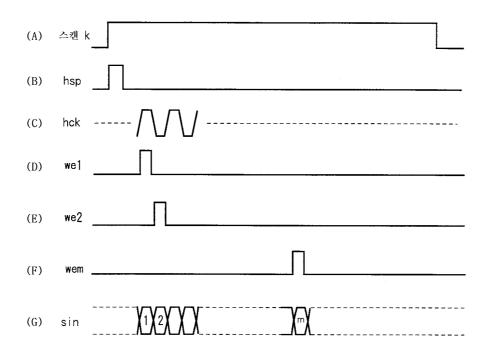

- <158> 한편, 수평 스캐너(18)는 도 9(A)~도 9(J)의 타이밍차트에 도시한 바와 같이, 수평 스타트 펄스 hsp의 입력후, 수평 클럭 신호 hck의 천이(상승 및 하강)에 대응하여, 1계통의 기입 제어 신호 we1~wem을 순차 발생하는 구성으로 되어 있다. 이 1계통의 기입 제어 신호 we1 ~wem은 2열분의 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)에 공급된다.

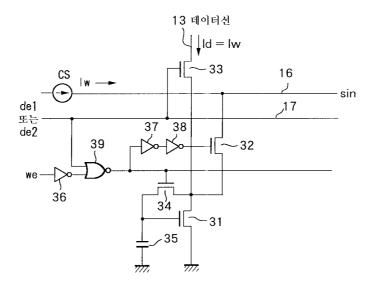

- <159> [제3 회로예]

- <160> 도 10은 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)의 구체적인 회로예를 도시하는 회로도로, 도 10 중, 도 4과 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 예에 따른 전류 드라이버 회로는, 4개의 TFT(31~34) 및 하나의 캐패시터(35)로 이루어지는 기본적인 회로 부분에 대해서는, 도 4의 전류 드라이버 회로와 동일하다.

- <161> 다른 점은 TFT(32) 및 TFT(34)를 제어하는 회로의 구성이다. 이 제어 회로는 3개의 인버터(36, 37, 38) 및 하

나의 NOR 회로(39)로 구성되어 있다. 인버터(36)는 수평 스캐너(18)로부터 공급되는 기입 제어 신호 we의 극성을 반전하여 NOR 회로(39)에 그 한쪽의 입력으로서 공급한다. NOR 회로(39)는 제어선(17-1)(또는, 17-2)을 통해 외부로부터 공급되는 구동 제어 신호 de1(또는, de2)을 다른 쪽의 입력으로 하고 있다.

- <162> 이 NOR 회로(39)를 통과한 구동 제어 신호 de1(또는, de2)은 직접 TFT(34)의 게이트에 공급됨과 함께, 인버터 (37, 38)를 통해 TFT(32)의 게이트에 공급된다. 인버터(37, 38)는 도 2(A)~도 2(K)의 타이밍차트에서의 제2 기입 제어 신호 weB에 대한 제1 기입 제어 신호 weA의 지연 시간에 상당하는 지연 시간을 갖고, NOR 회로(39)를 통과한 구동 제어 신호 de1(또는, de2)을 해당 지연 시간만 늦추어서 TFT(32)의 게이트에 제공한다.

- <163> 상기 구성의 전류 드라이버 회로에서, 그 기본적인 회로 동작은 도 4의 전류 드라이버 회로와 동일하다. 즉, 전류치의 형태로 기입된 휘도 데이터 sin을 일단 전압치로 변환하여 캐패시터(35)에 유지하여, 기입 종료 후에 도 캐패시터(35)의 전압치에 기초하여, 기입된 전류치와 거의 같은 전류치로 데이터선(13)을 구동하는 동작을 행한다.

- <164> 이에 덧붙여서, 본 예에 따른 전류 드라이버 회로에서는 구동 제어 신호 de1(또는, de2)를 비선택 상태(저레벨), 기입 제어 신호 we를 선택 상태(고레벨)로 함으로써 휘도 데이터 sin의 기입이 가능해지며, 구동 제어 신호 de1(또는, de2)을 선택 상태로 하는 것으로, 기입 제어 신호 we의 상태에 따르지 않고 데이터선(13)을 구동하는 상태가 된다.

- <165> 인버터(37, 38)는 상술한 바와 같이 지연 회로를 구성하고 있다. 이 인버터(37, 38)의 지연 작용에 의해 본 전류 드라이버 회로에의 기입 종료 시에, TFT(32)에 앞서서 TFT(34)를 비도통 상태로 함으로써, 확실한 데이터 기입을 행하도록 하고 있다.

- <166> 계속해서, 도 8에 도시한 제2 실시 형태에 따른 액티브 매트릭스형 표시 장치에 있어서, 화소 회로(11)로서 도 35의 전류 기입형 화소 회로를 이용하고, 또한 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)로서 도 10의 전류 기입형 전류 드라이버 회로를 이용한 경우의 동작에 대하여, 도 9(A)~도 9(J)의 타이밍차트에 기초하여 설명한다.

- <167> k번째의 주사선(12-k)의 선택 기간에 있어서, 구동 제어 신호 de1이 비선택 상태로 되어, 신호 입력선(16)으로 부터 제1 데이터선 드라이버 열(전류 드라이버 회로(15A-1~15A-m)에 대하여 휘도 데이터 sin의 기입이 가능해 진다. 그 동안, 수평 스캐너(18)로부터는 수평 클럭 hck에 대응하여 기입 제어 신호 we1~wem이 순차 출력되고, 신호 입력선(16)에는 그것에 동기하여 휘도 데이터 sin이 전류치의 형태로 주어지고, 제1 데이터선 드라이버 열에 휘도 데이터가 기입된다.

- <168> 다음에, k+1번째의 주사선(12-k+1)이 선택되면 구동 제어 신호 de1이 선택 상태로 되고, 전류 드라이버 회로 (15A-1~15A-m)에 기입되어 있는 데이터에 따라서 데이터선(13-1)~데이터선(13-m)이 구동된다. 이 때, 구동 제어 신호 de2는 비선택으로 되어 있고, 제2 데이터선 드라이버 열(전류 드라이버 회로(15B-1~15B-m)에 대하여 휘도 데이터 sin의 기입이 행해진다. 제2 데이터선 드라이버 열은 다음의 주사선 사이클에 있어서, k+2번째의 주사선(12-k+2)이 선택되었을 때에 데이터선(13-1~13-m)을 구동한다.

- <169> 이와 같이, 제1, 제2 데이터선 드라이버 열(전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)를 주사선(12-1~13-n)의 전환마다 교대로 피기입 상태/구동 상태로 함으로써, 데이터선 드라이버 회로(15')에의 기입 시간, 데이터선(13-1~13-m)의 구동 시간의 양방을 대략 1 주사선 주기분 확보할 수 있기 때문에, 데이터선 드라이버 회로(15')에의 기입 및 데이터선(13-1~13-m)의 구동에 대하여 확실한 동작이 가능해진다.

- <170> 또, 본 실시 형태에서는 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)로서, 도 10에 도시한 전류 기입형 전류 드라이버 회로를 이용한 경우를 예로 채용하여 설명하였지만, 이것에 한정되는 것은 아니고, 도 4, 도 6 및도 7에 도시한 전류 기입형 전류 드라이버 회로를 이용해도, 마찬가지의 작용 효과를 발휘한다. 단, 도 10의 회로예의 경우에는, 기입 제어 신호 we1~wem을 입력하는 신호선이 1개이기 때문에, 2개를 필요로 하는 도 4,도 6 및도 7의 회로예에 비교하여 데이터선 드라이버 회로(15)와 수평 스캐너(18) 사이를 접속하는 배선 개수를 반감할 수 있다고 하는 이점이 있다.

- <171> 또한, 본 실시 형태에 따른 액티브 매트릭스형 표시 장치에 있어서, 1 주사선 주기의 사이에 m개의 모든 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)에 대한 기입 동작을 완료하는 것이 어려운 경우에는 신호 입력선 (16)을 복수개 설치하고, 병렬 기입을 행하도록 하는 것도 가능하다(제2 실시 형태의 변형예).

- <172> 구체적으로는, 도 11에 도시한 바와 같이, 예를 들면 2개의 신호 입력선(16-1, 16-2)을 설치함과 함께, 전류 드

라이버 회로(15A-1~15A-m, 15B-1~15B-m)를 도면의 좌측반과 우측반으로 블록화하고, 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)에 대한 도면의 좌측반의 데이터 기입을 신호 입력선(16-1)이, 도면의 우측반의 데이터 기입을 신호 입력선(16-2)이 각각 담당하게 하도록 한다.

- <173> 이 구성을 채용하는 것으로, 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)에 대하여 2개씩 동시에(병렬로) 휘도 데이터 sin을 기입할 수 있기 때문에, 데이터선 드라이버 1개당 기입 시간은 2배가 되기 때문에, 기입 동작은 용이하게 된다. 마찬가지로 하여, 신호 입력선(16)을 3개 이상 설치하는 것도 가능하다.

- <174> 또한, 이와 같이 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)를 도면의 좌측반과 우측반으로 블록화한 구성의 액티브 매트릭스형 표시 장치에 대하여, 도 6에서 설명한 휘도 데이터 기입의 고속화의 개념을 적용할 수도 있다. 또, 이 경우에는 전류 기입형 전류 드라이버 회로로서, 도 4의 회로예가 이용되게 된다.

- <175> 즉, 도 12에 도시한 바와 같이, 신호 입력선(16-1, 16-2)의 입력부에 임피던스 변환용 트랜지스터, 예를 들면 P 채널 TFT(40-1, 40-2)를 삽입함과 함께, 이들 TFT(40-1, 40-2)의 각 게이트를 접지 전위보다도 높은 일정한 바이어스 전압치 Vbias로 바이어스하도록 한다. 여기서, 신호 입력선(16-1, 16-2)에는 각각 기생 용량 Cs1, Cs2가 존재하지만, 바이어스 전압치 Vbias를 적당하게 설정하면, P 채널 TFT(40-1, 40-2)를 포화 영역에서 동작시킬 수 있다.

- <176> 이와 같이, 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)를 블록화하고, 블록 내의 복수의 전류 드라이버 회로에 대하여, 휘도 데이터의 기입 시에 포화 영역에서 동작하는 임피던스 변환용 트랜지스터, 예를 들면 P 채널 TFT(40-1, 40-2)를 공통으로 설치하고, 이들 TFT(40-1, 40-2)의 Wp/Lp를 큰 값으로 설정함으로써, 도 6의 회로 설명의 경우와 마찬가지의 이유에 의해, 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)의 회로 구성이나 상수에 변경을 가하지 않고, 휘도 데이터의 기입의 고속화를 실현할 수 있다.

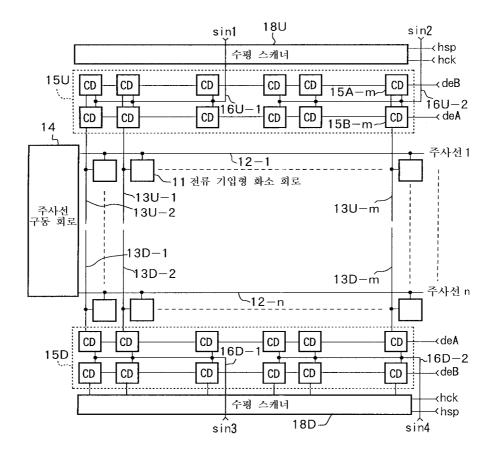

- <177> 또한, 제2 실시 형태의 다른 변형예로서, 도 13에 도시하는 구성을 채용하는 것도 가능하다. 도 13에 도시한 바와 같이, 이 외의 변형예에 따른 액티브 매트릭스형 표시 장치에서는, 도 11의 구성 외에 데이터선(13-1~13-m)을 중앙에서 2 분할하여, 표시 영역의 상하 양측에 데이터선 드라이버 회로(15U, 15D)를 배치한 구성을 채용하고 있다.

- <178> 이 경우, 수평 스캐너(18U, 18D)도 표시 영역의 상하 양측에 배치되게 된다. 또한, 도 11의 구성도 채용하기 때문에, 상측의 데이터선 드라이버 회로(15U)에 대하여 2개의 신호 입력선(16U-1, 16U-2)이 설치되고, 하측의 데이터선 드라이버 회로(15D)에 대하여 2개의 신호 입력선(16D-1, 16D-2)이 설치되게 된다.

- <179> 이 외의 변형예에 따른 구성을 채용함으로써, 상하의 데이터선 드라이버 회로(15U, 15D)가 각각 구동하는 데이터선(13U-1~13U-m, 13D-1~13D-m)의 배선 길이가 도 11의 구성의 경우의 절반으로 되기 때문에, 각 데이터선(13U-1~13U-m, 13D-1~13D-m)의 용량이 절반으로 되어, 그 만큼만 데이터선의 구동 시간이 짧게 되게 된다.

- <180> 또한, 화면 내의 상반분과 하반분에서 주사선(12-1~12-n)을 동시에 1개씩 선택·기입을 행할 수 있기 때문에, 1개의 주사선에 대한 기입 시간을 2배로 할 수 있기 때문에, 데이터선(13U-1~13U-m, 13D-1~13D-m)의 구동이나 데이터선 드라이버 회로(15U, 15D)에의 데이터 기입의 동작을 확실하게 행하는 것이 가능하다.

- <181> [제4 회로예]

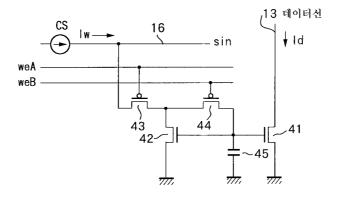

- <182> 도 14는 전류 드라이버 회로의 다른 회로예를 도시하는 회로도이다. 본 예에 따른 전류 드라이버 회로는, 제1 실시 형태(도 1 참조)에 따른 데이터선 드라이버 회로(15)의 전류 드라이버 회로(15-1~15-m) 또는 제2 실시 형 태에 따른 데이터선 드라이버 회로(15')의 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)로서 이용된다.

- <183> 도 14로부터 명백한 바와 같이, 본 예에 따른 전류 드라이버 회로는 4개의 TFT(41)~TFT(44) 및 하나의 캐패시 터(45)로 구성되어 있다. 이 회로예에서는, TFT(41, 42)를 NMOS로 구성하고, TFT(43, 44)를 PMOS로 구성하고 있지만, 이것은 일례로, 이것에 한정되는 것은 아니다.

- <184> TFT(41)는 그 소스가 접지되고, 그 드레인이 데이터선(13)에 접속되어 있다. TFT(41)의 게이트와 접지 사이에는, 캐패시터 C가 접속되어 있다. TFT(41)의 게이트에는 또한, TFT(42)의 게이트 및 TFT(44)의 드레인이 각각 접속되어 있다. TFT(41)와 TFT(42)는 근접하여 배치됨과 함께, 게이트가 공통 접속됨으로써 전류 미러 회로를 형성하고 있다.

- <185> TFT(42)의 소스는 접지되어 있다. TFT(42)의 드레인, TFT(43)의 드레인 및 TFT(44)의 소스가 공통으로 접속되어 있다. TFT(43)는 그 소스가 신호 입력선(16)에 접속되고, 그 게이트에는 제1 기입 제어 신호 weA가 주어진

- 다. 또한, TFT(43)의 게이트에는 제2 기입 제어 신호 weB가 주어진다.

- <186> 다음에, 상기 구성의 전류 드라이버 회로의 회로 동작에 대하여, 도 15(A)~도 15(C)의 구동 파형도를 이용하여 설명한다.

- 본 전류 드라이버 회로에의 기입 시에는 제1 기입 제어 신호 weA, 제2 기입 제어 신호 weB를 모두 선택 상태로 한다. 여기서는, 양자가 저레벨의 상태를 선택 상태로 하고 있다. 이 상태에서 신호 입력선(16)에 전류치 Iw의 전류원 CS를 접속함으로써, TFT(42)에 TFT(43)를 통해 기입 전류 Iw가 흐른다. 이 때, TFT(42)의 게이트·드레인 사이는 TFT(44)에 의해 전기적으로 단락되어 있기 때문에 수학식 3이 성립하고, TFT(42)는 포화 영역에서 동작한다. 따라서, TFT(42)의 게이트·소스 사이에는, 수학식 1에서 주어지는 전압 Vgs가 생긴다.

- <188> 다음에, 제1, 제2 기입 제어 신호 weA, weB를 비선택 상태로 한다. 자세하게는, 우선 제2 기입 제어 신호 weB를 고레벨로 하여 TFT(44)를 비도통 상태로 한다. 이에 따라, TFT(42)의 게이트·소스 사이에서 생긴 전압 Vgs 가 캐패시터(45)에 의해 유지된다.

- 지속해서, 제1 기입 제어 신호 weA를 고레벨로 하여 TFT(43)를 비도통 상태로 함으로써, 본 전류 드라이버 회로와 전류원 CS가 전기적으로 차단되기 때문에, 그 후에는 전류원 CS에 의해서 다른 전류 드라이버 회로에 대하여기입을 행할 수 있다. 여기서, 전류원 CS가 구동하는 데이터는, 제2 기입 제어 신호 WeB가 비선택으로 되는 시점에서는 유효할 필요가 있지만, 그 후는 임의의 값(예를 들면, 다음의 전류 드라이버 회로에의 기입 데이터)으로 되어도 된다.

- <190> TFT(41)와 TFT(42)는 게이트가 공통 접속되는 것으로, 전류 미러 회로를 형성하여 있기 때문에, TFT(41)가 포화 영역에서 동작하고 있으면, TFT(41)를 흐르는 전류는 수학식 2로 주어지고, 이것이 즉 데이터선(13)에 흐르는 전류로 되지만, 이것은 상술한 기입 전류 Iw에 비례한다.

- <191> 즉, 도 14에 도시하는 회로는, 도 4에 도시하는 회로와 마찬가지로, 전류치의 형태로 기입된 휘도 데이터 sin을 일단 전압치로 변환하여 캐패시터(45)에 유지하고, 기입 종료 후에도 캐패시터(45)의 전압치에 기초하여, 기입된 전류치에 비례하는 전류치로 데이터선(13)을 구동하는 기능을 갖는다. 이 동작에 있어서, TFT(41)와 TFT(42)가 근접 배치되는 등으로 해서, 이들 TFT의 이동도 μ나 임계치 Vth가 사실 상 같으면, 이들의 절대치는 문제가 되지 않는다. 즉, 도 14의 회로는 TFT의 특성 변동에 상관없이, 기입된 전류치와 정확하게 비례하는 전류치로 데이터선(13)을 구동할 수 있다.

- <192> 본 전류 드라이버 회로에의 기입 전류 Iw와 데이터선(13)의 구동 전류 Id와의 관계는, TFT(41)와 TFT(42)의 채널 폭 W 및 채널 길이 L의 설정에 의해, 바꿔 말하면 전류 미러 회로의 미러비의 설정에 의해서 원하는 값으로할 수 있다.

- <193> 예를 들면, TFT(41)와 TFT(42)에서 W/L의 값을 같게 하면 기입 전류 Iw와 구동 전류 Id는 같아지고, TFT(42)의 W/L을 TFT(41)의 W/L보다 크게 하면 기입 전류 Iw는 구동 전류 Id보다 커진다. 후자는, 예를 들면 외부의 전류 원 CS가 작은 전류를 구동하는 것이 어려운 경우나 전류 드라이버 회로에의 기입 시간을 고속화하고자 하는 경우에 유효하다.

- <194> 본 전류 드라이버 회로의 변형예를 도 16에 도시한다. 본 변형예에 따른 전류 드라이버 회로는 TFT(44)의 접속 위치가 도 14의 회로와 다를 뿐이다. 즉, T FT(44)는 TFT(41)의 게이트와 TFT(42)의 게이트 사이에 접속된 구성으로 되어 있다. 회로 동작으로서는 도 14의 회로의 경우와 마찬가지의 동작이 가능하다.

- <195> [제5 회로예]

- <196> 도 17은 전류 드라이버 회로의 또 다른 회로예를 도시하는 회로도이다. 본 예에 따른 전류 드라이버 회로도, 제1 실시 형태(도 1 참조)에 따른 데이터선 드라이버 회로(15)의 전류 드라이버 회로(15-1~15-m) 또는 제2 실시 형태에 따른 데이터선 드라이버 회로(15')의 전류 드라이버 회로(15A-1~15A-m, 15B-1~15B-m)로서 이용된다.

- <197> 본 예에 따른 전류 드라이버 회로는, 제1 회로예에 따른 전류 드라이버 회로(도 4를 참조)와 기본적인 회로 부분의 구성을 동일하게 하기 때문에, 이하의 설명에서는, 다른 회로 부분을 중심으로 그 구성에 대하여 설명한다. 또한, 도 17 중, 도 4와 동등 부분에는 동일 부호를 붙여서 나타낸다.

- <198> 도 17에서, TFT(41)의 드레인과 데이터선(13) 사이에 TFT(46)가 삽입되어 있다. 이 TFT(46)의 게이트·드레인 사이에는 TFT(47)가 접속되고, 그 게이트에는 제2 기입 제어 신호 weB가 주어진다. TFT(46)의 게이트와 접지

사이에는 캐패시터(48)가 접속되어 있다.

- <199> 다음에, 상기 구성의 전류 드라이버 회로의 회로 동작에 대하여 설명한다. 또, 이 회로 동작은 도 4의 회로와 마찬가지이기 때문에, 이하의 동작 설명에서는, 도 5(A)~도 5(D)의 구동 파형도를 이용하는 것으로 한다.

- <200> 우선, 본 전류 드라이버 회로에의 기입 시에는, 구동 제어 신호 de를 비선택 상태(저레벨)로 하여 데이터선(1 3)에 전류가 흐르지 않도록 한 상태에서 제1, 제2 기입 제어 신호 weA, WeB를 선택 상태(고레벨)로 하면, 기입 전류 Iw가 TFT(42)를 통하여 TFT(41) 및 TFT(46)로 흐른다. 이 때, 양 TFT(41), TFT(46) 모두, 게이트·소스 사이가 각각 TFT(44) 및 TFT(47)에 의해서 단락되어 있기 때문에, 포화 영역에서 동작한다.

- <201> 다음에, 제2 기입 제어 신호 weB를 비선택 상태로 한다. 이에 따라, TFT(41) 및 TFT(46)의 각 게이트·소스 사이에서 생긴 전압 Vgs가 캐패시터(45) 및 캐패시터(48)에 의해서 각각 유지된다. 다음에, 제1 기입 제어 신호 weA를 비선택 상태로 함으로써, 본 전류 드라이버 회로와 신호 입력선(16)이 전기적으로 차단되기 때문에, 그후에는 신호 입력선(16)을 통해 다른 전류 드라이버 회로에의 기입을 행할 수 있다.

- <202> 다음에, 데이터선 구동 제어 신호 de를 고레벨로 한다. TFT(41)의 게이트·소스 간 전압 Vgs는 캐패시터(45)에 의해서 유지되어 있기 때문에, TFT(41)가 포화 영역에서 동작하고 있으면, TFT(41)를 흐르는 전류는 수학식 5의 기입 전류 Iw에 일치하고, 이것이 즉 데이터선(13)에 흐르는 전류 Id로 된다. 즉, 기입 전류 Iw가 데이터선 (13)의 구동 전류 Id와 일치한다.

- <203> 여기서, TFT(46)의 작용에 대하여 설명한다. 도 4의 회로에서는, 상술한 바와 같이, 기입 전류 Iw, 데이터선 (13)의 구동 전류 Id는 모두 TFT(41)에 의해서 결정되기 때문에, 수학식 5, 수학식 6으로부터 Iw=Idrv였다. 단, 이것은 TFT(41)를 흐르는 전류 Ids가 포화 영역에서 드레인. 소스 간 전압 Vds에 의존하지 않는 것으로 한경우이다.

- <204> 그런데, 현실정의 트랜지스터에서는, 게이트·소스 간 전압 Vgs가 일정하여도, 드레인·소스 사이 전압 Vds가 클수록 드레인·소스 사이 Ids가 커지는 경우가 있다. 이것은 드레인·소스 사이 전압 Vds가 커짐으로써 드레인 근방의 핀치 오프점이 소스측으로 이동하여, 실효적인 채널 길이가 감소하는, 소위 쇼트 채널 효과나, 드레인의 전위가 채널 전위에 영향을 주어 채널의 도전율이 변화하는, 소위 백 게이트 효과 등의 때문이다.

- <205> 이 경우, 트랜지스터를 흐르는 전류 Ids는, 예를 들면,

- <206>  $Ids = \mu CoxW/L/2(Vgs-Vth)^{2} \times (1+\lambda Vds)$

- <207> 가 되는 관계식으로 표현되며, 드레인·소스 사이 전압 Vds에 의존하게 된다. 여기서, λ는 플러스의 상수이다. 이 경우, 도 4의 회로에서는, 기입 시와 구동 시에 드레인·소스 사이 전압 Vds가 동일하지 않으면, 기입 전류 Iw와 OLED에 흐르는 전류 Idrv는 일치하지 않는다.

- <208> 이것에 대하여, 도 17의 회로의 동작을 생각한다. 도 17의 TFT(46)의 동작에 주목하면, 그 드레인 전위는 기입시와 구동 시에 일반적으로 동일하지 않다. 예를 들면, 구동 시에 드레인 전위쪽이 높은 경우, TFT(46)의 드레인·소스 사이 전압 Vds도 커져, 이것을 수학식 17에 적용시키면, 기입 시와 구동 시에 게이트·소스 간 전압 Vgs가 일정하여도, 드레인·소스 사이 전류 Ids는 구동 시의 쪽이 증가한다. 바꾸어 말하면, 기입 전류 Iw보다 OLED에 흐르는 전류 Idrv가 커져 양자는 일치하지 않는다.

- <209> 그런데, OLED에 흐르는 전류 Idrv는 TFT(41)를 흐르기 때문에, 그 경우 TFT(41)에서의 전압 강하가 커져, 그 드레인 전위(TFT(46)의 소스 전위)가 상승한다. 이 결과, TFT(46)의 게이트·소스 간 전압 Vgs는 작아져, 이것은 OLED에 흐르는 전류 Idrv를 작게 하는 방향에 작용한다. 결과적으로, TFT(41)의 드레인 전위는 크게 변동하지 않아, TFT(41)에 주목하면, 기입 시와 구동 시에 드레인·소스 간 전류 Ids가 크게는 변하지 않는 것을 알 수 있다. 즉, 기입 전류 Iw보다 OLED에 흐르는 전류 Idrv가 꽤 정밀하게 일치하게 된다.

- <210> 이 동작을 보다 잘 행하게 하기 위해서는, TFT(41), TFT(46) 모두 드레인·소스 간 전압 Vds에 대한 드레인·소스 간 전류 Ids의 의존성을 작게 하는 것이 좋기 때문에, 양 트랜지스터를 포화 영역에서 동작시키는 것이 바람 직하다. 기입 시에는 TFT(41, 46) 모두 게이트·드레인 사이가 단락되어 있기 때문에, 기입되는 휘도 데이터에 상관없이, 필연적으로 양자 모두 포화 영역에서 동작한다. 구동 시에도 포화 영역에서 동작시키기 위해서는, 데이터선(13)을 충분히 높은 전위로 하면 된다. 이 구동에 따르면, 데이터선(13)에 흐르는 전류 Id는 TFT의 특

성 변동에 상관없이, 도 4의 회로예의 경우보다도 정확하게 기입 전류 Iw에 일치한다.

- <211> [제3 실시 형태]

- <212> 도 18은 본 발명의 제3 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도로, 도 18 중, 도 1과 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 실시 형태에 따른 액티브 매트릭스형 표시 장치에 있어서, 제1 실시 형태에 따른 액티브 매트릭스형 표시 장치와의 차이는 데이터선을 구동하는 데이터선 드라이버 회로의 구성에 있다.

- <213> 즉, 제1 실시 형태에서는 데이터선 드라이버 회로(15)로서 전류 기입형의 전류 드라이버 회로를 이용하여 있는데 대하여, 본 실시 형태에서는 데이터선 드라이버 회로(19)로서 전압 기입형의 전류 드라이버 회로(CD)(19-1~19-m)를 이용하고 있다. 전압 기입형의 전류 드라이버 회로(이하, 단순히 「전류 드라이버 회로」라고 적는다)(19-1~19-m)는, 각 출력단이 데이터선(13-1~13-m)의 각 일단에 접속되어 있다.

- <214> [제6 회로예]

- <215> 도 19는 데이터선 드라이버 회로(19)를 구성하는 전압 기입형 전류 드라이버 회로(19-1~19-m)의 구체적인 회로 예를 나타내는 회로도이다. 또, 전류 드라이버 회로(19-1~19-m) 각각은 완전히 동일한 회로 구성으로 되어 있다.

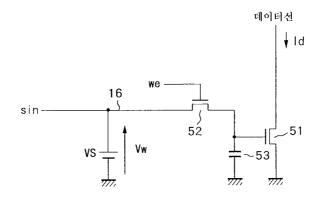

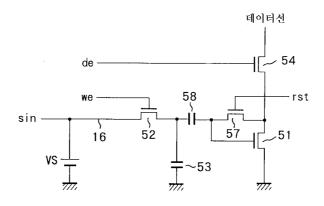

- <216> 도 19로부터 명백한 바와 같이, 본 예에 따른 전류 드라이버 회로는 2개의 TFT(51, 52) 및 하나의 캐패시터(5 3)로 구성되어 있다. TFT(51)는 데이터선(13)과 접지 사이에 접속되어 있다. TFT(52)는 TFT(51)의 게이트와 신호 입력선(16) 사이에 접속되어 있다. 캐패시터(53)는 TFT(51)의 게이트와 접지 사이에 접속되어 있다. 이 회로예에서는 TFT(51, 52)를 NMOS로 구성하고 있지만, 이것은 일례이고, 이것에 한정되는 것은 아니다.

- <217> 상기 구성의 전류 드라이버 회로에서는 휘도 데이터 sin이 신호 입력선(16)을 통해 전압의 형태로 전압원 VS에 의해서 주어지는 점이 특징이다. 휘도 데이터 sin 의 기입 시에는 기입 제어 신호 we를 선택 상태(여기서는, 고레벨)로 하여 신호 입력선(16)에 전압 Vw를 인가하면, TFT(52)가 도통 상태이기 때문에, TFT(51)의 게이트·소스 간 전압 Vgs가 기입 전압 Vw로 된다.

- <218> 이 기입 전압 Vw는 기입 제어 신호 we가 비선택 상태로 되어도 캐패시터(53)에 의해 유지된다. TFT(51)가 포화 영역에서 동작하고 있으면, TFT(51)를 흐르는 전류 Id는,

- <219> Id= $\mu$  CoxW/L/2(Vw-Vth)<sup>2</sup>

- <220> 이 된다. 따라서, 기입 전압 Vw에 의해서 데이터선(13)의 구동 전류 Id를 제어할 수 있다.

- <221> 도 18에 도시하는 액티브 매트릭스형 표시 장치에 있어서, 데이터선 드라이버 회로(19)를 상기 구성의 전류 드라이버 회로를 이용하여 구성한 경우의 동작의 타이밍차트를 도 20(A)~도 20(G)에 도시한다. 또, 그 동작은 기본적으로는 도 1의 경우와 마찬가지이기 때문에, 여기서는 그 상세한 설명에 대해서는 생략한다.

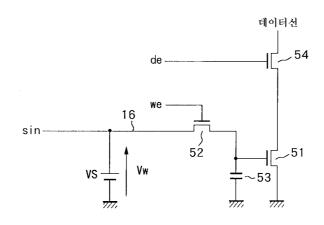

- <222> [제7 회로예]

- <223> 도 21은 전압 기입형 전류 드라이버 회로의 다른 회로예를 도시하는 회로도로, 도면 중, 도 19과 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 예에 따른 전류 드라이버 회로에서는, 도 19의 회로에, 데이터선 구동 제어 신호 de로 제어되는 TFT(54)를 추가한 구성으로 되어 있다. TFT(54)는 데이터선(13)과 TFT(51)의 드레인 사이에 접속되고, 그 게이트에 구동 제어 신호 de가 주어진다. 이 회로예에서도 TFT(51, 52, 54)를 NMOS로 구성하고 있지만, 이것은 일례이고, 이것에 한정되는 것은 아니다.

- <224> 이와 같이, 데이터선(13)과 TFT(51)의 드레인 사이에, 구동 제어 신호 de로 제어되는 TFT(54)를 접속한 구성을 채용함으로써, 해당 전류 드라이버 회로를 이용하여 도 1, 도 8, 도 11 혹은 도 12에 도시한 바와 같은 액티브 매트릭스형 표시 장치를 구성하는 것이 가능해진다. 특히, 도 8, 도 11 혹은 도 12의 구성의 액티브 매트릭스형 표시 장치에 적용한 경우에는 데이터선 드라이버 회로가 2열(2계통) 설치되어 있기 때문에, 데이터선 드라이버 회로에의 기입과 데이터선(13-1~13-m)의 구동을 교대로 행하게 함으로써 각각의 동작 시간에 여유가 생긴다.

- <225> [제8 회로예]

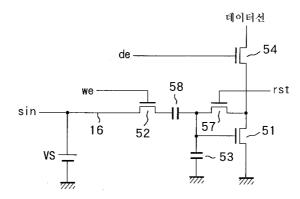

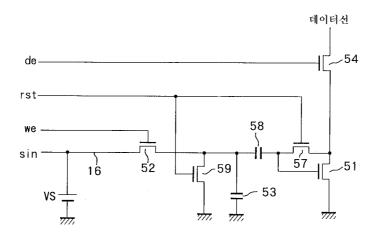

- <226> 도 22는 전압 기입형 전류 드라이버 회로의 또 다른 회로예를 도시하는 회로도로, 도 22 중, 도 21과 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 예에 따른 전류 드라이버 회로에서는, 도 21의 회로에, TFT(51)의 게이트와 드레인 사이에 접속된 리세트 TFT(57)와, TFT(51)의 게이트와 TFT(52)의 소스 사이에 접속된 데이터 기입 캠페시터(58)를 추가한 구성으로 되어 있다.

- <227> 그런데, 도 21의 회로예에서는, 휘도 데이터가 전압의 형태로 주어지고, 그것이 그대로 캐패시터(53)에 유지되고, 그 유지된 전압에 기초하여 TFT(51)가 데이터선에 전류를 흘리는 구성으로 되어 있지만, 이 구성에서는, TFT(51)의 임계치가 변동되면, 수학식 1에 따라 구동 전류가 변동하여, 화상의 품위를 손상시킬 가능성이 있다.

- <228> 이것에 대하여, 본 회로예에 따른 전압 기입형 전류 드라이버 회로에서는, 리세트 TFT(57)에 의해서 TFT(51)의 게이트·드레인을 소정의 기간 전기적으로 단락시키는 동작을 행한 후, TFT(51)의 게이트와 신호 입력선(16)을 데이터 기입 캐패시터(58)에 의해 용량 결합시키는 구성을 채용함으로써, TFT(51)의 임계치가 변동되어도, 구동 전류가 변동되지 않기 때문에, 화상의 품위를 손상시키지는 않는다. 이하에, 도 23(A)~도 23(D)의 타이밍차트를 이용하여 그 구체적인 동작 설명을 행한다.

- <229> 우선, TFT(54)가 온 상태일 때, 리세트 TFT(57)의 게이트에 고레벨의 리세트 신호 rst를 제공함으로써 해당 TFT(57)을 온 상태로 한다. 그러면, TFT(51)의 게이트·드레인이 전기적으로 단락되지만, 이 때 TFT(54)가 온 상태로서, 데이터선으로부터 TFT(54) 및 TFT(51)를 통해 접지를 향하여 전류가 흐르기 때문에, TFT(51)의 게이트·소스 간 전압은 그 임계치 Vth보다도 높아지고 있다.

- <230> 다음에, TFT(54)의 게이트에 주어지는 구동 신호 de가 저레벨이 됨으로써 TFT(54)가 오프 상태로 되면, TFT(5 1)을 흐르는 전류는 소정의 시간 경과한 후에 제로로 된다. 이 때, 그 드레인·게이트 사이가 TFT(57)에 의해서 단락되어 있기때문에, TFT(51)의 드레인 및 게이트의 전위는 점차로 저하해 가고, 그 값이 TFT(51)의 임계치 Vth로 된 상태에서 안정된다. 이 때, TFT(52)의 게이트에 고레벨의 기입 제어 신호 we가 인가됨으로써, 신호 입력선(16)은 소정의 전위(본 예에서는, 접지 레벨)로 된다(이하, 이 동작을 리세트 동작으로 칭한다). 그 후에, 신호 입력선(16)에 신호 전압 Vw를 인가한다.

- <231> 신호 입력선(16)과 TFT(51)의 게이트는, 데이터 기입 캐패시터(58)를 통해, 즉 용량 결합으로 접속되어 있기 때문에, 캐패시터(53, 58)의 용량치를 Co, Cd로 하면, TFT(51)의 게이트 전위는 대략,

## 수학식 19

- $\langle 232 \rangle$   $\Delta Vg = Vw \times Cd/(Cd + Co)$

- <233> 만큼 상승한다. 신호 전압 Vw의 인가 이전에는 Vg=Vth이기 때문에, TFT(51)의 게이트·소스 간 전압 Vgs는,

#### 수학식 20

$Vgs=Vth+\Delta Vg$

- $=Vth+Vw\times Cd/(Cd+Co)$

- <235> 로 된다(이하, 이 동작을 피(被)기입 동작으로 칭한다).

- <236> 신호 전압 Vw의 인가 후에는 TFT(52)를 오프 상태로 하고, TFT(54)의 게이트에 구동 제어 신호 de를 제공함으로 써 해당 TFT(54)를 온 상태라 하면, TFT(51)에 의해 데이터선에 전류가 흐른다. 이 때, 그 전류치 Id는 수학식 1 및 수학식 20으로부터

- Id= $\mu$  CoxW/L/2{Vw× Cd/(Cd+Co)}<sup>2</sup>

- <238> 로 된다(이하, 이 동작을 구동 동작으로 칭한다). 수학식 21은 임계치 Vth를 포함하지 않기 때문에, 구동 전류 치 Id는 TFT(51)의 임계치 Vth의 변동에 따르지 않는 것을 알 수 있다.

- <239> 도 24는 제8 회로예의 변형예를 도시하는 회로도이며, 도 24 중, 도 22와 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 변형예에 따른 전류 드라이버 회로에서는, 캐패시터(53)가 데이터 기입 캐패시터(58)의 출력단과

접지 사이에 접속되어 있는 제8 회로예에 대하여, 데이터 기입 캐패시터(58)의 입력단과 접지 사이에 접속되어 있는 점이 다를 뿐이며, 그 밖의 구성 및 동작 타이밍차트는 동일하다.

- <240> 이와 같이, 캐패시터(53)를 데이터 기입 캐패시터(58)의 입력단과 접지 사이에 접속한 구성을 채용함으로써, 신호 전압 Vw를 인가한 후의 TFT(51)의 게이트·소스 간 전압 Vgs가 거의 Vth+Vw로 주어진다. 즉, 제8 회로예에 따른 전류 드라이버 회로에 비하여, 동일한 신호 전압 Vw에 대하여 보다 큰 게이트·소스 간 전압 Vgs가 얻어지는 이점이 있다.

- <241> 도 25는 제8 회로예의 또 다른 변형예를 도시하는 회로도로, 도 25 중, 도 24와 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 변형예에 따른 전류 드라이버 회로에서는 데이터 기입 캐패시터(58)의 신호 입력선측 노드와 소정의 전위점(본 예에서는 접지) 사이에 접속된 스위치 소자, 예를 들면 TFT(59)가 새롭게 부가된 점 및 그에 대응하는 리세트 동작의 점에서, 도 24의 회로예에 따른 전류 드라이버 회로와 상위하고 있다.

- <242> 이하에, 본 변형예에 따른 전류 드라이버 회로의 동작에 대하여, 도  $26(A) \sim$ 도 26(D)의 타이밍차트를 이용하여 설명한다. 리세트 동작 시에는 도 24의 회로예와 마찬가지로, TFT(57)의 게이트에 고레벨의 리세트 신호 rst를 제공함으로써 해당 TFT(57)를 온 상태로 함으로써, TFT(51)의 게이트·드레인이 전기적으로 단락된다.

- <243> 다음에, TFT(54)의 게이트에 주어지는 구동 신호 de가 저레벨로 되어 TFT(54)가 오프 상태로 되면, 도 24의 회로예와 마찬가지로, TFT(51)의 게이트 및 드레인은 그 임계치 Vth로 된 상태에서 안정된다. 단 이 때, TFT(52)의 게이트에 주어지는 기입 제어 신호 we는 저레벨 그대로이고, 대신에 새롭게 부가된 TFT(59)가 리세트 신호rst에 의해 온 상태가 되기 때문에, 그 드레인 전위는 소정의 전위(본 예에서는 접지 레벨)로 된다.

- <244> 그 후, 리세트 신호 rst가 저레벨로 됨으로써, TFT(59)는 오프 상태로 되고, 그 후에 기입 제어 신호 we가 고레벨로 된다. 신호 입력선(16)에는 신호 전압 Vw가 인가되어 있기 때문에, 데이터 기입 캐패시터(58)를 통해 신호 전압 Vw가 구동 트랜지스터(51)의 게이트에 전달되어, 그 게이트·소스 간 전압은 도 24의 회로예와 마찬가지로, 대략 Vth+Vw가 된다.

- <245> 이와 같이, 도 25의 회로예에 따른 전류 드라이버 회로에서는, 기본적인 동작은 도 24의 회로예와 마찬가지이지만, 그 장점은, 신호 입력선(16)의 제어가 간단해짐과 동시에, 기입 속도가 빠르게 되는 점에 있다. 즉, 도 24의 회로예와 같이, 리세트 동작 시에, 신호 입력선(16) 및 TFT(52)을 통해 캐패시터(53)를 기준 전위(본 예에서는, 접지 레벨)로 리세트하는 구성을 채용한 경우에는 신호 입력선(16)의 전위의 제어가 필요해진다.

- <246> 이에 대하여, 도 25의 회로예에서는, TFT(59)에 의해서 간편하게 캐패시터(53)의 리세트를 행할 수 있기 때문에, 신호 입력선(16)에 기준 전위를 제공할 필요가 없다. 따라서, 신호 입력선(16)의 제어가 간단해지고, 더구나, 예를 들면 도 26(A)~도 26(D)에 도시한 바와 같이, 데이터선 구동 회로에의 신호 전압 Vw의 기입 종료후에는 신호 입력선(16)은 임의의 전위, 예를 들면 다음의 기입 사이클의 신호 전압으로 되기 때문에, 신호 전압 Vw 의 기입을 고속으로 행할 수 있게 된다.

- <247> [제4 실시 형태]

- <248> 도 27은 본 발명의 제4 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도로, 도 27 중, 도 18과 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 실시 형태에 따른 액티브 매트릭스형 표시 장치는 제3 실시 형태에 따른 액티브 매트릭스형 표시 장치와 다른 점은 데이터선 드라이버 회로(19')의 구성에 있다.

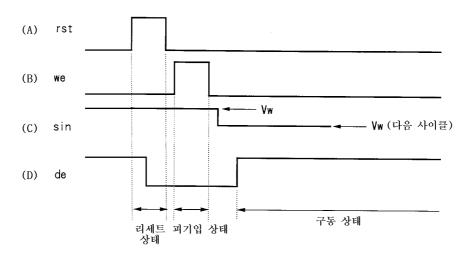

- <249> 즉, 제3 실시 형태에 따른 액티브 매트릭스형 표시 장치에서는, 데이터선 드라이버 회로(19)가 1계통의 전압 기입형 전류 드라이버 회로(CD)(19-1~19-m)에 의해서 구성되어 있는 데 대하여, 본 실시 형태에 따른 액티브 매트릭스형 표시 장치에서는, 데이터선 드라이버 회로(19')가 3계통의 전압 기입형 전류 드라이버 회로(19A-1~19A-m, 19B-1~19B-m, 19C-1~19C-m)에 의해서 구성되어 있다.

- <250> 그리고, 3계통의 전압 기입형 전류 드라이버 회로(19A-1~19A-m, 19B-1~19B-m, 19C-1~19C-m)로서, 상술한 제 8 회로예에 따른 전압 기입형 전류 드라이버 회로, 즉 구동 TFT(51)의 게이트·드레인을 소정의 기간 전기적으로 단락시키는 동작을 행한 후, TFT(51)의 게이트와 신호 입력선(16)을 용량 결합시킴으로써, TFT(51)의 임계치가 변동되어도, 구동 전류가 변동되지 않도록 한 드라이버 회로가 이용된다.

- <251> 전압 기입형 전류 드라이버 회로를 데이터선마다 3계통 설치한 이유는 다음과 같다. 즉, 제8 회로예에 따른 전류 드라이버 회로는, 상술한 바와 같이, 리세트 동작·피기입 동작·구동 동작의 3 종류의 동작을 반복함으로써 원하는 기능을 달성한다. 그래서, 본 실시 형태에 따른 액티브 매트릭스형 표시 장치에서는, 임의의 주사 사이

클에 있어서, 도 28(A)~도 28(C)에 도시한 바와 같이, 3열(3계통)의 데이터선 구동 회로 중 1열이 리세트 동작을, 다른 1열이 피기입 동작을, 남은 1열이 구동 동작을 행하도록 하고, 각각의 동작을 주사선 전환 주기마다 전환하도록 하고 있다.

- <252> 이와 같이, 리세트 동작·피기입 동작·구동 동작의 3 종류의 동작을 반복함으로써 원하는 기능을 달성하는 전압 기입형 전류 드라이버 회로를 데이터선 드라이버 회로로서 이용한 액티브 매트릭스형 표시 장치에 있어서, 전압 기입형 전류 드라이버 회로를 1개의 데이터선에 대하여 3계통씩 설치하고, 임의의 주사 사이클에 있어서 1계통의 드라이버 회로가 리세트 동작을, 다른 1계통의 드라이버 회로가 피기입 동작을, 남은 1계통의 드라이버 회로가 구동 동작을 행하도록 한 것으로, 각각의 동작에 1 주사선의 전환 주기(1H)를 써버리는 것이 가능해지기 때문에, 확실한 동작이 가능해진다.

- <253> [제5 실시 형태]

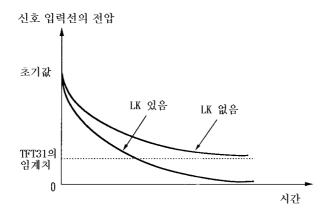

- <254> 도 29는 본 발명의 제5 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도로, 도 29 중, 도 1과 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 실시 형태에 따른 액티브 매트릭스형 표시 장치는, 제1 실시 형태에 따른 액티브 매트릭스형 표시 장치와 기본적인 구성이 완전히 동일하고, 이에 덧붙여서, 신호 입력선(16)과 접지 사이에, 예를 들면 NMOS 트랜지스터로 이루어지는 누설 소자(LK)(55)를 접속한 점을 특징으로 한다.

- <255> 이하에, 누설 소자(55)의 작용에 대하여 설명한다. 전류 기입형의 화소 회로에서, 「흑」을 기입하는 케이스는 기입 전류가 제로의 경우에 상당한다. 이 때, 직전의 기입 사이클에 있어서 신호 입력선(16)에 「백」 레벨, 즉 비교적 큰 전류가 기입되어, 결과적으로 신호 입력선(16)의 전위가 비교적 높은 레벨로 되어 있다고 하면, 그 직후에 「흑」을 기입하는 데에는 긴 시간이 필요하다.

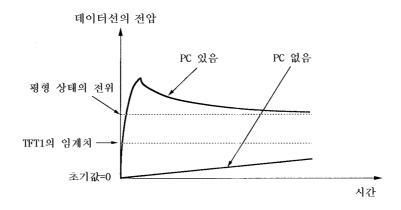

- <256> 왜냐하면, 「흑」을 기입한다고 하는 것은, 예를 들면 도 4에 도시한 전류 드라이버 회로에서, TFT(31)에 의해서 신호 입력선(16)의 용량 Cs 등에 축적된 초기 전하가 방전되고, 도 30에 도시한 바와 같이, 신호 입력선(16)의 전압이 TFT(31)의 임계치가 되기 때문이다. 이와 같이, 신호 입력선(16)의 전압이 내려가 TFT(31)의 임계치 근방이 되면, TFT(31)의 임피던스가 높아져, 이론적으로는 영구히 「흑」 기입이 종료하지 않는다. 현실적으로는, 유한의 시간에 기입을 행하는 것이므로, 이것은 「흑」 레벨이 완전하게 저하하지 않는, 소위 흑부유 현상으로서 나타나 화상의 콘트라스트를 저하시킨다.

- <257> 이것에 대하여, 본 실시 형태에 따른 액티브 매트릭스형 표시 장치에서는, 신호 입력선(16)과 소정의 전위점(예를 들면, 접지 전위) 사이에 누설 소자(55), 구체적으로는 NMOS 트랜지스터를 접속하고, 그 게이트 전압 Vg로서 일정 바이어스를 제공하도록 하고 있다. 이에 따라, 도 30에 도시한 바와 같이, 「흑」 기입 시에 TFT(31)의 임계치 근방에서도 데이터선 전위가 비교적 고속으로 저하하여, 상술한 흑부유를 방지할 수 있다.

- <258> 또, 누설 소자(55)로서는, 단순한 저항 소자 등이어도 좋지만, 그 경우, 「백」 기입 시에서 데이터선 전위가 상승하면, 그에 비례하여 저항 소자에 흐르는 전류가 증가한다. 이것은, 도 4에 도시한 전류 드라이버 회로에서 TFT(31)에 흐르는 전류의 저하나 소비 전력의 악화를 초래한다.

- <259> 이것에 대하여, 도 29에 도시한 바와 같이, 누설 소자(55)로서 NMOS 트랜지스터를 사용하여, 해당 트랜지스터를 포화 영역에서 동작시키면 정전류 동작으로 되기 때문에, 그와 같은 폐해를 최소한으로 억제할 수 있다. 또한, NMOS 트랜지스터의 누설 소자(LK)(55)를, 필요할 때(예를 들면, 흑 기입 시)에만 도통 상태가 되도록 게이트 전위를 제어하는 구성을 채용할 수도 있다.

- <260> 이와 같이, 신호 입력선(16)과 접지 전위 사이에 누설 소자(55)를 접속하는 구성은 데이터선 드라이버 회로로서도 4와 같은 전류 기입형의 드라이버 회로를 이용한 도 1의 구성의 액티브 매트릭스형 표시 장치에의 적용에 한정되는 것은 아니고, 다른 전류 기입형의 드라이버 회로, 혹은 도 19와 같은 전압 기입형의 데이터선 드라이버 회로를 이용한 구성의 액티브 매트릭스형 표시 장치에도 마찬가지로 적용 가능하다. 또, 누설 소자(55)로서는 TFT로 구성하거나, TFT 프로세스와는 별개로 외부 부품으로 구성하는 것도 가능하다.

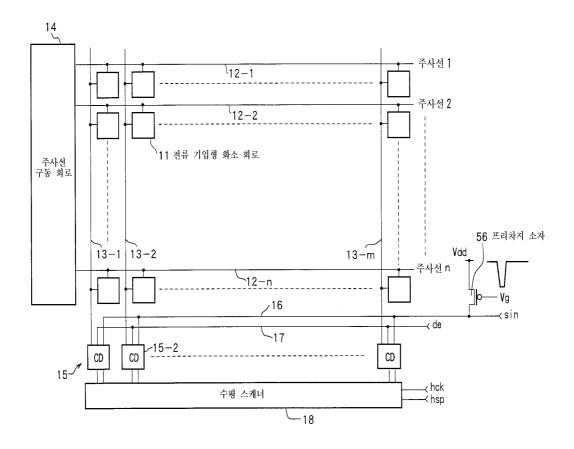

- <261> [제6 실시 형태]

- <262> 도 31은 본 발명의 제6 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 나타내는 블록도로, 도면 중, 도 1과 동등 부분에는 동일 부호를 붙여서 나타낸다. 본 실시 형태에 따른 액티브 매트릭스형 표시 장치는 제1 실시 형태에 따른 액티브 매트릭스형 표시 장치와 기본적인 구성이 완전히 동일하고, 이에 덧붙여서, 신호 입력선(16)과 플러스 전원 Vdd 사이에 초기치 설정용 소자, 예를 들면 PMOS 트랜지스터로 이루어지는 프리차지

소자(PC)(56)를 접속한 점을 특징으로 한다.

- <263> 이하에, 프리차지 소자(56)의 작용에 대하여 설명한다. 전류 기입형의 화소 회로에서, 흑에 가까운 회색을 기입할 때에 긴 시간을 요하는 경우가 있다. 도 32에서는, 기입 개시 시의 데이터선의 전위가 0V인 경우를 나타낸다. 이것은 직전의 기입 사이클에 있어서 「흑」을 기입한 경우에서, 기입된 전류 드라이버 회로(예를 들면,도 4의 경우)의 TFT(31)의 임계치가 0V 정도로 낮은 경우, 혹은 마찬가지로 흑 기입의 경우로서, 상술한 것과 같은 흑부유 대책용 누설 소자(55)를 구비한 경우에 발생할 수 있다.

- <264> 종래 기술에서는, 초기치의 0V에서 「흑」에 가까운 회색, 즉 매우 작은 전류치를 기입하고 있기 때문에, 평형 전위에 달하는 데 긴 시간이 걸린다. 예를 들면, 소정의 기입 시간 내에 TFT(31)의 임계치에 달하지 않은 것도 생각된다. 이 경우, TFT(31)는 데이터선(13)의 구동 시에 오프 상태로 되고, 표시 화상은 소위 흑색 붕괴의 상 태가 된다.

- 본 실시 형태에 따른 액티브 매트릭스형 표시 장치에서는, 데이터선(13)과 전원 전위 Vdd 사이에, 프리차지 소자(56)로서 PMOS 트랜지스터를 접속하고, 그 게이트 전위 Vg로서 기입 사이클의 최초에 펄스를 인가하도록 하고 있다. 이 펄스 인가에 의해서, 신호 입력선(16)의 전압이 TFT(31)의 임계치 이상으로 상승하고, 그 후는 기입전류 Iw와 데이터선 드라이버 회로 내부의 TFT의 동작과의 밸런스로 결정되는 평형 전위를 향하여 비교적 고속으로 수속하기 때문에, 올바른 휘도 데이터의 기입이 고속으로 가능하게 된다.

- <266> 이와 같이, 신호 입력선(16)과 플러스 전원 Vdd 사이에 프리차지 소자(56)를 접속하는 구성은 데이터선 드라이 버 회로로서 도 4와 같은 전류 기입형의 드라이버 회로를 이용한 도 1의 구성의 액티브 매트릭스형 표시 장치에 의 적용에 한정되는 것은 아니고, 다른 전류 기입형의 드라이버 회로를 이용한 구성의 액티브 매트릭스형 표시 장치에도 마찬가지로 적용 가능하다. 또, 프리차지 소자(56)로서는, TFT로 구성하거나, TFT 프로세스와는 별개 로 외부 부품으로 구성하는 것도 가능하다.

- <267> 또, 상기 각 실시 형태에서는, 전류 기입형 화소 회로(11)의 표시 소자로서, 유기 EL 소자를 이용한 액티브 매트릭스형 유기 EL 표시 장치에 적용한 경우를 예로 들어 설명하였지만, 본 발명은 이것에 한정되는 것은 아니고, 흐르는 전류에 의해서 휘도가 변화하는 전기 광학 소자를 표시 소자로서 이용한 액티브 매트릭스형 표시 장치 전반에 적용할 수 있는 것이다.

- <268> 또한, 상기 각 실시 형태에서 이용하는 각 회로예에 있어서는, 기입 전류를 전압으로 변환하는 변환부로서의 제 1 전계 효과 트랜지스터와, 캐패시터(유지부)에서 유지한 전압을 구동 전류로 변환하여 데이터선을 구동하는 구 동부로서의 제2 전계 효과 트랜지스터를 각각 별개의 트랜지스터로 구성하는 것으로 하였지만, 동일한 트랜지스 터로 구성하여, 전류-전압의 변환 동작과 그에 기초하는 데이터선의 구동 동작을 시분할적으로 행하도록 구성하 는 것도 가능하다. 이것에 따르면, 원리적으로, 양 동작 사이에 변동이 생기지 않는다.

#### 산업상 이용 가능성

<269> 이상 설명한 바와 같이, 본 발명에 따르면, 전류 기입형의 화소 회로를 이용한 액티브 매트릭스형 표시 장치에 있어서, 화상 정보를 구동 회로에서 전압의 형태로 일단 유지한 후, 전류의 형태로 변환하여 복수개의 데이터선의 각각에(일괄하여 동시에) 제공함으로써 각 화소 회로에 대한 화상 정보의 기입 구동을 행하도록 하였다. 이에 따라, 각 화소 회로에의 화상 정보의 기입을 선순차로써 행할 수 있어, 표시 패널과 외부의 데이터 드라이버 회로와의 접속 점수를 삭감하면서 정상적인 전류 기입 동작을 실현하는 것이 가능해진다.

## 도면의 간단한 설명

- <47> 도 1은 본 발명의 제1 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

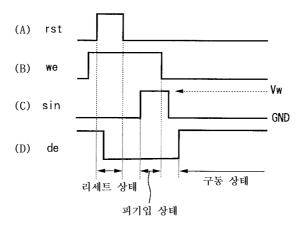

- <48> 도 2의 (A)~도 2의 (K)는 제1 실시 형태에 따른 액티브 매트릭스형 표시 장치의 회로 동작을 설명하기 위한 타이밍차트.

- <49> 도 3은 유기 EL 소자의 구성의 일례를 나타내는 단면 구조도.

- <50> 도 4는 데이터선 드라이버 회로의 제1 회로예를 도시하는 회로도.

- <51> 도 5의 (A)~도 5의 (D)는 제1 회로예에 따른 데이터선 드라이버 회로의 회로 동작의 타이밍차트.

- <52> 도 6은 데이터선 드라이버 회로의 제2 회로예를 도시하는 회로도.

- <53> 도 7은 제2 회로예의 변형예를 도시하는 회로도.

- <54> 도 8은 본 발명의 제2 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <55> 도 9 (A)~도 9 (J)는 제2 실시 형태에 따른 액티브 매트릭스형 표시 장치의 회로 동작을 설명하기 위한 타이밍 차트.

- <56> 도 10은 데이터선 드라이버 회로의 제3 회로예를 도시하는 회로도.

- <57> 도 11은 제2 실시 형태의 변형예에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <58> 도 12는 제2 실시 형태의 다른 변형예에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <59> 도 13은 제2 실시 형태의 또 다른 변형예에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <60> 도 14는 데이터선 드라이버 회로의 제4 회로예를 도시하는 회로도.

- <61> 도 15의 (A)~도 15의 (C)는 제4 회로예에 따른 데이터선 드라이버 회로의 회로 동작의 타이밍차트.

- <62> 도 16은 제4 회로예의 변형예를 도시하는 회로도.

- <63> 도 17은 데이터선 드라이버 회로의 제5 회로예를 도시하는 회로도.

- <64> 도 18은 본 발명의 제3 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <65> 도 19는 데이터선 드라이버 회로의 제6 회로예를 도시하는 회로도.

- <66> 도 20의 (A)~도 20의 (G)는 제6 회로예에 따른 데이터선 드라이버 회로의 회로 동작의 타이밍차트.

- <67> 도 21은 데이터선 드라이버 회로의 제7 회로예를 도시하는 회로도.

- <68> 도 22는 데이터선 드라이버 회로의 제8 회로예를 도시하는 회로도.

- <69> 도 23의 (A)~도 23의 (D)는 제8 회로예에 따른 데이터선 드라이버 회로의 회로 동작의 타이밍차트.

- <70> 도 24는 제8 회로예의 변형예를 도시하는 회로도.

- <71> 도 25는 제8 회로예의 또 다른 변형예를 도시하는 회로도.

- <72> 도 26의 (A)~도 26의 (D)는 제8 회로예의 또 다른 변형예에 따른 데이터선 드라이버 회로의 회로 동작의 타이 밍차트.

- <73> 도 27은 본 발명의 제4 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <74> 도 28의 (A)~도 28의 (C)는 제4 실시 형태에 따른 액티브 매트릭스형 표시 장치의 동작 설명도.

- <75> 도 29는 본 발명의 제5 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <76> 도 30은 제5 실시 형태에 따른 액티브 매트릭스형 표시 장치에서의 누설 소자(LK)의 효과를 설명하는 도면.

- <77> 도 31은 본 발명의 제6 실시 형태에 따른 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <78> 도 32는 제6 실시 형태에 따른 액티브 매트릭스형 표시 장치에서의 프리차지 소자(PC)의 효과를 설명하는 도면.

- <79> 도 33은 종래예에 따른 화소 회로의 회로 구성을 도시하는 회로도.

- <80> 도 34는 선순차 구동 방식의 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <81> 도 35는 종래예에 따른 전류 기입형 화소 회로의 회로 구성을 도시하는 회로도.

- <82> 도 36의 (A)~도 36의 (C)는 종래예에 따른 전류 기입형 화소 회로의 회로 동작을 설명하기 위한 타이밍차트.

- <83> 도 37은 점순차 구동 방식의 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <84> 도 38의 (A)~도 38의 (F)는 점순차 구동 방식의 액티브 매트릭스형 표시 장치의 회로 동작을 설명하기 위한 타이밍차트.

- <85> 도 39는 전류 기입형 화소 회로를 채용한 경우의 액티브 매트릭스형 표시 장치의 구성예를 도시하는 블록도.

- <86> 이하, 본 발명의 실시 형태에 대하여 도면을 참조하여 상세히 설명한다.

## 도면20

## 도면23

| (A) | 제1 데이터선<br>드라이버얼의 동작 | -H (1 주사선 수기)<br>★ 1<br>리세트 상태 | 기입 상태  | (1 수사선 수기)<br>             | 리세트 상태                  | 피기입 상태 |

|-----|----------------------|--------------------------------|--------|----------------------------|-------------------------|--------|

| (A) | 세1 메이터인<br>드라이버열의 동작 | 리세트 상태                         | 피기입 상태 | 구동 상태                      | 리세트 상태                  | 피기입 상  |

| (B) | 제2 데이터선<br>드라이버열의 동작 |                                | 리세트 상태 | 리세트 상태 의기입 상태 구동 상태 리세트 상태 | 구동 상태                   | 리세트 상  |

| (C) | 제3 데이터선<br>드라이버열의 동작 |                                |        | 리세트 상태                     | 리세트 상태 📗 피기입 상태 📗 구동 상태 | 구동 상1  |

| 专利名称(译)        | 有源矩阵型显示装置和有源矩阵型有机电致发光显示装置                                                                                                                                    |                            |             |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------|--|--|

| 公开(公告)号        | KR100830772B1                                                                                                                                                | 公开(公告)日                    | 2008-05-20  |  |  |

| 申请号            | KR1020027008789                                                                                                                                              | 申请日                        | 2001-11-07  |  |  |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                         |                            |             |  |  |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                         |                            |             |  |  |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                                                                         |                            |             |  |  |

| [标]发明人         | YUMOTO AKIRA<br>유모또아끼라                                                                                                                                       |                            |             |  |  |

| 发明人            | 유모또,아끼라                                                                                                                                                      |                            |             |  |  |

| IPC分类号         | G09G3/30 H01L51/50 G09F9/30 C                                                                                                                                | G09G3/20 G09G3/32 G09G3/36 | 3 H01L27/32 |  |  |

| CPC分类号         | G09G3/3241 G09G3/3283 G09G3/3685 G09G2300/0842 G09G2310/0221 G09G2310/0248 G09G3/30 G09G3/3225 G09G3/3233 G09G3/3291 G09G2300/0426 G09G2310/0272 G09G2310/08 |                            |             |  |  |

| 代理人(译)         | Jangsugil                                                                                                                                                    |                            |             |  |  |

| 优先权            | 2000338688 2000-11-07 JP<br>2001231807 2001-07-31 JP<br>2001320936 2001-10-18 JP<br>2001339772 2001-11-05 JP                                                 |                            |             |  |  |

| 其他公开文献         | KR1020020069241A                                                                                                                                             |                            |             |  |  |

| 外部链接           | Espacenet                                                                                                                                                    |                            |             |  |  |

|                |                                                                                                                                                              |                            |             |  |  |

#### 摘要(译)

当使用电流写入像素电路时,必须按行顺序写入像素。其中电流写入像素电路(11)以矩阵形式排列的有源矩阵显示器包括由m电流驱动器电路(CD)(15-1至15-m)组成的数据线驱动器电路(15),如此提供。对应于数据线(13-1至13-m)。数据线驱动电路(15)保持临时图像数据(在该工作示例中,亮度数据),并以数据形式将数据提供给数据线(13-1至13-m)。因此,执行像素电路(11)的图像信息写入驱动。©KIPO&WIPO 2007