(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0077003

(43) 공개일자 2010년07월06일

(51) Int. Cl.

G09G 3/30 (2006.01)

(21) 출원번호 10-2010-7009672

(22) 출원일자(국제출원일자) 2008년10월29일

심사청구일자 없음

(85) 번역문제출일자 2010년04월30일

(86) 국제출원번호 PCT/GB2008/051007

(87) 국제공개번호 WO 2009/056877

국제공개일자 2009년05월07일

(30) 우선권주장

0721567.6 2007년11월02일 영국(GB)

0723859.5 2007년12월06일 영국(GB)

(71) 출원인

캡브리지 디스플레이 테크놀로지 리미티드

영국 캡브리지 캡브리지셔 씨비23 6디더블유 캠버

른 비지니스 파크 캠버른 빌딩 2020

(72) 발명자

란코브 알렉산드라

영국 씨비23 6디더블유 캠버른 캡브리지셔 캠버른

비즈니스 파크 빌딩 2020

스미스 유안 크리스토퍼

영국 씨비4 5이에이치 롱스탄頓 캠프리지셔 램프

톤 드리프트 10

(74) 대리인

김창세, 김원준

전체 청구항 수 : 총 26 항

(54) 액티브 매트릭스 광전자 디바이스, 액티브 매트릭스 픽셀 회로 구동 방법, 플로팅 게이트 유기 박막 트랜지스터 및 픽셀 회로

### (57) 요 약

본 발명은 액티브 매트릭스 광전자 디바이스용 픽셀 드라이버 회로에 관한 것으로, 보다 구체적으로는 OLED(유기 발광 다이오드) 디스플레이에 관한 것이다. 본 발명은 복수의 액티브 매트릭스 픽셀을 구비하는 액티브 매트릭스 광전자 디바이스를 제공하며, 각각의 상기 픽셀은 상기 픽셀을 구동시키는 박막 트랜지스터(TFT) 및 픽셀값을 저장하는 픽셀 커패시터를 포함하는 픽셀 회로를 포함하고, 상기 TFT는 플로팅 게이트를 구비하는 TFT를 포함한다.

대 표 도 - 도3a

## 특허청구의 범위

### 청구항 1

복수의 액티브 매트릭스 픽셀을 구비하는 액티브 매트릭스 광전자 디바이스로서,

각각의 상기 픽셀은 상기 픽셀을 구동시키는 박막 트랜지스터(TFT) 및 픽셀값을 저장하는 픽셀 커패시터를 포함하는 픽셀 회로를 포함하되,

상기 TFT는 플로팅 게이트를 구비하는 TFT를 포함하는

액티브 매트릭스 광전자 디바이스.

### 청구항 2

제 1 항에 있어서,

플로팅 게이트를 구비하는 상기 TFT는 상기 TFT의 게이트에 대한 하나 이상의 접속부를 구비하는 TFT를 포함하고,

상기 게이트 접속부는 상기 TFT의 상기 게이트로 용량 결합되는(capacitively coupled) 접속부만을 포함하는

액티브 매트릭스 광전자 디바이스.

### 청구항 3

제 2 항에 있어서,

상기 용량 결합된 게이트 접속부는 두 개의 플레이트를 구비하는 게이트 접속 커패시터를 포함하고,

상기 TFT는 소스-드레인 금속 층을 포함하고,

상기 TFT의 상기 게이트로 용량 결합된 접속부는 상기 소스-드레인 금속 층 내의 패터닝된 접속부를 포함하고,

상기 소스-드레인 금속 층 내의 상기 패터닝된 접속부는 상기 게이트 접속 커패시터의 상기 플레이트 중 하나를 포함하며,

상기 TFT는 상기 게이트 접속 커패시터의 상기 플레이트 중 다른 하나를 포함하는 게이트 금속 층을 더 포함하는

액티브 매트릭스 광전자 디바이스.

### 청구항 4

제 1 항 또는 제 2 항에 있어서,

상기 플로팅 게이트는 상기 TFT와 접적되는

액티브 매트릭스 광전자 디바이스.

### 청구항 5

제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 플로팅 게이트는 연관된 플로팅 게이트 커패시턴스를 가지고,

상기 픽셀 커패시터는 상기 플로팅 게이트 커패시턴스를 포함하는

액티브 매트릭스 광전자 디바이스.

#### 청구항 6

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 디바이스는 유기 발광 다이오드(OLED) 디스플레이를 포함하고,

상기 픽셀 회로는 상기 플로팅 게이트 TFT에 의해 구동되는 OLED를 포함하는

액티브 매트릭스 광전자 디바이스.

#### 청구항 7

제 6 항에 있어서,

상기 픽셀 회로는 전압 프로그래밍되는 픽셀 회로를 포함하고,

상기 픽셀값은 상기 플로팅 게이트 TFT의 문턱 전압을 오프셋하기 위한 문턱 오프셋 전압값을 포함하는

액티브 매트릭스 광전자 디바이스.

#### 청구항 8

제 7 항에 있어서,

상기 플로팅 게이트 TFT는 두 개의 플로팅 게이트 접속부를 구비하고,

상기 전압 프로그래밍되는 픽셀 회로는, 상기 문턱 오프셋 전압값을 조정하기 위한 제 1 플로팅 게이트 접속부 및 상기 픽셀에 대한 프로그래밍 전압을 저장하기 위한 제 2 플로팅 게이트 접속부를 사용하도록 구성되는

액티브 매트릭스 광전자 디바이스.

#### 청구항 9

제 8 항에 있어서,

상기 픽셀 회로는, 상기 문턱 전압 오프셋과 상기 프로그래밍 전압을 제공하는 동작이 상기 TFT의 상기 플로팅 게이트와 소스 또는 드레인 단자 사이의 진성 디바이스 커패시턴스 상에 프로그래밍 전압을 저장하도록 구성되는

액티브 매트릭스 광전자 디바이스.

#### 청구항 10

제 7 항 내지 제 9 항 중 어느 한 항에 있어서,

상기 픽셀 회로는 상기 픽셀 내에 광학적 피드백을 제공하도록 상기 TFT의 플로팅 게이트 접속부로 연결된 광다이오드를 포함하는

액티브 매트릭스 광전자 디바이스.

#### 청구항 11

제 6 항 내지 제 10 항 중 어느 한 항에 있어서,

상기 픽셀 회로를 제어하도록 두 개의 사이클을 갖는 제어 회로를 더 포함하되,

제 1 사이클에서는 상기 OLED가 오프되도록 제어되고 상기 문턱 오프셋 전압값이 상기 접속 플로팅 게이트 커패

시터 상에 저장되고,

제 2 사이클에서는 상기 OLED의 밝기가 상기 문턱 오프셋 전압값에 의해 조정되는 프로그래밍 전압에 의해 설정되는

액티브 매트릭스 광전자 디바이스.

## 청구항 12

제 6 항에 있어서,

상기 픽셀 회로는 전류 프로그래밍되는 픽셀 회로를 포함하고,

상기 픽셀값은 상기 픽셀 회로에 인가된 프로그래밍 전류에 실질적으로 비례하는 상기 OLED를 통과하는 구동 전류에 상응하는 게이트-소스 전압값을 포함하는

액티브 매트릭스 광전자 디바이스.

## 청구항 13

제 12 항에 있어서,

상기 TFT는 제 1 플로팅 게이트 접속부 및 제 2 플로팅 게이트 접속부를 포함하는 두 개의 플로팅 게이트 접속부들을 구비하고,

상기 전류 프로그래밍되는 픽셀 회로는, 상기 플로팅 게이트 접속부들 중 하나의 플로팅 게이트 접속부가 상기 TFT의 유효 문턱 전압을 변조시키는 전압을 저장하는 커파시터에 대한 접속부를 포함하도록 구성되는

액티브 매트릭스 광전자 디바이스.

## 청구항 14

제 13 항에 있어서,

상기 제 1 플로팅 게이트 접속부는 상기 플로팅 게이트 TFT의 드레인 접속부로 연결되는

액티브 매트릭스 광전자 디바이스.

## 청구항 15

제 14 항에 있어서,

상기 제 1 플로팅 게이트 접속부는 상기 픽셀 회로가 상기 프로그래밍 회로에 의한 프로그래밍을 위해 선택될 수 있도록 적어도 하나의 선택 TFT를 통해 상기 TFT의 상기 드레인 접속부로 연결되는

액티브 매트릭스 광전자 디바이스.

## 청구항 16

제 13 항 내지 제 15 항 중 어느 한 항에 있어서,

상기 픽셀 회로는 상기 제 2 플로팅 게이트 접속부와 플로팅 게이트 TFT의 드레인 접속부 사이에 연결된 적어도 하나의 선택 TFT를 포함하는

액티브 매트릭스 광전자 디바이스.

#### 청구항 17

제 13 항 내지 제 15 항 중 어느 한 항에 있어서,

상기 픽셀 회로는 상기 제 1 플로팅 게이트 접속부와 상기 픽셀 회로의 바이어스 전압 접속부 사이에 연결된 적어도 하나의 선택 TFT를 포함하는

액티브 매트릭스 광전자 디바이스.

#### 청구항 18

제 13 항 내지 제 17 항 중 어느 한 항에 있어서,

상기 픽셀 회로는 상기 프로그래밍 전류를 상기 픽셀 회로에 선택적으로 제공하기 위해서, 상기 제 2 플로팅 게이트 접속부와 전류 데이터 라인 사이에 연결된 적어도 하나의 선택 TFT를 포함하는

액티브 매트릭스 광전자 디바이스.

#### 청구항 19

제 13 항 내지 제 18 항 중 어느 한 항에 있어서,

상기 픽셀 구동 회로의 프로그래밍 동안, 상기 OLED로부터의 발광을 불가능하게 하기 위해 상기 플로팅 게이트 TFT와 상기 OLED 사이에 연결된 디스에이블(disable) TFT를 더 포함하는

액티브 매트릭스 광전자 디바이스.

#### 청구항 20

제 1 항 내지 제 19 항 중 어느 한 항에 있어서,

상기 플로팅 게이트 TFT는 두 개의 플로팅 게이트 접속부를 구비하고,

상기 픽셀 회로는 상기 플로팅 게이트 TFT의 유효 문턱 전압 제어를 위해 상기 입력 단자 중 하나를 사용하도록 구성되는

액티브 매트릭스 광전자 디바이스.

#### 청구항 21

제 20 항에 있어서,

상기 픽셀 회로는 상기 플로팅 게이트 접속부 중 다른 하나를 이용하여 상기 액티브 매트릭스 픽셀의 프로그래밍을 가능케 하도록 구성되는

액티브 매트릭스 광전자 디바이스.

#### 청구항 22

제 20 항 또는 제 21 항에 있어서,

상기 픽셀 회로는 상기 플로팅 게이트 TFT를 입력 또는 출력 트랜지스터로서 포함하는 전류 미러 또는 전류 복

제기 회로를 포함하는

액티브 매트릭스 광전자 디바이스.

### 청구항 23

유기 전자발광(electroluminescent) 디스플레이의 액티브 매트릭스 픽셀 회로를 구동하는 방법으로서,

상기 픽셀 회로는 상기 픽셀을 구동시키는 박막 트랜지스터(TFT) 및 픽셀값을 저장하는 픽셀 커페시터를 포함하고, 상기 TFT는 플로팅 게이트를 구비하는 TFT를 포함하고, 상기 플로팅 게이트는 소스 커페시턴스에 연관된 플로팅 게이트를 구비하며,

상기 방법은 상기 플로팅 게이트 상의 전압을 소스 커페시터에 저장하도록 상기 픽셀 회로를 프로그래밍하는 단계를 포함하되,

상기 저장된 전압은 상기 유기 전자발광 디스플레이 소자의 밝기를 정의하는

액티브 매트릭스 픽셀 회로 구동 방법.

### 청구항 24

제 23 항에 있어서,

상기 플로팅 게이트 TFT는 두 개의 플로팅 게이트 접속부를 포함하고,

상기 방법은 상기 플로팅 게이트 접속부 중 하나를 이용하여 상기 유기 전자발광 디스플레이 소자의 상기 밝기를 프로그래밍하는 단계 및 상기 플로팅 게이트 접속부 중 다른 하나를 이용하여 상기 구동 TFT의 문턱 전압을 변조시키는 단계를 포함하는

액티브 매트릭스 픽셀 회로 구동 방법.

### 청구항 25

박막 트랜지스터의 플로팅 게이트에 용량 결합된 적어도 하나의 입력 단자를 포함하는 플로팅 게이트 유기 박막 트랜지스터(OTFT).

### 청구항 26

제 25 항의 플로팅 게이트 유기 박막 트랜지스터(OTFT)를 포함하는 픽셀 회로로서,

상기 회로에는 상기 OTFT의 드레인-소스 금속 층과 상기 OTFT의 게이트 금속 층 사이에 비아(via)가 존재하지 않는

픽셀 회로.

## 명세서

### 기술 분야

[0001]

본 발명은 액티브 매트릭스 광전자 디바이스용 픽셀 드라이버 회로에 관한 것으로, 보다 구체적으로는 OLED(유기 발광 다이오드) 디스플레이에 관한 것이다.

### 배경 기술

[0002]

특히 액티브 매트릭스 OLED 디스플레이에서 유용한 본 발명의 실시예가 기술되겠지만, 본 발명의 응용 및 실시예가 이러한 디스플레이로만 한정되는 것은 아니며, 실시예에서 액티브 매트릭스 센서 어레이뿐 아니라 그외의

유형의 액티브 매트릭스 디스플레이에도 사용될 수 있다.

[0003] 유기 발광 다이오드 디스플레이

[0004] 유기금속 LED를 포함하는 유기 발광 다이오드는, 중합체, 저분자 및 텐드리머를 포함하는 물질을 이용하여 제조될 수 있으며, 컬러의 범위는 사용된 물질에 의존한다. 중합체 기반의 유기 LED의 예가 WO 90/13148, WO 95/06400 및 WO 99/48160에 기술되었고, 텐드리머 기반 물질의 예가 WO 99/21935 및 WO 02/067343에 기술되었으며, 소위 저분자 기반의 디바이스의 예가 US 4,539,507에 기술되었다. 전형적인 OLED 디바이스는 두 개의 유기 물질 층을 포함하는데, 이들 중 하나의 층은 발광 중합체(LEP), 올리고머, 또는 발광 저분자 경량 물질(weight material)과 같은 발광 물질의 층이고, 이들 중 다른 하나의 층은 폴리사이온펜(polythiophene) 파생물 또는 폴리아닐린(polyaniline) 파생물과 같은 흰 수송 물질의 층이다.

[0005] 유기 LED는 단일 또는 멀티 컬러의 픽셀로 나누어진 디스플레이를 형성하도록 픽셀들의 매트릭스로 기판 상에 중착될 수 있다. 멀티 컬러 디스플레이에는 적색, 녹색 및 청색 발광 서브-픽셀을 사용하여 구성될 수 있다. 소위 액티브 매트릭스 디스플레이에는 각 픽셀과 연관된 메모리 소자(전형적으로 저장 커패시터) 및 트랜지스터를 구비한다(반면에 패시브 매트릭스 디스플레이에는 이러한 메모리 소자를 구비하지 않으며 대신 안정된 이미지의 느낌을 제공하도록 반복적으로 스캐닝된다). 중합체 및 저분자 액티브 매트릭스 디스플레이 드라이버의 예는 각각 WO 99/42983 및 EP 0,717,446A에서 찾을 수 있다.

[0006] OLED의 밝기가 디바이스를 통해 흐르는 전류에 의해 결정되기 때문에 OLED에 전류-프로그래밍되는 구동을 제공하는 것이 일반적이며, 이것이 전류가 생성하는 광자의 개수를 결정하는 반면, 단순한 전압-프로그래밍되는 구성에서 픽셀이 구동되었을 때의 밝기를 예측하는 것이 어려울 수 있다.

[0007] 전압-프로그래밍되는 액티브 매트릭스 픽셀 드라이버 회로와 관련된 종래의 배경 기술은, 1998년 캘리포니아 샌프란시스코에서 개최된 IEEE International Electron Device Meeting의 Dawson 외 다수에 의한 "The impact of the transient response of organic light emitting diodes on the design of active matrix OLED displays"의 페이지 875-878에서 찾아볼 수 있다. 전류 프로그래밍되는 액티브 매트릭스 픽셀 드라이버 회로와 관련된 종래의 배경 기술은, 2004년 12월 8-10일 개최된 제11회 국제 디스플레이 워크숍의 IDW '04 컨퍼런스 프로시딩 페이지 275-278의 Casio Computer Co Ltd 및 Kyushu University의 T. Shirasaki, T. Ozaki, T. Toyama, M. Takei, M. Kumagai, K. Sato, S. Shimoda, T. Tano, K. Yamamoto, K. Morimoto, J. Ogura 및 R. Hattori에 의한 초청 논문 AMD3/OLED5-1인 "Solution for Large-Area Full-color OLED Television-Light Emitting Polymer and a-Si TFT Technologies"에서 찾아볼 수 있다. 그외의 종래의 배경 기술은 US 5,982,462 및 JP2003/271095에서 찾아볼 수 있다.

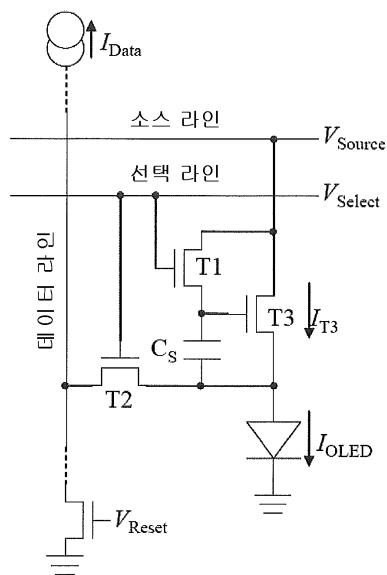

[0008] IDW '04 논문으로부터 차용한 도 1a 및 1b는 예시적인 전류 프로그래밍되는 액티브 매트릭스 픽셀 회로 및 상응하는 타이밍도를 도시한다. 동작시에, 제 1 스테이지에서 데이터 라인은 Cs 및 OLED의 접합 커패시턴스를 방전하도록 간단히 접지된다(Vselect, Vreset high; Vsource low). 그 다음 상응하는 전류가 T3를 T3를 통해 흐르고 Cs가 이러한 전류에 대해 요구되는 게이트 전압을 저장하도록 데이터 싱크 Idata가 인가된다(전류가 OLED를 통해 흐르지 않도록 Vsource는 낮고, T3이 다이오드에 접속되도록 T1은 온 상태이다). 마지막으로 프로그래밍되는 전류(Cs 상에 저장된 게이트 전압에 의해 결정됨)가 OLED를 통해 흐르도록 ( $I_{OLED}$ ) 선택 라인이 디-어써트(de-assert)되고 Vsource는 HIGH 상태가 된다.

[0009] 그러나, 개선된 픽셀 드라이버 회로에 대한 필요성이 존재한다.

## 발명의 내용

### 과제의 해결 수단

[0010] 따라서 본 발명의 제 1 측면에 따르면 복수의 액티브 매트릭스 픽셀을 구비하는 액티브 매트릭스 광전자 디바이스가 제공되며, 각각의 상기 픽셀은 상기 픽셀을 구동시키는 박막 트랜지스터(TFT) 및 픽셀값을 저장하는 픽셀 커패시터를 포함하는 픽셀 회로를 포함하고, 상기 TFT는 플로팅 게이트를 구비하는 TFT를 포함한다.

[0011] 실시예에서, 플로팅 게이트 TFT는 입력 커패시터를 통해 연결되는 플로팅 게이트에 대한 하나 이상의 용량 결합

된 입력 단자를 구비한다. 실시예에서, 입력 커패시터를 통과하는 것 외에 플로팅 게이트에 대한 다른 접속부는 존재하지 않는다(즉, 직접 입력단 또는 저항성 입력단이 존재하지 않음). 플로팅 게이트 및 연관된 게이트 접속부(들)는 TFT 구조 내에 접적될 수 있거나, 또는 플로팅 게이트가 픽셀 회로의 나머지 부분으로부터 실질적으로 저항성으로 분리된 TFT에 대한 게이트 접속부를 포함할 수 있다. 즉, 픽셀 회로의 나머지 부분에 대한 하나 이상의 용량 접속부(들)만을 구비한다("비-접적(non-integrated)"). 따라서 비-접적 디바이스에서, 입력 커패시터는 플로팅 게이트 TFT에 대해 개별적으로 패터닝되는 디바이스일 수 있다.

[0012] "비-접적" 구성은 이것이 게이트 금속 층과 드레인-소스 금속 층 사이의 비아를 필요로 하지 않는다는 점에서 특히 유용하다. 이는 결합 커패시터의 하나의 플레이트가 소스-드레인 층에서 패터닝될 수 있기 때문이다. 따라서 비-접적 입력 커패시터를 구비하는 플로팅 게이트 디바이스가 사용되는 실시예에서, 이러한 플로팅 게이트 (FG) 디바이스의 사용은, 전형적으로 구동 TFT의 게이트 층과 제어 또는 스위칭 TFT의 드레인-소스 층 사이에 있는 추가적인 비아에 대한 필요성을 없앤다.

[0013] 특히 바람직한 일부 실시예에서, 구동 TFT는 각각이 디바이스의 FG에 대한 연관된 용량 접속부를 구비하는 두 개의 입력단을 구비한다. 이들 입력 커패시턴스 중 하나는 구동 TFT의 문턱 전압을 변조시키는 전압을 저장하도록 이용될 수 있는 반면 다른 하나는 구동 TFT에 의해 구동되는 OLED 픽셀의 밝기를 제어하기 위해 OLED 디스플레이에서 프로그래밍 입력으로서 사용될 수 있다.

[0014] 두 개의 용량 결합된 입력 단자를 구비하는 실시예에서, 제 2 입력 단자에 의해 입수되는 추가적인 유연성은 개선된 동작 효율 및/또는 회로의 동작에 대한 보다 우수한 제어 능력을 갖는 픽셀 회로의 제조를 용이하게 한다. 따라서 실시예에서, 입력 단자들 중 하나와 그것의 연관된 커패시턴스는 노화, 온도 및 위치적 불균일성 중 하나 이상에 대한 픽셀 밝기 및/또는 색상의 보상에 이용될 수 있다. 입력 단자는 픽셀 밝기를 설정하도록 픽셀 회로를 프로그래밍하고/하거나 픽셀 회로의 하나 이상의 파라미터를 조정하는 데에 사용될 수 있다(여기에서 밝기란 멀티 컬러 디스플레이의 색상 서브-픽셀의 밝기를 포함한다).

[0015] 또 다른 실시예에서, 추가적인 용량 결합된 입력 단자는 예를 들어 전류 미러 기반의 픽셀 회로 내의 디바이스 미스매칭으로 인한 변화에 대한 보상을 위해, 디바이스들 간의 미스매칭에 대한 보상을 제공하도록 사용될 수 있다.

[0016] 또 다른 픽셀 회로에서, FG 박막 트랜지스터의 유효 문턱 전압이 0으로 감소되거나 또는 FG 트랜지스터의 하나(이상의) 용량 결합된 입력 단자에 전압을 인가함으로써 인버팅될 수 있다. 이것은 주어진 드레인-소스 전류에 대해 요구되는 입력 전압을 감소시킬 수 있고, 그에 따라 요구되는 드레인-소스 전압(Vds)을 감소시키며, 이는 특히 디바이스가 포화 상태에서 동작시에 바람직하다. 따라서 이것은 전력 요구량을 감소시키고 동작 효율성을 증가시킨다.

[0017] 또한, 유효 문턱 전압을 변화시키는 능력은, 인접하는 트랜지스터들 사이에서의 미스매칭이 정정되어야만 하는, 조정 및 프로그래밍을 필요로 하는 회로에서 유리하다.

[0018] 전술된 바와 같이 바람직한 실시예에서, 액티브 매트릭스 광전자 디바이스는 OLED 디바이스를 포함하고, 픽셀 회로는 TFT에 의해 구동되는 OLED를 포함한다. 또 다른 실시예에서, 액티브 매트릭스 디바이스는 액티브 매트릭스 센서를 포함할 수 있거나, 또는 액티브 매트릭스 디스플레이 디바이스와 조합된 액티브 매트릭스 센서를 포함할 수 있다.

[0019] 일부 실시예에서, 픽셀 회로는 전압 프로그래밍된 픽셀 회로를 포함하며, 즉 픽셀 회로에 인가된 프로그래밍 전압은 픽셀 밝기(또는 색상)를 제어한다. 입력 커패시터 상에 저장된 픽셀값은 TFT의 문턱 전압을 오프셋하도록 문턱 오프셋 전압값을 포함할 수 있다. 구동 TFT가 두 개의 용량 결합된 입력 단자를 구비하는 경우, 입력 단자는 픽셀에 대한 프로그래밍 전압을 설정하도록 사용될 수 있다. 일부 실시예에서, 픽셀 회로는 예를 들어 FG 구동 TFT의 입력 단자에 연결된 광다이오드를 포함하는 광-피드백을 포함할 수 있다. 실시예에서, 이러한 전압 프로그래밍되는 픽셀을 위한 제어 회로는 두 개의 사이클을 갖는데, 제 1 사이클에서는 문턱 오프셋 전압값이 저장되고, 제 2 사이클에서는 OLED의 밝기가 문턱 오프셋 전압값에 의해 조정 또는 변조되는 프로그래밍 전압에 의해 설정된다.

[0020] 다른 실시예에서, 픽셀 회로는 전류 프로그래밍되는 픽셀 회로를 포함하고, 입력 커패시터 상에 저장된 전압은 픽셀 회로에 대한 전류 데이터 라인으로 인가되는 전류에 의해 프로그래밍되는 전압을 포함한다. 실시예에서, FG TFT의 FG로 용량 결합되는 제 2 입력 단자는 TFT의 문턱 전압을 변조시키는 데에 사용될 수 있다. 그러나, 당업자는 두 개의 개별적인 용량 결합된 입력 단자가 제공되는 경우에서라도, TFT 구조 내의 공통 플로팅 게이

트가 두 접속부 모두에 대해 사용될 수 있음을 이해할 것이다(커패시터의 하나의 플레이트는 공통 플레이트이고, 상반되는 플레이트들에 대해서 각 입력은 다른 플레이트로 접속된다).

[0021] 구동 TFT가 구동 TFT의 FG에 용량 결합된 두 개의 입력 단자를 구비하는 전류 프로그래밍되는 픽셀 회로의 실시 예에서, 제 1 입력 단자는 하나 이상의 스위칭 또는 선택 트랜지스터를 통해서 직접 또는 간접적으로 구동 TFT의 소스(또는 드레인) 접속부로 연결될 수 있다. 이러한 선택 트랜지스터는 픽셀 회로의 전류 프로그래밍을 가능케 하도록 제어(스위칭 온)될 수 있다. 실시예에서, 하나의 선택 트랜지스터는 프로그래밍을 위해 제공될 수 있고, 다른 선택 트랜지스터는 구동 TFT를 다이오드 접속시키도록 제공될 수 있으며, 또는 두 기능 모두가 단일 트랜지스터에 의해 구현될 수도 있다.

[0022] 실시예에서, 구동 TFT의 다른 용량 결합된 입력 단자가 픽셀 선택 트랜지스터로 연결될 수도 있다(전술된 선택 트랜지스터들 중 하나, 또는 다른 선택 트랜지스터). 이러한 선택 트랜지스터는 구동 TFT의 구동 TFT의 용량 결합된 제 2 입력 단자와 드레인 접속부 사이에 연결될 수 있거나, 또는 예를 들어 구동 TFT의 문턱 전압을 조정하도록 바이어스 전압의 인가를 가능케 하기 위해 픽셀 회로에 대한 바이어스 전압 접속부로 연결될 수도 있다(예를 들어,  $V_t$ 를 증가시켜 이것이 프로그래밍 시간 동안에 OLED를 역 바이어싱하도록 함).

[0023] 전류 프로그래밍되는 픽셀 회로의 실시예는, 픽셀 회로에 프로그래밍 전류를 선택적으로 제공하고 프로그래밍 전류에 상응하는 게이트 전압이 플로팅 게이트 접속부와 연관된 입력 커패시터 상에 저장되는 것을 가능케 하도록, 선택 트랜지스터(전술된 트랜지스터들 중 하나 또는 추가적인 선택 트랜지스터)에 의해서 구동 TFT의 용량 결합된 입력 단자들 중 하나에 선택적으로 접속될 수 있는 전류 데이터 라인을 포함한다. 회로의 실시예는 프로그래밍 동안 OLED로부터의 발광을 불가능하게 하기 위해 구동 TFT와 OLED 사이에 연결된 디스에이블(disable) 트랜지스터를 포함할 수도 있다.

[0024] 또 다른 실시예에서, 픽셀 회로는 전류 미러 또는 다른 전류 복제기 회로를 포함하며, 이러한 경우에 구동 TFT가 전류 미러 또는 전류 복제기의 입력 또는 출력 트랜지스터를 포함할 수 있다. 따라서 실시예에서, 전류 미러 또는 전류 복제기 회로 내의 하나 이상의 트랜지스터는 예를 들어 디바이스의 특징을 서로 더욱 가깝게 매칭하도록 조정하기 위해 사용되는 일부 입력 단자를 구비하는 하나 이상의 FG 디바이스를 구비할 수 있다.

[0025] 관련된 측면에서, 본 발명은 특히 전술된 바와 같은 유기 전자발광(electroluminescent) 디스플레이의 액티브 매트릭스 픽셀 회로를 구동하는 방법을 제공하는데, 픽셀 회로는 픽셀을 구동시키는 박막 트랜지스터(TFT) 및 픽셀값을 저장하는 픽셀 커패시터를 포함하고, TFT는 플로팅 게이트를 구비하는 TFT를 포함하고, 플로팅 게이트는 소스 커패시턴스에 대한 연관된 플로팅 게이트를 구비하며, 상기 방법은 상기 플로팅 게이트 상의 전압을 소스 커패시터 상에 저장하도록 픽셀 회로를 프로그래밍하는 단계를 포함하되, 저장된 전압은 상기 유기 전자발광 디스플레이 소자의 밝기를 정의한다.

[0026] 전술된 바와 같이, 플로팅 게이트 TFT는 바람직하게는 하나 이상의 입력 커패시터를 통해 연결되는, 플로팅 게이트에 대한 하나 이상의 용량 결합되는 입력 단자를 구비한다. 이들은 플로팅 게이트 TFT와 접속될 수 있거나 또는 이러한 입력 커패시터를 통과하는 것 외에 플로팅 게이트에 대한 다른 접속부를 갖지 않고 플로팅 게이트 TFT에 대해 개별적으로 패터닝될 수 있다. 따라서, 픽셀 커패시터는 이러한 입력 커패시터를 포함할 수 있다.

[0027] 바람직한 실시예에서, 이 방법은 입력 접속부들 중 하나로 연결된 입력 커패시터 상에서 픽셀 밝기를 정의하는 전압을 설정하는 단계와, 제 2 입력 접속부로 연결된 입력 커패시터 상에서 TFT의 문턱 전압을 변조시키는 전압을 저장하는 단계를 포함한다. 입력 커패시터들은 접속 또는 비-접속될 수 있다.

[0028] 또 다른 실시예에서, 본 발명은 박막 트랜지스터의 플로팅 게이트로 용량 결합되는 적어도 하나의 입력 단자를 포함하는 플로팅 게이트 유기 박막 트랜지스터를 제공한다. 일 실시예에서, 입력 단자는 접속 플로팅 게이트 커패시터에 대한 플로팅 게이트 접속부를 포함한다.

[0029] 당업자는 전술된 본 발명의 측면들 및 실시예들에서 플로팅 게이트 트랜지스터가 n-채널 또는 p-채널일 수 있음을 이해할 것이다.

### 도면의 간단한 설명

[0030] 도 1a 내지 1g는 종래 기술에 따른 픽셀 회로의 예시와 상응하는 타이밍도, 및 액티브 매트릭스 픽셀 드라이버 회로의 추가적인 예시를 도시한 도면,

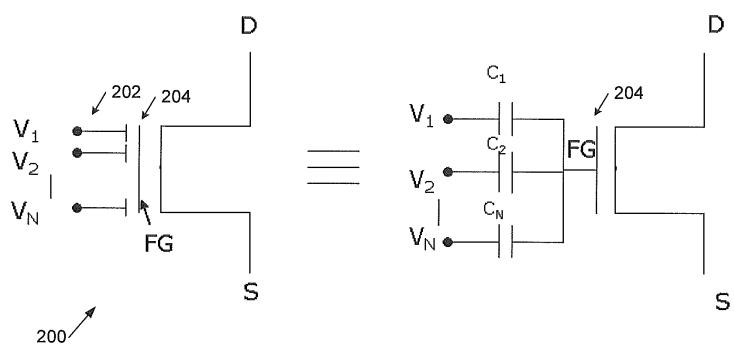

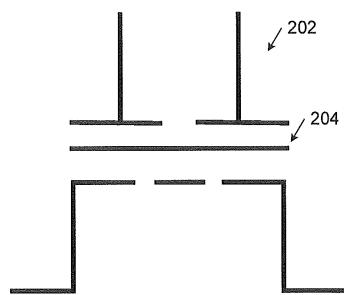

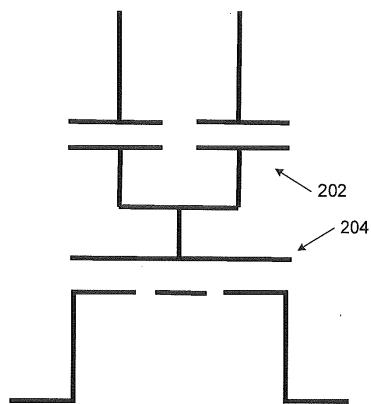

도 2는 플로팅 게이트 TFT(박막 트랜지스터)의 개략도,

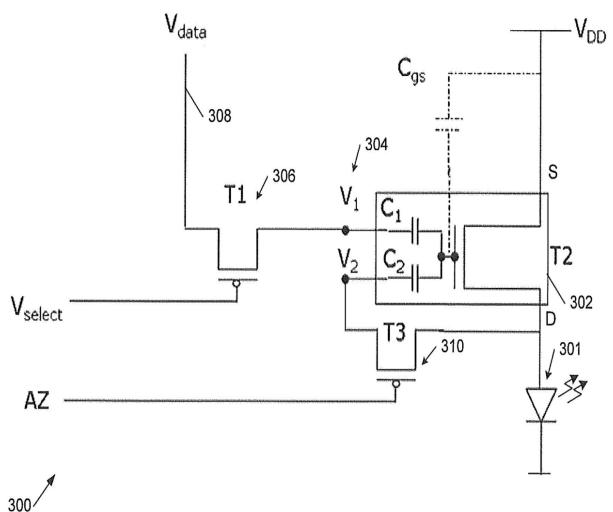

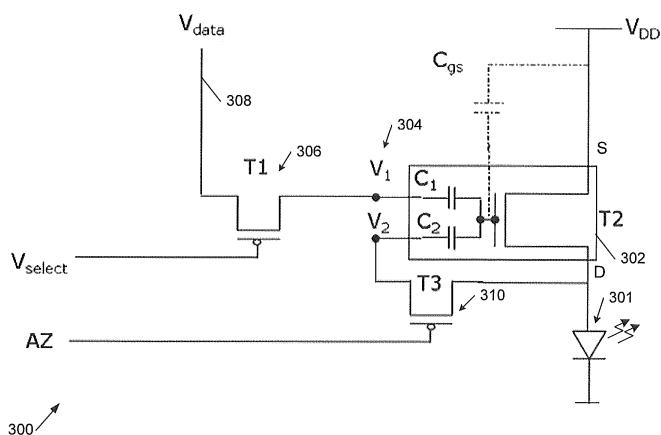

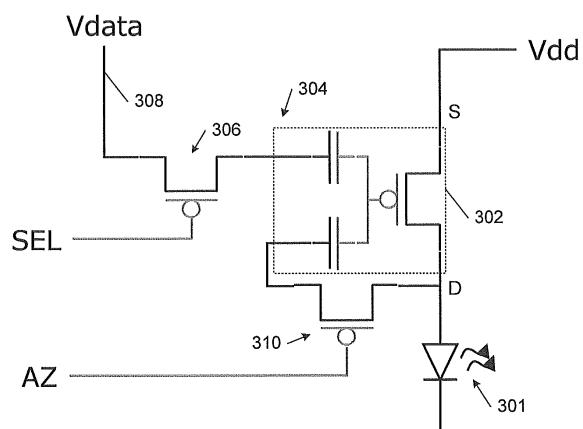

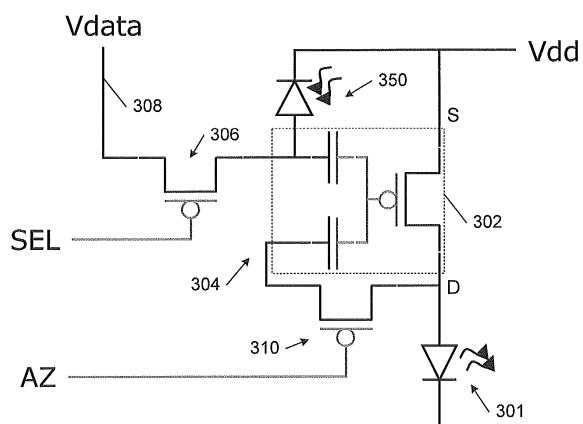

도 3a 내지 3c는 각각 본 발명의 측면의 실시예에 따른 전압 프로그래밍되는 픽셀 회로의 예시를 도시한 도면,

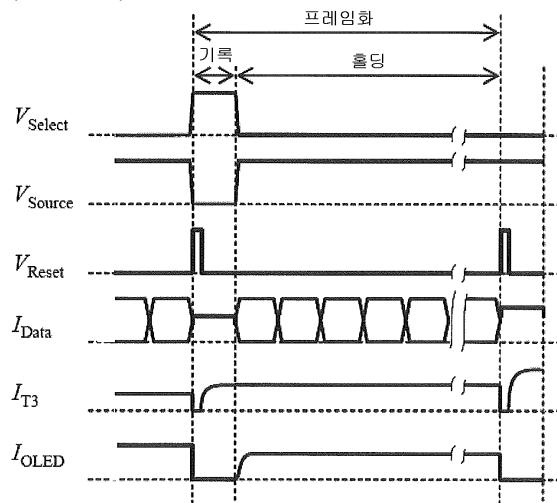

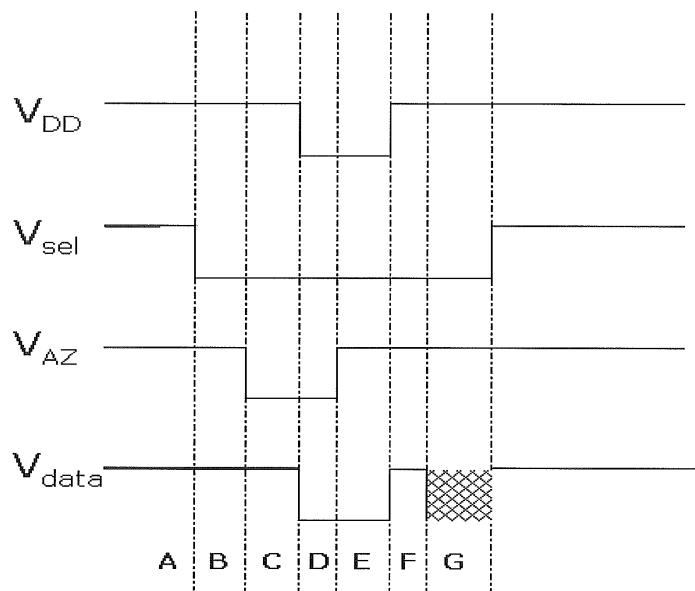

도 4는 도 3에 도시된 전압 프로그래밍되는 픽셀 회로 유형의 동작을 도시한 타이밍도,

도 5a 내지 5h는 본 발명의 측면의 실시예에 따른 전류 프로그래밍되는 픽셀 회로의 예시를 도시한 도면,

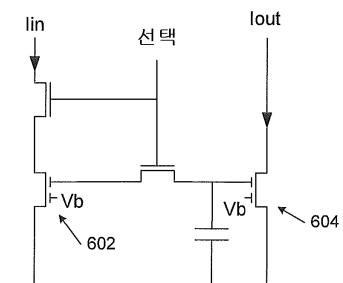

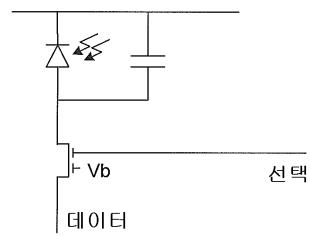

도 6a 및 6b는 각각 픽셀 회로에 대한 플로팅 게이트 전류 미러 회로의 예시 및 플로팅 게이트 박막 트랜지스터를 포함하는 액티브 매트릭스 센서 회로의 예시를 도시한 도면,

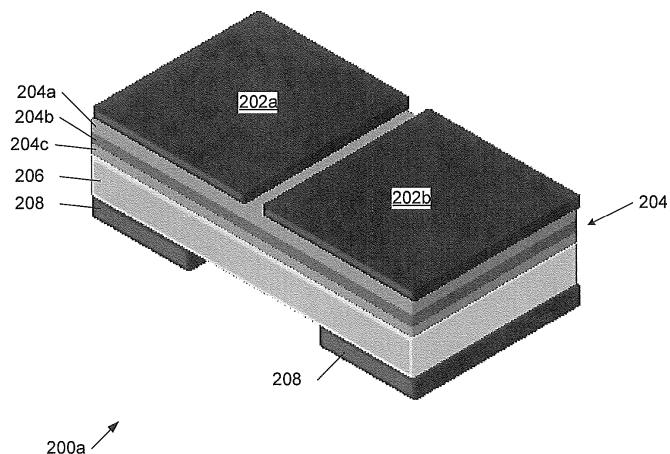

도 7a 및 7b는 각각 본 발명의 실시예에 따른 액티브 매트릭스 픽셀 회로에 대한 접적 및 비-접적 플로팅 게이트 디바이스 구조 및 상용하는 회로를 도시한 도면.

### 발명을 실시하기 위한 구체적인 내용

[0031]

본 발명의 전술된 측면 및 그외의 측면이 첨부된 도면을 참조하여 예시적인 방식으로 더 기술될 것이다.

[0032]

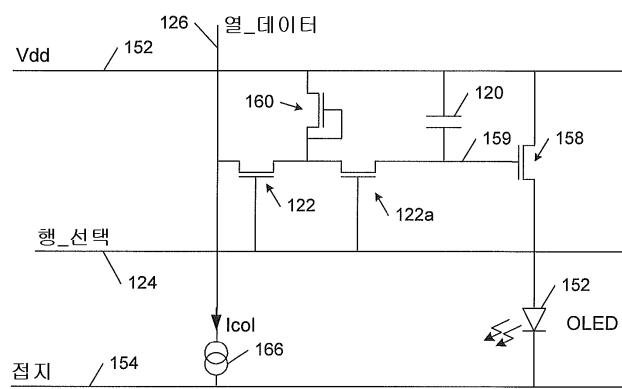

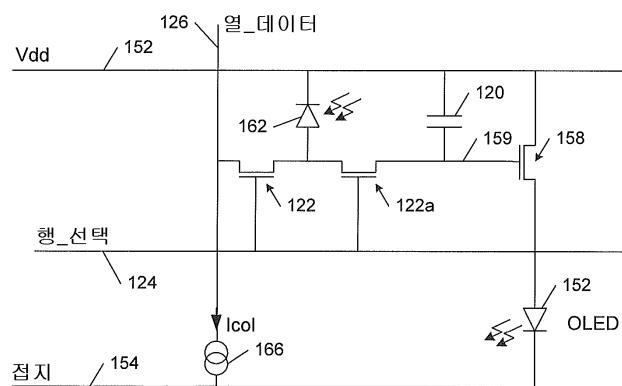

도 1c는 전압 프로그래밍되는 OLED 액티브 매트릭스 픽셀 회로(150)의 예시를 도시한다. 회로(150)는 디스플레이의 각 픽셀에 제공되고, Vdd(152), 접지(154), 행 선택(124) 및 열 데이터(126) 버스바(busbar)가 제공되어 픽셀들을 상호접속시킨다. 따라서 각 픽셀은 파워 및 접지 접속을 구비하고, 픽셀들의 각 행은 공통 행 선택 라인(124)을 구비하며, 픽셀들의 각 열은 공통 데이터 라인(126)을 구비한다.

[0033]

각 픽셀은 접지(154)와 파워 라인(152) 사이에 드라이버 트랜지스터(158)와 직렬 접속된 OLED(152)를 구비한다. 드라이버 트랜지스터(158)의 게이트 접속부(159)는 저장 커패시터(120)로 연결되고, 제어 트랜지스터(122)는 게이트(159)를 행 선택 라인(124) 제어하에서 열 데이터 라인(126)으로 연결한다. 트랜지스터(122)는 행 선택 라인(124)이 활성화되었을 때 열 데이터 라인(126)을 게이트(159) 및 커패시터(120)로 접속시키는 박막 전계 효과 트랜지스터(TFT) 스위치이다. 따라서 스위치(122)가 온 상태일 때, 열 데이터 라인(126) 상의 전압은 커패시터(120) 상에 저장될 수 있다. 이러한 전압은, 드라이버 트랜지스터(158)로의 게이트 접속의 비교적 높은 임피던스 및 스위치 트랜지스터(122)가 "오프" 상태일 때 그것의 비교적 높은 임피던스로 인해, 적어도 프레임 리프레쉬 기간 동안은 커패시터 상에 유지된다.

[0034]

드라이버 트랜지스터(158)는 전형적으로 TFT이고, 문턱 전압보다 낮은 트랜지스터의 게이트 전압에 의존하는 (드레인-소스) 전류를 전달한다. 따라서 게이트 노드(159)에서의 전압은 OLED(152)를 통과하는 전류를 제어하고 그에 따라 OLED의 밝기를 제어한다.

[0035]

도 1c의 전압-프로그래밍되는 회로는 특히 OLED 방출이 인가된 전압에 비선형적으로 의존한다는 사실로 인한 것과 같은 다수의 단점으로부터 문제를 겪으며, OLED로부터의 광 출력은 그것을 통과하는 전류에 비례하기 때문에 전류 제어가 바람직하다. 도 1d(도 1c와 동일한 요소에는 동일한 참조번호가 표시됨)는 전류 제어를 사용하는 도 1c의 회로의 변화를 도시한다. 보다 구체적으로, 전류 생성기(166)에 의해 설정되는 (열) 데이터 라인 상의 전류는 박막 트랜지스터(TFT)(160)를 통과하는 전류를 "프로그래밍"하고, 이는 다시 트랜지스터(122a)가 온 상태일 때 (매칭) 트랜지스터(160, 158)가 전류 미러를 형성하기 때문에 OLED(152)를 통과하는 전류를 설정한다. 도 1e는 (픽셀 드라이버 회로가 선택되었을 때) 데이터 라인 내의 전류가 광다이오드를 통과하는 전류를 설정함으로써 OLED로부터의 광 출력을 프로그램하도록 TFT(160)가 광다이오드(162)로 대체된 추가적인 변화를 도시한다.

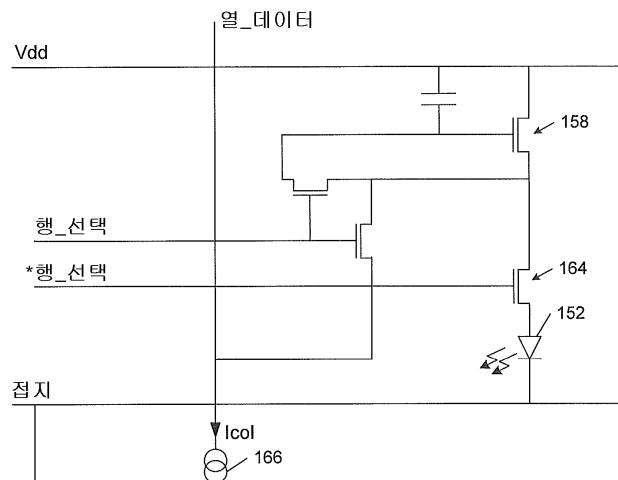

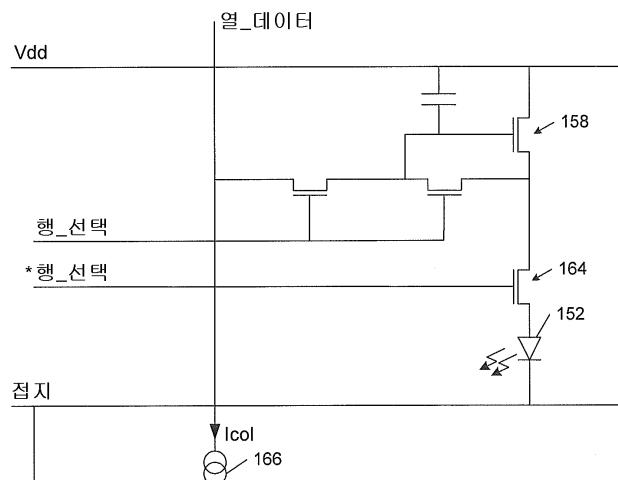

[0036]

도 1f는 전류-프로그래밍되는 픽셀 드라이버 회로의 추가적인 예시를 도시한 것으로, 이는 본 출원인의 출원 WO 03/038790으로부터 차용한 것이다. 이 회로에서, OLED(152)를 통과하는 전류는 예로서 기준 전류 싱크와 같은 전류 생성기(166)를 이용하여 OLED 드라이버 트랜지스터(158)에 대한 드레인-소스 전류를 설정하고, 이러한 드레인-소스 전류에 대해 요구되는 드라이버 트랜지스터 게이트 전압을 기억함으로써 설정된다. 따라서 OLED(152)의 밝기는, 바람직하게는 어드레스되는 픽셀에 대해 요구되는 바와 같이 조정가능하고 설정되는 기준 전류 싱크(166)로 흐르는 전류  $I_{col}$ 에 의해 결정된다. 또한, 추가적인 스위칭 트랜지스터(164)가 프로그래밍 상태 동안의 OLED 발광을 방지하도록 구동 트랜지스터(158)와 OLED(152) 사이에 접속된다. 일반적으로, 각각의 열 데이터 라인에 하나의 전류 싱크(166)가 제공된다. 도 1g는 도 1f의 회로의 변화를 도시한다.

[0037]

도 2는 드레인(D), 소스(S) 및 각각에 전압  $V_1$ ,  $V_2$ , ...,  $V_N$ 이 인가되는 트랜지스터의 플로팅 게이트(FG)(204)로 용량 결합되는 복수의 입력 단자(202)를 구비하는 플로팅 게이트 박막 트랜지스터(200)의 개략도를 도시한다.

트랜지스터(200)는 또한 플로팅 게이트(FG)(204)를 포함한다. 도 2는 또한 복수의 입력 단자 및 트랜지스터의 플로팅 게이트가 어떻게 커패시터  $C_1, C_2, \dots, C_N$ 의 세트로 고려될 수 있는지도 도시한다. 이러한 후자의 표현은 후에 기술되는 픽셀 회로에서 사용된다.

[0038] 도 3a를 참조하면, 각각이 TFT(302)(T2)의 플로팅 게이트로의 연관된 용량 결합을 갖는 복수의 입력 단자(304)를 구비하는 플로팅 게이트 구동 트랜지스터(302)를 포함하는 전압 프로그래밍된 픽셀 회로(300)의 제 1 예시를 도시한다. 또한 고유 게이트-소스 커패시턴스  $C_{gs}$ 가 점선으로 도시되었다(T2가 온 상태일 때 이것은 채널 커패시턴스의 일부와 트랜지스터의 기생 커패시턴스를 포함하며, T2가 오프 상태일 때는 단지 기생 커패시턴스만을 포함한다). 전형적으로 이러한 기생 커패시턴스는 회로 저장 커패시턴스를 제공하기 위해 게이트와 소스 사이의 오버랩 영역을 증가시킴으로써 증가된다. 구동 트랜지스터(302)는 OLED(301)를 구동한다. 제 1 선택 트랜지스터(306)(T1)는 플로팅 게이트 구동 TFT의 입력 단자들 중 하나를 픽셀 회로에 대한 프로그래밍 전압을 갖는 데이터 라인(308)에 선택적으로 연결하며, 제 2 선택 트랜지스터(310)는 오토 제로(auto-zero) 라인 AZ 상의 신호에 응답하여 트랜지스터(302)의 제 2 입력 단자를 트랜지스터(302)의 드레인 접속부로 선택적으로 연결시킨다. 이것은 예를 들어 픽셀 구동에서의 노화 및/또는 비균일성에 대해 보상하기 위한 오토 제로 기능을 제공한다. 도 3a의 예시적인 회로에서 트랜지스터(302)(T2)는 p-채널 디바이스이다.

[0039] 도 3b는 도 3a와 동일하지만 약간 상이한 모습을 갖는 회로를 도시한다.

[0040] 도 3c는 도 3a 및 3b의 회로의 p-채널 변화의 예시를 도시한 것으로, 동일한 요소는 동일한 참조번호로 표시되었으며, 도 3c의 회로는 이전에 기술된 도 1e의 회로와 유사한 방식으로 광다이오드(350)를 포함한다. 이것은 OLED(301)가 온 상태일 때 광학적 피드백을 제공하며, 이 회로가 트랜지스터(302)의 문턱 전압  $V_t$ 의 차이 또는 이동을 정정한다는 점에서 도 1e의 구성과 비교하여 장점을 제공한다.

[0041] 도 4는 도 3의 회로의 동작을 더욱 자세하게 도시한 타이밍도이다. 도 3a의 액티브 매트릭스 픽셀 회로의 동작에서 스테이지 A-G는 다음과 같이 기술된다:

[0042] A - 픽셀 회로는 오프 상태이고,  $V_{data}$ 는 픽셀 회로로부터 차단되며,  $C_1$  및  $C_2$  커패시터는 정확히 규정할 수 없는 상태임.

[0043] B - 선택 스위치가 인에이블되고 기준 데이터 전압(VHIGH)이 플로팅 게이트 TFT(302)의 하나의 입력 단자 ( $V_1=VHIGH$ )로 인가되며, 따라서 플로팅 게이트 TFT(302)를 통과하는 전류를 발생시키지 않음( $|V_{FGS}| < |V_t|$ ),  $V_{DD}$ 는 HIGH 상태임.

[0044] C - AZ는 LOW 상태이고 T3이 인에이블됨, 드라이브 TFT(T2)의 V2 입력은 드레인으로 접속되고 따라서 T2(302)가 다이오드 접속됨. V1 입력은 여전히 VHIGH에 있음( $V_1=VHIGH$ ). 전류는 T2를 통해 전도하기 시작하고  $V_{gs}/V_{ds}$ 가 증가함. 전하는 커패시터  $C_1, C_2$  및  $C_{gs}$  사이에서 재분배됨.

[0045] D -  $V_{DD}$  및  $V_1(V_{data}$  내에서의 변화에 의해 구동됨)는  $\Delta V$ 만큼 낮아짐,  $V_D(T2)$ 가 낮아지고 OLED(301)는 역 바이어스됨. T2를 통과하는 전류는 인에이블된 T3를 통해서  $C_2$ 로 재다이렉팅되고, 커패시턴스  $C_2$ 를 충전함. 전압 문턱이 TFT(302)의 플로팅 게이트에 도달하였을 때 전압  $V_2$ 가 HIGH 상태가 되고 트랜지스터(302) 스위치가 오프 상태로 됨(그리고  $V_t$ 가  $C_{gs}$  상에 기록됨).

[0046] E - AZ가 HIGH 상태가 되고, T3는 오프 상태가 되며,  $V_2$ 가 차단됨.

[0047] F - OLED가 정 바이어스된 상태에 있도록  $V_{DD}$  및  $V_1$ (인에이블된 T1을 통과함)는 다시 HIGH가 됨.

[0048] G - T2 상으로 프로그래밍되는 데이터는 문턱 전압  $V_t$ 에 의해 오프셋됨.

[0049] 당업자는 전술된 설명으로부터 도 3의 픽셀 회로가 OLED를 차단하기 위해 TFT 스위치를 필요로 하지 않고 전압 프로그래밍되는 픽셀 드라이브에서의 문턱 전압 보상을 가능케 한다는 것을 이해할 것이다(이것이 OLED를 역 바이어스하기 위해 입력 전압을 제어함으로써 효율적으로 달성되기 때문임). 또한 실시예에서 사용된 모든 커패시터들은 디바이스(302)와 같은 집적 플로팅 게이트 TFT에 의해 제공될 수 있다. 이와 달리, 만약 회로가 집적 TFT 없이 구성되면, 회로 레이아웃의 설계는 게이트와 소스/드레인 금속 층 사이의 비아에 대한 필요성을 방지할 수 있다. 데이터 전압 정보 프로그래밍 픽셀은, 실시예에서, 커패시턴스  $C_{gs}$ 에 의해 저장되며, 따라서 구동

TFT(302)(T2)의 기생 커패시턴스에 의해 결정된다. 이것은 구동 TFT(302)의 채널 커패시턴스의 일부에 의해서뿐 아니라, 게이트와 소스 사이의 오버랩 영역에 의해서도 결정된다. 이러한 오버랩은 충분한 저장 커패시턴스를 제공하기 위해 증가될 수 있거나, 또는 외부 커패시턴스가 제공된다. 커패시터 C1 및 C2는 플로팅 게이트 트랜지스터(302)(T2)의 접적 커패시턴스 또는 구동 TFT 옆의 개별적인 패터닝된 구성요소일 수 있으며, 회로 설계의 일부를 포함하고, 이들의 값은 접적되었는지 또는 개별적인 구성요소인지와 무관하게 플로팅 게이트 전극과 입력 단자 사이의 지형적인 오버랩 영역을 선택함으로써 결정될 수 있다.

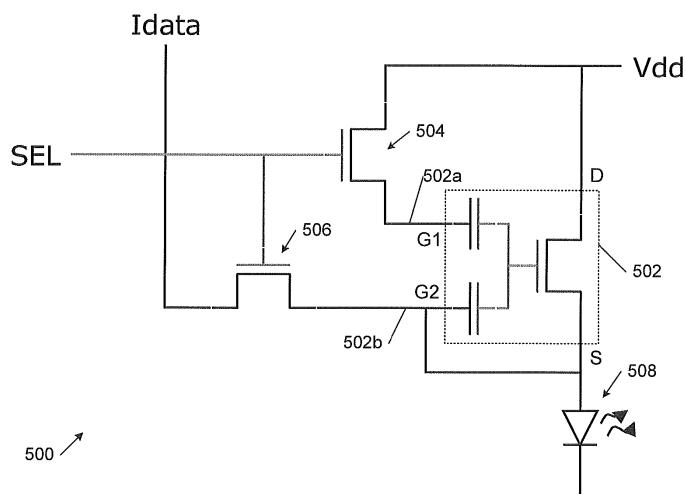

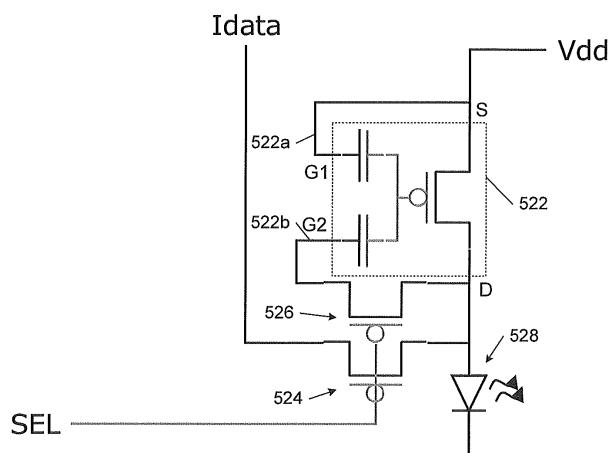

[0050] 도 5a는 플로팅 게이트 구동 트랜지스터(502)를 포함하는 전류 프로그래밍된 액티브 매트릭스 픽셀 회로(500)의 제 1 예시를 도시한다. 도 5a의 회로는 도 1a의 회로와 비교될 수 있다. 트랜지스터(502)의 하나의 입력 단자(502a)(G1)는 선택 트랜지스터(504)(도 1a의 T1에 해당됨)에 대한 입력 접속으로서의 역할을 한다. 다른 입력 단자(502b)(G2)는 이러한 입력 단자가 연결되는 제 2 선택 트랜지스터(506)가 스위칭 온 되었을 때 트랜지스터(502)의 입력 커패시턴스 상의 전류 데이터 라인 Idata 상에서 설정된 전류에 의해 프로그래밍되는 게이트-소스 전압을 저장하는 데에 사용된다. 따라서, 동작시에 SEL 라인이 어씨트되면, 트랜지스터(504, 506)가 스위칭 온 되고, 픽셀을 프로그래밍하기 위해 Vdd 라인이 LOW 상태가 되며, 전류 싱크는 트랜지스터(502)의 입력 단자 커패시터 상의 프로그래밍된 전류에 상응하는 전압을 설정하기 위해서 Idata 라인으로 인가된다. 그 다음 SEL 라인은 디-어씨트되고, Vdd는 HIGH 상태가 되어 프로그래밍된 전류가 OLED(508)를 통해 흐르도록 한다. 리셋 트랜지스터(도 5a에 도시되지 않음)는 출력 전류를 프로그래밍하기 전에 입력 단자 G2와 FG 사이에서 접속된 입력 커패시터 상에 저장된 전압을 리셋하기 위해 Idata 라인으로 연결될 수 있다.

[0051] 도 5a의 회로는 감소된 개수의 비아를 가지고 제조될 수 있으며, 접적 입력 커패시터는 픽셀 회로에 대한 물리적 크기를 더욱 작게 한다. 따라서 회로는 보다 총 구조가 보다 높은 복잡도를 갖는 대신 보다 작은 물리적 크기를 갖는 접적 플로팅 게이트 디바이스(즉, 접적 입력 커패시터를 구비함)로 구현될 수 있거나, 또는 보다 단순한 총 구조가 보다 적은 비아를 갖거나 비아가 없이 획득될 수 있는 비-접적 입력 커패시터로 구현될 수 있다.

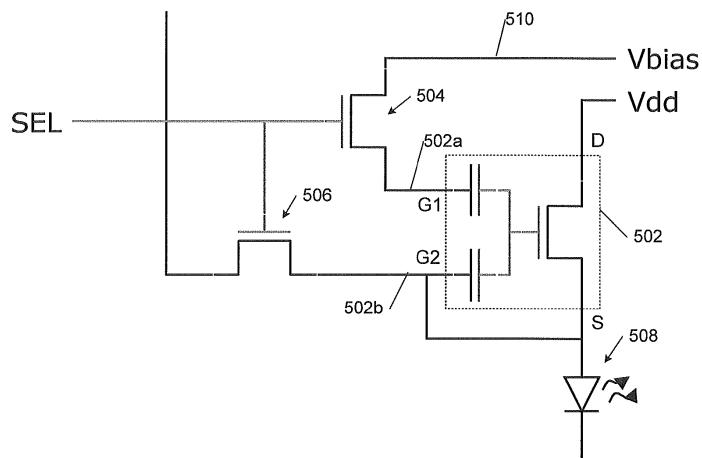

[0052] 도 5a의 회로는 n-채널 트랜지스터를 사용하지만, 당업자가 이해하는 바와 같이, 이와 달리 p-채널 트랜지스터가 사용될 수도 있다. 도 5b는 선택 트랜지스터(504)가 Vdd가 아닌 Vbias(510)으로 연결되는, 도 5a의 회로의 변화를 도시하며, 여기에서 동일한 요소들은 동일한 참조번호로 표시되었다. 이러한 바이어스 라인은 입력 단자(G1) 상의 전압을 조정함으로써 구동 트랜지스터의 유효 문턱 전압을 조정하는 데에 사용될 수 있다. 문턱 전압이 0이 아닌 경우에, 따라서 다이오드 접속을 사용하여 구동 디바이스를 프로그래밍하는 경우에 (포화 상태를 유지하는 데에 필요한 것보다) 더 큰 드레인-소스 전압이 생성될 것이며, 플로팅 게이트 디바이스를 위한 문턱 전압이 0으로 조정될 수 있고, 그에 따라 동일한 OLED 구동 전류에 대해 사용되는 게이트 소스 전압을 낮출 수 있다. 이것은 보다 낮은 Vdd가 사용되는 것을 가능케 하며, 따라서 전력 소비를 감소시킨다. 당업자는 유사한 방식으로 Vbias가 Vt를 감소시키기 위해서 양의 방향으로 조정되며, Vbias가 Vt를 증가시키기 위해서 음의 방향으로 조정될 수 있음을 이해할 것이다.

[0053] 도 5b의 구성은 또한 프로그래밍 동안에 Vdd가 OLED 바이어스를 반전시키기 위해 보다 낮은 전압 레벨로 전달되며, OLED가 픽셀 회로의 전류 프로그래밍 동안에 발광하지 않도록 Vbias 라인 상의 전압이 제어되는 대안적인 동작 모드를 용이하게 한다. 이러한 구성은 음의 방향으로 프로그래밍 전압을 이동시키기 위해 양의 방향으로 Vbias를 조정하는 것에 의존한다. 소스 전압이 증가하고 OLED가 턴온 됨에 따라, 프로그래밍 후에 Vgs가 대략 일정하게 유지된다(도 5b의 G1가 기본적으로 플로팅함).

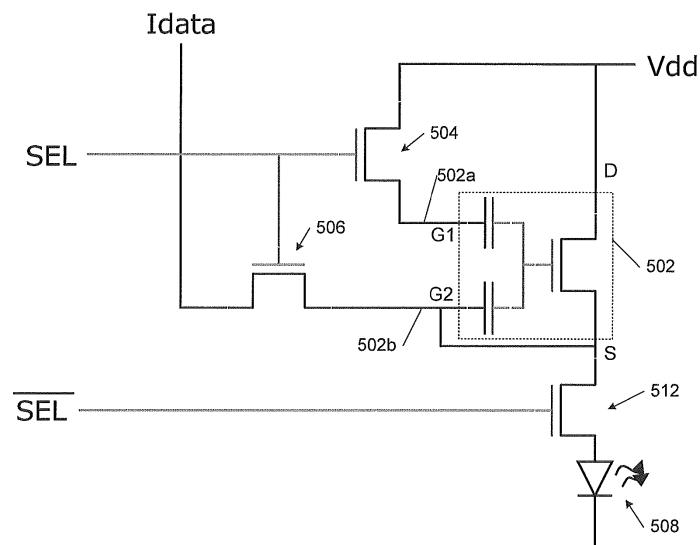

[0054] 도 5c는 프로그래밍 동안에 Vdd가 LOW를 취하지 않고 OLED(508)이 동적으로 스위칭 오프될 수 있도록, SEL 라인의 인버팅된 버전으로 연결된 디스에이블(disable) 트랜지스터(512)를 포함하는 도 5a의 회로에 대한 추가적인 변화를 도시하며, 동일한 요소들은 동일한 참조번호로 표시되었다.

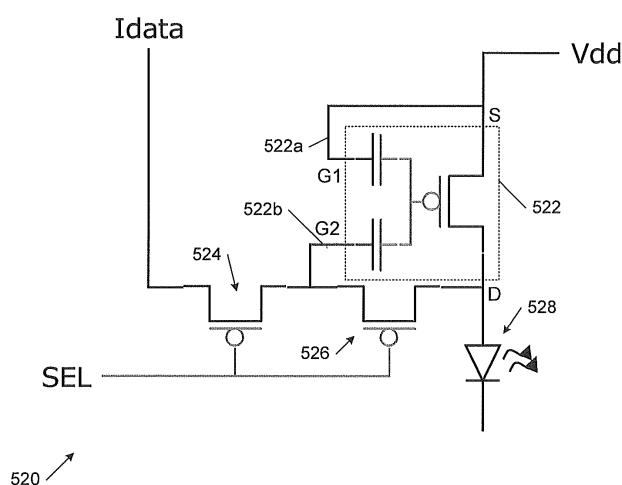

[0055] 도 5d는 회로가 n-채널 디바이스가 아닌 p-채널 디바이스를 사용하는 전류 프로그래밍된 액티브 매트릭스 픽셀 회로(520)의 다른 예시를 도시한다. 도 5d의 회로에서, 구동 트랜지스터(522)는 선택 트랜지스터(524, 526)가 온 상태일 때 Idata 라인 상의 전류에 의해 프로그래밍된 게이트 전압을 상응하는 입력 커패시터 상에 저장하는 제 1 입력 단자(522a)(G1)를 구비하는 반면, 제 2 입력 단자(522b)(G2)는 트랜지스터(522)에 대한 추가의 입력 단자로서의 역할을 하고, 구동 TFT의 드레인으로 접속되며, 제공하는 구동 TFT는 온 상태이고 프로그래밍 동안 포화 상태이다. 다시, 프로그래밍 동안에, 선택 트랜지스터(524, 526)는 온 상태에 있고 프로그래밍 전류는 Vdd 라인으로부터 구동 트랜지스터(522)를 통해 Idata 라인에 접속된 프로그램 가능한 데이터 싱크(도시되지 않음)로 흐른다. 선택 트랜지스터(524, 526)가 스위칭 오프되었을 때, 이러한 전류는 OLED(528)를 통해 흐른다(프로그래

밍 단계 중에 OLED를 통과하는 전류는 디스에이블되어야 한다).

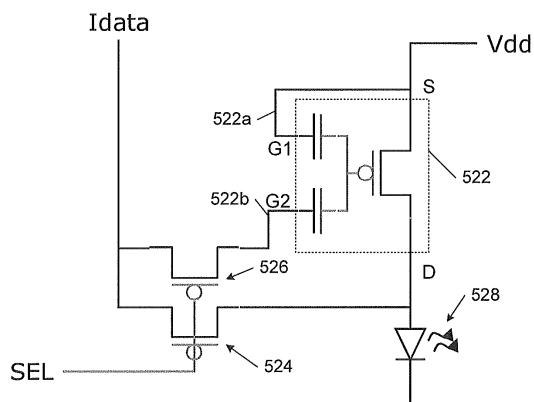

[0056] 도 5e는 도 5d의 변화를 도시하며, 여기에서 선택 트랜지스터(524, 526)가 Idata 라인과 구동 트랜지스터(522)의 드레인 접속부 사이에 직렬 연결되기보다는 선택 트랜지스터들(526) 중 하나가 이러한 트랜지스터의 제 2 입력 단자(G2)(522b)와 구동 트랜지스터(522)의 드레인 단자 사이에 연결되는 반면, 제 2 선택 트랜지스터(524)는 Idata 라인을 구동 트랜지스터(522)의 드레인 단자로 직접 연결시킨다. 이는 프로그래밍 전류를 전달하는 Idata 라인과 구동 트랜지스터 출력 사이에 단일 선택 트랜지스터가 존재한다는 장점을 갖는다.

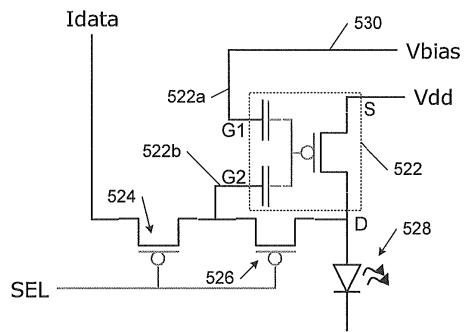

[0057] 도 5f는 도 5b를 참조로 기술된 것과 대략 유사한 방식으로 구동 트랜지스터(522)의 문턱 전압의 조정/제어를 허용하도록 입력 단자(G1)(522a)가 바이어스 전압 라인 Vbias(530)로 접속되는 회로의 추가적인 변화를 도시하며, 도 5d의 회로와 동일한 요소는 동일한 참조번호로 표시되었다.

[0058] 도 5f에 도시된 바와 같이 바이어스 전압 라인을 포함하는 구성을 계속 참조하면, 동작시에 플로팅 게이트 TFT의 하나의 입력 단자가 문턱 전압을 큰 값으로 증가시키기 위해 바이어스되면 -이것은 바이어스 전압 라인을 포지티브로 바이어싱함으로써 수행될 수 있음(p-타입)-, 다이오드 접속되었을 때, 구동 TFT 양단의 드레인 소스 전압 VDS가 OLED를 역 바이어싱할 수 있고 그러므로 프로그래밍 사이클 동안에 그 동작을 불가능하게 할 수 있다. 따라서, Vdd 전압의 변조(LOW를 취함)가 요구되지 않기 때문에 이것은 유용한 장점을 제공한다. 실시예에서, 일반적으로 이러한 라인과 연관된 상당한 커패시턴스가 존재하기 때문에 이것은 전력 절약을 제공할 수 있다. 실시예에서, 액티브 매트릭스 디스플레이 디바이스 내의 바이어스 전압은 이웃하는 픽셀들/픽셀들의 라인들 사이에서 공유될 수 있다.

[0059] 도 5g는 구동 트랜지스터의 제 2 입력 단자(G2)(522b)에 연결된 선택 트랜지스터(526)가 구동 트랜지스터의 드레인 단자에 연결되지 않고 직접 Idata 라인에 연결되는 (또는 도 5e에서와 같이 둘 모두에 연결되지 않음) 또 다른 회로를 도시한다(그에 따라 드레인 단자가 직렬 접속된 선택 트랜지스터(524, 526)를 통해 입력 단자(G2)로 접속됨).

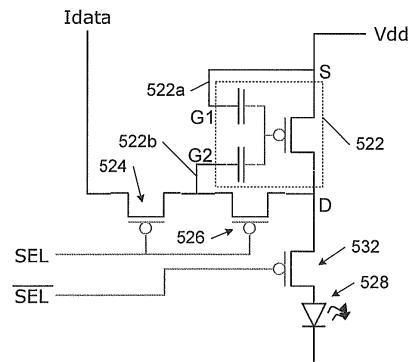

[0060] 도 5h는 OLED가 프로그래밍 동안에 동작으로 스위칭 오프될 수 있도록 (그리고 그에 따라 Vdd가 프로그래밍 동안에 LOW를 취할 필요가 없도록) 추가의 OLED 디스에이블 트랜지스터(532)가 제공되는 전류 프로그래밍된 회로의 추가적인 변화를 도시한다.

[0061] 도 6a는 하나의, 또는 도시된 바와 같이 두 개의 플로팅 게이트 트랜지스터(602, 604)를 사용하여 액티브 매트릭스 픽셀 드라이버 회로로 결합될 수 있는 전류 미러 회로의 예시를 도시한다. 도시된 예에서, 예를 들어 두 트랜지스터(602, 604)의 특징들을 더욱 잘 매칭시키기 위해 트랜지스터(602, 604)의 하나의 문턱 전압 또는 두 문턱 전압 모두를 조정하도록 제 2 입력 단자들 중 하나 또는 둘 모두가 바이어스 전압으로 연결될 수 있다. 유사한 구성이 전류 복제자(copier) 회로에서 사용될 수 있다. 하나 또는 그 이상의 플로팅 게이트 디바이스를 사용하는 것의 다른 장점은, 입력 단자들 중 하나에서의 게이트 전압을 제어함으로써 구동 TFT의 문턱 전압을 감소시켜 요구되는 전력 공급이 감소될 수 있다는 점이다.

[0062] 도 6b는 전술된 바와 같은 문턱 전압 조정을 다시 이용하여, 플로팅 게이트 TFT를 포함하는 센서를 위한 액티브 매트릭스 픽셀 회로의 예시를 도시한다.

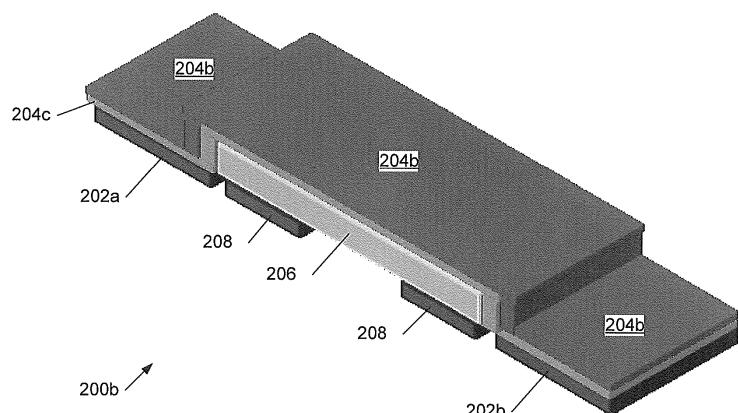

[0063] 도 7a 및 7b는 집적 및 비-집적 플로팅 게이트 디바이스 구조 및 회로를 도시한다. 도 2와 동일한 요소들은 동일한 참조번호로 표시되었다.

[0064] 도 7a는 집적 플로팅 게이트(204)를 구비하는 플로팅 게이트(FG) TFT(200a)의 실시예를 도시한다. 이러한 집적 FG 디바이스에서, 플로팅 게이트 커패시터는 반도체(206) 상의 플로팅 게이트와 소스-드레인 금속(208) 내의 소스 및 드레인 접속부를 형성하도록 유전층(204a, 204c) 사이에 샌드위치된 게이트 금속(204b)의 층을 포함한다. 용량 결합된 제 1 입력(202a)은 플로팅 게이트(204b)의 제 1 부분을 구비하는 제 1 입력 커패시터를 형성하고, 용량 결합된 제 2 입력(202b)은 플로팅 게이트(204b)의 제 2 부분을 구비하는 제 2 입력 커패시터를 형성한다.

[0065] 도 7b는 비-집적 플로팅 게이트를 구비하는 플로팅 게이트(FG) TFT(200b)의 실시예를 도시하고, 도 7a에서와 동일한 요소들은 동일한 참조번호로 표시되었다. 다시, 이러한 구조에서 용량 결합된 제 1 입력(202a)은 플로팅 게이트(204b)의 제 1 부분을 구비하는 제 1 입력 커패시터를 형성하고, 용량 결합된 제 2 입력(202b)은 플로팅 게이트(204b)의 제 2 부분을 구비하는 제 2 입력 커패시터를 형성한다. 그러나, 용량 결합된 제 1 및 제 2 입력은 수직 구조를 갖기보다는, 소스-드레인의 양 측면이 접촉하도록 수평으로 배치된다. 이것은 각 입력 커패시터의 하나의 플레이트가 소스-드레인 금속 층을 이용하여 형성되는 것을 가능하게 하고, 이것은 픽셀 구동 회로 내의 비아의 개수를 감소시키는 것을 가능하게 한다. 또한, 도 7a와의 비교에 의해 알 수 있는 바와 같이, 하나

적은 금속 층과 하나 적은 유전층이 존재한다.

[0066] 전술된 회로의 바람직한 실시예에서, 트랜지스터는 예를 들어 비정질 실리콘으로부터 제조된 MOS 디바이스를 포함한다. 그러나, 다른 구현에서 하나 이상의 유기 박막 트랜지스터가 사용될 수도 있다.

[0067] 당업자가 이해하는 바와 같이 전술된 회로는 n-채널 또는 p-채널 변형으로 구현될 수도 있다. 당업자는 다수의 다른 변화들이 이루어질 수 있으며, 예를 들어 도 1c 내지 1g에 도시된 하나 이상의 회로들이 플로팅 게이트 구동 트랜지스터를 이용하여 구현될 수도 있다는 것을 이해할 것이다. 보다 일반적으로, 사실상 당업계에서 사용되는 어떠한 픽셀 회로도 전술된 내용에 따라서 플로팅 게이트 TFT를 포함하도록 구성될 수 있다.

[0068] 당업자에 의해 다수의 다른 효율적인 대안들이 고안될 수 있다. 본 발명이 전술된 실시예로 제한되지 않으며, 본 명세서에 첨부된 특허청구범위의 사상 및 범주 내에 포함되는 변경사항들을 포함한다는 것이 당업자에게 명백하게 이해될 것이다.

## 도면

### 도면 1a

(종래기술)

### 도면 1b

(종래기술)

## 도면1c

## 도면1d

## 도면1e

## 도면 1f

도면 1g

## 도면2

## 도면3a

## 도면3b

## 도면3c

## 도면4

## 도면5a

## 도면5b

도면5c

도면5d

도면5e

## 도면5f

도면5g

## 도면5h

### 도면6a

도면6b

도면7a

도면7b

|                |                                                                                                                                                          |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵光电器件，有源矩阵像素电路驱动方法，浮栅有机薄膜晶体管                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">KR1020100077003A</a>                                                                                                                         | 公开(公告)日 | 2010-07-06 |

| 申请号            | KR1020107009672                                                                                                                                          | 申请日     | 2008-10-29 |

| [标]申请(专利权)人(译) | 剑桥显示技术有限公司                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 剑桥显示科技有限公司                                                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 剑桥显示科技有限公司                                                                                                                                               |         |            |

| [标]发明人         | RANKOV ALEKSANDRA<br>란코브알렉산드라<br>SMITH EUAN CHRISTOPHER<br>스미스유안크리스토퍼                                                                                    |         |            |

| 发明人            | 란코브알렉산드라<br>스미스유안크리스토퍼                                                                                                                                   |         |            |

| IPC分类号         | G09G3/30                                                                                                                                                 |         |            |

| CPC分类号         | G09G2300/0852 G09G2300/0465 G09G2300/0861 G09G2320/043 G09G3/325 G09G3/3233 G09G3/3283 G09G2300/0819 G09G2360/148 G09G2310/0256 G09G2300/0876 G09G3/3291 |         |            |

| 代理人(译)         | KIM , WON JOON                                                                                                                                           |         |            |

| 优先权            | 2007021567 2007-11-02 GB<br>2007023859 2007-12-06 GB                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                |         |            |

## 摘要(译)

本发明涉及用于有源矩阵光电器件的像素驱动电路，更具体地涉及OLED (有机发光二极管)显示器。本发明提供一种具有多个有源矩阵像素的有源矩阵光电器件，每个所述像素包括像素电路，该像素电路包括驱动所述像素的薄膜晶体管(TFT)和用于存储像素值的像素电容器TFT包括具有浮栅的TFT。