# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) Int. Cl.

**H05B 33/10** (2006.01) **H05B 33/22** (2006.01) **H01L 51/50** (2006.01)

(21) 출원번호

10-2008-0124192

(22) 출원일자

2008년12월08일

심사청구일자 🔓

없음

(11) 공개번호 10-2010-0065716

(43) 공개일자 2010년06월17일

(71) 출원인

#### 엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

#### 김동환

대구광역시 달서구 용산1동 롯데캐슬아파트 110동 406호

#### 김형철

서울특별시 관악구 봉천9동 관악벽산블루밍아파트 1718(17/1) 103-1902

#### 오경탁

경상북도 구미시 신평1동 150-27번지 LG전자기숙 사 가동 704호

(74) 대리인

특허법인네이트

전체 청구항 수 : 총 5 항

#### (54) 듀얼패널 타입 유기전계발광소자 및 이의 제조방법

#### (57) 요 약

본 발명은 듀얼패널 타입 유기전계발광 소자에 관한 것이며, 특히 상부 발광방식 유기전계발광소자에 관한 것이다.

본 발명의 특징은 버퍼층을 질화실리콘(SiNx)과 산화실리콘(Si02)으로 이루어진 이중층으로 형성하여, 산화실리콘(Si02) 패터닝 과정의 BOE(buffered oxide etching) 습식식각 공정에서 제 1 전극 상에 부착된 이물을 제거하는 것이다.

이로 인하여, 기존의 OLED는 제 1 전극 상에 부착된 이물에 의해 제 1 전극과 제 2 전극이 서로 접촉되어 통전되는 단락(short)됨으로써 발생했던 암점으로 인한 화소불량을 방지할 수 있어, OLED의 전반적인 휘도 및 화상 특성을 균일하게 할 수 있다.

#### 대 표 도 - 도3

#### 특허청구의 범위

#### 청구항 1

다수의 화소영역이 정의된 제 1 기판의 일면에 구동 박막트랜지스터를 형성하는 단계와;

상기 제 1 기판을 마주보는 제 2 기판의 일면에 제 1 전극을 형성하는 단계와;

상기 제 1 전극 상에 상기 다수의 화소영역의 경계에 포토레지스트 도포, 노광, 현상 및 건식식각을 포함하는 마스크 공정을 통해 질화실리콘(SiNx)으로 이루어진 제 1 버퍼층을 형성하는 단계와;

상기 제 1 버퍼층 상부에 포토레지스트 도포, 노광, 현상 및 BOE(buffered oxide etching)를 이용한 습식식각을 포함하는 마스크 공정을 통해 산화실리콘(Si02)으로 이루어진 제 2 버퍼층을 형성하는 동시에, 상기 제 1 전극 상의 이물을 제거하는 단계와;

상기 제 1 및 제 2 버퍼층 상부로 격벽을 형성하는 단계와;

상기 제 1 및 제 2 버퍼층의 상부로 연결패턴을 형성하는 단계와;

상기 각 화소영역 내의 상기 제 1 전극 상부로 유기발광층을 형성하는 단계와;

상기 유기발광층 상부에 상기 격벽에 의해 각 화소영역 별로 분리되는 제 2 전극을 형성하는 단계

를 포함하는 듀얼패널 타입 유기전계발광소자 제조방법.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 전극은 스퍼터링(sputtering) 방식을 통해 형성하며, 상기 이물은 상기 제 1 전극 형성 공정 중 발생하는 듀얼패널 타입 유기전계발광소자 제조방법.

#### 청구항 3

제 1 항에 있어서,

상기 건식식각은 이온빔 식각(ion beam etching), RF(radio frequency) 스퍼터 식각, 플라즈마(plasma) 식각 또는 반응 이온 식각 중 선택된 어느 하나로 식각하는 듀얼패널 타입 유기전계발광소자 제조방법.

#### 청구항 4

제 1 항에 있어서,

상기 제 1 전극을 형성하기 전에, 상기 제 1 기판 상의 상기 각 화소영역의 경계에 저저항 금속물질로 이루어진 보조전극을 형성하는 단계를 포함하는 듀얼패널 타입 유기전계발광소자 제조방법.

#### 청구항 5

서로 마주대하는 제 1 및 2 기판과;

상기 제 2 기판과 마주보는 상기 제 1 기판의 일면 형성된 구동 박막트랜지스타와;

상기 제 1 기판 상에 형성되며, 상기 구동 박막트랜지스터와 연결되는 연결전극과;

상기 제 1 기판과 마주보는 상기 제 2 기판의 일면에 형성된 제 1 전극과;

상기 제 1 전극 상부에 화면을 구현하는 최소단위 영역인 화소영역별 경계부에 형성되며, 질화실리콘(SiNx)과이의 상부에 산화실리콘(Si02)으로 이루어진 버퍼층과;

상기 버퍼층의 일측에 일정두께로 형성된 격벽과;

상기 격벽의 일측에 형성되며, 상기 연결전극과 연결되는 연결패턴과;

상기 연결패턴을 포함하는 상기 제 2 기판의 전면에 상기 격벽에 의해 상기 화소영역별로 분리된 구조로 차례 대로 형성된 유기발광층 및 제 2 전극

을 포함하는 유기전계발광소자.

#### 명세서

#### 발명의 상세한 설명

#### 기술분야

[0001] 본 발명은 듀얼패널 타입 유기전계발광 소자에 관한 것이며, 특히 상부 발광방식 유기전계발광소자에 관한 것이다.

#### 배경기술

- [0002] 최근까지, CRT(cathode ray tube)가 표시장치로서 주로 사용되었다. 그러나, 최근에 CRT를 대신할 수 있는, 플라즈마표시장치(plasma display panel : PDP), 액정표시장치(liquid crystal display device : LCD), 유기전계 발광소자(organic electro-luminescent device : OLED)와 같은 평판표시장치가 널리 연구되며 사용되고 있는 추세이다.

- [0003] 위와 같은 평판표시장치 중에서, 유기전계발광소자(이하, OLED라 함)는 자발광소자로서, 비발광소자인 액정표시 장치에 사용되는 백라이트가 필요하지 않기 때문에 경량 박형이 가능하다.

- [0004] 그리고, 액정표시장치에 비해 시야각 및 대비비가 우수하며, 소비전력 측면에서도 유리하며, 직류 저전압 구동 이 가능하고, 응답속도가 빠르며, 내부 구성요소가 고체이기 때문에 외부충격에 강하고, 사용 온도범위도 넓은 장점을 가지고 있다.

- [0005] 특히, 제조공정이 단순하기 때문에 생산원가를 기존의 액정표시장치 보다 많이 절감할 수 있는 장점이 있다.

- [0006] 이러한 특성을 갖는 OLED는 크게 패시브 매트릭스 타입(passive matrix type)과 액티브 매트릭스 타입(active matrix type)으로 나뉘어 지는데, 패시브 매트릭스 타입은 신호선을 교차하면서 매트릭스 형태로 소자를 구성하는 반면, 액티브 매트릭스 타입은 화소를 온/오프(on/off)하는 스위칭 소자인 박막트랜지스터가 화소 별로 위치하도록 한다.

- [0007] 최근, 패시브 매트릭스 타입은 해상도나 소비전력, 수명 등에 많은 제한적인 요소를 가지고 있어, 고해상도나 대화면을 구현할 수 있는 액티브 매트릭스 타입 OLED의 연구가 활발히 진행되고 있다.

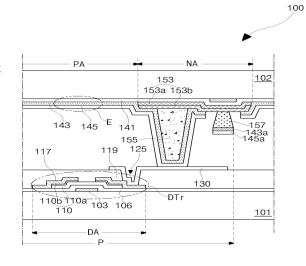

- [0008] 도 1은 일반적인 액티브 매트릭스형 OLED의 단면을 개략적으로 도시한 도면이다.

- [0009] 도시한 바와 같이, OLED(10)는 제 1 기판(1)과, 제 1 기판(1)과 마주하는 제 2 기판(2)으로 구성되며, 제 1 및 제 2 기판(1, 2)은 서로 이격되어 이의 가장자리가 실패턴(seal pattern : 20)을 통해 봉지되어 합착된다.

- [0010] 그리고, 제 2 기판(2)의 내부면에는 외부의 수분을 차단하는 흡습제(13)가 형성된다.

- [0011] 이를 좀더 자세히 살펴보면, 제 1 기판(1)의 상부에는 각 화소영역 별로 구동 박막트랜지스터(DTr)가 형성되어 있고, 각각의 구동 박막트랜지스터(DTr)와 연결되는 제 1 전극(3)과 제 1 전극(3)의 상부에 특정한 색의 빛을 발광하는 유기발광층(5)과, 유기발광층(5)의 상부에는 제 2 전극(7)이 구성된다.

- [0012] 유기발광층(5)은 적, 녹, 청의 색을 표현하게 되는데, 일반적인 방법으로는 각 화소마다 적, 녹, 청색을 발광하는 별도의 유기물질(5a, 5b, 5c)을 패턴하여 사용한다.

- [0013] 이들 제 1 및 제 2 전극(3, 7)과 그 사이에 형성된 유기발광층(5)은 유기전계 발광다이오드를 이루게 된다. 이 때, 이러한 구조를 갖는 OLED(10)는 제 1 전극(3)을 양극(anode)으로 제 2 전극(7)을 음극(cathode)으로 구성하게 된다.

- [0014] 한편, 제 1 전극(3)은 주로 ITO로 이루어진 단일막으로서 스퍼터링(sputtering) 방법에 의한 단일증착으로 형성

하는데, 이때, 스퍼터링 방법에 의한 단일 증착으로 제 1 전극(3) 형성 시 발생하는 이물(미도시)들이 제 1 전 극(3) 상에 단단히 부착되는 문제점이 발생한다.

- [0015] 이러한 이물(미도시)들은 유기발광층(5) 형성 전의 세정공정에 의해서도 제거되지 않아, 제 2 전극(7) 형성 시 제 1 전극(3)과 제 2 전극(7)이 서로 접촉되어 통전되는 단락(short)을 발생시키게 된다.

- [0016] 이로 인하여, 제 1 전극(3)에 전압이 인가되어 흐르는 구동 박막트랜지스터(DTr)의 전류가 유기발광층(5)으로 흘러 소정의 색상을 발광하는 것이 아니라 단락된 제 2 전극(7)으로 흘러 소정의 색상을 발광하지 않게 되어 암점(dark pixel)이 나타나는 화소불량을 발생시키게 된다.

- [0017] 특히, 이러한 암점은 구동 박막트랜지스터(DTr)의 성능감소를 억제하기 위해 구동 박막트랜지스터(DTr)의 게이 트와 소스단자에 정 바이어스(forward bias)가 아닌 역바이어스(reverse bias)를 인가해줌으로써 증가된 문턱전 압을 다시 감소시키는 과정에서 점차적으로 성장되는 진행성 불량으로 진행될 수 있다.

- 이는, 결국 휘도나 화상 특성의 불균일을 발생시키게 된다.

[0018]

[0019]

[0020]

해결 하고자하는 과제

발명의 내용

- 본 발명은 상기와 같은 문제점을 해결하기 위한 것으로, 유기전계발광 다이오드의 제 1 전극 상부의 이물을 제 거하고자 하는 것을 제 1 목적으로 하며, 이로 인한 암점 발생을 방지하고자 하는 것을 제 2 목적으로 한다.

- [0021] 이를 통해, 휘도 및 화상 특성을 향상시키고자 하는 것을 제 3 목적으로 한다.

#### 과제 해결수단

- [0022] 전술한 바와 같은 목적을 달성하기 위해, 본 발명은 다수의 화소영역이 정의된 제 1 기판의 일면에 구동 박막트 랜지스터를 형성하는 단계와; 상기 제 1 기판을 마주보는 제 2 기판의 일면에 제 1 전극을 형성하는 단계와; 상기 제 1 전극 상에 상기 다수의 화소영역의 경계에 포토레지스트 도포, 노광, 현상 및 건식식각을 포함하는 마스크 공정을 통해 질화실리콘(SiNx)으로 이루어진 제 1 버퍼층을 형성하는 단계와; 상기 제 1 버퍼층 상부에 포토레지스트 도포, 노광, 현상 및 BOE(buffered oxide etching)를 이용한 습식식각을 포함하는 마스크 공정을 통해 산화실리콘(SiO2)으로 이루어진 제 2 버퍼층을 형성하는 동시에, 상기 제 1 전극 상의 이물을 제거하는 단계와; 상기 제 1 및 제 2 버퍼층 상부로 격벽을 형성하는 단계와; 상기 제 1 및 제 2 버퍼층의 상부로 연결패턴을 형성하는 단계와; 상기 각 화소영역 내의 상기 제 1 전극 상부로 유기발광층을 형성하는 단계와; 상기 유기발광층 상부에 상기 격벽에 의해 각 화소영역 별로 분리되는 제 2 전극을 형성하는 단계를 포함하는 듀얼패널 타입유기전계발광소자 제조방법을 제공한다.

- [0023] 이때, 상기 제 1 전극은 스퍼터링(sputtering) 방식을 통해 형성하며, 상기 이물은 상기 제 1 전극 형성 공정 중 발생하며, 상기 건식식각은 이온빔 식각(ion beam etching), RF(radio frequency) 스퍼터 식각, 플라즈마 (plasma) 식각 또는 반응 이온 식각 중 선택된 어느 하나로 식각한다.

- [0024] 또한, 상기 제 1 전극을 형성하기 전에, 상기 제 1 기판 상의 상기 각 화소영역의 경계에 저저항 금속물질로 이루어진 보조전극을 형성하는 단계를 포함한다.

- [0025] 또한, 본 발명은 서로 마주대하는 제 1 및 2 기판과; 상기 제 2 기판과 마주보는 상기 제 1 기판의 일면 형성된 구동 박막트랜지스타와; 상기 제 1 기판 상에 형성되며, 상기 구동 박막트랜지스타와 연결되는 연결전극과; 상기 제 1 기판과 마주보는 상기 제 2 기판의 일면에 형성된 제 1 전극과; 상기 제 1 전극 상부에 화면을 구현하는 최소단위 영역인 화소영역별 경계부에 형성되며, 질화실리콘(SiNx)과 이의 상부에 산화실리콘(SiO2)으로 이루어진 버퍼층과; 상기 버퍼층의 일측에 일정두께로 형성된 격벽과; 상기 격벽의 일측에 형성되며, 상기 연결전 극과 연결되는 연결패턴과; 상기 연결패턴을 포함하는 상기 제 2 기판의 전면에 상기 격벽에 의해 상기 화소영역별로 분리된 구조로 차례대로 형성된 유기발광층 및 제 2 전극을 포함하는 유기전계발광소자를 제공한다.

[0026]

#### 京과

- [0027] 위에 상술한 바와 같이, 본 발명에 따라 본 발명의 특징은 버퍼층을 질화실리콘(SiNx)과 산화실리콘(Si02)으로 이루어진 이중층으로 형성하여, 산화실리콘(Si02) 패터닝 과정의 BOE(buffered oxide etching) 습식식각 공정에서 제 1 전극 상에 부착된 이물을 제거함으로써, 기존의 OLED는 제 1 전극 상에 부착된 이물에 의해 제 1 전극과 제 2 전극이 서로 접촉되어 통전되는 단락(short)됨으로써 발생했던 암점으로 인한 화소불량을 방지할 수 있는 효과가 있다.

- [0028] 이로 인하여, OLED의 전반적인 휘도 및 화상 특성을 균일하게 할 수 있는 효과가 있다.

#### 발명의 실시를 위한 구체적인 내용

- [0029] 이하, 도면을 참조하여 본 발명에 따른 실시예를 상세히 설명한다.

- [0030] 한편, 설명에 앞서 OLED는 유기발광층을 통해 발광된 빛의 투과방향에 따라 상부 발광방식(top emission type) 과 하부 발광방식(bottom emission type)으로 나뉘게 되는데, 하부 발광방식은 안정성 및 공정이 자유도가 높은 반면 개구율의 제한이 있어 고해상도 제품에 적용하기 어려운 문제점이 있다.

- [0031] 이에, 최근에는 고개구율 및 고해상도를 갖는 상부 발광방식에 대한 연구가 활발하게 진행되고 있으나, 상부 발광방식은 유기발광층 상부에 통상적으로 음극(cathode)이 위치함에 따라 재료 선택폭이 좁아 투과도가 제한되어 광효율이 저하되는 문제점이 있다.

- [0032] 특히, 이러한 OLED는 구동 박막트랜지스터 등이 형성되는 기판 상에 제 1 전극 및 유기발광층과 제 2 전극으로 구성되는 유기전계발광 다이오드를 동시에 형성함에 따라 어레이소자 또는 유기전계발광 다이오드 중 어느 한쪽에서 불량이 발생되면 최종 완성품인 OLED는 불량이 되므로 생산수율이 저하되는 문제가 있다.

- [0033] 이에 본 발명에서는 최근에 제시된 어레이소자와 유기전계발광 다이오드를 각각 별도의 기판 상에 형성한 뒤, 연결패턴(contact spacer)을 통해 이 두 기판이 서로 전기적으로 연결되도록 합착하여, 각 기판 제조 시 발생하는 불량을 독립적으로 관리할 수 있는 듀얼패널 타입 OLED를 실시예로 설명하도록 하겠다.

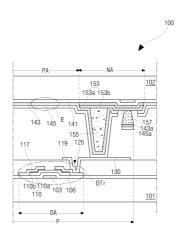

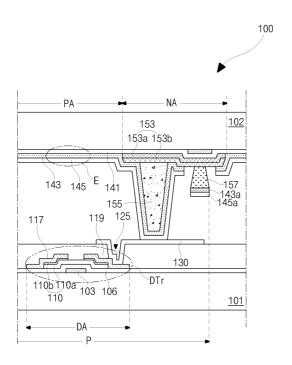

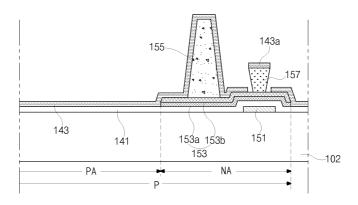

- [0034] 도 2는 본 발명의 실시예에 따른 상부 발광방식 OLED의 일부를 도시한 것으로써 구동 박막트랜지스터 및 유기전 계발광 다이오드를 포함하는 하나의 화소에 대한 단면도이다.

- [0035] 이때 설명의 편의를 위해 구동 박막트랜지스터(DTr)가 형성되는 영역을 구동영역(DA) 그리고 연결패턴가 형성되는 영역을 비화소영역(NP), 유기전계발광 다이오드(E)가 형성되는 영역을 발광영역(PA)이라 정의한다. 그리고 도면에는 나타내지 않았지만 스위칭 박막트랜지스터가 형성되는 영역을 스위칭 영역이라 정의한다.

- [0036] 도시한 바와 같이, OLED(100)는 구동 박막트랜지스터(DTr) 및 스위칭 박막트랜지스터(미도시)가 형성된 제 1 기 판(101)과 유기전계발광 다이오드(E)가 형성된 제 2 기판(102)이 서로 마주하며 대향하고 있으며, 제 1 및 제 2 기판(101, 102)은 서로 이격되어 이의 가장자리부를 실패턴(seal pattern : 160)을 통해 봉지되어 합착된다.

- [0037] 여기서, 제 1 기판(101) 상에는 게이트배선과 데이터배선(115)이 교차하여 화소영역(P)을 정의하며 형성되어 있다.

- [0038] 또한, 이들 두 배선(미도시, 115)의 교차지점에는 스위칭 소자인 스위칭 박막트랜지스터(미도시)가 형성되어 있으며, 스위칭 박막트랜지스터(미도시)와 전기적으로 연결되는 게이트전극(103)과 게이트절연막(106)과 반도체층 (110)과 소스 및 드레인전극(117, 119)을 갖는 구동 박막트랜지스터(DTr)가 형성되어 있다.

- [0039] 이때, 반도체층(110)은 순수 비정질 실리콘의 액티브층(110a)과 불순물을 포함하는 비정질 실리콘의 오믹콘택층 (110b)으로 구성되며, 이때, 스위칭 및 구동 박막트랜지스터(미도시, DTr)는 도면에서는 순수 및 불순물의 비정 질질실리콘(110a, 110b)으로 이루어진 보텀 케이트(bottom gate) 타입을 예로써 보이고 있으며, 이의 변형예로 써 폴리실리콘 반도체층을 포함하여 탑 게이트(top gate) 타입으로 형성될 수도 있다.

- [0040] 그리고, 스위칭 및 구동 박막트랜지스터(미도시, DTr)의 상부로 구동 박막트랜지스터(DTr)의 드레인전극(119)을 노출시키는 드레인콘택홀(125)을 갖는 보호층(120)이 형성되어 있다.

- [0041] 다음으로, 보호층(120) 상부에는 드레인콘택홀(125)을 통해 드레인전극(119)과 접촉하는 연결전극(130)이 각 화

소영역(P) 별로 형성되어 있다.

- [0042] 한편, 제 1 기판(101)과 서로 마주하며 대향하고 있는 제 2 기판(102) 상의 각 비화소영역(NP)에는 보조전극 (151)이 형성되어 있으며, 보조전극(151)을 포함하는 제 2 기판(102)의 전면에 유기전계발광 다이오드(E)를 구성하는 일 구성요소로써 양극(anode)을 이루는 제 1 전극(141)이 형성되어 있다.

- [0043] 여기서, 제 1 전극(141)은 일함수 값이 비교적 높은 물질인 인듐-틴-옥사이드(ITO)로 이루어질 수 있다.

- [0044] 그리고, 보조전극(151)이 형성된 제 1 전극(141) 상부 비화소영역(NP)에는 질화실리콘(SiNx)과 산화실리콘(Si02)으로 이루어지는 이중층의 제 1 및 제 2 버퍼층(153)이 형성되어 있으며, 제 1 기판(101)을 향하는 이중층의 제 1 및 제 2 버퍼층(153)의 상부에는 유기전계발광 다이오드(E)에 전류를 공급하기 위하여 각 화소영역(P) 별로 제 1 기판(101) 상에 형성된 구동 박막트랜지스터(DTr)와 전기적으로 연결되는 기둥 형상의 연결패턴(155)이 형성되어 있다.

- [0045] 그리고, 연결패턴(155)이 형성된 제 1 및 제 2 버퍼충(153)의 일측에는 각 화소영역(P) 별 경계부를 두르는 위치에 일정 두께를 갖는 격벽(157)이 형성된다.

- [0046] 그리고, 이러한 연결패턴(155) 및 격벽(157)을 포함하여 기판(102)의 전면에 유기발광층(143)과 제 2 전극(14 5)이 차례대로 형성되어 있다.

- [0047] 제 1, 2 전극(141, 145)과 그 사이에 형성된 유기발광층(143)은 유기전계발광 다이오드(E)를 이루게 된다.

- [0048] 이때, 유기전계발광 다이오드(E)는 제 1 전극(141)을 인듐-틴-옥사이드(ITO)와 같은 광투과성을 가지는 도전성 물질로 형성하므로, 유기발광층(143)에서 발광된 빛은 제 1 전극(141)을 통해 방출하는 상부발광 방식으로 구동된다.

- [0049] 따라서, 유기발광층(143)으로부터 발광되는 빛이 제 1 전극(141)을 투과하여 전면으로 조사되게 되는데, 이때 제 1 전극(141)을 유기발광층(143) 상부에 형성하는 과정에서 유기발광층(143)의 손상을 최소화하기 위하여 제 1 전극(141)은 비저항이 높아지게 되어, 화소영역(P)의 위치별로 동일한 전압이 인가되는 것이 아니라 전압강하 (IR drop)에 의해 전압이 입력되는 부위에서 가까운 영역과 먼 영역에서 전압 차이가 발생하게 된다.

- [0050] 이에, 휘도나 화상 특성의 불균일을 발생시키게 되며 소비전력을 상승시키는 문제점을 야기하게 되는데, 본 발명은 각 화소영역(P) 별로 제 1 전극(141)이 보조전극(151)과 전기적으로 연결됨으로써 제 1 전극(141)의 전압강하를 방지할 수 있다.

- [0051] 유기발광층(143)과 제 2 전극(145)은 격벽(157)에 의해 각 화소영역(P) 별로 분리된 구조를 가지며, 유기발광층 (143)은 각 화소영역(P) 별로 적(R), 녹(G), 청(B)색을 발광하는 물질로써 적, 녹, 청색의 발광패턴으로 이루어 진다.

- [0052] 여기서, 유기발광층(143)은 발광물질로 이루어진 단일층으로 구성될 수도 있으며, 발광 효율을 높이기 위해 정 공주입층(hole injection layer), 정공수송층(hole transporting layer), 발광층(emitting layer), 전자수송 층(electron transporting layer) 및 전자주입층(electron injection layer)의 다중층으로 구성될 수도 있다.

- [0053] 그리고, 제 2 전극(145)은 음극(cathode)의 역할을 하기 위해 비교적 일함수 값이 낮은 금속물질인 알루미늄 (Al) 또는 알루미늄합금(AlNd)으로 이루어진다.

- [0054] 전술한 본 발명의 실시예에 따른 OLED(100)는 스위칭 및 구동박막트랜지스터(미도시, DTr)를 갖는 제 1 기판 (101)과 유기전계발광 다이오드(E)를 갖는 제 2 기판(102)을 각각 따로 형성한 후, 이들 두 기판(101, 102)을 합착하여 OLED(100)를 완성한다.

- [0055] 이때, 제 2 기판(102) 상에 형성된 연결패턴(155)의 끝단부에 대응하여 형성된 제 2 전극(145)이 제 1 기판 (101) 상의 연결전극(130)과 접촉하게 됨으로써, 결과적으로 제 2 기판(102) 상에 형성된 유기전계발광 다이오 드(E)와 제 1 기판(101) 상에 형성된 구동 박막트랜지스터(DTr)가 전기적으로 연결된다.

- [0056] 따라서, 이러한 OLED(100)는 선택된 색 신호에 따라 제 1 전극(141)과 제 2 전극(145)으로 소정의 전압이 인가되면, 제 1 전극(141)으로부터 주입된 정공과 제 2 전극(145)으로부터 인가된 전자가 유기발광층(143)으로 수송되어 엑시톤(exciton)을 이루고, 이러한 엑시톤이 여기상태에서 기저상태로 천이 될 때 빛이 발생되어 가시광선의 형태로 방출된다.

- [0057] 이때, 발광된 빛은 투명한 제 1 전극(141)을 통과하여 외부로 나가게 되므로, OLED(100)는 임의의 화상을 구현

하게 된다.

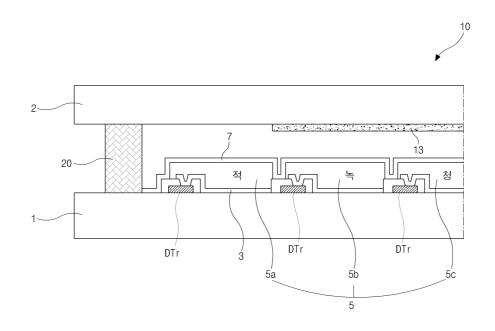

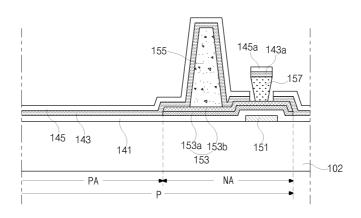

- [0058] 도 3은 도 2의 일부를 확대 도시한 단면도이다.

- [0059] 도시한 바와 같이, 제 1 기판(101) 상에는 게이트전극(103)과 게이트 절연막(106)과 반도체층(110)과 소스 및 드레인전극(117, 119)을 갖는 구동 박막트랜지스터(DTr)가 형성되어 있으며, 구동 박막트랜지스터(DTr)의 상부에는 드레인콘택홀(125)을 통해 드레인전극(119)을 노출시키는 보호층(120)이 형성되어 있다.

- [0060] 그리고, 보호층(120) 상부에는 드레인콘택홀(125)을 통해 드레인전극(119)과 접촉하는 연결전극(130)이 각 화소 영역(P) 별로 형성되어 있다.

- [0061] 제 1 기판(101)과 서로 마주하며 대향하고 있는 제 2 기판(102) 상에는 보조전극(151)과 유기전계발광 다이오드 (E)를 구성하는 제 1 전극(141)이 형성되어 있으며, 제 2 기판(102)의 비화소영역(NP)에는 질화실리콘(SiNx)과 산화실리콘(Si02)으로 이루어지는 제 1 및 제 2 버퍼충(153)과 일정 두께를 갖는 기둥 형상의 연결패턴(155)이 형성되어 있다.

- [0062] 연결패턴(155)은 제 1 및 제 2 버퍼층(153)에 근접한 단면적이 크고 멀어질수록 단면적이 감소하는 형상으로 즉 테이퍼(taper) 구조로 이루어져, 제 2 기판(102) 상에 형성된 제 2 전극(145)은 연결패턴(155)에 의해 제 1 기판(101)에 형성된 연결전극(130)과 전기적으로 접촉하게 된다.

- [0063] 그리고, 연결패턴(155)이 형성된 제 1 및 제 2 버퍼충(153)의 일측에는 각 화소영역(P) 별 경계부를 두르는 위치에 일정 두께를 갖는 격벽(157)을 형성한다.

- [0064] 격벽은 제 1 및 제 2 버퍼충(153)과 가까운 쪽의 단면적이 작고 멀어질수록 그 단면적이 증가하는 구조로써, 즉, 단면이 제 2 기판(102)의 내측면을 기준으로 역테이퍼(inversed taper) 구조로 이루어진다.

- [0065] 그리고, 이러한 연결패턴(155) 및 격벽(157)을 포함하여 기판(102)의 전면에 유기발광층(143)과 제 2 전극(14 5)이 차례대로 형성되어 있다.

- [0066] 제 1, 2 전극(141, 145)과 그 사이에 형성된 유기발광층(143)은 유기전계발광 다이오드(E)를 이루게 된다.

- [0067] 이때, 유기발광층(143)과 제 2 전극(145)은 별도의 마스크 공정 없이 격벽(157)에 의해 각 화소영역(P) 별로 자동 분리된 구조로 형성되므로, 격벽(157)의 상부에는 유기발광물질층(143a) 및 제 2 전극물질층(145a)이 차례대로 남겨질 수 있다.

- [0068] 한편, 이러한 본 발명의 OLED(100)는 유기전계발광 다이오드(E)의 제 1 전극(141)과 제 2 전극(145)이 단락됨으로써 발생되는 암점(dark pixel)이 나타나는 화소불량을 감소시킬 수 있다.

- [0069] 이는, 질화실리콘(SiNx)과 산화실리콘(Si02)의 이중층으로 이루어지는 제 1 및 제 2 버퍼층(153)의 형성과정 중, 제 1 전극(141) 상에 부착된 이물(미도시)을 별도의 추가 공정없이 제거할 수 있기 때문이다.

- [0070] 이로 인하여, 휘도나 화상 특성을 향상시킬 수 있다.

- [0071] 이는, 결국 휘도나 화상 특성의 불균일을 발생시키게 된다.

- [0072] 이에 대하여 아래 본 발명의 실시예에 따른 OLED(100)의 제조방법을 통해 자세히 설명하도록 하겠다.

- [0073] 여기서, 본 발명에 따른 OLED(100)는 유기전계발광 다이오드(E)가 형성된 제 2 기판(102 : 이하, 유기전계발광 다이오드 기판 이라 함)에 구조적 특징이 있으므로, 제 2 기판(102)의 제조방법에 대해서만 설명하도록 하겠다.

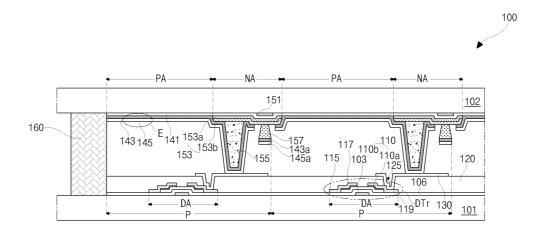

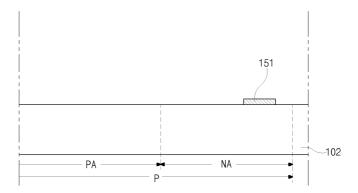

- [0074] 도 4a ~ 4i는 본 발명의 실시예에 따른 유기전계발광 다이오드 기판의 제조 단계별 단면도이다.

- [0075] 먼저, 도 4a에 도시한 바와 같이 기판(102) 상에 몰리브덴(Mo), 티타늄(Ti), 은-인듐-틴-옥사이드(Ag-ITO)물질과 같은 금속물질 중에서 선택되는 하나의 물질을 증착하고, 이를 포토레지스트의 도포, 노광, 현상 및 식각을 포함하는 마스크 공정을 통해 패터닝함으로써, 각 화소영역(P)의 경계에 보조전극(151)을 형성한다.

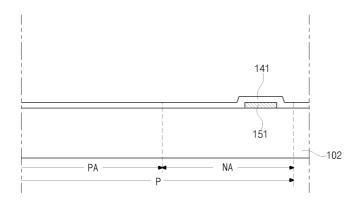

- [0076] 다음으로 도 4b에 도시한 바와 같이 보조전극(151)을 포함하는 기판(102)의 전면에 제 1 전극(141)을 형성하는 데, 제 1 전극(141)은 투광성을 가지는 전도성 물질에서 선택되는데, 일예로 제 1 전극(141)이 양극(anode)으로 이루어질 경우 투광성을 가짐과 동시에 일함수 값이 비교적 높은 물질인 인듐-틴-옥사이드(ITO)로 이루어질 수 있다.

- [0077] 이때, 제 1 전극은 스퍼터링(sputtering) 방식을 통해 증착한다.

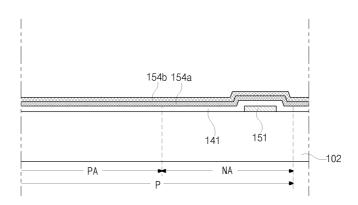

- [0078] 다음으로 도 4c에 도시한 바와 같이, 보조전극(151)이 형성된 제 1 전극(141)의 상부에 산화실리콘(Si02)물질 (154a)과 질화실리콘(SiNx)물질(154b)을 순차적으로 증착한다.

- [0079] 이때, 산화실리콘(Si02)물질(154a)과 질화실리콘(SiNx)물질(153b)은 각각 플라즈마 화학기상증착(PECVD) 공정을 통해 증착한다.

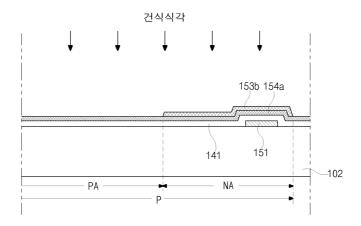

- [0080] 다음으로, 도 4d에 도시한 바와 같이, 질화실리콘물질(154b) 상에 포토레지스트 도포, 노광, 현상 및 식각을 포함하는 마스크 공정을 통해 패터닝함으로써, 제 1 버퍼층(153a)을 형성한다.

- [0081] 이때, 질화실리콘물질(154b)은 건식식각을 통해 식각하는데, 이온빔 식각(ion beam etching), RF(radio frequency) 스퍼터 식각, 플라즈마(plasma) 식각 또는 반응 이온 식각 중 선택되는 어느 하나로 수행한다.

- [0082] 반응 이온 식각을 이용할 경우, CF<sub>4</sub>, CF<sub>4</sub>/O<sub>2</sub>, C<sub>2</sub>F<sub>6</sub> 또는 C<sub>2</sub>F<sub>8</sub> 등의 식각 가스를 이용하여 식각한다.

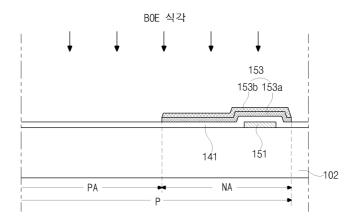

- [0083] 다음으로, 도 4e에 도시한 바와 같이 산화실리콘물질(154a)을 패터닝하여 제 2 버퍼층(153a)을 형성하는데, 이 때, 산화실리콘물질(154a)은 제 1 버퍼층(153b)을 마스크로 패터닝한다.

- [0084] 여기서, 산화실리콘물질(154a)은 습식식각을 통해 식각하는데, BOE(buffered oxide etching)를 이용하여 식각한 다.

- [0085] 이때, 이러한 습식식각을 통해 제 1 전극(141) 상에 부착된 이물(미도시)을 제거할 수 있다.

- [0086] 즉, 제 1 전극(141) 상에 부착된 이물(미도시)은 제 1 전극(141) 형성 공정 시 발생된 이물(미도시)로써 제 1 전극(141) 형성물질과 동일한 전도성 물질로 이루어지는데, 이러한 전도성 물질로 이루어진 이물(미도시)은 산화실리콘물질(154a)을 습식식각하는 과정에서 동시에 제거하게 된다.

- [0087] 특히, 제 1 전극(141)의 표면이 평탄화되어, 제 1 전극(141)의 표면거칠기(roughness)를 낮출 수 있어, 차후 제 1 전극(141) 상에 증착되는 유기발광층(도 3의 143)의 증착 안정성을 향상시킬 수 있고, 더 나아가 본 발명의 유기전계발광 다이오드(도 3의 E)의 동작 특성을 향상시키게 된다.

- [0088] 이때, 제 1 및 제 2 버퍼층(153)은 보조전극(151)을 완전히 덮는 형태로 형성한다.

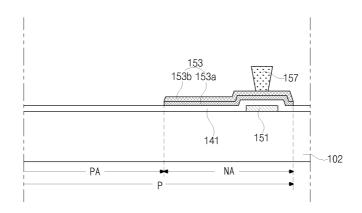

- [0089] 다음으로 도 4f에 도시한 바와 같이, 제 1 및 제 2 버퍼층(153) 상부에 감광성의 유기절연물질을 도포하고 이를 패터닝함으로써, 기판(102)을 기준으로 이에 수직하게 절단하였을 경우 그 단면 구조가제 1 및 제 2 버퍼층 (153)과 가까운 쪽의 단면적이 작고 멀어질수록 그 단면적이 증가하는 구조로써, 즉, 단면이 제 2 기판(102)의 내측면을 기준으로 역테이퍼(inversed taper) 구조의 격벽(157)을 형성한다.

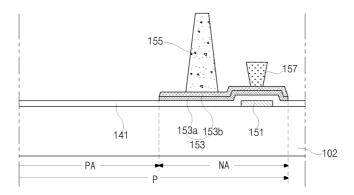

- [0090] 다음으로 도 4g에 도시한 바와 같이, 제 1 및 제 2 버퍼충(153) 상부에 유기절연물질을 중착하고 이를 패터닝함으로써, 제 1 및 제 2 버퍼충(153)에 근접한 밑면이 넓고 위로 갈수록 폭이 좁아지는 형상의 연결패턴(155)을 형성한다.

- [0091] 다음으로 도 4h에 도시한 바와 같이, 격벽(157)이 형성된 상태에서 연결패턴(155) 상부로 유기발광물질을 도포 또는 증착함으로써, 유기발광층(143)을 형성한다.

- [0092] 이때, 유기발광물질은 노즐코팅 장치, 디스펜싱 장치 또는 잉크젯 장치를 이용하여 코팅 또는 분사함으로써, 각화소영역(P) 별로 각각 분리된 유기발광층(143)을 형성할 수도 있으며, 마스크를 이용하여 유기발광물질을 열증착 함으로써 각화소영역(P) 별로 유기발광층(143)을 형성할 수도 있다.

- [0093] 다음으로 도 4i에 도시한 바와 같이, 유기발광층(143) 상부에 일함수 값이 비교적 작은 금속물질인 알루미늄 (Al) 또는 알루미늄합금(AlNd)을 증착함으로써, 격벽(157)에 의해 자동으로 각 화소영역(P) 별로 분리된 형태의 제 2 전극(145)을 형성한다.

- [0094] 이에, 본 발명에 따른 유기전계발광 다이오드 기판을 완성하게 된다.

- [0095] 이후, 도면에 도시하지는 않았지만 전술한 공정을 통해 완성된 유기전계발광 다이오드 기판과 일반적인 공정을 통해 완성된 스위칭 및 구동 박막트랜지스터를 포함하는 제 1 기판 중 어느 하나의 기판의 테두리를 따라 씰패턴을 형성한다.

- [0096] 다음으로 이들 두 기판을 서로 대향시킨 후, 연결패턴(155) 상에 형성된 제 2 전극(145)과 연결전극(도 3의 130)이 서로 맞닿도록 한 상태에서 진공 또는 불활성 기체인 질소(N2) 분위기에서 합착함으로써 상부 발광방식 OLED(도 2의 100)를 완성한다.

- [0097] 이때, 실패턴(미도시)의 내측으로 흡습제(미도시)가 형성되어 있는데, 흡습제(미도시)는 외부의 수분을 차단하기 위하여 구비되는데, 이는 유기발광층(143)이 산소 및 수분에 노출되면 쉽게 열화되는 특성 때문에 이를 방지하기 위함이다.

- [0098] 도 5는 본 발명의 실시예에 따른 OLED에 역바이어스(reverse bias) 인가 시 암점에 의한 화소불량이 발생된 개수를 나타낸 그래프이다.

- [0099] 그래프를 참조하면, 기존의 OLED(도 1의 10)는 제 1 전극(141) 상에 부착된 이물(미도시)에 의해 제 1 전극 (141)과 제 2 전극(143)이 서로 접촉되어 통전되는 단락(short)됨으로써 암점이 6개 이상 발견되었었으나, 본 발명에 따른 OLED(도 2의 100)에서는 암점이 1개가 발견되는 것을 알 수 있다.

- [0100] 이로 인하여, 본 발명과 같이 버퍼충(153)을 질화실리콘(SiNx)과 산화실리콘(Si02)으로 형성하여, 산화실리콘 패터닝 과정의 습식식각 공정에서 제 1 전극(141) 상에 부착된 이물(미도시)을 제거함으로써, 암점을 줄일 수 있는 것을 확인할 수 있다.

- [0101] 이로 인하여, OLED(도 2의 100)의 전반적인 휘도 및 화상 특성을 균일하게 할 수 있다.

- [0102] 본 발명은 상기 실시예로 한정되지 않고, 본 발명의 취지를 벗어나지 않는 한도내에서 다양하게 변경하여 실시 할 수 있다.

#### 도면의 간단한 설명

- [0103] 도 1은 일반적인 액티브 매트릭스형 OLED의 단면을 개략적으로 도시한 도면.

- [0104] 도 2는 본 발명의 실시예에 따른 상부 발광방식 OLED의 일부를 도시한 단면도.

- [0105] 도 3은 도 2의 일부를 확대 도시한 단면도이다.

- [0106] 도 4a ~ 4i는 본 발명의 실시예에 따른 유기전계발광 다이오드 기판의 제조 단계별 단면도.

#### 도면

#### 도면1

## 도면2

### 도면3

## 도면4a

## 도면4b

## 도면4c

## *도면4d*

## *도면4e*

## *도면4f*

## 도면4g

## 도면4h

## 도면4i

#### 摘要(译)

双面板型有机电致发光器件技术领域本发明涉及双面板型有机电致发光器件,更具体地涉及顶部发光有机电致发光器件。 本发明的一个特征在于缓冲层由双层氮化硅(SiNx)和氧化硅(SiO2)形成,并且在氧化硅的BOE(缓冲氧化物蚀刻)湿法蚀刻工艺中沉积在第一电极上。删除异物。 因此,在传统的OLED中,可以防止由于由于附着在第一电极上的异物而使第一电极和第二电极彼此接触的短路引起的暗点引起的像素缺陷,可以使整体亮度和图像特性均匀。