(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0009219

(43) 공개일자 2010년01월27일

(51) Int. Cl.

G09G 3/30 (2006.01) G09G 3/32 (2006.01)

G09G 3/20 (2006.01) H01L 51/50 (2006.01)

(21) 출원번호 10-2008-0070002

(22) 출원일자 2008년07월18일

심사청구일자 2008년07월18일

(71) 출원인

삼성모바일디스플레이주식회사

경기도 용인시 기흥구 농서동 산24번지

(72) 발명자

곽원규

충청남도 천안시 성성동 508번지 삼성SDI(주)

(74) 대리인

신영무

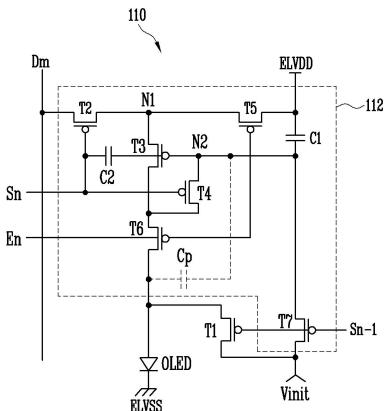

전체 청구항 수 : 총 9 항

(54) 화소 및 이를 이용한 유기전계발광 표시장치

**(57) 요 약**

본 발명은, 응답특성이 개선되고, 균일한 화질의 영상을 표시하는 화소에 관한 것이다.

본 발명의 화소는, 제1 전원과 제2 전원 사이에 접속되는 유기발광다이오드와, 상기 제1 전원과 상기 유기발광다이오드 사이에 접속되어 상기 유기발광다이오드로 구동전류를 공급하는 화소회로와, 이전 주사선으로 이전 주사신호가 공급되는 제1 기간 동안 상기 유기발광다이오드의 애노드 전극으로 리셋전압을 공급하는 제1 트랜지스터를 포함한다.

**대 표 도** - 도2

## 특허청구의 범위

### 청구항 1

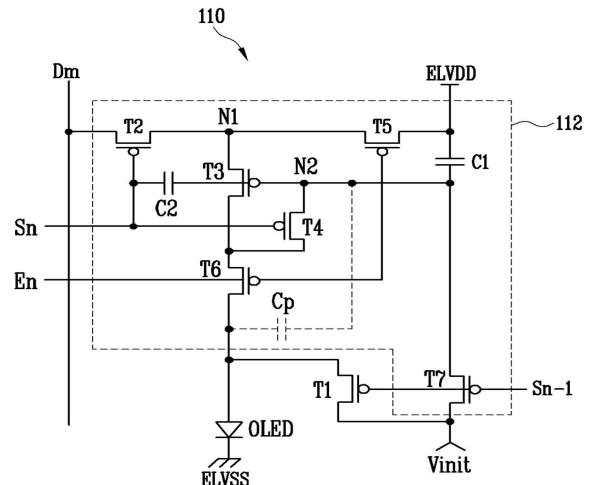

제1 전원과 제2 전원 사이에 접속되는 유기발광다이오드와,

상기 제1 전원과 상기 유기발광다이오드 사이에 접속되어 상기 유기발광다이오드로 구동전류를 공급하는 화소회로와,

이전 주사선으로 이전 주사신호가 공급되는 제1 기간 동안 상기 유기발광다이오드의 애노드 전극으로 리셋전압을 공급하는 제1 트랜지스터를 포함하는 화소.

### 청구항 2

제1항에 있어서,

상기 리셋전압은 별도의 초기화전원의 전압으로 설정되며,

상기 제1 트랜지스터는 상기 유기발광다이오드의 애노드 전극과 상기 초기화전원 사이에 접속되고, 상기 제1 트랜지스터의 게이트 전극은 상기 이전 주사선에 접속되는 화소.

### 청구항 3

제1항에 있어서,

상기 리셋전압은 상기 제2 전원의 전압으로 설정되며,

상기 제1 트랜지스터는 상기 유기발광다이오드의 애노드 전극과 상기 제2 전원 사이에 접속되고, 상기 제1 트랜지스터의 게이트 전극은 상기 이전 주사선에 접속되는 화소.

### 청구항 4

제1항에 있어서,

상기 화소회로는,

데이터선과 제1 노드 사이에 접속되며, 게이트 전극이 현재 주사선에 접속되는 제2 트랜지스터와,

상기 제1 노드와 상기 유기발광다이오드 사이에 접속되며, 게이트 전극이 제2 노드에 접속되는 제3 트랜지스터와,

상기 제2 노드와 상기 제1 전원 사이에 접속되는 제1 커패시터를 포함하는 화소.

### 청구항 5

제4항에 있어서,

상기 화소회로는,

상기 제3 트랜지스터의 게이트 전극과 드레인 전극 사이에 접속되며, 게이트 전극이 상기 현재 주사선에 접속되는 제4 트랜지스터와,

상기 제1 전원과 상기 제1 노드 사이에 접속되며, 게이트 전극이 발광 제어선에 접속되는 제5 트랜지스터와,

상기 제3 트랜지스터와 상기 유기발광다이오드 사이에 접속되며, 게이트 전극이 상기 발광제어선에 접속되는 제6 트랜지스터와,

상기 제2 노드와 초기화 전원 사이에 접속되며, 게이트 전극이 상기 이전 주사선에 접속되는 제7 트랜지스터를 더 포함하는 화소.

### 청구항 6

제4항에 있어서,

상기 화소회로는, 상기 제2 노드와 상기 현재 주사선 사이에 접속되는 제2 커패시터를 더 포함하는 화소.

## 청구항 7

주사선들, 발광 제어선들 및 데이터선들의 교차부에 배치되는 다수의 화소들을 포함하며,

상기 화소들 각각은,

제1 전원과 제2 전원 사이에 접속되는 유기발광다이오드와,

상기 제1 전원과 상기 유기발광다이오드 사이에 접속되어 상기 유기발광다이오드로 구동전류를 공급하는 화소회로와,

이전 주사선으로 이전 주사신호가 공급되는 제1 기간 동안 상기 유기발광다이오드의 애노드 전극으로 리셋전압을 공급하는 제1 트랜지스터를 포함하는 유기전계발광 표시장치.

## 청구항 8

제7항에 있어서,

상기 리셋전압은 별도의 초기화전원의 전압으로 설정되며,

상기 제1 트랜지스터는 상기 유기발광다이오드의 애노드 전극과 상기 초기화전원 사이에 접속되고, 상기 제1 트랜지스터의 게이트 전극은 상기 이전 주사선에 접속되는 유기전계발광 표시장치.

## 청구항 9

제7항에 있어서,

상기 리셋전압은 상기 제2 전원의 전압으로 설정되며,

상기 제1 트랜지스터는 상기 유기발광다이오드의 애노드 전극과 상기 제2 전원 사이에 접속되고, 상기 제1 트랜지스터의 게이트 전극은 상기 이전 주사선에 접속되는 유기전계발광 표시장치.

## 명세서

### 발명의 상세한 설명

#### 기술 분야

<1> 본 발명은 화소 및 이를 이용한 유기전계발광 표시장치에 관한 것으로, 특히 응답특성이 개선되고, 균일한 화질의 영상을 표시하는 화소 및 이를 이용한 유기전계발광 표시장치에 관한 것이다.

#### 배경기술

<2> 최근, 음극선관과 비교하여 무게가 가볍고 부피가 작은 각종 평판 표시장치(Flat Panel Display Device)들이 개발되고 있다.

<3> 평판 표시장치들 중 특히 유기전계발광 표시장치(Organic Light Emitting Display Device)는 자발광소자인 유기발광다이오드를 이용하여 영상을 표시함으로써, 휴대 및 색순도가 뛰어나 차세대 표시장치로 주목받고 있다.

<4> 이와 같은 유기전계발광 표시장치는 유기발광다이오드를 구동하는 방식에 따라, 패시브 매트릭스형 유기전계발광 표시장치(PMOLED)와, 액티브 매트릭스형 유기전계발광 표시장치(AMOLED)로 나뉜다.

<5> AMOLED는 주사선들 및 데이터선들의 교차부에 위치된 다수의 화소들을 포함한다. 그리고, 각 화소는 유기발광다이오드와, 이를 구동하기 위한 화소회로를 포함한다. 여기서, 화소회로는 통상적으로 스위칭 트랜지스터, 드라이빙 트랜지스터 및 스토리지 커패시터를 포함하여 구성된다.

<6> 이와 같은 AMOLED는 소비전력이 작은 이점을 가져, 휴대용 표시장치 등에 유용하게 이용된다.

<7> 단, AMOLED의 경우, 화소의 구조상 발생하는 기생 커패시터에 의해 화소의 응답특성이 저하되고, 영상의 화질이 불균일해지는 문제점이 발생할 수 있다.

<8> 특히, 화소회로와 유기발광다이오드가 중첩되도록 배치되는 전면발광형 AMOLED의 경우, 스토리지 커패시터와 유기발광다이오드의 애노드 전극 간에 생성된 기생 커패시터에 의해 킥백 전압(kickback voltage)이 발생하게 된

다.

- <9> 이와 같은 킥백 전압은 드라이빙 트랜지스터의 게이트 전극이 접속되는 노드의 전압 변동을 야기시키며, 특히 이전 프레임에서의 계조에 따라 동일 계조를 표시하는 프레임 간에도 변동값의 편차가 발생해 화소의 응답특성을 저하시키고, 영상의 화질을 저하시킬 수 있다.

### 발명의 내용

#### 해결 하고자하는 과제

- <10> 따라서, 본 발명의 목적은 응답특성이 개선되고, 균일한 화질의 영상을 표시하는 화소와 이를 이용한 유기전계 발광 표시장치를 제공하는 것이다.

#### 과제 해결수단

- <11> 이와 같은 목적을 달성하기 위하여 본 발명의 제1 측면은 제1 전원과 제2 전원 사이에 접속되는 유기발광다이오드와, 상기 제1 전원과 상기 유기발광다이오드 사이에 접속되어 상기 유기발광다이오드로 구동전류를 공급하는 화소회로와, 이전 주사선으로 이전 주사신호가 공급되는 제1 기간 동안 상기 유기발광다이오드의 애노드 전극으로 리셋전압을 공급하는 제1 트랜지스터를 포함하는 화소를 제공한다.

- <12> 여기서, 상기 리셋전압은 별도의 초기화전원의 전압으로 설정되며, 상기 제1 트랜지스터는 상기 유기발광다이오드의 애노드 전극과 상기 초기화전원 사이에 접속되고, 상기 제1 트랜지스터의 게이트 전극은 상기 이전 주사선에 접속될 수 있다.

- <13> 또는, 상기 리셋전압은 상기 제2 전원의 전압으로 설정되며, 상기 제1 트랜지스터는 상기 유기발광다이오드의 애노드 전극과 상기 제2 전원 사이에 접속되고, 상기 제1 트랜지스터의 게이트 전극은 상기 이전 주사선에 접속될 수 있다.

- <14> 또한, 상기 화소회로는, 데이터선과 제1 노드 사이에 접속되며 게이트 전극이 현재 주사선에 접속되는 제2 트랜지스터와, 상기 제1 노드와 상기 유기발광다이오드 사이에 접속되며 게이트 전극이 제2 노드에 접속되는 제3 트랜지스터와, 상기 제2 노드와 상기 제1 전원 사이에 접속되는 제1 커패시터와, 상기 제3 트랜지스터의 게이트 전극과 드레인 전극 사이에 접속되며 게이트 전극이 상기 현재 주사선에 접속되는 제4 트랜지스터와, 상기 제1 전원과 상기 제1 노드 사이에 접속되며 게이트 전극이 발광 제어선에 접속되는 제5 트랜지스터와, 상기 제3 트랜지스터와 상기 유기발광다이오드 사이에 접속되며 게이트 전극이 상기 발광제어선에 접속되는 제6 트랜지스터와, 상기 제2 노드와 초기화 전원 사이에 접속되며 게이트 전극이 상기 이전 주사선에 접속되는 제7 트랜지스터와, 상기 제2 노드와 상기 현재 주사선 사이에 접속되는 제2 커패시터를 더 포함할 수 있다.

- <15> 본 발명의 제2 측면은, 주사선들, 발광 제어선들 및 데이터선들의 교차부에 배치되는 다수의 화소들을 포함하며, 상기 화소들 각각은, 제1 전원과 제2 전원 사이에 접속되는 유기발광다이오드와, 상기 제1 전원과 상기 유기발광다이오드 사이에 접속되어 상기 유기발광다이오드로 구동전류를 공급하는 화소회로와, 이전 주사선으로 이전 주사신호가 공급되는 제1 기간 동안 상기 유기발광다이오드의 애노드 전극으로 리셋전압을 공급하는 제1 트랜지스터를 포함하는 유기전계발광 표시장치를 제공한다.

#### 효과

- <16> 이와 같은 본 발명의 화소 및 이를 이용한 유기전계발광 표시장치에 따르면, 각 화소는 초기화 기간 동안 유기발광다이오드의 애노드 전극에 일정한 전압을 인가하는 리셋용 트랜지스터(제1 트랜지스터)를 구비한다. 이에 의해, 이전 프레임의 계조와 무관하게 각 계조에 대한 킥백 전압의 값이 균일하게 유지됨으로써, 화소의 응답특성을 개선하고 균일한 화질의 영상을 표시할 수 있다.

### 발명의 실시를 위한 구체적인 내용

- <17> 이하, 첨부된 도면을 참조하여 본 발명의 실시예를 보다 상세히 설명하기로 한다.

- <18> 도 1은 유기전계발광 표시장치의 구성을 개략적으로 도시한 블럭도이다.

- <19> 도 1을 참조하면, 본 발명의 실시예에 의한 유기전계발광 표시장치는 화소부(100), 주사 구동부(200) 및 데이터 구동부(300)를 포함한다.

- <20> 화소부(100)는 주사선들(S0 내지 Sn), 발광 제어선들(E1 내지 En) 및 데이터선들(D1 내지 Dm)의 교차부에 매트릭스 탑입으로 배치되는 다수의 화소들(110)을 포함한다.

- <21> 화소들(110)은 각각 자신이 위치된 행의 주사선(이하, 현재 주사선이라 함) 및 발광 제어선, 이전 행의 주사선(이하, 이전 주사선이라 함) 및 자신이 위치된 열의 데이터선에 접속된다. 예를 들어, 제i행 제j열에 위치된 화소(110)는 제i 주사선(Si), 제i 발광 제어선(Ei), 제i-1 주사선(Si-1) 및 제j 데이터선(Dj)에 접속된다.

- <22> 이와 같은 화소들(110) 각각은, 이전 주사선으로부터 주사신호가 공급되는 제1 기간 동안 초기화되고, 현재 주사선으로부터 주사신호가 공급되는 제2 기간 동안 데이터선으로부터 데이터 신호를 공급받는다. 그리고, 화소들(110)은 발광 제어선으로부터 공급되는 발광 제어신호의 전압레벨이 천이되어 각각의 화소들(110) 내에 구비된 유기발광다이오드로 전류가 공급되는 제3 기간 동안 데이터 신호에 대응하는 휘도로 발광함으로써 영상을 표시한다.

- <23> 한편, 화소부(100)는 외부(예컨대, 전원 공급부)로부터 제1 및 제2 전원(ELVDD, ELVSS)을 공급받는다. 이와 같은 제1 및 제2 전원(ELVDD, ELVSS)은 각각 하이레벨 전압원 및 로우레벨 전압원으로 작용하는 것으로, 화소들(110)의 구동전원으로 이용된다.

- <24> 주사 구동부(200)는 외부(예컨대, 타이밍 제어부)로부터 공급되는 주사 제어신호에 대응하여 주사신호 및 발광 제어신호를 생성한다. 주사 구동부(200)에서 생성된 주사신호 및 발광 제어신호는 각각 주사선들(S0 내지 Sn) 및 발광 제어선들(E1 내지 En)을 통해 화소들(110)로 순차적으로 공급된다.

- <25> 데이터 구동부(300)는 외부(예컨대, 타이밍 제어부)로부터 공급되는 데이터 및 데이터 제어신호에 대응하여 데이터 신호를 생성한다. 데이터 구동부(300)에서 생성된 데이터 신호는 데이터선들(D1 내지 Dm)을 통해 주사신호와 동기되도록 화소들(110)로 공급된다.

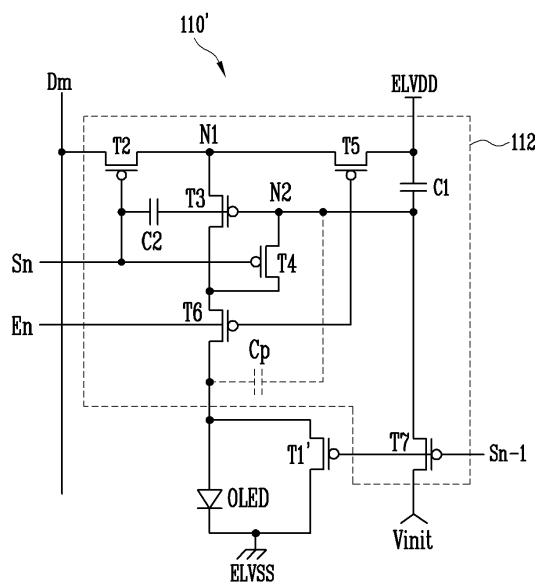

- <26> 도 2는 본 발명의 일 실시예에 의한 화소를 도시한 회로도로, 도 2에 도시된 화소는 도 1에 도시된 유기전계발광 표시장치 등에 적용될 수 있다. 편의상, 도 2에서는 제n행 및 제m열에 위치된 화소를 도시하기로 한다.

- <27> 도 2를 참조하면, 본 발명의 일 실시예에 의한 화소(110)는 제1 전원(ELVDD)과 제2 전원(ELVSS) 사이에 접속되는 유기발광다이오드(OLED)와, 이전 주사선(Sn-1)으로 이전 주사신호가 공급되는 기간 동안 유기발광다이오드(OLED)의 애노드 전극으로 리셋전압을 공급하는 제1 트랜지스터(T1)와, 제1 전원(ELVDD)과 유기발광다이오드(OLED) 사이에 접속되어 유기발광다이오드(OLED)로 구동전류를 공급하는 화소회로(112)를 포함한다.

- <28> 보다 구체적으로, 제1 트랜지스터(T1)는 유기발광다이오드(OLED)의 애노드 전극과 초기화전원(Vinit) 사이에 접속되며, 제1 트랜지스터(T1)의 게이트 전극은 이전 주사선(Sn-1)에 접속된다. 여기서, 초기화전원(Vinit)은 제1 및 제2 전원(ELVDD, ELVSS)과 상이한 별도의 전원으로 화소(110)를 초기화하기 위해 추가적으로 공급되는 전원이다.

- <29> 이와 같은 제1 트랜지스터(T1)는 이전 주사선(Sn-1)으로 이전 주사신호가 공급되는 기간 동안 턴-온되어, 유기발광다이오드(OLED)의 애노드 전극에 초기화전원(Vinit)의 전압을 공급한다.

- <30> 즉, 제1 트랜지스터(T1)는 화소(110)의 초기화 기간 동안 유기발광다이오드(OLED)의 애노드 전극에 일정한 리셋전압을 공급하기 위한 리셋용 트랜지스터로 구비되며, 본 실시예에서 리셋전압은 초기화전원(Vinit)의 전압으로 설정된다.

- <31> 화소회로(112)는 제2 내지 제7 트랜지스터(T2 내지 T7)와, 제1 내지 제2 커패시터(C1 내지 C2)를 포함한다.

- <32> 제2 트랜지스터(T2)는 데이터선(Dm)과 제1 노드(N1) 사이에 접속되며, 제2 트랜지스터(T2)의 게이트 전극은 현재 주사선(Sn)에 접속된다. 이와 같은 제2 트랜지스터(T2)는 현재 주사선(Sn)으로 현재 주사신호가 공급되는 기간 동안 턴-온되어, 데이터선(Dm)으로부터 공급되는 데이터 신호를 화소(110) 내부로 전달한다.

- <33> 제3 트랜지스터(T3)는 제1 노드(N1)와 유기발광다이오드(OLED) 사이에 접속되며, 제3 트랜지스터(T3)의 게이트 전극은 제2 노드(N2)에 접속된다. 이와 같은 제3 트랜지스터(T3)는 제2 트랜지스터(T2)를 통해 전달되는 데이터 신호에 대응하여 화소(110)의 발광 기간 동안 유기발광다이오드(OLED)로 흐르는 구동전류의 크기를 제어한다.

- <34> 제4 트랜지스터(T4)는 제3 트랜지스터(T3)의 게이트 전극과 드레인 전극 사이에 접속되며, 제4 트랜지스터(T4)의 게이트 전극은 현재 주사선(Sn)에 접속된다. 이와 같은 제4 트랜지스터(T4)는 현재 주사선(Sn)으로 현재 주사신호가 공급되는 기간 동안 턴-온되어, 제3 트랜지스터(T3)를 다이오드 연결시킨다.

- <35> 제5 트랜지스터(T5)는 제1 전원(ELVDD)과 제1 노드(N1) 사이에 접속되며, 제5 트랜지스터(T5)의 게이트 전극은 발광 제어선(En)에 접속된다. 이와 같은 제5 트랜지스터(T5)는 발광 제어선(En)으로부터 공급되는 발광 제어신호가 로우레벨로 천이되면 제1 전원(ELVDD)과 제1 노드(N1)를 전기적으로 연결한다. 즉, 제5 트랜지스터(T5)가 턴-온되면 제3 트랜지스터(T3)와 제1 전원(ELVDD)이 전기적으로 연결된다.

- <36> 제6 트랜지스터(T6)는 제3 트랜지스터(T3)와 유기발광다이오드(OLED) 사이에 접속되며, 제6 트랜지스터(T6)의 게이트 전극은 발광 제어선(En)에 접속된다. 이와 같은 제6 트랜지스터(T6)는 발광 제어선(En)으로 하이레벨의 발광 제어신호가 공급되는 기간 동안 턴-오프됨으로써, 유기발광다이오드(OLED)로 구동전류가 공급되는 것을 방지한다. 그리고, 제6 트랜지스터(T6)는 발광 제어신호의 전압레벨이 로우레벨로 천이되는 발광기간 동안 턴-온되어, 제3 트랜지스터(T3)와 유기발광다이오드(OLED)를 전기적으로 연결한다.

- <37> 제7 트랜지스터(T7)는 제2 노드(N2)와 초기화전원(Vinit) 사이에 접속되며, 제7 트랜지스터(T7)의 게이트 전극은 이전 주사선(Sn-1)에 접속된다. 이와 같은 제7 트랜지스터(T7)는 이전 주사선(Sn-1)으로 이전 주사신호가 공급되는 기간 동안 턴-온되어 제2 노드(N2)로 초기화전원(Vinit)의 전압을 공급한다.

- <38> 제1 커패시터(C1)는 제2 노드(N2)와 제1 전원(ELVDD) 사이에 접속된다. 이와 같은 제1 커패시터(C1)는 이전 주사선(Sn-1)으로 이전 주사신호가 공급되는 기간 동안 제7 트랜지스터(T7)를 경유하여 공급되는 초기화전원(Vinit)에 의해 초기화된다. 이후, 제1 커패시터(C1)는 현재 주사선(Sn)으로 현재 주사신호가 공급되는 기간 동안 제2 내지 제4 트랜지스터(T2 내지 T4)를 경유하여 공급되는 데이터 신호를 저장한다.

- <39> 제2 커패시터(C2)는 제2 노드(N2)와 현재 주사선(Sn) 사이에 접속된다. 이와 같은 제2 커패시터(C2)는 현재 주사선(Sn)으로부터의 현재 주사신호와 제2 노드(N2)의 전압차를 일정하게 유지한다. 즉, 제2 커패시터(C2)는 현재 주사신호의 전압레벨이 천이될 때, 특히 현재 주사신호의 공급이 중단되는 시점에서 커플링 작용에 의해 제2 노드(N2)의 전압을 상승시킴으로써, 패널 내의 로드로 인한 전압강하를 보상한다.

- <40> 유기발광다이오드(OLED)는 화소회로(112)와 제2 전원(ELVSS) 사이에 접속된다. 이와 같은 유기발광다이오드(OLED)는 화소(110)의 발광 기간 동안 제1 전원(ELVDD), 제5 트랜지스터(T5), 제3 트랜지스터(T3) 및 제6 트랜지스터(T6)를 경유하여 공급되는 구동전류에 대응하여 발광한다.

- <41> 전술한 바와 같은 화소(110)에서, 유기발광다이오드(OLED)의 애노드 전극이 화소회로(112), 특히 제1 및/또는 제2 커패시터(C1, C2)와 중첩되는 화소의 구조상, 제2 노드(N2)와 유기발광다이오드(OLED)의 애노드 전극 사이에는 기생 커패시터(Cp)가 생성된다.

- <42> 이와 같은 기생 커패시터(Cp)는 유기발광다이오드(OLED)의 애노드 전극의 전압(이하, 애노드 전압이라 함)이 변경되면, 킥백 전압을 발생시켜 제2 노드(N2)의 전압을 변화시킨다.

- <43> 여기서, 킥백 전압은 애노드 전압의 변화폭이 클수록 크게 발생하게 된다. 예컨대, 유기발광다이오드(OLED)가 이전 프레임에서 블랙계조를 표시하고, 후속되는 프레임에서 화이트계조를 표시하는 경우, 화소(110)의 발광기간이 시작될 때 애노드 전압이 매우 낮은 상태에서 높은 상태로 전환되면서 애노드 전압이 급격히 상승한다. 이에 따라, 기생 커패시터(Cp)에 의해 킥백 전압이 크게 발생하면서 제2 노드(N2)의 전압이 상승된다. 따라서, 블랙계조에서 화이트계조로 전환된 첫 프레임에서는 제2 노드(N2)의 전압이 화이트계조를 표시할 수 있을 만큼 충분히 낮게 설정되지 못하므로, 구동전류가 감소한다.

- <44> 그리고, 이전 프레임과 다음 프레임 모두 화이트계조를 표시하는 경우에는 이전 프레임에서 애노드 전압이 상대적으로 높은 상태로 설정되어 있기 때문에(단, 제1 트랜지스터(T1)가 구비되지 않은 경우) 킥백 전압이 상대적으로 작게 발생한다.

- <45> 따라서, 블랙계조에서 화이트계조로 전환되는 첫 프레임에 비해, 화이트계조를 유지하는 이후 프레임에서의 구동전류가 커서 이후 프레임에서 유기발광다이오드(OLED)가 더 높은 휘도로 발광한다.

- <46> 즉, 프레임마다 애노드 전압이 리셋되지 않으면, 동일한 계조에 대응하는 데이터신호를 공급받더라도 이전 프레임과의 계조 차에 따라 프레임 단위로 휘도편차가 발생하게 된다. 이에 따라, 저계조에서 고계조로 전환되는 첫 프레임에서의 화소(110)의 발광휘도는 유사 또는 동일 계조가 유지되는 이후의 프레임에서의 발광휘도에 비해 상대적으로 낮게 되므로 휘도곡선에 단차가 발생하여 지연(delay)의 형태로 나타나게 된다. 이에 의해, 화소(110)의 응답특성이 저하되고, 화질이 불균일해질 수 있다.

- <47> 따라서, 본 발명에서는 이를 방지하기 위하여 각 프레임의 초기화 기간 동안 애노드 전압을 일정하게 리셋하는

제1 트랜지스터(T1)를 구비한다.

<48> 이에 의해, 이전 프레임에서 공급되는 데이터 신호의 계조와 무관하게 계조별로 킥백 전압의 값이 균일하게 유지된다. 따라서, 휘도곡선에 단차가 발생하는 현상이 방지되어 화소(110)의 응답특성이 개선되고, 균일한 화질의 영상이 표시된다.

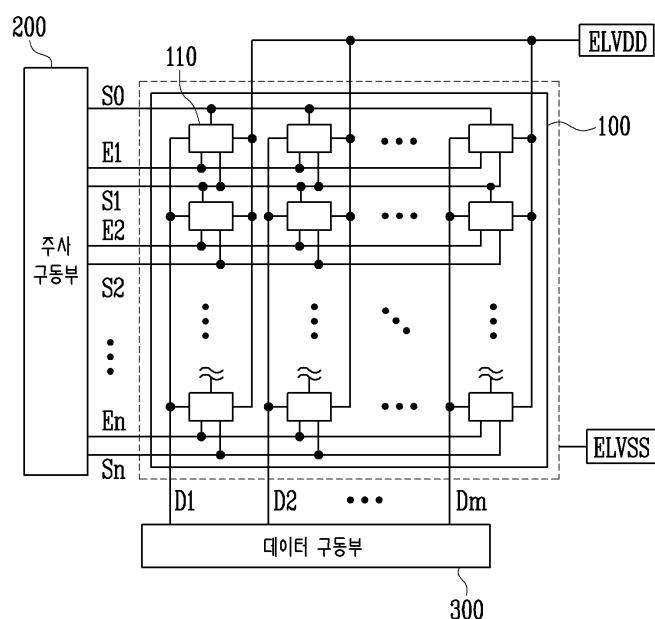

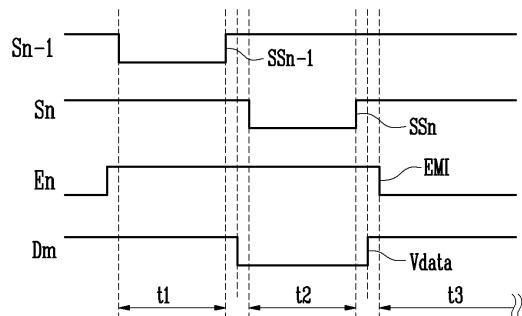

<49> 도 3은 도 2에 도시된 화소의 구동방법을 나타내는 과정도이다. 편의상, 도 3에서는 한 프레임 동안 화소로 공급되는 구동신호를 도시하기로 한다. 이하에서는 도 3을 도 2와 결부하여 도 2에 도시된 화소의 구동방법을 상세히 설명하기로 한다.

<50> 도 3을 참조하면, 우선 초기화 기간으로 설정되는 제1 기간(t1) 동안 화소(110)로 로우레벨의 이전 주사신호(SSn-1)가 공급된다. 그러면, 로우레벨의 이전 주사신호(SSn-1)에 대응하여 제1 및 제7 트랜지스터(T1, T7)가 턴-온된다. 이에 따라, 유기발광다이오드(OLED)의 애노드 전극 및 제2 노드(N2)에 초기화전원(Vinit)의 전압이 전달된다. 여기서, 초기화전원(Vinit)의 전압은 화소(110)를 초기화할 수 있는 값, 예컨대, 데이터 신호(Vdat a)의 최저전압보다 낮은 값으로 설정될 수 있다.

<51> 특히, 본 발명에서는 제1 트랜지스터(T1)에 의해 제1 기간(t1) 동안 유기발광다이오드(OLED)의 애노드 전극에 초기화전원(Vinit)의 전압을 리셋전압으로 공급함으로써, 프레임마다 애노드 전압을 일정하게 리셋시킬 수 있다.

<52> 이후, 프로그래밍 기간으로 설정되는 제2 기간(t2) 동안 화소(110)로 로우레벨의 현재 주사신호(SSn)가 공급된다. 그러면, 로우레벨의 현재 주사신호(SSn)에 대응하여 제2 및 제4 트랜지스터(T2, T4)가 턴-온된다. 그리고, 제4 트랜지스터(T4)에 의해 다이오드 연결되는 제3 트랜지스터(T3)가 턴-온되며, 앞선 제1 기간(t1) 동안 제2 노드(N2)가 초기화되었으므로 제3 트랜지스터(T3)는 순방향으로 다이오드 연결된다.

<53> 이에 의해, 데이터선(Dm)으로 공급된 데이터 신호(Vdata)가 제2 내지 제4 트랜지스터(T2 내지 T4)를 경유하여 제2 노드(N2)로 공급된다. 이때, 제3 트랜지스터(T3)가 다이오드 연결되었으므로, 제2 노드(N2)에는 데이터 신호(Vdata)와 제3 트랜지스터(T3)의 문턱전압의 차에 대응하는 전압이 공급된다. 제2 노드(N2)에 공급된 전압은 제1 커패시터(C1)에 저장된다.

<54> 이후, 현재 주사신호(SSn)의 전압레벨이 하이레벨로 천이되면, 제2 커패시터(C2)의 커플링 작용에 의해 제2 노드(N2)의 전압이 현재 주사신호(SSn)의 전압 변동폭에 대응하여 변경된다.

<55> 이후, 발광 기간으로 설정되는 제3 기간(t3) 동안 발광 제어신호(EMI)가 로우레벨로 천이된다. 그러면, 로우레벨의 발광 제어신호(EMI)에 의해 제5 및 제6 트랜지스터(T5, T6)가 턴-온된다. 이에 의해, 제1 전원(ELVDD)으로부터 제5 트랜지스터(T5), 제3 트랜지스터(T3), 제6 트랜지스터(T6) 및 유기발광다이오드(OLED)를 경유하여 제2 전원(ELVSS)의 경로로 구동전류가 흐르게 된다.

<56> 이때, 구동전류는 제3 트랜지스터(T3)에 의해 제어되는 것으로, 제3 트랜지스터(T3)는 자신의 게이트 전극에 공급되는 전압, 즉 제2 노드(N2)의 전압에 대응하는 크기의 구동전류를 발생시킨다.

<57> 한편, 제2 기간(t2) 동안 제1 커패시터(C1)에는 제3 트랜지스터(T3)의 문턱전압이 반영된 전압이 저장되었으므로, 제3 기간(t3) 동안 제3 트랜지스터(T3)의 문턱전압이 보상된다.

<58> 또한, 각 프레임의 제1 기간(t1) 동안 애노드 전압이 일정한 리셋전압으로 리셋되기 때문에 제3 기간(t3) 동안 애노드 전압의 변동으로 인한 킥백 전압이 발생하더라도 이는 이전 프레임의 계조와 무관하게 계조별로 균일하게 유지된다.

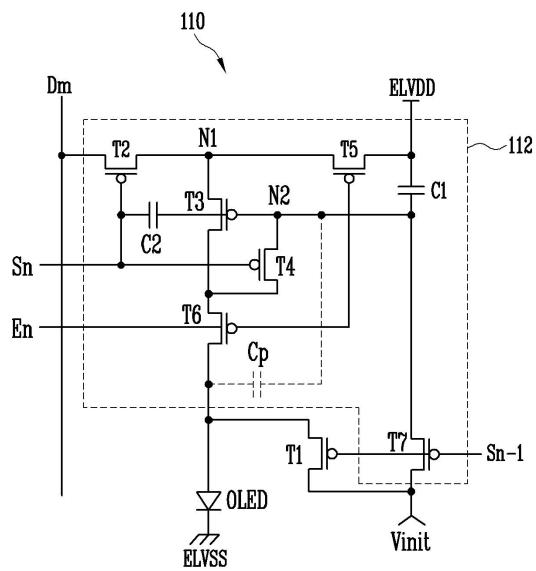

<59> 도 4는 본 발명의 다른 실시예에 의한 화소를 도시한 회로도이다. 도 4를 설명할 때, 도 2와 동일한 부분은 동일 부호를 부여하고, 이에 대한 상세한 설명은 생략하기로 한다.

<60> 도 4를 참조하면, 본 발명의 다른 실시예에 의한 화소(110')에 있어서, 제1 트랜지스터(T1')는 유기발광다이오드(OLED)의 애노드 전극과 제2 전원(ELVSS) 사이에 접속된다. 즉, 본 실시예에서 애노드 전압을 리셋하기 위한 리셋전압은 제2 전원(ELVSS)의 전압으로 설정된다. 이와 같이 리셋전압이 제2 전원(ELVSS)의 전압으로 설정되면, 킥백 전압이 크게 발생하여 제2 노드(N2) 전압의 상승폭이 증가한다. 이에 따라, 저계조(특히, 블랙 계조)에서의 계조 표현이 보다 용이해진다.

<61> 본 발명의 기술 사상은 상기 바람직한 실시예에 따라 구체적으로 기술되었으나, 상기한 실시예는 그 설명을 위한 것이며 그 제한을 위한 것이 아님을 주의하여야 한다. 또한, 본 발명의 기술 분야의 통상의 지식을 가진 자

라면 본 발명의 기술 사상의 범위 내에서 다양한 변형이 가능함을 이해할 수 있을 것이다.

### 도면의 간단한 설명

<62> 도 1은 유기전계발광 표시장치의 구성을 개략적으로 도시한 블럭도.

<63> 도 2는 본 발명의 일 실시예에 의한 화소를 도시한 회로도.

<64> 도 3은 도 2에 도시된 화소의 구동방법을 나타내는 과정도.

<65> 도 4는 본 발명의 다른 실시예에 의한 화소를 도시한 회로도.

<66> <도면의 주요 부분에 대한 부호의 설명>

<67> 110, 110': 화소 112, 112': 화소회로

<68> T1, T1': 제1 트랜지스터(리셋용 트랜지스터)

### 도면

#### 도면1

## 도면2

## 도면3

## 도면4

|                |                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 使用相同的像素和有机电致发光显示器                                                                                  |         |            |

| 公开(公告)号        | <a href="#">KR1020100009219A</a>                                                                   | 公开(公告)日 | 2010-01-27 |

| 申请号            | KR1020080070002                                                                                    | 申请日     | 2008-07-18 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                           |         |            |

| 申请(专利权)人(译)    | 三圣母工作显示有限公司                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 三圣母工作显示有限公司                                                                                        |         |            |

| [标]发明人         | WONKYU KWAK<br>곽원규                                                                                 |         |            |

| 发明人            | 곽원규                                                                                                |         |            |

| IPC分类号         | G09G3/30 G09G3/32 G09G3/20 H01L51/50                                                               |         |            |

| CPC分类号         | G09G2300/0852 G09G2300/0861 G09G2310/0251 G09G3/3233 G09G2300/0819 G09G2310/0248<br>H01L2924/12044 |         |            |

| 代理人(译)         | SHIN , YOUNG MOO                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                          |         |            |

### 摘要(译)

本发明涉及一种像素，其中响应特性得到改善并指示均匀图像质量的图像。本发明的像素包括连接到第一电源和第二电源之间的有机发光二极管，第一电源和有机发光二极管，第一晶体管，用于将复位电压提供给阳极电极。有机发光二极管在其提供先前扫描信号的第一持续时间内连接在有机发光二极管之间。