(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2009-0067949

(43) 공개일자 2009년06월25일

(51) Int. Cl.

H05B 33/08 (2006.01) H05B 33/02 (2006.01)

H05B 33/26 (2006.01)

(21) 출원번호 10-2007-0135785

(22) 출원일자 2007년12월21일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

박재희

경북 구미시 구평동 부영7단지 부영아파트 708동

1504호

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 10 항

(54) 유기전계발광표시장치 및 이의 제조방법

### (57) 요 약

본 발명은, 제1영역, 제2영역, 제3영역 및 제4영역이 정의된 기판; 및 제1영역에 위치하는 스위칭 트랜지스터와, 제2영역에 위치하는 커패시터와, 제3영역에 위치하는 구동 트랜지스터 및 유기 발광다이오드와, 제1영역, 제2영역, 제3영역 및 제4영역에 위치하고 스위칭 트랜지스터의 게이트 및 구동 트랜지스터의 게이트 상에 위치하며 제4영역에 위치하는 구동 트랜지스터의 게이트의 일부를 노출하는 제1콘택홀과, 제4영역에 위치하는 스위칭 트랜지스터의 게이트의 일부를 노출하는 제2콘택홀을 포함하는 게이트 절연막을 포함하는 서브 광셀을 포함하되, 스위칭 트랜지스터의 제2전극에 연장된 커패시터의 일단과 구동 트랜지스터의 게이트는 제4영역에 위치하는 제1콘택홀을 통해 연결되고 제2전극에 연장된 커패시터의 타단과 구동 트랜지스터의 제2전극은 제2콘택홀을 통해 연결된 유기전계발광표시장치를 제공한다.

대 표 도 - 도4

## 특허청구의 범위

### 청구항 1

제1영역, 제2영역, 제3영역 및 제4영역이 정의된 기판; 및

상기 제1영역에 위치하는 스위칭 트랜지스터와, 상기 제2영역에 위치하는 커패시터와, 상기 제3영역에 위치하는 구동 트랜지스터 및 유기 발광다이오드와, 상기 제1영역, 제2영역, 제3영역 및 제4영역에 위치하고 상기 스위칭 트랜지스터의 게이트 및 상기 구동 트랜지스터의 게이트 상에 위치하며 상기 제4영역에 위치하는 상기 구동 트랜지스터의 게이트의 일부를 노출하는 제1콘택홀과, 상기 제4영역에 위치하는 상기 스위칭 트랜지스터의 게이트의 일부를 노출하는 제2콘택홀을 포함하는 게이트 절연막을 포함하는 서브 팩셀을 포함하되,

상기 스위칭 트랜지스터의 제2전극에 연장된 상기 커패시터의 일단과 상기 구동 트랜지스터의 게이트는 상기 제4영역에 위치하는 상기 제1콘택홀을 통해 연결되고 상기 제2전원 배선에 연장된 상기 커패시터의 타단과 상기 구동 트랜지스터의 제2전극은 상기 제2콘택홀을 통해 연결된 유기전계발광표시장치.

### 청구항 2

제1항에 있어서,

상기 서브 팩셀은,

상기 제1영역에 위치하는 상기 스위칭 트랜지스터의 게이트와, 상기 제3영역에 위치하는 상기 구동 트랜지스터의 게이트와, 상기 제4영역에 위치하며 상기 제2전원 배선에 연장된 상기 커패시터의 타단과, 상기 스위칭 트랜지스터의 게이트, 상기 구동 트랜지스터의 게이트 및 상기 커패시터의 타단 상에 위치하는 상기 게이트 절연막과, 상기 제1영역의 상기 게이트 절연막 상에 위치하는 상기 스위칭 트랜지스터의 반도체층과, 상기 제3영역의 상기 게이트 절연막 상에 위치하는 상기 구동 트랜지스터의 반도체층과, 상기 스위칭 트랜지스터의 반도체층에 접촉하며 상기 게이트 절연막 상에 위치하는 상기 스위칭 트랜지스터의 제1전극 및 제2전극과, 상기 구동 트랜지스터의 반도체층에 접촉하며 상기 게이트 절연막 상에 위치하는 상기 구동 트랜지스터의 제1전극 및 제2전극과, 상기 스위칭 트랜지스터의 제2전극에 연장되며 상기 게이트 절연막 상에 위치하는 상기 커패시터의 일단과, 상기 스위칭 트랜지스터의 제1전극 및 제2전극과 상기 구동 트랜지스터의 제1전극 및 제2전극 및 상기 커패시터의 일단 상에 위치하는 보호막과, 상기 보호막 상에 위치하며 상기 제3영역의 중앙 영역에서 상기 구동 트랜지스터의 제1전극의 일부를 노출하는 제3콘택홀을 포함하는 평탄화막을 포함하는 유기전계발광표시장치.

### 청구항 3

제2항에 있어서,

상기 서브 팩셀은,

상기 평탄화막 상에 위치하며 상기 구동 트랜지스터의 제1전극에 연결된 캐소드와, 상기 캐소드 상에 위치하며 상기 캐소드를 노출하는 개구부를 포함하는 뱅크층과, 상기 뱅크층에 노출된 상기 캐소드 상에 위치하는 유기 발광층과, 상기 유기 발광층 상에 위치하는 애노드를 포함하는 유기전계발광표시장치.

### 청구항 4

제1항에 있어서,

상기 구동 트랜지스터는,

상기 제3영역에 위치하며 일부가 상기 제4영역으로 연장된 게이트와, 상기 게이트 상에 위치하는 게이트 절연막과, 상기 게이트 절연막 상에 위치하는 반도체층과, 상기 게이트 절연막 상에서 상기 반도체층의 일측에 접촉하고 상기 제3영역의 중앙에 직사각형 형태로 위치하는 제1전극과, 상기 게이트 절연막 상에서 상기 반도체층의 타측에 접촉하며 상기 제1전극과 이격된 제2전극을 포함하는 유기전계발광표시장치.

### 청구항 5

제1항에 있어서,

상기 서브 팩셀은,

스캔 배선에 게이트가 연결되고 데이터 배선에 제1전극이 연결된 상기 스위칭 트랜지스터와, 상기 제1콘택홀을 통해 상기 스위칭 트랜지스터의 제2전극에 게이트가 연결되고 상기 제2콘택홀을 통해 상기 제2전원 배선에 제2전극이 연결된 상기 구동 트랜지스터와, 상기 제2전원 배선에 연장되고 상기 제2콘택홀을 통해 상기 구동 트랜지스터의 제2전극에 연결된 일단과 상기 스위칭 트랜지스터의 제2전극에 연장되고 상기 제1콘택홀을 통해 상기 구동 트랜지스터의 게이트에 연결된 타단을 포함하는 상기 커패시터와, 제1전원 배선에 애노드가 연결되고 제3콘택홀을 통해 상기 구동 트랜지스터의 제1전극에 캐소드가 연결된 상기 유기 발광다이오드를 포함하는 유기전계발광표시장치.

## 청구항 6

기판 상에 제1영역, 제2영역, 제3영역 및 제4영역을 정의하는 영역 정의단계;

상기 제1영역에 스위칭 트랜지스터의 게이트와, 상기 제2영역에 제2전원 배선에 연장된 커패시터의 타단과, 상기 제3영역에 구동 트랜지스터의 게이트를 형성하는 게이트 형성단계;

상기 스위칭 트랜지스터의 게이트, 구동 트랜지스터의 게이트 및 상기 커패시터의 타단 상에 게이트 절연막을 형성하는 게이트 절연막 형성단계;

상기 제1영역의 상기 게이트 절연막 상에 상기 스위칭 트랜지스터의 반도체층과, 상기 제3영역의 상기 게이트 절연막 상에 상기 구동 트랜지스터의 반도체층을 형성하는 반도체층 형성단계;

상기 제4영역의 상기 게이트 절연막 상에 상기 구동 트랜지스터의 게이트의 일부가 노출되도록 제1콘택홀과, 상기 제4영역의 상기 게이트 절연막 상에 상기 커패시터의 타단의 일부가 노출되도록 제2콘택홀을 형성하는 콘택홀 형성단계; 및

상기 제1영역의 상기 반도체층과 접촉하도록 상기 게이트 절연막 상에 상기 스위칭 트랜지스터의 제1전극 및 제2전극과, 상기 제3영역의 상기 반도체층과 접촉하도록 상기 게이트 절연막 상에 상기 구동 트랜지스터의 제1전극 및 제2전극을 형성하는 전극 형성단계를 포함하되,

상기 전극 형성단계에서,

상기 스위칭 트랜지스터의 제2전극에 연장된 상기 커패시터의 일단은 상기 제1콘택홀을 통해 상기 구동 트랜지스터의 게이트와 연결되고, 상기 구동 트랜지스터의 제2전극은 상기 제2콘택홀을 통해 상기 제2전원 배선에 연장된 상기 커패시터의 타단에 연결된 유기전계발광표시장치의 제조방법.

## 청구항 7

제6항에 있어서,

상기 구동 트랜지스터의 게이트 및 제2전극은,

상기 제4영역으로 일부가 연장되도록 각각 패턴된 유기전계발광표시장치의 제조방법.

## 청구항 8

제6항에 있어서,

상기 구동 트랜지스터의 제1전극은,

상기 제3영역의 중앙에 직사각형 형태로 패턴되고 상기 제2전극은 상기 제1전극과 이격되고 상기 제1전극을 감싸도록 직사각형 띠 형태로 패턴된 유기전계발광표시장치의 제조방법.

## 청구항 9

제6항에 있어서,

상기 전극 형성단계 이후,

상기 스위칭 트랜지스터의 제1전극 및 제2전극과 상기 구동 트랜지스터의 제1전극 및 제2전극 상에 보호막을 형성하는 보호막 형성단계와, 상기 보호막 상에 상기 구동 트랜지스터의 제1전극이 노출되도록 제3콘택홀을 포함하는 평탄화막을 형성하는 평탄화막 형성단계를 포함하는 유기전계발광표시장치의 제조방법.

## 청구항 10

제9항에 있어서,

상기 평탄화막 형성단계 이후,

상기 평탄화막 상에 상기 제3콘택홀을 통해 상기 구동 트랜지스터의 제1전극에 연결된 캐소드와, 상기 캐소드 상에 위치하는 유기 발광층과, 상기 유기 발광층 상에 위치하는 애노드를 포함하는 유기 발광다이오드 형성단계를 포함하는 유기전계발광표시장치의 제조방법.

## 명세서

### 발명의 상세한 설명

#### 기술분야

<1> 본 발명은 유기전계발광표시장치 및 이의 제조방법에 관한 것이다.

#### 배경기술

<2> 유기전계발광표시장치에 사용되는 유기전계발광소자는 기판 상에 위치하는 두 개의 전극 사이에 발광층이 형성된 자발광소자였다.

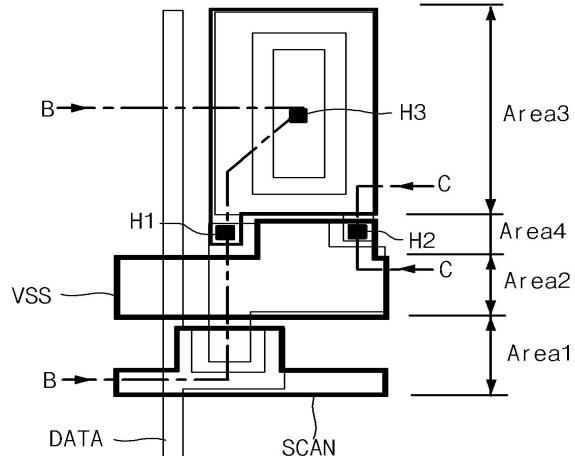

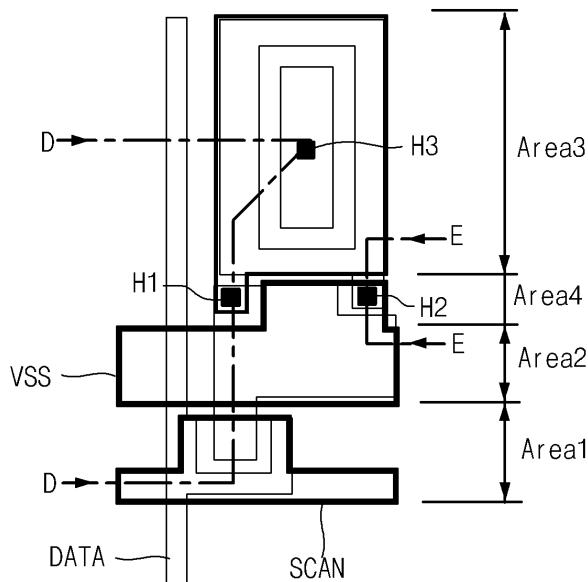

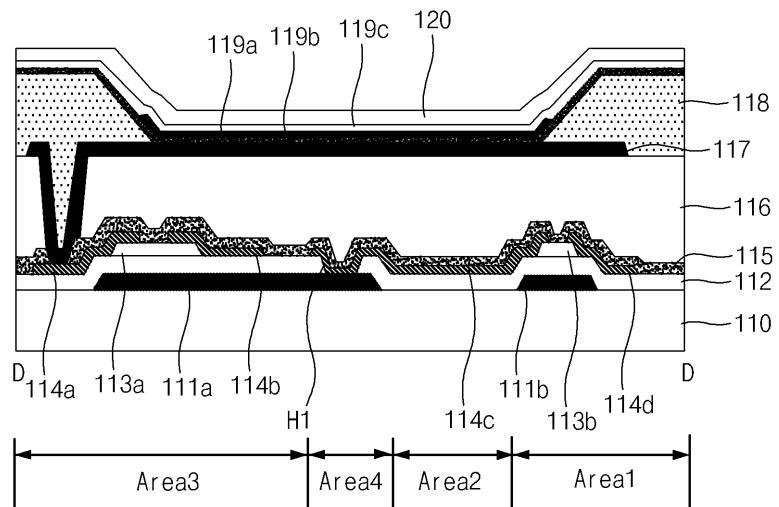

<3> 도 1은 종래 유기전계발광표시장치의 서브 퍽셀의 개략적인 평면도이고, 도 2는 도 1의 A-A영역의 단면도이다. 단, 도 1에서 전원전압을 공급하는 제1전원 배선은 평면 구조의 이해를 돋기 위해 생략한다.

<4> 도 1 및 도 2에 도시된 바와 같이, 서브 퍽셀은 제1영역(Area1)에 위치하는 스위칭 트랜지스터(111b, 113b, 114c, 114d)와, 제2영역(Area2)에 위치하는 커패시터(미도시)와, 제3영역(Area3)에 위치하는 구동 트랜지스터(111a, 113a, 114a, 114b) 및 유기 발광다이오드(117, 119a, 119b, 119c, 120)를 포함할 수 있다. 참고로, 미도시된 커패시터는 제2전원 배선과 스위칭 트랜지스터의 소오스 또는 드레인의 중첩영역에 형성될 수 있다.

<5> 이와 같은 구성을 갖는 서브 퍽셀은 스캔 배선(SCAN) 및 데이터 배선(DATA)에 연결되어 스캔 신호 및 데이터 신호가 공급되면, 미도시된 제1전원 배선과 제2전원 배선(VSS) 사이에 위치하는 유기 발광다이오드(117, 119a, 119b, 119c, 120)가 발광함으로써 영상을 표현할 수 있다.

<6> 한편, 종래 유기전계발광표시장치의 서브 퍽셀 구조는 보호막(115)에 제1콘택홀(H1) 및 제2콘택홀(H2)을 형성하고 제1연결전극(Con1)을 형성하여 제2영역(Area2)에 위치하는 스위칭 트랜지스터의 타단(114c)(커패시터의 일단)과 제3영역(Area3)에 위치하는 구동 트랜지스터의 게이트(111a)를 연결하였다. 또한, 보호막(115)에 제3콘택홀(H3) 및 제4콘택홀(H4)을 형성하고 제2연결전극(Con2)을 형성하여 제2영역(Area2)에 위치하는 제2전원 배선(VSS)(커패시터의 타단)과 제3영역(Area3)에 위치하는 구동 트랜지스터의 타단을 연결하였다. 참고로, 구동 트랜지스터의 일단(114a)은 평탄화막(116)에 형성된 제5콘택홀(H5)을 통해 유기 발광다이오드의 전극(117)과 연결될 수 있다. 미설명된 "118"은 뱅크층이다.

<7> 이와 같이, 서브 퍽셀의 구조적 특성상 배선 또는 전극 간의 신호 전달을 위해 서로 다른 층에 위치하는 배선 또는 전극에 제1콘택홀(H1), 제2콘택홀(H2), 제3콘택홀(H3) 및 제4콘택홀(H4)을 형성하고 이들의 상부에 제1연결전극(Con1) 및 제2연결전극(Con2)을 형성하면, 서브 퍽셀의 개구율이 좁아지게 된은 물론 보상회로를 형성하기 위한 마진을 확보할 수가 없어 이를 개선할 수 있는 방안이 마련되어야 할 필요성이 있다.

### 발명의 내용

#### 해결하고자하는 과제

<8> 상술한 배경기술의 문제점을 해결하기 위한 본 발명의 목적은, 제조공정을 개선하여 개구율을 확보할 수 있음은 물론 보상회로를 형성할 수 있도록 마진을 확보할 수 있는 유기전계발광표시장치와 이의 제조방법을 제공하는 것이다.

#### 과제 해결수단

<9> 상술한 과제 해결 수단으로 본 발명은, 제1영역, 제2영역, 제3영역 및 제4영역이 정의된 기판; 및 제1영역에 위

치하는 스위칭 트랜지스터와, 제2영역에 위치하는 커패시터와, 제3영역에 위치하는 구동 트랜지스터 및 유기 발광다이오드와, 제1영역, 제2영역, 제3영역 및 제4영역에 위치하고 스위칭 트랜지스터의 게이트 및 구동 트랜지스터의 게이트 상에 위치하며 제4영역에 위치하는 구동 트랜지스터의 게이트의 일부를 노출하는 제1콘택홀과, 제4영역에 위치하는 스위칭 트랜지스터의 게이트의 일부를 노출하는 제2콘택홀을 포함하는 게이트 절연막을 포함하는 서브 핵셀을 포함하되, 스위칭 트랜지스터의 제2전극에 연장된 커패시터의 일단과 구동 트랜지스터의 게이트는 제4영역에 위치하는 제1콘택홀을 통해 연결되고 제2전원 배선에 연장된 커패시터의 타단과 구동 트랜지스터의 제2전극은 제2콘택홀을 통해 연결된 유기전계발광표시장치를 제공한다.

<10> 서브 핵셀은, 제1영역에 위치하는 스위칭 트랜지스터의 게이트와, 제3영역에 위치하는 구동 트랜지스터의 게이트와, 제4영역에 위치하며 제2전원 배선에 연장된 커패시터의 타단과, 스위칭 트랜지스터의 게이트, 구동 트랜지스터의 게이트 및 커패시터의 타단 상에 위치하는 게이트 절연막과, 제1영역의 게이트 절연막 상에 위치하는 스위칭 트랜지스터의 반도체층과, 제3영역의 게이트 절연막 상에 위치하는 구동 트랜지스터의 반도체층과, 스위칭 트랜지스터의 반도체층에 접촉하며 게이트 절연막 상에 위치하는 스위칭 트랜지스터의 제1전극 및 제2전극과, 구동 트랜지스터의 반도체층에 접촉하며 게이트 절연막 상에 위치하는 구동 트랜지스터의 제1전극 및 제2전극과, 스위칭 트랜지스터의 제2전극에 연장되며 게이트 절연막 상에 위치하는 커패시터의 일단과, 스위칭 트랜지스터의 제1전극 및 제2전극과 구동 트랜지스터의 제1전극 및 제2전극 및 커패시터의 일단 상에 위치하는 보호막과, 보호막 상에 위치하며 제3영역의 중앙 영역에서 구동 트랜지스터의 제1전극의 일부를 노출하는 제3콘택홀을 포함하는 평탄화막을 포함할 수 있다.

<11> 서브 핵셀은, 평탄화막 상에 위치하며 구동 트랜지스터의 제1전극에 연결된 캐소드와, 캐소드 상에 위치하며 캐소드를 노출하는 개구부를 포함하는 뱅크층과, 뱅크층에 노출된 캐소드 상에 위치하는 유기 발광층과, 유기 발광층 상에 위치하는 애노드를 포함할 수 있다.

<12> 구동 트랜지스터는, 제3영역에 위치하며 일부가 제4영역으로 연장된 게이트와, 게이트 상에 위치하는 게이트 절연막과, 게이트 절연막 상에 위치하는 반도체층과, 게이트 절연막 상에서 반도체층의 일측에 접촉하고 제3영역의 중앙에 직사각형 형태로 위치하는 제1전극과, 게이트 절연막 상에서 반도체층의 타측에 접촉하며 제1전극과 이격된 제2전극을 포함할 수 있다.

<13> 서브 핵셀은, 스캔 배선에 게이트가 연결되고 데이터 배선에 제1전극이 연결된 스위칭 트랜지스터와, 제1콘택홀을 통해 스위칭 트랜지스터의 제2전극에 게이트가 연결되고 제2콘택홀을 통해 제2전원 배선에 제2전극이 연결된 구동 트랜지스터와, 제2전원 배선에 연장되고 제2콘택홀을 통해 구동 트랜지스터의 제2전극에 연결된 일단과 스위칭 트랜지스터의 제2전극에 연장되고 제1콘택홀을 통해 구동 트랜지스터의 게이트에 연결된 타단을 포함하는 커패시터와, 제1전원 배선에 애노드가 연결되고 제3콘택홀을 통해 구동 트랜지스터의 제1전극에 캐소드가 연결된 유기 발광다이오드를 포함할 수 있다.

<14> 한편, 다른 측면에서 본 발명은, 기판 상에 제1영역, 제2영역, 제3영역 및 제4영역을 정의하는 영역 정의단계; 제1영역에 스위칭 트랜지스터의 게이트와, 제2영역에 제2전원 배선에 연장된 커패시터의 타단과, 제3영역에 구동 트랜지스터의 게이트를 형성하는 게이트 형성단계; 스위칭 트랜지스터의 게이트, 구동 트랜지스터의 게이트 및 커패시터의 타단 상에 게이트 절연막을 형성하는 게이트 절연막 형성단계; 제1영역의 게이트 절연막 상에 스위칭 트랜지스터의 반도체층과, 제3영역의 게이트 절연막 상에 구동 트랜지스터의 반도체층을 형성하는 반도체층 형성단계; 제4영역의 게이트 절연막 상에 구동 트랜지스터의 게이트의 일부가 노출되도록 제1콘택홀과, 제4영역의 게이트 절연막 상에 커패시터의 타단의 일부가 노출되도록 제2콘택홀을 형성하는 콘택홀 형성단계; 및 제1영역의 반도체층과 접촉하도록 게이트 절연막 상에 스위칭 트랜지스터의 제1전극 및 제2전극과, 제3영역의 반도체층과 접촉하도록 게이트 절연막 상에 구동 트랜지스터의 제1전극 및 제2전극을 형성하는 전극 형성단계를 포함하되, 전극 형성단계에서, 스위칭 트랜지스터의 제2전극에 연장된 커패시터의 일단은 제1콘택홀을 통해 구동 트랜지스터의 게이트는 연결되고, 구동 트랜지스터의 제2전극은 제2콘택홀을 통해 제2전원 배선에 연장된 커패시터의 타단에 연결된 유기전계발광표시장치의 제조방법을 제공한다.

<15> 구동 트랜지스터의 게이트 및 제2전극은, 제4영역으로 일부가 연장되도록 각각 패턴될 수 있다.

<16> 구동 트랜지스터의 제1전극은, 제3영역의 중앙에 직사각형 형태로 패턴되고 제2전극은 제1전극과 이격되고 제1전극을 감싸도록 직사각형 띠 형태로 패턴될 수 있다.

<17> 전극 형성단계 이후, 스위칭 트랜지스터의 제1전극 및 제2전극과 구동 트랜지스터의 제1전극 및 제2전극 상에 보호막을 형성하는 보호막 형성단계와, 보호막 상에 구동 트랜지스터의 제1전극이 노출되도록 제3콘택홀을 포함

하는 평탄화막을 형성하는 평탄화막 형성단계를 포함할 수 있다.

<18> 평탄화막 형성단계 이후, 평탄화막 상에 제3콘택홀을 통해 구동 트랜지스터의 제1전극에 연결된 캐소드와, 캐소드 상에 위치하는 유기 발광층과, 유기 발광층 상에 위치하는 애노드를 포함하는 유기 발광다이오드 형성단계를 포함할 수 있다.

### 효과

<19> 본 발명은, 제조공정을 개선하여 개구율을 확보할 수 있음은 물론 보상회로를 형성할 수 있도록 마진을 확보할 수 있는 유기전계발광표시장치와 이의 제조방법을 제공하는 효과가 있다.

### 발명의 실시를 위한 구체적인 내용

<20> 이하, 본 발명의 실시를 위한 구체적인 내용을 첨부된 도면을 참조하여 설명한다.

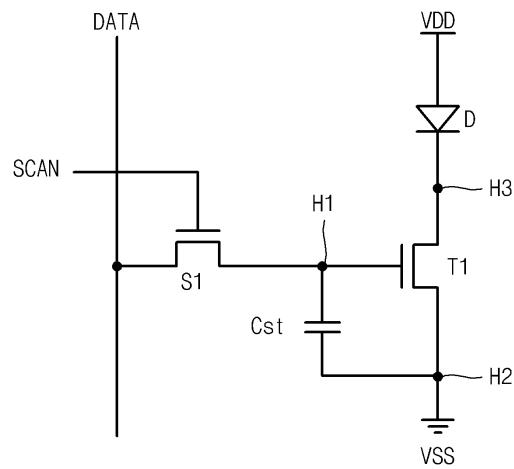

<21> 도 3은 본 발명의 일 실시예에 따른 유기전계발광표시장치의 서브 픽셀의 회로 구성예시도이다.

<22> 도 3에 도시된 바와 같이, 서브 픽셀은 스캔 배선(SCAN)에 게이트가 연결되고 데이터 배선(DATA)에 제1전극이 연결된 스위칭 트랜지스터(S1)를 포함할 수 있다. 또한, 제1콘택홀(H1)을 통해 스위칭 트랜지스터(S1)의 제2전극에 게이트가 연결되고 제2콘택홀(H2)을 통해 제2전원 배선(VSS)에 제2전극이 연결된 구동 트랜지스터(T1)를 포함할 수 있다. 또한, 제2전원 배선(VSS)에 연장되고 제2콘택홀(H2)을 통해 구동 트랜지스터(T1)의 제2전극에 연결된 일단과 스위칭 트랜지스터(S1)의 제2전극에 연장되고 제1콘택홀(H1)을 통해 구동 트랜지스터(T1)의 게이트에 연결된 타단을 포함하는 커패시터(Cst)를 포함할 수 있다. 또한, 제1전원 배선(VDD)에 애노드가 연결되고 제3콘택홀(H3)을 통해 구동 트랜지스터(T1)의 제1전극에 캐소드가 연결된 유기 발광다이오드(D)를 포함할 수 있다.

<23> 여기서, 서브 픽셀에 포함된 스위칭 트랜지스터(S1) 및 구동 트랜지스터(T1)는 a-Si 또는 p-Si으로 형성될 수 있으며, N-type 또는 P-type으로 형성될 수 있으나 이에 한정되지 않는다.

<24> 이와 같은 서브 픽셀은, 스캔 배선(SCAN)으로부터 스캔 신호가 공급되면 스위칭 트랜지스터(S1)가 턴온될 수 있다. 이때, 데이터 배선(DATA)으로부터 데이터 신호가 공급되면 턴온된 스위칭 트랜지스터(S1)를 통해 커패시터(Cst)에 데이터 전압이 저장될 수 있다. 이후, 스캔 배선(SCAN)으로부터 공급된 스캔 신호가 차단되면 커패시터(Cst)에 저장된 데이터 전압이 구동 트랜지스터(T1)의 게이트를 턴온할 수 있다. 그러면, 제1전원 배선(VDD)으로부터 공급된 전원이 유기 발광다이오드(D)를 통해 제2전원 배선(VSS)으로 흐를 수 있게 되어 유기 발광다이오드(D)는 발광할 수 있다.

<25> 이하에서는, 서브 픽셀의 평면도를 참조하여 도 3에 도시된 서브 픽셀에 대해 개략적으로 설명한다.

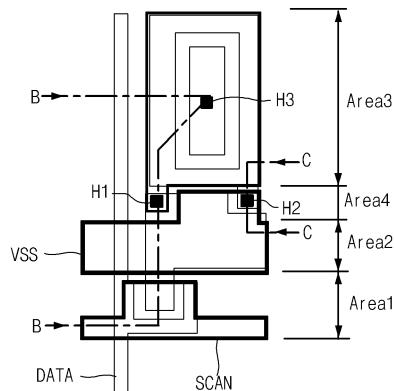

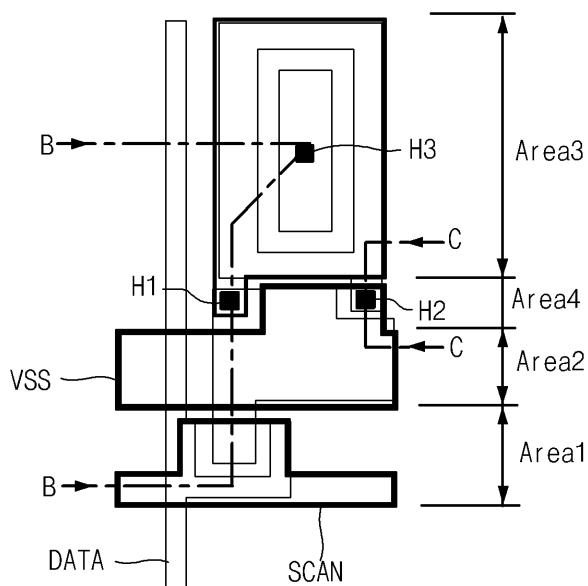

<26> 도 4는 본 발명의 일 실시예에 따른 서브 픽셀의 개략적인 평면도이다. 단, 설명의 이해를 돋기 위해 도 3을 함께 참조한다.

<27> 도 4에 도시된 바와 같이, 앞서 설명한 서브 픽셀은 제1영역(Area1)에 위치하는 스위칭 트랜지스터(S1)와, 제2영역(Area2)에 위치하는 커패시터(Cst)와, 제3영역(Area3)에 위치하는 구동 트랜지스터(T1) 및 유기 발광다이오드(D)를 포함할 수 있다.

<28> 여기서, 제1영역(Area1)에 위치하는 스위칭 트랜지스터(S1)는 앞서 설명한 바와 같이 스캔 배선(SCAN) 및 데이터 배선(DATA)에 연결될 수 있다.

<29> 여기서, 스위칭 트랜지스터(S1)의 제2전극에 연장된 커패시터(Cst)의 일단과 구동 트랜지스터(T1)의 게이트는 제4영역(Area4)에 위치하는 제1콘택홀(H1)을 통해 연결될 수 있고, 제2전원 배선(VSS)에 연장된 커패시터(Cst)의 타단과 구동 트랜지스터(T1)의 제2전극은 제2콘택홀(H2)을 통해 연결될 수 있다.

<30> 이하에서는, 서브 픽셀의 단면도를 참조하여, 도 4에 도시된 서브 픽셀에 대해 더욱 자세히 설명한다.

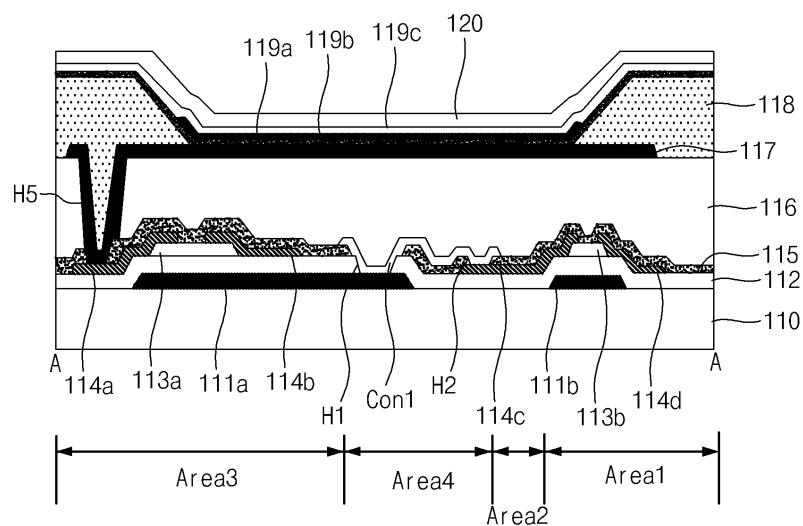

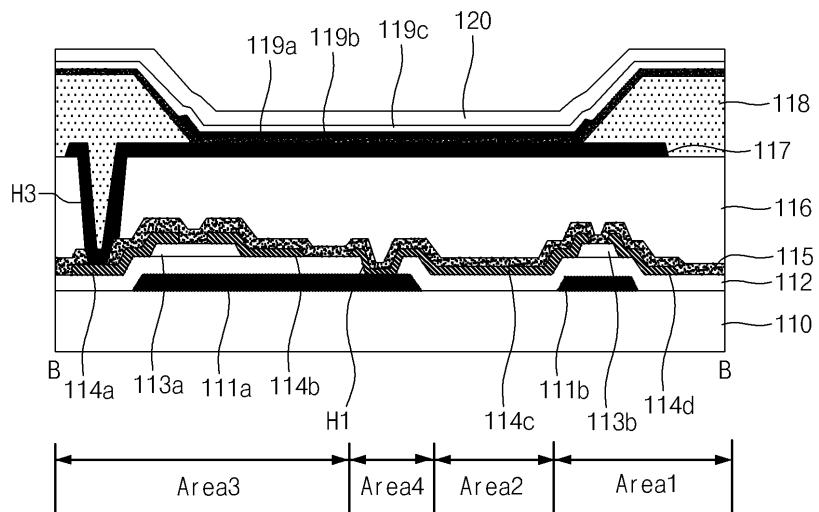

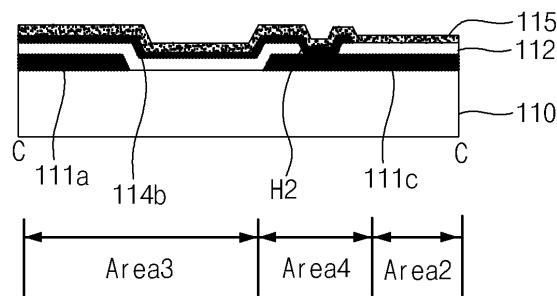

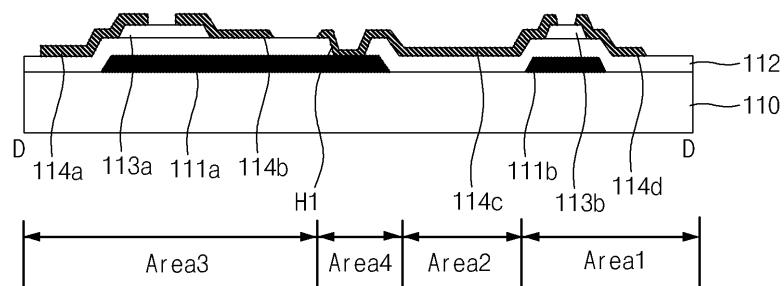

<31> 도 5는 도 4의 B-B영역의 단면도이고, 도 6은 도 4의 C-C영역의 단면도이다. 단, 설명의 이해를 돋기 위해 도 3 및 도 4를 함께 참조한다.

<32> 도 5 및 도 6에 도시된 바와 같이, 서브 픽셀은 기판(110) 상에 정의된 제1영역(Area1)에 위치하는 스위칭 트랜지스터(S1)와, 제2영역(Area2)에 위치하는 커패시터(Cst)와, 제3영역(Area3)에 위치하는 구동 트랜지스터(T1), 유기 발광다이오드(D)와, 제4영역(Area4)에 위치하는 제1콘택홀(H1), 제2콘택홀(H2)을 포함할 수 있다.

- <33> 기판(110) 상에는 제1영역(Area1)에 위치하는 스위칭 트랜지스터(S1)의 게이트(111b)와, 제3영역(Area3)에 위치하는 구동 트랜지스터(T1)의 게이트(111a)와, 제4영역(Area4)에 위치하며 제2전원 배선(VSS)에 연장된 커패시터(Cst)의 타단(111c)이 위치할 수 있다.

- <34> 스위칭 트랜지스터(S1)의 게이트(111b), 구동 트랜지스터(T1)의 게이트(111a) 및 커패시터(Cst)의 타단 상에는 게이트 절연막(112)이 위치할 수 있다.

- <35> 제1영역(Area1)의 게이트 절연막(112) 상에는 스위칭 트랜지스터(S1)의 반도체층(113b)이 위치할 수 있고, 제3영역(Area3)의 게이트 절연막(112) 상에는 구동 트랜지스터(T1)의 반도체층(113a)이 위치할 수 있다.

- <36> 게이트 절연막(112)에는 도 5에 도시된 바와 같이, 제4영역(Area4)에서 구동 트랜지스터(T1)의 게이트(111a)를 노출하는 제1콘택홀(H1)이 위치할 수 있다. 또한, 게이트 절연막(112)에는 도 6에 도시된 바와 같이, 제4영역(Area4)에서 커패시터(Cst)의 타단(111c)을 노출하는 제2콘택홀(H2)이 위치할 수 있다.

- <37> 게이트 절연막(112) 상에는 스위칭 트랜지스터(S1)의 반도체층(113b)에 접촉하는 스위칭 트랜지스터(S1)의 제1전극(114d) 및 제2전극(114c)이 위치할 수 있다. 게이트 절연막(112) 상에는 구동 트랜지스터(T1)의 반도체층(113a)에 접촉하는 구동 트랜지스터(T1)의 제1전극(114a) 및 제2전극(114b)이 위치할 수 있다.

- <38> 한편, 게이트 절연막(112) 상에 위치하며 스위칭 트랜지스터(S1)의 제2전극(114c)에 연장된 커패시터(Cst)의 일단(114c)은 도 5에 도시된 바와 같이, 제1콘택홀(H1)을 통해 구동 트랜지스터(T1)의 게이트(111a)에 연결될 수 있다. 또한, 구동 트랜지스터(T1)의 제2전극(114b)은 제2콘택홀(H2)을 통해 제2전원 배선(VSS)에 연장된 커패시터(Cst)의 타단(111c)에 연결될 수 있다.

- <39> 스위칭 트랜지스터(S1)의 제1전극(114d)과 제2전극(114c), 구동 트랜지스터(T1)의 제1전극(114a)과 제2전극(114b) 및 커패시터(Cst)의 일단 상에는 보호막(115)이 위치할 수 있다.

- <40> 보호막(115) 상에는 제3영역(Area3)의 중앙 영역에서 구동 트랜지스터(T1)의 제1전극(114a)의 일부를 노출하는 제3콘택홀(H3)을 포함하는 평탄화막(116)이 위치할 수 있다.

- <41> 평탄화막(116) 상에는 유기 발광다이오드(117, 119a, 119b, 119c, 120)가 위치할 수 있다.

- <42> 여기서, 앞서 설명한 구동 트랜지스터(T1)의 게이트(111a)는 제3영역(Area3)에 위치하며 일부가 제4영역(Area4)으로 연장될 수 있다. 또한, 구동 트랜지스터(T1)의 제1전극(114a)은 반도체층(113a)의 일측에 접촉하고 제3영역(Area3)의 중앙에서 직사각형 형태로 위치할 수 있다. 또한, 구동 트랜지스터(T1)의 제2전극(114b)은 제3영역(Area3)에 위치하며 일부가 제4영역(Area4)으로 연장될 수 있으며 상기 반도체층(113a)의 타측에 접촉하고 제1전극(114a)을 둘러싸도록 이격되어 위치할 수 있다.

- <43> 여기서, 유기 발광다이오드(117, 119a, 119b, 119c, 120)는 구동 트랜지스터(T1)의 제1전극(114a)에 연결된 캐소드(117)와, 캐소드(117) 상에서 캐소드(117)를 노출하는 개구부를 포함하는 뱅크층(118)과, 뱅크층(118)에 노출된 캐소드(117) 상에 위치하는 유기 발광층(119a, 119b, 119c)과, 유기 발광층(119a, 119b, 119c) 상에 위치하는 애노드(120)를 포함할 수 있다.

- <44> 이하에서는, 서브 팩셀의 구조 중 유기 발광다이오드(117, 119a, 119b, 119c, 120)의 계층 구조에 대해 더욱 자세히 설명한다.

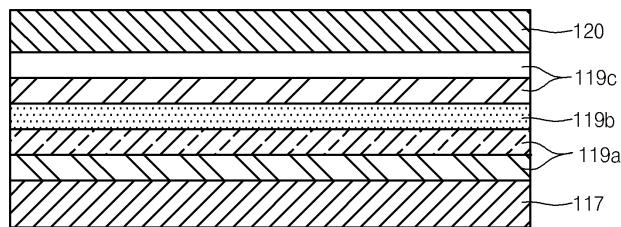

- <45> 도 7은 유기 발광다이오드의 계층 구조도이다.

- <46> 도 7을 참조하면, 유기 발광다이오드는 캐소드(117), 캐소드(117) 상에 위치하는 전자주입층 및 전자수송층을 포함하는 하부 공통층(119a), 발광층(119b), 정공수송층 및 정공주입층을 포함하는 상부 공통층(119c) 및 애노드(120)를 포함할 수 있다.

- <47> 여기서, 발광층(119b)은 적색, 녹색, 청색 및 백색을 발광하는 물질로 이루어질 수 있으며, 인광 또는 형광물질을 이용하여 형성할 수 있다.

- <48> 발광층(119b)이 적색인 경우, CBP(carbazole biphenyl) 또는 mCP(1,3-bis(carbazol-9-yl)를 포함하는 호스트물질을 포함하며, PIQIr(acac)(bis(1-phenylisoquinoline)acetylacetone) iridium, PQIr(acac)(bis(1-phenylquinoline)acetylacetone) iridium, PQIr(tris(1-phenylquinoline)iridium) 및 PtOEP(octaethylporphyrin platinum)로 이루어진 군에서 선택된 어느 하나 이상을 포함하는 도편트를 포함하는 인광물질로 이루어질 수 있고, 이와는 달리 PBD:Eu(DBM)3(Phen) 또는 Perylene을 포함하는 형광물질로 이루어질

수 있으나 이에 한정되지 않는다.

- <49> 발광층(119b)이 녹색인 경우, CBP 또는 mCP를 포함하는 호스트 물질을 포함하며, Ir(ppy)3(fac tris(2-phenylpyridine)iridium)을 포함하는 도편트 물질을 포함하는 인광물질로 이루어질 수 있고, 이와는 달리, Alq3(tris(8-hydroxyquinolino)aluminum)을 포함하는 형광물질로 이루어질 수 있으나 이에 한정되지 않는다.

- <50> 발광층(119b)이 청색인 경우, CBP 또는 mCP를 포함하는 호스트 물질을 포함하며, (4,6-F2ppy)2Irpic을 포함하는 도편트 물질을 포함하는 인광물질로 이루어질 수 있다.

- <51> 이와는 달리, spiro-DPVBi, spiro-6P, 디스틸벤젠(DSB), 디스트릴아릴렌(DSA), PFO계 고분자 및 PPV계 고분자로 이루어진 군에서 선택된 어느 하나를 포함하는 형광물질로 이루어질 수 있으나 이에 한정되지 않는다.

- <52> 여기서, 하부 공통층(119a) 중 하나인 전자주입층은 전자의 주입을 원활하게 하는 역할을 하며, Alq3(tris(8-hydroxyquinolino)aluminum), PBD, TAZ, spiro-PBD, BAlq 또는 SA1q를 사용할 수 있으나 이에 한정되지 않는다.

- <53> 전자주입층은 전자주입층을 이루는 유기물과 무기물을 진공증착법으로 형성할 수 있으나 이에 한정되지 않는다.

- <54> 여기서, 하부 공통층(119a) 중 남은 하나인 전자수송층은 전자의 수송을 원활하게 하는 역할을 하며, Alq3(tris(8-hydroxyquinolino)aluminum), PBD, TAZ, spiro-PBD, BAlq 및 SA1q로 이루어진 군에서 선택된 어느 하나 이상으로 이루어질 수 있으나 이에 한정되지 않는다.

- <55> 전자수송층은 증발법 또는 스판코팅법을 이용하여 형성할 수 있다. 전자수송층은 캐소드(117)로부터 주입된 정공이 발광층을 통과하여 애노드(120)로 이동하는 것을 방지하는 역할도 할 수 있다. 즉, 정공저지층의 역할을 하여 발광층(119b)에서 정공과 전자의 결합을 효율적이게 하는 역할을 할 수도 있다.

- <56> 여기서, 상부 공통층(119c) 중 하나인 정공주입층은 정공의 주입을 원활하게 하는 역할을 할 수 있으며, CuPc(copper phthalocyanine), PEDOT(poly(3,4)-ethylenedioxithiophene), PANI(polyaniline) 및 NPD(N,N-dinaphthyl-N,N'-diphenyl benzidine)로 이루어진 군에서 선택된 어느 하나 이상으로 이루어질 수 있으나 이에 한정되지 않는다.

- <57> 앞서 설명한, 정공주입층은 증발법 또는 스판코팅법을 이용하여 형성할 수 있으나 이에 한정되지 않는다.

- <58> 상부 공통층(119c) 중 다른 하나인 정공수송층은 정공의 수송을 원활하게 하는 역할을 하며, NPD(N,N-dinaphthyl-N,N'-diphenyl benzidine), TPD(N,N'-bis-(3-methylphenyl)-N,N'-bis-(phenyl)-benzidine), s-TAD 및 MTDATA(4,4',4"-Tris(N-3-methylphenyl-N-phenyl-amino)-triphenylamine)로 이루어진 군에서 선택된 어느 하나 이상으로 이루어질 수 있으나 이에 한정되지 않는다.

- <59> 정공수송층은 증발법 또는 스판코팅법을 이용하여 형성할 수 있으나 이에 한정되지 않는다.

- <60> 한편, 정공주입층 또는 전자주입층은 무기물을 더 포함할 수 있으며, 무기물은 금속화합물을 더 포함할 수 있다. 금속화합물은 알칼리 금속 또는 알칼리 토금속을 포함할 수 있다. 알칼리 금속 또는 알칼리 토금속을 포함하는 금속화합물은 LiQ, LiF, NaF, KF, RbF, CsF, FrF, BeF<sub>2</sub>, MgF<sub>2</sub>, CaF<sub>2</sub>, SrF<sub>2</sub>, BaF<sub>2</sub> 및 RaF<sub>2</sub>로 이루어진 군에서 선택된 어느 하나 이상일 수 있으나 이에 한정되지 않는다.

- <61> 즉, 전자주입층 내의 무기물은 애노드(120)로부터 발광층(119b)으로 주입되는 전자의 호핑(hopping)을 용이하게 하여, 발광층(119b) 내로 주입되는 정공과 전자의 밸런스를 맞추어 발광효율을 향상시킬 수 있다.

- <62> 또한, 정공주입층 내의 무기물은 캐소드(117)로부터 발광층(119b)으로 주입되는 정공의 이동성을 줄여줌으로써, 발광층(119b) 내로 주입되는 정공과 전자의 밸런스를 맞추어 발광효율을 향상시킬 수 있다.

- <63> 여기서, 본 발명은 도 7에 한정되는 것은 아니며, 하부 공통층(119a) 및 상부 공통층(119b)에 포함된 전자 주입층, 전자 수송층, 정공 수송층, 정공 주입층 중 적어도 어느 하나가 생략될 수도 있다.

- <64> 이하에서는, 본 발명의 일 실시예에 따른 유기전계발광표시장치의 제조방법에 대해 설명한다.

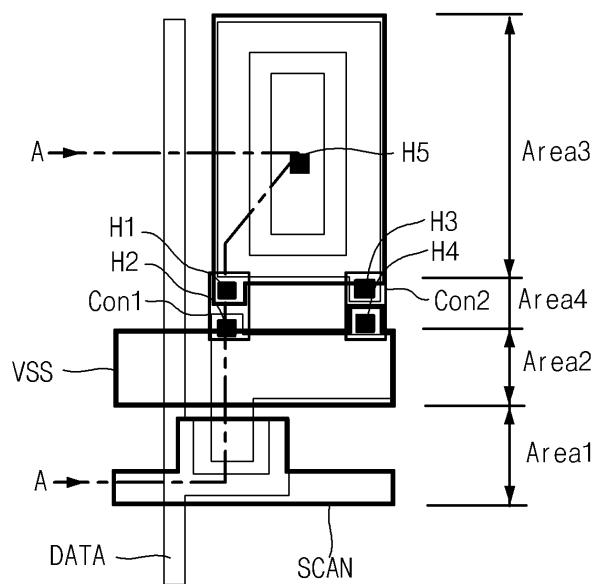

- <65> 도 8은 본 발명의 일 실시예에 따른 유기전계발광표시장치의 제조방법을 설명하기 위한 서브 팩셀의 개략적인 평면도이다. 단, 설명의 이해를 돋기 위해 도 3의 회로 구성 예시도를 함께 참조한다.

- <66> 도 8에 도시된 바와 같이, 앞서 설명한 서브 팩셀은 제1영역(Area1)에 위치하는 스위칭 트랜지스터(S1)와, 제2영역(Area2)에 위치하는 커패시터(Cst)와, 제3영역(Area3)에 위치하는 구동 트랜지스터(T1) 및 유기 발광다이오

드(D)를 포함할 수 있다.

<67> 여기서, 제1영역(Area1)에 위치하는 스위칭 트랜지스터(S1)는 스캔 배선(SCAN) 및 데이터 배선(DATA)에 연결될 수 있다.

<68> 여기서, 스위칭 트랜지스터(S1)의 제2전극에 연장된 커패시터(Cst)의 일단과 구동 트랜지스터(T1)의 게이트는 제4영역(Area4)에 위치하는 제1콘택홀(H1)을 통해 연결될 수 있고, 제2전원 배선(VSS)에 연장된 커패시터(Cst)의 타단과 구동 트랜지스터(T1)의 제2전극은 제2콘택홀(H2)을 통해 연결될 수 있다.

<69> 이하에서는, 서브 픽셀의 단면도를 참조하여, 도 8에 도시된 서브 픽셀에 대해 더욱 자세히 설명한다.

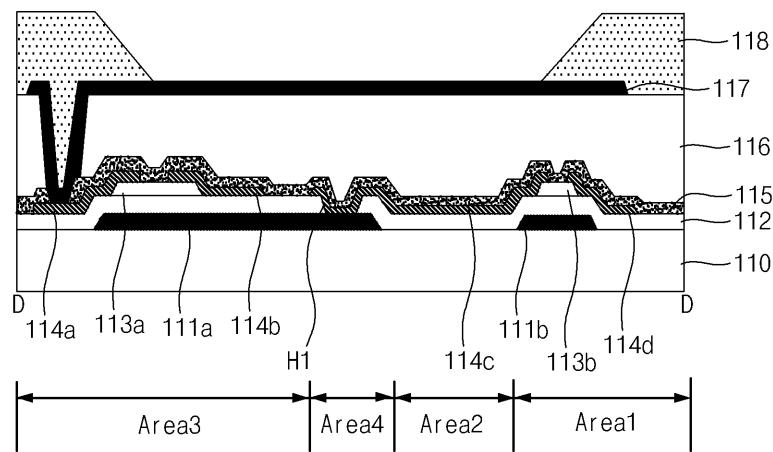

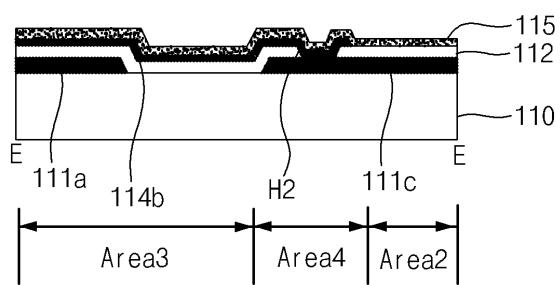

<70> 도 9a 내지 도 9c는 도 8의 D-D영역의 단면도이고, 도 10은 도 8의 E-E영역의 단면도이다.

<71> 먼저, 도 9a에 도시된 바와 같이, 기판(110) 상에 제1영역(Area1), 제2영역(Area2), 제3영역(Area3) 및 제4영역(Area4)을 정의하는 영역 정의단계를 실시한다.

<72> 다음, 도 9a에 도시된 바와 같이, 제1영역(Area1)에 스위칭 트랜지스터(S1)의 게이트(111b)와, 제2영역(Area2)에 제2전원 배선(VSS)에 연장된 커패시터(Cst)의 타단(미도시)과, 제3영역(Area3)에 구동 트랜지스터(T1)의 게이트(111a)를 형성하는 게이트 형성단계를 실시한다.

<73> 다음, 도 9a에 도시된 바와 같이, 스위칭 트랜지스터(S1)의 게이트(111b), 구동 트랜지스터(T1)의 게이트(111a) 및 커패시터(Cst)의 타단 상에 게이트 절연막(112)을 형성하는 게이트 절연막 형성단계를 실시한다.

<74> 다음, 도 9a에 도시된 바와 같이, 제1영역(Area1)의 게이트 절연막(112) 상에 스위칭 트랜지스터(S1)의 반도체층(113b)과, 제3영역(Area3)의 게이트 절연막(112) 상에 구동 트랜지스터(T1)의 반도체층(113a)을 형성하는 반도체층 형성단계를 실시한다.

<75> 다음, 도 9a에 도시된 바와 같이, 제4영역(Area4)의 게이트 절연막(112) 상에 구동 트랜지스터(T1)의 게이트(111a)의 일부가 노출되도록 제1콘택홀(H1)을 형성하고, 도 10에 도시된 바와 같이, 제4영역(Area4)의 게이트 절연막(112) 상에 커패시터(Cst)의 타단(111c)의 일부가 노출되도록 제2콘택홀(H2)을 형성하는 콘택홀 형성단계를 실시한다.

<76> 다음, 제1영역(Area1)의 반도체층(113b)과 접촉하도록 게이트 절연막(112) 상에 스위칭 트랜지스터(S1)의 제1전극(114d) 및 제2전극(114c)과, 제3영역(Area3)의 반도체층(113a)과 접촉하도록 게이트 절연막(112) 상에 구동 트랜지스터(T1)의 제1전극(114a) 및 제2전극(114b)을 형성하는 전극 형성단계를 실시한다.

<77> 여기서, 구동 트랜지스터(T1)의 게이트(111a) 및 제2전극(114b)은, 제4영역(Area4)으로 일부가 연장되도록 각각 패턴될 수 있다.

<78> 이에 따라, 도 9a에 도시된 바와 같이, 스위칭 트랜지스터(S1)의 제2전극(114c)에 연장된 커패시터의 일단(114c)은 제1콘택홀(H1)을 통해 구동 트랜지스터(T1)의 게이트(111a)와 연결될 수 있다. 또한, 도 10에 도시된 바와 같이, 구동 트랜지스터(T1)의 제2전극(114b)은 제2콘택홀(H2)을 통해 제2전원 배선(VSS)에 연장된 커패시터(Cst)의 타단(111c)에 연결될 수 있다.

<79> 이와 같은 단계에서, 앞서 설명한 구동 트랜지스터(T1)의 제1전극(114a)은 반도체층(113a)의 일측에 접촉하고 제3영역(Area3)의 중앙에서 직사각형 형태로 위치할 수 있다. 또한, 구동 트랜지스터(T1)의 제2전극(114b)은 반도체층(113a)의 타측에 접촉하고 제1전극(114a)을 감싸도록 이격되어 직사각형 띠 형태로 위치할 수 있다.

<80> 한편, 전극 형성단계 이후, 도 9b에 도시된 바와 같이, 스위칭 트랜지스터(S1)의 제1전극(114d) 및 제2전극(114c)과 구동 트랜지스터(T1)의 제1전극(114a) 및 제2전극(114b) 상에 보호막(115)을 형성하는 보호막 형성단계를 실시한다. 또한, 보호막(115) 상에 구동 트랜지스터(T1)의 제1전극(114a)이 노출되도록 제3콘택홀(H3)을 포함하는 평탄화막(116)을 형성하는 단계를 실시할 수 있다.

<81> 평탄화막(116) 형성단계 이후, 평탄화막(116) 상에 제3콘택홀(H3)을 통해 구동 트랜지스터(T1)의 제1전극(114a)에 연결된 캐소드(117)를 형성할 수 있다. 또한, 평탄화막(116) 상에 캐소드(117)를 노출하는 뱅크층(118)을 형성할 수 있다.

<82> 이후, 도 9c에 도시된 바와 같이, 캐소드(117) 상에 위치하는 유기 발광층(119a, 119b, 119c)을 형성하고, 유기 발광층(119a, 119b, 119c) 상에 애노드(120)를 포함하는 유기 발광다이오드(D)를 형성할 수 있다.

<83> 이상 본 발명은 서브 픽셀의 구조적 특성상 서로 다른 층에 위치하는 배선 또는 전극을 전기적으로 연결할 때,

별도의 연결전극을 사용하지 않도록 제조공정을 개선하여 개구율을 확보할 수 있음은 물론 보상회로를 형성할 수 있도록 마진을 확보할 수 있는 유기전계발광표시장치와 이의 제조방법을 제공하는 것이다.

<84> 이상 첨부된 도면을 참조하여 본 발명의 실시예를 설명하였지만, 상술한 본 발명의 기술적 구성은 본 발명이 속하는 기술 분야의 당업자가 본 발명의 그 기술적 사상이나 필수적 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시 예들은 모든 면에서 예시적인 것이며 한정적인 것이 아닌 것으로서 이해되어야 한다. 아울러, 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어진다. 또한, 특허청구범위의 의미 및 범위 그리고 그 등가 개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

### 도면의 간단한 설명

<85> 도 1은 종래 유기전계발광표시장치의 서브 팩셀의 개략적인 평면도.

<86> 도 2는 도 1의 A-A영역의 단면도.

<87> 도 3은 본 발명의 일 실시예에 따른 유기전계발광표시장치의 서브 팩셀의 회로 구성예시도.

<88> 도 4는 본 발명의 일 실시예에 따른 서브 팩셀의 개략적인 평면도.

<89> 도 5는 도 4의 B-B영역의 단면도.

<90> 도 6은 도 4의 C-C영역의 단면도.

<91> 도 7은 유기 발광다이오드의 계층 구조도.

<92> 도 8은 본 발명의 일 실시예에 따른 유기전계발광표시장치의 제조방법을 설명하기 위한 서브 팩셀의 개략적인 평면도.

<93> 도 9a 내지 도 9c는 도 8의 D-D영역의 단면도.

<94> 도 10은 도 8의 E-E영역의 단면도.

<95> <도면의 주요 부분에 관한 부호의 설명>

<96> 110: 기판 111a, 111b: 게이트

<97> 112: 게이트 절연막 113a, 113b: 반도체층

<98> 114a, 114b, 114c, 114d: 제1전극 및 제2전극

<99> 115: 보호막 116: 평탄화막

<100> 117: 캐소드 119a, 119b, 119c: 유기 발광층

<101> 120: 애노드 H1, H2 : 제1콘택홀, 제2콘택홀

도면

도면1

도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

도면8

도면9a

도면9b

도면9c

도면10

|                |                                  |         |            |

|----------------|----------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光显示装置及其制造方法                 |         |            |

| 公开(公告)号        | <a href="#">KR1020090067949A</a> | 公开(公告)日 | 2009-06-25 |

| 申请号            | KR1020070135785                  | 申请日     | 2007-12-21 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                         |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                        |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                        |         |            |

| [标]发明人         | PARK JAE HEE                     |         |            |

| 发明人            | PARK, JAE HEE                    |         |            |

| IPC分类号         | H05B33/08 H05B33/02 H05B33/26    |         |            |

| CPC分类号         | Y02B20/346 Y02B20/343            |         |            |

| 其他公开文献         | KR101373958B1                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>        |         |            |

### 摘要(译)

本发明提供一种有机电致发光显示装置，其中驱动晶体管的栅极和包括子像素的电容器的一端包括栅极绝缘层并且由于开关晶体管的第二电极而延伸，通过第一接触孔连接位于第四区域中并且电容器的延伸的另一端和驱动晶体管的第二电极通过第二接触孔连接到第二电源线，第二接触孔包括暴露第一区域，第二部分和部分的第二接触孔第三区域的栅极和限定第四区域的基板，位于第一区域的开关晶体管和位于电容器中的开关晶体管，位于第二部分和第一接触孔中，暴露部分位于第三区域的驱动晶体管的栅极和有机发光二极管的栅极第一区域，第二部分，第三区域和驱动晶体管，其位于第四区域中并且位于开关晶体管的栅极和驱动晶体管的栅极的表面上，并且位于第四区域和第四区域中。有机电致发光显示装置，接触孔和栅极。