(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) . Int. Cl. (45) 공고일자 2006년05월23일

H05B 33/00 (2006.01) (11) 등록번호 10-0583135

H05B 33/08 (2006.01) (24) 등록일자 2006년05월17일

(21) 출원번호 10-2004-0041588 (65) 공개번호 10-2005-0116509

(22) 출원일자 2004년06월08일 (43) 공개일자 2005년12월13일

(73) 특허권자 삼성에스디아이 주식회사

경기 수원시 영통구 신동 575

(72) 발명자 강태옥

경기도 성남시 분당구 분당동 샛별마을우방아파트 302동 1103호

신동용

서울특별시 관악구 봉천1동 969-37

정창용

경기도 수원시 팔달구 영통동 1043-8 301호

## (74) 대립의 신영무

(56) 선행기술조사문현

JP2001035662 A JP20020040990 A

JP2004062198 A KR1020050050242 A

\* 선행기술조사문현에 의하여 이용된 문현

## 심사관 : 김재문

### (54) 전계 발광 표시장치

## 요약

본 발명은 전계 발광 표시장치에 관한 것으로, 복수의 화소가 복수의 행과 열로 배열되어 화상을 표시하는 화소부, 복수의 화소에 데이터 신호를 인가하는 복수의 데이터선, 복수의 화소에 선택신호를 인가하는 복수의 주사선 및 복수의 화소에 전원을 공급하는 복수의 전원 공급선을 포함하며, 복수의 화소 중 하나의 행에 있는 인접한 두 개의 화소는 복수의 데이터선 중 하나의 데이터선을 공유하고 복수의 주사선 중 서로 다른 두 개의 주사선에 각각 연결되는 전계 발광 표시장치를 제공한다.

전원 공급선과 데이터선이 사이에 화소가 위치하게 되어 전원 공급선과 데이터선 상호간에 단락 불량이 발생하는 것을 방지할 수 있다.

또한, 두 개의 화소가 하나의 데이터선 또는/및 전원 공급선을 공통으로 사용하게 되어 전계 발광 표시장치의 화소 주변의 배선의 수를 줄일 수 있다.

### 대표도

도 3

### 색인어

유기 EL, 화소, 단락, 공통

### 명세서

#### 도면의 간단한 설명

도 1은 종래 기술에 따른 전계 발광 표시장치에 채용된 복수 화소의 등가회로도이다.

도 2는 도 1의 전계 발광 표시장치의 레이아웃을 나타내는 투과 평면도이다.

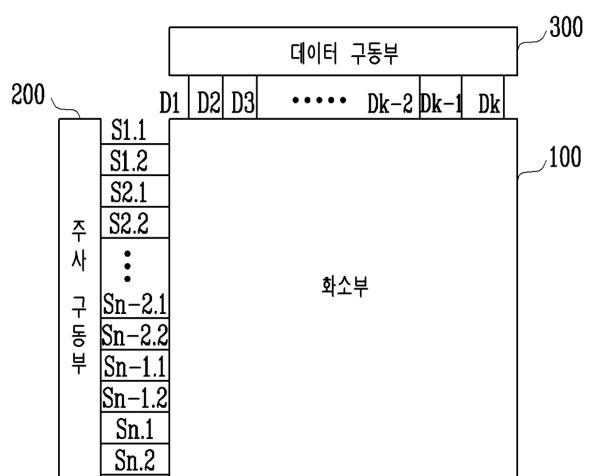

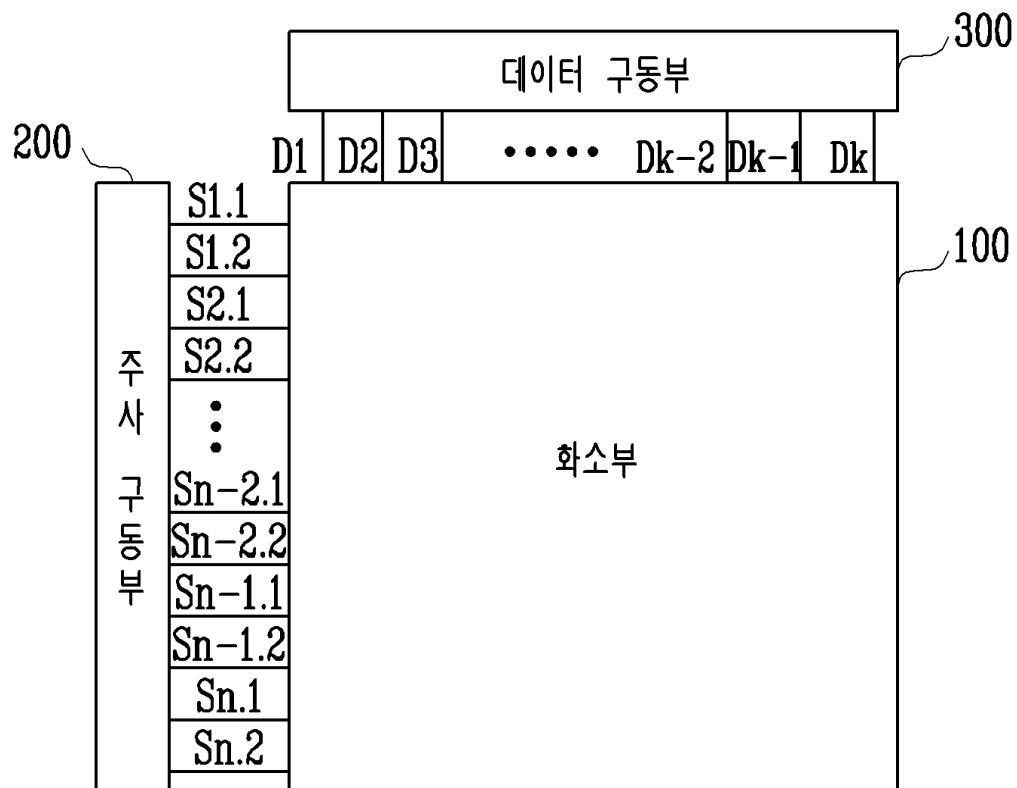

도 3은 본 발명에 따른 전계 발광 표시장치의 일실시례의 구성을 나타내는 구성도이다.

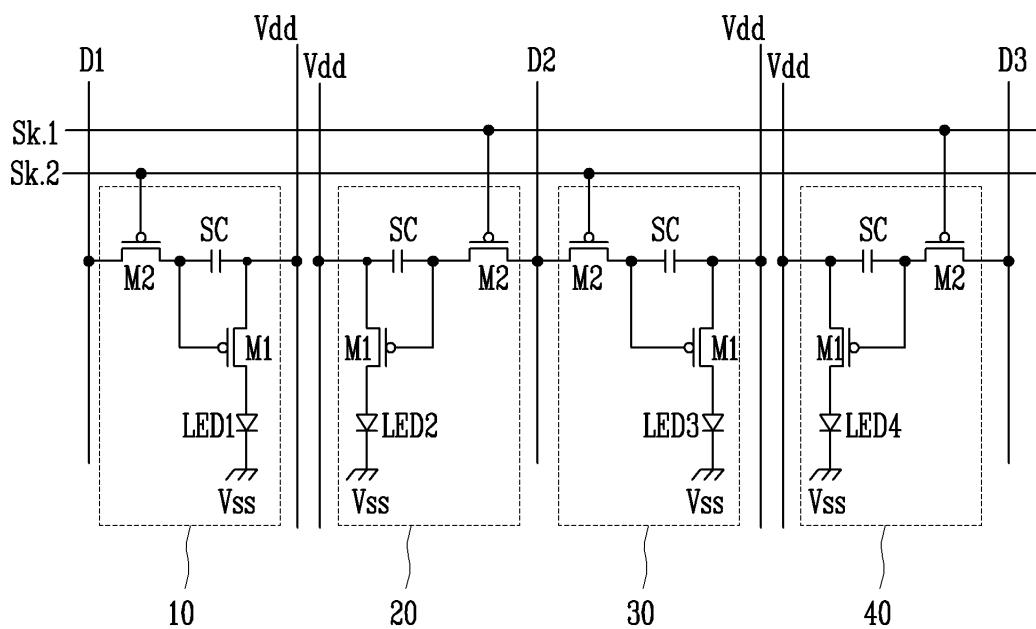

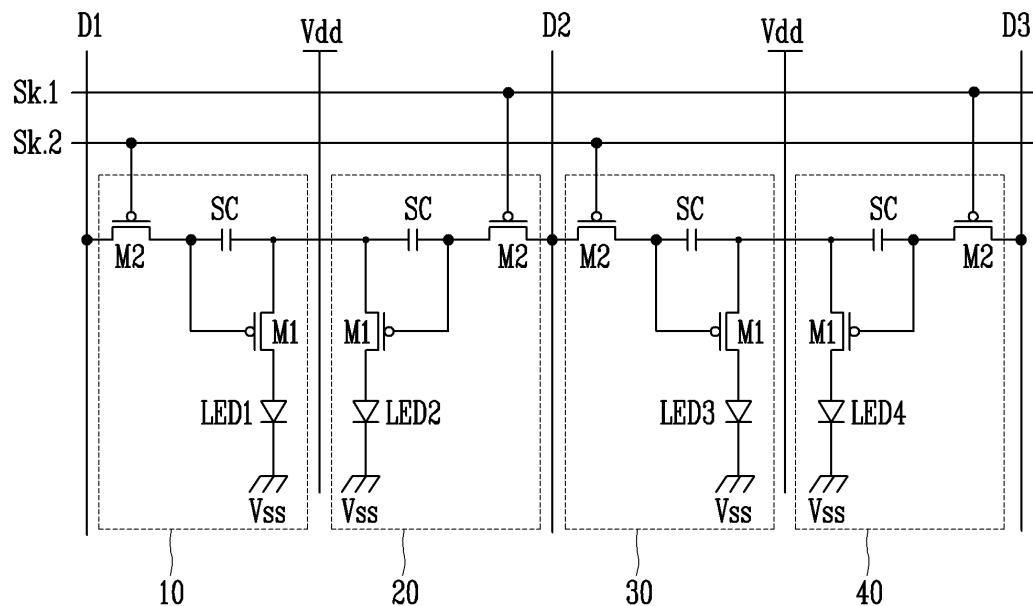

도 4는 본 발명에 따른 전계 발광 표시장치에 채용된 복수 화소의 등가회로도이다.

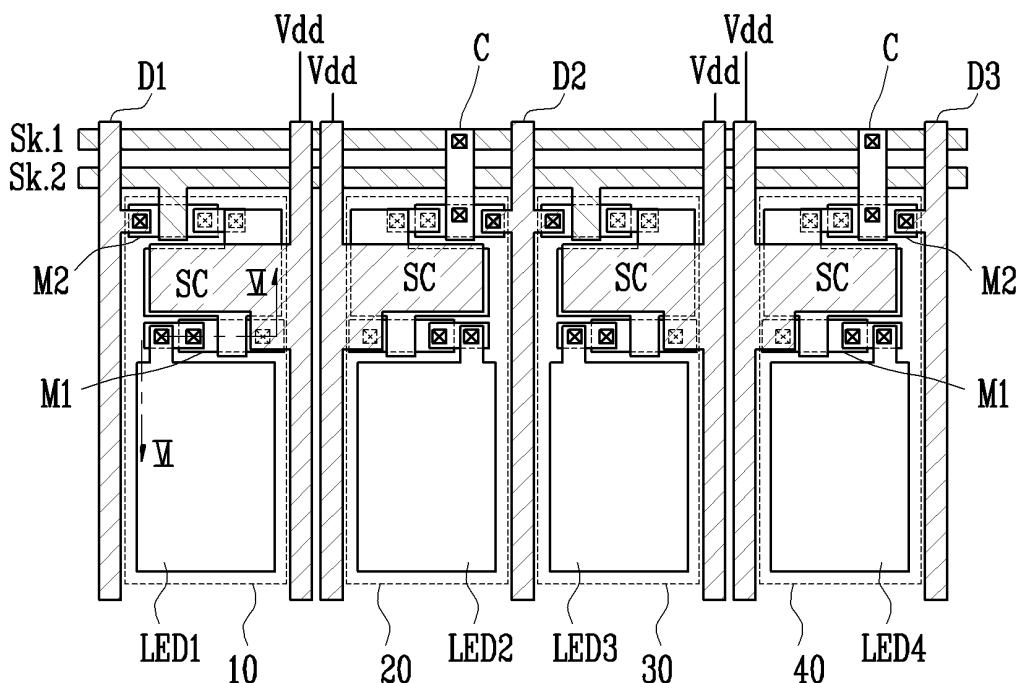

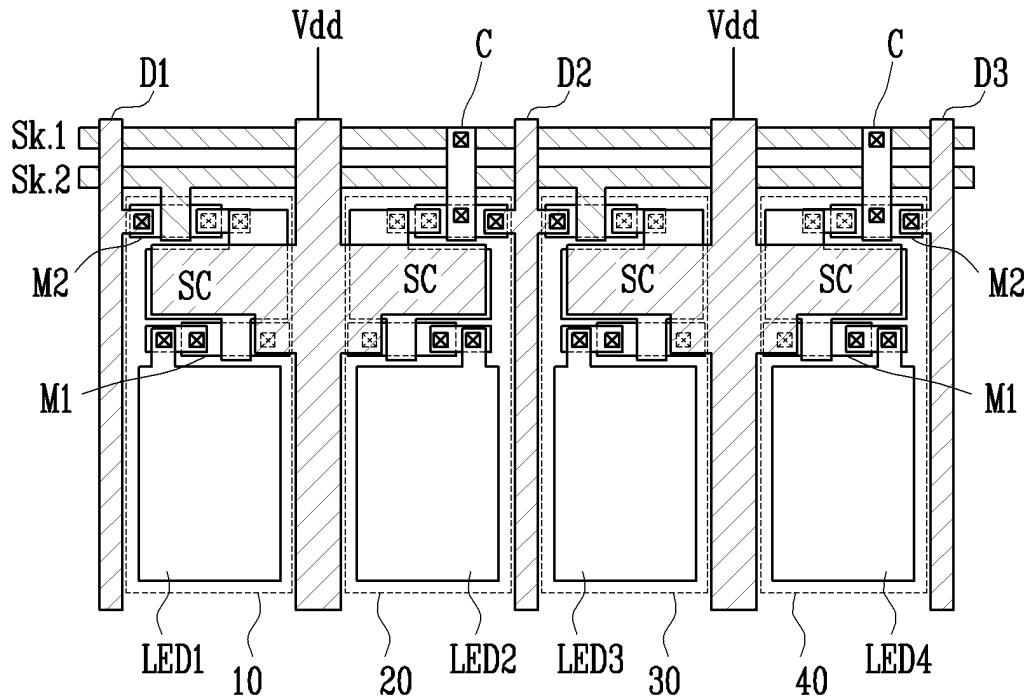

도 5는 도 4에 표현된 화소의 레이아웃에 기초한 투시 평면도이다.

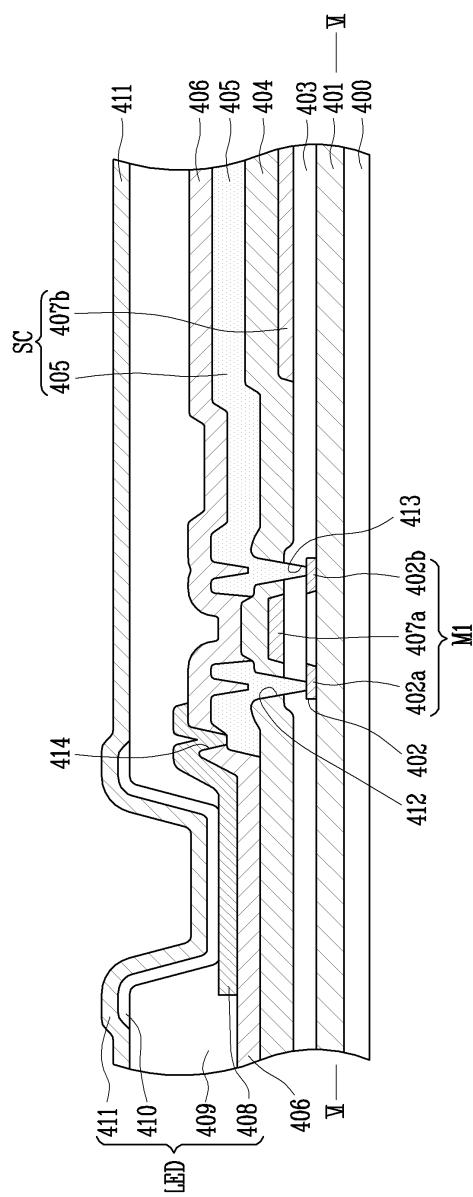

도 6은 도 5의 VI-VI` 선에 따른 단면구조를 나타낸다.

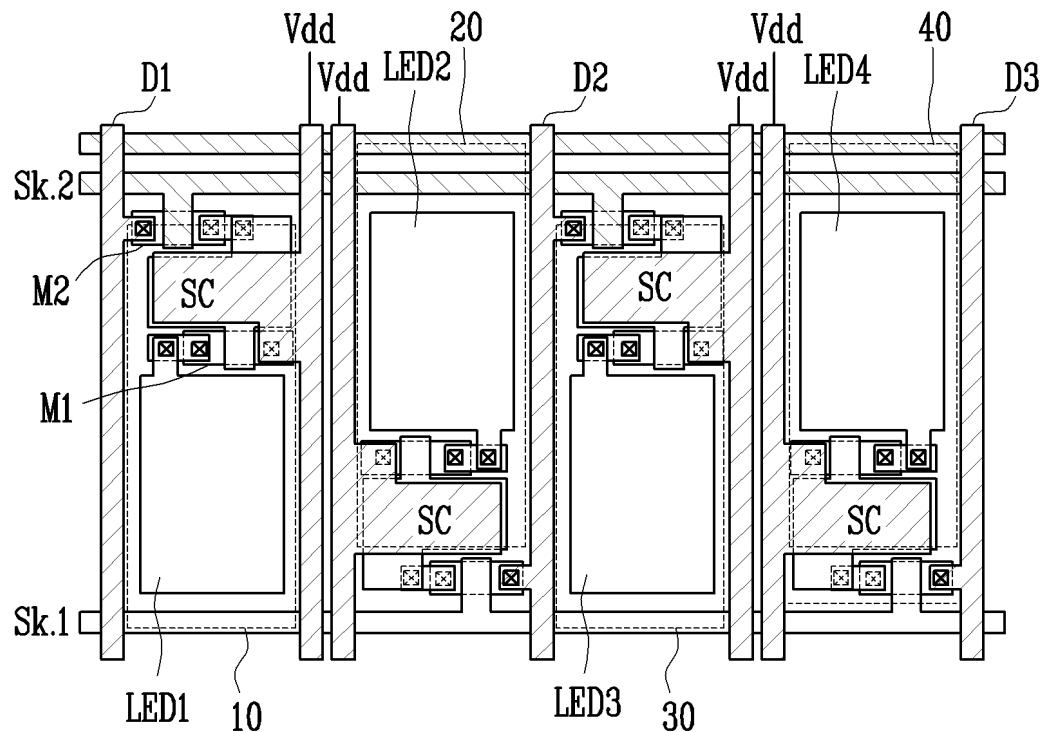

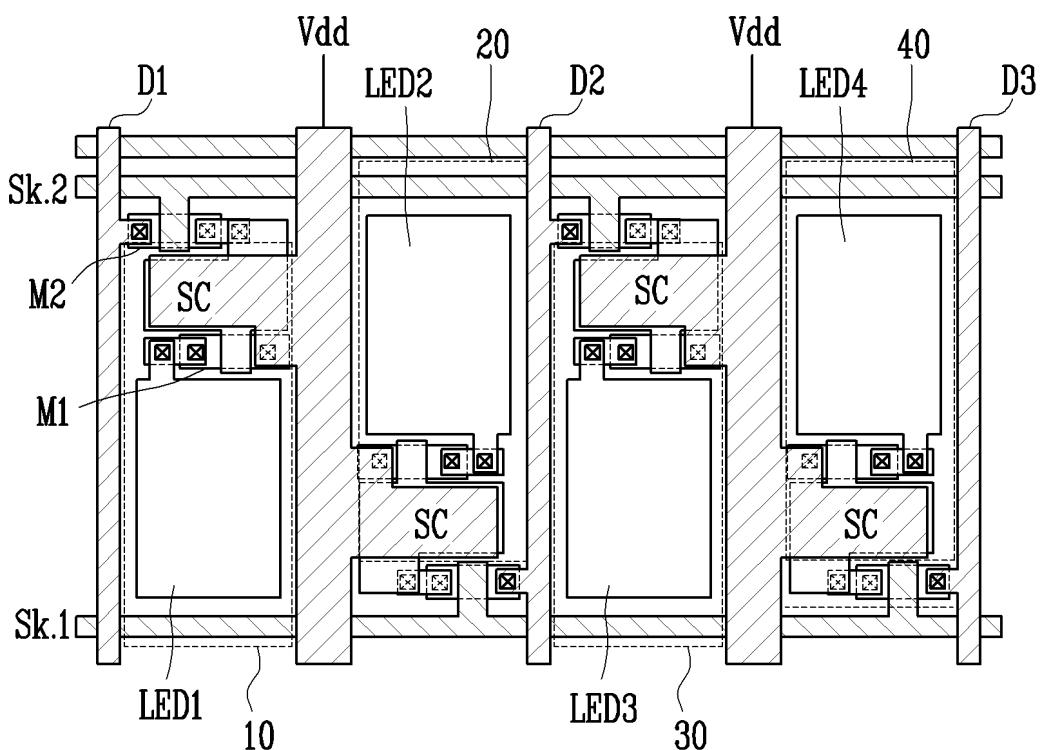

도 7은 도 4에 표현된 화소의 레이아웃에 기초한 투사평면도의 다른 예이다.

도 8은 본 발명에 따른 전계 발광 표시장치에 채용된 복수 화소에 대한 다른 등가회로도이다.

도 9는 도 8에 표현된 화소의 레이아웃에 기초한 투시 평면도이다.

도 10은 도 8에 표현된 화소의 레이아웃에 기초한 투시 평면도의 다른 예이다.

\*\*\*도면의 주요 부분에 대한 부호설명\*\*\*

100: 화소부 200: 주사 구동부

300: 데이터 구동부 S1,S2: 제 1 주사선, 제 2 주사선

D1,D2,D3: 데이터 선 M1,M2: 제 1 트랜지스터, 제 2 트랜지스터

SC: 스토리지 캐패시터 Vdd: 전원공급선

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 전계 발광 표시장치 및 그의 구동방법에 관한 것으로, 더욱 상세히 설명하면, 하나의 행에 있는 인접한 두 개의 화소는 하나의 데이터선을 공유하는 전계 발광 표시장치에 관한 것이다.

최근에 음극선관과 비교하여 무게와 부피가 작은 각종 평판 표시장치들이 개발되고 있으며 특히 발광효율, 휘도 및 시야각이 뛰어나며 응답속도가 빠른 전계 발광 표시장치가 주목받고 있다. 전계 발광 표시장치는 발광층의 재료에 따라 무기 전계 발광표시장치와 유기 전계 발광표시장치로 구별된다.

이중 유기 전계 발광 표시장치의 핵심은 빛을 발산하는 박막인 발광층이 캐소드 전극과 애노드 전극 사이에 위치하는 구조를 갖고 발광층에 전자 및 정공을 주입하여 이들을 재결합시킴으로써 여기자가 생성되며 여기자가 낮은 에너지로 떨어지면서 발광하는 특성을 가지고 있다.

도 1은 종래 기술에 따른 전계 발광 표시장치에 채용된 복수 화소의 등가회로도이다. 도 1을 참조하여 설명하면, 전계 발광 표시장치는 행 방향으로 주사선 (S)이 배열되고 열방향으로 데이터선(D1,D2,D3,D4) 및 전원 공급선(Vdd)이 배열된다. 그리고, 복수 개의 화소가 주사선(S), 데이터선(D1,D2,D3,D4) 및 전원 공급선 (Vdd)에 연결된다. 화소는 발광소자 (LED:Light Emitting Device), 제 1 트랜지스터(M1), 스토리지 캐패시터(SC) 및 제 2 트랜지스터(M2)를 포함한다.

하나의 화소에 있어서 제 2 트랜지스터(M2)의 게이트 전극에 주사선(S)은 연결되고 제 2 트랜지스터(M2)의 소스 전극은 데이터선(D1,D2,D3,D4)에 연결되며 제 2 트랜지스터(M2)의 드레인 전극은 제 1 트랜지스터(M1)의 게이트 전극에 연결된다.

또한, 제 1 트랜지스터(M1)의 소스 전극이 전원 공급선(Vdd)에 연결되고 제 1 트랜지스터(M1)의 드레인 전극이 발광소자의 애노드 전극에 연결된다. 또한 스토리지 캐패시터(SC)가 화소 전원공급선(Vdd)과 제 1 트랜지스터(M1)의 게이트 전극에 연결되는 구성을 갖게 된다.

이와 같은 구성으로 인하여, 하나의 행에 위치하는 각 화소는 제 2 트랜지스터(M2)의 게이트에 인가되는 선택신호에 의하여 제 2 트랜지스터(M2)가 온 상태가 되어, 데이터선(D1,D2,D3,D4)을 통해 데이터 신호가 제 1 트랜지스터(M1)의 게이트 전극에 인가된다. 그리고, 데이터 신호에 대응되어 제 1 트랜지스터(M1)를 통해 발광소자에 전류가 흘러 발광이 이루어지며, 발광 소자의 발광물질에 따라 적, 녹, 청색을 발광하게 된다.

또한, 스토리지 캐패시터(SC)는 전원 공급선(Vdd)의 전압과 데이터선을 통해 입력되는 전압의 차이에 해당하는 전압이 충전되며, 주사선(S)을 통해 입력되는 선택신호의 입력이 종료되어도 일정시간 동안 스토리지 캐패시터(SC)에 충전된 전압이 제 1 트랜지스터(M1)의 게이트 전극 및 소스 전극 사이에 인가되어 발광소자에 전류가 흐르게 된다.

도 2는 도 1의 전계 발광 표시장치의 레이아웃을 나타내는 투과 평면도이다. 도 2를 참조하여 설명하면, 투명기판 위에 제 1 트랜지스터(M1)와 제 2 트랜지스터 (M2)가 형성되고 제 1 트랜지스터(M1)와 제 2 트랜지스터(M2) 사이에 스토리지 캐패시터(SC)의 제 1 전극이 형성되며, 스토리지 캐패시터(SC)의 제 1 전극은 제 1 트랜지스터(M1)의 게이트 전극과 제 2 트랜지스터(M2)의 드레인 전극과 연결된다. 그리고, 제 1 트랜지스터(M1)의 드레인 전극과 화소의 애노드 전극이 연결된다.

그리고, 수평방향으로 주사선(S)이 형성되며 주사선(S)은 제 2 트랜지스터 (M2)의 게이트 전극과 연결되고, 데이터선 (D1,D2,D3,D4)과 화소 전원공급선(Vdd)이 주사선(S)과 수직으로 교차하여 형성된다.

그리고, 스토리지 캐패시터(SC)의 제 1 전극과 대향되는 위치에 스토리지 캐패시터(SC)의 제 2 전극이 형성되며 제 2 전극은 화소 전원공급선(Vdd)과 제 1 트랜지스터(M1)의 소스 전극에 연결된다.

이러한 종래 기술에 의한 전계 발광 표시 장치는 화소와 화소사이에 전압공급선과 데이터선이 인접하게 위치하게 된다. 따라서, 화소에 데이터 신호를 인가하는 데이터선과 인접한 화소에 전원을 공급하는 전원 공급선이 인접함으로 인해 데이터선과 전원공급선이 단락되는 문제점이 발생하게 된다. 또한, 화소주변의 배선구조가 복잡하게 되는 문제점이 있다.

### 발명이 이루고자 하는 기술적 과제

따라서, 본 발명은 상기 종래 기술의 문제점을 해결하기 위하여 창출된 것으로, 본 발명의 목적은 전원공급선과 데이터선이 인접하지 않도록 하여 데이터선과 화소 전원공급선이 단락되지 않도록 하며, 두 개의 화소가 전원 공급선 또는/및 데이터선을 공통으로 사용함으로써 전원공급선 또는/및 데이터선의 수가 줄어 화소주변부의 배선구조가 단순하게 되는 전계 발광 표시장치를 제공하는 것이다.

## 발명의 구성 및 작용

상기 목적을 달성하기 위하여 본 발명에 따른 전계 발광 표시장치는 복수의 화소가 복수의 행과 열로 배열되어 화상을 표시하는 화소부; 상기 복수의 화소에 데이터 신호를 인가하는 복수의 데이터선; 상기 복수의 화소에 선택신호를 인가하는 복수의 주사선; 및 상기 복수의 화소에 전원을 공급하는 복수의 전원 공급선을 포함하며, 상기 복수의 화소 중 하나의 행에 있는 인접한 두 개의 화소는 상기 복수의 데이터선 중 하나의 데이터선을 공유하고 상기 복수의 주사선 중 서로 다른 두 개의 주사선에 각각 연결된다.

바람직하게는 상기 복수의 전원 공급선 중 두 개의 전원 공급선은 상기 인접한 두 개의 화소에 각각 연결된다.

또한, 상기 복수의 전원 공급선 중 하나의 전원 공급선에는 두 개의 화소가 연결되며, 상기 두 개의 화소는 서로 다른 두 개의 데이터선과 연결된다.

또한, 상기 하나의 행에 위치하는 인접한 두 개의 화소에 연결되는 상기 두 개의 주사선은 서로 인접하게 배열된다.

또한, 상기 하나의 행에 위치하는 인접한 두 개의 화소에 연결되는 상기 두 개의 주사선은 소정의 간격을 갖고 배열된다.

또한, 상기 화소는, 주사선에 인가되는 선택신호에 응답하여 데이터선에 인가되는 데이터 신호를 제 1 노드에 인가하는 스위칭 트랜지스터; 제 1 단자는 상기 제 1 노드에 연결되고 제 2 단자는 제 2 노드에 연결되며, 일정기간 동안 일정전압을 유지하는 제 1 캐패시터; 게이트는 상기 제 1 노드에 연결되고, 소스는 상기 제 2 노드에 연결되며 상기 제 1 캐패시터에 충전된 전압에 대응하여 발광소자에 전류를 흐르게 하는 구동트랜지스터를 포함하며, 인접한 두 개의 상기 화소는 서로 다른 주사선에 연결된다.

이하, 본 발명의 실시예를 첨부한 도면을 참조하여 설명하면 다음과 같다.

도 3은 본 발명에 따른 전계 발광 표시장치의 일실시례의 구성을 나타내는 구성도이다. 도 3을 참조하여 설명하면, 본 발명에 따른 전계 발광 표시장치는 복수의 화소로 구성되는 화소부(100), 화소부(100)의 특정한 행을 선택하도록 하는 주사 구동부(200), 화소부(100)에 데이터신호를 전달하는 데이터 구동부(300)로 구성된다.

화소부(100)는 화상을 표시하는 수단으로, 복수의 주사선(S1.1, S1.2, S2.1, S2.2, ..., Sn-1.1, Sn-1.2, Sn.1, Sn.2)과 복수의 데이터선(D1, D2, ..., Dk-1, Dk)이 교차하는 영역에 위치하여 주사선(S)과 데이터선(D)에 인가되는 신호에 따라 발광하는 복수의 화소(미도시)로 이루어진다. 각 화소는 발광소자와 발광소자를 구동하는 회로를 포함한다.

그리고, 한 행의 화소에는 제 1 주사선(SN.1)과 제 2 주사선(SN.2)에 의해 선택신호가 인가된다. 또한, 하나의 행에 있는 인접한 두 화소는 하나의 데이터선 (DK)을 공유하며 상기 두 개의 화소 중 하나의 화소는 제 1 주사선(SN.1)과 연결되고, 다른 하나의 화소는 제 2 주사선(SN.2)에 연결된다. 따라서, 하나의 행에 M 개의 화소가 있으면, 데이터선의 총 수 k는 M/2 개가 된다. 여기서, K는 1에서 k 사이의 정수이고 N은 1에서 n 사이의 정수를 나타낸다.

주사 구동부(200)는 화소부(100)의 특정한 행을 선택하도록 하는 선택신호를 발생하여 화소부(100)의 주사선에 전달하는 수단이다.

데이터 구동부(300)는 화소부(100)의 데이터선과 연결되어 데이터 신호를 화소에 인가하는 수단으로, 주사선에 의해 선택되어진 복수의 화소에 데이터 신호를 인가한다.

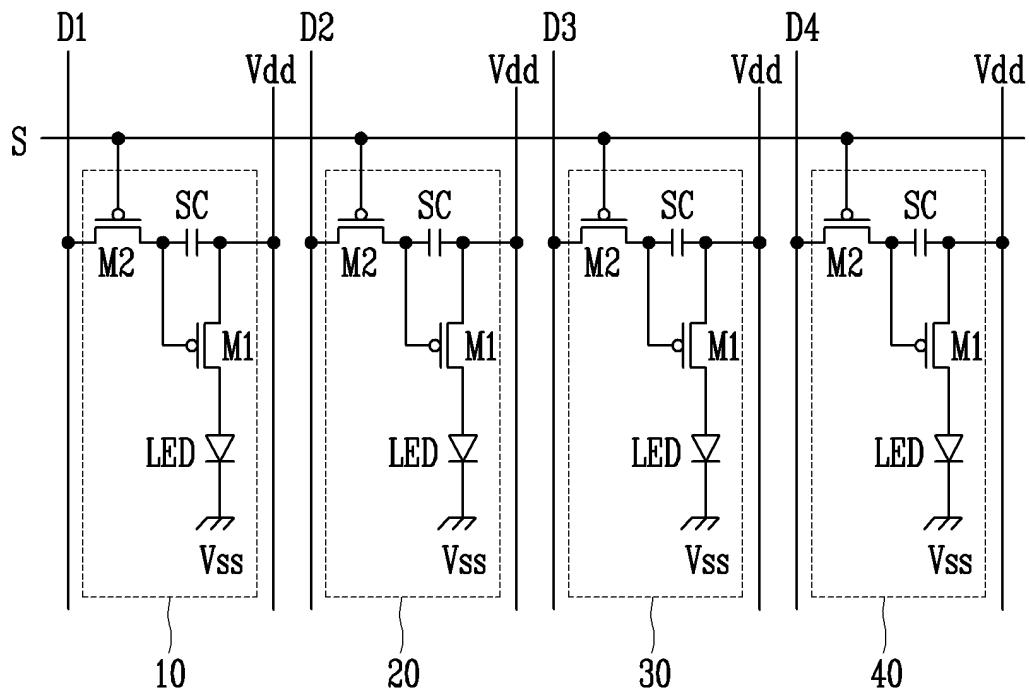

도 4는 본 발명에 따른 전계 발광 표시장치에 채용된 복수 화소의 등가회로도이다. 도 4를 참조하여 설명하면, 전계 발광 표시장치는 동일한 행에 위치하는 화소에 선택신호를 인가하는 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)이 행방향으로 배열되고 열방향으로 데이터선 및 전원 공급선이 배열된다. 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)은 도면에 도시된 바와 같이 인접하게 배열될 수도 있고 일정한 간격을 유지하며 배열될 수도 있다. 만일, 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)이 일정한 간격을 갖게 되면 그 사이에 화소가 위치하게 된다. 그리고, 복수 개의 화소에 주사선, 데이터선 및 전원 공급선이 연결된다. 화소는 발광소자(LED: Light Emitting Device), 제 1 트랜지스터(M1), 스토리지 캐패시터(SC) 및 제 2 트랜지스터(M2)를 포함한다.

그리고, 왼쪽에서 오른쪽으로 순서대로 제 1 화소(10), 제 2 화소(20), 제 3 화소(30) 및 제 4 화소(40)라 칭하며 각 화소에는 제 1 발광소자(LED1), 제 2 발광소자(LED2), 제 3 발광소자(LED3) 및 제 4 발광 소자(LED4)가 각각 포함된다.

제 2 화소(20)는 제 1 주사선(Sk.1)에 제 2 트랜지스터(M2)의 게이트 전극이 연결되고, 제 3 화소(30)는 제 1 주사선(Sk.2)에 제 2 트랜지스터(M2)의 게이트 전극이 연결된다. 그리고, 제 2 데이터선(D2)이 제 2 화소(20)와 제 3 화소(30) 사이에 위치하며 제 2 화소(20)의 제 2 트랜지스터(M2)와 제 3 화소(30)의 제 2 트랜지스터(M2)의 소스 전극이 제 2 데이터선(D2)에 연결된다. 따라서, 제 2 화소(20)와 제 3 화소(30)는 제 2 데이터선(D2)을 공유하게 된다. 그리고, 제 2 화소(20)와 제 3 화소(30)의 제 2 트랜지스터(M2)는 드레인 전극이 스토리지 캐패시터(SC)의 하부전극과 제 1 트랜지스터(M1)의 게이트 전극에 연결된다.

제 2 화소(20)에 있는 제 1 트랜지스터(M1)의 소스전극은 전원 공급선(Vdd)과 연결되고 드레인 전극은 제 2 발광소자(LED2)의 애노드 전극에 연결된다. 이때, 제 1 화소(10)는 제 2 화소(20)에 연결되어 있는 전원 공급선과 다른 전원 공급선이 연결되며, 각각의 제 1 트랜지스터(M1)의 드레인전극에 각기 다른 발광소자의 애노드 전극에 연결된다.

또한 스토리지 캐패시터(SC)가 화소 전원공급선(Vdd)과 제 1 트랜지스터(M1)의 게이트 전극에 연결되는 구성을 갖게 된다.

이와 같은 구성으로 인하여, 제 1 주사선(Sk.1)에 선택신호가 인가되면 제 2 화소(20)가 선택되어 데이터선(D2)을 통해 입력되는 데이터 신호가 제 2 화소(20)의 구동트랜지스터(M1)의 게이트전극에 인가되고, 제 2 주사선(Sk.2)에 선택신호가 인가되면 제 3 화소(30)가 선택되어 데이터선(D2)을 통해 입력되는 데이터신호가 제 3 화소(30)의 구동트랜지스터(M1)의 게이트 전극에 인가되게 된다.

그리고, 스토리지 캐패시터(SC)는 제 1 트랜지스터(M1)의 게이트 전극에 입력되는 신호를 일정시간 유지하여 상기 시간 동안 발광소자가 발광하도록 한다.

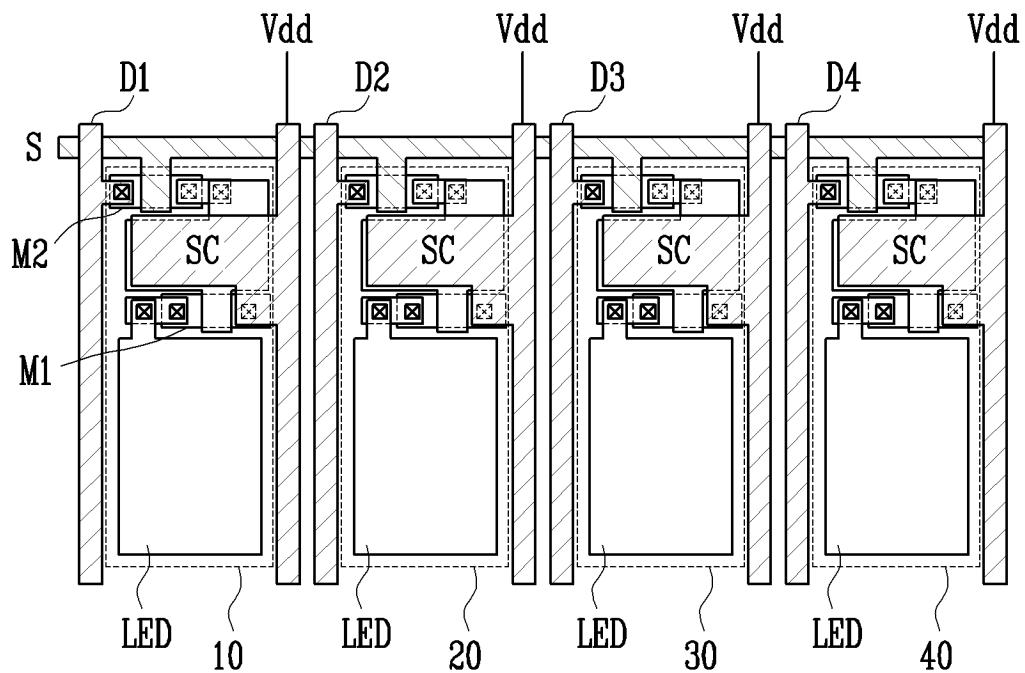

도 5는 도 4에 표현된 화소의 레이아웃에 기초한 투시 평면도이다. 도 5를 참조하여 설명하면, 인접한 4개의 화소를 왼쪽에서 오른쪽 방향으로 제 1 화소(10), 제 2 화소(20), 제 3 화소(30) 및 제 4 화소(40)라 칭한다. 각 화소의 상부에는 수평으로 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)으로 이루어진 주사선이 인접하여 형성되고 주사선(Sk.1,Sk.2)에 수직한 방향으로 일정한 간격을 갖는 복수의 데이터선(D1,D2,D3)과 전원 공급선(Vdd)이 형성된다. 그리고, 제 1 화소(10), 제 2 화소(20), 제 3 화소(30) 및 제 4 화소(40)는 각각 제 1 발광소자(LED1), 제 2 발광소자(LED2), 제 3 발광소자(LED3) 및 제 4 발광소자(LED4)가 포함된다.

데이터선(D1,D2,D3)은 제 1 화소(10)의 왼쪽, 제 2 화소(20)와 제 3 화소 (30)의 사이 그리고, 제 4 화소(40)의 오른쪽에 형성되고, 전원 공급선(Vdd)은 제 1 화소(10)의 오른쪽, 제 2 화소(20)의 왼쪽, 제 3 화소(30)의 오른쪽 및 제 4 화소(40)의 왼쪽에 형성된다.

그리고, 제 2 화소(20)와 제 4 화소(40)는 컨넥터(C)를 구비함으로써, 제 2 화소(20)와 제 4 화소(40)의 제 2 트랜지스터(M2)의 게이트 전극이 제 2 주사선 (Sk.2)에 연결되지 않고 컨넥터(C)에 의해 제 1 주사선(Sk.1)에 연결되도록 한다.

그리고, 제 1 트랜지스터(M1)와 제 2 트랜지스터(M2) 사이에 스토리지 캐패시터(SC)의 제 1 전극이 형성되며, 스토리지 캐패시터(SC)의 제 1 전극은 제 1 트랜지스터(M1)의 게이트 전극에 연결되고 제 2 트랜지스터(M2)의 드레인 전극과 연결된다. 또한, 스토리지 캐패시터(SC)의 제 2 전극은 제 1 전극에 대향되게 형성되고 전원 공급선(Vdd)에 연결된다. 그리고, 제 1 트랜지스터(M1)의 드레인 전극과 발광소자(LED)의 애노드 전극이 연결된다.

이때, 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)으로 이루어진 주사선과 발광소자 사이에 제 1 트랜지스터(M1), 제 2 트랜지스터(M2) 및 스토리지 캐패시터(SC)가 위치하도록 하여 복수의 화소의 배열이 나란하게 형성된다.

상기와 같이 형성되어, 인접한 제 2 화소(20)와 제 3 화소(30)는 하나의 데이터선을 공유하게 되고 두 개의 전원 공급선이 서로 인접하게 되며, 전원 공급선과 데이터선은 일정한 거리를 유지하게 된다.

도 6은 도 5의 VI-VI` 선에 따른 단면구조를 나타낸다. 도 6은 제 1 트랜지스터(M1), 스토리지 캐패시터(SC) 및 발광소자(LED) 만이 도시되어 있다.

유리 등의 투명 절연기판(400)상에 산화막으로 이루어지는 베퍼층(401)이 형성되고, 베퍼층(401)의 상부에 능동층(402)이 형성된다. 능동층(402)으로는 비정질 실리콘(Amorphous Silicon)을 열처리하여 얻어진 폴리실리콘(Polycrystalline Silicon)이 사용될 수 있다.

그리고, 능동층(402) 위에 산화막으로 이루어진 게이트 절연층(403)이 형성되며, 게이트 절연층(403) 위에 알루미늄 등의 금속층을 형성하고 패터닝을 하여 게이트 전극(407a)과 하부전극(407b)을 형성한다. 그리고, 능동층(402) 중 게이트 전극(407a) 아래에 위치하는 영역이 채널에 해당하고, 채널의 양측에는 이온 주입에 의해 P형 불순물이 도핑된 영역이 소스전극(402b)과 드레인전극(402a)에 해당한다.

그리고, 게이트전극(407a)과 하부전극(407b) 상부에 충간 절연막(404)을 증착하고 패터닝 하여 소스전극(402b)과 드레인전극(402a) 상부에 제 1 컨택홀(413)과 제 2 컨택홀(412)이 형성되도록 한다. 그리고, 금속층(405)을 충간 절연막(404)의 상부에 증착되고 패터닝을 하며, 금속층(405)이 제 1 컨택홀(412)과 제 2 컨택홀(413)을 통해 드레인전극(402a)과 소스전극(402b)에 접촉하도록 한다.

그리고, 금속층(405)의 상부에 보호막(406)을 증착하고 패터닝하여 보호막에 제 3 컨택홀(414)을 형성하며 보호막(406) 상부에 애노드 전극(408)을 증착하여 애노드 전극(408)이 제 3 컨택홀(414)과 제 2 컨택홀(412)을 통해 드레인 전극(402a)에 전기적으로 연결되도록 한다.

그리고, 그 상부에 절연막으로 이루어진 평탄화막(409)을 증착하고 패터닝 하여 개구부를 형성하고 개구부에 발광물질(410)을 도포하고, 발광물질(410)을 포함한 전면에 캐소드전극(411)을 형성한다.

따라서, 능동층(402)에 형성된 소스전극(402b)과 드레인전극(402a) 및 능동층(402) 상부에 형성되어 있는 게이트 전극(407a)에 의해 제 1 트랜지스터(M1)가 형성되고, 하부전극(407b)과 하부전극(407b) 상부에 위치하는 금속층(405)에 의해 스토리지 캐패시터(SC)가 형성된다. 또한, 애노드 전극(408), 발광물질(410) 및 캐소드 전극(411)에 의해 발광소자가 형성된다.

도 7은 도 4에 표현된 화소의 레이아웃에 기초한 투사평면도의 다른 예이다. 도 7을 참조하여 설명하면, 인접한 4개의 화소를 왼쪽에서 오른쪽 방향으로 제 1 화소(10), 제 2 화소(20), 제 3 화소(30) 및 제 4 화소(40)라 칭한다. 각 발광소자의 하부와 상부에 각각 수평으로 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)으로 이루어진 주사선이 형성된다. 그리고, 주사선에 수직으로 일정한 간격을 갖고 데이터선(D1,D2,D3)과 전원 공급선(Vdd)이 형성되며, 데이터선(D1,D2,D3)은 제 1 화소(10)의 왼쪽, 제 2 화소(20)와 제 3 화소(30)의 사이 및 제 4 화소(40)의 오른쪽에 형성되고, 제 1 화소(10)의 오른쪽, 제 2 화소(20)의 왼쪽, 제 3 화소(30)의 오른쪽, 제 4 화소(40)의 왼쪽에 전원 공급선(Vdd)이 형성된다.

그리고, 제 1 화소(10)와 제 3 화소(30)는 화소의 상부에 있는 제 2 주사선(Sk.2)을 통해 선택신호를 인가받고, 제 2 화소(20)와 제 4 화소(40)는 화소의 하부에 있는 제 1 주사선(Sk.1)을 통해 선택신호를 인가받게 된다.

화소는 제 1 트랜지스터(M1)를 통해 전원 공급선(Vdd)과 연결되며, 제 1 트랜지스터(M1)의 드레인 전극은 제 1 발광소자(LED1)의 애노드 전극과 연결되고, 소스 전극은 전원 공급선(Vdd)과 연결된다. 그리고, 게이트 전극은 제 2 트랜지스터(M2)를 통해 데이터선(D1,D2,D3)과 연결된다. 또한, 전원 공급선(Vdd)과 게이트 전극 사이에 스토리지 캐패시터(SC)가 연결된다.

제 2 트랜지스터(M2)는 게이트 전극이 주사선의 제 1 주사선(Sk.1)과 연결되며, 소스 전극은 데이터선(D1,D2,D3)과 연결된다. 또한, 드레인 전극은 제 1 트랜지스터(M1)의 게이트 전극과 연결된다.

따라서, 제 2 화소(20)와 제 3 화소(30) 사이에 표시된 것과 같이 인접한 두 개의 화소는 하나의 데이터선(D2)을 공유하게 되고, 두 개의 전원 공급선(Vdd)은 인접하게 된다.

도 8은 본 발명에 따른 전계 발광 표시장치에 채용된 복수 화소에 대한 다른 등가회로도이다. 도 8을 참조하여 설명하면, 전계 발광 표시장치는 동일한 행에 위치하는 화소에 선택신호를 인가하는 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)이 행방향으로 배열되고 데이터선 및 전원 공급선이 열방향으로 배열된다. 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)은 도면에 도시된 바와 같이 인접하게 배열될 수도 있고 일정한 간격을 유지하며 배열될 수도 있다. 만일, 제 1 주사선(Sk.1)과 제 2 주사

선(Sk.2)이 일정한 간격을 갖게 되면 그 사이에 화소가 위치하게 된다. 그리고, 복수 개의 화소가 주사선, 데이터선 및 전원 공급선에 연결된다. 화소는 발광소자(LED: Light Emitting Device), 제 1 트랜지스터(M1), 스토리지 캐패시터(SC) 및 제 2 트랜지스터(M2)를 포함한다.

그리고, 왼쪽에서 오른쪽으로 순서대로 제 1 화소(10), 제 2 화소(20), 제 3 화소(30) 및 제 4 화소(40)라 칭하고 설명하면, 제 2 화소(20)는 제 1 주사선 (Sk.1)에 제 2 트랜지스터(M2)의 게이트 전극이 연결되고, 제 3 화소(30)는 제 2 주사선 (Sk.2)에 제 2 트랜지스터(M2)의 게이트 전극이 연결된다. 그리고, 제 2 데이터선(D2)이 제 2 화소(20)와 제 3 화소(30) 사이에 위치하며 제 2 화소(20)의 제 2 트랜지스터(M2)와 제 3 화소(30)의 제 2 트랜지스터(M2)의 소스 전극이 제 2 데이터선(D2)에 연결된다. 따라서, 제 2 화소(20)와 제 3 화소(30)는 데이터선을 공유하게 된다. 그리고, 제 2 화소(20)와 제 3 화소(30)의 제 2 트랜지스터(M2)는 드레인 전극이 스토리지 캐패시터(SC)의 하부전극과 제 1 트랜지스터(M1)의 게이트 전극에 연결된다.

그리고, 제 1 화소(10)와 제 2 화소(20), 제 3 화소(30)와 제 4 화소(40) 사이에 하나의 전원 공급선이 위치하며, 제 1 화소(10)와 제 2 화소(20) 및 제 3 화소(30)와 제 4 화소(40)는 각각 하나의 전원 공급선(Vdd)을 공유한다.

제 2 화소(20)에 있는 제 1 트랜지스터(M1)의 소스전극은 전원 공급선(Vdd)과 연결되고 드레인 전극은 발광소자의 애노드 전극에 연결된다. 이때, 제 1 화소 (10)는 제 2 화소(20)에 연결되어 있는 전원 공급선과 다른 전원 공급선이 연결되며, 각각의 제 1 트랜지스터(M1)의 드레인전극에 각기 다른 발광소자의 애노드 전극에 연결된다.

또한 스토리지 캐패시터(SC)가 화소 전원공급선(Vdd)과 제 1 트랜지스터(M1)의 게이트 전극에 연결되는 구성을 갖게 된다.

이와 같은 구성으로 인하여, 제 1 주사선에 선택신호가 인가되면 제 2 화소 (20)가 선택되어 데이터선(D2)을 통해 입력되는 데이터신호가 제 2 화소(20)의 제 1 트랜지스터(M1)의 게이트 전극에 인가되고, 제 2 주사선에 선택신호가 인가되면 제 3 화소가 선택되어 데이터선(D2)을 통해 입력되는 데이터신호가 제 3 화소(30)의 제 1 트랜지스터(M1)의 게이트 전극에 인가되게 된다.

그리고, 스토리지 캐패시터(SC)는 제 1 트랜지스터(M1)의 게이트 전극에 입력되는 신호를 일정시간 유지시켜 상기 시간 동안 발광소자가 발광하도록 한다.

도 9는 도 8에 표현된 화소의 레이아웃에 기초한 투시 평면도이다. 도 9를 참조하여 설명하면, 인접한 4개의 화소(10)를 왼쪽에서 오른쪽 방향으로 제 1 화소 (10), 제 2 화소(20), 제 3 화소(30) 및 제 4 화소(40)라 칭한다. 각 화소의 상부에는 수평으로 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)으로 이루어진 주사선 (Sk.1,Sk.2)이 인접하여 나란하게 형성된다.

그리고, 주사선(Sk.1,Sk.2)에 수직한 방향으로 일정한 간격을 갖는 데이터선 (D1,D2,D3)이 형성되며, 데이터선 (D1,D2,D3)은 제 1 화소(10)의 왼쪽, 제 2 화소 (20)와 제 3 화소(30)의 사이 및 제 4 화소(40)의 오른쪽에 형성되고, 제 1 화소 (10)와 제 2 화소(20) 사이, 제 3 화소(30)와 제 4 화소(40) 사이에 전원 공급선 (Vdd)이 형성된다. 그리고, 제 1 화소 (10), 제 2 화소(20), 제 3 화소(30) 및 제 4 화소(40)는 각각 제 1 발광소자(LED1), 제 2 발광소자(LED2), 제 3 발광소자(LED3) 및 제 4 발광소자(LED4)를 포함한다.

따라서, 제 2 화소(20)와 제 3 화소(30) 사이에 표시된 것과 같이 인접한 두 개의 화소는 하나의 데이터선과 하나의 전원 공급선을 공유하게 된다.

또한, 제 2 화소(20)와 제 4 화소(40)가 연결되며 제 1 주사선(Sk.1)과 연결되고 제 2 주사선(Sk.2)에는 연결되지 않도록 하기 위해 컨넥터(C)를 구비하여 제 2 발광소자(LED2)와 제 4 발광소자(LED4)의 제 2 트랜지스터(M1)의 게이트 전극이 컨넥터(C)에 의해 제 2 주사선(Sk.2)에 연결되지 않고 제 1 주사선(Sk.1)에 연결되도록 한다.

그리고, 하나의 전원 공급선(Vdd)에 연결되며, 서로 대칭되는 방향으로 스토리지 캐패시터(SC)가 형성되도록 한다.

스토리지 캐패시터(SC)의 연결은 도 5의 설명과 동일하며 생략한다.

도 10은 도 8에 표현된 화소의 레이아웃에 기초한 투시 평면도의 다른 예이다. 도 10을 참조하여 설명하면, 왼쪽에서 오른쪽 방향으로 제 1 화소(10), 제 2 화소(20), 제 3 화소(30) 및 제 4 화소(40)라 칭한다. 각 화소의 하부와 상부에 각각 수평으로 제 1 주사선(Sk.1)과 제 2 주사선(Sk.2)으로 이루어진 주사선이 형성된다. 그리고, 주사선에 수직으로 일정한 간격을

갖고 데이터선(D1,D2,D3)과 전원 공급선(Vdd)이 형성되며, 데이터선은 제 1 화소(10)의 왼쪽, 제 2 화소(20)와 제 3 화소(30)의 사이 그리고, 제 4 화소(40)의 오른쪽에 형성되고, 제 1 화소(10)와 제 2 발광소자 (20) 사이, 제 3 화소(30)와 제 4 화소(40) 사이에 전원 공급선 (Vdd)이 형성된다. 따라서, 인접한 두 개의 화소는 하나의 데이터선과 전원 공급선(Vdd)을 공유하게 된다.

그리고, 제 1 발광소자(LED1)와 제 3 발광소자(LED3)는 화소의 상부에 있는 제 2 주사선(Sk.2)을 통해 선택신호를 인가받고, 제 2 발광소자(LED2)와 제 4 발광소자(LED4)는 화소의 하부에 있는 제 1 주사선(Sk.1)을 통해 선택신호를 인가받게 된다. 따라서, 인접한 두 개의 화소의 구성은 서로 180도 대칭한 형태로 나타나게 된다.

제 2 화소(20)는 제 1 트랜지스터(M1)를 통해 전원 공급선(Vdd)과 연결되며, 제 1 트랜지스터(M1)의 드레인 전극은 제 1 발광소자(LED1)의 애노드 전극과 연결되고, 소스 전극은 전원 공급선(Vdd)과 연결된다. 그리고, 게이트 전극은 제 2 트랜지스터(M2)를 통해 데이터선과 연결된다. 또한, 전원 공급선(Vdd)과 게이트 전극의 사이에 스토리지 캐패시터(SC)가 연결된다.

제 2 트랜지스터(M2)는 게이트 전극이 주사선의 제 1 주사선(Sk.1)과 연결되며, 소스 전극은 데이터선(D2)과 연결된다. 또한, 드레인 전극은 제 1 트랜지스터 (M1)의 게이트 전극과 연결되며, 제 3 화소(30)는 제 2 화소(20)과 동일한 구성을 갖고, 제 2 트랜지스터(M2)가 제 2 주사선(Sk.2)에 연결되는 구성을 한다.

따라서, 제 2 화소(20)와 제 3 화소(30) 사이에 도시된 바와 같이 인접한 두 개의 발광소자는 하나의 데이터선과 하나의 전원 공급선을 공유하게 된다.

상기 도 3 내지 도 10에 도시된 전계발광 표시장치는 제 1 트랜지스터(M1)의 문턱전압의 크기가 다른 경우에 각 화소에 흐르는 전류량에 차이가 생기게 되어, 균일한 화상을 표시하기 어렵다는 문제점이 있다. 따라서, 이러한 문제점을 해결하기 위해  $V_{th}$  전압의 크기에 관계 없이 화소에 흐르는 전류량이 일정하도록 하여 화상을 표시하도록 하는 여러 방법이 제안되고 있다.

이러한 전류량이 일정하도록 하는 방법에도 도 3 내지 도 10에 도시되어 있는 것과 같이 주사선과 데이터선을 구성할 수 있어, 전원 공급선과 데이터선이 인접하지 않도록 하여 전원 공급선과 데이터선 간에 단락이 발생하지 않도록 하는 것도 가능하다.

본 발명의 바람직한 실시례가 특정 용어들을 사용하여 기술되어 왔지만, 그러한 기술은 단지 설명을 하기 위한 것이며, 다음의 청구범위의 기술적 사상 및 범위로부터 이탈되지 않고 여러 가지 변경 및 변화가 가능할 수 있는 것으로 이해되어져야 한다.

### 발명의 효과

본 발명에 따른 전계 발광 표시장치는 전원 공급선과 데이터선이 사이에 화소가 위치하게 되어 전원 공급선과 데이터선이 일정한 거리를 유지할 수 있게 되어 전원 공급선과 데이터선 상호간에 단락 불량이 발생하는 것을 방지할 수 있다.

또한, 두 개의 화소가 하나의 데이터선 또는/및 전원 공급선을 공통으로 사용하게 되어 전계 발광 표시장치의 화소 주변의 배선의 수를 줄이고 간단히 할 수 있어 전계 발광 표시장치의 공정을 단순히 하여 생산 비를 절감할 수 있게 된다.

### (57) 청구의 범위

#### 청구항 1.

복수의 화소가 복수의 행과 열로 배열되어 화상을 표시하는 화소부;

상기 복수의 화소에 데이터 신호를 인가하는 복수의 데이터선;

상기 복수의 화소에 선택신호를 인가하는 복수의 주사선; 및

상기 복수의 화소에 전원을 공급하는 복수의 전원 공급선을 포함하며,

상기 복수의 화소 중 하나의 행에 있는 인접한 두 개의 화소는 상기 복수의 데이터선 중 하나의 데이터선을 공유하고 상기 복수의 주사선 중 서로 다른 두 개의 주사선에 각각 연결되는 전계 발광 표시장치.

## 청구항 2.

제 1 항에 있어서,

상기 복수의 전원 공급선 중 두 개의 전원 공급선은 상기 인접한 두 개의 화소에 각각 연결되는 전계 발광 표시장치.

## 청구항 3.

제 1 항에 있어서,

상기 복수의 전원 공급선 중 하나의 전원 공급선에는 두 개의 화소가 연결되며, 상기 두 개의 화소는 서로 다른 두 개의 데이터선과 연결되는 전계 발광 표시장치.

## 청구항 4.

제 1 항에 있어서,

상기 하나의 행에 위치하는 인접한 두 개의 화소에 연결되는 상기 두 개의 주사선은 서로 인접하게 배열되는 전계 발광 표시장치.

## 청구항 5.

제 1 항에 있어서,

상기 하나의 행에 위치하는 인접한 두 개의 화소에 연결되는 상기 두 개의 주사선은 상기 화소를 사이에 두고 대향 배치되는 전계 발광 표시장치.

## 청구항 6.

제 1 항에 있어서,

상기 화소는, 주사선에 인가되는 선택신호에 응답하여 데이터선에 인가되는 데이터 신호를 제 1 노드에 인가하는 스위칭 트랜지스터;

제 1 단자는 상기 제 1 노드에 연결되고 제 2 단자는 전원공급선에 연결되며, 일정기간 동안 일정전압을 유지하는 제 1 캐페시터;

케이트는 상기 제 1 노드에 연결되고, 소스는 상기 전원공급선에 연결되며 상기 제 1 캐페시터에 충전된 전압에 대응하여 발광소자에 전류를 흐르게 하는 구동트랜지스터를 포함하며,

인접한 두 개의 상기 화소는 서로 다른 주사선에 연결되는 전계 발광 표시장치.

도면

도면1

도면2

도면3

도면4

## 도면5

도면6

도면7

도면8

도면9

도면10

|               |                                                                                              |         |            |

|---------------|----------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)       | 电致发光显示器                                                                                      |         |            |

| 公开(公告)号       | <a href="#">KR100583135B1</a>                                                                | 公开(公告)日 | 2006-05-23 |

| 申请号           | KR1020040041588                                                                              | 申请日     | 2004-06-08 |

| 申请(专利权)人(译)   | 三星SD眼有限公司                                                                                    |         |            |

| 当前申请(专利权)人(译) | 三星SD眼有限公司                                                                                    |         |            |

| [标]发明人        | KANG TAEWOOK<br>강태욱<br>SHIN DONGYONG<br>신동용<br>JEONG CHANGYONG<br>정창용<br>KIM CHANGSOO<br>김창수 |         |            |

| 发明人           | 강태욱<br>신동용<br>정창용<br>김창수                                                                     |         |            |

| IPC分类号        | H05B33/00 H05B33/08                                                                          |         |            |

| CPC分类号        | Y02B20/343                                                                                   |         |            |

| 代理人(译)        | SHIN , YOUNG MOO                                                                             |         |            |

| 其他公开文献        | KR1020050116509A                                                                             |         |            |

| 外部链接          | <a href="#">Espacenet</a>                                                                    |         |            |

## 摘要(译)

电致发光显示装置本发明涉及一种电致发光显示装置，更具体地说，涉及一种电致发光显示装置，其中多个像素以多行和多列排列以显示图像，多个数据线被数据信号施加到多个像素，要应用的多条扫描线和多个电源并且，所述多个像素中的一行中的两个相邻像素共享所述多条数据线中的一条数据线，并连接到所述多条扫描线中的两条不同的扫描线，的。像素位于电源线和数据线之间从而可以防止电源线和数据线之间发生短路故障。另外，由于两个像素通常使用一条数据线和/或电源线，所以可以减少电致发光显示装置的像素周围的布线数量。3指教方面 有机EL，像素，段落，