**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) . Int. Cl.<sup>7</sup>

H05B 33/00

(11) 공개번호 10-2005-0080406

(43) 공개일자 2005년08월12일

(21) 출원번호 10-2004-0008494

(22) 출원일자 2004년02월09일

(71) 출원인 삼성에스디아이 주식회사

경기 수원시 영통구 신동 575

(72) 발명자 이현정

경기도안양시만안구안양1동삼성래미안아파트107동504호

박상일

서울특별시양천구신정4동983-12호한솔그린아트빌B동501호

(74) 대리인 박상수

**심사청구 : 있음**

**(54) 유기전계발광표시장치 및 그의 제조방법**

**요약**

유기전계발광표시장치 및 그의 제조방법을 제공한다. 상기 유기전계발광표시장치는 회로영역 및 화소영역을 구비하는 기판; 상기 기판의 회로영역 및 화소영역 상에 각각 위치하고, 반도체층, 게이트 전극 및 한 쌍의 소오스/드레인 전극을 구비하는 회로 TFT 및 화소 TFT; 상기 화소 TFT의 소오스/드레인 전극과 전기적으로 연결된 화소전극; 및 상기 소오스/드레인 전극과 상기 기판 사이에 위치하고, 상기 전 화소영역에서 오픈된 적어도 한층의 실리콘 질화막 패턴을 포함한다.

**대표도**

도 1d

**색인어**

유기전계발광표시장치, 실리콘 질화막, 화소 TFT, 회로 TFT, 휘도

**명세서**

**도면의 간단한 설명**

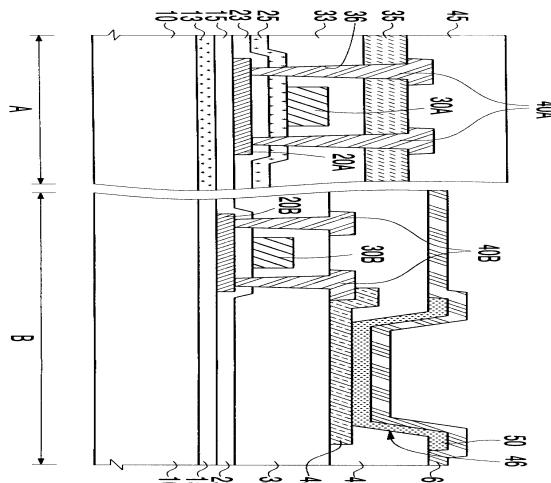

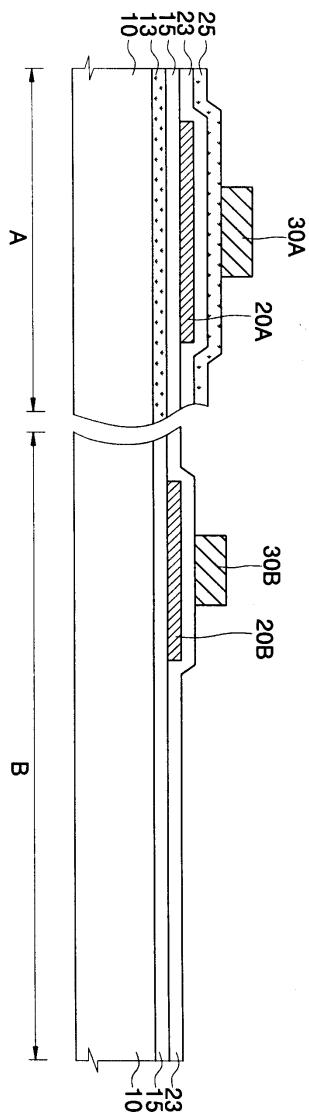

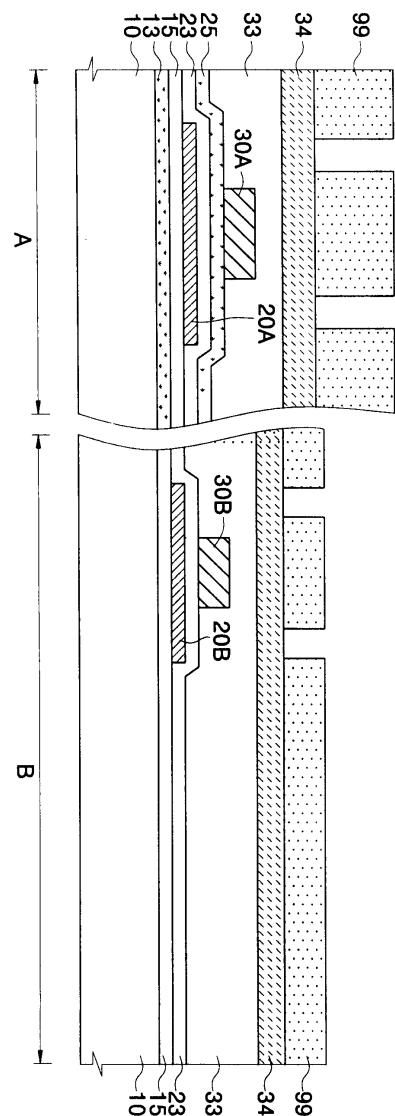

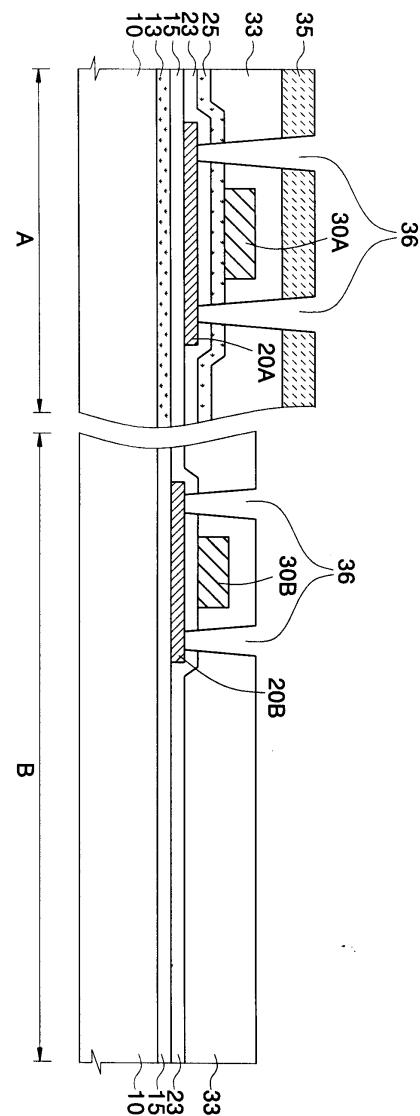

도 1a 내지 1d는 본 발명의 실시예에 따른 유기전계발광소자 및 그의 제조방법을 설명하기 위한 단면도들이다.

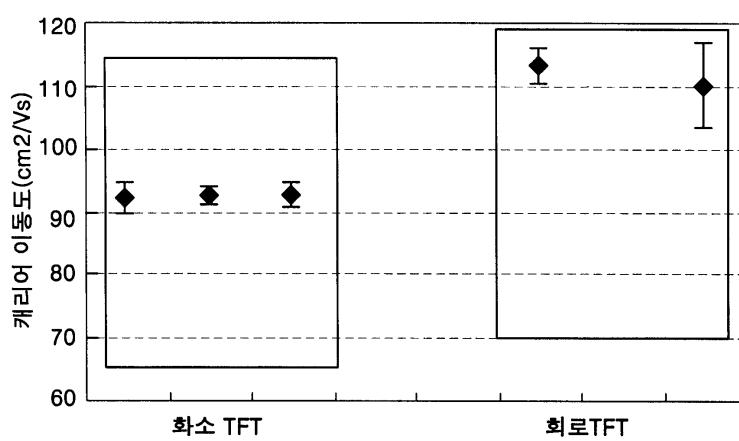

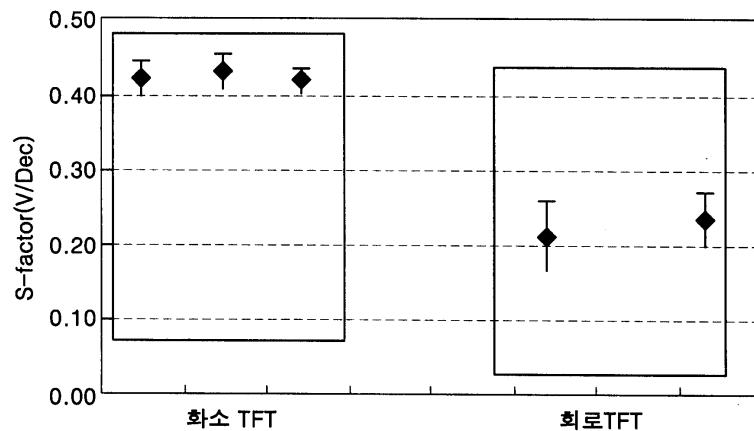

도 2a는 본 발명의 실시예에 따라 제조된 화소 TFT와 회로 TFT의 캐리어 이동도를 보여주는 그래프이다.

도 2b는 본 발명의 실시예에 따라 제조된 화소 TFT와 회로 TFT의 에스-펙터값을 보여주는 그래프이다.

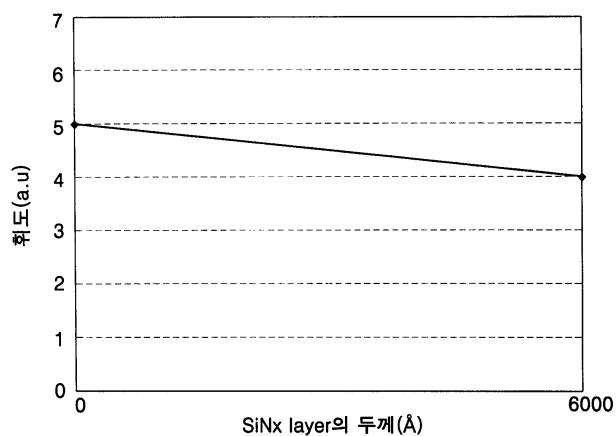

도 3은 실리콘 질화막의 두께에 따른 휘도의 변화를 나타낸 그래프이다.

(도면의 주요 부위에 대한 부호의 설명)

10 : 기판 13, 25, 34 : 실리콘 질화막 패턴

20A, 20B : 반도체층 30A, 30B : 게이트 전극

40A, 40B : 소오스/드레인 전극 43 : 화소전극

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 표시장치 및 그의 제조방법에 관한 것으로, 더욱 자세하게는 유기전계발광표시장치 및 그의 제조방법에 관한 것이다.

유기전계발광표시장치는 매트릭스 형태로 위치한  $N \times M$  개의 단위화소(sub-pixel)를 구비하는데, 상기  $N \times M$  개의 단위화소들을 구동하는 방식에 따라 수동 매트릭스(passive matrix)방식과 능동 매트릭스(active matrix)방식으로 나뉘어진다.

상기 능동 매트릭스 방식의 유기전계발광표시장치의 단위화소는 화소전극과 상기 화소전극에 전기적 신호를 인가하기 위한 적어도 하나의 박막트랜지스터를 구비한다. 더 나아가서, 상기 능동 매트릭스 방식의 유기전계발광표시장치는 단위화소가 매트릭스 형태로 위치한 화소부와 상기 화소부를 제어하기 위한 회로를 갖는 회로부를 하나의 기판 상에 구비할 수 있다. 상기 회로부는 상기 화소부의 주변부에 위치하며, 상기 화소부를 제어하기 위한 회로는 박막트랜지스터로 구성되어 진다. 결론적으로 능동 매트릭스 방식의 유기전계발광표시장치는 화소부와 회로부에 각각 박막트랜지스터들 즉, 화소TFT와 회로TFT를 구비할 수 있다.

이러한 박막트랜지스터가 일본공개특허 특개평5-55582호에 개시된 바 있다. 상기 일본공개특허에 개시된 박막트랜지스터는 절연성 기판 상에 위치하는 질화규소로 형성된 제1블로킹막, 상기 제1블로킹막 상에 위치하는 산화규소로 형성된 절연성 피막, 상기 절연성 피막 상에 위치하는 반도체층, 상기 반도체층 상에 위치하는 게이트 전극, 상기 게이트 전극 상에 위치하는 질화규소로 형성된 제2블로킹막, 상기 제2블로킹막 상에 위치하는 PSG로 형성된 층간절연막을 구비한다. 그러나, 이러한 박막트랜지스터를 회로 TFT와 화소 TFT에 공통으로 적용하는 것은 서로 다른 전기적 특성을 필요로 하는 상기 회로 TFT와 상기 화소 TFT의 전기적 특성을 최적화시키는 것을 저해할 수 있다.

#### 발명이 이루고자 하는 기술적 과제

본 발명이 이루고자 하는 기술적 과제는 상기한 종래기술의 문제점을 해결하기 위한 것으로, 회로 TFT와 화소 TFT 각각의 전기적 특성이 최적화된 유기전계발광표시장치를 제공함에 있다.

#### 발명의 구성 및 작용

상기 기술적 과제를 이루기 위하여 본 발명은 유기전계발광표시장치를 제공한다. 상기 유기전계발광표시장치는 회로영역 및 화소영역을 구비하는 기판; 상기 기판의 회로영역 및 화소영역 상에 각각 위치하고, 반도체층, 게이트 전극 및 한 쌍의 소오스/드레인 전극을 구비하는 회로 TFT 및 화소 TFT; 상기 화소 TFT의 소오스/드레인 전극과 전기적으로 연결된 화소전극; 및 상기 소오스/드레인 전극과 상기 기판 사이에 위치하고, 상기 전 화소영역에서 오픈된 적어도 한 층의 실리콘 질화막 패턴을 포함한다.

상기 유기전계발광표시장치는 상기 소오스/드레인 전극과 상기 기판 사이에 위치하는 적어도 한 층의 실리콘 산화막을 더욱 포함할 수 있다.

상기 실리콘 질화막 패턴은 SiNx 또는 SiON로 이루어질 수 있다.

상기 실리콘 질화막 패턴은 상기 기판과 상기 회로 TFT의 반도체층 사이에 위치하는 베퍼 질화막 패턴일 수 있다. 더 나아가서, 상기 유기전계발광표시장치는 상기 기판과 상기 베퍼 질화막 패턴 사이 또는 상기 베퍼 질화막 패턴과 상기 회로 TFT의 반도체층 사이; 및 상기 기판과 상기 화소 TFT의 반도체층 사이에 위치하는 베퍼 실리콘 산화막을 더욱 포함할 수 있다.

상기 실리콘 질화막 패턴은 상기 회로 TFT의 반도체층과 상기 회로 TFT의 게이트 전극 사이에 위치하는 게이트 절연 질화막 패턴일 수 있다. 더 나아가서, 상기 유기전계발광표시장치는 상기 회로 TFT의 반도체층과 상기 게이트 절연 질화막 패턴 사이 또는 상기 게이트 절연 질화막 패턴과 상기 회로 TFT의 게이트 전극 사이; 및 상기 화소 TFT의 반도체층과 상기 화소 TFT의 게이트 전극 사이에 위치하는 게이트 절연 실리콘 산화막을 더욱 포함할 수 있다.

상기 실리콘 질화막 패턴은 상기 회로 TFT의 게이트 전극과 상기 회로 TFT의 소오스/드레인 전극 사이에 위치하는 층간 질화막 패턴일 수 있다. 더 나아가서, 상기 유기전계발광표시장치는 상기 회로 TFT의 게이트 전극과 상기 층간 질화막 패턴 사이 또는 상기 층간 질화막 패턴과 상기 회로 TFT의 소오스/드레인 전극 사이; 및 상기 화소 TFT의 게이트 전극과 상기 화소 TFT의 소오스/드레인 전극 사이에 위치하는 층간 실리콘 산화막을 더욱 포함할 수 있다.

상기 반도체층은 다결정 실리콘으로 이루어진 것이 바람직하다. 또한, 상기 화소전극은 투명전극인 것이 바람직하다.

상기 유기전계발광표시장치는 상기 화소전극 상에 위치하는 발광층 및 상기 발광층 상에 위치하는 대향전극을 더욱 포함할 수 있다.

상기 기술적 과제를 이루기 위하여 본 발명은 유기전계발광표시장치의 제조방법을 제공한다. 상기 제조방법은 회로영역 및 화소영역을 구비하는 기판을 제공하고; 상기 기판의 회로영역 및 화소영역 상에 반도체층, 게이트 전극 및 한 쌍의 소오스/드레인 전극을 구비하는 회로 TFT 및 화소 TFT를 각각 형성하고; 상기 화소 TFT의 소오스/드레인 전극과 전기적으로 연결된 화소전극을 형성하고; 상기 소오스/드레인 전극을 형성하기 전에, 상기 기판 상에 상기 전 화소영역에서 오픈된 적어도 한층의 실리콘 질화막 패턴을 형성하는 것을 포함한다.

상기 제조방법은 상기 소오스/드레인 전극을 형성하기 전에, 상기 기판 상에 적어도 한층의 실리콘 산화막을 형성하는 것을 더욱 포함할 수 있다.

상기 실리콘 질화막 패턴은 SiNx 또는 SiON으로 형성할 수 있다.

상기 실리콘 질화막 패턴은 상기 반도체층을 형성하기 전에 상기 기판 상에 형성하는 베퍼 질화막 패턴일 수 있다. 이 경우, 상기 제조방법은 상기 베퍼 질화막 패턴을 형성하기 전 또는 상기 베퍼 질화막 패턴을 형성한 후, 상기 기판 전면에 베퍼 실리콘 산화막을 형성하는 것을 더욱 포함한다.

상기 실리콘 질화막 패턴은 상기 게이트 전극을 형성하기 전에 상기 반도체층 상에 형성하는 게이트 절연 질화막 패턴일 수 있다. 이 경우, 상기 제조방법은 상기 게이트 절연 질화막 패턴을 형성하기 전 또는 상기 게이트 절연 질화막 패턴을 형성한 후, 상기 기판 전면에 게이트 절연 실리콘 산화막을 형성하는 것을 더욱 포함할 수 있다.

상기 실리콘 질화막 패턴은 상기 소오스/드레인 전극을 형성하기 전에 상기 게이트 전극 상에 형성하는 층간 질화막 패턴일 수 있다. 이 경우, 상기 층간 질화막 패턴을 형성하는 것은 상기 게이트 전극 상에 층간 실리콘 산화막과 층간 질화막을 차례로 형성하고, 하프톤 마스크를 사용하여 상기 층간 질화막 및 상기 층간 실리콘 산화막 내에 소오스/드레인 콘택홀을 형성함과 동시에 형성하는 것이 바람직하다.

이하, 본 발명을 보다 구체적으로 설명하기 위하여 본 발명에 따른 바람직한 실시예를 첨부된 도면을 참조하여 보다 상세하게 설명한다. 그러나, 본 발명은 여기서 설명되어지는 실시예에 한정되지 않고 다른 형태로 구체화될 수도 있다. 오히려 여기서 소개되는 실시예는 개시된 내용이 철저하고 완전해질 수 있도록 그리고 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위해 제공되어지는 것이다. 도면들에 있어서, 층이 다른 층 또는 기판 "상"에 있다고 언급되어지는 경우에 그것은 다른 층 또는 기판 상에 직접 형성될 수 있거나 또는 그들 사이에 제 3의 층이 개재될 수도 있다. 명세서 전체에 걸쳐서 동일한 참조번호들은 동일한 구성요소를 나타낸다.

도 1d는 본 발명의 실시예에 따른 유기전계발광소자를 설명하기 위한 단면도이다.

도 1d를 참조하면, 본 발명의 실시예에 따른 유기전계발광소자는 회로영역(A) 및 화소영역(B)을 구비하는 기판(10)을 포함한다. 상기 화소영역(B)은 단위화소들이 매트릭스 형태로 위치하는 영역이고, 상기 회로영역(A)은 상기 단위화소들을 전기적으로 제어하기 위한 회로가 위치하는 영역으로서, 도면에는 상기 각 영역의 일부가 도시되었다.

상기 기판의 회로영역(A) 상에 회로 박막트랜지스터(이하, 회로 TFT라 한다)가 위치한다. 상기 회로 박막트랜지스터는 반도체층(20A), 상기 반도체층(20A)과 일부 중첩되는 게이트 전극(30A) 및 상기 반도체층(20A)의 양단부에 전기적으로 접하는 한 쌍의 소오스/드레인 전극(40A)을 구비한다. 한편, 상기 기판의 화소영역(B) 상에 화소 박막트랜지스터(이하, 화소 TFT라 한다)가 위치한다. 상기 화소 박막트랜지스터 또한 반도체층(20B), 상기 반도체층(20B)과 일부 중첩되는 게이트 전극(30B) 및 상기 반도체층(20B)의 양단부에 전기적으로 접하는 한 쌍의 소오스/드레인 전극(40B)을 구비한다. 상기 반도체층(20A, 20B)은 비정질 실리콘에 비해 캐리어 이동도가 높은 다결정 실리콘으로 이루어진 것이 바람직하다.

상기 화소 TFT의 소오스/드레인 전극들(40B) 중 하나에 전기적으로 접하는 화소전극(43)이 위치한다. 상기 화소전극(43)은 상기 기판(10) 방향으로 빛을 방출할 수 있는 투명전극인 것이 바람직하다. 상기 투명전극인 화소전극(43)은 애노드 또는 캐소드일 수 있다. 상기 애노드이면서 투명전극인 화소전극(43)은 ITO 또는 IZO로 이루어지는 것이 바람직하고, 상기 캐소드이면서 투명전극인 화소전극(43)은 Mg, Ca, Al, Ag, Ba 및 이들의 합금으로 이루어진 군에서 선택되는 하나로 이루어지되 빛을 투과시킬 수 있을 정도로 얇은 두께를 갖는 것이 바람직하다.

상기 화소전극(43) 및 상기 소오스/드레인 전극들(40A, 40B) 상에 화소정의막(pixel defining layer; 45)이 위치한다. 상기 화소정의막(45)은 상기 화소전극(43)의 표면 일부를 노출시키는 개구부(46)를 구비하고, 상기 개구부(46) 내에 노출된 화소전극(43)은 단위화소의 발광영역을 정의한다. 상기 노출된 화소전극(43) 상에 발광층(50)이 위치하고, 상기 발광층(50) 상에 대향전극(60)이 위치한다. 상기 발광층(50)은 단위화소별로 패터닝될 수 있다. 또한, 상기 발광층(50)과 상기 화소전극(43) 사이 또는 상기 발광층(50)과 상기 대향전극(60) 사이에는 각각 전하주입층(미도시) 및/또는 전하수송층(미도시)이 위치할 수 있다. 상기 대향전극(60)은 투명전극 또는 반사전극일 수 있으며, 상기 화소전극(43)이 애노드인 경우 캐소드이고, 상기 화소전극(43)이 캐소드인 경우 애노드이다.

상기 소오스/드레인 전극(40A, 40B)과 상기 기판(10) 사이에는 상기 전 화소영역(B)에서 오픈된 적어도 한 층의 실리콘 질화막 패턴(13, 25, 35)이 위치한다. 다시 말해서, 상기 실리콘 질화막 패턴(13, 25, 35)은 상기 화소영역(B)에는 위치하지 않으며, 상기 회로영역(A)에는 위치한다. 상기 실리콘 질화막은 SiNx 또는 SiON으로 이루어진 막일 수 있다. 이러한 실리콘 질화막은 수소를 풍부하게 함유하고 있는 막으로, 상기 수소는 상기 실리콘 질화막에 인접한 다결정 반도체층의 결정입자경계에 존재하는 불완전결합(dangling bond)와 같은 결함을 치유할 수 있다. 이로써, 박막트랜지스터의 전기적 특성 예를 들어, 캐리어 이동도와 에스-펙터(s-factor)를 변화시킬 수 있다. 더욱 자세하게는 상기 실리콘 질화막 패턴(13, 25, 35)이 위치하는 회로영역(A)의 회로 TFT는 높은 캐리어 이동도 및 작은 에스-펙터 값을 나타내어, 상기 회로 TFT로 구성하는 회로는 빠른 데이터 전달 속도를 가질 수 있고, 또한 상기 회로 TFT는 스위칭 동작을 양호하게 구현할 수 있다. 반면, 상기 실리콘 질화막 패턴(13, 25, 35)이 위치하지 않는 화소영역(B)의 화소 TFT는 상기 회로 TFT에 비해 낮은 캐리어 이동도 및 큰 에스-펙터 값을 나타낸다. 상기 큰 에스-펙터 값을 나타내는 화소 TFT는 계조를 용이하게 표시할 수 있으며, 낮은 캐리어 이동도는 화소 TFT의 특성상 큰 문제가 되지 않는다. 결과적으로, 상기 전 화소영역(B)에서 오픈된 적어도 한 층의 실리콘 질화막 패턴(13, 25, 35)을 형성함으로써, 화소 TFT와 회로 TFT의 최적화된 전기적 특성을 구현할 수 있다.

한편, 실리콘 질화막은 광투과율이 낮은 특성을 갖고 있다. 따라서, 상기 화소영역(B)에는 실리콘 질화막 패턴이 위치하지 않도록 함으로써, 상기 발광층(46)으로부터 상기 기판(10)으로 방출되는 광의 손실을 막아 유기전계발광소자의 휙도를 향상시킬 수 있다.

상기 실리콘 질화막 패턴은 상기 기판(10)과 상기 회로 TFT의 반도체층(20A) 사이에 위치하는 버퍼 질화막 패턴(13)일 수 있다. 이에 더하여, 상기 기판(10)과 상기 버퍼 질화막 패턴(13) 사이에 버퍼 실리콘 산화막(15)이 위치할 수 있다. 바람직하게는 상기 버퍼 실리콘 산화막(15)은 도면에 도시된 바와 같이 상기 버퍼 질화막 패턴(13)과 상기 회로 TFT의 반도체층(20A) 사이에 위치한다. 그 이유는 실리콘 산화막은 실리콘 질화막에 비해 반도체층과 부착(adhesion)특성이 양호하기 때문이다. 또한, 상기 버퍼 실리콘 산화막(15)은 상기 기판(10)과 상기 화소 TFT의 반도체층(20B) 사이에도 위치한다. 상기 버퍼 질화막 패턴(13) 및 상기 버퍼 실리콘 산화막(15)은 상기 기판으로부터 유출되는 불순물에 의해 상기 반도체층(20A, 20B)이 열화되는 것을 방지하는 역할을 한다.

상기 실리콘 질화막 패턴은 상기 회로 TFT의 반도체층(20A)과 상기 회로 TFT의 게이트 전극(30A) 사이에 위치하는 게이트 절연 질화막 패턴(25)일 수 있다. 이에 더하여, 상기 회로 TFT의 반도체층(20A)과 상기 게이트 절연 질화막 패턴

(25) 사이 또는 상기 게이트 절연 질화막 패턴(25)과 상기 회로 TFT의 게이트 전극(30A) 사이에 게이트 절연 실리콘 산화막(23)이 위치할 수 있다. 또한, 상기 게이트 절연 실리콘 산화막(23)은 상기 화소 TFT의 반도체층(20B)과 상기 화소 TFT의 게이트 전극(30B) 사이에도 위치한다.

또한, 상기 실리콘 질화막 패턴은 상기 회로 TFT의 게이트 전극(30A)과 상기 회로 TFT의 소오스/드레인 전극(40A) 사이에 위치하는 충간 질화막 패턴(35)일 수 있다. 이에 더하여, 상기 회로 TFT의 게이트 전극(30A)과 상기 충간 질화막 패턴(35) 사이 또는 상기 충간 질화막 패턴(35)과 상기 회로 TFT의 소오스/드레인 전극(40A) 사이에 충간 실리콘 산화막(33)이 위치할 수 있다. 상기 충간 실리콘 산화막(33)은 상기 화소 TFT의 게이트 전극(30B)과 상기 화소 TFT의 소오스/드레인 전극(40B) 사이에도 위치한다. 바람직하게는 상기 충간 실리콘 산화막(33)은 회로 TFT의 게이트 전극(30A)과 상기 충간 질화막 패턴(35) 사이에 위치한다.

도 1a 내지 1d는 본 발명의 실시예에 따른 유기전계발광소자의 제조방법을 설명하기 위한 단면도들이다.

도 1a를 참조하면, 회로영역(A) 및 화소영역(B)을 구비하는 기판(10)을 제공한다. 상기 기판(10) 상에 버퍼 질화막을 형성하고, 이를 패터닝하여 상기 전 화소영역(B)에서 오픈된 버퍼 질화막 패턴(13)을 형성한다. 상기 버퍼 질화막 패턴(13)을 형성하기 전에 상기 기판 전면에 버퍼 실리콘 산화막(15)을 형성할 수 있다. 바람직하게는 상기 버퍼 질화막 패턴(13)을 형성한 후, 상기 기판 전면에 버퍼 실리콘 산화막(15)을 형성한다. 상기 버퍼 실리콘 산화막(15)은 상기 회로영역(A) 및 상기 화소영역(B) 상에 위치한다.

상기 회로영역(A) 및 상기 화소영역(B)의 버퍼 실리콘 산화막(15) 상에 반도체층들(20A, 20B)을 각각 형성한다. 상기 반도체층(20A, 20B)은 다결정 실리콘으로 이루어진 반도체층으로 형성하는 것이 바람직하다. 상기 다결정 실리콘으로 이루어진 반도체층(20A, 20B)을 형성하는 것은 상기 버퍼 실리콘 산화막(15) 상에 비정질 실리콘막을 형성하고, 이를 결정화한 후 패터닝함으로써 수행하는데, 상기 결정화 방법에는 고상결정화(solid phase crystallization; SPC)법, 엑시머 레이저 어닐링(eximer laser annealing; ELA)법, 연속측면고상화(sequential lateral solidification; SLS)법, 금속유도결정화법(metal induced crystallization; 이하 MIC라 한다), 금속유도측면결정화법(metal induced lateral crystallization; 이하 MILC라 한다)등이 있다.

상기 반도체층(20A, 20B) 상에 게이트 절연 질화막을 형성한 후, 이를 패터닝하여 상기 전 화소영역(B)에서 오픈된 게이트 절연 질화막 패턴(25)을 형성한다. 상기 게이트 절연 질화막 패턴(25)을 형성하기 전 또는 상기 게이트 절연 질화막 패턴(25)을 형성한 후, 상기 기판 전면에 게이트 절연 실리콘 산화막(23)을 형성할 수 있다. 상기 게이트 절연 실리콘 산화막(23)은 상기 회로영역(A) 및 상기 화소영역(B) 상에 위치한다.

상기 회로영역(A) 및 상기 화소영역(B)의 게이트 절연 실리콘 산화막(23) 상에 상기 반도체층(20A, 20B)과 일부 중첩되는 게이트 전극들(30A, 30B)을 각각 형성한다.

도 1b를 참조하면, 상기 게이트 전극(30A, 30B) 상에 충간 실리콘 산화막(33)과 충간 질화막(34)을 차례로 형성하고, 상기 충간 질화막(34) 상에 하프톤 마스크를 사용하여 포토레지스트 패턴(99)을 형성한다. 상기 포토레지스트 패턴(99)은 상기 회로영역(A)에서의 패턴높이가 상기 화소영역(B)에서의 패턴높이에 비해 높으며, 소오스/드레인 콘택홀이 형성될 영역이 오픈되어 있다.

도 1c를 참조하면, 상기 포토레지스트 패턴(99)를 마스크로 하여 상기 충간 질화막(34), 상기 충간 실리콘 산화막(33), 상기 게이트 절연 질화막 패턴(25) 및 상기 게이트 절연 실리콘 산화막(23)을 식각함으로써, 상기 반도체층(20A, 20B)의 양단부를 노출시키는 소오스/드레인 콘택홀(36)을 형성한다. 이와 동시에 상기 회로영역(A)에 비해 패턴높이가 낮은 상기 화소영역(B)의 포토레지스트는 식각되고, 또한 그 하부의 충간 질화막(34)도 식각되어, 상기 전 화소영역(B)에서 오픈된 충간 질화막 패턴(35)이 형성된다.

이와는 달리, 상기 충간 질화막(34)을 상기 게이트 전극(30A, 30B) 상에 적층하고, 이를 패터닝하여 상기 전 화소영역(B)에서 오픈된 충간 질화막 패턴(35)를 형성한 후, 상기 충간 질화막 패턴(35) 상에 상기 충간 실리콘 산화막(33)을 형성하는 것도 가능하다. 이 경우, 상기 소오스/드레인 콘택홀(36)은 상기 충간 실리콘 산화막(33)을 형성한 후 형성한다.

상기 버퍼 질화막 패턴(13), 상기 게이트 절연 질화막 패턴(25) 및 상기 충간 질화막 패턴(35) 중에서 적어도 하나의 실리콘 질화막 패턴을 형성하고, 나머지는 형성하지 않을 수 있다. 상기 실리콘 질화막 패턴은 SiNx 또는 SiON을 사용하여 형성한다.

도 1d를 참조하면, 상기 소오스/드레인 콘택홀(36)을 구비하는 기판 전면에 소오스/드레인 전극물질을 적층하고 이를 패터닝하여, 상기 회로영역(A)과 상기 화소영역(B) 상에 각각 소오스/드레인 전극들(40A, 40B)을 형성한다. 상기 회로영역(A)에 형성된 상기 반도체층(20A), 상기 게이트 전극(30A) 및 상기 한 쌍의 소오스/드레인 전극(40A)은 회로 TFT를 형성하고, 상기 화소영역(B)에 형성된 상기 반도체층(20B), 상기 게이트 전극(30B) 및 상기 한 쌍의 소오스/드레인 전극(40B)은 화소 TFT를 형성한다.

이어서, 상기 화소 TFT의 소오스/드레인 전극(40B)들 중 어느 하나에 접하는 화소전극(43)을 형성한다. 상기 화소전극(43)을 형성하는 것은 샐도우 마스크를 사용하여 화소전극물질을 진공증착함으로써 형성할 수 있다. 상기 화소전극(43)은 투명전극으로 형성하는 것이 바람직하다. 상기 투명전극인 화소전극(43)을 형성함에 있어, 상기 화소전극물질은 ITO 또는 IZO일 수 있다. 이 경우, 상기 화소전극(43)은 애노드이다. 이와는 달리, 상기 투명전극인 화소전극(43)을 형성함에 있어, 상기 화소전극물질은 Mg, Ca, Al, Ag, Ba 및 이들의 합금으로 이루어진 군에서 선택되는 하나일 수 있으며, 빛을 투과시킬 수 있을 정도로 얇은 두께로 형성한다. 이 경우, 상기 화소전극(43)은 캐소드이다.

상기 화소전극(43) 및 상기 소오스/드레인 전극들(40A, 40B) 상에 화소정의막(pixel defining layer; 45)을 형성한다. 상기 화소정의막(45) 내에 상기 화소전극(43)의 표면 일부를 노출시키는 개구부(46)를 형성한다. 상기 개구부(46) 내에 노출된 화소전극(43)은 단위화소의 발광영역을 정의한다. 상기 노출된 화소전극(43) 상에 발광층(50)을 형성하고, 상기 발광층(50) 상에 대향전극(60)을 형성한다. 상기 발광층(50)은 단위화소별로 패터닝하여 형성할 수 있다. 또한, 상기 발광층(50)과 상기 화소전극(43) 사이 또는 상기 발광층(50)과 상기 대향전극(60) 사이에는 각각 전하주입층(미도시) 및/또는 전하수송층(미도시)을 형성할 수 있다. 상기 대향전극(60)은 투명전극 또는 반사전극으로 형성할 수 있으며, 상기 화소전극(43)이 애노드인 경우 캐소드로 형성하고, 상기 화소전극(43)이 캐소드인 경우 애노드로 형성한다.

도 2a는 본 발명의 실시예에 따라 제조된 화소 TFT와 회로 TFT의 캐리어 이동도를 보여주는 그래프이고, 도 2b는 본 발명의 실시예에 따라 제조된 화소 TFT와 회로 TFT의 에스-펙터값을 보여주는 그래프이다.

도 2a 및 도 2b를 참조하면, 회로 TFT의 캐리어 이동도는 화소 TFT의 캐리어 이동도에 비해 우수하고, 작은 에스-펙터값을 갖는다. 따라서, 상기 회로 TFT로 구성하는 회로는 빠른 데이터 전달 속도를 가질 수 있고, 또한 상기 회로 TFT스위칭 동작을 양호하게 구현할 수 있다. 반면, 상기 화소 TFT는 계조를 용이하게 표시할 수 있다. 결과적으로, 회로 TFT와 화소 TFT의 전기적 특성을 최적화할 수 있다.

도 3은 실리콘 질화막의 두께에 따른 휘도의 변화를 나타낸 그래프이다.

도 3을 참조하면, 실리콘 질화막의 두께가 증가할수록 휘도는 저하되는 것을 알 수 있다. 따라서, 실리콘 질화막 패턴을 화소영역 전체에 걸쳐 오픈시킴으로써, 유기전계발광소자의 휘도저하를 막을 수 있다.

### 발명의 효과

상술한 바와 같이 본 발명에 따르면, 전 화소영역에서 오픈된 실리콘 질화막 패턴을 형성함으로써, 화소 TFT와 회로 TFT의 최적화된 전기적 특성을 얻을 수 있을 뿐 아니라, 유기전계발광소자의 휘도저하를 막을 수 있다.

### (57) 청구의 범위

#### 청구항 1.

회로영역 및 화소영역을 구비하는 기판;

상기 기판의 회로영역 및 화소영역 상에 각각 위치하고, 반도체층, 게이트 전극 및 한 쌍의 소오스/드레인 전극을 구비하는 회로 TFT 및 화소 TFT;

상기 화소 TFT의 소오스/드레인 전극과 전기적으로 연결된 화소전극; 및

상기 소오스/드레인 전극과 상기 기판 사이에 위치하고, 상기 전 화소영역에서 오픈된 적어도 한 층의 실리콘 질화막 패턴을 포함하는 것을 특징으로 하는 유기전계발광표시장치.

## 청구항 2.

제 1 항에 있어서,

상기 소오스/드레인 전극과 상기 기판 사이에 위치하는 적어도 한층의 실리콘 산화막을 더욱 포함하는 것을 특징으로 하는 유기전계발광표시장치.

## 청구항 3.

제 1 항에 있어서,

상기 실리콘 질화막 패턴은 SiNx 또는 SiON로 이루어진 것을 특징으로 하는 유기전계발광표시장치.

## 청구항 4.

제 1 항에 있어서,

상기 실리콘 질화막 패턴은 상기 기판과 상기 회로 TFT의 반도체층 사이에 위치하는 베퍼 질화막 패턴인 것을 특징으로 하는 유기전계발광표시장치.

## 청구항 5.

제 4 항에 있어서,

상기 기판과 상기 베퍼 질화막 패턴 사이 또는 상기 베퍼 질화막 패턴과 상기 회로 TFT의 반도체층 사이; 및 상기 기판과 상기 화소 TFT의 반도체층 사이에 위치하는 베퍼 실리콘 산화막을 더욱 포함하는 것을 특징으로 하는 유기전계발광표시장치.

## 청구항 6.

제 1 항에 있어서,

상기 실리콘 질화막 패턴은 상기 회로 TFT의 반도체층과 상기 회로 TFT의 게이트 전극 사이에 위치하는 게이트 절연 질화막 패턴인 것을 특징으로 하는 유기전계발광표시장치.

## 청구항 7.

제 6 항에 있어서,

상기 회로 TFT의 반도체층과 상기 게이트 절연 질화막 패턴 사이 또는 상기 게이트 절연 질화막 패턴과 상기 회로 TFT의 게이트 전극 사이; 및 상기 화소 TFT의 반도체층과 상기 화소 TFT의 게이트 전극 사이에 위치하는 게이트 절연 실리콘 산화막을 더욱 포함하는 것을 특징으로 하는 유기전계발광표시장치.

## 청구항 8.

제 1 항에 있어서,

상기 실리콘 질화막 패턴은 상기 회로 TFT의 게이트 전극과 상기 회로 TFT의 소오스/드레인 전극 사이에 위치하는 층간 질화막 패턴인 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 9.

제 8 항에 있어서,

상기 회로 TFT의 게이트 전극과 상기 층간 질화막 패턴 사이 또는 상기 층간 질화막 패턴과 상기 회로 TFT의 소오스/드레인 전극 사이; 및 상기 화소 TFT의 게이트 전극과 상기 화소 TFT의 소오스/드레인 전극 사이에 위치하는 층간 실리콘 산화막을 더욱 포함하는 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 10.

제 1 항에 있어서,

상기 반도체층은 다결정 실리콘으로 이루어진 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 11.

제 1 항에 있어서,

상기 화소전극은 투명전극인 것을 특징으로 하는 유기전계발광표시장치.

### 청구항 12.

제 1 항에 있어서,

상기 화소전극 상에 위치하는 발광층 및 상기 발광층 상에 위치하는 대향전극을 더욱 포함하는 것을 특징으로 하는 유기 전계발광표시장치.

### 청구항 13.

회로영역 및 화소영역을 구비하는 기판을 제공하고;

상기 기판의 회로영역 및 화소영역 상에 반도체층, 게이트 전극 및 한 쌍의 소오스/드레인 전극을 구비하는 회로 TFT 및 화소 TFT를 각각 형성하고;

상기 화소 TFT의 소오스/드레인 전극과 전기적으로 연결된 화소전극을 형성하고;

상기 소오스/드레인 전극을 형성하기 전에, 상기 기판 상에 상기 전 화소영역에서 오픈된 적어도 한 층의 실리콘 질화막 패턴을 형성하는 것을 포함하는 것을 특징으로 하는 유기전계발광표시장치의 제조방법.

### 청구항 14.

제 13 항에 있어서,

상기 소오스/드레인 전극을 형성하기 전에, 상기 기판 상에 적어도 한층의 실리콘 산화막을 형성하는 것을 더욱 포함하는 것을 특징으로 하는 유기전계발광표시장치의 제조방법.

### 청구항 15.

제 13 항에 있어서,

상기 실리콘 질화막 패턴은 SiNx 또는 SiON으로 형성하는 것을 특징으로 하는 유기전계발광소자의 제조방법.

### 청구항 16.

제 13 항에 있어서,

상기 실리콘 질화막 패턴은 상기 반도체층을 형성하기 전에 상기 기판 상에 형성하는 버퍼 질화막 패턴이고,

상기 버퍼 질화막 패턴을 형성하기 전 또는 상기 버퍼 질화막 패턴을 형성한 후, 상기 기판 전면에 버퍼 실리콘 산화막을 형성하는 것을 더욱 포함하는 것을 특징으로 하는 유기전계발광소자의 제조방법.

### 청구항 17.

제 13 항에 있어서,

상기 실리콘 질화막 패턴은 상기 게이트 전극을 형성하기 전에 상기 반도체층 상에 형성하는 게이트 절연 질화막 패턴이고,

상기 게이트 절연 질화막 패턴을 형성하기 전 또는 상기 게이트 절연 질화막 패턴을 형성한 후, 상기 기판 전면에 게이트 절연 실리콘 산화막을 형성하는 것을 더욱 포함하는 것을 특징으로 하는 유기전계발광소자의 제조방법.

### 청구항 18.

제 13 항에 있어서,

상기 실리콘 질화막 패턴은 상기 소오스/드레인 전극을 형성하기 전에 상기 게이트 전극 상에 형성하는 층간 질화막 패턴이고,

상기 층간 질화막 패턴을 형성하는 것은 상기 게이트 전극 상에 층간 실리콘 산화막과 층간 질화막을 차례로 형성하고, 하프톤 마스크를 사용하여 상기 층간 질화막 및 상기 층간 실리콘 산화막 내에 소오스/드레인 콘택홀을 형성함과 동시에 형성하는 것을 특징으로 하는 유기전계발광소자 제조방법.

**도면**

도면1a

도면1b

도면1c

도면1d

도면2a

도면2b

도면3

|               |                                                                                                                               |         |            |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)       | 有机电致发光显示装置及其制造方法                                                                                                              |         |            |

| 公开(公告)号       | <a href="#">KR1020050080406A</a>                                                                                              | 公开(公告)日 | 2005-08-12 |

| 申请号           | KR1020040008494                                                                                                               | 申请日     | 2004-02-09 |

| 申请(专利权)人(译)   | 三星SD眼有限公司                                                                                                                     |         |            |

| 当前申请(专利权)人(译) | 三星SD眼有限公司                                                                                                                     |         |            |

| [标]发明人        | LEE HUNJUNG<br>이현정<br>PARK SANGIL<br>박상일                                                                                      |         |            |

| 发明人           | 이현정<br>박상일                                                                                                                    |         |            |

| IPC分类号        | H01L51/50 H01L21/314 H01L27/32 H01L21/318 G09F9/30 H05B33/10 H01L29/786 H01L21/77<br>H05B33/00                                |         |            |

| CPC分类号        | H01L27/3244 H01L21/3185 H01L29/78603 H01L27/1214 H01L51/5253 G09G2320/0233 H01L21/3144<br>G09G2300/0426 H01L51/50 H01L27/1248 |         |            |

| 代理人(译)        | PARK , 常树                                                                                                                     |         |            |

| 其他公开文献        | <a href="#">KR100656497B1</a>                                                                                                 |         |            |

| 外部链接          | <a href="#">Espacenet</a>                                                                                                     |         |            |

## 摘要(译)

提供了一种有机发光显示装置及其制造方法。有机电致发光显示装置包括包括电路区域和像素区域的基板;电路TFT和配备有半导体层的像素TFT位于基板的电路区域和像素区域，以及栅电极和一对源/漏电极;像素TFT的源/漏电极;至少单层的氮化硅膜图案位于像素电极之间，与源/漏电极和基板电连接，并在全像素区域开口。有机电致发光显示装置，氮化硅膜，像素TFT，电路TFT，亮度。