(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년02월25일

(11) 등록번호 10-0807062

(24) 등록일자 2008년02월18일

(51) Int. Cl.

H05B 33/02 (2006.01)

(21) 출원번호 10-2007-0034285

(22) 출원일자 2007년04월06일

심사청구일자 2007년04월06일

### (56) 선행기술조사문항

KR1020040039640 A

KR1020070034800 A

KR1020070079838 A

전체 청구항 수 : 총 29 항

(73) 특허권자

삼성에스디아이 주식회사

경기 수원시 영통구 신동 575

(72) 발명자

김종운

경기 용인시 기흥구 공세동 428-5

(74) 대리인

서경민, 서만규

심사관 : 하정규

(54) 유키 전계 밝꽝 표시 장치

(57) 요약

본 발명은 유기 전계 발광 표시 장치에 관한 것으로, 해결하고자 하는 기술적 과제는 유기 전계 발광 표시 패널의 필센 세로 슛트 불량을 사전 검출 하여 모듈 공정 비용을 절감하고, 신뢰성을 높이는데 있다.

이를 위해 본 발명은 원시 클럭선, 원시 부클럭선 및 초기 구동선에 전기적으로 연결된 제1시프트레지스터와, 초기구동선, 제1시프트레지스터의 출력선인 제1발광제어선 및 제1클럭선에 전기적으로 연결된 제1낸드게이트와, 초기구동선, 제1발광제어선 및 제2클럭선에 전기적으로 연결된 제2낸드게이트와, 제1낸드게이트의 출력선인 제1주사선에 전기적으로 연결된 제1화소부와, 제2낸드게이트의 출력선인 제2주사선에 전기적으로 연결된 제2화소부와, 제1주사선에 전기적으로 연결된 제3화소부 및 제2주사선에 전기적으로 연결된 제4화소부를 포함하는 유기 전계발광 표시 장치를 개시한다.

대표도 - 도9

## 특허청구의 범위

### 청구항 1

원시클럭선, 원시부클럭선 및 초기구동선에 전기적으로 연결된 제1시프트레지스터;

상기 원시부클럭선, 상기 원시클럭선 및 상기 제1시프트레지스터의 출력선인 제1발광제어선에 전기적으로 연결된 제2시프트레지스터;

상기 초기구동선, 상기 제1발광제어선 및 제1클럭선에 전기적으로 연결된 제1낸드게이트;

상기 제1발광제어선, 상기 제2시프트레지스터의 출력선인 제2발광제어선 및 제2클럭선에 전기적으로 연결된 제2낸드게이트;

상기 제1낸드게이트의 출력선인 제1주사선에 전기적으로 연결된 제1화소부;

상기 제2낸드게이트의 출력선인 제2주사선에 전기적으로 연결된 제2화소부;

상기 제1주사선에 전기적으로 연결된 제3화소부; 및

상기 제2주사선에 전기적으로 연결된 제4화소부를 포함하여 이루어진 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 2

청구항 1 항에 있어서,

상기 제1시프트레지스터는 입력단자가 상기 초기구동선에 전기적으로 연결되고, 제1클럭단자가 상기 원시클럭선에 전기적으로 연결되고, 제2클럭단자가 상기 원시부클럭선에 전기적으로 연결되고, 출력단자가 상기 제1발광제어선에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 3

청구항 1 항에 있어서,

상기 제2시프트레지스터는 입력단자가 상기 제1발광제어선에 전기적으로 연결되고, 제1클럭단자가 상기 원시부클럭선에 전기적으로 연결되고, 제2클럭단자가 상기 원시클럭선에 전기적으로 연결되고, 출력단자가 상기 제2발광제어선에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 4

청구항 1 항에 있어서,

상기 제1낸드게이트는 상기 초기구동선, 상기 제1발광제어선 및 제1클럭선에 전기적으로 연결되어, 초기구동신호, 제1발광제어신호 및 제1클럭신호를 인가받아 제1주사선으로 제1주사신호를 출력하는 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 5

청구항 1 항에 있어서,

상기 제2낸드게이트는 상기 제1발광제어선, 상기 제2발광제어선 및 제2클럭선에 전기적으로 연결되어 제1발광제어신호, 제2발광제어신호 및 제2클럭신호를 인가받아 제2주사선으로 제2주사신호를 출력하는 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 6

청구항 1 항에 있어서,

상기 제1화소부는 제-1주사선, 제1주사선 및 제1발광제어선과 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 7

청구항 6항에 있어서,

상기 제2화소부는 제0주사선, 제2주사선 및 제2발광제어선과 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 8

청구항 7 항에 있어서,

상기 제3화소부는 제1주사선, 제3주사선 및 제1발광제어선과 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 9

청구항 8 항에 있어서,

상기 제4화소부는 제2주사선, 제4주사선 및 제2발광제어선과 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 10

청구항 1 항에 있어서,

상기 제1화소부 내지 제4화소부의 화소 회로는

제1전원전압선과 데이터선 사이에 전기적으로 연결되고, 주사선에 제어전극이 전기적으로 연결된 제1스위칭소자;

상기 제1스위칭소자와 상기 제1전원전압선 사이에 전기적으로 연결되고, 발광제어선에 제어전극이 전기적으로 연결된 제2스위칭소자;

상기 제1스위칭소자와 제2전원전압선 사이에 전기적으로 연결된 구동트랜지스터;

상기 제1전원전압선과 제3전원전압 사이에 전기적으로 연결된 제1용량성 소자;

상기 주사선과 상기 구동트랜지스터의 제어전극 사이에 전기적으로 연결된 제2용량성 소자;

상기 구동트랜지스터와 제2전원전압선 사이에 전기적으로 연결되고, 제어전극이 상기 발광제어선에 전기적으로 연결된 제3스위칭소자;

상기 제1용량성 소자와 상기 제3전원전압선 사이에 전기적으로 연결되고 제어전극에 두단 이전의 주사선이 전기적으로 연결된 제4스위칭소자;

상기 구동트랜지스터의 제어전극과 제3스위칭소자 사이에 전기적으로 연결된 제5스위칭소자; 및

상기 제3스위칭소자와 상기 제2전원전압선 사이에 전기적으로 연결된 유기전계발광소자를 포함하여 이루어진 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 11

청구항 10 항에 있어서,

상기 제1스위칭소자는 제1전극이 상기 데이터선에 전기적으로 연결되고, 제2전극이 상기 제2스위칭소자와 구동 트랜지스터 사이에 전기적으로 연결되고, 제어전극이 주사선에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 12

청구항 10 항에 있어서,

상기 제2스위칭소자는 제1전극이 상기 제1스위칭소자와 구동트랜지스터 사이에 전기적으로 연결되고, 제2전극이 상기 제1전원전압선과 제1용량성소자 사이에 전기적으로 연결되고, 제어전극이 발광제어선에 전기적으로 연결된

것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 13

청구항 10 항에 있어서,

상기 제3스위칭소자는 제1전극이 상기 구동트랜지스터와 제5스위칭소자 사이에 전기적으로 연결되고, 제2전극이 상기 유기 전계 발광 소자의 애노드에 전기적으로 연결되고, 제어전극이 발광제어선에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 14

청구항 10 항에 있어서,

상기 제4스위칭소자는 제1전극이 상기 제1용량성소자와 구동트랜지스터의 제어전극 사이에 전기적으로 연결되고, 제2전극이 제3전원전압선에 전기적으로 연결되고, 제어전극이 두단 이전의 주사선에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 15

청구항 10 항에 있어서,

상기 제5스위칭소자는 제1전극이 상기 구동트랜지스터의 제어전극에 전기적으로 연결되고, 제2전극이 상기 구동트랜지스터와 상기 제3스위칭소자 사이에 전기적으로 연결되고, 제어전극이 주사선에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 16

청구항 10 항에 있어서,

상기 구동트랜지스터는 제1전극이 상기 제1스위칭소자와 상기 제2스위칭소자 사이에 전기적으로 연결되고, 제2전극이 제3스위칭소자의 제1전극에 전기적으로 연결되고, 제어전극이 발광제어선에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 17

청구항 1 항에 있어서,

상기 시프트 레지스터는

상기 클럭선에 제어전극이 전기적으로 연결되어 제1전원전압을 스위칭하는 제1피모스 스위칭소자;

상기 제1피모스 스위칭소자와 제1노드 사이에 전기적으로 연결되고, 제어전극이 입력선에 전기적으로 연결된 제2피모스 스위칭소자;

상기 부클럭선에 제어전극이 전기적으로 연결되어 제2전원전압을 스위칭하는 제1엔모스 스위칭소자;

상기 제1엔모스 스위칭소자와 제1노드 사이에 전기적으로 연결되고, 제어전극이 입력선에 전기적으로 연결된 제2피모스 스위칭소자;

상기 부클럭선에 제어전극이 전기적으로 연결되어 제1전원전압을 스위칭하는 제3피모스 스위칭소자;

상기 제3피모스 스위칭소자와 상기 제1노드 사이에 전기적으로 연결되고, 제어전극이 제2노드에 전기적으로 연결된 제4피모스 스위칭소자;

상기 클럭선에 제어전극이 전기적으로 연결되어 제2전원전압을 스위칭하는 제3엔모스 스위칭소자;

상기 제3엔모스 스위칭소자와 상기 제1노드 사이에 전기적으로 연결되고, 제어전극이 제2노드에 전기적으로 연결된 제4엔모스 스위칭소자;

상기 제1전원전압선과 상기 제2노드 사이에 전기적으로 연결되고, 제어전극이 제1노드에 전기적으로 연결된 제5피모스 스위칭소자; 및

상기 제2전원전압선과 상기 제2노드 사이에 전기적으로 연결되고, 제어전극이 제1노드에 전기적으로 연결된 제5

엔모스 스위칭소자를 포함하여 이루어진 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 18

청구항 17 항에 있어서,

상기 제2노드의 신호는 시프트 레지스터의 출력신호인 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 19

청구항 1항에 있어서,

상기 원시클럭선에 전기적으로 연결되어 원시클럭신호를 전달받아 상기 원시부클럭선으로 원시부클럭신호를 생성하는 클럭인버터를 포함하여 이루어 진 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 20

청구항 1항에 있어서,

상기 제1클럭선은 기수 번째 낸드게이트에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 21

청구항 20항에 있어서,

상기 제1클럭선에 로우레벨의 제1클럭신호가 인가되고 상기 제2클럭선에 하이레벨의 제2클럭신호가 인가되면, 기수 번째 화로회로부에 로우레벨의 주사신호가 인가되어 화소 회로부에 데이터 신호가 인가되는 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 22

청구항 21항에 있어서,

상기 기수 번째 화소 회로부에 로우레벨의 발광제어신호가 인가되면 발광하는 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 23

청구항 1항에 있어서,

상기 제2클럭선은 우수 번째 낸드게이트에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 24

청구항 23항에 있어서,

상기 제1클럭선에 하이레벨의 제1클럭신호가 인가되고 상기 제2클럭선에 로우레벨의 제2클럭신호가 인가되면, 우수 번째 화로회로부에 로우레벨의 주사신호가 인가되어 화소 회로부에 데이터 신호가 인가되는 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 25

청구항 24항에 있어서,

상기 우수 번째 화소 회로부에 로우레벨의 발광제어신호가 인가되면 발광하는 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 26

청구항 1항에 있어서,

상기 초기구동선의 초기구동신호가 하이레벨이고 상기 제1발광제어선의 제1발광제어신호가 하이레벨일때, 상기 제1클럭선에 하이레벨의 제1클럭신호가 인가되고, 상기 제2클럭선에 로우레벨의 제2클럭신호가 인가되면, 제1낸드게이트가 로우레벨의 제1주사신호를 제1주사선으로 출력하는 것을 특징으로 하는 유기 전계 발광 표시 장치.

## 청구항 27

청구항 1항에 있어서,

상기 제1발광제어선의 제1발광제어신호가 하이레벨이고 상기 제2발광제어선의 제2발광제어신호가 하이레벨일 때, 상기 제1클럭선에 로우레벨의 제1클럭신호가 인가되고, 상기 제2클럭선에 하이레벨의 제2클럭신호가 인가되면, 제2낸드게이트가 로우레벨의 제2주사신호를 제2주사선으로 출력하는 것을 특징으로 하는 유기 전계 발광 표시 장치.

## 청구항 28

청구항 1항에 있어서,

상기 제1발광제어선의 제1발광제어신호가 하이레벨이고 상기 제2발광제어선의 제2발광제어신호가 하이레벨일 때, 상기 제1클럭선에 하이레벨의 제1클럭신호가 인가되고, 상기 제2클럭선에 로우레벨의 제2클럭신호가 인가되면, 제3낸드게이트가 로우레벨의 제3주사신호를 제3주사선으로 출력하는 것을 특징으로 하는 유기 전계 발광 표시 장치.

## 청구항 29

청구항 1항에 있어서,

상기 제2발광제어선의 제2발광제어신호가 하이레벨이고 상기 제3발광제어선의 제3발광제어신호가 하이레벨일 때, 상기 제1클럭선에 로우레벨의 제1클럭신호가 인가되고, 상기 제2클럭선에 하이레벨의 제2클럭신호가 인가되면, 제4낸드게이트가 로우레벨의 제4주사신호를 제4주사선으로 출력하는 것을 특징으로 하는 유기 전계 발광 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <31> 본 발명은 유기 전계 발광 표시 장치에 관한 것으로서, 보다 자세하게는 유기 전계 발광 표시 장치의 화소 회로에 세로 쇼트 불량을 사전에 검출할 수 있는 유기 전계 발광 표시 장치에 관한 것이다.

- <32> 유기 전계 발광 표시 장치는 형광 또는 인광 유기 화합물을 전기적으로 여기시켜 발광시키는 표시장치로서, N개의 유기전계발광소자들을 구동하여 영상을 표현할 수 있도록 되어 있다. 이러한 유기전계발광소자는 애노드(ITO), 유기박막, 캐소드(metal)의 구조로 되어 있다. 유기 박막은 전자와 정공의 결합을 통해 빛을 발광하는 발광층(emitting layer, EML), 전자를 수송하는 전자 수송 층(electron transport layer, ETL) 및 정공을 수송하는 정공수송층(hole transport layer, HTL)을 포함한 다층 구조로 이루어지고, 또한 별도의 전자를 주입하는 전자 주입층(electron injecting layer, EIL)과 정공을 주입하는 정공주입층(hole injecting layer, HIL)을 포함할 수 있다.

- <33> 이와 같이 이루어지는 유기전계발광소자를 구동하는 방식에는 단순매트릭스(passive matrix, PM) 방식과 MOS형(Metal Oxide Silicon)박막 트랜지스터(thin film transistor, TFT)를 이용한 능동 구동(active matrix, AM) 방식이 있다. 단순 매트릭스 방식은 양극과 음극을 직교하도록 형성하여 라인을 선택하여 구동하는데 비해, 능동 구동 방식은 박막 트랜지스터와 커패시터를 각 ITO(indium tin oxide) 화소 전극에 접속하여 커패시터 용량에 의해 전압을 유지하도록 하는 구동 방식이다.

- <34> 이러한 유기 전계 발광 표시 장치는 퍼스널 컴퓨터, 휴대전화기, PDA 등의 휴대 정보단말기 등의 표시장치나 각종 정보기기의 표시장치로서 사용되고 있다.

- <35> 최근에 음극선관에 비교하여 무게와 부피가 작은 각종 발광 표시장치들이 개발되고 있으며, 특히 발광효율, 휙도 및 시야각이 뛰어나며 응답속도가 빠른 유기 전계 발광 표시 장치가 주목 받고 있다.

- <36> 이러한 유기 전계 발광 표시 장치의 화소 회로(Pixel)는 이웃하는 두 주사선(또는 발광제어선)과 이웃하는 두

데이터선에 의해 정의 되는 화소 영역에 형성 되어 이웃하는 두 주사선(또는 발광제어선)에서 주사신호(또는 발광제어신호)가 인가되면 화소회로의 유기 전계 발광 소자(OLED)가 발광하게 된다. 상기 화소회로와 전기적으로 연결된 이웃하는 두주사선(또는 발광제어선)은 일반적으로 n번째 화소회로일 경우, n번째 주사선(또는 발광제어선)과 n-1번째 주사선(또는 발광제어선)이 될 수 있다. 화소회로에 전기적으로 연결된 주사선(또는 발광제어선)은 주사신호(또는 발광제어신호)를 화소회로의 유기 전계 발광 소자(OLED)에 인가하여 화소회로의 유기 전계 발광 소자(OLED)는 발광하게 되어 한 프레임의 영상을 패널로 출력하게 된다. 그러나 유기 전계 발광 표시 장치는 한프레임의 영상이 한번에 발광하게 되므로 일정한 패턴을 인가하기 이전에는 픽셀 셀트를 검출하기 어렵다.

<37> 종래의 화소회로에 셀트가 발생한 것을 검출하기 위해서는 모듈 공정에서 일정한 패턴을 유기 전계 발광 표시 패널에 인가하여 셀트가 발생한 것을 검출할 수 있었다. 그러나 셀트가 발생한 불량 패널에 모듈 공정 작업 비용이 추가적으로 발생하고, 모듈 공정에서 전수 검사를 하지 않을 경우 세로 방향 셀트가 불량으로 검출 되지 않아 최종 이용 고객이 불량을 발견하게 되어 상품의 신뢰성이 저하되는 문제점이 있다.

### 발명이 이루고자 하는 기술적 과제

<38> 본 발명은 상술한 종래의 문제점을 극복하기 위한 것으로서, 본 발명의 목적은 유기 전계 발광 표시 패널의 픽셀 세로 셀트 불량을 사전 검출 하여 모듈 공정 비용을 절감하고, 신뢰성이 높은 유기 전계 발광 표시 장치를 제공하는데 있다.

### 발명의 구성 및 작용

<39> 상기한 목적을 달성하기 위해 본 발명에 의한 유기 전계 발광 표시 장치는 원시클럭선, 원시부클럭선 및 초기구동선에 전기적으로 연결된 제1시프트레지스터와, 상기 원시부클럭선, 상기 원시클럭선 및 상기 제1시프트레지스터의 출력선인 제1발광제어선에 전기적으로 연결된 제2시프트레지스터와 상기 초기구동선, 상기 제1발광제어선 및 제1클럭선에 전기적으로 연결된 제1낸드게이트와 상기 제1발광제어선, 상기 제2시프트레지스터의 출력선인 제2발광제어선 및 제2클럭선에 전기적으로 연결된 제2낸드게이트와 상기 제1낸드게이트의 출력선인 제1주사선에 전기적으로 연결된 제1화소부와 상기 제2낸드게이트의 출력선인 제2주사선에 전기적으로 연결된 제2화소부와 상기 제1주사선에 전기적으로 연결된 제3화소부 및 상기 제2주사선에 전기적으로 연결된 제4화소부를 포함할 수 있다.

<40> 상기 제1시프트레지스터는 입력단자가 상기 초기구동선에 전기적으로 연결되고, 제1클럭단자가 상기 원시클럭선에 전기적으로 연결되고, 제2클럭단자가 상기 원시부클럭선에 전기적으로 연결되고, 출력단자가 상기 제1발광제어선에 전기적으로 연결될 수 있다.

<41> 상기 제2시프트레지스터는 입력단자가 상기 제1발광제어선에 전기적으로 연결되고, 제1클럭단자가 상기 원시부클럭선에 전기적으로 연결되고, 제2클럭단자가 상기 원시클럭선에 전기적으로 연결되고, 출력단자가 상기 제2발광제어선에 전기적으로 연결될 있다.

<42> 상기 제1낸드게이트는 상기 초기구동선, 상기 제1발광제어선 및 제1클럭선에 전기적으로 연결되어, 초기구동신호, 제1발광제어신호 및 제1클럭신호를 인가받아 제1주사선으로 제1주사신호를 출력할 수 있다.

<43> 상기 제2낸드게이트는 상기 제1발광제어선, 상기 제2발광제어선 및 제2클럭선에 전기적으로 연결되어 제1발광제어신호, 제2발광제어신호 및 제2클럭신호를 인가받아 제2주사선으로 제2주사신호를 출력할 수 있다.

<44> 상기 제1화소부는 제-1주사선, 제1주사선 및 제1발광제어선과 전기적으로 연결될 수 있다.

<45> 상기 제2화소부는 제0주사선, 제2주사선 및 제2발광제어선과 전기적으로 연결될 수 있다.

<46> 상기 제3화소부는 제1주사선, 제3주사선 및 제1발광제어선과 전기적으로 연결될 수 있다.

<47> 상기 제4화소부는 제2주사선, 제4주사선 및 제2발광제어선과 전기적으로 연결될 수 있다.

<48> 상기 제1화소부 내지 제4화소부의 화소 회로는 제1전원전압선과 데이터선 사이에 전기적으로 연결되고, 주사선에 제어전극이 전기적으로 연결된 제1스위칭소자와 상기 제1스위칭소자와 상기 제1전원전압선 사이에 전기적으로 연결되고, 발광제어선에 제어전극이 전기적으로 연결된 제2스위칭소자와 상기 제1스위칭소자와 제2전원전압선 사이에 전기적으로 연결된 구동트랜지스터와 상기 제1전원전압선과 제3전원전압 사이에 전기적으로 연결된 제1용량성 소자와 상기 주사선과 상기 구동트랜지스터의 제어전극 사이에 전기적으로 연결된 제2용량성 소자와 상기 구동트랜지스터와 제2전원전압선 사이에 전기적으로 연결되고, 제어전극이 상기 발광제어선에 전기적으로

연결된 제3스위칭소자와 상기 제1용량성 소자와 상기 제3전원전압선 사이에 전기적으로 연결되고 제어전극에 두 단 이전의 주사선이 전기적으로 연결된 제4스위칭소자와 상기 구동트랜지스터의 제어전극과 제3스위칭소자 사이에 전기적으로 연결된 제5스위칭소자 및 상기 제3스위칭소자와 상기 제2전원전압선 사이에 전기적으로 연결된 유기전계발광소자를 포함할 수 있다.

- <49> 상기 제1스위칭소자는 제1전극이 상기 데이터선에 전기적으로 연결되고, 제2전극이 상기 제2스위칭소자와 구동트랜지스터 사이에 전기적으로 연결되고, 제어전극이 주사선에 전기적으로 연결될 수 있다.

- <50> 상기 제2스위칭소자는 제1전극이 상기 제1스위칭소자와 구동트랜지스터 사이에 전기적으로 연결되고, 제2전극이 상기 제1전원전압선과 제1용량성소자 사이에 전기적으로 연결되고, 제어전극이 발광제어선에 전기적으로 연결될 수 있다.

- <51> 상기 제3스위칭소자는 제1전극이 상기 구동트랜지스터와 제5스위칭소자 사이에 전기적으로 연결되고, 제2전극이 상기 유기 전계 발광 소자의 애노드에 전기적으로 연결되고, 제어전극이 발광제어선에 전기적으로 연결될 수 있다.

- <52> 상기 제4스위칭소자는 제1전극이 상기 제1용량성소자와 구동트랜지스터의 제어전극 사이에 전기적으로 연결되고, 제2전극이 제3전원전압선에 전기적으로 연결되고, 제어전극이 두 단 이전의 주사선에 전기적으로 연결될 수 있다.

- <53> 상기 제5스위칭소자는 제1전극이 상기 구동트랜지스터의 제어전극에 전기적으로 연결되고, 제2전극이 상기 구동트랜지스터와 상기 제3스위칭소자 사이에 전기적으로 연결되고, 제어전극이 주사선에 전기적으로 연결될 수 있다.

- <54> 상기 구동트랜지스터는 제1전극이 상기 제1스위칭소자와 상기 제2스위칭소자 사이에 전기적으로 연결되고, 제2전극이 제3스위칭소자의 제1전극에 전기적으로 연결되고, 제어전극이 발광제어선에 전기적으로 연결될 수 있다.

- <55> 상기 시프트 레지스터는 상기 클럭선에 제어전극이 전기적으로 연결되어 제1전원전압을 스위칭하는 제1피모스 스위칭소자와 상기 제1피모스 스위칭소자와 제1노드 사이에 전기적으로 연결되고, 제어전극이 입력선에 전기적으로 연결된 제2피모스 스위칭소자와 상기 부클럭선에 제어전극이 전기적으로 연결되어 제2전원전압을 스위칭하는 제1엔모스 스위칭소자와 상기 제1엔모스 스위칭소자와 제1노드 사이에 전기적으로 연결되고, 제어전극이 입력선에 전기적으로 연결된 제2피모스 스위칭소자와 상기 부클럭선에 제어전극이 전기적으로 연결되어 제1전원전압을 스위칭하는 제3피모스 스위칭소자와 상기 제3피모스 스위칭소자와 상기 제1노드 사이에 전기적으로 연결되고, 제어전극이 제2노드에 전기적으로 연결된 제4피모스 스위칭소자와 상기 클럭선에 제어전극이 전기적으로 연결되어 제2전원전압을 스위칭하는 제3엔모스 스위칭소자와 상기 제3엔모스 스위칭소자와 상기 제1노드 사이에 전기적으로 연결되고, 제어전극이 제2노드에 전기적으로 연결된 제4엔모스 스위칭소자와 상기 제1전원전압선과 상기 제2노드 사이에 전기적으로 연결되고, 제어전극이 제1노드에 전기적으로 연결된 제5피모스 스위칭소자 및 상기 제2전원전압선과 상기 제2노드 사이에 전기적으로 연결되고, 제어전극이 제1노드에 전기적으로 연결된 제5엔모스 스위칭소자를 포함할 수 있다.

- <56> 상기 제2노드의 신호는 시프트 레지스터의 출력신호일 수 있다.

- <57> 상기 원시클럭선에 전기적으로 연결되어 원시클럭신호를 전달받아 상기 원시부클럭선으로 원시부클럭신호를 생성하는 클럭인버터를 포함할 수 있다.

- <58> 상기 제1클럭선은 기수 번째 낸드게이트에 전기적으로 연결될 수 있다.

- <59> 상기 제1클럭선에 로우레벨의 제1클럭신호가 인가되고 상기 제2클럭선에 하이레벨의 제2클럭신호가 인가되면, 기수 번째 화로회로부에 로우레벨의 주사신호가 인가되어 화소 회로부에 데이터 신호가 인가될 수 있다.

- <60> 상기 기수 번째 화소 회로부에 로우레벨의 발광제어신호가 인가되면 발광할 수 있다.

- <61> 상기 제2클럭선은 우수 번째 낸드게이트에 전기적으로 연결될 수 있다.

- <62> 상기 제1클럭선에 하이레벨의 제1클럭신호가 인가되고 상기 제2클럭선에 로우레벨의 제2클럭신호가 인가되면, 우수 번째 화로회로부에 로우레벨의 주사신호가 인가되어 화소 회로부에 데이터 신호가 인가될 수 있다.

- <63> 상기 우수 번째 화소 회로부에 로우레벨의 발광제어신호가 인가되면 발광할 수 있다.

- <64> 상기 초기구동선의 초기구동신호가 하이레벨이고 상기 제1발광제어선의 제1발광제어신호가 하이레벨일 때, 상기

제1클럭선에 하이레벨의 제1클럭신호가 인가되고, 상기 제2클럭선에 로우레벨의 제2클럭신호가 인가되면, 제1낸드게이트가 로우레벨의 제1주사신호를 제1주사선으로 출력할 수 있다.

<65> 상기 제1발광제어선의 제1발광제어신호가 하이레벨이고 상기 제2발광제어선의 제2발광제어신호가 하이레벨일 때, 상기 제1클럭선에 로우레벨의 제1클럭신호가 인가되고, 상기 제2클럭선에 하이레벨의 제2클럭신호가 인가되면, 제2낸드게이트가 로우레벨의 제2주사신호를 제2주사선으로 출력할 수 있다.

<66> 상기 제1발광제어선의 제1발광제어신호가 하이레벨이고 상기 제2발광제어선의 제2발광제어신호가 하이레벨일 때, 상기 제1클럭선에 하이레벨의 제1클럭신호가 인가되고, 상기 제2클럭선에 로우레벨의 제2클럭신호가 인가되면, 제3낸드게이트가 로우레벨의 제3주사신호를 제3주사선으로 출력할 수 있다.

<67> 상기 제2발광제어선의 제2발광제어신호가 하이레벨이고 상기 제3발광제어선의 제3발광제어신호가 하이레벨일 때, 상기 제1클럭선에 로우레벨의 제1클럭신호가 인가되고, 상기 제2클럭선에 하이레벨의 제2클럭신호가 인가되면, 제4낸드게이트가 로우레벨의 제4주사신호를 제4주사선으로 출력할 수 있다.

<68> 상기와 같이 하여 본 발명에 의한 유기 전계 발광 표시 장치는 유기 전계 발광 표시 패널의 픽셀 세로 쇼트 불량을 사전 검출 하여 모듈 공정 비용을 절감하고, 신뢰성이 높은 유기 전계 발광 표시 장치를 제공한다.

<69> 이하, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 본 발명을 용이하게 실시할 수 있을 정도로 본 발명의 바람직한 실시예를 첨부된 도면을 참조하여 상세하게 설명하면 다음과 같다.

<70> 여기서, 명세서 전체를 통하여 유사한 구성 및 동작을 갖는 부분에 대해서는 동일한 도면 부호를 붙였다. 또한, 어떤 부분이 다른 부분과 전기적으로 연결되어 있다고 할 때, 이는 직접적으로 연결되어 있는 경우뿐만 아니라 그 중간에 다른 소자를 사이에 두고 연결되어 있는 경우도 포함한다.

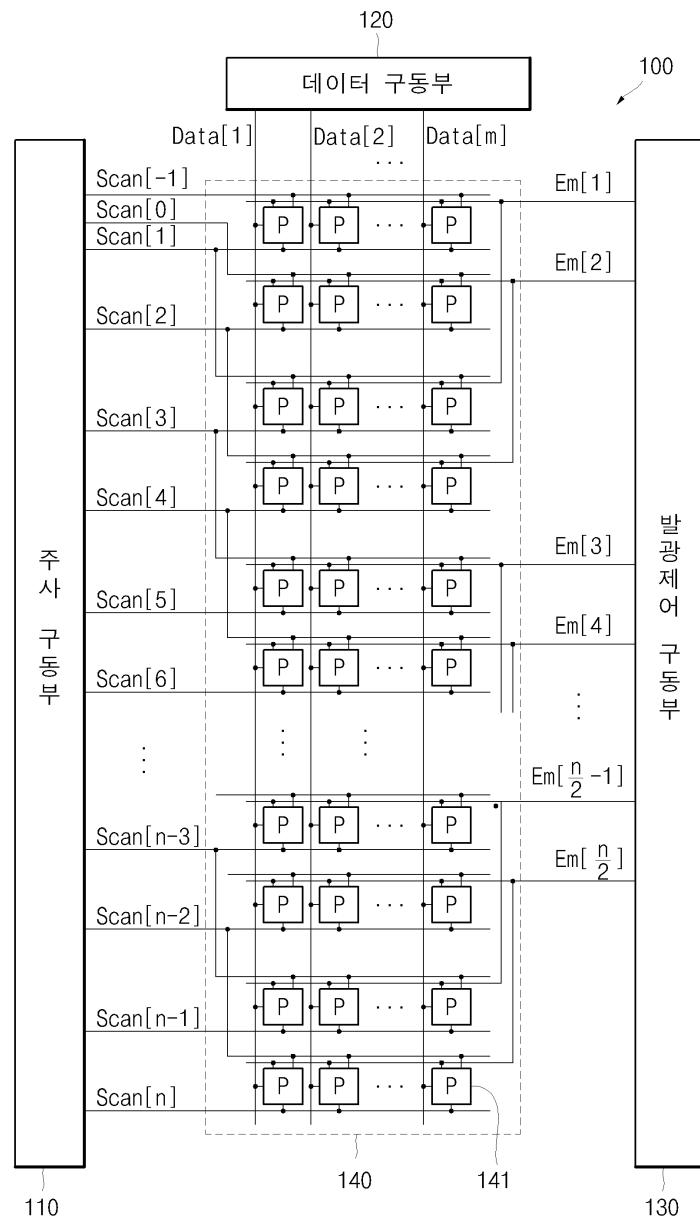

<71> 도 1을 참조하면, 본 발명에 따른 유기 전계 발광 표시 장치를 개략적으로 도시한 블록도가 도시되어 있다.

<72> 도 1에서 도시된 바와 같이 유기 전계 발광 표시 장치(100)는 주사구동부(110), 데이터구동부(120), 발광 제어 구동부(130) 및 유기 전계 발광 표시 패널(이하, 패널(140))를 포함 할 수 있다.

<73> 상기 주사 구동부(110)는 다수의 주사선(Scan[1], Scan[2], …, Scan[n])을 통하여 상기 패널(140)에 주사신호를 순차적으로 공급할 수 있다.

<74> 상기 데이터 구동부(120)는 다수의 데이터선 (Data[1], Data[2], …, Data[m])을 통하여 상기 패널(140)에 데이터 신호를 공급할 수 있다.

<75> 상기 발광 제어 구동부(130)는 다수의 발광제어선 (Em[1], Em[2], …, Em[n])을 통하여 상기 패널(140)에 발광 제어 신호를 순차적으로 공급할 수 있다. 또한 발광 제어 구동부(130)는 발광제어신호의 펄스폭을 조절할 수 있도록 하며 한 구간에서 발생하는 발광제어신호의 펄스의 수를 조절할 수 있다. 발광제어선 (Em[1], Em[2], …, Em[n])과 연결되어 있는 화소 회로(141, Pixel)는 발광제어신호를 전달받아 화소 회로(141)에서 생성된 전류가 발광소자로 흐르도록 하는 시점을 결정할 수 있다.

<76> 또한 상기 패널(140)은 열방향으로 배열되어 있는 다수의 주사선(Scan[1], Scan[2], …, Scan[n]) 및 발광제어선 (Em[1], Em[2], …, Em[n])과, 행방향으로 배열되는 다수의 데이터선(Data[1], Data[2], …, Data[m])과, 상기의 다수의 주사선(Scan[1], Scan[2], …, Scan[n]) 및 데이터선 (Data[1], Data[2], …, Data[m])과 발광제어선 (Em[1], Em[2], …, Em[n])에 의해 정의되는 화소 회로(141, Pixel)를 포함 할 수 있다.

<77> 여기서 상기 화소 회로(Pixel)는 기수 번째 주사선(또는 기수 번째 발광제어선)과 이웃하는 두 데이터선에 의해 정의 되는 화소 영역 기수 번째 화소부가 형성 될 수 있고, 우수 번째 주사선(또는 우수 번째 발광제어선)과 이웃하는 두 데이터선에 의해 정의 되는 화소 영역 우수 번째 화소부가 형성 될 수 있다. 물론, 상술한 바와 같이 상기 주사선(Scan[1], Scan[2], …, Scan[n])에는 상기 주사 구동부(110)로부터 주사신호가 공급될 수 있고, 상기 데이터선 (Data[1], Data[2], …, Data[m])에는 상기의 데이터 구동부(120)로부터 데이터 신호가 공급될 수 있으며, 상기 발광제어선 (Em[1], Em[2], …, Em[n])에는 상기 발광 제어 구동부(130)로부터 발광 제어 신호가 공급될 수 있다.

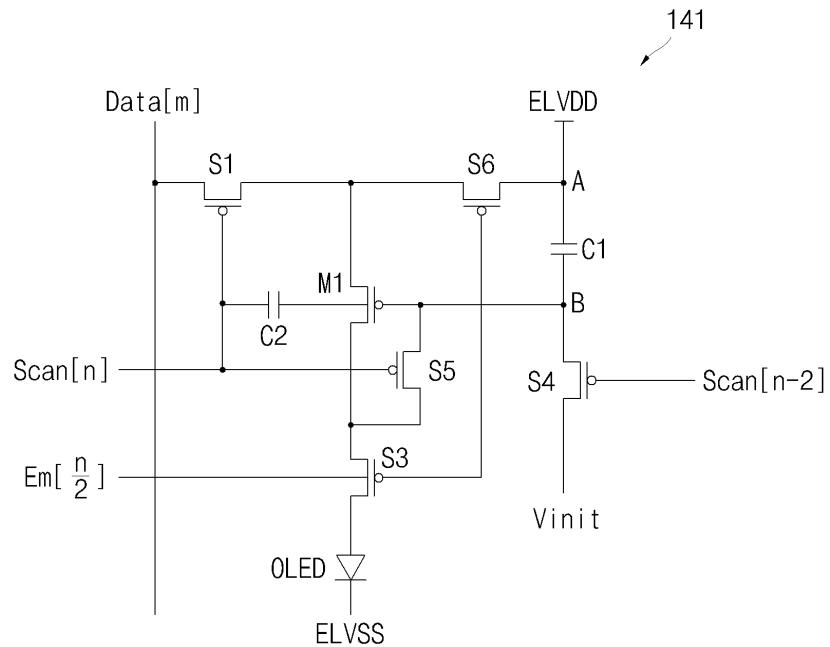

<78> 도 2를 참조하면, 본 발명에 따른 유기 전계 발광 표시 장치의 화소 회로의 회로도가 도시되어 있다.

<79> 도 2에서 도시된 바와 같이 유기 전계 발광 표시 장치의 화소 회로는 주사선(Scan[n]), 두 번째 이전주사선 (Scan[n-2]), 데이터선(Data[m]), 발광제어선(Em(n/2)), 제1전원 전압선(ELVDD), 제2전원 전압선(ELVSS), 제3전

원 진압선(Vinit), 구동트랜지스터(M1), 제1스위칭 소자(S1), 제2스위칭 소자(S2), 제3스위칭소자(S3), 제4스위칭소자(S4), 제5스위칭 소자(S5), 제1용량성소자(C1), 제2용량성소자(C2) 및 유기 전계 발광 소자(OLED)를 포함할 수 있다.

- <80> 상기 주사선(Scan[n])은 발광 시키고자 하는 유기 전계 발광 소자(OLED)를 선택하는 주사신호를 상기 제1스위칭 소자(S1)의 제어 전극에 공급하는 역할을 한다. 물론, 이러한 주사선(Scan[n])은 주사신호를 생성하는 주사 구동부(110, 도 1 참조)에 전기적으로 연결될 수 있다.

- <81> 상기 두 번째 이전주사선(Scan[n-2])은 앞서 선택되는 n-2번째 주사선을 공통 연결하여 이용한다는 점에서 Scan[n-2]로 표시하였다. 다시 말하면 상기 두 번째 이전주사선(Scan[n-2])은 기수 번째 주사선일 경우 이전 기수 번째 주사선이고, 우수 번째 주사선일 경우 이전 우수 번째 주사선과 공통으로 연결하여 이용한다는 점에서 Scan[n-2]로 표시하였다. 상기 두 번째 이전주사선(Scan[n-2])은 제3전원 전압(Vinit)을 제1용량성 소자(C1)와 제2용량성 소자(C2)에 인가하여 제1용량성 소자(C1)와 제2용량성 소자(C2)에 저장되어 있던 전압을 초기화 시킬 수 있다.

- <82> 상기 데이터선(Data[m])은 발광 회도에 비례하는 데이터 신호(전압)를 상기 제1용량성 소자(C1)의 제1전극(A) 및 상기 구동트랜지스터(M1)의 제1전극에 공급하는 역할을 할 수 있다. 물론, 이러한 데이터선(Data[m])은 데이터 신호를 생성하는 데이터 구동부(120, 도 1 참조)에 전기적으로 연결될 수 있다.

- <83> 상기 발광제어선(Em[n/2])은 실질적으로 상기 유기 전계 발광 소자(OLED)의 발광 시간을 제어할 수 있도록, 상기 제3스위칭 소자(S3)의 제어 전극에 전기적으로 연결되어 제3스위칭 소자(S3)를 제어할 수 있다. 발광제어선(Em[n/2])은 발광제어신호를 생성하는 발광 제어 구동부(130, 도 1참조)에 전기적으로 연결될 수 있다.

- <84> 상기 제1전원 전압선(ELVDD)은 제1전원전압이 유기 전계 발광 소자(OLED)에 공급되도록 할 수 있다.

- <85> 상기 제2전원 전압선(ELVSS)은 제2전원전압이 유기 전계 발광 소자(OLED)에 공급되도록 한다. 여기서, 상기 제1전원전압은 통상적으로 상기 제2전원전압에 비해 하이 레벨(high level)일 수 있다.

- <86> 상기 제3전원 전압선(Vinit)은 제3전원전압이 제1용량성 소자(C1)와 제2용량성소자(C2)에 인가되어 상기 제1용량성 소자(C1)와 제2용량성 소자(C2)에 저장되어 있던 전압을 초기화 시킬 수 있다.

- <87> 상기 제1스위칭 소자(S1)는 제1전극(드레인 전극 또는 소스 전극)이 상기 데이터선(Data[m])에 전기적으로 연결되고, 제2전극(소스 전극 또는 드레인 전극)이 구동트랜지스터(M1)의 제1전극에 전기적으로 연결되며, 제어 전극(게이트 전극)이 주사선(Scan[n])에 전기적으로 연결될 수 있다. 이러한 제1스위칭 소자(S1)는 턴온되면, 데이터 신호를 제1용량성 소자(C1)의 제1전극(A) 및 구동트랜지스터(M1)의 제1전극에 공급할 수 있다.

- <88> 상기 제2스위칭 소자(S2)는 제1전극이 제1스위칭 소자(S1)와 구동트랜지스터(M1) 사이에 전기적으로 연결되고, 제2전극이 제1전원전압선(ELVDD)과 제1용량성소자(C1)의 제1전극에 전기적으로 연결되며, 제어전극이 발광 제어 선(Em/2)에 전기적으로 연결될 수 있다. 상기 제2스위칭 소자(S2)는 제어 전극에 로우레벨의 주사신호가 인가되면, 턴온되어 구동트랜지스터(M1)에 제1전원전압(V<sub>b</sub>)을 인가할 수 있다.

- <89> 상기 제3스위칭 소자(S3)는 제1전극이 구동트랜지스터(M1)와 제5스위칭 소자(S5)사이에 전기적으로 연결되고, 제2전극이 유기 전계 발광 소자(OLED)의 애노드에 전기적으로 연결되며, 제어전극이 발광제어선(Em[n/2])에 전기적으로 연결될 수 있다. 상기 제3스위칭 소자(S3)는 제어전극에 로우레벨의 발광제어 신호가 인가되면 턴온되어 구동트랜지스터(M1)의 구동전류를 유기 전계 발광 소자(OLED)로 흘르게 할 수 있다.

- <90> 상기 제4스위칭 소자(S4)는 제1전극이 구동트랜지스터(M1)의 제어전극과 제1용량성 소자(C1) 사이에 전기적으로 연결되고, 제2전극이 제3전원전압선(Vinit)에 전기적으로 연결되며, 제어전극이 두 번째 이전 주사선(Scan[n-2])에 전기적으로 연결될 수 있다. 상기 제4스위칭 소자(S4)는 제어전극에 로우레벨의 주사신호가 인가되면 턴온되어 제1용량성 소자(C1)와 제2용량성 소자(C2)에 저장되어 있던 전압을 초기화시킨다.

- <91> 상기 제5스위칭 소자(S5)는 제1전극이 구동트랜지스터(M1)의 제어전극과 제1용량성 소자(C1) 사이에 전기적으로 연결되고, 제2전극이 구동트랜지스터(M1)와 제3스위칭 소자(S3) 사이에 전기적으로 연결되며, 제어전극이 주사선(Scan[n])에 전기적으로 연결된다. 상기 제5스위칭 소자(S5)는 제어전극에 로우레벨의 주사신호가 인가되면 턴온되어 구동트랜지스터(M1)를 다이오드 구조로 연결한다.

- <92> 상기 제1용량성 소자(C1)는 제1전극이 제1전원전압선(ELVDD)과 제2스위칭 소자(S2) 사이에 전기적으로 연결되고, 제2전극이 구동트랜지스터(M1)와 제4스위칭 소자(S4) 사이에 전기적으로 연결될 수 있다. 상기 제1용

량성 소자(C1)는 제1전극(A)과 제2전극(B) 사이에 전압차를 저장할 수 있다.

<93> 상기 제2용량성 소자(C2)는 제1전극이 상기 주사선(Scan[n])과 제1스위칭 소자(S1)의 제어전극 사이에 전기적으로 연결되고, 제2전극이 구동트랜지스터(M1)의 제어전극에 전기적으로 연결될 수 있다. 화소 회로를 구동하기 위한 제1전원전압은 데이터 전압의 최대 계조 전압 보다 작거나 같아야 한다. 데이터 전압이 최대 계조 전압(블랙전압)일 때 제1전원전압선(ELVDD)의 제1전원전압이 일정 전압 이하가 되어야 한다. 이때, 유기 전계 발광 소자(OLED)의 구동전압은 일정하게 유지되어야 하므로, 제2전원전압선(ELVSS)의 제2전원전압도 떨어지게 된다. 즉, 데이터전압의 최대 계조 전압(블랙전압)은 약 5V이므로 제1전원전압 또한 5V를 넘어서 설정할 수 없다. 따라서 제1전원전압과 제2전원전압의 전압차가 11V를 유지하기 위하여 제2전원전압은 음의 전압 값 -6V을 가져야 하며, 그 경우 제1전원전압과 제2전원전압을 공급하는 디시/디시컨버터(DC/DC Converter) 효율이 상대적으로 떨어져서 화소 회로의 전체 효율이 감소하게 된다. 디시/디시컨버터(DC/DC Converter) 효율을 증가시키기 위하여 제1전원전압과 제2전원전압 모두 양의 전압 범위를 가지는 것이 바람직하다.

<94> 이를 보상하기 위하여 제2용량성 소자(C2)를 연결하였다. 이러한 상기 제2용량성 소자(C2)는 구동트랜지스터의 제어전극의 전압을 상승시킬 수 있다. 여기서 제어전극의 전압은 데이터전압과 문턱전압의 합으로 나타낼 수 있다.

<95> 상기 구동트랜지스터(M1)는 제1전극이 제1스위칭 소자(S1)와 제2스위칭 소자(S2) 사이에 전기적으로 연결되고 제2전극은 제5스위칭 소자(S5)와 제3스위칭 소자(S3) 사이에 전기적으로 연결되며, 제어전극이 제1용량성 소자(C1), 제4스위칭 소자(S4) 및 제5스위칭 소자(S5) 사이에 전기적으로 연결된다. 이러한 구동트랜지스터(M1)는 제1전원전압선(ELVDD)에서 인가되는 제1전원전압과 데이터선(Data[m])에서 인가되는 데이터전압으로 생성된 일정량의 전류를 유기 전계 발광 소자(OLED) 쪽으로 공급하는 역할을 한다.

<96> 상기 유기 전계 발광 소자(OLED)는 애노드가 제3스위칭소자의 제2전극에 전기적으로 연결되고 캐소드가 제2전원전압선(ELVSS)에 전기적으로 연결될 수 있다. 상기 구동트랜지스터(M1)에서 인가되는 전류가 제3스위칭 소자(S3)를 통해서 유기 전계 발광 소자(OLED)에 인가되어 유기 전계 발광 소자(OLED)는 소정 밝기로 발광 한다.

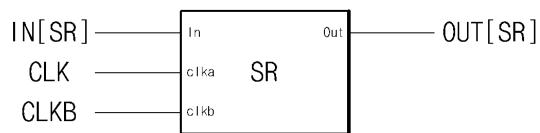

<97> 도 3을 참조하면, 본 발명에 따른 유기 전계 발광 표시 장치의 주사구동부와 발광제어구동부에서 시프트 레지스터의 블록도가 도시되어 있다.

<98> 도3에서 도시된 바와 같이 시프트 레지스터는 시프트레지스터 입력신호(IN[SR]), 클럭신호(CLK) 및 부클럭신호(CLKB)가 입력되어 시프트레지스터 입력신호(IN[SR])가 일측으로 시프트된 시프트레지스터 출력신호(OUT[SR])를 출력할 수 있다. 상기 시프트레지스터는 로우레벨의 클럭신호(CLK)와 하이레벨의 부클럭신호(CLKB)가 인가될 때는 입력신호(IN[SR])와 동일한 출력신호(OUT[SR])를 출력하고, 하이레벨의 출력신호(OUT[SR])와 로우레벨의 부클럭신호(CLKB)가 인가될 때는 이전 출력신호와 동일한 출력신호(OUT[SR])를 출력할 수 있다. 여기서 이전 출력신호는 하이레벨의 출력신호(OUT[SR])와 로우레벨의 부클럭신호(CLKB)가 인가되기 직전에 로우레벨의 클럭신호(CLK)와 하이레벨의 부클럭신호(CLKB)가 인가될 때의 출력되었던 출력신호를 의미한다.

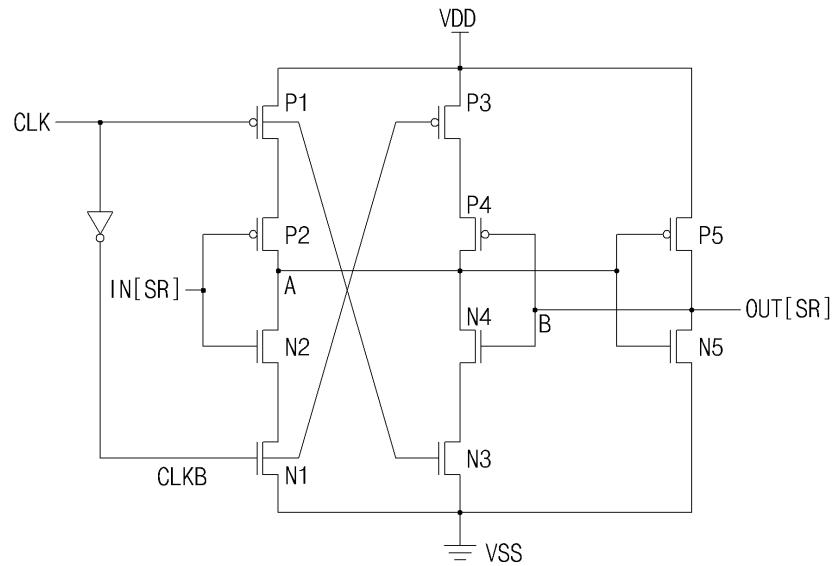

<99> 도 4를 참조하면, 도 3에 도시된 시프트 레지스터의 회로도가 도시되어 있다.

<100> 도 3에서 도시된 바와 같이, 본 발명에 따른 유기 전계 발광 표시 장치의 주사구동부와 발광제어구동부에서 시프트 레지스터는 클럭신호(CLK), 부클럭신호(CLKB), 시프트레지스터 입력신호(IN[SR]), 제1전원 전압선(VDD), 제2전원 전압선(VSS), 제1피모스스위칭소자(P1), 제2피모스 스위칭소자(P2), 제3피모스 스위칭소자(P3), 제4피모스스위칭소자(P4), 제5피모스 스위칭소자(P5), 제1엔모스 스위칭소자(N1), 제2엔모스 스위칭소자(N2), 제3엔모스 스위칭소자(N3), 제4엔모스 스위칭소자(N4) 및 제5엔모스 스위칭소자(N5)를 포함할 수 있다.

<101> 상기 클럭신호(CLK)와 상기 부클럭신호(CLKB)는 반대되는 신호로 상기 클럭신호(CLK)가 하이레벨일 경우에, 상기 부클럭신호(CLKB)는 로우레벨이 되고, 상기 클럭신호(CLK)가 로우레벨일 경우에, 상기 부클럭신호(CLKB)는 하이레벨이 된다.

<102> 상기 제1전원 전압선(VDD)은 제1전원전압이 시프트레지스터(SR)에 공급될 수 있다.

<103> 상기 제2전원 전압선(VSS)은 제2전원전압이 시프트레지스터(SR)에 공급되도록 한다. 여기서, 상기 제1전원전압은 통상적으로 상기 제2전원전압에 비해 하이 레벨(high level)일 수 있다.

<104> 상기 제1피모스 스위칭소자(P1)의 제1전극(드레인 전극 또는 소스 전극)은 제1전원전압(VDD)에 전기적으로 연결되고 제2전극(소스 전극 또는 드레인 전극)은 제2피모스 스위칭소자(P2)에 전기적으로 연결되고, 제어전극(케이트 전극)은 클럭신호(CLK)에 전기적으로 연결될 수 있다. 이러한 제1피모스 스위칭소자(P1)는 제어전극에 로우

레벨의 클럭신호(CLK)가 입력되면 턴온되어 제1전원전압(VDD)을 제2피모스 스위칭소자(P2)의 제1전극에 공급할 수 있다.

<105> 상기 제2피모스 스위칭소자(P2)의 제1전극은 상기 제1피모스 스위칭소자(P1)의 제2전극에 전기적으로 연결되고, 제2전극은 상기 제1엔모스 스위칭소자(N1)의 제1전극 즉, 제1노드(A)에 전기적으로 연결되고, 제어전극은 시프트레지스터 입력신호(IN[SR])에 전기적으로 연결될 수 있다. 이러한 제2피모스 스위칭소자(P2)는 제어전극에 로우레벨의 시프트레지스터 입력신호(IN[SR])가 입력되면 턴온되어 제1피모스 스위칭소자(P1)에서 공급받은 제1전원전압(VDD)를 제1노드(A)로 공급할 수 있다.

<106> 상기 제3피모스 스위칭소자(P3)의 제1전극은 제1전원전압(VDD)에 전기적으로 연결되고 제2전극은 제4피모스 스위칭소자(P4)에 전기적으로 연결되고, 제어전극은 부클럭신호(CLKB)에 전기적으로 연결될 수 있다. 이러한 제3피모스 스위칭소자(P3)는 제어전극에 로우레벨의 부클럭신호(CLKB)가 입력되면 턴온되어 제1전원전압(VDD)을 제4피모스 스위칭소자(P4)의 제1전극에 공급할 수 있다.

<107> 상기 제4피모스 스위칭소자(P4)의 제1전극은 상기 제3피모스 스위칭소자(P3)의 제2전극에 전기적으로 연결되고, 제2전극은 상기 제3엔모스 스위칭소자(N3)의 제1전극 즉, 제1노드(A)에 전기적으로 연결되고, 제어전극은 시프트레지스터 출력신호(OUT[SR])에 전기적으로 연결될 수 있다. 이러한 제4피모스 스위칭소자(P4)는 제어전극에 로우레벨의 시프트레지스터 출력신호(OUT[SR])가 입력되면 턴온되어 제3피모스 스위칭소자(P3)에서 공급받은 제1전원전압(VDD)를 제1노드(A)로 공급할 수 있다.

<108> 상기 제5피모스 스위칭소자(P5)의 제1전극은 제1전원전압(VDD)에 전기적으로 연결되고 제2전극은 제5엔모스 스위칭소자(N5)의 제1전극에 전기적으로 연결되고, 제어전극은 제1노드(A)에 전기적으로 연결될 수 있다. 이러한 제5피모스 스위칭소자(P5)는 제어전극에 로우레벨의 신호가 제1노드(A)를 통해 입력되면 턴온되어 제1전원전압(VDD)을 시프트레지스터 출력신호(OUT[SR])로 출력할 수 있다.

<109> 상기 제1엔모스 스위칭소자(N1)의 제1전극은 제2엔모스 스위칭소자(N2)에 전기적으로 연결되고 제2전극은 제2전원전압(VSS)에 전기적으로 연결되고 제어전극은 부클럭신호(CLKB)에 전기적으로 연결될 수 있다. 이러한 제1엔모스 스위칭소자(N1)는 제어전극에 하이레벨의 부클럭신호(CLKB)가 입력되면 턴온되어 제2전원전압(VSS)을 제2엔모스 스위칭소자(N2)의 제2전극에 공급할 수 있다.

<110> 상기 제2엔모스 스위칭소자(N2)의 제1전극은 상기 제2피모스 스위칭소자(P2)의 제2전극 즉, 제1노드(A)에 전기적으로 연결되고, 제2전극은 상기 제1엔모스 스위칭소자(N1)의 제1전극에 전기적으로 연결되고, 제어전극은 시프트레지스터 입력신호(IN[SR])에 전기적으로 연결될 수 있다. 이러한 제2엔모스 스위칭소자(N2)는 제어전극에 하이레벨의 시프트레지스터 입력신호(IN[SR])가 입력되면 턴온되어 제1엔모스 스위칭소자(N1)에서 공급받은 제2전원전압(VSS)를 제1노드(A)로 공급할 수 있다.

<111> 상기 제3엔모스 스위칭소자(N3)의 제1전극은 제4엔모스 스위칭소자(N4)에 전기적으로 연결되고 제2전극은 제2전원전압(VSS)에 전기적으로 연결되고 제어전극은 클럭신호(CLK)에 전기적으로 연결될 수 있다. 이러한 제3엔모스 스위칭소자(N3)는 제어전극에 하이레벨의 클럭신호(CLK)가 입력되면 턴온되어 제2전원전압(VSS)을 제4엔모스 스위칭소자(N4)의 제2전극에 공급할 수 있다.

<112> 상기 제4엔모스 스위칭소자(N4)의 제1전극은 상기 제4피모스 스위칭소자(P4)의 제2전극 즉, 제1노드(A)에 전기적으로 연결되고, 제2전극은 상기 제3엔모스 스위칭소자(N3)의 제1전극에 전기적으로 연결되고, 제어전극은 시프트레지스터 출력신호(OUT[SR])에 전기적으로 연결될 수 있다. 이러한 제4엔모스 스위칭소자(N4)는 제어전극에 하이레벨의 시프트레지스터 출력신호(OUT[SR])가 입력되면 턴온되어 제3엔모스 스위칭소자(N3)에서 공급받은 제2전원전압(VSS)를 제1노드(A)로 공급할 수 있다.

<113> 상기 제5엔모스 스위칭소자(N5)의 제5피모스 스위칭소자(P5)의 제2전극에 전기적으로 연결되고, 제2전극은 제2전원전압(VSS)에 전기적으로 연결되고, 제어전극은 제1노드(A)에 전기적으로 연결될 수 있다. 이러한 제5엔모스 스위칭소자(N5)는 제어전극에 하이레벨의 신호가 제1노드(A)를 통해 입력되면 턴온되어 제2전원전압(VSS)을 시프트레지스터 출력신호(OUT[SR])로 출력할 수 있다.

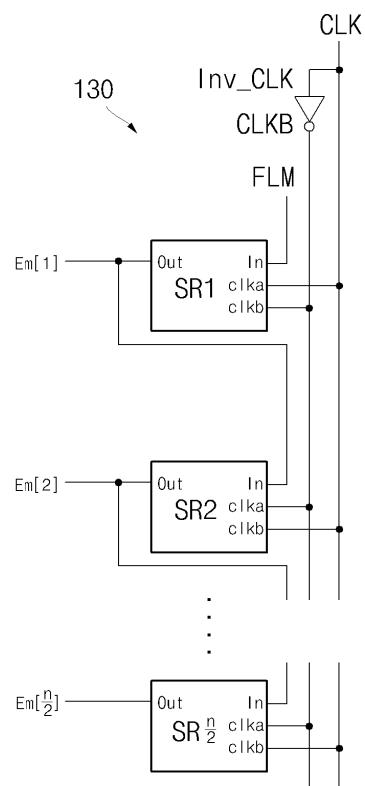

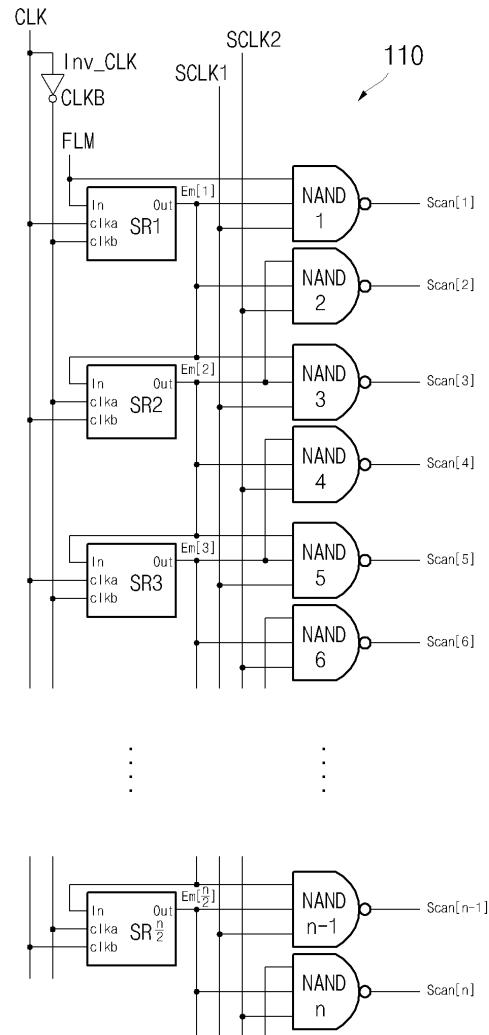

<114> 도 5를 참조하면, 본 발명에 따른 유기 전계 발광 표시 장치의 발광제어구동부를 도시한 블록도가 도시되어 있다.

<115> 도 5에 도시된 바와 같이 유기 전계 발광 표시 장치의 발광제어구동부는 클럭인버터(Inv\_CLK)와 제1시프트레지스터(SR1) 내지 제n/2시프트레지스터(SRn/2)를 포함할 수 있다.

- <116> 상기 클럭인버터(Inv\_CLK)는 상기 클럭신호(CLK)를 전달받아 상기 부클럭신호(CLKB)를 생성하여 제1시프트레지스터(SR1) 내지 제n/2시프트레지스터(SRn/2)에 공급할 수 있다. 그리고 상기 클럭신호(CLK)가 하이레벨일 경우에, 상기 부클럭신호(CLKB)는 로우레벨이 되고, 상기 클럭신호(CLK)가 로우레벨일 경우에, 상기 부클럭신호(CLKB)는 하이레벨이 되는 반대되는 신호이다.

- <117> 상기 제1시프트레지스터(SR1)는 입력단자(In)가 초기구동선(FLM)과 전기적으로 연결되고, 제1클럭단자(clka)가 원시클럭선(CLK)에 전기적으로 연결되며, 제2클럭단자(clkb)가 원시부클럭선(CLKB)에 전기적으로 연결되어 출력단자(Out)로 제1시프트레지스터(SR1)의 출력신호를 출력할 수 있다. 상기 제1시프트레지스터(SR1)의 출력신호는 초기구동신호를 일측으로 시프트한 신호로, 제1발광제어선(Em[1])으로 출력되는 제1발광제어신호가 된다. 상기 제1시프트레지스터(SR1)의 출력신호인 제1발광제어신호는 제2시프트레지스터(SR2)의 입력신호일수 있다.

- <118> 상기 제2시프트레지스터(SR2)는 입력단자(In)가 제1발광제어선(Em[1])과 전기적으로 연결되고, 제1클럭단자(clka)가 원시부클럭선(CLKB)에 전기적으로 연결되며, 제2클럭단자(clkb)가 원시클럭선(CLK)에 전기적으로 연결되어 출력단자(Out)로 제2시프트레지스터(SR2)의 출력신호를 출력한다. 상기 제2시프트레지스터(SR2)의 출력신호는 제1발광제어신호를 일측으로 시프트한 신호로, 제2발광제어선(Em[2])으로 출력되는 제2발광제어신호가 될 수 있다. 상기 제2시프트레지스터(SR2)의 출력신호인 제2발광제어신호는 제3시프트레지스터(SR3)의 입력신호일 수 있다.

- <119> 상기 제3시프트레지스터(SR3) 내지 제n/2시프트레지스터(SRn/2) 중 기수 번째 시프트레지스터는 상기 제1시프트레지스터(SR1)와 동일하게 제1클럭단자(clka)가 원시클럭선(CLK)에 전기적으로 연결되며, 제2클럭단자(clkb)가 원시부클럭선(CLKB)에 전기적으로 연결되어 출력단자(Out)로 출력신호를 출력할 수 있다. 그리고, 우수 번째 시프트레지스터는 제2시프트레지스터(SR2)와 동일하게 제1클럭단자(clka)가 원시부클럭선(CLKB)에 전기적으로 연결되며, 제2클럭단자(clkb)가 원시클럭선(CLK)에 전기적으로 연결되어 출력단자(Out)로 출력신호를 출력할 수 있다. 이때, 시프트레지스터의 입력단자는 이전 시프트레지스터의 출력단자(Out)로 출력된 발광제어신호가 인가된다. 즉, 제3시프트레지스터(SR3) 내지 제n/2시프트레지스터(SRn/2)의 입력단자(In)에는 제2시프트레지스터(SR2) 내지 제n/2-1시프트레지스터(SRn/2-1)의 출력단자(Out)로 출력된 제2발광제어신호 내지 제n/2-1발광제어신호가 각각 인가될 수 있다.

- <120> 상기 제1발광제어선(Em[1]) 내지 제n/2발광제어선(Em[n/2])은 유기 전계 발광 표시 패널(140, 도 1참조)와 전기적으로 연결되어 발광제어신호를 유기 전계 발광 표시 패널(140, 도 1참조)에 인가할 수 있다.

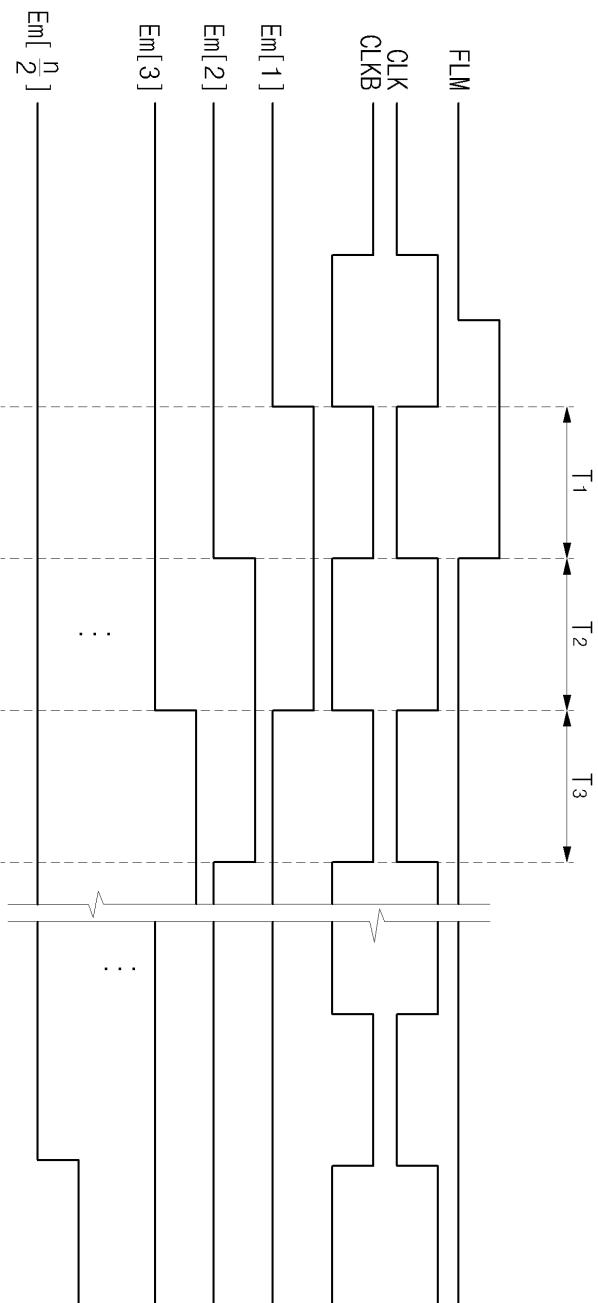

- <121> 도 6을 참조하면 도5에 도시된 발광제어구동부의 타이밍 도가 도시되어 있다.

- <122> 도 6에 도시된 바와 같이 발광제어구동부의 타이밍 도는 제1구동기간(T1), 제2구동기간(T2) 및 제3구동기간(T3)을 포함할 수 있다. 여기서 시프트레지스터는 제1클럭단자(clka)에 로우레벨의 클럭신호가 인가되고 제2클럭단자(clkb)에 하이레벨의 클럭신호가 인가될 때는 입력단자에 인가된 신호와 동일한 신호를 출력하고, 제1클럭단자(clka)에 하이레벨의 클럭신호가 인가되고 제2클럭단자(clkb)에 로우레벨의 클럭신호가 될 때는 이전 기간에 출력단자에 출력되었던 신호와 동일한 신호를 출력한다. 상기 제1시프트레지스터(SR1) 내지 상기 제n/2시프트레지스터(n/2)는 제1구동기간(T1) 내지 제3구동기간(T3)과 이전 시프트레지스터에서 인가받은 입력신호, 이전 구동기간의 출력신호, 원시클럭신호, 원시부클럭신호에 의해서 하이레벨의 제1발광제어신호 내지 제n/2발광제어신호를 순차적으로 출력할 수 있다.

- <123> 상기 제1구동기간(T1)은 초기구동선(FLM)에서 하이레벨의 초기구동신호, 원시클럭선(CLK)에서 로우레벨의 원시클럭신호 및 원시부클럭선(CLKB)에서 하이레벨의 원시부클럭신호가 인가될 수 있다.

- <124> 먼저, 제1시프트레지스터(SR1)는 입력단자에 하이레벨의 초기구동신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 원시부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 하이레벨의 초기구동신호와 동일한 하이레벨의 제1발광제어신호를 출력할 수 있다.

- <125> 다음 제2시프트레지스터(SR2)는 입력단자에 하이레벨의 제1발광제어신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 원시클럭신호가 인가되므로, 출력단자는 이전구동기간의 출력신호와 동일한 로우레벨의 제2발광제어신호를 출력할 수 있다.

- <126> 다음 제3시프트레지스터(SR3)는 입력단자에 로우레벨의 제2발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 로우레벨의 제2발광제어신호와 동일한 로우레벨의 제3발광제어신호를 출력할 수 있다.

- <127> 마지막으로 제4시프트레지스터(SR4) 내지 제n/2시프트레지스터(n/2)중 우수 번째 레지스터는 제2시프트레지스터(SR2)와 동일하게 동작하여 로우레벨의 발광신호를 출력하고, 기수 번째 레지스터는 제3시프트레지스터(SR3)과 동일하게 동작하여 로우레벨의 발광신호를 출력할 수 있다.

- <128> 상기 제2구동기간(T2)은 초기구동선(FLM)에서 로우레벨의 초기구동신호, 원시클럭선(CLK)에서 하이레벨의 원시클럭신호 및 원시부클럭선(CLKB)에서 로우레벨의 원시부클럭신호가 인가될 수 있다.

- <129> 먼저, 제1시프트레지스터(SR1)는 입력단자에 로우레벨의 초기구동신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 원시부클럭신호가 인가되므로, 출력단자는 제1구동기간(T1)의 출력신호와 동일한 하이레벨의 제1발광제어신호를 출력할 수 있다.

- <130> 다음 제2시프트레지스터(SR2)는 입력단자에 하이레벨의 제1발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 원시클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 하이레벨의 제1발광제어신호와 동일한 하이레벨의 제2발광제어신호를 출력할 수 있다.

- <131> 다음 제3시프트레지스터(SR3)는 입력단자에 하이레벨의 제2발광제어신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 부클럭신호가 인가되므로, 출력단자는 제1구동기간(T1)의 출력신호와 동일한 로우레벨의 제3발광제어신호를 출력할 수 있다.

- <132> 다음 제4시프트레지스터(SR2)는 입력단자에 로우레벨의 제3발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 원시클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 로우레벨의 제3발광제어신호와 동일한 로우레벨의 제4발광제어신호를 출력할 수 있다.

- <133> 마지막으로 제5시프트레지스터(SR5) 내지 제n/2시프트레지스터(n/2)중 기수 번째 레지스터는 제3시프트레지스터(SR3)과 동일하게 동작하여 로우레벨의 발광신호를 출력하고, 우수 번째 레지스터는 제4시프트레지스터(SR4)와 동일하게 동작하여 로우레벨의 발광신호를 출력한다.

- <134> 상기 제3구동기간(T3)은 초기구동선(FLM)에서 로우레벨의 초기구동신호, 원시클럭선(CLK)에서 로우레벨의 원시클럭신호 및 원시부클럭선(CLKB)에서 하이레벨의 원시부클럭신호가 인가될 수 있다.

- <135> 먼저, 제1시프트레지스터(SR1)는 입력단자에 로우레벨의 초기구동신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 원시부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 로우레벨의 초기구동신호와 동일한 로우레벨의 제1발광제어신호를 출력할 수 있다.

- <136> 다음 제2시프트레지스터(SR2)는 입력단자에 로우레벨의 제1발광제어신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 원시클럭신호가 인가되므로, 출력단자는 제2구동기간(T2)의 출력신호와 동일한 하이레벨의 제2발광제어신호를 출력할 수 있다.

- <137> 다음 제3시프트레지스터(SR3)는 입력단자에 하이레벨의 제2발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 하이레벨의 제2발광제어신호와 동일한 하이레벨의 제3발광제어신호를 출력할 수 있다.

- <138> 다음 제4시프트레지스터(SR4)는 입력단자에 하이레벨의 제3발광제어신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 원시클럭신호가 인가되므로, 출력단자는 제2구동기간(T2)의 출력신호와 동일한 로우레벨의 제4발광제어신호를 출력할 수 있다.

- <139> 다음 제5시프트레지스터(SR5)는 입력단자에 로우레벨의 제4발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 로우레벨의 제4발광제어신호와 동일한 로우레벨의 제5발광제어신호를 출력할 수 있다.

- <140> 마지막으로 제6시프트레지스터(SR6) 내지 제n/2시프트레지스터(n/2)중 우수 번째 레지스터는 제4시프트레지스터(SR4)와 동일하게 동작하여 로우레벨의 발광신호를 출력하고, 기수 번째 레지스터는 제5시프트레지스터(SR5)과 동일하게 동작하여 로우레벨의 발광신호를 출력할 수 있다.

- <141> 상기 제1시프트레지스터(SR1) 내지 상기 제n/2시프트레지스터(n/2)는 제1구동기간(T1) 내지 제3구동기간(T3)과 이전 시프트레지스터에서 인가받은 입력신호와 이전 구동기간의 출력신호에 의해서 하이레벨의 제1발광제어신호 내지 제n/2발광제어신호를 순차적으로 출력할 수 있다.

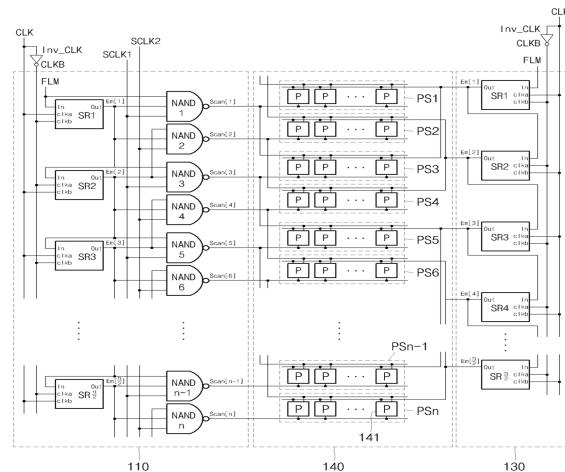

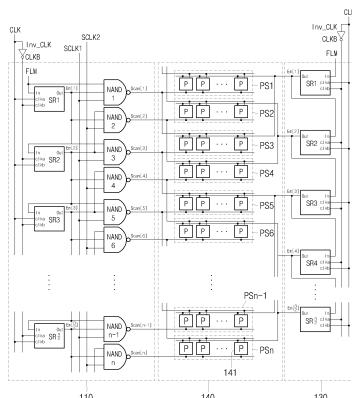

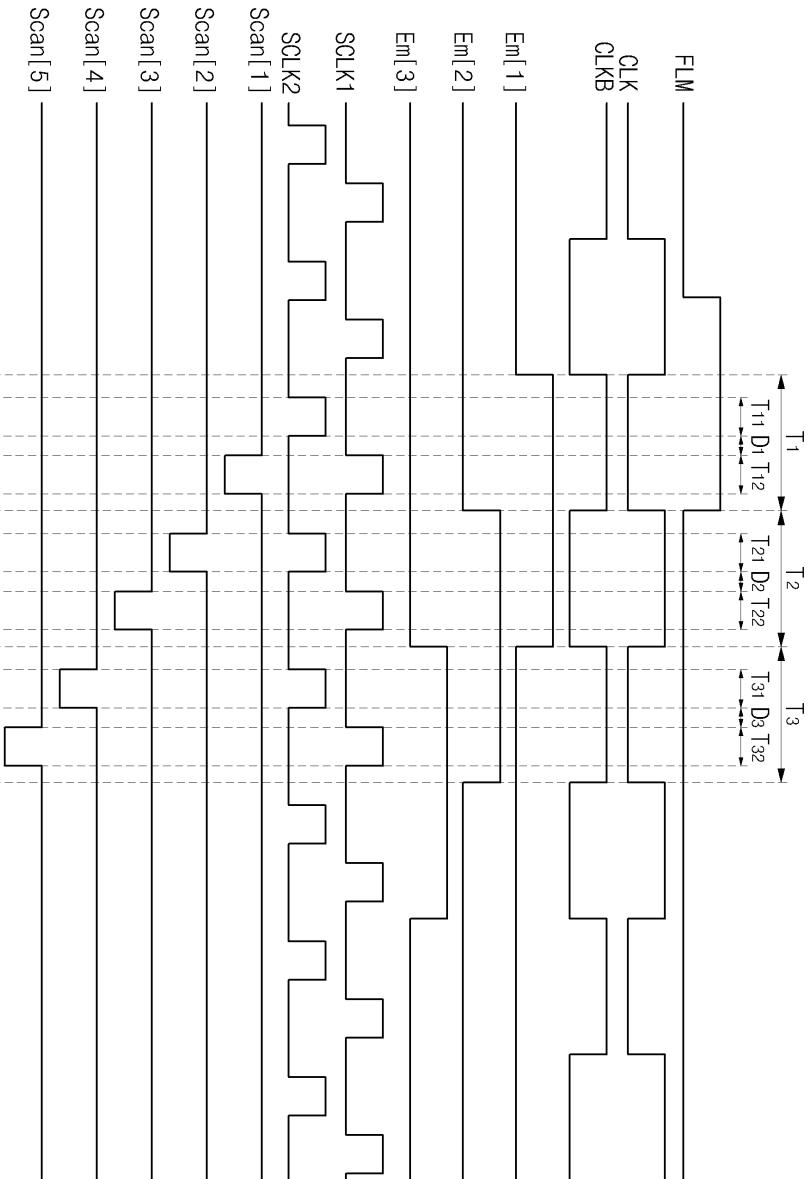

- <142> 도 7을 참조하면 본 발명에 따른 유기 전계 발광 표시 장치의 주사구동부를 도시한 블록도가 도시되어 있다.

- <143> 도 7에서 도시된 바와 같이, 유기 전계 발광 표시 장치의 주사구동부는 클럭인버터(Inv\_CLK), 제1시프트레지스터(SR1) 내지 제 n/2시프트레지스터(SRn/2) 및 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)을 포함할 수 있다. 상기 제1시프트레지스터(SR1) 내지 제 n/2시프트레지스터(SRn/2)는 도5에 도시된 발광제어구동부의 제1시프트레지스터(SR1) 내지 제 n/2시프트레지스터(SRn/2)와 동일한 시프트레지스터이다. 그러므로 제1시프트레지스터(SR1) 내지 제 n/2시프트레지스터(SRn/2)의 출력신호는 제1발광제어신호 내지 제n/2발광제어신호(n/2)이다. 상기 클럭인버터(Inv\_CLK)도 도 5에 도시된 클럭인버터(Inv\_CLK)와 동일한 인버터이다.

- <144> 상기 클럭인버터(Inv\_CLK)는 상기 클럭신호(CLK)를 전달받아 상기 부클럭신호(CLKB)를 생성하여 제1시프트레지스터(SR1) 내지 제n/2시프트레지스터(SRn/2)에 공급할 수 있다. 그리고 상기 클럭신호(CLK)가 하이레벨일 경우에, 상기 부클럭신호(CLKB)는 로우레벨이 되고, 상기 클럭신호(CLK)가 로우레벨일 경우에, 상기 부클럭신호(CLKB)는 하이레벨이 되는 반대되는 신호이다.

- <145> 상기 제1시프트레지스터(SR1)는 입력단자(In)가 초기구동선(FLM)과 전기적으로 연결되고, 제1클럭단자(clka)가 원시클럭선(CLK)에 전기적으로 연결되며, 제2클럭단자(clkb)가 원시부클럭선(CLKB)에 전기적으로 연결되어 출력단자(Out)로 제1시프트레지스터(SR1)의 출력신호를 출력할 수 있다. 상기 제1시프트레지스터(SR1)의 출력신호는 초기구동신호를 일측으로 시프트한 신호로, 제1발광제어선(Em[1])으로 출력되는 제1발광제어신호가 된다. 상기 제1시프트레지스터(SR1)의 출력신호인 제1발광제어신호는 제2시프트레지스터(SR2)의 입력신호일수 있다.

- <146> 상기 제1낸드게이트(NAND1)는 초기구동선(FLM), 제1클럭선(SCLK1) 및 제1발광제어선(Em[1])과 전기적으로 연결되어 초기구동신호, 제1클럭신호 및 제1발광제어신호를 인가받아 제1주사선으로 제1주사신호를 출력할 수 있다.

- <147> 상기 제2시프트레지스터(SR2)는 입력단자(In)가 제1발광제어선(Em[1])과 전기적으로 연결되고, 제1클럭단자(clka)가 원시부클럭선(CLKB)에 전기적으로 연결되며, 제2클럭단자(clkb)가 원시클럭선(CLK)에 전기적으로 연결되어 출력단자(Out)로 제2시프트레지스터(SR2)의 출력신호를 출력할 수 있다. 상기 제2시프트레지스터(SR2)의 출력신호는 제1발광제어신호를 일측으로 시프트한 신호로, 제2발광제어선(Em[2])으로 출력되는 제2발광제어신호가 된다. 상기 제2시프트레지스터(SR2)의 출력신호인 제2발광제어신호는 제3시프트레지스터(SR3)의 입력신호일수 있다.

- <148> 상기 제2낸드게이트(NAND2)는 제1발광제어선(Em[1]), 제2클럭선(SCLK2) 및 제2발광제어선(Em[2])과 전기적으로 연결되어 제1발광제어신호, 제2클럭신호 및 제2발광제어신호를 인가받아 제2주사선으로 제2주사신호를 출력할 수 있다.

- <149> 상기 제3낸드게이트(NAND3)는 제1발광제어선(Em[1]), 제1클럭선(SCLK1) 및 제2발광제어선(Em[2])과 전기적으로 연결되어 제1발광제어신호, 제1클럭신호 및 제2발광제어신호를 인가받아 제3주사선으로 제3주사신호를 출력할 수 있다.

- <150> 상기 제4낸드게이트(NAND4)는 제2발광제어선(Em[2]), 제2클럭선(SCLK2) 및 제3발광제어선(Em[3])과 전기적으로 연결되어 제2발광제어신호, 제2클럭신호 및 제3발광제어신호를 인가받아 제4주사선으로 제4주사신호를 출력할 수 있다.

- <151> 상기 제5낸드게이트(NAND5) 내지 제n낸드게이트(NANDn)중 기수 번째 낸드게이트는 상기 제3낸드게이트(NAND3)와 동일하게 제1클럭선(SCLK1)과 두개의 발광제어선에 전기적으로 연결되어 주사선으로 주사신호를 출력할 수 있다. 여기서 두개의 발광제어선은, 기수 번째 낸드게이트를 제a낸드게이트라고 하면 제(a-1)/2발광제어선(Em[(a-1)/2])과 제(a+1)/2발광제어선(Em[(a+1)/2])이다. 그리고, 우수 번째 낸드게이트는 상기 제4낸드게이트(NAND4)와 동일하게 제2클럭선(SCLK2)과 두개의 발광제어선에 전기적으로 연결되어 주사선으로 주사신호를 출력할 수 있다.. 여기서 두개의 발광제어선은, 우수 번째 낸드게이트를 제b낸드게이트라고 하면 제(b/2)발광제어선(Em[b/2])과 제(b+2)/2발광제어선(Em[(b+2)/2])이다.

- <152> 상기 제1주사선(Scan[1]) 내지 제n주사선(Scan[n])은 유기 전계 발광 표시 패널(140, 도 1참조)와 전기적으로 연결되어 주사신호를 유기 전계 발광 표시 패널(140, 도 1참조)에 인가할 수 있다.

- <153> 상기 제3시프트레지스터(SR3) 내지 제n/2시프트레지스터(SRn/2)중 기수 번째 시프트레지스터는 상기 제1시프트레지스터(SR1)와 동일하게 제1클럭단자(clka)가 원시클럭선(CLK)에 전기적으로 연결되며, 제2클럭단자(clkb)가 원시부클럭선(CLKB)에 전기적으로 연결되어 출력단자(Out)로 출력신호를 출력할 수 있다.. 그리고, 우수 번째 시프트레지스터는 제2시프트레지스터(SR2)와 동일하게 제1클럭단자(clka)가 원시부클럭선(CLKB)에 전기적으로 연결되며, 제2클럭단자(clkb)가 원시클럭선(CLK)에 전기적으로 연결되어 출력단자(Out)로 출력신호를 출력할 수

있다. 이때, 시프트레지스터의 입력단자는 이전 시프트레지스터의 출력단자(Out)로 출력된 발광제어신호가 인가된다. 즉, 제3시프트레지스터(SR3) 내지 제n/2시프트레지스터(SRn/2)의 입력단자(In)에는 제2시프트레지스터(SR2) 내지 제n/2-1시프트레지스터(SRn/2-1)의 출력단자(Out)로 출력된 제2발광제어신호 내지 제n/2-1발광제어신호가 각각 인가될 수 있다.

<154> 상기 제1발광제어선(Em[1]) 내지 제n/2발광제어선(Em[n/2])은 유기 전계 발광 표시 패널(140, 도 1참조)와 전기적으로 연결되어 발광제어신호를 유기 전계 발광 표시 패널(140, 도 1참조)에 인가할 수 있다.

<155> 도 8을 참조하면 도7에 도시된 주사구동부의 타이밍 도가 도시되어 있다.

<156> 도 8에서 도시된 바와 같이, 상기 주사구동부의 타이밍 도는 제1구동기간(T1), 제2구동기간(T2) 및 제3구동기간(T3)을 포함할 수 있다. 그리고 제1구동기간(T1), 제2구동기간(T2) 및 제3구동기간(T3)은 제1서브구동기간, 지연기간 및 제2서브구동기간을 포함할 수 있다. 상기 제1서브구동기간, 지연기간 및 제2서브구동기간은 제1클럭선(SCLK1)의 제1클럭신호, 제2클럭선(SCLK2)의 제2클럭신호 및 발광제어선(Em[1], Em[2], …, Em[n/2])의 발광제어신호가 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 인가되어 주사선(Scan[1], Scan[2], …, Scan[n])으로 주사신호를 출력하는 구간을 나타낸다. 상기 제1클럭신호와 제2클럭신호는 위상이 반전되고 로우 레벨에서 소정부분 오버랩 된 신호이다. 이는 출력되는 주사신호 간에 소정의 시간 간격을 두도록 하며, 이는 클럭 스케이프(skew) 또는 지연(delay)에 대한 마진을 확보할 수 있게 한다.

<157> 상기 제1구동기간(T1)은 초기구동선(FLM)에서 하이레벨의 초기구동신호, 원시클럭선(CLK)에서 로우레벨의 원시클럭신호 및 원시부클럭선(CLKB)에서 하이레벨의 원시부클럭신호가 인가될 수 있다.

<158> 먼저, 제1시프트레지스터(SR1)는 입력단자에 하이레벨의 초기구동신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 원시부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 하이레벨의 초기구동신호와 동일한 하이레벨의 제1발광제어신호를 출력할 수 있다.

<159> 다음 제2시프트레지스터(SR2)는 입력단자에 하이레벨의 제1발광제어신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 원시클럭신호가 인가되므로, 출력단자는 이전구동기간의 출력신호와 동일한 로우레벨의 제2발광제어신호를 출력할 수 있다.

<160> 다음 제3시프트레지스터(SR3)는 입력단자에 로우레벨의 제2발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 로우레벨의 제2발광제어신호와 동일한 로우레벨의 제3발광제어신호를 출력할 수 있다.

<161> 마지막으로 제4시프트레지스터(SR4) 내지 제n/2시프트레지스터(n/2)중 우수 번째 레지스터는 제2시프트레지스터(SR2)와 동일하게 동작하여 로우레벨의 발광신호를 출력하고, 기수 번째 레지스터는 제3시프트레지스터(SR3)과 동일하게 동작하여 로우레벨의 발광신호를 출력할 수 있다.

<162> 상기 제1구동기간(T1)의 제1서브구동기간(T11)은 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 제1클럭선(SCLK1)에서 인가되는 로우레벨의 제1클럭신호와 제2클럭선(SCLK2)에서 인가되는 하이레벨의 제2클럭신호를 인가할 수 있다.

<163> 우선 제1낸드게이트(NAND1)는 로우레벨의 제1클럭신호, 하이레벨의 초기구동신호, 하이레벨의 제1발광제어신호가 인가되어, 제1주사선(Scan[1])으로 하이레벨의 제1주사신호를 출력할 수 있다.

<164> 다음 제2낸드게이트(NAND2)는 하이레벨의 제2클럭신호, 하이레벨의 제1발광제어신호, 로우레벨 제2발광제어신호가 인가되어, 제2주사선(Scan[2])으로 하이레벨의 제2주사신호를 출력할 수 있다.

<165> 마지막으로 제3낸드게이트(NAND3) 내지 제n낸드게이트(NANDn)에 전기적으로 연결된 제2발광제어선(Em[2]) 내지 제n/2발광제어선(Em[n/2])에서 로우레벨의 발광제어신호를 제3낸드게이트(NAND3) 내지 제n낸드게이트(NANDn)에 인가하므로 하이레벨의 제3주사신호 내지 제n주사신호를 출력할 수 있다.

<166> 상기 제1구동기간(T1)의 지연기간(D1)은 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 제1클럭선(SCLK1)에서 인가되는 로우레벨의 제1클럭신호와 제2클럭선(SCLK2)에서 인가되는 로우레벨의 제2클럭신호를 인가할 수 있다. 상기 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 전기적으로 연결된 제1클럭선(SCLK1)과 제2클럭선(SCLK2)에서 로우레벨의 제1클럭신호와 제2클럭신호를 상기 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 인가하므로 하이레벨의 제1주사신호 내지 제n주사신호를 출력할 수 있다.

<167> 상기 제1구동기간(T1)의 제2서브구동기간(T12)은 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 제1클럭선

(SCLK1)에서 인가되는 하이레벨의 제1클럭신호와 제2클럭선(SCLK2)에서 인가되는 로우레벨의 제2클럭신호를 인가할 수 있다.

<168> 우선 제1낸드게이트(NAND1)는 하이레벨의 제1클럭신호, 하이레벨의 초기구동신호, 하이레벨의 제1발광제어신호가 인가되어, 제1주사선(Scan[1])으로 로우레벨의 제1주사신호를 출력할 수 있다.

<169> 다음 제2낸드게이트(NAND2) 내지 제n낸드게이트(NANDn)에 전기적으로 연결된 제2발광제어선(Em[2]) 내지 제n/2발광제어선(Em[n/2])에서 로우레벨의 발광제어신호를 제2낸드게이트(NAND2) 내지 제n낸드게이트(NANDn)에 인가하므로 하이레벨의 제2주사신호 내지 제n주사신호를 출력할 수 있다.

<170> 상기 제2구동기간(T2)은 초기구동선(FLM)에서 로우레벨의 초기구동신호, 원시클럭선(CLK)에서 하이레벨의 원시클럭신호 및 원시부클럭선(CLKB)에서 로우레벨의 원시부클럭신호가 인가될 수 있다.

<171> 먼저, 제1시프트레지스터(SR1)는 입력단자에 로우레벨의 초기구동신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 원시부클럭신호가 인가되므로, 출력단자는 제1구동기간(T1)의 출력신호와 동일한 하이레벨의 제1발광제어신호를 출력할 수 있다.

<172> 다음 제2시프트레지스터(SR2)는 입력단자에 하이레벨의 제1발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 원시클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 하이레벨의 제1발광제어신호와 동일한 하이레벨의 제2발광제어신호를 출력할 수 있다.

<173> 다음 제3시프트레지스터(SR3)는 입력단자에 하이레벨의 제2발광제어신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 부클럭신호가 인가되므로, 출력단자는 제1구동기간(T1)의 출력신호와 동일한 로우레벨의 제3발광제어신호를 출력할 수 있다.

<174> 다음 제4시프트레지스터(SR2)는 입력단자에 로우레벨의 제3발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 원시클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 로우레벨의 제3발광제어신호와 동일한 로우레벨의 제4발광제어신호를 출력할 수 있다.

<175> 마지막으로 제5시프트레지스터(SR5) 내지 제n/2시프트레지스터(n/2)중 기수 번째 레지스터는 제3시프트레지스터(SR3)과 동일하게 동작하여 로우레벨의 발광신호를 출력하고, 우수 번째 레지스터는 제4시프트레지스터(SR4)와 동일하게 동작하여 로우레벨의 발광신호를 출력할 수 있다.

<176> 상기 제2구동기간(T2)의 제1서브구동기간(T21)은 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 제1클럭선(SCLK1)에서 인가되는 로우레벨의 제1클럭신호와 제2클럭선(SCLK2)에서 인가되는 하이레벨의 제2클럭신호를 인가할 수 있다.

<177> 우선 제1낸드게이트(NAND1)는 로우레벨의 제1클럭신호, 로우레벨의 초기구동신호, 하이레벨의 제1발광제어신호가 인가되어, 제1주사선(Scan[1])으로 하이레벨의 제1주사신호를 출력할 수 있다.

<178> 다음 제2낸드게이트(NAND2)는 하이레벨의 제2클럭신호, 하이레벨의 제1발광제어신호, 하이레벨의 제2발광제어신호가 인가되어, 제2주사선(Scan[2])으로 로우레벨의 제2주사신호를 출력할 수 있다.

<179> 다음 제3낸드게이트(NAND3)는 로우레벨의 제1클럭신호, 하이레벨의 제1발광제어신호, 하이레벨의 제2발광제어신호가 인가되어, 제3주사선(Scan[3])으로 하이레벨의 제3주사신호를 출력할 수 있다.

<180> 마지막으로 제4낸드게이트(NAND4) 내지 제n낸드게이트(NANDn)에 전기적으로 연결된 제3발광제어선(Em[3]) 내지 제n/2발광제어선(Em[n/2])에서 로우레벨의 발광제어신호를 제4낸드게이트(NAND4) 내지 제n낸드게이트(NANDn)에 인가하므로 하이레벨의 제4주사신호 내지 제n주사신호를 출력할 수 있다.

<181> 상기 제2구동기간(T2)의 지연기간(D2)은 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 제1클럭선(SCLK1)에서 인가되는 로우레벨의 제1클럭신호와 제2클럭선(SCLK2)에서 인가되는 로우레벨의 제2클럭신호를 인가할 수 있다. 상기 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 전기적으로 연결된 제1클럭선(SCLK1)과 제2클럭선(SCLK2)에서 로우레벨의 제1클럭신호와 제2클럭신호를 상기 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 인가하므로 하이레벨의 주사신호를 출력할 수 있다.

<182> 상기 제2구동기간(T2)의 제2서브구동기간(T22)은 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 제1클럭선(SCLK1)에서 인가되는 하이레벨의 제1클럭신호와 제2클럭선(SCLK2)에서 인가되는 로우레벨의 제2클럭신호를 인가할 수 있다.

- <183> 우선 제1낸드게이트(NAND1)는 하이레벨의 제1클럭신호, 로우레벨의 초기구동신호, 하이레벨의 제1발광제어신호가 인가되어, 제1주사선(Scan[1])으로 하이레벨의 제1주사신호를 출력할 수 있다.

- <184> 다음 제2낸드게이트(NAND2)는 로우레벨의 제2클럭신호, 하이레벨의 제1발광제어신호, 하이레벨의 제2발광제어신호가 인가되어, 제2주사선(Scan[2])으로 하이레벨의 제2주사신호를 출력할 수 있다.

- <185> 다음 제3낸드게이트(NAND3)는 하이레벨의 제1클럭신호, 하이레벨의 제1발광제어신호, 하이레벨의 제2발광제어신호가 인가되어, 제3주사선(Scan[3])으로 로우레벨의 제3주사신호를 출력할 수 있다.

- <186> 마지막으로 제4낸드게이트(NAND4) 내지 제n낸드게이트(NANDn)에 전기적으로 연결된 제3발광제어선(Em[3]) 내지 제n/2발광제어선(Em[n/2])의 발광제어신호가 로우레벨의 신호를 제4낸드게이트(NAND4) 내지 제n낸드게이트(NANDn)에 인가하므로 하이레벨의 제4주사신호 내지 제n주사신호를 출력할 수 있다.

- <187> 상기 제3구동기간(T3)은 초기구동선(FLM)에서 로우레벨의 초기구동신호, 원시클럭선(CLK)에서 로우레벨의 원시클럭신호 및 원시부클럭선(CLKB)에서 하이레벨의 원시부클럭신호가 인가될 수 있다.

- <188> 먼저, 제1시프트레지스터(SR1)는 입력단자에 로우레벨의 초기구동신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 원시부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 로우레벨의 초기구동신호와 동일한 로우레벨의 제1발광제어신호를 출력할 수 있다.

- <189> 다음 제2시프트레지스터(SR2)는 입력단자에 로우레벨의 제1발광제어신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 원시클럭신호가 인가되므로, 출력단자는 제2구동기간(T2)의 출력신호와 동일한 하이레벨의 제2발광제어신호를 출력할 수 있다.

- <190> 다음 제3시프트레지스터(SR3)는 입력단자에 하이레벨의 제2발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 하이레벨의 제2발광제어신호와 동일한 하이레벨의 제3발광제어신호를 출력할 수 있다.

- <191> 다음 제4시프트레지스터(SR4)는 입력단자에 하이레벨의 제3발광제어신호가 인가되고, 제1클럭단자(clka)에 하이레벨의 원시부클럭신호가 인가되며, 제2클럭단자(clkb)에 로우레벨의 원시클럭신호가 인가되므로, 출력단자는 제2구동기간(T2)의 출력신호와 동일한 로우레벨의 제4발광제어신호를 출력할 수 있다.

- <192> 다음 제5시프트레지스터(SR5)는 입력단자에 로우레벨의 제4발광제어신호가 인가되고, 제1클럭단자(clka)에 로우레벨의 원시클럭신호가 인가되며, 제2클럭단자(clkb)에 하이레벨의 부클럭신호가 인가되므로, 출력단자는 입력단자로 인가된 로우레벨의 제4발광제어신호와 동일한 로우레벨의 제5발광제어신호를 출력할 수 있다.

- <193> 마지막으로 제6시프트레지스터(SR6) 내지 제n/2시프트레지스터(n/2)중 우수 번째 레지스터는 제4시프트레지스터(SR4)와 동일하게 동작하여 로우레벨의 발광신호를 출력하고, 기수 번째 레지스터는 제5시프트레지스터(SR5)과 동일하게 동작하여 로우레벨의 발광신호를 출력할 수 있다.

- <194> 상기 제3구동기간(T3)의 제1서브구동기간(T31)은 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 제1클럭선(SCLK1)에서 인가되는 로우레벨의 제1클럭신호와 제2클럭선(SCLK2)에서 인가되는 하이레벨의 제2클럭신호를 인가할 수 있다.

- <195> 우선, 제1낸드게이트(NAND1) 내지 제3낸드게이트(NAND3)에 전기적으로 연결된 초기구동선(FLM)과 제1발광제어선(Em[1])에서 로우레벨의 초기구동신호와 제1발광제어신호를 제1낸드게이트(NAND1) 내지 제3낸드게이트(NAND3)에 인가하므로 하이레벨의 제1주사신호 내지 제3주사신호를 출력할 수 있다.

- <196> 다음 제4낸드게이트(NAND4)는 하이레벨의 제2클럭신호, 하이레벨의 제2발광제어신호, 하이레벨의 제3발광제어신호가 인가되어, 제4주사선(Scan[4])으로 로우레벨의 제4주사신호를 출력할 수 있다.

- <197> 다음 제5낸드게이트(NAND5)는 로우레벨의 제1클럭신호, 하이레벨의 제2발광제어신호, 하이레벨의 제3발광제어신호가 인가되어, 제5주사선(Scan[5])으로 하이레벨의 제5주사신호를 출력할 수 있다.

- <198> 마지막으로 제6낸드게이트(NAND6) 내지 제n낸드게이트(NANDn)에 전기적으로 연결된 제4발광제어선(Em[4]) 내지 제n/2발광제어선(Em[n/2])의 발광제어신호가 로우레벨의 신호를 제6낸드게이트(NAND6) 내지 제n낸드게이트(NANDn)에 인가하므로 하이레벨의 제6주사신호 내지 제n주사신호를 출력할 수 있다.

- <199> 상기 제3구동기간(T3)의 지연기간(D3)은 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 제1클럭선(SCLK1)에서 인가되는 로우레벨의 제1클럭신호와 제2클럭선(SCLK2)에서 인가되는 로우레벨의 제2클럭신호를 인가할 수

있다. 상기 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 전기적으로 연결된 제1클럭선(SCLK1)과 제2클럭선(SCLK2)에서 로우레벨의 제1클럭신호와 제2클럭신호를 상기 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 인가하므로 하이레벨의 주사신호를 출력할 수 있다.

<200> 상기 제3구동기간(T3)의 제2서브구동기간(T23)은 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 제1클럭선(SCLK1)에서 인가되는 하이레벨의 제1클럭신호와 제2클럭선(SCLK2)에서 인가되는 로우레벨의 제2클럭신호를 인가할 수 있다.

<201> 우선, 제1낸드게이트(NAND1) 내지 제3낸드게이트(NAND3)에 전기적으로 연결된 초기구동선(FLM)과 제1발광제어선(Em[1])에서 로우레벨의 초기구동신호와 발광제어신호를 제1낸드게이트(NAND1) 내지 제3낸드게이트(NAND3)에 인가하므로 하이레벨의 제1주사신호 내지 제3주사신호를 출력할 수 있다.

<202> 다음 제4낸드게이트(NAND4)는 로우레벨의 제2클럭신호, 하이레벨의 제2발광제어신호, 하이레벨의 제3발광제어신호가 인가되어, 제4주사선(Scan[4])으로 하이레벨의 제5주사신호를 출력할 수 있다.

<203> 다음 제5낸드게이트(NAND5)는 하이레벨의 제1클럭신호, 하이레벨의 제2발광제어신호, 하이레벨의 제3발광제어신호가 인가되어, 제5주사선(Scan[5])으로 로우레벨의 제5주사신호를 출력할 수 있다.

<204> 마지막으로 제6낸드게이트(NAND6) 내지 제n낸드게이트(NANDn)에 전기적으로 연결된 제4발광제어선(Em[4]) 내지 제n/2발광제어선(Em[n/2])의 발광제어신호가 로우레벨의 신호를 제6낸드게이트(NAND6) 내지 제n낸드게이트(NANDn)에 인가하므로 하이레벨의 제6주사신호 내지 제n주사신호를 출력할 수 있다.

<205> 상기 제1시프트레지스터(SR1) 내지 상기 제n/2시프트레지스터(n/2)는 제1구동기간(T1) 내지 제3구동기간(T3)과 이전 시프트레지스터에서 인가받은 입력신호와 이전 구동기간의 출력신호에 의해서 하이레벨의 제1발광제어신호 내지 제n/2발광제어신호를 순차적으로 출력할 수 있다.

<206> 상기 제1낸드게이트(NAND1) 내지 상기 제n낸드게이트(NANDn)는 제1구동기간(T1)의 제1서브구동기간(T11)과 제2서브구동기간(T12) 내지 제3구동기간(T3)의 제1서브구동기간(T31)과 제2서브구동기간(T32)에서 제1클럭신호 내지 제2클럭신호, 초기구동신호, 제1발광제어신호 내지 제n/2발광제어신호를 인가받아 로우레벨의 제1주사신호 내지 제n주사신호를 순차적으로 출력할 수 있다. 상기 제1낸드게이트(NAND1) 내지 상기 제n낸드게이트(NANDn)는 초기구동신호와 제1발광제어신호 내지 제n발광제어신호가 모두 하이레벨이고, 제1클럭선에서 하이레벨의 제1클럭신호를 인가하고, 제2클럭선에서 로우레벨의 제2클럭신호를 인가하면, 제1클럭선과 전기적으로 연결된 기수 번째 낸드게이트의 출력신호인 기수 번째 주사신호는 모두 로우레벨의 주사신호가 출력된다. 그리고, 제2클럭선과 전기적으로 연결된 우수 번째 낸드게이트의 출력신호인 우수 번째 주사신호는 모두 하이레벨의 주사신호가 출력된다. 상기 제1낸드게이트(NAND1) 내지 상기 제n낸드게이트(NANDn)는 초기구동신호와 제1발광제어신호 내지 제n발광제어신호가 모두 하이레벨이고, 제1클럭선에서 로우레벨의 제1클럭신호를 인가하고, 제2클럭선에서 하이레벨의 제2클럭신호를 인가하면, 제1클럭선과 전기적으로 연결된 기수 번째 낸드게이트의 출력신호인 기수 번째 주사신호는 모두 하이레벨의 주사신호가 출력된다. 그리고, 제2클럭선과 전기적으로 연결된 우수 번째 낸드게이트의 출력신호인 우수 번째 주사신호는 모두 로우레벨의 주사신호가 출력된다. 즉, 상기 제1클럭신호와 제2클럭신호를 이용하여 기수번째, 우수번째 주사신호를 출력할 수 있다.

&lt;207&gt;

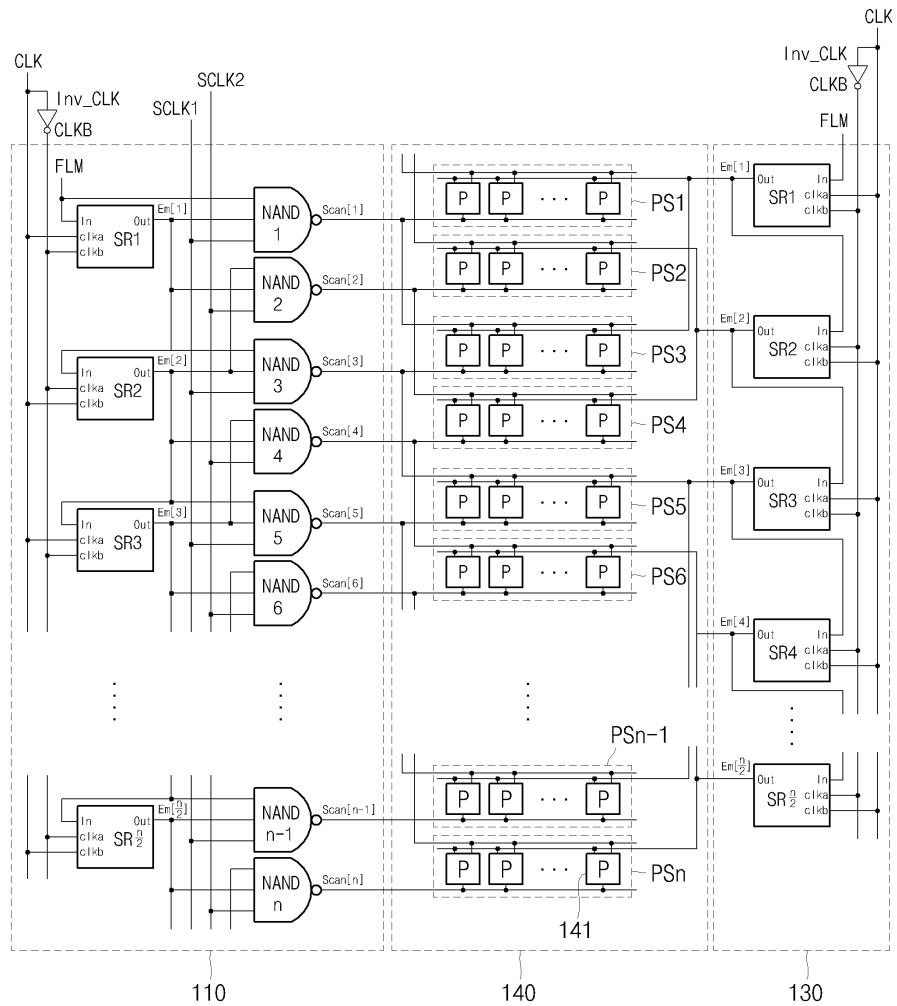

<208> 도 9를 참조하면 본 발명의 일실시예에 따른 유기 전계 발광 표시 장치를 도시한 블록도가 도시되어 있다.

<209> 도 9에 도시된 바와 같이 유기 전계 발광 표시 장치는 주사구동부(110), 발광제어구동부(130) 및 유기 전계 발광 표시 패널(140)을 포함한다.

<210> 상기 주사구동부(110)는 도 7과 도 8에서 설명한 것과 같이 동작하여 제1주사선(Scan[1]) 내지 제n주사선(Scan[n])으로 제1주사신호 내지 제n주사신호를 출력한다. 상기 제1주사선(Scan[1]) 내지 제n주사선(Scan[n])은 유기 전계 발광 표시 패널(140)과 전기적으로 연결되어 제1주사신호 내지 제n주사신호를 유기 전계 발광 표시 패널(140)에 인가한다. 이때, 도 7의 유기 전계 발광 표시 장치의 주사구동부는 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 초기구동신호와 제1발광제어신호 내지 제n발광제어신호가 모두 하이레벨이고, 제1클럭선에서 하이레벨의 제1클럭신호를 인가하고, 제2클럭선에서 로우레벨의 제2클럭신호를 인가하면, 제1클럭선과 전기적으로 연결된 기수 번째 낸드게이트의 출력신호인 기수 번째 주사신호는 모두 로우레벨의 주사신호가 출력된다. 그리고, 제2클럭선과 전기적으로 연결된 우수 번째 낸드게이트의 출력신호인 우수 번째 주사신호는 모두 하이레벨의 주사신호가 출력된다. 상기 제1낸드게이트(NAND1) 내지 상기 제n낸드게이트(NANDn)는 초기구동신호와

제1발광제어신호 내지 제n발광제어신호가 모두 하이레벨이고, 제1클럭선에서 로우레벨의 제1클럭신호를 인가하고, 제2클럭선에서 하이레벨의 제2클럭신호를 인가하면, 제1클럭선과 전기적으로 연결된 기수 번째 낸드게이트의 출력신호인 기수 번째 주사신호는 모두 하이레벨의 주사신호가 출력된다. 그리고, 제2클럭선과 전기적으로 연결된 우수 번째 낸드게이트의 출력신호인 우수 번째 주사신호는 모두 로우의 주사신호가 출력된다. 즉, 제1클럭선(SCLK1)과 제2클럭선(SCLK2)에 인가되는 제1클럭신호와 제2클럭신호에 따라 기수 번째와 우수 번째 주사신호를 출력할 수 있다.

<211> 상기 발광제어구동부(130)는 도 5과 도 6에서 설명한 것과 같이 동작하여 제1발광제어선(Em[1]) 내지 제n/2발광제어선(Em[n/2])으로 제1발광제어신호 내지 제n/2발광제어신호를 출력한다. 상기 제1발광제어선(Em[1]) 내지 제n/2발광제어선(Em[n/2])은 유기 전계 발광 표시 패널(140)과 전기적으로 연결되어 제1발광제어신호 내지 제n/2발광제어신호를 유기 전계 발광 표시 패널(140)에 인가한다. 상기 발광제어선(Em[1], Em[2], …, Em[n/2])은 기수 번째 화소부에는 기수 번째 발광제어선을 우수 번째 화소부에는 우수 번째 발광제어선을 전기적으로 연결한다. 상기 기수 번째 발광제어선은 상기 기수 번째 화소부에 기수 번째 주사신호가 인가되어 데이터 신호를 유기 전계 발광 소자(OLED)로 전달 할 때, 기수 번째 발광제어신호를 인가하여, 기수 번째 화소부에 발광제어신호를 동시에 공급하여 기수 번째 유기 전계 발광 소자(OLED)가 동시에 발광하도록 한다.

<212> 상기 유기 전계 발광 표시 패널(140)은 제1화소부(PS1) 내지 제n화소부(PSn)를 포함한다.

<213> 상기 제1화소부(PS1)은 제-1주사선(Scan[-1]), 제1주사선(Scan[1]) 및 제1발광제어선(Em[1])과 전기적으로 연결된다. 상기 제2화소부(PS2)은 제0주사선(Scan[0]), 제2주사선(Scan[2]) 및 제2발광제어선(Em[2])과 전기적으로 연결된다. 상기 제3화소부(PS3)은 제1주사선(Scan[1]), 제3주사선(Scan[3]) 및 제1발광제어선(Em[1])과 전기적으로 연결된다. 상기 제4화소부(PS4)은 제2주사선(Scan[2]), 제4주사선(Scan[4]) 및 제2발광제어선(Em[2])과 전기적으로 연결된다. 상기 제5화소부(PS5)은 제3주사선(Scan[3]), 제5주사선(Scan[5]) 및 제3발광제어선(Em[3])과 전기적으로 연결된다. 상기 제6화소부(PS6)는 제4주사선(Scan[4]), 제6주사선(Scan[6]) 및 제4발광제어선(Em[4])과 전기적으로 연결된다. 이와 같이 화소부는 제n-2주사선(Scan[n-2])과 제n주사선(Scan[n])과 전기적으로 연결되어 제n-2주사신호와 제n주사신호를 인가받아 동작하게 된다. 즉, 우수 번째 화소부에는 우수 번째 주사선이 연결되고, 기수 번째 화소부는 기수 번째 주사선이 전기적으로 연결된다. 여기서 제-1주사선(Scan[-1])과 제0주사선(Scan[0])은 데드스페이스(Dead Space)로 삽입되어 사용자에게 보이지 않는 패널의 주사선으로 제-1주사선(Scan[-1])과 제0주사선(Scan[0])으로 표현하였다. 그리고 우수 번째 화소부에는 우수 번째 발광제어선이 연결되고, 기수 번째 화소부는 기수 번째 발광제어선이 전기적으로 연결된다.

<214> 이때, 주사구동부(110)의 제1낸드게이트(NAND1) 내지 제n낸드게이트(NANDn)에 초기구동신호와 제1발광제어신호 내지 제n발광제어신호가 모두 하이 레벨이고, 제1클럭선(SCLK1)에서 하이레벨의 제1클럭신호를 인가하고, 제2클럭선에서 로우 레벨의 제2클럭신호를 인가하면, 제1클럭선(SCLK1)과 전기적으로 연결된 기수 번째 낸드게이트의 출력신호인 기수 번째 주사신호는 모두 로우레벨의 주사신호가 출력된다. 그리고, 제2클럭선(SCLK2)과 전기적으로 연결된 우수 번째 낸드게이트의 출력신호인 우수 번째 주사신호는 모두 하이레벨의 주사신호가 출력된다. 상기 제1낸드게이트(NAND1) 내지 상기 제n낸드게이트(NANDn)는 초기구동신호와 제1발광제어신호 내지 제n발광제어신호가 모두 하이레벨이고, 제1클럭선(SCLK1)에서 로우레벨의 제1클럭신호를 인가하고, 제2클럭선(SCLK2)에서 하이레벨의 제2클럭신호를 인가하면, 제1클럭선(SCLK1)과 전기적으로 연결된 기수 번째 낸드게이트의 출력신호인 기수 번째 주사신호는 모두 하이레벨의 주사신호가 출력된다. 그리고, 제2클럭선(SCLK2)과 전기적으로 연결된 우수 번째 낸드게이트의 출력신호인 우수 번째 주사신호는 모두 로우의 주사신호가 출력된다.

<215> 상기 제1클럭선(SCLK1)에 하이레벨의 제1클럭신호가 인가되고, 제2클럭선(SCLK2)에 로우레벨의 제2클럭신호가 인가될 때, 기수 번째 주사신호는 모두 로우 레벨의 주사신호가 출력되므로, 기수 번째 화소 회로는 로우 레벨의 기수 번째 주사신호를 인가받아 동작하게 되고, 유기 전계 발광 소자(OLED)는 데이터신호를 전달받아 발광하게 된다. 이때, 우수 번째 화소 회로는 하이 레벨의 우수 번째 주사신호를 인가받아 유기 전계 발광 소자(OLED)로 전달되어야 하는 데이터 신호가 차단된다.

<216> 상기 제1클럭선(SCLK1)에 로우레벨의 제1클럭신호가 인가되고, 제2클럭선(SCLK2)에 하이레벨의 제2클럭신호가 인가될 때, 우수 번째 주사신호는 모두 로우 레벨의 주사신호가 출력되므로, 우수 번째 화소 회로는 로우 레벨의 우수 번째 주사신호를 인가받아 동작하게 되고, 유기 전계 발광 소자(OLED)는 데이터신호를 전달받아 발광하게 된다. 이때, 기수 번째 화소 회로는 하이 레벨의 기수 번째 주사신호를 인가받아 유기 전계 발광 소자(OLED)로 전달되어야 하는 데이터 신호가 차단된다.

<217> 즉, 상기 제1클럭선(SCLK1)과 제2클럭선(SCLK2)을 기수번째 낸드게이트와 우수번째 낸드게이트에 각각 전기적으

로 연결하고, 상기 기수번째 낸드케이트와 우수번째 낸드케이트는 각각 기수번째 화소부와 우수번째 화소부와 전기적으로 연결된다. 이때, 제1클럭선(SCLK1)에 로우레벨의 제1클럭신호를 인가하고, 제2클럭선(SCLK2)에 하이레벨의 제2클럭신호를 인가하여 기수 번째 화소부의 유기 전계 발광 소자(OLED)만 터온 한다. 그리고 제1클럭선(SCLK1)에 하이레벨의 제1클럭신호를 인가하고, 제2클럭선(SCLK2)에 로우레벨의 제2클럭신호를 인가하여 우수 번째 화소부의 유기 전계 발광 소자(OLED)만 터온 한다. 상기와 같이 우수 번째 화소부의 유기 전계 발광 소자(OLED)만 발광해야 하는데 기수 번째 화소부의 유기 전계 발광 소자(OLED)가 발광을 할 경우, 기수 번째 화소부의 유기 전계 발광 소자(OLED)만 발광해야 하는데 우수 번째 화소부의 유기 전계 발광 소자(OLED)가 발광을 할 경우에 세로 방향으로 쇼트가 발생한 것을 알 수 있다.

<218> 예를 들어 제1화소부(PS1)와 제2화소부(PS2)의 m번째 화소회로(141, Pixel)이 쇼트가 되었다고 하면, 제1클럭선(SCLK1)에 로우레벨의 제1클럭신호를 인가하고, 제2클럭선(SCLK2)에 하이레벨의 제2클럭신호를 인가 했을 때 기수 번째 화소부의 유기 전계 발광 소자(OLED)만 발광해야 하는데, 제2화소부(PS2)의 m번째 화소회로(141)의 유기 전계 발광 소자(OLED)도 발광하게 되므로 세로 방향으로 쇼트가 된 것을 발견 할 수 있다.

<219> 이러한 세로방향으로 발생한 쇼트의 검출은 종래에는 모듈공정에서 일정한 패턴을 유기 전계 발광 표시 패널에 인가하여 검출 하므로 쇼트가 발생한 불량 패널에 모듈 공정 작업 비용이 추가적으로 발생하였다. 그러나 본 발명의 세로방향으로 발생한 쇼트의 검출은 모듈 공정 이전에 패널에 클럭신호를 인가하여 불량을 검출할 수 있으므로 불량 패널의 모듈 공정 작업 비용을 절감할 수 있다. 또한 모듈 공정에서 전수 검사를 하지 않을 경우 세로 방향 쇼트가 불량으로 검출 되지 않아 최종 이용 고객이 불량을 발견하게 되어 상품의 신뢰성이 저하되는 것을 방지 할 수 있다.

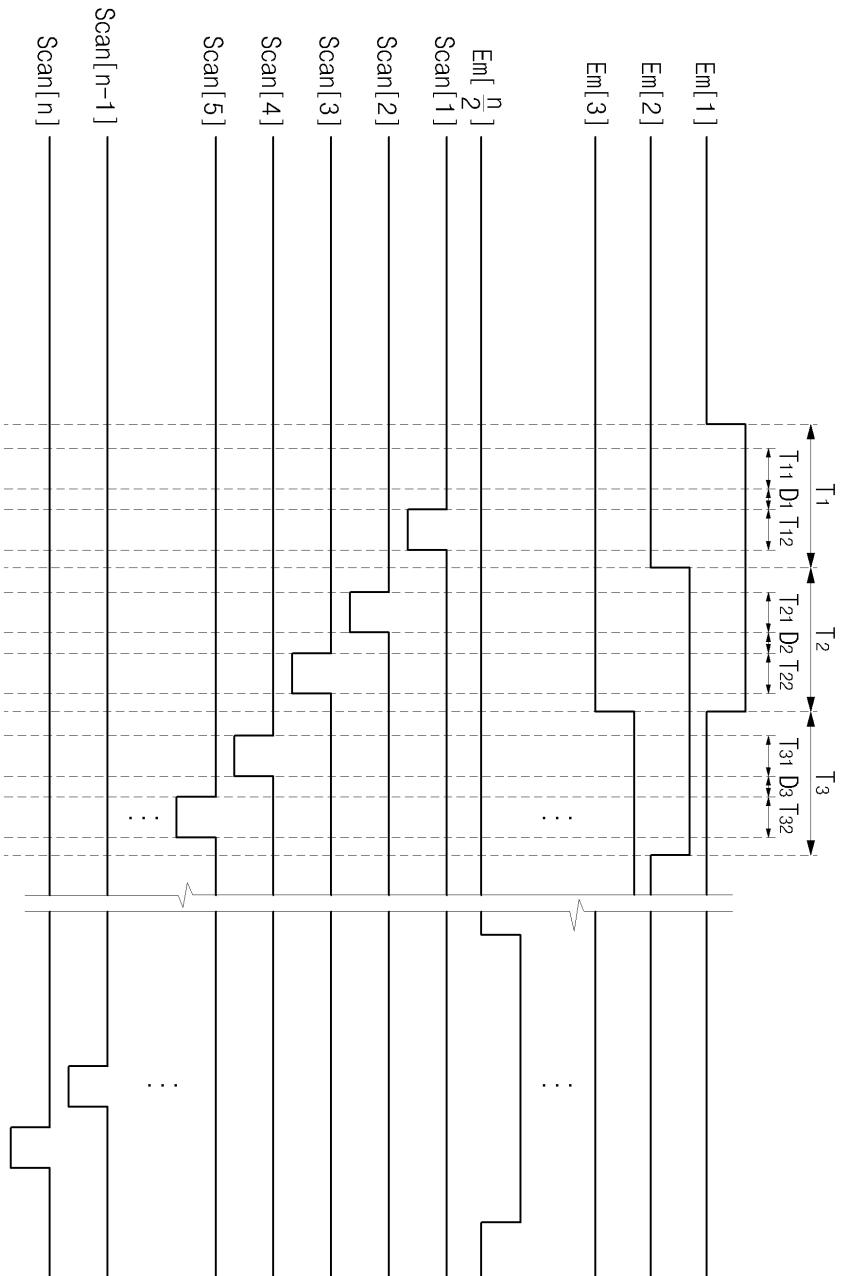

<220> 도 10을 참조하면 도 9에 도시된 유기 전계 발광 표시 장치의 타이밍 도가 도시되어 있다.

<221> 도 10에 도시된 바와 같이 유기 전계 발광 표시 장치의 타이밍 도는 제1구동기간(T1), 제2구동기간(T2) 및 제3구동기간(T3)을 포함한다. 그리고 상기 제1구동기간(T1) 내지 제3구동기간(T3)은 제1서브구동기간, 지연기간, 제2서브구동기간을 포함한다.

<222> 우선 제1구동기간(T1)은 유기 전계 발광 표시 패널(140)에 하이레벨의 제1발광제어신호가 인가되고, 로우레벨의 제2발광제어신호 내지 제n발광제어신호가 인가된다.

<223> 상기 제1구동기간(T1)의 제1서브구동기간(T11)은 상기 유기 전계 발광 표시 패널(140)에 하이레벨의 제1주사신호 내지 제n주사신호가 인가된다.

<224> 상기 제1구동기간(T1)의 지연기간(D1)은 인가되는 주사신호 간에 소정의 시간 간격을 두도록 하며, 이는 클럭스퀴(skew) 또는 지연(delay)에 대한 마진을 확보할 수 있게 하는 기간이다.

<225> 상기 제1구동기간(T1)의 제2서브구동기간(T12)은 상기 유기 전계 발광 표시 패널(140)에 로우레벨의 제1주사신호가 인가되고, 하이레벨의 제2주사신호 내지 제n주사신호가 인가된다. 이때, 제1화소부(PS1)의 화소회로는 로우레벨의 제1주사신호를 전달받아 제1스위치소자(S1)과 제5스위칭소자(S5)가 터온된다. 제1스위칭소자(S1)이 터온 되어 데이터신호를 구동트랜지스터에 전달하고, 제5스위칭소자(S5)가 터온되어 구동트랜지스터를 다이오드 구조로 연결시켜서 구동트랜지스터의 문턱전압을 보상한다. 상기 제1화소부(PS1)의 화소회로는 제1용량성소자(C1)에 제1전원전압(ELVDD)과 구동트랜지스터(M1)의 제어전극 사이에 전압차를 저장한다. 그리고 제3화소부(PS3)의 화소회로는 두 번째 이전주사신호인 로우레벨의 제1주사신호를 인가받아 제1용량성소자(C1)과 제2용량성소자(C2)에 저장되어 있던 전압을 초기화 시킨다.

<226> 다음 제2구동기간(T2)은 유기 전계 발광 표시 패널(140)에 하이레벨의 제1발광제어신호와 제2발광제어신호가 인가되고, 로우레벨의 제3발광제어신호 내지 제n발광제어신호가 인가된다.

<227> 상기 제2구동기간(T2)의 제1서브구동기간(T21)은 상기 유기 전계 발광 표시 패널(140)에 로우레벨의 제2주사신호가 인가되고, 하이레벨의 제1주사신호와 제3주사신호 내지 제n주사신호가 인가된다. 이때, 제2화소부(PS2)의 화소회로는 로우레벨의 제2주사신호를 전달받아 제1스위치소자(S1)과 제5스위칭소자(S5)가 터온된다. 제1스위칭소자(S1)이 터온 되어 데이터신호를 구동트랜지스터에 전달하고, 제5스위칭소자(S5)가 터온되어 구동트랜지스터를 다이오드 구조로 연결시켜서 구동트랜지스터의 문턱전압을 보상한다. 상기 제2화소부(PS2)의 화소회로는 제1용량성소자(C1)에 제1전원전압(ELVDD)과 구동트랜지스터(M1)의 제어전극 사이에 전압차를 저장한다. 그리고 제4화소부(PS4)의 화소회로는 두 번째 이전주사신호인 로우레벨의 제2주사신호를 인가받아 제1용량성소자(C1)과 제2용량성소자(C2)에 저장되어 있던 전압을 초기화 시킨다.

- <228> 상기 제2구동기간(T2)의 지연기간(D1)은 인가되는 주사신호 간에 소정의 시간 간격을 두도록 하며, 이는 클럭 스큐(skew) 또는 지연(delay)에 대한 마진을 확보할 수 있게 하는 기간이다.

- <229> 상기 제2구동기간(T2)의 제2서브구동기간(T22)은 상기 유기 전계 발광 표시 패널(140)에 로우레벨의 제3주사신호가 인가되고, 하이레벨의 제1주사신호와 제2주사신호 및 제4주사신호 내지 제n주사신호가 인가된다. 이때, 제3화소부(PS3)의 화소회로는 로우레벨의 제3주사신호를 전달받아 제1스위치소자(S1)과 제5스위치소자(S5)가 터온된다. 제1스위치소자(S1)이 터온 되어 데이터신호를 구동트랜지스터에 전달하고, 제5스위치소자(S5)가 터온되어 구동트랜지스터를 다이오드 구조로 연결시켜서 구동트랜지스터의 문턱전압을 보상한다. 상기 제3화소부(PS3)의 화소회로는 제1용량성소자(C1)에 제1전원전압(ELVDD)과 구동트랜지스터(M1)의 제어전극 사이에 전압차를 저장한다. 그리고 제5화소부(PS5)의 화소회로는 두 번째 이전주사신호인 로우레벨의 제3주사신호를 인가받아 제1용량성소자(C1)과 제2용량성소자(C2)에 저장되어 있던 전압을 초기화 시킨다.

- <230> 마지막으로 제3구동기간(T3)은 유기 전계 발광 표시 패널(140)에 하이레벨의 제2발광제어신호와 제3발광제어신호가 인가되고, 로우레벨의 제1발광제어신호와 제3발광제어신호 내지 제n발광제어신호가 인가된다. 상기 제1화소부(PS1)의 화소회로는 로우레벨의 제1발광제어신호가 인가되어 제2스위치소자(S2)와 제3스위치소자(S3)가 터온된다. 상기 제2스위치소자(S2)가 터온되어 제1전원전압(ELVDD)을 상기 구동트랜지스터(M1)에 전달하고, 상기 제3스위치소자(S3)가 터온되어 유기 전계 발광 소자(OLED)에 구동전류를 전달하여 제1화소부(PS1)의 유기 전계 발광 소자(OLED)는 발광하게 된다.

- <231> 상기 제3구동기간(T3)의 제1서브구동기간(T31)은 상기 유기 전계 발광 표시 패널(140)에 로우레벨의 제4주사신호가 인가되고, 하이레벨의 제1주사신호 내지 제3주사신호와 제5주사신호 내지 제n주사신호가 인가된다. 이때, 제4화소부(PS4)의 화소회로는 로우레벨의 제4주사신호를 전달받아 제1스위치소자(S1)과 제5스위치소자(S5)가 터온된다. 제1스위치소자(S1)이 터온 되어 데이터신호를 구동트랜지스터에 전달하고, 제5스위치소자(S5)가 터온되어 구동트랜지스터를 다이오드 구조로 연결시켜서 구동트랜지스터의 문턱전압을 보상한다. 상기 제4화소부(PS4)의 화소회로는 제1용량성소자(C1)에 제1전원전압(ELVDD)과 구동트랜지스터(M1)의 제어전극 사이에 전압차를 저장한다. 그리고 제6화소부(PS6)의 화소회로는 두 번째 이전주사신호인 로우레벨의 제4주사신호를 인가받아 제1용량성소자(C1)과 제2용량성소자(C2)에 저장되어 있던 전압을 초기화 시킨다.

- <232> 상기 제2구동기간(T2)의 지연기간(D1)은 인가되는 주사신호 간에 소정의 시간 간격을 두도록 하며, 이는 클럭 스큐(skew) 또는 지연(delay)에 대한 마진을 확보할 수 있게 하는 기간이다.

- <233> 상기 제3구동기간(T3)의 제2서브구동기간(T32)은 상기 유기 전계 발광 표시 패널(140)에 로우레벨의 제5주사신호가 인가되고, 하이레벨의 제1주사신호 내지 제4주사신호와 제6주사신호 내지 제n주사신호가 인가된다. 이때, 제5화소부(PS5)의 화소회로는 로우레벨의 제5주사신호를 전달받아 제1스위치소자(S1)과 제5스위치소자(S5)가 터온된다. 제1스위치소자(S1)이 터온 되어 데이터신호를 구동트랜지스터에 전달하고, 제5스위치소자(S5)가 터온되어 구동트랜지스터를 다이오드 구조로 연결시켜서 구동트랜지스터의 문턱전압을 보상한다. 상기 제5화소부(PS5)의 화소회로는 제1용량성소자(C1)에 제1전원전압(ELVDD)과 구동트랜지스터(M1)의 제어전극 사이에 전압차를 저장한다. 그리고 제7화소부(PS7)의 화소회로는 두 번째 이전주사신호인 로우레벨의 제5주사신호를 인가받아 제1용량성소자(C1)과 제2용량성소자(C2)에 저장되어 있던 전압을 초기화 시킨다.

- <234> 상기와 같은 방법으로 제1화소부(PS1) 내지 제n화소부(PSn)은 순차적으로 동작하여 유기 전계 발광 소자(OLED)는 발광하게 된다.

### 발명의 효과

- <235> 상술한 바와 같이, 본 발명에 의한 유기 전계 발광 표시 장치는 유기 전계 발광 표시 패널의 픽셀 세로 쇼트 불량을 사전 검출 하여 모듈 공정 비용을 절감하고, 신뢰성이 높은 효과가 있다.

- <236> 이상에서 설명한 것은 본 발명에 의한 유기 전계 발광 표시 장치를 실시하기 위한 하나의 실시예에 불과한 것으로서, 본 발명은 상기한 실시예에 한정되지 않고, 이하의 특허청구범위에서 청구하는 바와 같이 본 발명의 요지를 벗어남이 없이 당해 발명이 속하는 분야에서 통상의 지식을 가진 자라면 누구든지 다양한 변경 실시가 가능한 범위까지 본 발명의 기술적 정신이 있다고 할 것이다.

### 도면의 간단한 설명

- <1> 도 1은 본 발명에 따른 유기 전계 발광 표시 장치를 개략적으로 도시한 블록도이다.

- <2> 도 2는 본 발명에 따른 유기 전계 발광 표시 장치의 화소 회로를 도시한 회로도이다.

- <3> 도 3은 본 발명에 따른 유기 전계 발광 표시 장치의 주사구동부와 발광제어구동부에서 시프트 레지스터의 블록도이다.

- <4> 도 4는 도 3에 도시된 시프트 레지스터의 회로도이다.

- <5> 도 5는 본 발명에 따른 유기 전계 발광 표시 장치의 발광 제어 구동 부를 도시한 블록도이다.

- <6> 도 6은 도 5에 도시된 발광제어구동부의 타이밍 도이다.

- <7> 도 7은 본 발명에 따른 유기 전계 발광 표시 장치의 주사구동부를 도시한 블록도이다.

- <8> 도 8은 도 7에 도시된 주사구동부의 타이밍 도이다.

- <9> 도 9는 본 발명의 일실시예에 따른 유기 전계 발광 표시 장치를 도시한 블록도이다.

- <10> 도 10은 도 9에 도시된 유기 전계 발광 표시 장치의 타이밍 도이다.

- <11> < 도면의 주요 부분에 대한 부호의 설명 >

- |      |                    |                     |

|------|--------------------|---------------------|

| <12> | 110; 주사구동부         | 120; 데이터구동부         |

| <13> | 130; 발광제어 구동부      | 140; 유기 전계 발광 표시 패널 |

| <14> | 141; 유기 전계 발광 소자   |                     |

| <15> | PS1; 제1화소부         | PS2; 제2화소부          |

| <16> | PS3; 제3화소부         | PS4; 제4화소부          |

| <17> | PS5; 제5화소부         | PS6; 제6화소부          |

| <18> | SR1; 제1시프트레지스터     | SR2; 제2시프트레지스터      |

| <19> | SR3; 제3시프트레지스터     | SRn/2; 제n/2시프트레지스터  |

| <20> | NAND1; 제1낸드게이트     | NAND2; 제2낸드게이트      |

| <21> | NAND3; 제3낸드게이트     | NAND4; 제4낸드게이트      |

| <22> | NANDn-1; 제n-1낸드게이트 | NANDn; 제n낸드게이트      |

| <23> | Data[m]; 데이터선      | Scan[n]; 주사선        |

| <24> | Em[n]; 발광제어선       | ELVDD; 제1전원 전압선     |

| <25> | ELVSS; 제2전원 전압선    | Vinit; 제3전원 전압선     |

| <26> | M1; 구동트랜지스터        | S1; 제1스위칭소자         |

| <27> | S2; 제2스위칭소자        | S3; 제3스위칭소자         |

| <28> | S4; 제4스위칭소자        | S5; 제5스위칭소자         |

| <29> | S6; 제6스위칭소자        | S7; 제7스위칭소자         |

| <30> | C1; 제1용량성소자        | C2; 제2용량성소자         |

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

દોર્ની 6

## 도면7

도면8

## 도면9

도면10

|               |                                                                                                                           |         |            |

|---------------|---------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)       | 有机电致发光显示装置                                                                                                                |         |            |

| 公开(公告)号       | KR100807062B1                                                                                                             | 公开(公告)日 | 2008-02-25 |

| 申请号           | KR1020070034285                                                                                                           | 申请日     | 2007-04-06 |

| 申请(专利权)人(译)   | 三星SD眼有限公司                                                                                                                 |         |            |

| 当前申请(专利权)人(译) | 三星SD眼有限公司                                                                                                                 |         |            |

| [标]发明人        | KIM JONG YUN                                                                                                              |         |            |

| 发明人           | KIM, JONG YUN                                                                                                             |         |            |

| IPC分类号        | H05B33/02                                                                                                                 |         |            |

| CPC分类号        | G11C19/28 G09G2300/0852 G09G2300/0861 G09G3/006 G09G3/3233 G09G2310/0286 G09G2300/0819 G11C19/00 G09G2310/0224 G09G3/3266 |         |            |

| 外部链接          | <a href="#">Espacenet</a>                                                                                                 |         |            |

### 摘要(译)

本发明可以以提高所要解决的技术问题是通过检测有机发光显示面板和有机发光显示器的可靠性的像素预垂直短路缺陷来降低模块工艺成本。为此，本发明是原始时钟线，时钟线和源极部，并且电耦合到初始驱动线的第一移位寄存器，初始驱动线，所述第一移位寄存器1中的良好的发射控制线的输出与第一时钟线并且电耦合与所述初始驱动线，第一发光控制线和第二与非门电耦合到所述时钟线的第一NAND门，第一像素电连接到NAND门的输出前辈第一扫描线含有有机光部和第二与电耦合到所述NAND门的输出前辈第二扫描线的第二像素单元，所述第一扫描线电连接到所述第三像素和所述第二扫描线电连接到所述第四像素部分中公开了一种发光显示装置。