(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) . Int. Cl.

*H05B 33/22* (2006.01) (45) 공고일자 2007년03월19일

*H05B 33/26* (2006.01) (11) 등록번호 10-0696303

*H05B 33/14* (2006.01) (24) 등록일자 2007년03월12일

*H05B 33/10* (2006.01)

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2005-7003982   | (65) 공개번호   | 10-2005-0052487 |

| (22) 출원일자   | 2005년03월08일       | (43) 공개일자   | 2005년06월02일     |

| 심사청구일자      | 2005년03월08일       |             |                 |

| 번역문 제출일자    | 2005년03월08일       |             |                 |

| (86) 국제출원번호 | PCT/JP2003/011342 | (87) 국제공개번호 | WO 2004/026004  |

| 국제출원일자      | 2003년09월05일       | 국제공개일자      | 2004년03월25일     |

(30) 우선권주장 JP-P-2002-00266449 2002년09월12일 일본(JP)

(74) 대리인 백덕 이태호

(56) 선행기술조사문현

11109890 14215065

14221936

\* 석사과에 의하여 이용된 문헌

### 심사관 : 손희수

전체 청구항 수 : 총 8 항

#### (54) 유기 일렉트로루미네센스 표시장치 및 그 제조방법

### (57) 요약

기판과, 기판상에 형성되고 각각이 유기 일렉트로루미네센스 소자 및 유기 일렉트로루미네센스 소자에 접속된 유기 박막 트랜지스터를 포함하는 복수의 발광부를 포함하는 유기 일렉트로루미네센스 표시장치에 있어서, 유기 일렉트로루미네센스 소자는, 대향하는 한 쌍의 전극과, 한 쌍의 전극 사이에 적층된 유기 발광층을 포함하는 유기 재료층을 갖는다. 유기 박막 트랜지스터는, 대향하는 소스 전극 및 드레인 전극과, 소스 전극 및 드레인 전극 사이에 채널을 형성할 수 있도록 적층된 유기 반도체막과, 소스 전극 및 드레인 전극 사이의 유기 반도체막에 전계를 인가시키는 게이트 전극을 갖는다. 또한, 유기 일렉트로루미네센스 표시장치는, 발광부 내에 있어서, 소스 전극 및 드레인 전극 사이의 단락을 방지하는 소스 드레

인 절연막, 유기 반도체막을 보호하는 보호 절연막 및 유기 일렉트로루미네선스 소자의 일방의 전극의 에지를 피복하는 화소 절연막을 구비하고, 소스 드레인 절연막, 보호 절연막 및 화소 절연막 중 적어도 2개가 동일한 유전체 재료로 이루어진다.

## 내표도

도 4

## 특허청구의 범위

### 청구항 1.

기판과, 상기 기판상에 형성되고 각각이 유기 일렉트로루미네선스 소자 및 상기 유기 일렉트로루미네선스 소자에 접속된 유기 박막 트랜지스터를 포함하는 복수의 발광부를 포함하고 있는, 유기 일렉트로루미네선스 표시장치에 있어서,

상기 유기 일렉트로루미네선스 소자는, 대향하는 한 쌍의 전극과, 상기 한 쌍의 전극 사이에 적층된 유기 발광층을 포함하는 유기 재료층을 갖고,

상기 유기 박막 트랜지스터는, 대향하는 소스 전극 및 드레인 전극과, 상기 소스 전극 및 드레인 전극 사이에 채널을 형성 할 수 있도록 적층된 유기 반도체막과, 상기 소스 전극 및 드레인 전극 사이의 상기 유기 반도체막에 전계를 인가시키는 게이트 전극을 갖고,

또한, 상기 발광부는, 단락을 방지하는 소스 드레인 절연막, 상기 유기 반도체막을 보호하는 보호 절연막, 및 상기 유기 일렉트로루미네선스 소자의 전극들 중 하나의 에지를 피복하는 화소 절연막을 포함하는 유전체막을 더 구비하고,

상기 유전체막 중 적어도 2개가 동일한 유전체 재료로 이루어지는 것을 특징으로 하는 유기 일렉트로루미네선스 표시장치.

### 청구항 2.

제1항에 있어서,

상기 유기 박막 트랜지스터에 접속된 커패시터를 구비하고, 상기 유기 박막 트랜지스터는 상기 게이트 전극을 상기 소스 전극 및 드레인 전극으로부터 절연하는 게이트 절연막을 갖고, 상기 게이트 절연막은 상기 커패시터의 유전체와 동일한 재료로 이루어지는 것을 특징으로 하는 유기 일렉트로루미네선스 표시장치.

### 청구항 3.

제1항에 있어서,

상기 기판상에 전원 라인, 복수의 데이터 라인 및 주사 라인이 제공되고, 이들 교점 근방에 상기 발광부는 매트릭스 형태로 배치된 것을 특징으로 하는 유기 일렉트로루미네선스 표시장치.

### 청구항 4.

제1항 내지 제3항 중 어느 하나의 항에 있어서,

상기 발광부마다, 상기 주사 라인 및 테이터 라인에 접속된 제1 유기 박막 트랜지스터와, 상기 전원 라인 및 상기 유기 일렉트로루미네선스 소자에 접속된 제2 유기 박막 트랜지스터가 제공되고, 상기 제1 유기 박막 트랜지스터는, 상기 게이트 절연막과 동일한 재료로 이루어지는 절연막에 제공된 스루 홀을 통해, 상기 제2 유기 박막 트랜지스터의 게이트 전극에 접속된 것을 특징으로 하는 유기 일렉트로루미네선스 표시장치.

## 청구항 5.

제4항에 있어서,

상기 커패시터는, 상기 제2 유기 박막 트랜지스터에 대해 상기 제1 유기 박막 트랜지스터의 반대측에 배치된 것을 특징으로 하는 유기 일렉트로루미네선스 표시장치.

## 청구항 6.

제4항 또는 제5항에 있어서,

상기 커패시터는, 상기 전원 라인 바로 아래에 배치된 것을 특징으로 하는 유기 일렉트로루미네선스 표시장치.

## 청구항 7.

기판과, 상기 기판상에 형성되고 각각이 유기 일렉트로루미네선스 소자 및 상기 유기 일렉트로루미네선스 소자에 접속된 유기 박막 트랜지스터를 포함하는 복수의 발광부를 포함하고 있는 유기 일렉트로루미네선스 표시장치의 제조방법에 있어서,

대향하는 소스 전극 및 드레인 전극과, 상기 소스 전극 및 드레인 전극 사이에 채널을 형성할 수 있도록 적층된 유기 반도체막과, 상기 소스 전극 및 드레인 전극 사이의 상기 유기 반도체막에 전계를 인가시키는 게이트 전극을 갖는 유기 박막 트랜지스터를 형성하는 공정과,

대향하는 한 쌍의 전극과, 상기 한 쌍의 전극 사이에 적층된 유기 발광층을 포함하는 유기 재료층을 갖는 상기 유기 일렉트로루미네선스 소자를 형성하는 공정과,

상기 각 발광부에 있어서, 단락을 방지하는 소스 드레인 절연막, 상기 유기 반도체막을 보호하는 보호 절연막, 및 상기 유기 일렉트로루미네선스 소자의 전극들 중 하나의 에지를 회복하는 화소 절연막을 포함하는 유전체막을 형성하는 절연막 형성 공정을 포함하고,

상기 유전체막 중 적어도 2개가 동일한 유전체 재료로 이루어지고, 상기 2개가 동일한 공정으로 형성되는 것을 특징으로 하는 유기 일렉트로루미네선스 표시장치의 제조방법

## 청구항 8.

제7항에 있어서,

상기 유기 반도체막의 형성 후, 상기 유기 반도체막을, 상기 유기 반도체막의 내열성, 내용제성 및 내습성을 넘지 않는 환경으로 유지하는 것을 특징으로 하는 제조방법.

**명세서**

**기술분야**

본 발명은, 전자 및 홀의 주입에 의해 발광하는 유기 화합물 재료의 일렉트로루미네선스(이하, EL이라 한다)를 이용한 유기EL재료의 박막으로 이루어지는 발광층을 구비하고 있는, 유기EL소자로 이루어진 복수의 발광부가 규칙적으로 배치된 표시 배열을 갖는 유기EL 표시장치에 관한 것이다.

## 배경기술

복수의 유기EL소자를 매트릭스 형태로 배열하여 구성되는 유기EL 표시장치는, 저소비전력, 고표시품질 및 박형화가 가능한 디스플레이로서 주목받고 있다.

유기EL소자는, 예컨대, 인듐 주석 산화물, 소위 ITO로 이루어지는 투명전극이 형성된 유리판 등의 투명 기판상에, 유기 전자 수송층, 유기 발광층, 유기 홀 수송층 등에 있어서, 적어도 한 층의 유기 재료층, 및 금속 전극이 적층된 자발광 소자로서 알려져 있다. 투명 전극의 양극에 플러스, 금속 전극의 음극에 마이너스 전압을 인가함으로써, 전하가 축적되고, 이어서 소자 고유의 장벽 전압 또는 발광 문턱전압을 넘어서면, 전류가 흐르기 시작하고, 이 직류에 거의 비례하는 강도로 발광한다.

유기EL소자를 사용한 표시패널로서, 유기EL소자를 단순히 매트릭스 형태로 배치한 단순 매트릭스형 표시패널과, 매트릭스 형태로 배치한 유기EL소자의 각각에 트랜지스터로 이루어지는 구동 소자를 부가한 액티브 매트릭스형 표시패널이다. 액티브 매트릭스형 표시패널은 단순 매트릭스형 표시패널에 비해, 저소비전력이고, 또한 화소간의 크로스토크가 적은 등의 이점을 가져, 특히 대면적 디스플레이나 고정밀도 디스플레이에 적합하다.

액티브 매트릭스 구동방식의 표시장치는, 발광부마다, 예컨대, 폴리실리콘으로 이루어지는 박막 트랜지스터(TFT)를 사용한 스위칭에 의해 화소마다 전류를 공급하여 유기EL소자를 발광시키도록 한 것이다. TFT에는 MOS-FET(Metal Oxide Semiconductor Field Effect Transistor)이 사용되고 있다.

MOS-FET에는, 예컨대, 유리기판상에 폴리실리콘으로 이루어지는 2개의 반전 전도 영역을 형성하고, 상기 반전 전도 영역간의 기판 표면상에 산화물  $\text{SiO}_2$  박막, 금속 게이트 전극을 순차적으로 제공하고, 금속 게이트 전극으로부터 인가되는 전류에 의해, 전도성을 제어하는 것이다. 따라서, 디스플레이 기판에 고온 처리를 필요로 하는 폴리실리콘 기판 등이 필요하고, 그 위에 Si 등 무기 재료의 성막이 필요하기 때문에, 고온 프로세스가 그 제조에 사용된다.

표시장치로서는 대형 디스플레이 패널에 대한 수요가 많아, 저온 폴리실리콘 기판이 개발되고 있다. 그러나, 상기 기판은 제조시에 저온이라고는 해도  $500^{\circ}\text{C}$  정도의 가열 처리를 필요로 한다. 어느 경우든, 무기재료 TFT를 액티브 매트릭스 구동방식의 유기EL 표시장치의 대형 디스플레이 패널에 사용하면, 표시장치의 고가격화는 피할 수 없다.

그래서, 대향하는 한 쌍의 전극 사이에 성막된 유기재료로 이루어지는 유기 반도체막을 구비한 유기 TFT가 제안되어 있다. 이 유기 TFT를 사용하여 유기EL소자를 구동하는 것이 가능하다고 여겨진다.

그러나, 구체적인 유기 TFT 구조는 제안되어 있지 않다. 또한, 유기 TFT로 구동하는 유기EL소자에 구조상 불가결한 유기 반도체 재료, 유기재료층(15b)은 모두 내열성, 내용제성, 내습성 등이 매우 약하고, 실용적인 유기EL 표시패널을 실현하는 것이 곤란하다.

## 발명의 상세한 설명

그래서, 본 발명이 해결하고자 하는 과제에는, 비교적 저온에서 제조될 수 있는 유기 박막 트랜지스터 및 유기EL소자를 공통의 기판상에 형성한 유기EL 표시장치를 제공하는 것을 일례로 들 수 있다.

본 발명의 유기EL 표시장치는, 기판과, 상기 기판상에 형성되고 각각이 유기EL소자 및 상기 유기EL소자에 접속된 유기 박막 트랜지스터를 포함하는 복수의 발광부를 포함하는 유기EL 표시장치로서,

상기 유기EL소자는, 대향하는 한 쌍의 전극과, 상기 한 쌍의 전극 사이에 적층된 유기 발광층을 포함하는 유기 재료층을 갖고,

상기 유기 박막 트랜지스터는, 대향하는 소스 전극 및 드레인 전극과, 상기 소스 전극 및 드레인 전극 사이에 채널을 형성 할 수 있도록 적층된 유기 반도체막과, 상기 소스 전극 및 드레인 전극 사이의 상기 유기 반도체막에 전계를 인가시키는 게이트 전극을 갖고,

또한, 상기 각 발광부는, 단락을 방지하는 소스 드레인 절연막, 상기 유기 반도체막을 보호하는 보호 절연막 및 상기 유기 EL소자의 일방의 전극의 에지를 피복하는 화소 절연막을 포함하는 유전체막을 더 구비하고, 상기 유전체막 중 적어도 2개가 동일한 유전체 재료로 이루어지는 것을 특징으로 한다.

본 발명의 유기EL 표시장치의 제조방법은, 기판과, 상기 기판상에 형성되고 각각이 유기EL소자 및 상기 유기EL소자에 접속된 유기 박막 트랜지스터를 포함하는 복수의 발광부를 포함하는 유기EL 표시장치의 제조방법으로서,

대향하는 소스 전극 및 드레인 전극과, 상기 소스 전극 및 드레인 전극 사이에 채널을 형성할 수 있도록 적층된 유기 반도체막과, 상기 소스 전극 및 드레인 전극 사이의 상기 유기 반도체막에 전계를 인가시키는 게이트 전극을 갖는 유기 박막 트랜지스터를 형성하는 공정과,

대향하는 한 쌍의 전극과, 상기 한 쌍의 전극 사이에 적층된 유기 발광층을 포함하는 유기 재료층을 갖는 상기 유기EL소자를 형성하는 공정과,

상기 각 발광부에 있어서, 단락을 방지하는 소스 드레인 절연막, 상기 유기 반도체막을 보호하는 보호 절연막 및 상기 유기 EL소자의 전극들 중 하나의 에지를 피복하는 화소 절연막을 포함하는 유전체막을 형성하는 절연막 형성공정을 포함하고,

상기 유전체막 중 적어도 2개가 동일한 유전체 재료로 이루어지고, 상기 2개가 동일한 공정으로 형성되는 것을 특징으로 한다.

### 실시예

이하, 본 발명에 따른 실시예를 도면을 참조하여 설명한다.

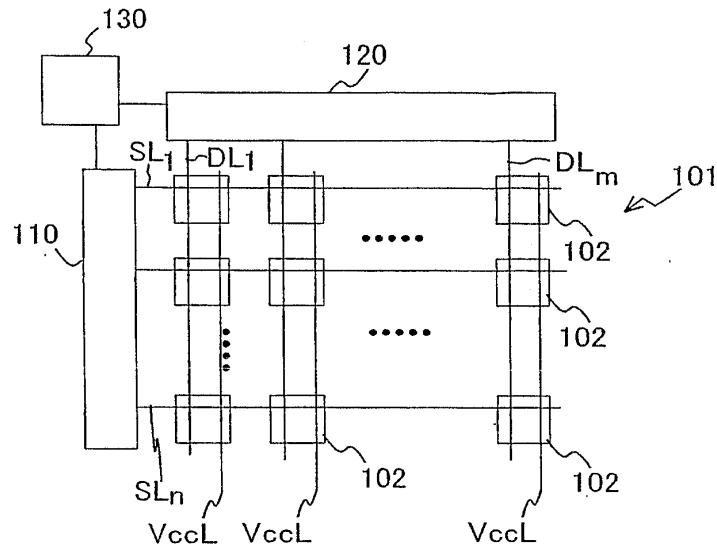

도1에, 액티브 매트릭스 구동방식에 따른 실시예의 유기EL 표시장치를 나타낸다. 표시장치는, 표시패널(101), 어드레스 드라이버(110), 데이터 드라이버(120) 및, 컨트롤러(130)를 구비하고 있다.

표시패널(101)은, 도1에 나타낸 바와 같이, 각각 소정 간극으로 평행하게 형성되어 있는 n개의 주사 라인 SL1~SLn과 각각 소정 간극으로 평행하게 형성되어 있는 m개의 데이터 라인 DL1~DLm을 구비하고 있고, 주사 라인 및 데이터 라인은 소정 간극을 사이에 두고 서로 직각이 되도록 형성되어 있다. 또한, 표시패널(101)은, 각각이 주사 라인 및 데이터 라인의 각 교점에 대응하는 부분에 형성되어 있는  $n \times m$  개의 발광부(102)를 구비하고 있다. 각 주사 라인의 일단은 어드레스 드라이버(110)에 접속되고, 각 데이터 라인의 일단은 데이터 드라이버(120)에 접속되어 있다.

어드레스 드라이버(110)는, 주사 라인 SL1~SLn에 1개씩 순차적으로 전압을 인가한다.

데이터 드라이버(120)는, 발광부(102)를 발광시키기 위한 데이터 전압을, 데이터 라인 DL1~DLm에 인가한다.

컨트롤러(130)는, 어드레스 드라이버(110) 및 데이터 드라이버(120)에 접속되고, 미리 공급된 화상 데이터에 따라, 어드레스 드라이버(110) 및 데이터 드라이버(120)의 동작을 제어한다.

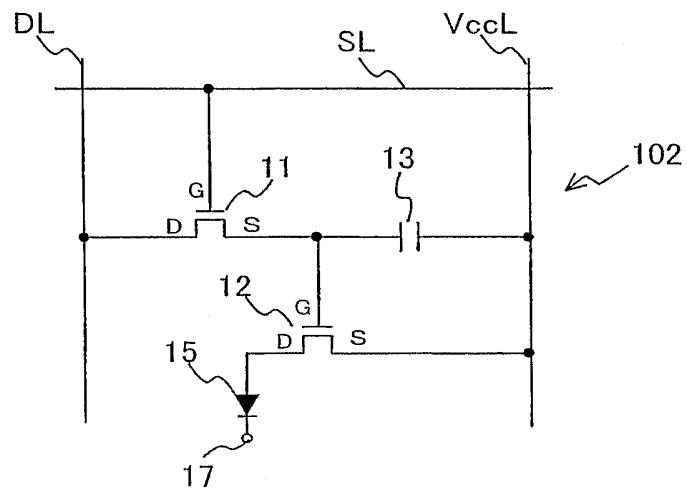

발광부(102)는, 도2에 나타낸 바와 같이, 선택용 트랜지스터의 어드레스 유기 TFT(11), 구동용 트랜지스터의 드라이브 유기 TFT(12), 커패시터(13), 및 유기EL소자(15)로 구성되어 있다.

도2에 있어서, 어드레스 유기 TFT(11)의 게이트 전극 G는, 어드레스 신호가 공급되는 주사 라인 SL에 접속되고, 어드레스 유기 TFT(11)의 드레인 전극 D는 데이터 신호가 공급되는 데이터 라인 DL에 접속되어 있다. 어드레스 유기 TFT(11)의 소스 전극 S는 드라이브 유기 TFT(12)의 게이트 전극 G에 접속되고, 커패시터(13)의 일방의 단자에 접속되어 있다. 드라이브 유기 TFT(12)의 소스 전극 S는 커패시터(13)의 타방의 단자와 함께 전원 라인 VccL에 접속되어 있다. 드라이브 유기 TFT(12)의 드레인 전극 D는 유기EL소자(15)의 양극에 접속되고, 유기EL소자(15)의 음극은 공통전극(17)에 접속되어 있다.

도2에 나타낸 전원 라인 VccL 및 각 유기EL소자(15)의 음극이 접속된 공통전극(17)은, 이들에 전력을 공급하는 전압원(도시하지 않음)에 접속되어 있다.

이 회로의 발광 제어 동작에 대해 설명하면, 우선, 도2에 있어서 어드레스 유기 TFT(11)의 게이트 전극 G에 ON전압이 공급되면, 어드레스 유기 TFT(11)은 소스 전극 S에 공급되는 데이터의 전압에 대응된 전류를 소스 전극 S로부터 드레인 전극 D로 흐르게 한다. 어드레스 유기 TFT(11)의 게이트 전극 G가 OFF 전압이면 어드레스 유기 TFT(11)은 소위 컷오프로 되고, 어드레스 유기 TFT(11)의 드레인 전극 D는 오픈 상태로 된다. 따라서, 어드레스 유기 TFT(11)의 게이트 전극 G가 ON 전압의 기간에, 커패시터(13)는 충전되고, 그 전압이 드라이브 유기 TFT(12)의 게이트 전극 G에 공급되고, 드라이브 유기 TFT(12)에는 그 게이트 전압과 소스 전압에 기초한 전류가 소스 전극 S로부터 드레인 전극 D로 흘러, 유기EL소자(15)를 발광시킨다. 또한, 어드레스 유기 TFT(11)의 게이트 전극 G가 ON 전압으로 되면, 어드레스 유기 TFT(11)은 오픈 상태로 되고, 드라이브 유기 TFT(12)는 커패시터(13)에 축적된 전하에 의해 게이트 전극 G의 전압이 유지되고, 다음 주사까지 구동전류를 유지하여, 유기EL소자(15)의 발광도 유지된다.

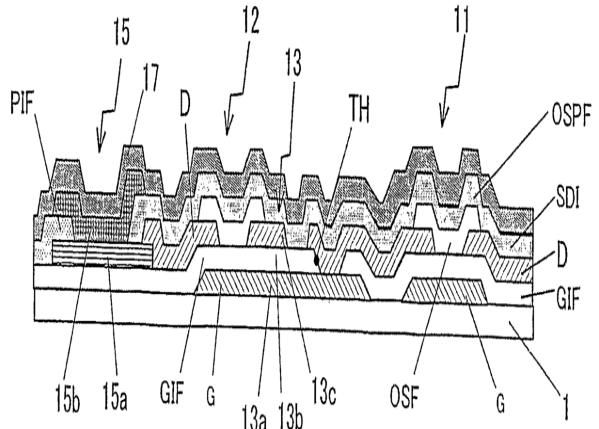

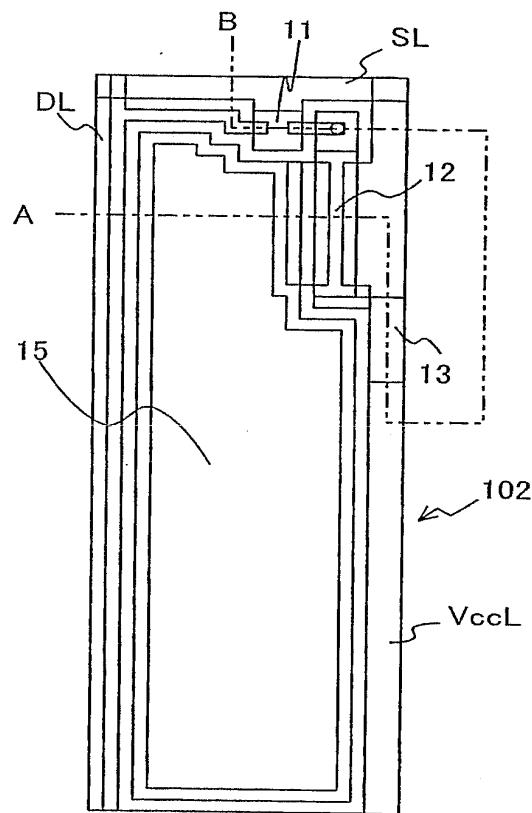

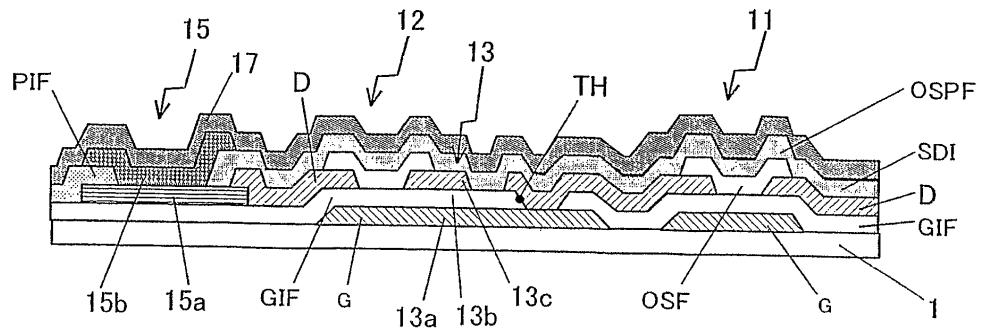

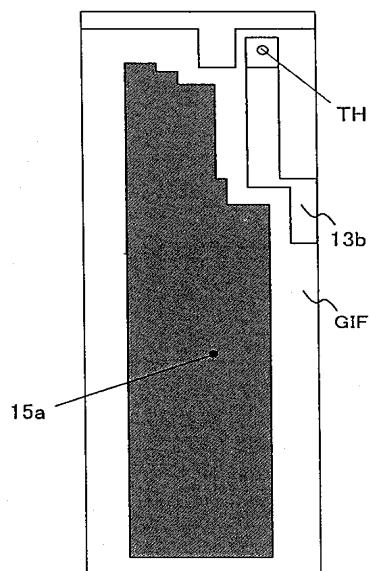

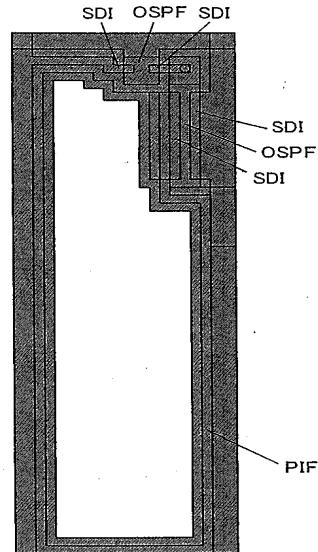

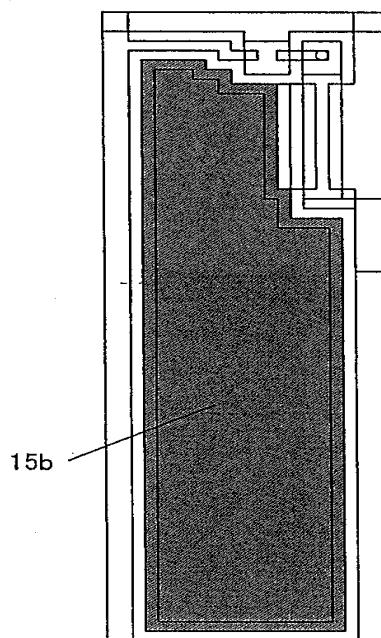

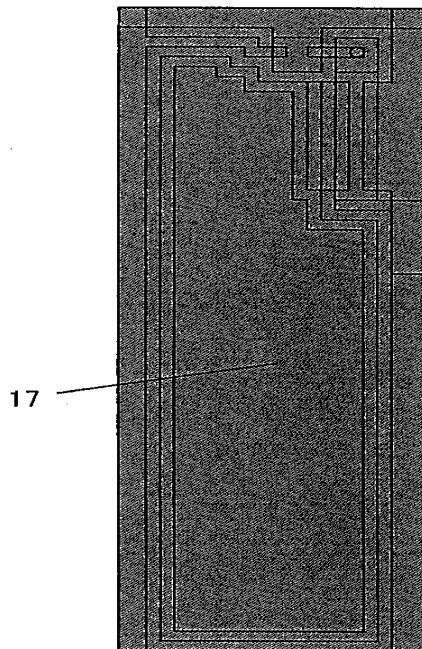

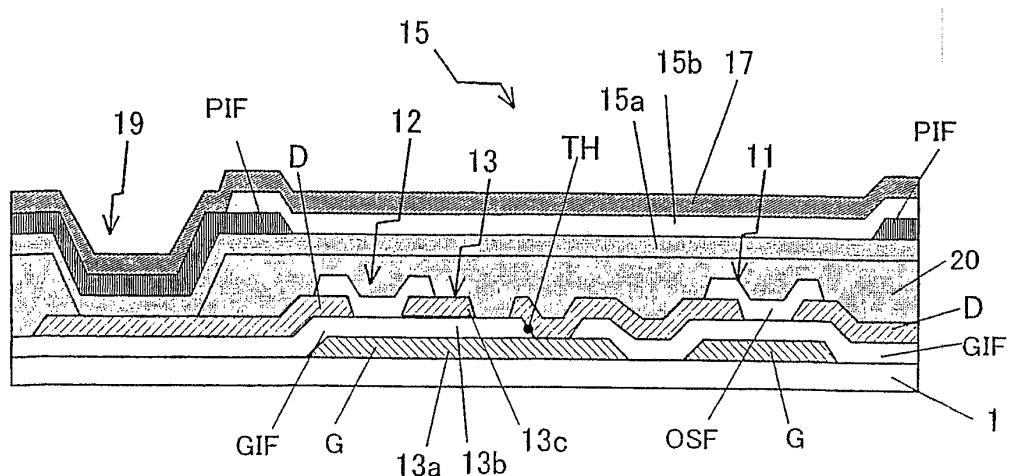

본 발명에 따른 유기 TFT에 의해 구동되는 유기EL소자로 이루어지는 유기EL 표시패널의 구조를 도3과 도4에 나타낸다. 도3의 평면도에 나타낸 바와 같이, 유기EL 표시패널은, 하나의 발광부마다, 유기EL소자(15), 이를 구동하기 위해 필요한 복수의 유기 TFT, 예컨대, 어드레스 유기 TFT(11) 및 드라이브 유기 TFT(12), 및, 데이터 전압의 유지에 필요한 커패시터(13)를 포함한다. 이 구성을 주사 라인 SL, 데이터 라인 DL 및 전원 라인 VccL의 각 교점 근방에, 배치시킴으로써 화소의 발광부를 실현할 수 있다. 도4는 도3에 나타낸 선 AB에 있어서의 단면을 나타낸다.

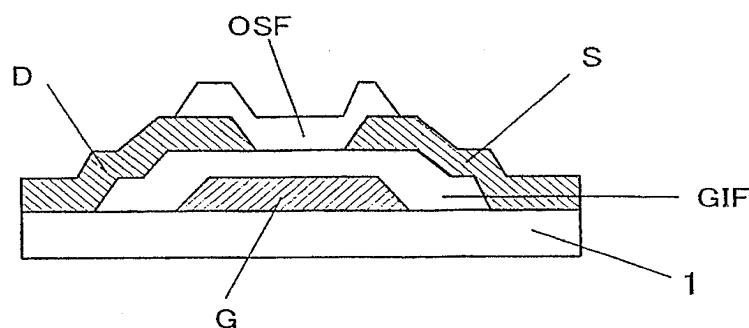

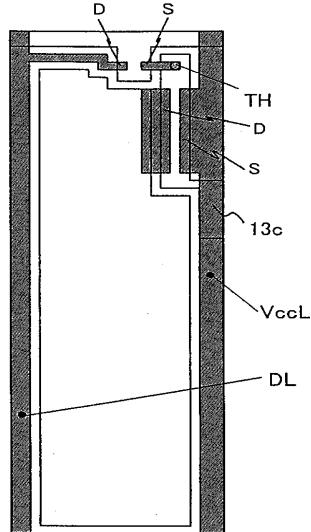

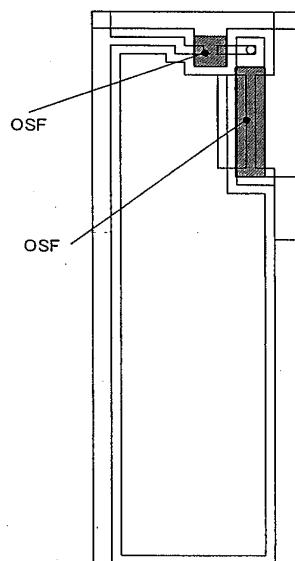

어드레스 유기 TFT(11) 및 드라이브 유기 TFT(12)의 구조를 도5에 나타낸다. 도5에 나타낸 바와 같이, 유기 TFT는, 대향하는 소스 전극 S 및 드레인 전극 D와, 소스 전극 및 드레인 전극 사이에 채널을 형성할 수 있도록 적층된 유기 반도체로 이루어지는 유기 반도체막 OSF와, 소스 전극 S 및 드레인 전극 D 사이의 유기 반도체막 OSF에 전계를 인가시키는 게이트 전극 G를 포함하고, 또한, 게이트 전극 G를 소스 전극 S 및 드레인 전극 D로부터 절연하는 게이트 절연막 GIF를 갖고 있다.

도4에 나타낸 바와 같이, 적어도 게이트 전극 G와 트랜지스터부를 피복하도록 게이트 절연막 GIF가 형성되어 있다. 게이트 절연막 GIF에는 트랜지스터끼리를 배선하기 위해 필요한 스루 홀 TH가 제공되어 있다. 동일한 유전체 재료를, 게이트 절연막 GIF로서 기능하고, 커패시터(13)의 유전체로서 기능하도록, 동시에 성막할 수 있다. 따라서, 도4에 나타낸 바와 같이, 게이트 절연막 GIF와 커패시터(13)의 유전체가 연속적으로 형성되어 있다.

도4에 나타낸 바와 같이, 소스 전극 S 및 드레인 전극 D의 위에는 전체면에 걸쳐 소스 드레인 절연막 SDI가 형성되어 있다. 유기EL소자의 공통전극(17)과의 단락을 방지하기 위한 것이다. 소스 드레인 절연막 SDI는 마찬가지로 유기 반도체막 OSF도 피복하여, 유기 반도체막의 유기 반도체 보호 절연막 OSPF로서 기능한다. 또한, 소스 드레인 절연막 SDI는 유기 EL소자(15)의 화소전극(15a)의 에지 부분도 피복하여, 화소 절연막 PIF로서도 기능한다.

드라이브 유기 TFT(12)는 화소전극(15a)으로 접속된다. 유기EL소자의 유기 재료층(15b)의 막두께는 통상  $0.1\mu\text{m}$  오더로 매우 얇기 때문에, 화소전극(15a)의 에지 부분은 공통전극(17)과 단락되기 쉽다. 이를 방지하기 위해 화소전극(15a)의 에지 부분을 피복하는 화소 절연막 PIF를 제공하는 것이 바람직하다.

유기EL소자(15)는 화소전극(15a), 유기 재료층(15b) 및 공통전극(17)으로 구성된다. 유기 재료층(15b)은, 통상, 홀 주입층, 홀 수송층, 발광층, 전자 수송층, 전자 주입층 등 복수의 층으로 구성되지만, 적어도 발광층을 포함하고 있으면 된다. 유기 재료층(15b)은 그 발광색에 의해 화소마다 색을 띤다. 발광층 이외의 층에서 각 색에 공통하는 층이 있는 경우, 그 층은 화소마다가 아닌 공통전극(17)과 같이 전체면에 형성되어도 된다.

화소전극(15a), 공통전극(17) 중 적어도 일방은, EL 발광을 외부로 취출하기 위해 광투과성을 가져야 한다.

본 발명에 따른 유기EL 표시장치에 사용되는 3개의 절연막, 즉 소스 드레인 절연막 SDI, 화소 절연막 PIF, 유기 반도체 보호 절연막 OSP 중 임의의 2이상의 막을 동시에 형성할 수 있다. 도4의 구조에서는 소스 드레인 절연막 SDI와 화소 절연막 PIF와 유기 반도체 보호 절연막 OSPF를 3개 동시에 형성하고 있다. 이들 2개의 절연막을 동시에 형성할 수 있어, 소스 드레인 절연막 SDI와 화소 절연막 PIF의 동시 형성의 경우는 도6과 같은 구조로 된다. 유기 반도체막 OSF를 성막하기 전에 소스 드레인 절연막 SDI와 화소 절연막 PIF를 동시에 형성하고, 유기 반도체막 OSF를 성막한 후에 유기 반도체 보호 절연막 OSPF를 형성한다.

상기 예에서는, 유기EL소자를 구동하기 위해 가장 단순한 구성인 2트랜지스터의 경우를 나타냈지만, 본 발명은 3이상의 트랜지스터를 사용한 소자에도 적용할 수 있다.

이하, 본 발명에 따른 유기EL 표시장치의 제조방법을 설명한다.

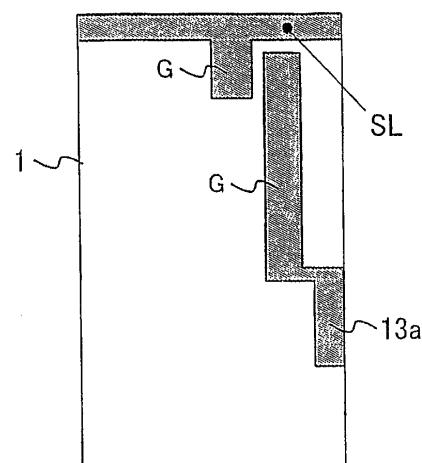

#### -게이트 전극의 형성-

도7에 나타낸 바와 같이, 우선, 유리, 플라스틱 등의 기판(1)상에 주사 라인 SL, 게이트 전극 G를 포함하는 하부 배선 패턴을 형성한다. 주사 라인 SL에 접속해야 할 어드레스 유기 TFT와 전원 라인에 접속해야 할 드라이브 유기 TFT의 게이트 전극 G 및 커패시터의 일방의 전극(13a)으로 되는 영역이 형성된다. 커패시터의 전극(13a)의 위치는 후에 접속되어야 할 전원 라인의 바로 아래의 위치에 배치된다. 전원 라인의 바로 아래에 커패시터를 제공함으로써, 화소 면적을 보다 넓게 확보할 수 있다.

주사 라인 SL이나 게이트 전극의 재료로서는 저항률이 낮은 것이 바람직하고, 일반적으로는 순금속, 또는 합금을 사용한다. 예를 들면, Al, Ag, Cu, Au, Cr 등, 및 이들을 포함하는 금속을 사용할 수 있다. 막의 형성 방법은 어떠한 방법이어도 상관없지만, 예컨대, 스퍼터링법, EB증착법, 저항가열 증착법, CVD법, 인쇄법 등을 사용할 수 있다. 패턴 형성 방법도 임의의 방법이라도 상관없지만, 예컨대, 포토 에칭법, 인쇄법, 마스크 증착법 등을 사용할 수 있다.

또한, 저항률의 면에서는 금속보다 열등하지만 게이트 전극에 도전성의 고분자를 사용할 수 있다. 이 경우 패턴 형성에 인쇄법 등 코스트가 낮은 방법을 사용할 수 있다.

#### -게이트 절연막의 형성-

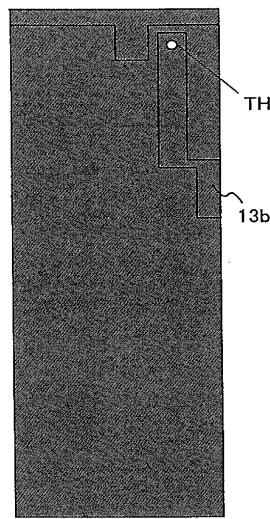

도8에 나타낸 바와 같이, 하부 배선 패턴상에 게이트 절연막 GIF를 소정의 패턴으로 형성한다. 여기서, 게이트 절연막 GIF와 동일한 유전체 재료로, 커패시터의 유전체층(13b)을, 그 전극(13a)상에 동시에 성막한다. 또한, 게이트 절연막 GIF에는, 어드레스 유기 TFT와 드라이브 유기 TFT의 게이트 전극 G을 접속시키기 위한 스루 흘 TH이 제공된다. 여기서, 게이트 절연막 GIF 및 커패시터의 유전체층(13b)의 기능을 각각 달성하기 위해 얇게 하고, 또한, 교차하는 전원 라인 및 주사 라인의 절연을 확보하기 위해 두껍게 하는 등, 개별적으로 복수회에 걸쳐 부분적으로 막두께가 상이한 게이트 절연막의 소정 패턴을 형성할 수 있다.

게이트 절연막 GIF의 재료로서는 금속 산화물, 금속 질화물, 금속 불화물 등 금속의 화합물, 예컨대,  $Al_2O_3$ ,  $SiO_2$ ,  $SiN$ ,  $SiON$  등, 또는 절연성의 폴리머, 예컨대, 폴리이미드 등을 사용할 수 있다. 막의 형성 방법은 어떠한 방법이어도 상관없지만, 예컨대, 스퍼터링법, EB 증착법, 저항가열 증착법, CVD법, 인쇄법, 스픬코팅법 등을 사용할 수 있다. 패턴 형성 방법도 임의의 방법이라도 상관없지만, 예컨대, 포토에칭법, 인쇄법, 마스크 증착법 등을 사용할 수 있다.

#### -화소 전극의 형성-

도9에 나타낸 바와 같이, 유기EL소자의 양극으로서 거의 직사각형의 화소전극(15a)을 게이트 절연막 GIF상에 소정의 패턴으로 형성한다.

화소전극(15a)에 광투과성이 필요한 경우, 전극 재료로서 일반적으로는 순금속이나, 합금의 매우 얇은 반투과막, 금속 산화물 등의 투명 전극을 사용한다. 예를 들면, Au, Pd 등의 반투과막, ITO 등의 투명 전극을 사용할 수 있다. 광투과성이 필요하지 않은 경우, 재료로서는 일반적으로 순금속, 또는 합금을 사용한다. 예를 들면, Al, Ag, Cu, Au, Cr 등, 및 이들을 포함하는 합금을 사용할 수 있다.

막의 형성 방법은 어떠한 방법이어도 상관없지만, 예를 들면 스퍼터링법, EB 증착법, 저항가열 증착법, CVD법, 인쇄법 등을 사용할 수 있다. 패턴 형성 방법도 임의의 방법이라도 상관없지만, 예컨대, 포토에칭법, 인쇄법, 마스크 증착법 등을 사용할 수 있다.

#### -소스 전극 및 드레인 전극의 형성-

도10에 나타낸 바와 같이, 어드레스 유기 TFT 및 드라이브 유기 TFT의 소스 전극 S 및 드레인 전극 D와 동시에 데이터 라인 DL 및 전원 라인 VccL을, 화소전극(15a) 또는 게이트 절연막 GIF상에 소정의 배선 패턴으로 형성한다. 화소전극(15a)을 협지하고 서로 평행한 데이터 라인 DL 및 전원 라인 VccL은 주사 라인 SL에 직교차하도록 게이트 절연막 GIF상에 형성된다.

여기서, 전원 라인 VccL의 일부는, 커패시터의 전극(13a)상의 유전체층(13b)을 협지하는 커패시터의 타방의 전극(13c)으로서, 동시에 성막된다. 형성된 커패시터(13)에 있어서, 전원 라인 VccL은 전력 공급을 행하기 위한 타 라인보다도 폭이 넓게 성막되어, 그 전원 라인 바로 아래에 배치되기 때문에, 화소 전극을 압박하지 않고 커패시터(13)의 용량을 충분히 확보할 수 있다. 또한, 커패시터(13)는, 드라이브 유기 TFT(12)에 대해 어드레스 유기 TFT(11)의 반대측에 배치되어 있기 때문에, 드라이브 유기 TFT(12) 및 어드레스 유기 TFT(11)의 배선 거리가, 커패시터(13)를 드라이브 유기 TFT(12) 및 어드레스 유기 TFT(11) 사이에 배치한 경우보다 짧아진다. 따라서, 화소 전극 면적의 확보와 전하의 이동 속도의 향상도 기대할 수 있다.

전원 라인 VccL에 접속되는 드라이브 유기 TFT의 소스 전극 S 및 드레인 전극 D는, 대응하는 게이트 전극에 걸리도록 형성되고, 드레인 전극 D는 화소 전극(15a)에 접속하도록 형성된다. 데이터 라인 DL에 접속되는 어드레스 유기 TFT의 드레인 전극 D 및 소스 전극 S는, 대응하는 게이트 전극에 걸리도록 형성되고, 소스 전극 S는 스루 흘 TH를 통해 드라이브 유기 TFT의 게이트 전극에 접속하도록 형성된다.

소스 전극 및 드레인 전극의 재료로서는, 사용하는 유기 반도체에 대해 효율 높은 캐리어 주입이 가능하고, 저항률이 낮은 것이 바람직하고, 예컨대, Au, Pd 등이 사용된다. 데이터 라인 DL 및 전원 라인 VccL의 재료로서는 주사 라인 SL과 동일한 것이 사용된다.

막의 형성 방법은 어떠한 방법이어도 상관없지만, 예컨대, 스퍼터링법, EB 증착법, 저항가열 증착법, CVD법, 인쇄법 등을 사용할 수 있다. 패턴 형성 방법도 임의의 방법이라도 상관없지만, 예컨대 포토 에칭법, 인쇄법, 마스크 증착법, 등을 사용할 수 있다.

저항률의 면에서는 금속보다 열등하지만, 소스 전극 및 드레인 전극에 도전성의 고분자를 사용할 수 있다. 이 경우 패턴 형성에 인쇄법 등 코스트가 낮은 방법을 사용할 수 있다.

또한, 소스 전극 및 드레인 전극의 재료와 화소전극(15a)의 재료를 동일하게 하는 것이 가능하고, 이 경우, 화소전극(15a)과 소스 전극 및 드레인 전극의 형성을 1공정으로 행할 수 있다. 또한, 재료에 따라 개별적으로 복수회 걸쳐 상기 소정배선 패턴을 형성할 수 있다.

또한, 본 실시예에서는 화소전극(15a)의 형성 공정을 소스 전극 및 드레인 전극의 형성 공정보다 먼저 행했지만, 역순으로 행해도 된다.

#### -유기 반도체막의 형성-

도11에 나타낸 바와 같이, 전원 라인 VccL에 접속되는 드라이브 유기 TFT 및 데이터 라인 DL에 접속되는 어드레스 유기 TFT의 게이트 전극의 바로 위의 소스 전극 S, 드레인 전극 D 및 게이트 절연막 GIF에 접속하도록, 각각 유기 반도체막 OSF가 소정의 패턴으로 형성된다.

유기 반도체막 OSF의 재료로서는 캐리어의 이동도가 높은 재료가 바람직하고, 저분자의 유기 반도체 재료, 유기 반도체 폴리머를 사용할 수 있다.

막의 형성 방법은 어떠한 방법이어도 상관없지만, 예컨대, 스퍼터링법, EB 증착법, 저항가열 증착법, CVD법, 인쇄법, 스플로팅법 등을 사용할 수 있다.

패턴 형성 방법도 임의의 방법이라도 상관없지만, 예컨대, 포토 에칭, 인쇄법, 마스크 증착법 등을 사용할 수 있다.

#### -공통 절연막(소스 드레인 절연막, 화소 절연막, 유기 반도체 보호 절연막)의 형성-

도12에 나타낸 바와 같이, 소스 드레인 절연막 SDI, 화소 절연막 PIF 및 유기 반도체 보호 절연막 OSPF로서 기능하는 공통 절연막을 소정의 패턴, 즉, 유기EL소자(15)의 화소전극(15a)의 에지 부분까지를 피복하고, 화소전극(15a)을 노출시키는 패턴으로 형성한다.

공통 절연막 재료로서는 금속 산화물, 금속 질화물, 금속 불화물 등 금속의 화합물, 예컨대,  $Al_2O_3$ ,  $SiO_2$ ,  $SiN$ ,  $SiON$  등, 또는 절연성의 폴리머, 예컨대 폴리이미드 등을 사용할 수 있다.

막의 형성 방법은 어떠한 방법이어도 상관없지만, 예컨대, 스퍼터링법, EB 증착법, 저항가열 증착법, CVD법, 인쇄법, 스플로팅법 등을 사용할 수 있다. 패턴 형성 방법도 임의의 방법이라도 상관없지만, 예컨대 포토 에칭법, 인쇄법, 마스크 증착법 등을 사용할 수 있다.

단, 중간층의 유기 반도체막 OSF의 재료는 일반적으로 내열성, 내용제성, 내습성이 강하여, 유기 반도체막상에 형성하는 공통 절연막의 형성 프로세스로 반도체막의 특성을 손상하지 않도록 해야 한다.

#### -유기 재료층의 형성-

도13에 나타낸 바와 같이, 공통 절연막의 개구를 통해, 적어도 발광층을 포함하는 유기 재료층(15b)을 화소전극(15a)상에 형성한다. 유기 재료층(15b)은 발광층 이외에 홀 주입층, 홀 수송층, 전자 수송층, 전자 주입층 등을 포함하고 있어도 된다.

막의 형성 방법은 어떠한 방법이어도 상관없지만, 예컨대, 스퍼터링법, EB 증착법, 저항가열 증착법, CVD법, 인쇄법, 스플로팅법 등을 사용할 수 있다.

패턴 형성 방법도 임의의 방법이라도 상관없지만, 예컨대 포토 에칭법, 인쇄법, 마스크 증착법 등을 사용할 수 있다.

#### -공통 전극의 형성-

도14에 나타낸 바와 같이, 유기 재료층(15b)상에 유기EL소자(15)의 음극으로서의 공통전극(17)을 소정의 패턴으로 형성한다.

공통전극(17)의 재료로서는 순금속, 또는 합금을 사용한다. 예를 들면, Al, Ag, Cu, Au, Cr 등, 및 이들의 합금을 사용할 수 있다.

막의 형성 방법은 어떠한 방법이어도 상관없지만, 상기 유기 재료층의 형성공정으로 성막된 어떠한 유기 재료층도 열화시키지 않도록, 예컨대, 각각의 유기 재료층의 유리 전이점 이하의 온도에서, 스퍼터링법, EB 증착법, 저항가열 증착법, CVD법, 인쇄법 등을 사용할 수 있다.

패턴 형성 방법도 임의의 방법이라도 상관없지만, 예컨대, 포토 에칭법, 인쇄법, 마스크 증착법, 등을 사용할 수 있다.

#### -타 실시예-

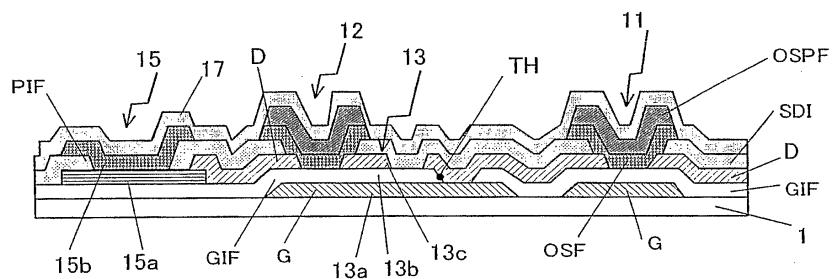

도15와 같이, 유기 TFT(11,12)와 유기EL소자(15)를 중첩적으로 배치하는 것도 가능하다. 도15와 도6에서 동일한 부호로 나타낸 부재는 동일하기 때문에 설명은 생략한다. 이 경우, 공통전극(17)을 광투과성 재료로 형성하는 것이 바람직하다. 이 구조에서는, 유기EL소자(15)의 면적을 크게 할 수 있기 때문에 개구율을 높일 수 있는 장점이 있다.

어드레스 유기 TFT(11) 및 드라이브 유기 TFT(12)를 형성한 후, 화소전극(15a)과의 접속부(19)를 제외하고, 유기 반도체 보호 절연막 OSPF와 소스 드레인 절연막 SDI를 겸한 평탄화층(20)을 형성한다. 유기 TFT에 의한 요철이 있으면, 유기 EL소자의 화소전극(15a)과 공통전극(17)이 쉽게 단락되기 때문에, 평탄화층(20)은 이 요철을 매끄럽게 피복할 필요가 있다. 또한, 중간층의 유기 반도체 재료는 일반적으로 내열성, 내용제성, 내습성이 강하기 때문에, 평탄화층(20)의 형성 프로세스로 반도체막의 특성을 손상하지 않도록 해야 한다.

평탄화층(20)을 형성한 후, 드라이브 유기 TFT(12)와 접속하여 화소전극(15a)을 형성하고, 다시 유기 재료층(15b), 공통전극(17)을 형성하고, 본 발명에 따른 유기EL 표시장치의 표시 패널이 완성된다.

이와 같이 이상의 실시예에 따르면, 현실적인 구조로 유기 TFT 구동의 유기EL 표시패널을 실현할 수 있다. 또한, 제조방법상, 배선이나 절연막 등 포토리소그래피 공정 등 내열성, 내용제성, 내습성이 필요한 부재는, 유기물의 증착 전에 미리 형성해 두기 때문에, 포토리소그래피 공정 등 내열성, 내용제성, 내습성에 강한 유기물로 이루어지는 부재를 손상시키지 않는다. 또한, 필요한 절연막 중 적어도 2개를 동시에 형성하기 때문에 공정이 간략화될 수 있다.

또한, 이상의 실시예에 있어서는, 발광부 내의 유기 TFT로서, 소위 MIS(Metal Insulator Semiconductor)형 유기 박막 트랜지스터를 사용했지만, MIS형을 대신하여 SIT(Static Induction Transistor)형 유기 박막 트랜지스터를 사용해도 된다.

### 도면의 간단한 설명

도1은, 본 발명에 따른 실시예에 있어서, 유기EL 표시장치의 표시패널의 구성을 나타내는 블록도이다.

도2는, 본 발명에 따른 실시예에 있어서, 유기EL 표시장치의 발광부를 나타내는 회로도이다.

도3은, 본 발명에 따른 실시예에 있어서, 유기EL 표시장치의 발광부를 나타내는 표시측에서 바라본 평면도이다.

도4는, 도3의 선 AB의 단면도이다.

도5는, 본 발명에 따른 실시예에 있어서, 유기EL 표시장치의 발광부의 유기 박막 트랜지스터의 단면도이다.

도6은, 본 발명에 따른 타 실시예에 있어서, 유기EL 표시장치의 표시패널의 발광부를 나타내는 단면도이다.

도7~도14는, 본 발명에 따른 실시예에서의 유기EL 표시장치의 표시패널의 제조 공정에 있어서, 기판의 개략 부분의 확대 평면도이다.

도15는, 본 발명에 따른 타 실시예에 있어서, 유기EL 표시장치의 표시패널의 발광부를 나타내는 단면도이다.

### 도면

#### 도면1

## 도면2

### 도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

|                |                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光显示装置及其制造方法                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">KR100696303B1</a>                                                                                     | 公开(公告)日 | 2007-03-19 |

| 申请号            | KR1020057003982                                                                                                   | 申请日     | 2003-09-05 |

| [标]申请(专利权)人(译) | 日本先锋公司                                                                                                            |         |            |

| 申请(专利权)人(译)    | 先锋株式会社                                                                                                            |         |            |

| 当前申请(专利权)人(译)  | 先锋株式会社                                                                                                            |         |            |

| [标]发明人         | NAGAYAMA KENICHI                                                                                                  |         |            |

| 发明人            | NAGAYAMA, KENICHI                                                                                                 |         |            |

| IPC分类号         | H05B33/22 H05B33/26 H05B33/14 H05B33/10 H01L21/312 H01L21/316 H01L21/318 H01L27/32 H01L29/786 H01L51/05 H01L51/50 |         |            |

| CPC分类号         | H01L27/3248 H01L51/107 H01L27/3274 H01L51/0545                                                                    |         |            |

| 代理人(译)         | LEE , 金泰熙                                                                                                         |         |            |

| 优先权            | 2002266449 2002-09-12 JP                                                                                          |         |            |

| 其他公开文献         | <a href="#">KR1020050052487A</a>                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                         |         |            |

### 摘要(译)

关于有机电致发光显示装置的有机电致发光元件，包括包括基板的多个发光单元，并且每个都是有机电致发光元件和连接到有机电致发光元件的有机薄膜晶体管，它在基板上形成有有机材料包括对的电极的层，以及层叠在一对电极之间的有机发光层，只要它面对即可。有机薄膜晶体管具有栅电极，在有机导体膜之间施加电场，有机导体膜被层压以形成相对的源电极和漏电极之间的沟道，以及源电极和漏电极以及源电极和漏电极。此外，有机电致发光显示装置包括其在发光单元内具有的源电极，保护源极漏极绝缘层的保护绝缘膜，其能够防止漏电极与有机导体膜之间的短路，以及源极漏极绝缘层，保护绝缘膜和介电物质，其中在像素绝缘层中至少2是相同的，包括涂覆有机电致发光元件的一个电极的边缘的像素绝缘层。