Europäisches

Patentamt

European

Patent Office

Office européen

des brevets

(11)

EP 1 352 545 B1

(12)

## EUROPEAN PATENT SPECIFICATION

(45) Date of publication and mention

of the grant of the patent:

**17.06.2009 Bulletin 2009/25**

(21) Application number: **02709927.4**

(22) Date of filing: **10.01.2002**

(51) Int Cl.:

**H05B 33/22 (2006.01)**

(86) International application number:

**PCT/CA2002/000034**

(87) International publication number:

**WO 2002/058438 (25.07.2002 Gazette 2002/30)**

### (54) INSERTION LAYER FOR THICK FILM ELECTROLUMINESCENT DISPLAYS

EINFÜGUNGSSCHICHT FÜR DICKFILM-ELEKTROLUMINESZENZANZEIGEN

COUCHE D'INSERTION POUR AFFICHEURS ELECTROLUMINESCENTS A FILM MINCE

(84) Designated Contracting States:

**AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU

MC NL PT SE TR**

(30) Priority: **17.01.2001 US 761971**

(43) Date of publication of application:

**15.10.2003 Bulletin 2003/42**

(73) Proprietor: **iFire IP Corporation

Fort Saskatchewan AB T8L 3W4 (CA)**

(72) Inventors:

• **LI, Wu

Brampton, Ontario L6Z 1M8 (CA)**

• **XIN, Yongbao

Mississauga, Ontario L5M 5M6 (CA)**

• **WESTCOTT, Michael, R.

Oakville, Ontario L6J 2T7 (CA)**

(74) Representative: **Carpmaels & Ransford

43-45 Bloomsbury Square

London WC1A 2RA (GB)**

(56) References cited:

**EP-A- 1 215 946 WO-A-00/70917

US-A- 4 897 319 US-A- 5 309 070

US-A- 5 634 835 US-A- 5 912 532**

- **DATABASE WPI Section Ch, Week 198451

Derwent Publications Ltd., London, GB; Class

L03, AN 1984-316765 XP002203043 & JP 59

047879 B (OMRON TATEISI ELECTRONICS CO),

21 November 1984 (1984-11-21)**

- **DATABASE INSPEC [Online] INSTITUTE OF

ELECTRICAL ENGINEERS, STEVENAGE, GB;

EVANGELOU E K ET AL: "Characterisation of the

BaTiO<sub>3</sub>/p-Si interface and applications"

Database accession no. 6751868 XP002203042 &

SEVENTH INTERNATIONAL CONFERENCE ON

THE FORMATION OF SEMICONDUCTOR

INTERFACES, GOTEBORG, SWEDEN, 21-25

JUNE 1999, vol. 166, pages 504-507, Applied

Surface Science, 9 Oct. 2000, Elsevier,

Netherlands ISSN: 0169-4332**

#### Remarks:

The file contains technical information submitted after

the application was filed and not included in this

specification

EP 1 352 545 B1

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

**Description****FIELD OF THE INVENTION**

**[0001]** The present invention relates to insertion layers for thick film electroluminescent displays, and especially to a non-porous layer between the thick film dielectric layer and the phosphor in such displays.

**[0002]** The term "non-porous" as used in this patent application means that the layer inhibits the transport of deleterious atomic species across the layer to the extent required to substantially prevent performance degradation of the electroluminescent display, and especially phosphors therein, due to migration of these species into the phosphor layer.

**BACKGROUND OF THE INVENTION**

**[0003]** The present invention relates to improving the luminance and operating stability of electroluminescent displays having thick film dielectric layers with a high dielectric constant. In such displays, a display pixel is addressed by applying a voltage between a selected address row and a selected address column on opposite sides of a phosphor film sandwiched between two dielectric layers, one of which is a thick film dielectric layer. The applied voltage creates an electric field across the phosphor film at the pixel located at the intersection of the selected row and column site.

**[0004]** A significant advantage of electroluminescent displays with thick film dielectric layers over traditional thin film electroluminescent (TFEL) displays is that the thick film high dielectric constant layer may be made sufficiently thick to prevent dielectric breakdown. The high relative dielectric constant of the materials that are used minimizes the voltage drop across the dielectric layer when a pixel is illuminated. In order to prevent dielectric breakdown, the thick film layer is typically comprised of a sintered perovskite, piezoelectric or ferroelectric material e.g. PMN-PT, with a relative dielectric constant of several thousand and a thickness greater than about 10 micrometers. PMN-PT is a material that includes lead and magnesium niobates and titanates. An additional thinner overlayer of a compatible piezoelectric material e.g. lead zirconate titanate, may be applied using metal organic deposition (MOD) or sol gel techniques, to smooth the surface of the thick film for subsequent deposition of a thin film phosphor structure. The processes used to deposit the overlayer are typically practical for deposition of layers of not more than about 3 micrometers, and thus are not suitable for deposition of the primary component of the thick film dielectric layer. In addition, the relative dielectric constants of the materials deposited using sol gel or MOD processes are significantly lower than that of PMN-PT, being typically less than 1000, but the dielectric breakdown strengths are comparable. The consequence is that substantially thicker layers would need to be used as the primary thick film

dielectric that prevents dielectric breakdown, and this is not a practical option.

**[0005]** A thick film dielectric electroluminescent display is constructed on a ceramic or other heat resistant substrate. The fabrication process for the display entails first depositing a set of row electrodes on the substrate. A thick film dielectric layer is deposited on the substrate using thick film deposition techniques that are exemplified in U.S. Patent 5,432,015. A thin film structure comprised of one or more thin film dielectric layers sandwiching one or more thin phosphor films is then deposited, followed by a set of optically transparent column electrodes using vacuum techniques as exemplified by published PCT patent application WO 00/70917 of Wu et al. The entire resulting structure is covered with a sealing layer that protects the thick and thin film structures from degradation due to moisture or other atmospheric contaminants. The thick film electroluminescent display structure that is obtained provides for superior resistance to dielectric breakdown as well as reduced operating voltage, compared to thin film electroluminescent (TFEL) displays. This is due to the high relative dielectric constant of the thick film dielectric materials that are used, which facilitates the use of thick layers while still permitting an acceptably low display operating voltage.

**[0006]** The thick film dielectric structure, when it is deposited on a ceramic substrate, will also withstand higher processing temperatures than TFEL devices, which are typically fabricated on glass substrates. The increased temperature tolerance facilitates annealing of subsequently deposited phosphor films to improve luminosity. However, even with these enhancements, thick film electroluminescent displays have not achieved the phosphor luminance and colour coordinates needed to be fully competitive with cathode ray tube (CRT) displays, particularly with recent trends in CRT specifications to higher luminance and colour temperature. Increased luminance can be realized by increasing the operating voltage, but this increases the power consumption of the displays, decreases reliability and increases the cost of driving electronics for the displays.

**[0007]** Increased luminance can also be achieved by using a patterned phosphor structure, instead of the traditional unpatterned white emitting phosphor systems used for TFEL displays. This reduces optical losses in the filters that are used to achieve acceptable CIE colour coordinates for red, green and blue emissions by at least partially matching the omission spectra of the phosphors to that required to achieve the needed CIE coordinates for each colour. However, such patterning requires the use of photolithographic processes to fabricate high-resolution displays. The use of photolithography for electroluminescent phosphors, as exemplified by the aforementioned published PCT patent application WO 00/70917, requires the deposition of photoresist films and the etching or lift-off of portions of the phosphor films to provide the required pattern. Deposition and removal of photoresist films and etching or lift-off of phosphor films typically

requires the use of solvent-based solutions that contain water or other reactive solvents and solutes. These solutions or any residues may react with the underlying display structure, thereby degrading the performance of the completed display device. The degradation may increase if the residues of the solutions become trapped and then diffuse within the structure during subsequent phosphor annealing steps.

**[0008]** The performance of thick film electroluminescent displays can be enhanced by judicious choice of thin film dielectric layers used to sandwich the phosphor films used in the displays. The enhanced performance is related to the inhibition of transportation of deleterious species from the thick film structure to the thin film structure and causing degradation of phosphor performance. In addition, there is an increase in the effective surface density of electrons injected into the phosphor film under conditions appropriate to generation of light. Nevertheless, such thin film dielectric layers have limitations. If the thin film dielectric layers are made thicker so as to be more effective to inhibit diffusion of atomic species, there is an increased voltage drop across the layers relative to the voltage across the phosphor film required for electron injection into the phosphor to generate light. The increased voltage drop results in a requirement for a higher display operating voltage, the disadvantages of which have been discussed above.

**[0009]** US-A-5634835 discloses a display device comprising (i) a (first) thick film dielectric layer made of  $PbNbO_3$ ,  $BaTiO_3$ ,  $SrTiO_3$  and  $PbTiO_3$  (ii) a second dielectric (smoothing) layer that may or may not be deposited on the first dielectric layer, and (iii) a phosphor layer deposited on the smoothing layer/first dielectric layer.

**[0010]** EP-A-1215946 describes a thick film electroluminescent device which comprises a dielectric laminate positioned between an electrode layer and a light emitting layer. The dielectric laminate is comprised of two lead-containing layers and a third high permittivity layer which is free of lead. The dielectric layer maybe formed from  $BaTiO_3$ ,  $SrTiO_3$  or a solid solution of  $Ba_{1-x}Sr_xTiO_3$ .

## SUMMARY OF THE INVENTION

**[0011]** A non-porous insertion layer for thick film electroluminescent displays has now been developed. Accordingly, one aspect of the present invention provides in a thick film electroluminescent display having a thick film dielectric layer and phosphor layer, the improvement comprising:

an adherent thin non-porous layer interposed between the thick film dielectric layer and the phosphor layer, said thin non-porous layer comprising a crystalline material having a crystal structure with a permanent or electric-field induced dipole moment; said thin non-porous layer being chemically more stable with respect to the phosphor layer than the thick film dielectric layer;

said non porous layer exhibiting reduced diffusion characteristics to atomic species than the thick film dielectric layer and wherein the non-porous layer is formed from  $BaTa_2O_6$ .

**[0012]** In preferred embodiments of the invention, the crystal structure does not have a centre of inversion symmetry.

**[0013]** In a further embodiment, the non-porous layer is adjacent both the thick film dielectric layer and the phosphor layer, or the non-porous layer is adjacent to (i) a smoothing dielectric layer on the thick film dielectric layer and to (ii) the phosphor layer.

**[0014]** In other embodiments, the non porous layer is ferroelectric.

**[0015]** In still further embodiments, the non-porous layer has a relative dielectric constant of greater than 20, especially greater than 50 and in particular greater than 100.

**[0016]** The non-porous layer is formed from  $BaTa_2O_6$ .

**[0017]** In further embodiments, the non-porous layer has a thickness of 0.05-1.0 micrometers, especially a thickness of 0.1-0.3 micrometers.

**[0018]** In still further embodiments of the present invention, a thin film dielectric layer is applied on the phosphor layer, especially a thin film dielectric layer that is  $Al_2O_3$  or  $BaTiO_3$ .

**[0019]** In preferred embodiments, a layer of indium tin oxide is applied over the thin film dielectric layer.

## BRIEF DESCRIPTION OF THE DRAWINGS

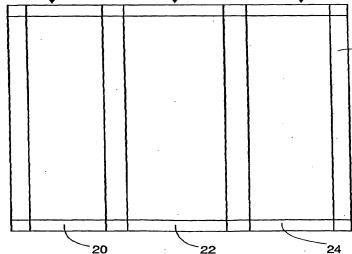

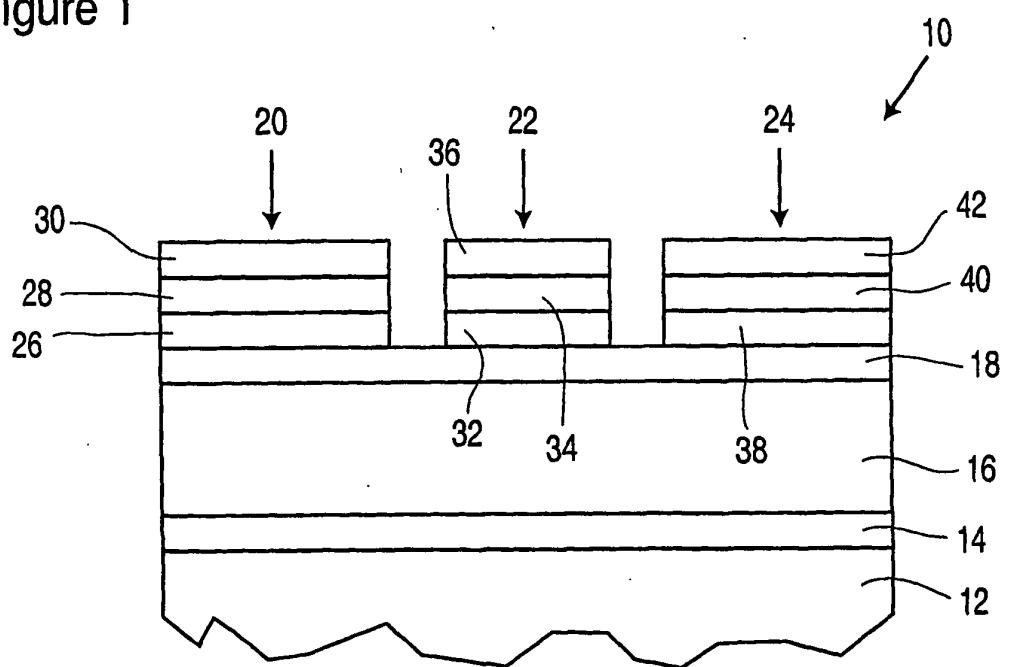

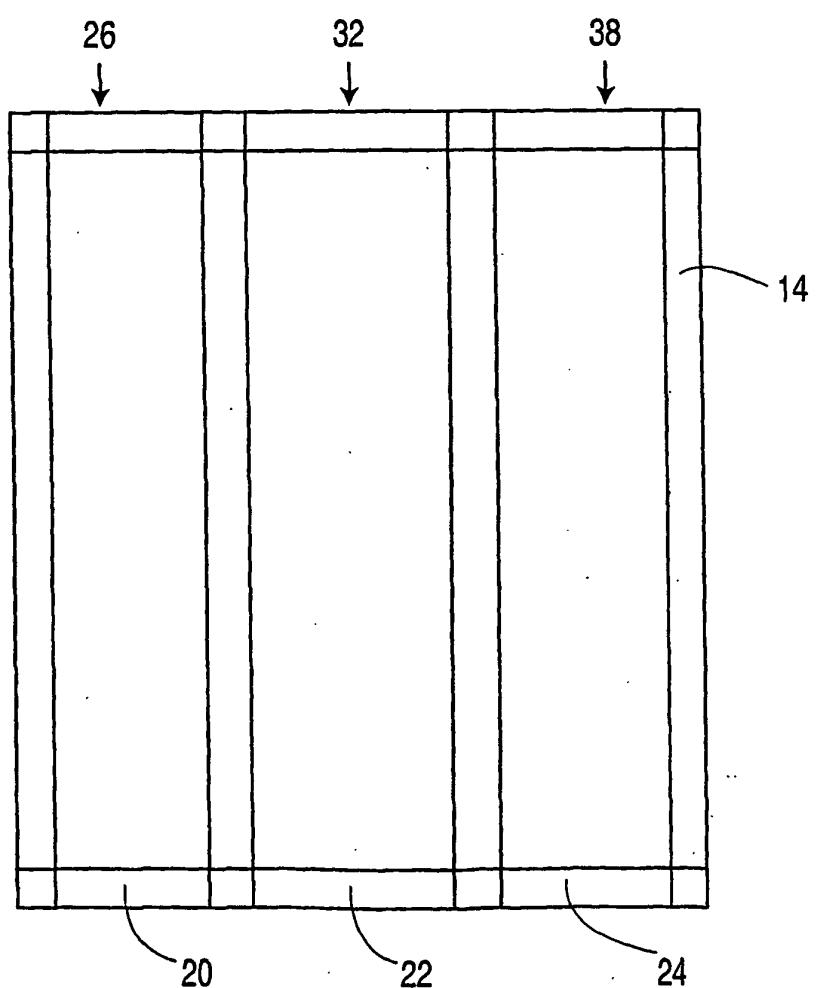

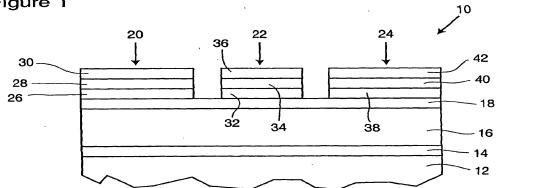

**[0020]** The present invention is illustrated by the embodiments shown in the drawings, in which:

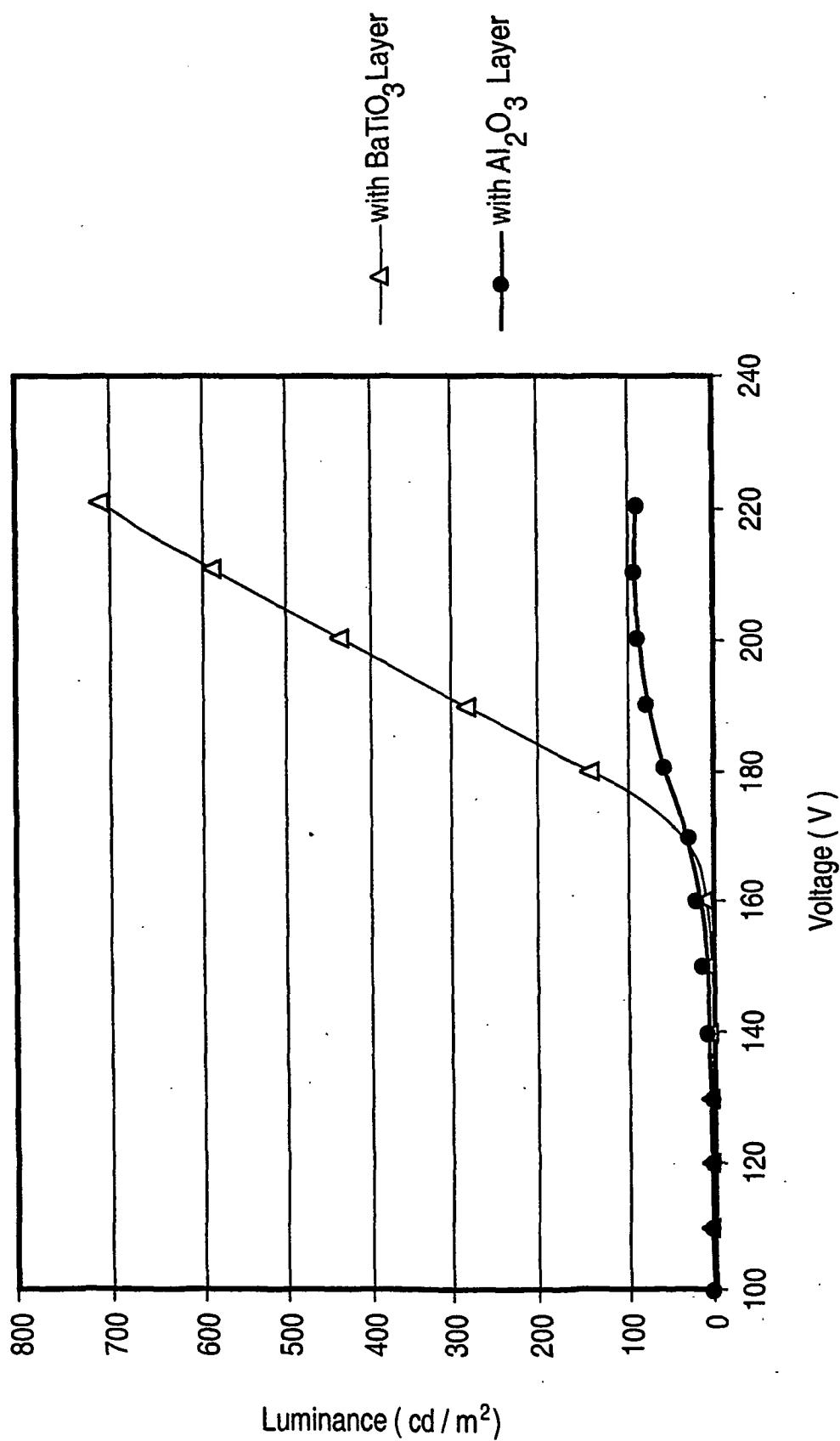

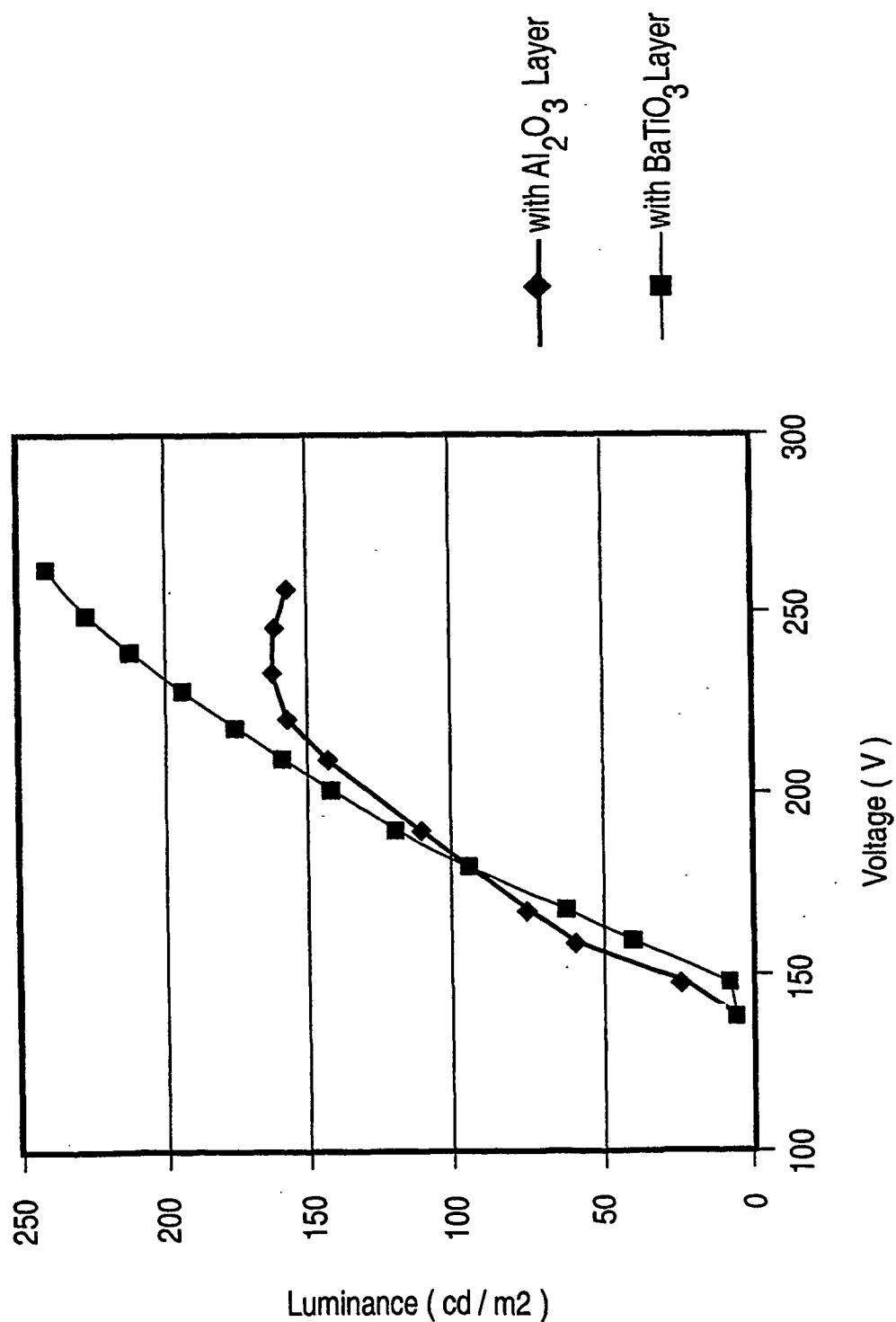

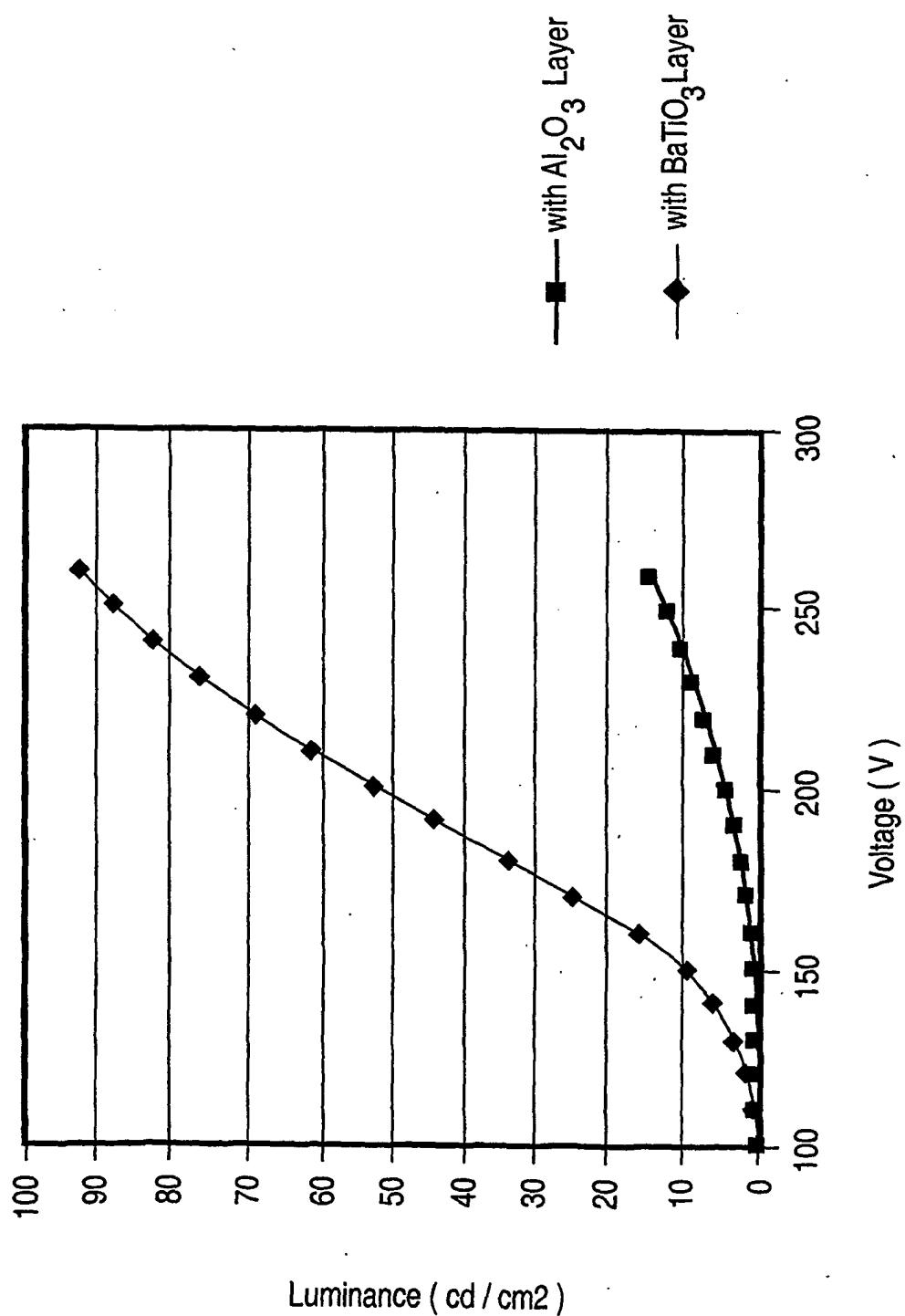

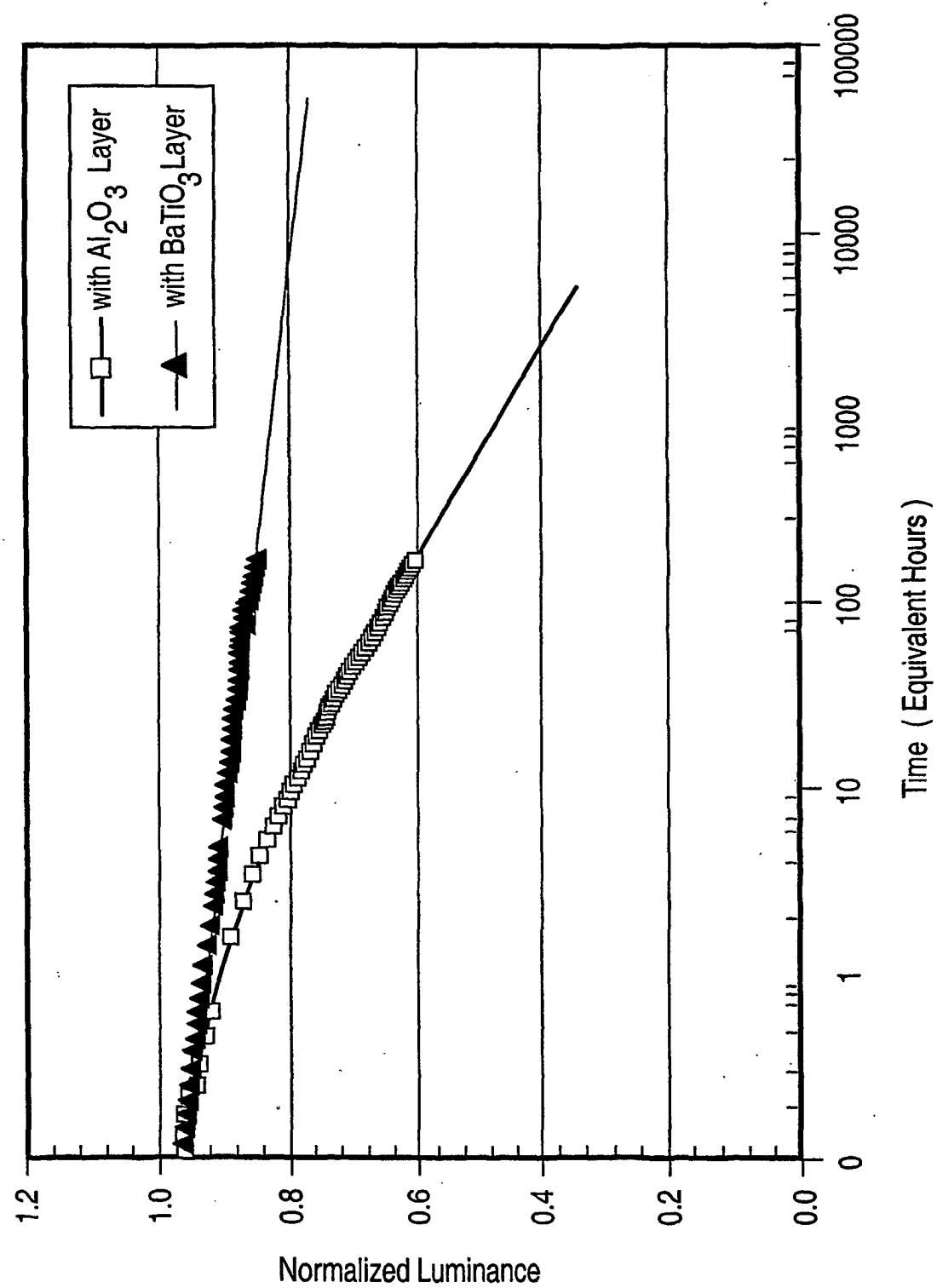

Fig. 1 is a schematic representation of a cross-section of an electroluminescent element of the prior art; Fig. 2 is a schematic representation of a plan view of an electroluminescent element of Fig. 1; Fig. 3 is a schematic representation of a cross-section of an electroluminescent element showing an insertion layer of the present invention; Fig. 4 is a graphical representation of luminance versus applied voltage for two thick film electroluminescent elements having a manganese-activated magnesium zinc sulphide phosphor film, with and without the insertion layer of the present invention; Fig. 5 is a graphical representation of luminance versus applied voltage for two thick film electroluminescent elements having a cerium-activated strontium sulphide phosphor film, with and without the insertion layer of the present invention; Fig. 6 is a graphical representation of luminance versus applied voltage for two thick film electroluminescent elements having a europium-activated barium thioaluminate phosphor film, with and without the insertion layer of the present invention; and Fig. 7 is a graphical representation of luminance ver-

sus operating time for two thick film electroluminescent displays having a manganese-activated zinc sulphide phosphor film, with and without the insertion layer of the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

**[0021]** The present invention relates to the insertion of a thin non-porous layer between the thick film dielectric layer and the phosphor layer in a thick film electroluminescent display. In the event that the thick film electroluminescent display has multiple phosphor layers, the thin non-porous layer is interposed between the thick film dielectric layer and the phosphor layer juxtaposed thereto.

**[0022]** The thin non-porous layer is comprised of a crystalline material that has a crystal structure that facilitates the formation of a permanent or electric field-induced dipole moment in the crystalline material. In particular, the crystalline material lacks a center of inversion symmetry, which facilitates the formation of the permanent or electric field-induced dipole moment. The thin non-porous layer, is inserted, or interposed, between the thick film dielectric layer and the phosphor layer, or the phosphor layer juxtaposed thereto, of the electroluminescent display for the purpose of improving luminance and operating stability. As described herein, the electroluminescent device may have one or more dielectric layers between the thick film dielectric layer and the phosphor layer, especially on the thick film dielectric layer. Such layers may act as smoothing layers on the thick film dielectric layer. The non-porous layer may be adjacent to any such layers.

**[0023]** The crystalline material may be ferroelectric as understood by the usual scientific definition of these terms as referenced for example on page 419 of C. Kittel, Introduction to Solid State Physics, third edition 1968 (J. Wiley & Sons, New York).

**[0024]** It is understood that the non-porous layer does not include materials through which certain deleterious atomic species may migrate, and in particular does not include materials such as lead titanate-zirconate (PZT) or PMN-PT. Such materials contain lead, which readily diffuses at high temperature e.g. during deposition or annealing of the phosphor. In addition, PZT and PMT-PT have tendencies to react with phosphors. An important reason for the use of a layer  $Al_2O_3$  in the prior art is to reduce chemical reaction and diffusion of lead.

**[0025]** In preferred embodiments of the present invention, the crystalline material of the non-porous layer has a relative dielectric constant that is greater than about 20, especially greater than about 50 and especially greater than about 100.

**[0026]** The crystalline material of the non-porous layer is  $BaTa_2O_6$ .

**[0027]** The non-porous crystalline layer may be 0.05 to 1.0 micrometers thick, and preferably 0.1 to 0.3 micrometers thick. Such thicknesses are significantly less

than the thicknesses of either the primary thick film dielectric layer or the overlying surface smoothing layer that is generally applied to the electroluminescent device as described herein. The thickness of the crystalline layer is limited in part by the sol gel or vacuum deposition processes used in deposition of the layer and in part by the relatively low dielectric constant of the material of the non-porous layer in comparison to the primary thick film dielectric material. The crystalline layer may serve the

purpose of thin film dielectric layers described herein and may replace one or more of them. As a result of the high dielectric constant of the crystalline layer relative to typical thin film dielectric materials, the layers can be made relatively thicker without suffering an unduly large voltage drop across the layer. This provides improved resistance to diffusion of atomic species across the layer.

**[0028]** It is understood that there may be an increased electric charge at the surfaces of the non-porous layer in the present invention relative to the electric charge that would be present if the layer was formed from for example alumina or silicon oxynitride. The latter have restive dielectric constants of less than 10, and have been used previously for the thin film dielectric layers in electroluminescent displays. It is understood that under the appropriate circumstances, the increased charge may increase the surface density of electrons injected into the phosphor, facilitating increased luminosity.

**[0029]** The improved resistance to diffusion of atomic species facilitates the use of higher phosphor annealing temperatures, a wider range of annealing atmospheres and longer annealing times. There may also be a reduction in degradation of the performance of the electroluminescent display during operation by inhibition of diffusion of atomic species from the thick film structure into the phosphor and adjacent thin film structures. In the absence of an appropriate barrier, such diffusion may be significant, even at ambient temperature, when electric fields are present within the display structure.

**[0030]** It is understood that the non-porous crystalline layer of the present invention must not react in an unfavourable manner with various chemical species that may come into contact with the non-porous layer during any of the various stages of fabrication of the electroluminescent display, subsequent to deposition of the non-porous layer. Such species include those in thin film dielectric layers that encapsulate phosphor films, the phosphor films per se, as well as photoresist materials and etchants used in photolithographic processes that may be associated with fabrication of the display. Thus, the composition of adjacent layers, the chemicals used in process steps subsequent to the deposition of the barium titanate layer and the process steps that are used must be selected to be compatible with the selected non-porous crystalline layer. In particular, the non-porous layer must be more stable with respect to phosphor materials than the thick film dielectric layer. Reactions of phosphor with the non-porous layer during phosphor deposition and phosphor annealing steps are to be avoided or mini-

mized. It is particularly preferred that there be no such reaction. PZT and PMN-PT do not meet such requirements because of chemical reactions with phosphors during deposition and annealing.

**[0031]** It is understood that a further requirement is that the non-porous layer must be adherent to the layers that it comes in contact with, i.e. the layers immediately below and above the non-porous layer in the display structure. Typically, one such layer is a high dielectric material such as lead zirconate-titanate (PZT), and the other such layer is a phosphor film or a thin film dielectric layer chosen to provide optimum electron injection into the phosphor. It is understood that the adherence of the layers is dependent on the interfacial surface tension between the materials of the adjacent layers, which is related to the strength of chemical bonding across the interface relative to the chemical bond strengths parallel to the interface. Thus, the composition of the layers in contact with the non-porous crystalline layer is chosen to facilitate adequate adhesion between these layers and the non-porous crystalline layer so that delamination of the layers does not occur during fabrication or operation of the display.

**[0032]** There may be factors in the ability of the non-porous crystalline layer of the present invention to impede diffusion of atomic species that are in addition to the increase in thickness of the layer due to its high dielectric constant. It is understood that transport of atomic species may occur via several mechanisms. In what is believed to be the order of decreasing importance, these are as follows: (a) Transport may occur through pinholes in the non-porous layer by vapour transport or surface diffusion. These are relatively rapid processes, and minimization of the number and size of pinholes in the layer is an important consideration. (b) Atomic diffusion may occur along grain boundaries, also at a relatively rapid rate, and minimization of the areal density of grain boundaries is desirable. (c) Transport may occur by bulk diffusion through the crystal lattice of individual grains, which occurs by atomic species hopping between vacancies in the crystal lattice or by hopping from one interstitial site to another. Typically, the process of hopping between vacancies occurs faster, since the vacancies will more readily accommodate hopping atoms. Diffusion between interstitial sites tends to be lowest for crystal lattices having a high atomic density, since these lattices have smaller interstices. Thus, the factors in the development of a good diffusion barrier include the crystal structure, as well as grain structure and morphology of the deposited film. Such factors may be used in selection of possible alternate diffusion barrier materials.

**[0033]** Although the inserted layer is described herein as "non-porous", it will be appreciated that a layer that completely inhibits transport of atomic species is unattainable in the context of the invention. The non-porous layer is understood to reduce or inhibit transport of atomic species, with the result of improved electroluminescent properties.

**[0034]** It is understood that an upper thin film dielectric

layer is typically applied onto the phosphor layer, followed by a layer of for example indium tin oxide. The thin film dielectric layer is typically aluminum oxide ( $Al_2O_3$ ). However, in an embodiment of the present invention, the upper thin film dielectric layer may also be a non-porous layer as described herein, especially barium titanate ( $BaTiO_3$ ).

**[0035]** Fig. 1 shows a cross-section of an electroluminescent device of the prior art. Fig. 2 shows a plan view of the same electroluminescent device. The electroluminescent device, generally indicated by 10, has a substrate 12 on which is located row electrode 14. Thick film dielectric 16 has thin film dielectric 18 thereon. Thin film dielectric 18 is shown with three pixel columns, referred to as 20, 22 and 24, located thereon. The pixel columns contain phosphors to provide the three basic colours viz. red, green and blue. Pixel column 20 has red phosphor 26 located in contact with thin film dielectric 18. Another thin film dielectric 28 is located on red phosphor 26, and column electrode 30 is located on thin film dielectric 28. Similarly, pixel column 22 has green phosphor 32 on thin film dielectric 18, with thin film dielectric 34 and column electrode 36 thereon. Pixel column 24 has blue phosphor 38 on thin film dielectric 18, with thin film dielectric 40 and column electrode 42 thereon.

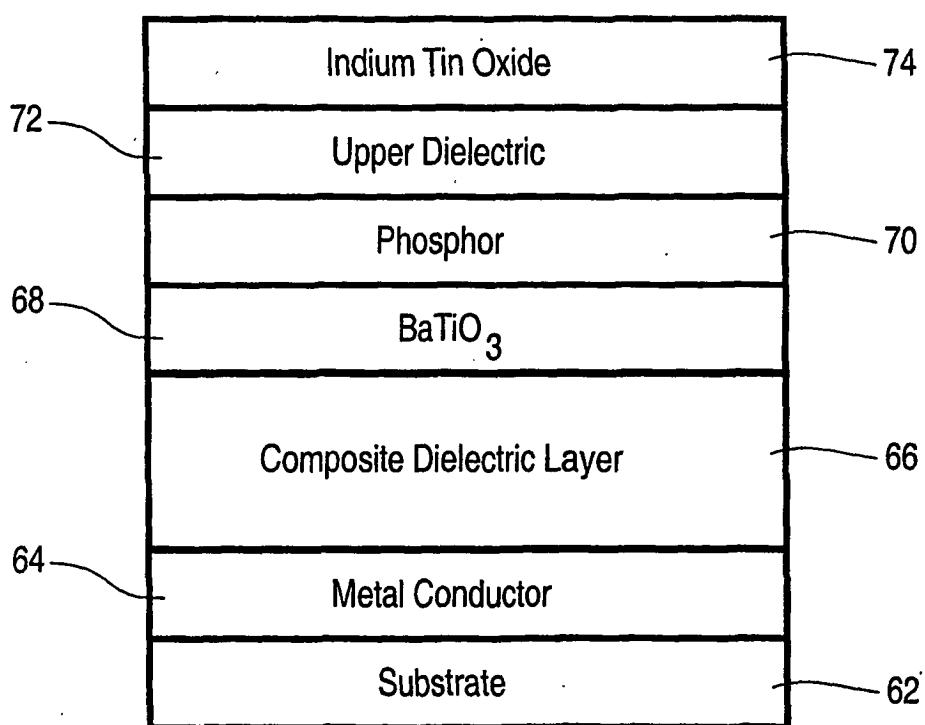

**[0036]** A particular embodiment of an electroluminescent device of the present invention is illustrated in Fig. 3. The electroluminescent device, generally indicated by 60, has a substrate 62 e.g. alumina, with a metal conductor layer 64 e.g. a gold conductor layer. Thick film dielectric layer 66, which may be PMT-PT, is located on metal conductor layer 64. A thin film dielectric layer e.g. lead zirconate-titanate, may be applied to thick film dielectric layer 66; this thin film dielectric layer is not shown in Fig. 3 but is exemplified in Example I.

**[0037]** The non-porous layer of the present invention, 68, is located on thick film dielectric layer 66. Phosphor 70 is located on non-porous layer 68. In the embodiment of Example I, phosphor 70 is of the nominal formula  $Mg_xZ_{1-x}S: Mn$  with  $x = 0.1$  and doped with 0.4 atomic percent manganese. An upper thin film dielectric layer 72, which is  $Al_2O_3$ , and then a layer of indium tin oxide 74, are located over phosphor 70.

**[0038]** The present invention relates to a novel structure for a thick film electroluminescent display element wherein a barium tantalate layer is interposed between the thick film and thin film structures of the element to provide enhanced luminosity and operating life.

**[0039]** The present invention is illustrated by the following examples. The examples describe the fabrication of and test results for electroluminescent elements incorporating a barium titanate layer fabricated using a sol gel process. It is understood that such a layer may be deposited by any means that enables the deposition of a conformal, largely pinhole-free layer.

**EXAMPLE I**

**[0040]** An electroluminescent element of the type generally shown in Fig. 3 was fabricated.

**[0041]** The electroluminescent element was formed on a 5 cm x 5 cm alumina substrate. A thick film layer structure comprising a gold conductor patterned to form a lower electrode connected to a contact was deposited on the substrate, followed by a composite dielectric layer comprising thick film dielectric layer screen printed and fired using PMN-PT based paste 98-42 from MRA of North Adams, MA, USA or CL-90-7239 from Heracul of W. Conshocken, PA, USA. Two layers of lead zirconium titanate (PZT) were then deposited onto the substrate by spin coating using a metal organic deposition process and firing. The method is disclosed in the aforementioned PCT patent application WO 00/70917.

**[0042]** A barium titanate layer was deposited on top of the PZT layer on the thick film structure using the following procedure. A barium titanate sol suspension (0.5M) in methoxypropanol was obtained as a prepared product. DRAT 150, from Gelest of Tullytown, PA, USA. As this suspension tends to have a very short shelf life in air, it was diluted with 2 parts by volume of methanol to 1 part of Gelest suspension to increase the working time in air. The diluted suspension was spin coated onto the thick film structure, and the resultant structure was then fired at a peak temperature of 700° C for 10 minutes in a belt furnace to form a barium titanate layer approximately 0.1 micrometer thick.

**[0043]** The barium titanate deposition process was repeated twice to increase the thickness of the barium titanate layer to 0.2 micrometers.

**[0044]** A 0.5 micrometer thick manganese-activated magnesium zinc sulphide phosphor film having the nominal formula  $Mg_xZn_{1-x}S: Mn$  with  $x = 0.1$  and doped with 0.4 atomic percent manganese was deposited on the barium titanate layer using electron beam evaporation. A 50 nanometer thick film of a thin upper dielectric film consisting of  $Al_2O_3$  was deposited on the phosphor film and finally an indium tin oxide layer was deposited on top and patterned to form a top electrode connected to a contact pad.

**[0045]** The entire assembly was covered by a sheet of glass, which was attached to the substrate using an epoxy perimeter seal to isolate the structure from moisture in the atmosphere, leaving the contact pads exposed for electrical connection.

**[0046]** The electroluminance of the completed device, which is a device of the present invention, was measured as a function of peak voltage for an applied 120 Hz bipolar square wave excitation voltage waveform.

**[0047]** A comparative device that was identical except that the barium titanate layer was replaced with a 50 nanometer thick layer of  $Al_2O_3$  was fabricated, and the electroluminance was measured.

**[0048]** The results are shown in Fig. 4.

**[0049]** As can be seen from the data, the devices of

the invention, with barium titanate layers, have a sharp threshold voltage for the onset of luminance and show a luminance of about 700 candelas per square meter at 200 volts. By contrast, the comparative devices without the barium titanate layer have a more gradual threshold and a luminance of only about 100 candelas per square meter at 200 volts. In addition, the devices with barium titanate show a linear dependence of luminance above the threshold voltage, thereby providing improved utility for gray scale control, compared with the devices without barium titanate which show a non-linear luminance dependence.

**EXAMPLE II**

**[0050]** An electroluminescent element similar to that of Example I was fabricated, except that a paste having PMN-PT from Ferro Corporation Niagara Falls, U.S.A. was used for the thick film structure in place of the MRA

20 paste and a 1.0 micrometer thick phosphor film comprising cerium-activated strontium sulphide with a cerium concentration of 0.3 atomic percent was used in place of the magnesium zinc sulfide phosphor film. Comparative devices having a 50 nanometer thick layer of  $Al_2O_3$  instead of barium titanate were also fabricated.

**[0051]** The results are shown in Fig. 5.

**[0052]** The test results on the devices of the invention with barium titanate layers, show improved luminance at 260 volts and 120 Hz over the comparative devices with a 50 nanometer thick  $Al_2O_3$  layer in place of the barium titanate layer. In addition, the luminance above the threshold voltage was linear with voltage for the devices of the invention, whereas luminance approached a constant value with increasing voltage for the devices without the barium titanate layer, giving the present invention improved utility for gray scale control.

**EXAMPLE III**

**[0053]** An electroluminescent element similar to that of Example II was fabricated, except that the phosphor film was a 150 nanometer thick film of europium-activated barium thioaluminate deposited according to the methods disclosed in WO-A-02/23957. This barium thioaluminate phosphor is a blue light-emitting phosphor. Comparative devices with a 200 nanometer thick layer of  $Al_2O_3$  in place of the barium titanate layer were also fabricated.

**[0054]** The results are shown in Fig. 6.

**[0055]** The measured luminance of the device of the invention with a barium titanate layer was about 80 candelas per square meter at 250 volts and 120 Hz. The luminance under the same test conditions for the comparative device with a 200 nanometer thick  $Al_2O_3$  layer in place of the barium titanate layer was about 10 candelas per square meter.

**EXAMPLE IV**

**[0056]** An electroluminescent element similar to that of Example I was fabricated, except that the phosphor comprised manganese-activated zinc sulphide rather than manganese-activated magnesium zinc sulphide. A comparative device was constructed with a 50 nanometer thick  $\text{Al}_2\text{O}_3$  layer in place of the barium titanate layer i.e. the device of the present invention.

**[0057]** Both devices were operated using a 200 volt 2.4 kilohertz bipolar square wave pulse and the luminance was measured as a function of operating time.

**[0058]** The results are shown in Fig. 7.

**[0059]** The relative luminance for the two devices is plotted versus operating time on a log scale at an assumed operating frequency of 120 Hz, it being assumed that the degradation rate for the luminance is proportional to the frequency of the applied voltage signal. As can be seen from Fig. 7, the luminance decreases far more slowly in the device with the barium titanate layer i.e. the device of the present invention.

**Claims**

1. In a thick film electroluminescent display (60) having a thick film dielectric layer (66) and phosphor layer (70), the improvement comprising:

an adherent non-porous layer (68) having a thickness of about 0.05 to 0.3  $\mu\text{m}$  interposed between the thick film dielectric layer (66) and the phosphor layer (70), said thin non-porous layer (68) comprising a crystalline material having a crystal structure with a permanent or electric-field induced dipole moment;

said thin non-porous layer (68) being chemically more stable and unreactive with respect to the phosphor layer (70) than the thick film dielectric layer (66);

said non-porous layer (68) exhibiting reduced diffusion characteristics to atomic species than the thick film dielectric layer (66); and

wherein the non-porous layer (68) is formed from  $\text{BaTa}_2\text{O}_6$

2. The thick film electroluminescent display (60) of claim 1 in which the crystal structure of said non-porous layer (68) does not have a centre of inversion symmetry.

3. The thick film electroluminescent display (60) of claim 1 in which the non-porous layer (68) is adjacent both the thick film dielectric layer (66) and the phosphor layer (70).

4. The thick film electroluminescent display (60) of claim 1 wherein said display further comprises 3 di-

electric smoothing layer on the thick film dielectric layer (66).

5. The thick film electroluminescent display (60) of claim 1 in which the non-porous layer (68) is ferroelectric.

10 6. The thick film electroluminescent display (60) of claim 1 in which the non-porous layer (68) has a relative dielectric constant of greater than 20.

15 7. The thick film electroluminescent display (60) of claim 6 in which the non-porous layer (68) has a relative dielectric constant of greater than 50.

20 8. The thick film electroluminescent display (60) of claim 6 in which the non-porous layer (68) has a relative dielectric constant of greater than 100.

25 9. The thick film electroluminescent display (60) of claim 6 in which a thin film dielectric layer (72) is applied on the phosphor layer (70).

30 10. The thick film electroluminescent display (60) of claim 9 in which the thin film dielectric layer (72) is  $\text{Al}_2\text{O}_3$ .

35 11. The thick film electroluminescent display (60) of claim 9 in which the thin film dielectric layer (72) is  $\text{BaTiO}_3$ .

40 12. The thick film electroluminescent display (60) of claim 16 in which a layer of indium tin oxide (74) is applied over the thin film dielectric layer (72).

**Patentansprüche**

1. In einer Elektrolumineszenz-Dickfilmvorrichtung (60) mit einer dielektrischen Dickfilmschicht (66) und einer Phosphorschicht (70), die Verbesserung, umfassend:

45 eine anhaftende, nicht-poröse Schicht (68) mit einer Dicke von etwa 0,05 bis 0,3  $\mu\text{m}$ , zwischen gelegt zwischen der dielektrischen Dickfilmschicht (66) und der Phosphorschicht (70), wobei die dünne nicht-poröse Schicht (68) ein kristallines Material mit einer Kristallstruktur mit einem permanenten oder durch ein elektrisches Feld induzierten Dipolmoment umfaßt,

50 55 wobei die dünne nicht-poröse Schicht (68) chemisch stabiler und unreaktiver bezüglich der Phosphorschicht (70) als die dielektrische Dickfilmschicht (66) ist,

wobei die nicht-poröse Schicht (68) verminderte Dif-

fusionseigenschaften bezüglich Atomspezies zeigt als die dielektrische Dickfilmschicht (66), und wobei die nicht-poröse Schicht (68) aus  $\text{BaTa}_2\text{O}_6$  gebildet ist.

2. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 1, worin die Kristallstruktur der nicht-porösen Schicht (68) kein Inversionssymmetriezentrum aufweist.

3. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 1, worin die nicht-poröse Schicht (68) sowohl an die dielektrische Dickfilmschicht (66) als auch die Phosphorschicht (70) angrenzend ist.

4. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 1, wobei die Vorrichtung weiter eine dielektrische Glättungsschicht auf der dielektrischen Dickfilmschicht (66) umfaßt.

5. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 1, worin die nicht-poröse Schicht (68) ferroelektrisch ist.

6. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 1, worin die nicht-poröse Schicht (68) eine relative Dielektrizitätskonstante von größer als 20 aufweist.

7. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 6, worin die nicht-poröse Schicht (68) eine relative Dielektrizitätskonstante von größer als 50 aufweist.

8. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 6, worin die nicht-poröse Schicht (68) eine relative Dielektrizitätskonstante von größer als 100 aufweist.

9. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 6, worin eine dielektrische Dünffilmschicht (72) auf der Phosphorschicht (70) angeordnet ist.

10. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 9, worin die dielektrische Dünffilmschicht (72)  $\text{Al}_2\text{O}_3$  ist.

11. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 9, worin die dielektrische Dünffilmschicht (72)  $\text{BaTiO}_3$  ist.

12. Elektrolumineszenz-Dickfilmvorrichtung (60) gemäß Anspruch 16, worin eine Schicht von Indium-Zinn-Oxid (74) über der dielektrischen Dünffilmschicht (72) angeordnet ist.

## Revendications

1. Dans un affichage électroluminescent à film épais (60) comprenant une couche diélectrique à film épais (66) et une couche de phosphore (70), perfectionnement comprenant :

une couche non poreuse adhésive (68) ayant une épaisseur d'environ 0,05 à 0,3  $\mu\text{m}$  intercalée entre la couche diélectrique à film épais (68) et la couche de phosphore (70), ladite couche non poreuse mince (68) comprenant un matériau cristallin ayant une structure de cristal à moment dipolaire permanent ou induit par un champ électrique ;

ladite couche non poreuse mince (68) étant chimiquement plus stable et non réactive par rapport à la couche de phosphore (70) que la couche diélectrique à film épais (66) ;

ladite couche non poreuse (68) possédant des caractéristiques de diffusion réduite d'espèces atomiques par rapport à la couche diélectrique à film épais (68) ; et

la couche non poreuse (68) étant constituée de  $\text{BaTa}_2\text{O}_8$ .

2. Affichage électroluminescent à film épais (60) selon la revendication 1, dans lequel la structure de cristal de ladite couche non poreuse (68) n'a pas de centre de symétrie d'inversion.

3. Affichage électroluminescent à film épais (60) selon la revendication 1, dans lequel la couche non poreuse (68) est adjacente à la fois à la couche diélectrique à film épais (66) et à la couche de phosphore (70).

4. Affichage électroluminescent à film épais (60) selon la revendication 1, dans lequel ledit affichage comprend, en outre, une couche de lissage diélectrique sur la couche diélectrique à film épais (66).

5. Affichage électroluminescent à film épais (60) selon la revendication 1, dans lequel la couche non poreuse (68) est ferroélectrique.

6. Affichage électroluminescent à film épais (60) selon la revendication 1, dans lequel la couche non poreuse (68) a une constante diélectrique relative supérieure à 20.

7. Affichage électroluminescent à film épais (60) selon la revendication 6, dans lequel la couche non poreuse (68) a une constante diélectrique relative supérieure à 50.

8. Affichage électroluminescent à film épais (60) selon la revendication 6, dans lequel la couche non poreuse (68) a une constante diélectrique relative supérieure à 100.

riéure à 100.

9. Affichage électroluminescent à film épais (60) selon la revendication 6, dans lequel une couche diélectrique à film mince (72) est appliquée sur la couche de phosphore (70). 5

10. Affichage électroluminescent à film épais (60) selon la revendication 9, dans lequel la couche diélectrique à film mince (72) est constituée de  $\text{Al}_2\text{O}_3$ . 10

11. Affichage électroluminescent à film épais (60) selon la revendication 9, dans lequel la couche diélectrique à film mince (72) est constituée de  $\text{BaTiO}_3$ . 15

12. Affichage électroluminescent à film épais (60) selon la revendication 9, dans lequel une couche d'oxyde d'indium-étain (71) est appliquée sur la couche diélectrique à film mince (72). 20

15

20

25

30

35

40

45

50

55

Figure 1

Figure 2

Figure 3

Figure 4

Figure 5

Figure 6

Figure 7

**REFERENCES CITED IN THE DESCRIPTION**

*This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.*

**Patent documents cited in the description**

- US 5432015 A [0005]

- WO 0070917 A [0005] [0007] [0041]

- US 5634835 A [0009]

- EP 1215946 A [0010]

- WO 0223957 A [0053]

**Non-patent literature cited in the description**

- **C. Kittel.** Introduction to Solid State Physics. J. Wiley & Sons, 1968, 419 [0023]

|                |                                                             |         |            |

|----------------|-------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于厚膜电致发光显示器的插入层                                             |         |            |

| 公开(公告)号        | <a href="#">EP1352545B1</a>                                 | 公开(公告)日 | 2009-06-17 |

| 申请号            | EP2002709927                                                | 申请日     | 2002-01-10 |

| [标]申请(专利权)人(译) | 伊菲雷技术公司                                                     |         |            |

| 申请(专利权)人(译)    | IFIRE TECHNOLOGY INC.                                       |         |            |

| 当前申请(专利权)人(译)  | IFIRE IP CORPORATION                                        |         |            |

| [标]发明人         | LI WU<br>XIN YONGBAO<br>WESTCOTT MICHAEL R                  |         |            |

| 发明人            | LI, WU<br>XIN, YONGBAO<br>WESTCOTT, MICHAEL, R.             |         |            |

| IPC分类号         | H05B33/22                                                   |         |            |

| CPC分类号         | H05B33/22 Y10S428/917 Y10T428/24942 Y10T428/2495 Y10T428/26 |         |            |

| 代理机构(译)        | CARPMAELS和兰斯福德                                              |         |            |

| 优先权            | 09/761971 2001-01-17 US                                     |         |            |

| 其他公开文献         | EP1352545A2                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                   |         |            |

#### 摘要(译)

通过在这些显示器中的厚膜介电层和薄膜磷光体结构之间插入的无孔层来增强厚膜电致发光显示器的性能和稳定性。插入层有助于提高亮度，提高能量效率和改善操作稳定性。

Figure 1

Figure 2