(12)

## DEMANDE DE BREVET EUROPEEN

(43) Date de publication:

17.09.2008 Bulletin 2008/38

(51) Int Cl.:

**H01L 27/32** (2006.01)      **G09G 3/32** (2006.01)

(21) Numéro de dépôt: 08102599.1

(22) Date de dépôt: 14.03.2008

(84) Etats contractants désignés:

**AT BE BG CH CY CZ DE DK EE ES FI FR GB GR**

**HR HU IE IS IT LI LT LU LV MC MT NL NO PL PT**

**RO SE SI SK TR**

Etats d'extension désignés:

**AL BA MK RS**

(30) Priorité: 16.03.2007 FR 0701929

(71) Demandeur: THALES

92200 Neuilly sur Seine (FR)

(72) Inventeurs:

**Kretz, Thierry**

38430 Saint Jean de Moirans (FR)

**Lebrun, Hugues**

38500 Coublevie (FR)

**Chuiton, Elisabeth**

38420 Revel (FR)

(74) Mandataire: **Esselin, Sophie et al**

**Marks & Clerk France**

31-33 Avenue Aristide Briand

94117 Arcueil Cedex (FR)

### (54) Matrice active d'un écran électroluminescent organique

(57) Dans une matrice active pour écran électroluminescent organique, chaque point image est安排 entre deux lignes de sélection qui commande chacune au moins un premier transistor de commutation T1, T1' des premier et deuxième circuits de commande COM et COM' de ce point image. Ces deux circuits sont disposés de façon symétrique par rapport à l'électrode pixel E1 du point image, chacun dans l'espace entre l'électrode pixel et une des lignes de sélection qui encadrent le point image. Les lignes de données sont chacune réalisées dans l'intervalle entre deux colonnes de points image successives, par tricotage au moyen de points de contact ct1, ct2 entre le niveau de métal source drain et le niveau de métal de grille, réalisant respectivement les électrodes source drain, et les grilles de transistors. Une électrode source drain des transistors de commande est formée par un bus d'alimentation Vdd réalisé sur le niveau métal source drain, et l'autre électrode source drain des transistors de commande est formée par au moins un doigt formé par excroissance de l'électrode pixel sur le même niveau métal source drain

Application aux matrices actives à transistors TFT notamment à canal en silicium amorphe.

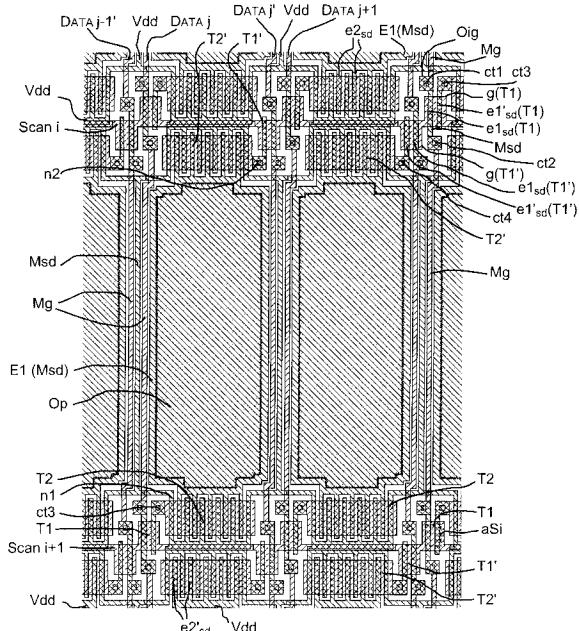

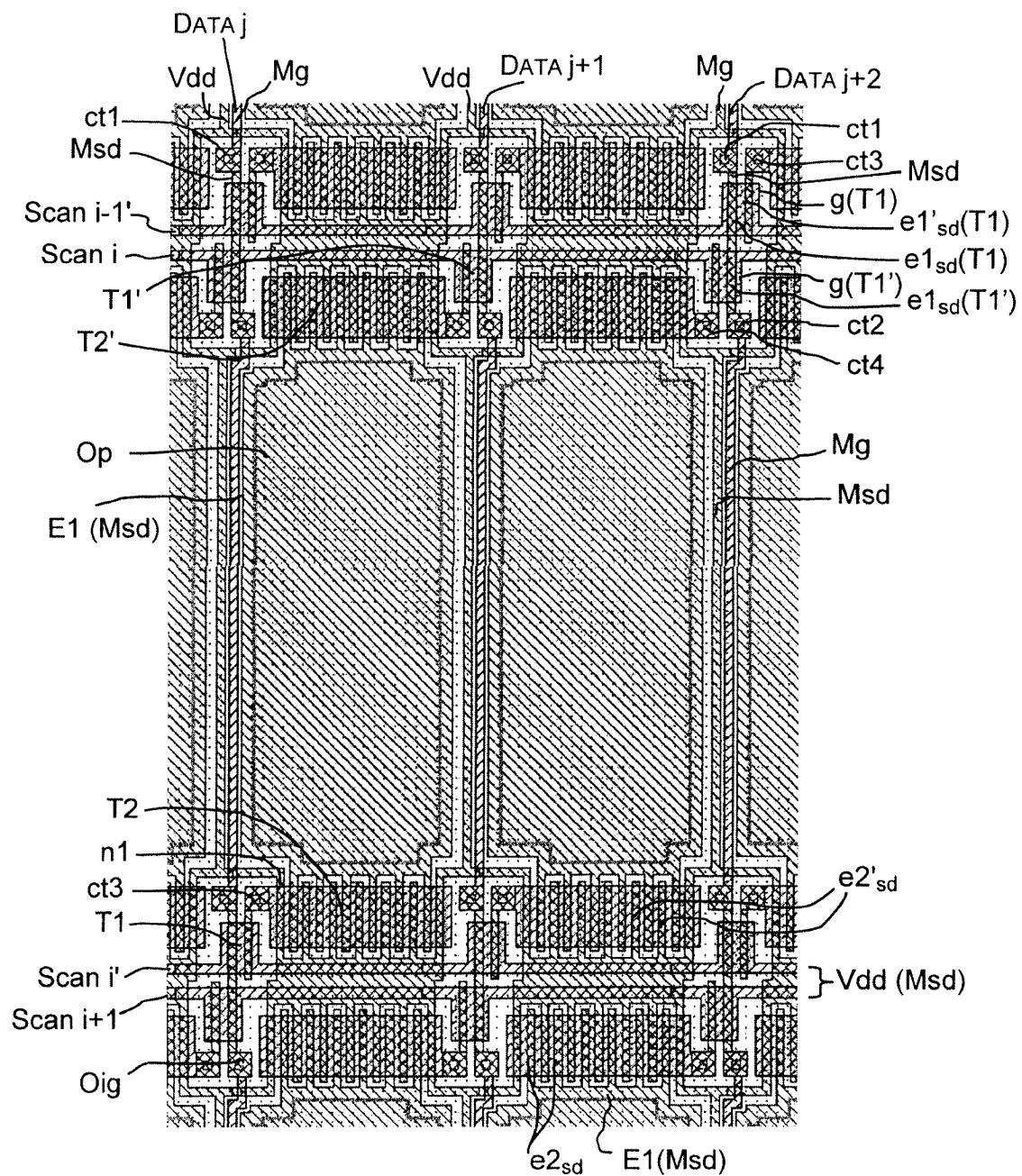

FIG.5

## Description

**[0001]** La présente invention concerne une matrice active pour écran électroluminescent organique, matrice AMOLED (*Active Matrix Organic Light Emitting Diode*), et plus particulièrement un arrangement des points image dans une telle matrice.

**[0002]** Dans un écran électroluminescent organique, l'élément image (pixel) est une structure à diode électroluminescente organique. Un tel écran ne nécessite pas de source de lumière additionnelle, contrairement à d'autres dispositifs d'affichage tels que les dispositifs dits LCD (*Liquid Crystal Display*). Il a comme autres avantages, de consommer peu, d'avoir une grande brillance, et des coûts de fabrication réduits. Le principe à la base de l'affichage de données vidéo par des diodes OLED est la modulation du courant de la diode. Ceci est obtenu par un transistor de commande en courant, qui reçoit sur sa grille une tension correspondant à la donnée vidéo à afficher et fournit un courant correspondant à la diode. En pratique, l'écran est ainsi constitué de deux substrats, typiquement l'un en verre supportant une matrice active avec les circuits de commande en courant et des électrodes pixels, une diode électroluminescente organique étant constituée sur chaque électrode pixel, entre chaque électrode pixel et un plan de tension de référence, l'autre en verre également scelle la zone contenant les diodes électroluminescentes ainsi que leurs électrodes en les isolant de l'eau et de l'air.

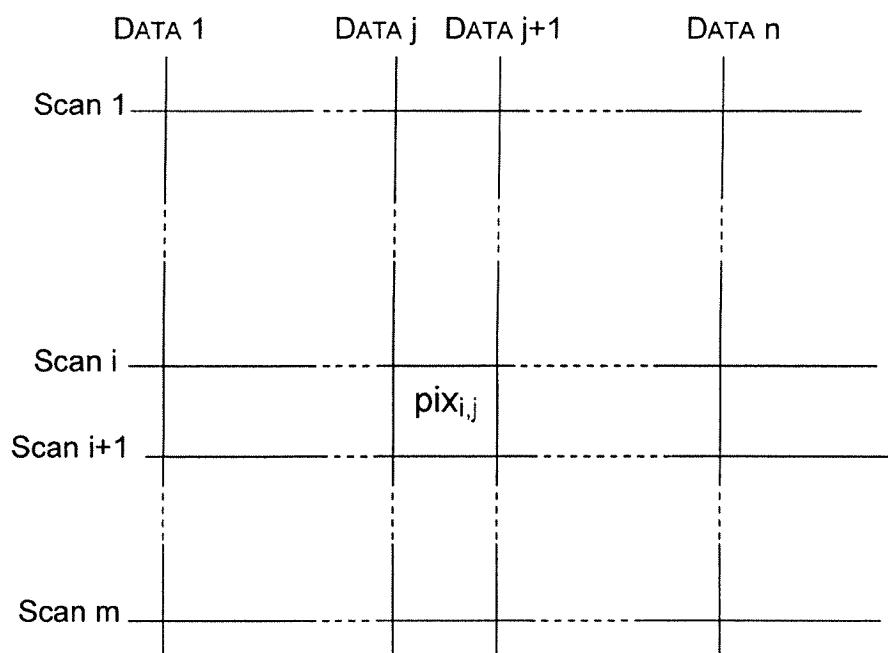

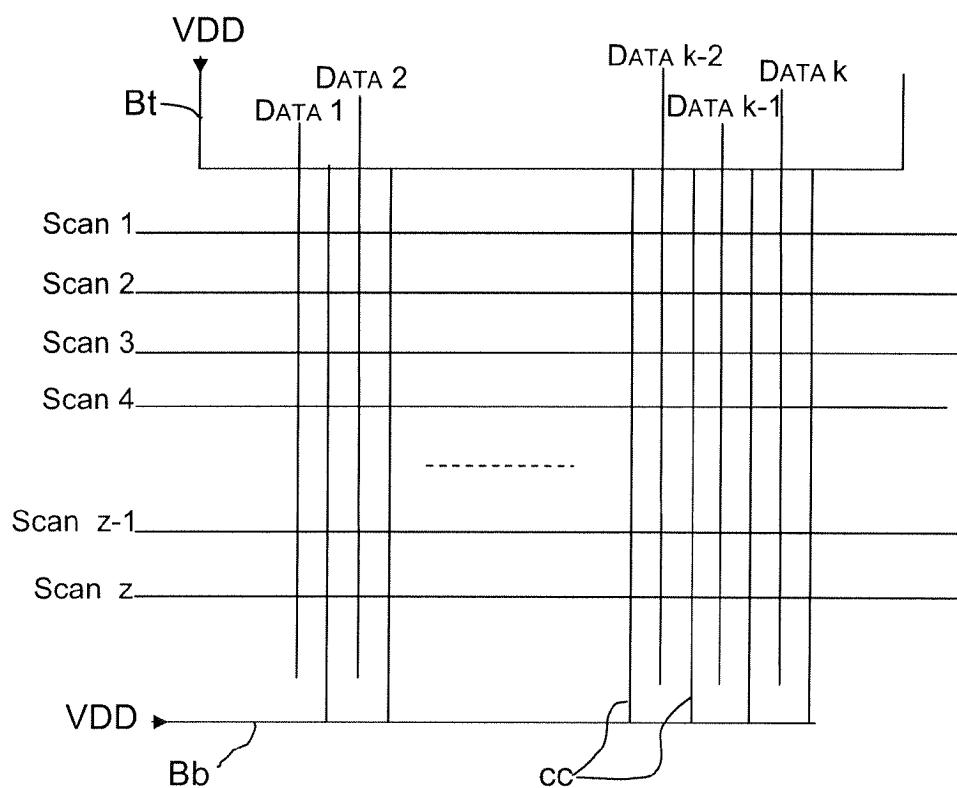

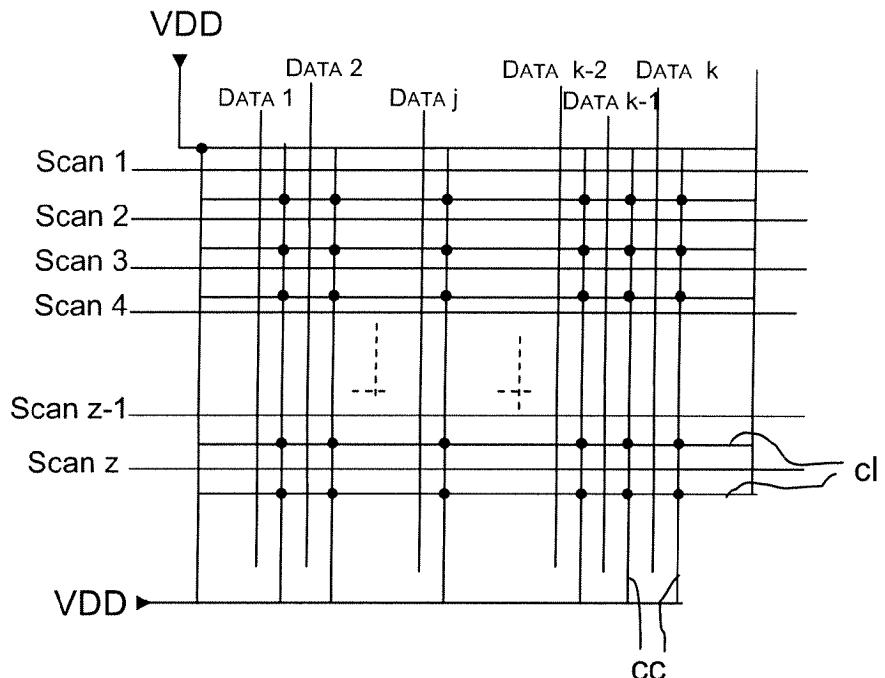

**[0003]** Comme illustré de façon schématique sur la figure 1, une matrice active d'un écran AMOLED comprend habituellement  $n \cdot m$  pixels  $\text{pix}_{i,j}$ ,  $i = 1 \text{ à } m$ ;  $j = 1 \text{ à } n$ ,  $m$  lignes de sélection Scan  $i$  et  $n$  colonnes Data  $j$  permettant d'adresser  $n$  pixels de l'écran. Par exemple le pixel  $\text{pix}_{i,j}$  peut être commandé pour afficher une information vidéo, au moyen de la colonne Data  $j$ , par laquelle est appliquée une tension correspondant à l'information vidéo à afficher et une ligne de sélection Scan  $i$ .

**[0004]** Dans l'invention, on s'intéresse à des structures de commande en courant d'un point image, ou pixel, particulières qui permettent de résoudre un problème connu de dégradation de l'affichage des écrans AMOLEDs dû à la dérive de la tension de seuil des transistors de commande en courant qui pilotent les diodes électroluminescentes organiques.

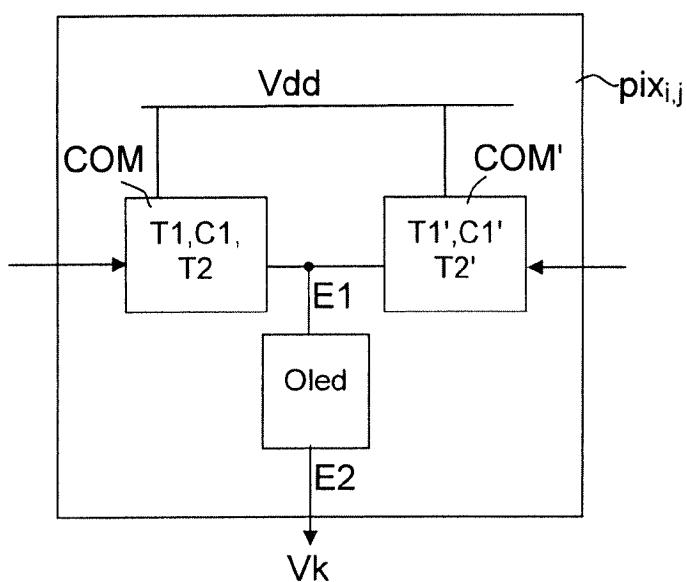

**[0005]** Ces structures permettent de ménager une phase de récupération de la dérive de la tension de seuil des transistors de commande en courant de chaque pixel au moyen d'une structure à deux circuits de commande en courant. Plus précisément, comme représenté en figure 2, chaque pixel  $\text{pix}_{i,j}$  comprend une structure à deux circuits de commande COM et COM' pour piloter la diode organique Oled du pixel. Ces deux circuits COM et COM' ont chacun une sortie qui commande une électrode E1 de la diode Oled, qui correspond à l'électrode pixel réalisée sur la matrice active, tandis que l'autre électrode E2 (cathode) de la diode qui correspond à la contre-électrode est reliée à un potentiel  $V_k$  commun à tous les

pixels.

**[0006]** Les circuits COM et COM' ont une structure identique, comprenant au moins : un transistor de commutation, un transistor de commande en courant et une capacité de maintien. Par convention, on note T1, C1 et T2 ces éléments du premier circuit référencé COM et T1', C1' et T2' ces éléments du deuxième circuit référencé COM'.

**[0007]** Les circuits COM et COM' sont commandés par des lignes de sélection et/ou de données de la matrice de telle sorte qu'ils aient une fonction différente à chaque trame vidéo, ces fonctions étant inversées périodiquement. Ces fonctions sont : 1.-afficher une information vidéo, par application d'une tension vidéo sur la grille du transistor de commande en courant, pour fournir un courant correspondant à la diode Oled et 2.-compenser le stress occasionné par la première fonction, par application d'une tension de blocage sur la grille du transistor de commande en courant.

**[0008]** Ainsi, pendant une trame vidéo donnée, l'un des deux circuits, par exemple le circuit COM, a la fonction d'afficher l'information vidéo via la diode Oled, par application d'une tension vidéo correspondante sur la grille de son transistor de commande en courant, T2, alors que l'autre circuit, dans l'exemple COM', a la fonction d'appliquer une tension de blocage sur la grille de son transistor de commande en courant, T2', ce qui met ce transistor en phase de récupération de la dérive de tension de seuil.

**[0009]** Les fonctions des deux circuits sont inversées périodiquement, en sorte qu'une trame sur deux en moyenne est mise à profit pour chaque circuit de commande pour destresser son transistor de commande en courant. La dérive moyenne de la tension de seuil de chaque transistor de commande en courant de la matrice active est nulle ou approximativement nulle. Ceci peut être obtenu sans affecter le rapport de cycle d'application de la tension vidéo sur la diode OLED, en sorte que la diode reste commandée en continu (rapport de cycle de 100%).

**[0010]** Pour commander les deux circuits COM et COM' de façon appropriée comme indiqué ci-dessus, des lignes et/ou des colonnes de la matrice sont utilisées, avec le cas échéant des lignes ou colonnes supplémentaires prévues spécialement, suivant la structure des circuits de commande. Plus précisément, dans un premier mode de réalisation, on a une structure de commande à quatre transistors, deux par circuit de commande COM, COM' (un transistor de commutation T1, T1' et un transistor de commande en courant T2, T2'), et des lignes ou des colonnes supplémentaires sont insérées dans la matrice pour les piloter de manière appropriée. Dans un autre mode de réalisation, on a une structure de commande à six transistors, trois par circuit de commande COM, COM' (deux transistors de commutation et un transistor de commande en courant), et des lignes de sélection des pixels précédente et suivante de la matrice sont utilisées en plus de la ligne et de la colonne de sélection

habituelles pour piloter les transistors des circuits de commande COM et COM' de manière appropriée.

**[0011]** Un problème technique qui se pose dans l'invention est comment augmenter le nombre de transistors par pixel et/ou le nombre de lignes ou colonnes nécessaires pour commander chaque pixel, tout en obttenant un taux d'ouverture optique pour une taille de pixel (et donc de matrice active) et un rendement de fabrication optimum.

**[0012]** Une solution apportée par l'invention à ce problème technique est un arrangement particulier des éléments de commande du point image et une topologie optimisée de matrice active correspondant à ces structures de commande des points images OLED avec les fonctionnalités souhaitées, et en particulier une topologie d'une matrice active pour écran AMOLED à 4 ou 6 transistors TFT par électrode pixel.

**[0013]** Telle que revendiquée l'invention concerne donc une matrice active pour un écran électroluminescent organique, comprenant des points images arrangés en lignes et en colonnes, comprenant chacun une électrode pixel apte à recevoir une diode électroluminescente organique en surface, et un premier et un deuxième circuits de commande en courant connectés à ladite électrode pixel, chaque premier circuit et chaque deuxième circuit comprenant un transistor de commande en courant connecté entre une tension d'alimentation Vdd et ladite électrode pixel et au moins un premier transistor de commutation pour commander la grille dudit transistor de commande en courant, ledit premier transistor de commutation étant connecté entre une ligne de donnée de la matrice et la grille dudit transistor de commande en courant, et ayant sa grille connectée à une ligne de sélection de la matrice, les électrodes de source ou drain des transistors de commutation et de commande et les électrodes pixel étant réalisées sur un niveau métal source drain, et les électrodes de grille de ces transistors étant chacune réalisées par une ligne de sélection de la matrice, sur un niveau métal de grille, caractérisé en ce que

- chaque point image est disposé entre deux lignes de sélection de la matrice, avec un circuit de commande disposé entre une première de ces deux lignes de sélection et son électrode pixel, ladite première ligne de sélection formant la grille du premier transistor de commutation de ce circuit de commande, et l'autre circuit de commande disposé entre une deuxième de ces deux lignes de sélection et l'électrode pixel, ladite deuxième ligne de sélection formant la grille du premier transistor de commutation de ce circuit de commande,

- une électrode source drain des transistors de commande est formée par un bus d'alimentation Vdd réalisé sur le niveau métal source drain, et l'autre électrode source drain des transistors de commande est formée par au moins un doigt qui est une excroissance de l'électrode pixel sur le même niveau métal

source drain;

- chaque ligne de données est disposée entre deux colonnes de points image de la matrice et formée en utilisant ledit niveau de métal source-drain et ledit niveau métal de grille, ledit niveau de métal de grille étant utilisé le long des électrodes pixel et ledit niveau de métal source drain étant utilisé dans les zones entre lesdites électrodes pixel où sont réalisés les transistors de commutation desdits circuits de commande.

**[0014]** Dans un mode de réalisation, pour une matrice dans laquelle les circuits de commande comprennent un deuxième transistor de commutation connecté entre la

ligne de sélection à laquelle est connectée la grille du premier transistor de commutation du circuit de commande considéré, et la grille dudit transistor de commande et dont la grille est connectée à une autre ligne de sélection, chaque ligne de sélection est dédoublée dans la zone active en une première branche et une deuxième branche disposées de part et d'autre d'une rangée correspondante de points image.

**[0015]** L'invention s'applique à des écrans à diodes organiques électroluminescentes comprenant une matrice active selon l'invention.

**[0016]** D'autres avantages et caractéristiques de l'invention sont détaillés dans la description suivante en référence aux dessins illustrés de modes de réalisation de l'invention, donnés à titre d'exemple non limitatif. Dans ces dessins :

- la figure 1 illustre de façon schématique une structure de matrice active OLED selon l'état de l'art;

- la figure 2 est un schéma de principe d'un point image OLED d'une matrice à laquelle s'applique l'invention;

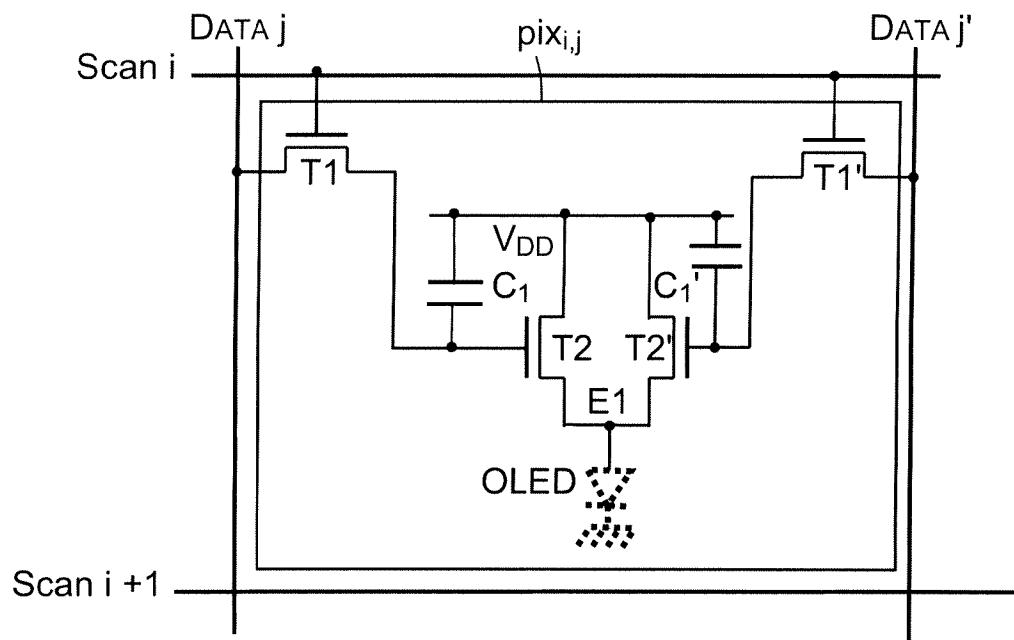

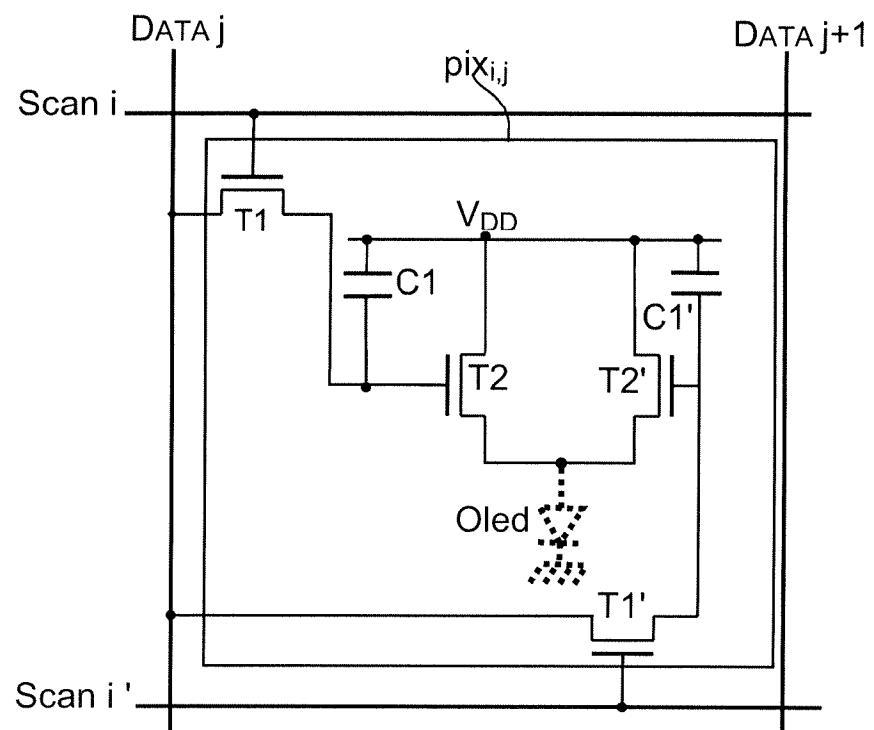

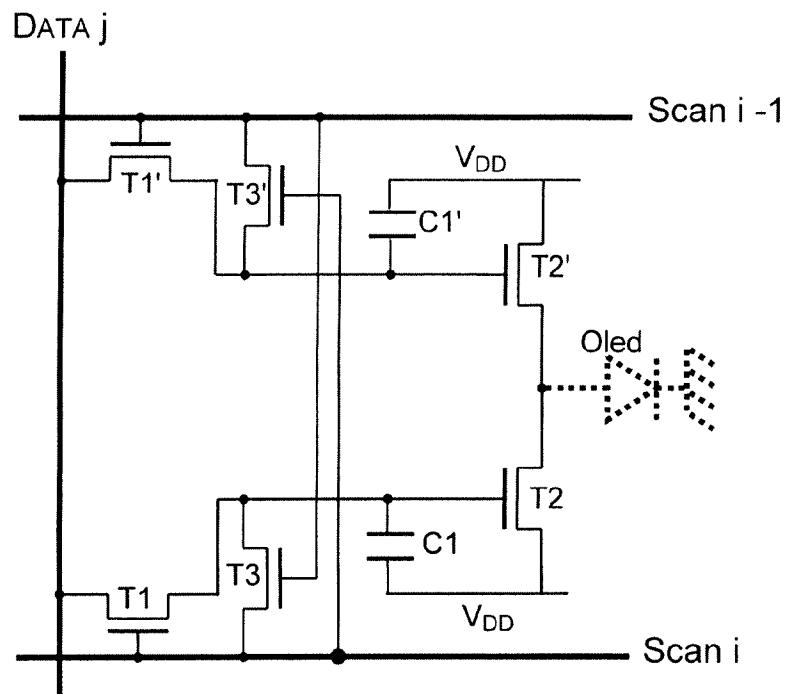

- la figure 3 illustre un schéma électrique équivalent d'une première structure d'élément image à diode OLED; et

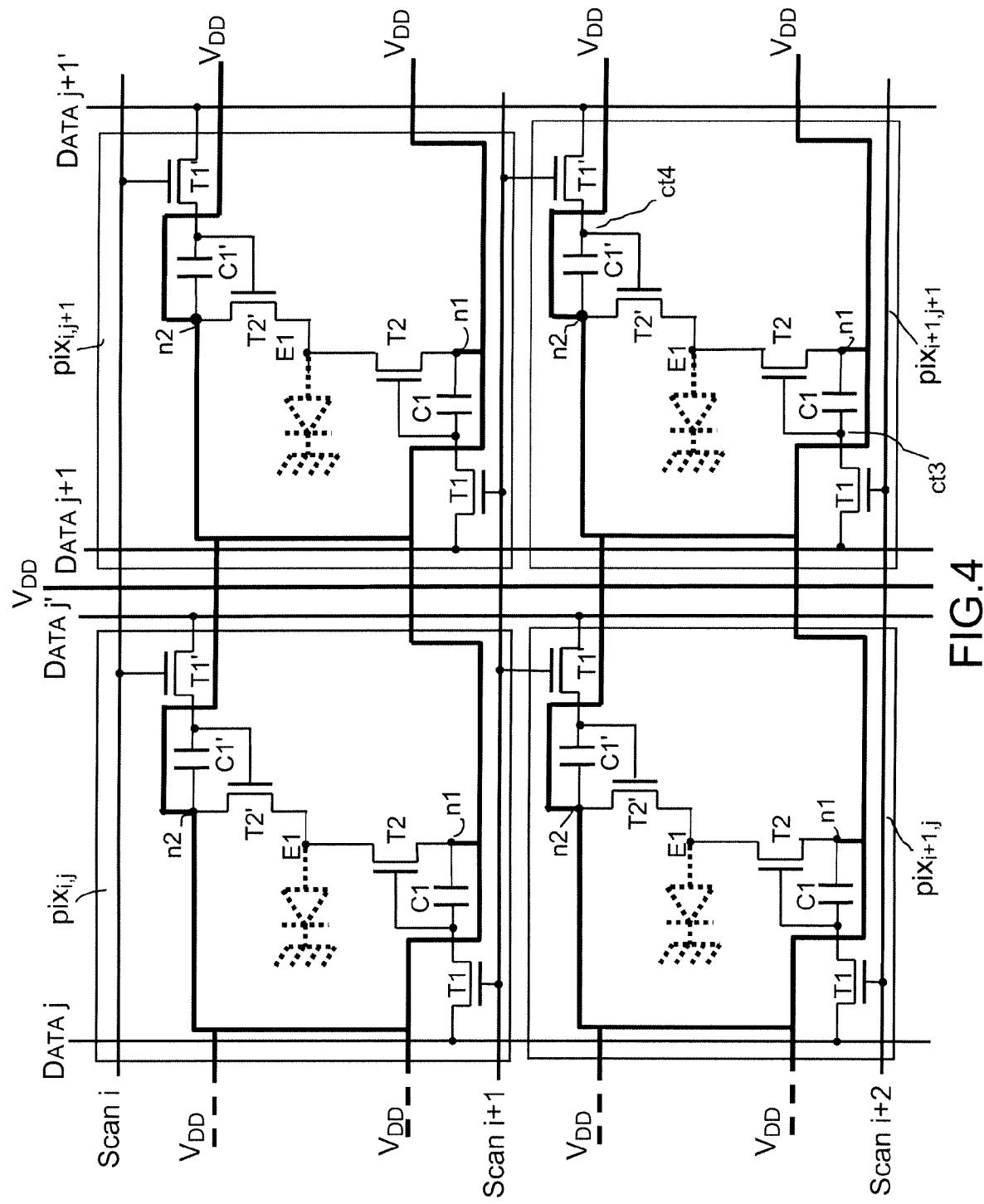

- les figures 4 et 5 illustrent une implémentation correspondante selon l'invention;

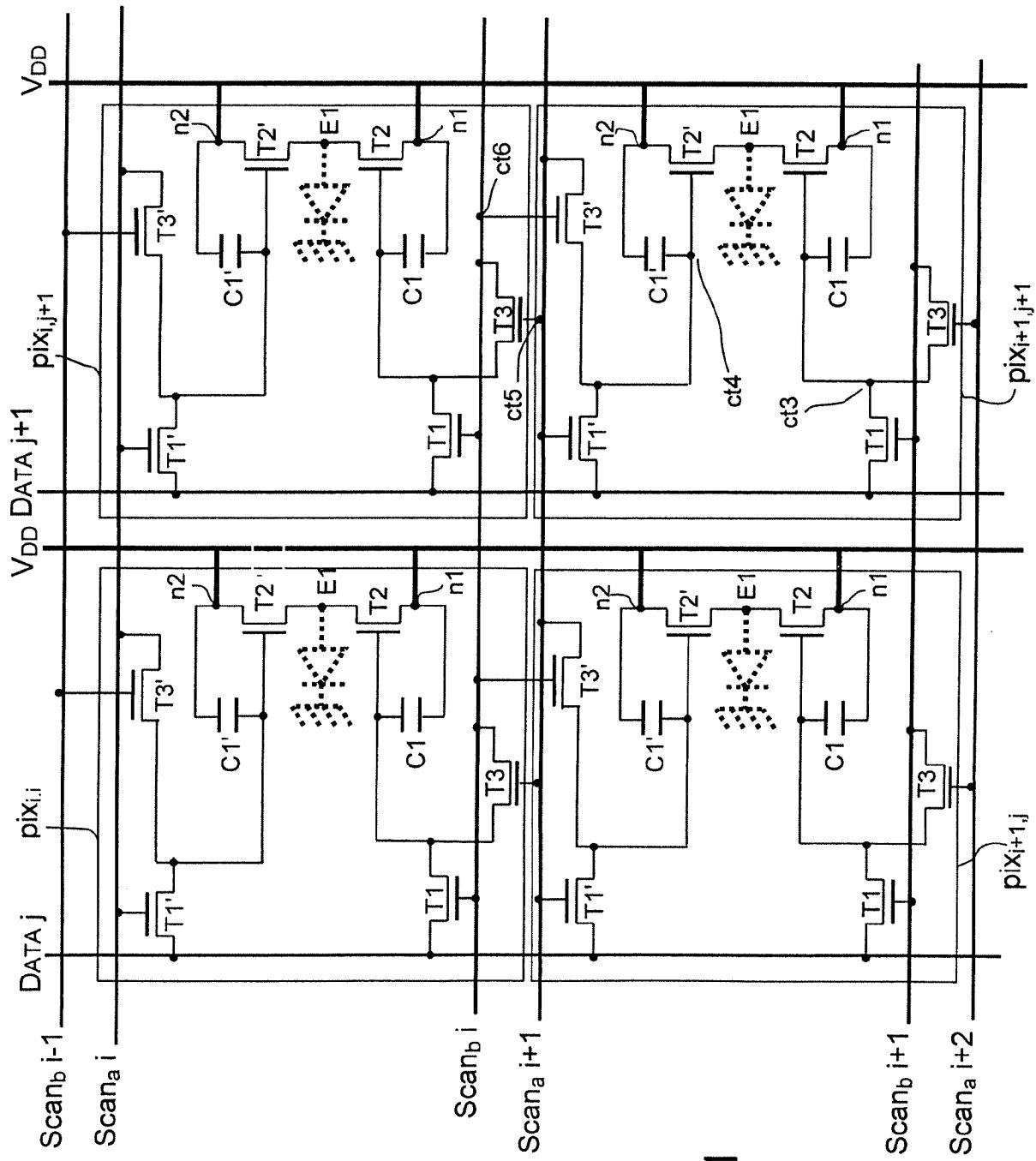

- la figure 6 illustre un schéma électrique équivalent d'une deuxième structure d'élément image à diode OLED;

- et les figures 7 et 8 illustrent une implémentation correspondante selon l'invention;

- la figure 9 illustre une troisième structure d'élément image à diode OLED selon un autre mode de réalisation selon l'invention; et

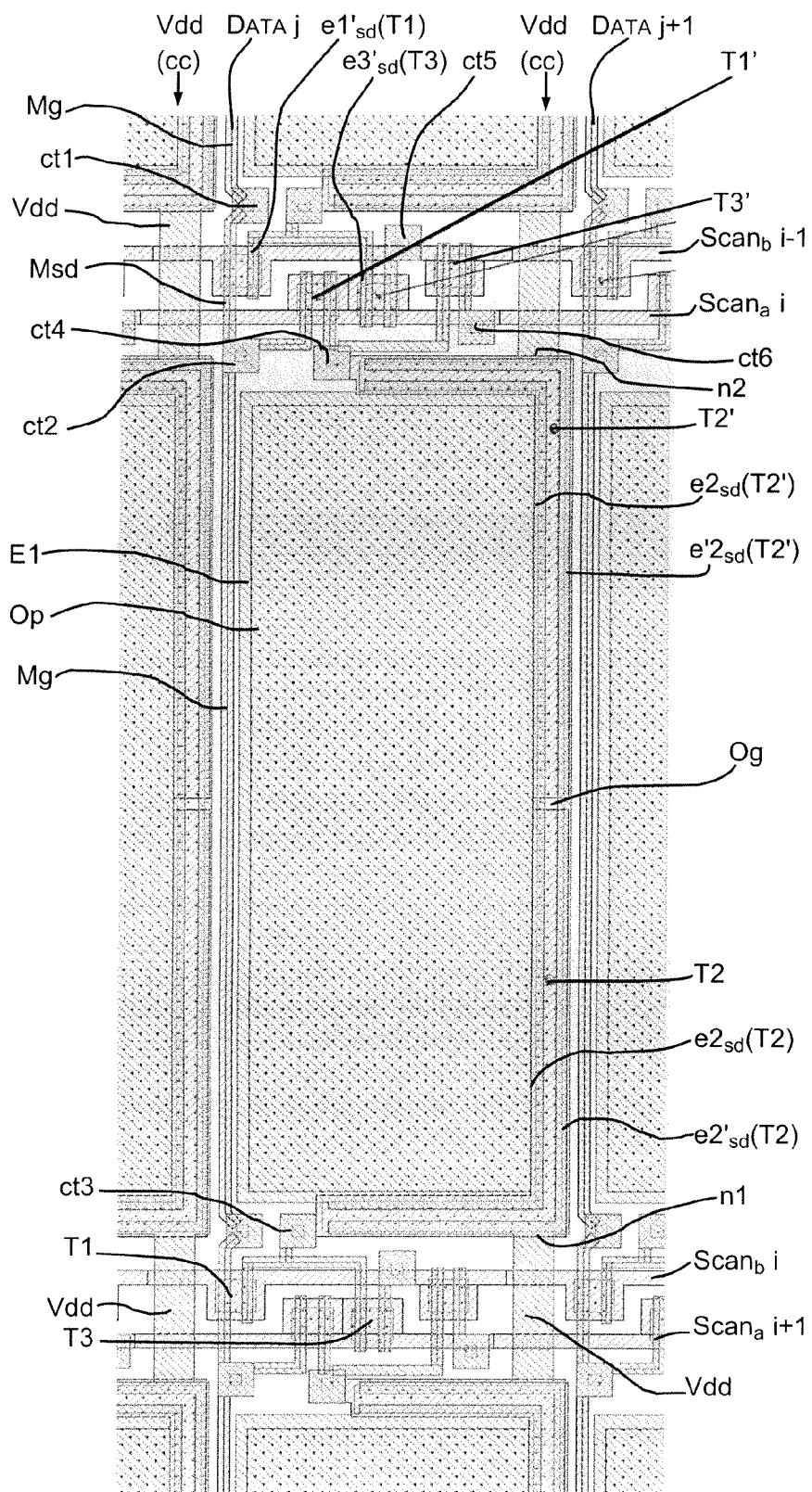

- les figures 10 à 12 illustrent une implémentation correspondante selon l'invention; et

- la figure 13 illustre le maillage de la tension Vdd applicable notamment aux figures 3 à 8 et la figure 14 une distribution du Vdd qui s'applique plus particulièrement aux figures 9 à 12.

**[0017]** Dans la description suivante trois structures de commande en courant à deux circuits COM ET COM'

sont présentées et pour chaque structure, un arrangement du point image et une implémentation correspondante de la matrice active, suivant l'invention sont expliqués.

**[0018]** Dans un souci de clarté et de simplification de l'exposé, les éléments communs aux différentes figures portent les même références.

**[0019]** On appelle lignes de sélection Scan i ou Scan i' les lignes qui commandent les grilles des transistors de commutation. Le prime signifie que la ligne est prévue dans la matrice en plus de la ligne de sélection habituelle.

**[0020]** On appelle lignes de donnée DATA j ou Data j' les lignes par lesquelles les tensions vidéo ou de blocage sont transmises aux transistors de commutation. Le signe prime signifie que la ligne est prévue dans la matrice en plus de la ligne de donnée habituelle.

**[0021]** On appelle indifféremment électrode source-drain d'un transistor Tk, les deux électrodes de part et d'autre du canal d'un transistor, leurs fonctions étant indifférenciées. Ces deux électrodes sont notées  $e_{k_{sd}}$  et  $e_{k'_{sd}}$ .

**[0022]** Les figures 3 et 6 sont deux exemples de schéma de connexion électrique d'une structure de commande à quatre transistors, deux par circuit de commande COM, COM'. Dans ce cas, chaque circuit de commande comprend deux transistors, un transistor de commutation T1, T1', et un transistor de commande en courant T2, T2'. Le transistor de commutation (T1, T1') est connecté entre une ligne de donnée et la grille du transistor de commande (T2, T2') et sa grille est connectée à une ligne de sélection, permettant d'appliquer une tension de commande (vidéo ou blocage) sur la grille du transistor de commande (T2, T2') quand le pixel est sélectionné. Le transistor de commande (T2, T2') est connecté en générateur de courant entre une tension d'alimentation Vdd et l'électrode E1 de commande de la diode Oled. La capacité de maintien (C1, C1') est connectée entre la grille du transistor de commande et la tension d'alimentation Vdd. On notera qu'il existe des variantes de connexion de la capacité de maintien. Par exemple, la capacité de maintien de l'un des circuits de commande pourrait être connectée à la ligne de sélection qui commande la grille du transistor de commutation de l'autre circuit de commande (non illustré).

**[0023]** La différence entre les deux structures tient dans la réalisation de l'adressage des transistors de commutation T1 et T1', pour commander de manière alternative la fonction d'affichage ou la fonction de récupération sur les circuits de commande associés COM et COM'.

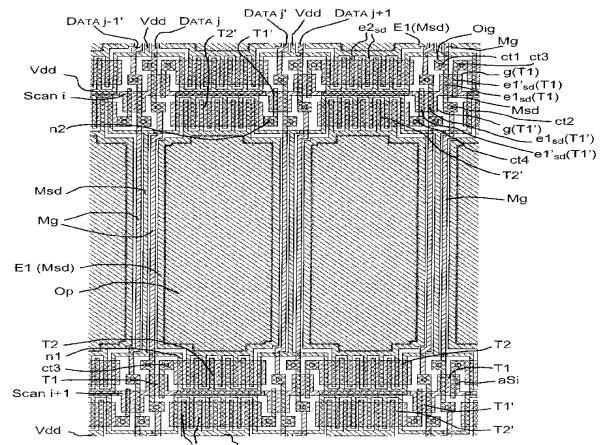

**[0024]** La figure 3 est un schéma électrique de principe qui illustre un premier mode de réalisation de cet adressage. La figure 4 est un schéma électrique correspondant à l'implémentation d'un point image correspondant selon l'invention et la figure 5 montre une implémentation topologique d'une matrice active correspondante.

**[0025]** Dans ce premier mode de réalisation, deux lignes de données par pixel sont prévues, et la commande

alternative en affichage vidéo et phase de récupération des deux transistors de commutation d'un point image  $\text{pix}_{i,j}$  utilise deux lignes de donnée DATA j et DATA j' associées au point image, chaque ligne de donnée recevant alternativement une tension vidéo et une tension de blocage, les grilles des transistors de commutation T1 et T1' étant pilotées par la ligne de sélection Scan i du point image. La première ligne de donnée DATA j est connectée au drain ou à la source du transistor de commutation T1 ; la deuxième ligne de donnée DATA j' est connectée au transistor de commutation T1'. Une matrice correspondante de n colonnes x m rangées de points image nécessite alors 2.n lignes de données, deux par colonne, et m lignes de sélection pour son adressage, soit n colonnes supplémentaires par rapport à une matrice habituelle. Elle comprend par ailleurs deux circuits de commande à 2 transistors chacun par point image.

**[0026]** Dans un arrangement selon l'invention, chaque point image  $\text{pix}_{i,j}$  est disposé entre deux lignes de sélection Scan i et Scan i+1, comme mis en évidence sur le schéma électrique de la figure 4 et le schéma topologique de la figure 5, avec une disposition symétrique des circuits COM et COM'. Cette disposition est facilitée par une modification de la commande des transistors de commutation T1 et T1' par rapport au schéma de la figure 3 : ces transistors sont commandés par deux lignes de sélection différentes de l'écran, Scan i et Scan i+1, plutôt que par la même ligne. Dans l'exemple, la grille du transistor de commutation T1' est pilotée par la ligne de sélection Scan i ; la grille du transistor de commutation T1 est pilotée par la ligne de sélection Scan i+1.

**[0027]** Cet arrangement présente avantageusement :

- une symétrie de la topologie au sein du point image  $\text{pix}_{i,j}$  par rapport à l'électrode pixel E1, chaque circuit de commande situé au plus près de la ligne de sélection qui le pilote, dans l'exemple Scan i pour le circuit COM' et Scan i+1 pour le circuit COM ;

- un positionnement symétrique des transistors T2 des points image d'une rangée par rapport aux transistors T2' (et vice versa) des points image de la rangée suivante (ou précédente) relativement à la ligne de sélection entre les deux rangées. Dans l'exemple les transistors T2 sont positionnés au-dessus de chaque ligne de sélection et les transistors T2' positionnés en dessous ;

- une disposition tête-bêche de part et d'autre d'une ligne de sélection du premier transistor de commutation du premier circuit de commande d'un point image avec le premier transistor de commutation d'un deuxième circuit de commande d'un autre point image. On a ainsi des couples de transistors T1, T1' disposés tête bêche par rapport à une ligne de sélection commune qui pilote ces deux transistors T1 et T1', comme par exemple le couple formé par le transistor T1 du point image  $\text{pix}_{i+1,j}$  et le transistor T1' du point image  $\text{pix}_{i,j+1}$  comme on peut le voir sur la figure 4, et comme mis en évidence dans la partie

en bas à droite du schéma topologique sur la figure 5. Ce positionnement tête-bêche par rapport à une ligne de sélection permet d'optimiser l'espace et donc favorise le taux d'ouverture optique. En effet, les lignes de sélection qui sont réalisées de manière habituelle en métal de grille Mg (typiquement du titane molybdène), ont un dessin adapté (figure 5) pour venir former les grilles g des transistors de commutation T1 et T1'. Et une électrode source de ces transistors est formée par la ligne de données associée, sans avoir à réaliser d'excroissance de cette ligne. L'espace est optimisé au mieux.

**[0028]** L'alimentation Vdd est avantageusement distribuée sur la matrice non pas seulement en colonne (ou seulement en ligne) mais suivant un maillage de conducteurs lignes/colonnes cl et cc en continuité électrique comme illustré sur la figure 13, qui permet d'amener Vdd sur les électrodes source/drain des transistors de commande en courant T2 et T2', aux noeuds n1 et n2 qui correspondent aussi chacun au noeud commun entre le transistor de commande en courant et le condensateur de maintien du circuit de commande correspondant. Cette distribution de l'alimentation Vdd se fait sans empiéter sur la zone de l'électrode pixel E1 sur laquelle est réalisée la diode Oled. Avec un tel maillage du bus d'alimentation Vdd, la résistance d'accès est faible et sensiblement la même pour tous les points image. Le maillage assure avantageusement une fonction de redondance en sorte que le rendement de fabrication de la matrice est bien meilleur : le maillage permet de garantir la distribution en courant pour tous les points image de la zone active même dans le cas de coupures qui peuvent se produire sur les colonnes ou les lignes d'alimentation dans le processus de fabrication. Le maillage permet d'atteindre tous les noeuds de connexion à Vdd (n1, n2) de la matrice tout en optimisant la zone optique disponible en chaque point image.

**[0029]** Le bus d'alimentation Vdd est typiquement réalisé sur le niveau de métal source-drain Msd de la matrice (typiquement du molybdène (Mo)). Il réalise ainsi naturellement une électrode source-drain des transistors T2 et T2' en s'étendant latéralement suivant les rangées de part et d'autre de chaque colonne d'alimentation Vdd, formant ainsi le maillage.

**[0030]** Le niveau de métal source-drain est aussi habituellement celui des lignes de données DATA j, DATA j' qui forment ainsi naturellement dans les électrodes source-drain des transistors de commutation T1, T1', par exemple l'électrode e1<sub>sd</sub> du transistor T1 (figure 5).

**[0031]** Entre deux colonnes de points images, on a ainsi trois conducteurs verticaux : un conducteur colonne d'alimentation Vdd et deux conducteurs colonne de lignes de données disposés par exemple de part et d'autre, DATA j' et DATA j+1.

**[0032]** Pour à la fois limiter les risques de court-circuit sur le niveau métal source-drain entre les conducteurs colonne coplanaires, et réaliser ces différents conduc-

teurs colonne de manière rapprochée de manière à favoriser l'ouverture optique, les lignes de données sont avantageusement réalisées en utilisant un procédé de tricotage entre deux niveaux métal de la matrice : le niveau métal source-drain Msd est utilisé uniquement dans la zone géographique des transistors, pour réaliser des électrodes source/drain e1<sub>sd</sub> des transistors de commutation T1 et T1'. Le niveau métal de grille Mg est utilisé partout ailleurs, et notamment le long des électrodes pixels E1, ce qui permet d'avoir la colonne d'alimentation Vdd et les lignes de données de part et d'autre très rapprochées. Pour les lignes de données, le passage entre les deux niveaux de métal Msd et Mg se fait typiquement au moyen de points de contacts ct1, ct2, obtenus par une ouverture Oig dans la couche d'isolant de grille, permettant au niveau de métal source-drain Msd de venir contacter en ces points le niveau de métal de grille.

**[0033]** L'autre électrode source-drain e1'<sub>sd</sub> des transistors de commutation T1, T1' en métal source drain est connectée à la grille du transistor de commande en courant associé T2 ou T2' en prévoyant une ouverture dans l'isolant de grille pour faire le contact (ct3).

**[0034]** Le maillage du bus d'alimentation Vdd permet de ne pas faire passer un conducteur en métal source drain Msd dans la zone entre les deux points de contacts ct1 et ct2 : le conducteur colonne Vdd en métal source drain Msd se dédouble de part et d'autre en conducteurs ligne d'alimentation avant ct1 pour former de chaque côté les électrodes source-drain e2<sub>sd</sub> et e2'<sub>sd</sub> des transistors T2 et T2' qui se font face symétriquement par rapport à la ligne de sélection, et se réunifie de l'autre côté après ct2. En d'autres termes le maillage Vdd est réalisé de manière à détourer chacun des couples de transistors T1 et T1' tête-bêche. De cette façon l'ouverture optique est optimisée sans rien sacrifier à la fiabilité du procédé de fabrication et au rendement de fabrication.

**[0035]** L'électrode pixel E1 est typiquement réalisée sur le niveau de métal source/drain Msd (figure 5). Une ouverture Op est réalisée dans la couche de passivation de la matrice pour dégager une zone de contact sur cette électrode E1, c'est à dire la zone optique du point image sur laquelle viendra se "poser" la diode électroluminescente organique.

**[0036]** Pour optimiser la surface occupée par les transistors de commande en courant, qui doivent avoir un dimensionnement de la largeur W du canal suffisamment important pour fournir le courant nécessaire aux diodes Oled, ces transistors T2, T2' ont avantageusement une topologie dite à électrodes source-drain interdigitées comme illustré sur la figure 5, ce qui permet d'obtenir le rapport désiré dans un minimum de largeur (en considérant la largeur dans le sens des lignes de sélection), et donc sans dégrader le taux d'ouverture optique du point image. Plus précisément, une électrode source-drain e2<sub>sd</sub> de ces transistors est formée par des excroissances (des doigts) de l'électrode pixel E1 (métal source-drain Msd), tandis que l'autre électrode source-drain e2'<sub>sd</sub> est formé par des excroissances partant du bus d'alimenta-

tion Vdd. Le positionnement symétrique de deux transistors T2 et T2' par rapport à chaque ligne de sélection permet de réaliser une électrode correspondante  $e_{2_{sd}}$  dans chacun de ces deux transistors à partir de la même portion de conducteur ligne d'alimentation Vdd. On notera qu'à cet endroit le conducteur d'alimentation Vdd (en métal Msd) est situé sur la ligne de sélection en métal de grille Mg, en sorte que l'on a une gestion optimum de l'espace occupé. En outre cette implémentation avec une pluralité de doigts d'électrodes permet de limiter les problèmes de défectuosité de points images en cas de coupure au niveau d'un doigt, par rapport à des implantations à doigts uniques.

**[0037]** Entre deux colonnes d'éléments image, on trouve ainsi deux conducteurs colonne de lignes de données, par exemple DATA j' et DATA j+1 encadrant de part et d'autre un conducteur colonne d'alimentation Vdd.

**[0038]** L'arrangement selon l'invention permet notamment d'optimiser la surface occupée par un point image à quatre transistors, avec un taux d'ouverture optique intéressant.

**[0039]** Les transistors sont typiquement des transistors à couche mince TFT, de préférence en silicium amorphe : le canal de ces transistors est réalisé en silicium amorphe aSi, entre les électrodes source-drain (niveau Msd) et commandé par la grille (sur le niveau Mg) comme plus particulièrement mis en évidence sur un des transistors de la figure 5.

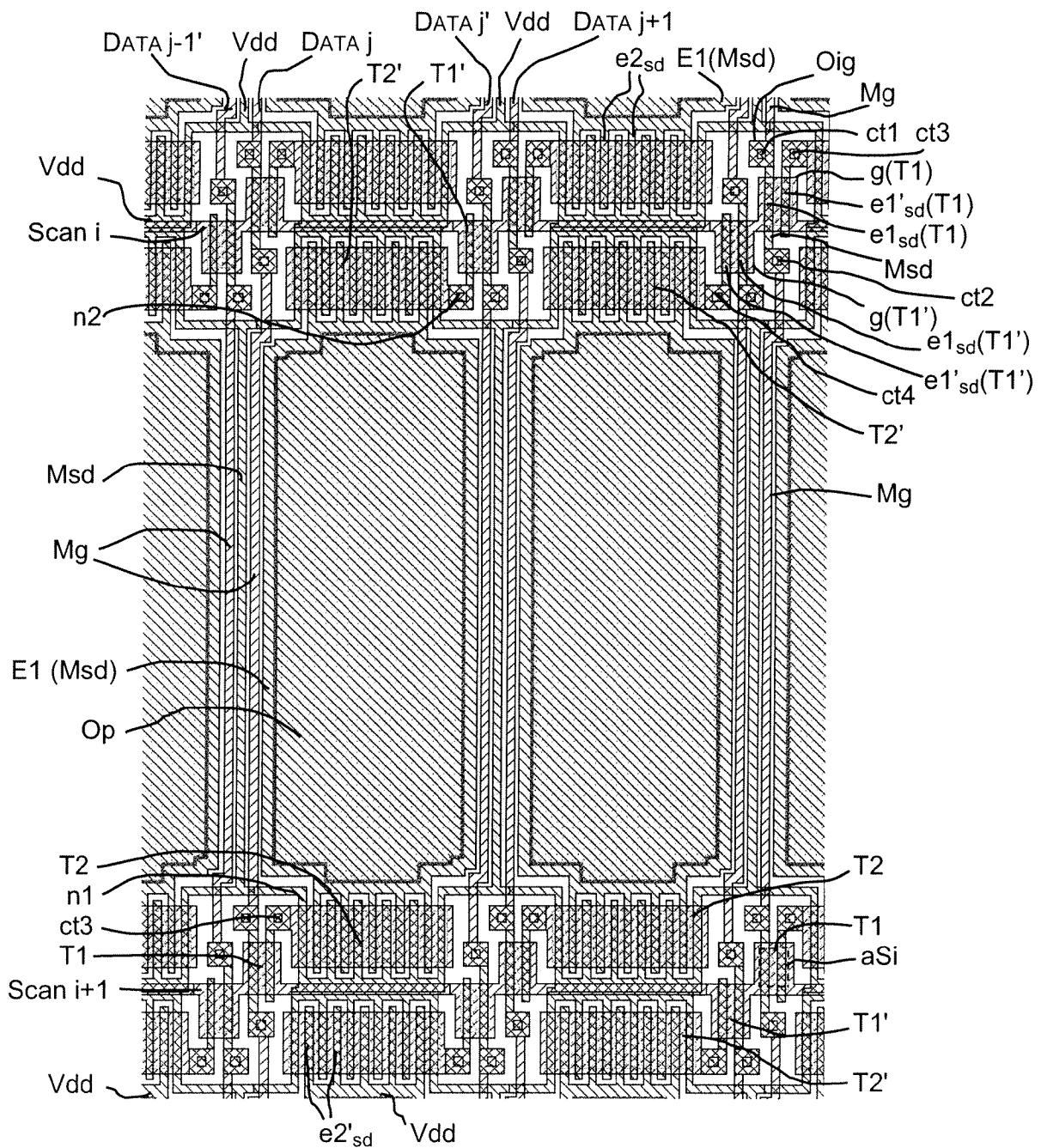

**[0040]** La figure 6 est un schéma électrique de principe qui illustre un autre mode de réalisation de l'adressage des transistors de commutation T1 et T1' d'une structure de commande à quatre transistors, pour commander de manière alternative la fonction d'affichage ou la fonction de récupération sur les circuits de commande associés COM et COM'. La figure 7 est un schéma électrique correspondant à une implémentation d'un point image correspondant selon l'invention et la figure 8 montre une implémentation topologique d'une matrice active correspondante.

**[0041]** Au lieu d'insérer des lignes de données supplémentaires pour permettre l'alternance des fonctions d'affichage et de récupération des circuits de commande COM et COM' comme dans la figure 3, on utilise les lignes de sélection : au lieu de doubler le nombre de lignes de données, on double les lignes de sélection. Une matrice correspondante comprendra alors 2.m lignes de sélection, deux par pixel, et n lignes de données associées aux m.n pixels  $\text{pix}_{i,j}$  de l'écran.

**[0042]** Dans ce mode de réalisation, la grille du transistor de commutation T1 est connectée à la ligne de sélection Scan i du pixel  $\text{pix}_{i,j}$ , et la grille du transistor de commutation dual T1' est connectée à une autre ligne de sélection que l'on note Scan i'. Comme illustré sur la figure 8, la même ligne de données, par exemple Data j+2, est connectée à une électrode source-drain  $e_{1_{sd}}$  de tous les transistors T1 des points image de la colonne à droite de cette ligne et à une électrode source-drain  $e'_{1_{sd}}$  de tous les transistors T1' des points image de la colonne

à gauche de cette ligne.

**[0043]** Sur le plan de l'arrangement et de la topologie de la matrice, tout ce qui a été décrit précédemment en relation avec les figures 3 à 6 s'applique de la même manière, puisque dans les deux cas chaque point image est encadré par deux lignes de sélection qui commandent chacune un des transistors de commutation (T1, T1') de ce point image. Mais l'espace nécessaire pour la réalisation des points image est plus intéressant ici, car on a seulement un conducteur d'alimentation et une ligne de données entre deux colonnes de points image.

**[0044]** En outre le positionnement tête-bêche des deux transistors T1 et T1' associés à la même ligne de données et à la même ligne de sélection permet alors de réaliser l'électrode source drain  $e_{1_{sd}}$  de ces deux transistors T1 et T1' avec le même conducteur de ligne de donnée, c'est à dire la partie de métal source-drain Msd entre les deux contacts ct1 et ct2, sans avoir à en adapter le dessin. L'espace est ainsi optimisé au mieux.

**[0045]** La figure 9 illustre un schéma de principe d'un point image Oled avec une structure de commande à six transistors, trois par circuit de commande COM. L'intérêt d'une telle structure est de ne pas nécessiter de lignes de sélection ou de données supplémentaires pour commander les fonctions d'affichage vidéo et de récupération en alternance sur les circuits de commande COM et COM'. On a donc pour un écran de n.m points images, m lignes de sélection Scan i et n lignes de données DATA j comme dans l'état de l'art (Figure 1).

**[0046]** Ceci est un avantage précieux en termes de topologie de circuit (croisement de lignes, commande des lignes) et d'espace occupé. Ceci est obtenu en prévoyant un transistor de commutation supplémentaire par lequel on va assurer la commande alternée des transistors de commande en courant. On note T3 pour le circuit COM et T3' pour le circuit COM' ce transistor de commutation supplémentaire du circuit de commande. Dans la suite on désigne par premier transistor de commutation les transistors T1 et T1' et par deuxième transistor de commutation les transistors T3 et T3'.

**[0047]** Comme illustré sur les figures 8 et 9, pour chaque point image  $\text{pix}_{i,j}$  on a une seule ligne de donnée DATA j qui est connectée aux premiers transistors de commutation T1 et T1' des deux circuits de commande COM et COM', une première ligne de sélection à laquelle est connectée la grille du premier transistor de commutation de l'un des circuits de commande et une autre ligne de sélection de la matrice, de préférence la ligne précédente, à laquelle est connectée la grille du premier transistor de commutation de l'autre circuit de commande. Dans l'exemple, pour le point image  $\text{pix}_{i,j}$ , la ligne de sélection Scan i est connectée à la grille du transistor de commutation T1 du circuit COM, la ligne de sélection Scan i-1 est connectée à la grille du transistor de commutation T1' du circuit COM'. Les éléments T1, C1 et T2 du circuit COM et T1', C1' et T2' du circuit COM' sont par ailleurs connectés entre eux et à la diode Oled comme indiqué précédemment notamment en relation avec la

figure 3. On note comme précédemment : n1, respectivement n2, le noeud de connexion à Vdd d'une électrode source-drain du transistor, T2, respectivement T2' ; et ct3, respectivement ct4, le noeud de connexion d'une électrode source-drain du premier transistor de commutation T1, respectivement T1' à la grille du transistor de commande T2, respectivement T2'.

**[0048]** Le deuxième transistor de commutation T3, T3' prévu dans chaque circuit de commande, est connecté entre la grille du transistor de commande en courant et la ligne de sélection Scan i respectivement Scan i-1 du premier transistor de commutation du circuit de commande auquel il appartient. La grille du deuxième transistor de commutation d'un circuit de commande est connectée à la ligne de sélection associée à l'autre circuit de commande. Dans l'exemple illustré, le transistor T3 du point image pix<sub>i,j</sub> est ainsi connecté entre la ligne de sélection Scan i du transistor de commutation T1 et la grille du transistor de commande en courant T2. Et sa grille est connectée à la ligne de sélection Scan i-1. Le transistor T3' est connecté entre la ligne de sélection Scan i-1 du transistor de commutation T1' et la grille du transistor de commande en courant T2'. Et sa grille est connectée à la ligne de sélection Scan i.

**[0049]** Selon l'invention, un arrangement du point image correspondant est prévu de manière à optimiser l'espace au mieux, tout en tenant compte des contraintes technologiques. Notamment, comme déjà indiqué précédemment, on cherche à disposer les circuits de commande COM et COM' de manière symétrique au sein du point image de manière à obtenir un taux d'ouverture optique optimal. Il est particulièrement avantageux de pouvoir disposer les transistors de commutation de manière tête-bêche, permettant de limiter l'espace nécessaire et de faciliter les connexions. Il est également avantageux de pouvoir disposer les transistors de commande en courant de manière symétrique relativement aux lignes de sélection.

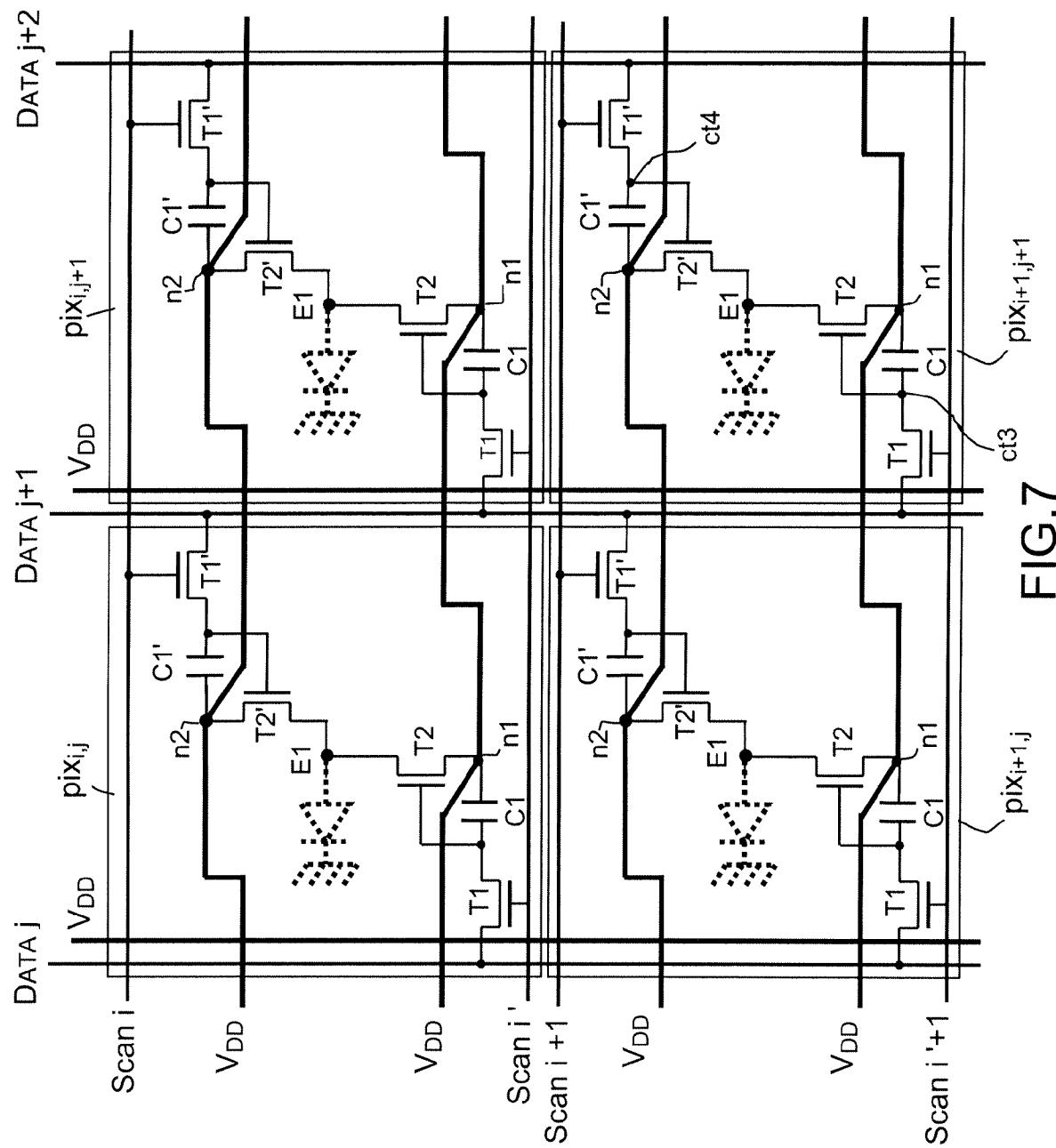

**[0050]** Un arrangement correspondant suivant l'invention est illustré sur les figures 10, 11 et 12. Les figures 10 et 11 sont des schémas électriques d'un point image (figure 10) et de quatre points images adjacents (figure 11). La figure 12 est un schéma topologique d'une matrice correspondante.

**[0051]** Dans cet arrangement, un dédoublement des lignes de sélection est prévu en sorte que l'on ait deux branches Scan<sub>a</sub> i et Scan<sub>b</sub> i d'une ligne de sélection Scan i de part et d'autre de la zone optique. Chaque point image est ainsi encadré par deux lignes de sélection qui sont les branches haute Scan<sub>a</sub> i et basse Scan<sub>b</sub> i de la même ligne de sélection. Cet arrangement permet une implantation favorable des transistors de commutation du point image sans croisement au travers du point image. Il permet aussi une disposition symétrique des deux circuits de commande COM et COM' du point image, de part et d'autre de l'électrode pixel E1. En pratique le dédoublement des lignes est prévu en limite de zone active ZA.

**[0052]** Les transistors de commande T2 et T2' en courant d'un pixel sont disposés le long de l'électrode pixel, entre l'électrode pixel E1, qui forme une électrode source-drain e2<sub>sd</sub> de ces transistors et une colonne d'alimentation Vdd, qui en forme l'autre électrode e2'<sub>sd</sub>. On a ici des transistors en L, à un seul doigt d'électrodes source-drain. La largeur W du canal qui doit être importante pour ces transistors est ici obtenue en exploitant la longueur de l'électrode pixel E1. La séparation entre les deux transistors T2 et T2' est obtenue par une séparation Og entre les deux grilles g de ces transistors.

**[0053]** Le bus d'alimentation Vdd est distribué par des conducteurs colonnes d'alimentation cc issus d'un bus principal haut Bt ou bas Bb comme illustré sur la figure 14. On a ainsi un conducteur colonne d'alimentation cc pour chaque colonne de points image, disposé dans chaque intervalle entre deux colonnes de points image (figure 12). En effet, un maillage comme sur la figure 13 n'est pas avantageux dans le cas de la structure de commande à six transistors. Pour limiter la chute de tension dans les conducteurs colonnes d'alimentation cc du fait de la consommation de courant dans les points d'image, on réalise de larges conducteurs colonnes d'alimentation comme on peut le voir sur la figure 12, de manière à obtenir une résistance d'accès la plus faible possible.

**[0054]** En dehors de ces différences, liées à la présence d'un transistor de commutation supplémentaire par circuit de commande, les autres particularités d'un arrangement selon l'invention vues en relation avec les modes de réalisation précédents pour des structures de commande à quatre transistors s'appliquent à l'identique avec les même effets. On retrouve notamment le tricotage avec les points de contacts ct1 et ct2. Les transistors de commutation sont concentrés entre deux lignes de sélection successives, à savoir entre la branche basse d'une ligne de sélection, par exemple Scan<sub>b</sub> i et la branche haute de la ligne de sélection suivante, dans l'exemple Scan<sub>a</sub> i+1. Cette disposition permet d'optimiser les différentes connexions à réaliser, notamment les connexions reliant en commun les électrodes source-drain des transistors de commutation d'un circuit de commande à la grille du transistor de commande en courant : on a ainsi un point de contact ct3 pour connecter l'électrode source-drain e1<sub>sd</sub> du transistors T1 et l'électrode source-drain e3<sub>sd</sub> du transistors T3, à la grille du transistor T2 ; un point de contact ct4 pour connecter l'électrode source-drain e1'<sub>sd</sub> du transistors T1' et l'électrode source-drain e3'<sub>sd</sub> du transistors T3', à la grille du transistor T2'.

**[0055]** Les points de contact ct1 et ct2 servent en outre à connecter l'électrode source-drain e1 sd du transistor T1' à la ligne de donnée associée au point image correspondant, qui forme l'électrode source-drain e1<sub>sd</sub> du transistor T1 du point image précédent dans la colonne.

**[0056]** Un point de contact ct5, respectivement ct6 permet de connecter l'électrode e3<sub>sd</sub> du transistor T3, respectivement T3', à la ligne de sélection correspondante.

**[0057]** Les différents exemples d'arrangements qui viennent d'être donnés pour illustrer l'invention, montrent

qu'en arrangeant chaque point image entre deux lignes de sélection qui pilotent les transistors de commutation de ce point image (dans le premier exemple, Scan i et Scan i' dans le deuxième exemple, Scan<sub>a</sub> i et Scan<sub>b</sub> i), il est possible de disposer les deux circuits de commande de façon symétrique, de part et d'autre de l'électrode pixel, entre l'électrode pixel et la ligne de sélection qui pilote le ou les transistors de commutation du circuit de commande concerné, et un tricotage des lignes de données entre le niveau conducteur des électrodes source-drain des transistors et le niveau conducteur de grille des transistors permet de réaliser une matrice active avec une ouverture optique maximale et une fiabilité de fabrication optimale (pas de risques de courts-circuits liés à des excès de métaux entre des conducteurs coplanaires). 5

**[0058]** L'arrangement tête-bêche des transistors de commutation pilotées par la même ligne de sélection favorise avantageusement l'ouverture optique. 10

**[0059]** Dans les exemples illustrés, les condensateurs de maintien C1 et C1' sont typiquement réalisés par les capacités grille-source (ou grille-drain) des transistors de commande en courant. 20

**[0060]** Le maillage du bus d'alimentation (figure 13) qui peut être avantageusement mis en oeuvre dans le cas où les circuits de commande comprennent un unique transistor de commutation, permet d'améliorer la résistance d'accès et donc d'obtenir une meilleure distribution énergétique sur la matrice, tout en améliorant la fiabilité du procédé de fabrication (redondance). 25

**[0061]** L'invention qui vient d'être décrite s'applique tout particulièrement aux écrans électroluminescents organiques, qui utilisent une matrice active à transistors TFT (silicium amorphe). Elle s'applique de manière plus générale aux écrans électroluminescents organiques à matrice active. 30

## Revendications

1. Matrice active pour un écran électroluminescent organique, comprenant des points images (pix<sub>i,j</sub>) arangés en lignes et en colonnes, comprenant chacun une électrode pixel (E1) apte à recevoir une diode électroluminescente organique (Oled) en surface, et un premier et un deuxième circuits de commande en courant (COM, COM') connectés à ladite électrode de pixel (E1), chaque premier circuit (COM) et chaque deuxième circuit (COM') comprenant un transistor de commande en courant (T2, T2') connecté entre une tension d'alimentation Vdd et ladite électrode pixel (E1) et au moins un premier transistor de commutation (T1, T1') pour commander la grille dudit transistor de commande en courant, ledit premier transistor de commutation étant connecté entre une ligne de donnée (DATA j) de la matrice et la grille dudit transistor de commande en courant (T2), et ayant sa grille connectée à une ligne de sélection 5

(Scan i) de la matrice, les électrodes de source ou drain des transistors de commutation et de commande et les électrodes pixel étant réalisées sur un niveau métal source drain (Msd), et les électrodes de grille de ces transistors étant chacune réalisées par une ligne de sélection de la matrice, sur un niveau métal de grille (Mg), **caractérisé en ce que**

- chaque point image est disposé entre deux lignes de sélection de la matrice (Scan i, Scan i+1), avec un circuit de commande (COM) disposé entre une première (Scan i) de ces deux lignes de sélection et son électrode pixel (E1), ladite première ligne de sélection formant la grille du premier transistor de commutation (T1) de ce circuit de commande (COM), et l'autre circuit de commande disposé entre une deuxième (Scan i+1) de ces deux lignes de sélection et l'électrode pixel, ladite deuxième ligne de sélection formant la grille du premier transistor de commutation (T1') de ce circuit de commande (COM'),

- une électrode source drain (e2'<sub>sd</sub>) des transistors de commande (T2, T2') est formée par un bus d'alimentation Vdd réalisé sur le niveau métal source drain, et l'autre électrode source drain (e2<sub>sd</sub>) des transistors de commande est formée par au moins un doigt qui est une excroissance de l'électrode pixel (E1) sur le même niveau métal source drain;

- chaque ligne de données est disposée entre deux colonnes de points image de la matrice et formée en utilisant ledit niveau de métal source-drain (Msd) et ledit niveau métal de grille (Mg), ledit niveau de métal de grille étant utilisé le long des électrodes pixel (E1) et ledit niveau de métal source drain étant utilisé dans les zones entre lesdites électrodes pixel où sont réalisés les transistors de commutation desdits circuits de commande.

- 40

2. Matrice selon la revendication 1, dans laquelle ladite tension d'alimentation Vdd est distribuée sur la matrice au moyen d'un bus d'alimentation avec un maillage ligne/colonne. 45

3. Matrice selon la revendication 2, dans laquelle chaque intervalle entre deux colonnes successives de points image, comprend un conducteur colonne de bus d'alimentation Vdd et au moins un conducteur colonne de ligne de donnée (Data j).

- 50

4. Matrice selon la revendication 2 ou 3, dans laquelle le premier transistor de commutation (T1) du premier circuit de commande (COM) d'un point image et le premier transistor de commutation (T1') d'un deuxième circuit de commande (COM') d'un autre point image, sont disposés tête-bêche de part et d'autre 55

d'une ligne de sélection (Scan i).

5. Matrice selon la revendication 4, dans laquelle chaque intervalle entre deux colonnes successives de points image, comprend un conducteur colonne de bus d'alimentation Vdd et un conducteur colonne de ligne de donnée (Data j), et lesdits premiers transistors de commutation disposés tête-bêche ont une électrode de source drain ( $e1_{sd}$ ) formée par une portion de conducteur colonne en métal source drain de la même ligne de donnée (Data j+1). 5

6. Matrice selon la revendication 2 ou 3, dans laquelle le transistor de commande (T2) du premier circuit de commande (COM) d'un point image dans une colonne et le transistor de commande (T2') du deuxième circuit de commande (COM') d'un point image précédent ou suivant dans la même colonne, sont disposés de façon symétrique de part et d'autre d'une ligne de sélection (Scan i). 15 20

7. Matrice selon la revendication 2 ou 3, dans laquelle les transistors de commande desdits premier et deuxième circuit de commande sont à électrodes source-drain interdigitées, chaque électrode source drain comportant plus d'un doigt. 25

8. Matrice selon la revendication 1, dans laquelle chaque premier circuit (COM), et chaque deuxième circuit (COM') comprend un deuxième transistor de commutation (T3) connecté entre la ligne de sélection (Scan i) à laquelle est connectée la grille du premier transistor de commutation (T1) du circuit de commande considéré (COM), et la grille dudit transistor de commande (T2) et dont la grille est connectée à une autre ligne de sélection (Scan i+1), **caractérisée en ce que** chaque ligne de sélection est dédoublée dans la zone active (ZA) en une première branche (Scan<sub>b</sub> i) et une deuxième branche (Scan<sub>b</sub> i) disposées de part et d'autre d'une rangée correspondante de points image (pix<sub>i,j</sub>). 30 35 40

9. Matrice selon la revendication 8, dans laquelle la tension d'alimentation est distribuée par des conducteurs colonnes, avec un conducteur colonne d'alimentation Vdd dans chaque intervalle entre deux colonnes de points image, et dans laquelle les transistors de commande (T2, T2') des premier et deuxième circuits de commande d'un point image sont réalisés le long de l'électrode pixel, entre ladite électrode pixel (E1) et ledit conducteur colonne d'alimentation Vdd qui forment respectivement une première ( $e2_{sd}$ ) et une deuxième électrode source drain ( $e2'_{sd}$ ) des dits transistors de commande (T2, T2'). 45 50 55

10. Ecran à diodes organiques électroluminescentes comprenant une matrice active selon l'une quelconque des revendications précédentes.

FIG.1

FIG.2

FIG.3

FIG.6

FIG.4

FIG.5

FIG.7

FIG. 8

FIG.11

FIG.12

Office européen

des brevets

## RAPPORT DE RECHERCHE EUROPEENNE

Numéro de la demande

EP 08 10 2599

| DOCUMENTS CONSIDERES COMME PERTINENTS                                                                                                                                                                                                                           |                                                                                                                                |                                   | CLASSEMENT DE LA DEMANDE (IPC)       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------|

| Catégorie                                                                                                                                                                                                                                                       | Citation du document avec indication, en cas de besoin, des parties pertinentes                                                | Revendication concernée           |                                      |

| A                                                                                                                                                                                                                                                               | US 2004/066146 A1 (PARK JAE-YONG [KR] ET AL) 8 avril 2004 (2004-04-08)<br>* alinéa [0041] - alinéa [0050] *<br>* figure 5 *    | 1-10                              | INV.<br>H01L27/32<br>G09G3/32        |

| A                                                                                                                                                                                                                                                               | -----<br>US 2004/164303 A1 (ANZAI KATSUYA [JP]) 26 août 2004 (2004-08-26)<br>* alinéa [0049] - alinéa [0051] *<br>* figure 6 * | 1-10                              | -----                                |

| Le présent rapport a été établi pour toutes les revendications                                                                                                                                                                                                  |                                                                                                                                |                                   | DOMAINES TECHNIQUES RECHERCHES (IPC) |

| 2                                                                                                                                                                                                                                                               | Lieu de la recherche                                                                                                           | Date d'achèvement de la recherche | Examinateur                          |

|                                                                                                                                                                                                                                                                 | Munich                                                                                                                         | 8 mai 2008                        | Bernabé Prieto, A                    |

| CATEGORIE DES DOCUMENTS CITES                                                                                                                                                                                                                                   |                                                                                                                                |                                   |                                      |

| X : particulièrement pertinent à lui seul<br>Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie<br>A : arrière-plan technologique<br>O : divulgation non écrite<br>P : document intercalaire                             |                                                                                                                                |                                   |                                      |

| T : théorie ou principe à la base de l'invention<br>E : document de brevet antérieur, mais publié à la date de dépôt ou après cette date<br>D : cité dans la demande<br>L : cité pour d'autres raisons<br>& : membre de la même famille, document correspondant |                                                                                                                                |                                   |                                      |

**ANNEXE AU RAPPORT DE RECHERCHE EUROPEENNE

RELATIF A LA DEMANDE DE BREVET EUROPEEN NO.**

EP 08 10 2599

La présente annexe indique les membres de la famille de brevets relatifs aux documents brevets cités dans le rapport de recherche européenne visé ci-dessus.

Lesdits membres sont contenus au fichier informatique de l'Office européen des brevets à la date du

Les renseignements fournis sont donnés à titre indicatif et n'engagent pas la responsabilité de l'Office européen des brevets.

08-05-2008

| Document brevet cité<br>au rapport de recherche | Date de<br>publication | Membre(s) de la<br>famille de brevet(s)             | Date de<br>publication                 |

|-------------------------------------------------|------------------------|-----------------------------------------------------|----------------------------------------|

| US 2004066146 A1                                | 08-04-2004             | CN 1477610 A<br>JP 2004038188 A<br>KR 20040006987 A | 25-02-2004<br>05-02-2004<br>24-01-2004 |

| US 2004164303 A1                                | 26-08-2004             | AUCUN                                               |                                        |

EPO FORM P0460

Pour tout renseignement concernant cette annexe : voir Journal Officiel de l'Office européen des brevets, No.12/82

|                |                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光显示器的有源矩阵                                                                                 |         |            |

| 公开(公告)号        | <a href="#">EP1970961A1</a>                                                                    | 公开(公告)日 | 2008-09-17 |

| 申请号            | EP2008102599                                                                                   | 申请日     | 2008-03-14 |

| [标]申请(专利权)人(译) | 汤姆森 - 无线电报总公司                                                                                  |         |            |

| 申请(专利权)人(译)    | THALES                                                                                         |         |            |

| 当前申请(专利权)人(译)  | THALES                                                                                         |         |            |

| [标]发明人         | KRETZ THIERRY<br>LEBRUN HUGUES<br>CHUITON ELISABETH                                            |         |            |

| 发明人            | KRETZ, THIERRY<br>LEBRUN, HUGUES<br>CHUITON, ELISABETH                                         |         |            |

| IPC分类号         | H01L27/32 G09G3/32                                                                             |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0426 G09G2300/0465 G09G2300/0852 G09G2310/0254 G09G2320/043<br>H01L27/3276 |         |            |

| 代理机构(译)        | ESSELIN , SOPHIE                                                                               |         |            |

| 优先权            | 2007001929 2007-03-16 FR                                                                       |         |            |

| 其他公开文献         | EP1970961B1                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                      |         |            |

### 摘要(译)

矩阵具有电流驱动晶体管 ( T2 , T2' ) , 漏极源电极 ( e2sd ) , 由在漏极源极金属 ( Msd ) 的电平上实现的电源总线 ( Vdd ) 形成 , 并且具有漏极由手指形成的源电极 ( e2sd ) 。通过接触点 ( ct1 , ct2 ) 在漏极源极金属和金属栅极 ( Mg ) 的水平之间形成数据线 ( Dataj ) 。沿像素电极 ( E1 ) 利用金属栅极的电平 , 并且在实现开关晶体管 ( T1 , T1' ) 的像素电极之间的区域中利用金属 ( Msd ) 的电平。

FIG.5