Europäisches

Patentamt

European

Patent Office

Office européen

des brevets

(11)

EP 2 816 546 A1

(12)

## EUROPEAN PATENT APPLICATION

(43) Date of publication:

24.12.2014 Bulletin 2014/52

(51) Int Cl.:

G09G 3/32 (2006.01)

(21) Application number: 13194052.0

(22) Date of filing: 22.11.2013

(84) Designated Contracting States:

**AL AT BE BG CH CY CZ DE DK EE ES FI FR GB

GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO

PL PT RO RS SE SI SK SM TR**

Designated Extension States:

**BA ME**

(30) Priority: 18.06.2013 CN 201310242553

(71) Applicants:

• **Shanghai Tianma Micro-electronics Co., Ltd.

Pudong New District

Shanghai 201201 (CN)**

• **Tianma Micro-Electronics Co., Ltd.

Shenzen Guangdong 518052 (CN)**

(72) Inventors:

• **Gu, Hanyu

201201 Shanghai (CN)**

• **Tseng, Chang-ho

201201 Shanghai (CN)**

(74) Representative: **Epping - Hermann - Fischer

Patentanwaltsgeellschaft mbH

Schloßschmidstraße 5

80639 München (DE)**

### (54) OLED display device

(57) An OLED display device, includes multiple pixel units arranged in a matrix and a power supply driver chip located at one side of the multiple pixel units. The power supply driver chip is configured to supply input voltages to the multiple pixel units. The power supply driver chip provides the input voltages to the multiple pixel units through a plurality of input paths. An input point of each of the input paths corresponds to a pixel unit at a different

location, and at the input point the input path is connected to the pixel unit. In the OLED display device provided in the invention, all of the pixel units at different locations may have an approximately equal input voltage, enabling the entire display region of the OLED display device to display with a uniform brightness and improving the display performance.

Fig. 4

**Description****CROSS REFERENCE TO RELATED APPLICATION**

5 [0001] This application claims the benefit of priority to Chinese Patent Application No.201310242553.3, entitled "OLED DISPLAY DEVICE", filed on June 18, 2013 with State Intellectual Property Office of PRC.

**FIELD OF THE INVENTION**

10 [0002] The invention relates to display technology, and in particular to an Organic Light-Emitting Diode (OLED) display device and a method for detecting and compensating an output voltage of the OLED display device.

**BACKGROUND OF THE INVENTION**

15 [0003] OLED display device, which is also known as organic electroluminescence display, has the characteristics of self-luminescence and adopts very thin organic material coating and glass substrate. The organic material glows when the current flows through it. Moreover, the OLED display device has large visual angle and is significant power saving. Therefore, the OLED display device has incomparable advantages over many traditional display devices, such as liquid crystal display device.

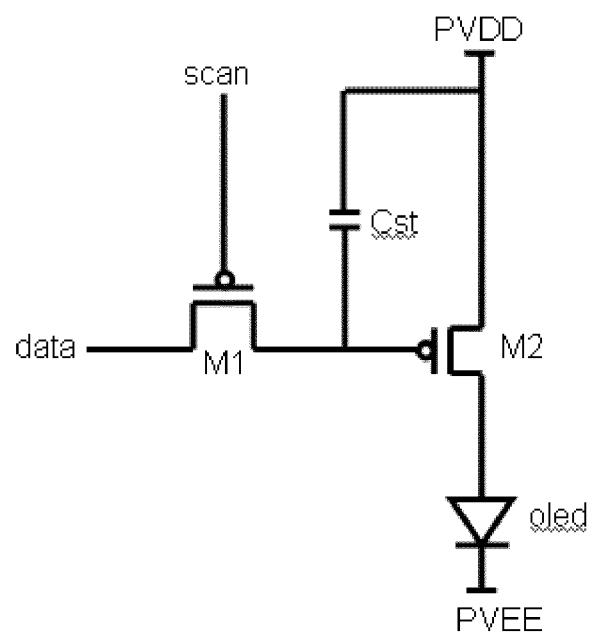

20 [0004] FIG. 1 shows a schematic diagram of an equivalent circuit for a pixel unit in an OLED display device, and FIG. 2 shows a schematic diagram of an OLED display device in the prior art.

25 [0005] As shown in FIG. 1, in one pixel unit, a scan signal "scan" controls the on or off state of a thin film transistor M1. In the case that M1 is in on state, a data signal "data" is transferred to the gate electrode of a thin film transistor M2 to control the current in M2. A power supply signal PVDD is transferred to the low potential end PVEE through the thin film transistor M2, and thus the organic light-emitting diode "oled" is controlled to emit lights and implement the display. The organic light-emitting diode "oled" is a current-driven element, in which the current flowing through the organic light-emitting diode "oled" may be calculated from the following formula:

$$30 I_{oled} = 1/2 \times \mu \times C_{ox} \times W/L \times (PVDD - V_{data} - V_{th})^2$$

$\mu$ : the mobility of the active layer;

35  $C_{ox}$ : the capacitance of the capacitor formed by the gate electrode and the active layer;

W: the width of the channel in the organic light-emitting diode;

40 L: the length of the channel in the organic light-emitting diode;

$V_{data}$ : the voltage of the data signal;

45  $V_{th}$ : the threshold voltage of the organic light-emitting diode;

PVDD: the voltage of the power supply signal;

50 [0006] Once the size of the organic light-emitting diode "oled" is determined, the values of  $\mu$ ,  $C_{ox}$ , W, L and  $V_{th}$  are also determined. As can be seen from the above formula, for a certain organic light-emitting diode "oled", the current flowing through the organic light-emitting diode "oled" is determined by the value of the power supply signal PVDD and the data signal  $V_{data}$ .

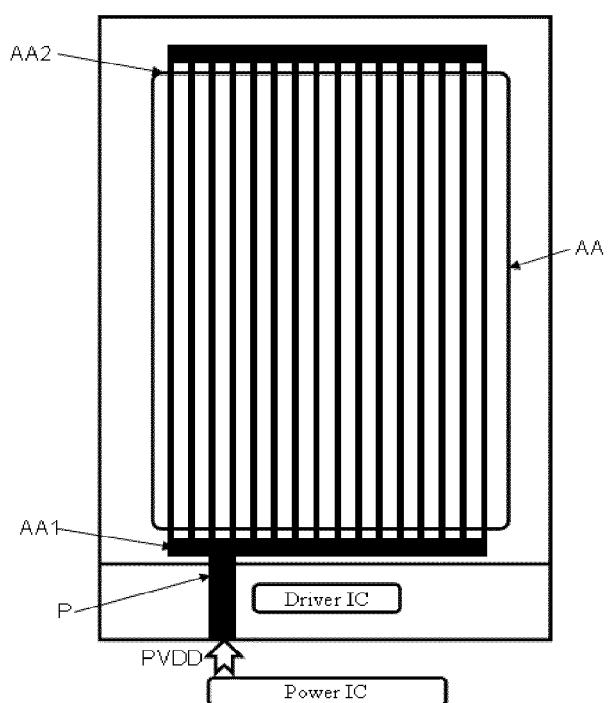

55 [0007] Next, reference is made to FIG. 2. In an OLED display device, multiple pixel units arranged in a matrix is disposed in a region AA, and a driver chip "Driver IC" is further disposed on one side of the OLED display device, which is configured to provide scan signals and data signals to the multiple pixel units. A power supply driver chip "Power IC" is further disposed. Generally, only one power supply driver chip is disposed for the OLED display device with a small panel. The driver chip "Driver IC" is disposed on the panel of the OLED display device, and the power supply driver chip "Power IC" is disposed on a flexible circuit board or a printed circuit board.

[0008] The power supply driver chip "Power IC" supplies an input voltage PVDD to the multiple pixel units through an input path P, for driving the organic light-emitting diodes to emit lights and implement the display. In the entire display

region AA, input terminals of the pixel units for input the voltage PVDD are connected together. Since the OLED display device is a current-driven device and each pixel unit has a resistance, a voltage drop is generated in the pixel units from the point AA1 nearest to the power supply driver chip "Power IC" to the point AA2 farthest to the power supply driver chip "Power IC" due to the driving current. That is, the voltage at the nearest point AA1 is larger than that at the farthest point AA2.

[0009] From the nearest point AA1 to the farthest point AA2, the currents flowing through the pixel units decrease gradually from one pixel unit to another as the voltages decrease sequentially from one pixel unit to another, resulting in gradually reduced brightness from one to another portion of the OLED device. As a result, the OLED display device does not display uniformly. This problem becomes more serious as the size of the OLED display device increases.

## SUMMARY OF THE INVENTION

[0010] In view of the above, the invention provides an OLED display device.

[0011] The OLED display device includes multiple pixel units arranged in a matrix and a power supply driver chip located at one side of the multiple pixel units. The power supply driver chip is configured to supply input voltages to the multiple pixel units, and the power supply driver chip supplies input voltages to the multiple pixel units through a plurality of input paths. An input point of each of the input paths corresponds to a pixel unit at a different location.

[0012] Preferably, in the OLED display device provided by the invention, a reference voltage is set, and a detecting wire is disposed for each of the input paths. The detecting wire is configured to transfer the voltage at the input point of the input path to a detecting point for being compared with the reference voltage. In the case that a voltage difference exists between the voltage at the input point and the reference voltage, the power supply driver chip supplies a compensation voltage to the input path to change the input voltage of the input path, so as to reduce the voltage difference.

[0013] In the OLED display device provided in the invention, the power supply driver chip supplies the input voltages to the multiple pixel units through the plurality of input paths, all of the pixel units at different locations may have an approximately equal input voltage, enabling the entire display region of the OLED display device to display with a uniform brightness and improving the display performance.

[0014] Further, because the OLED display device provided in the invention has the function of detecting and correcting the input voltages, the voltages at the respective input points may be consistent or approximate. That is, for all of the pixel units in the entire display region AA, not only the input points are disposed evenly, but also the voltages at the respective input points are the same or approximate, which may further improve the brightness uniformity of the OLED display device.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0015]

FIG. 1 shows a schematic diagram of an equivalent circuit for a pixel unit in an OLED display device;

FIG. 2 shows a schematic diagram of an OLED display device in the prior art;

FIG. 3 is a schematic diagram of an OLED display device provided in a first embodiment;

FIG. 4 is a schematic diagram of an OLED display device provided in a second embodiment;

FIG. 5 is a schematic diagram of an equivalent circuit for an input path P1 and a display region AA in the second embodiment;

FIG. 6 is a schematic diagram of an OLED display device provided in a third embodiment; and

FIG. 7 is a schematic diagram of an OLED display device provided in a fourth embodiment.

## DETAILED DESCRIPTION OF THE INVENTION

First embodiment

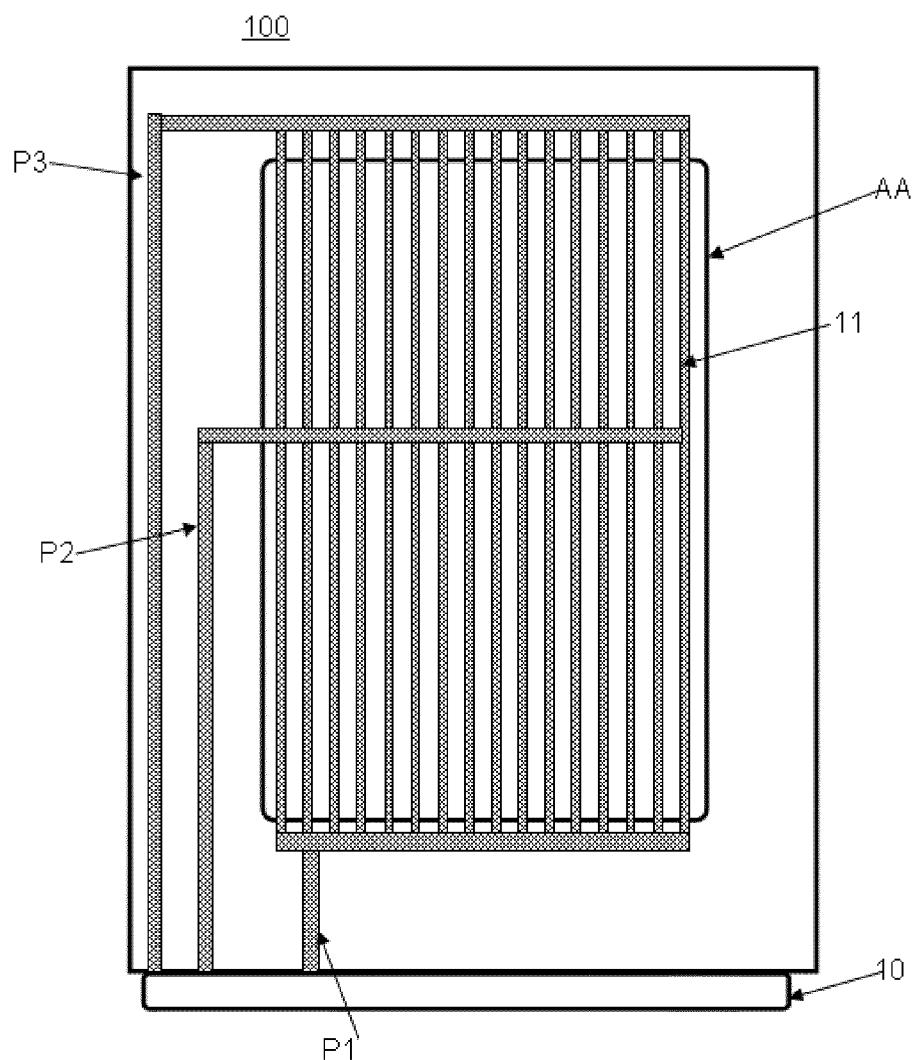

[0016] Reference is made to FIG. 3, which is a schematic diagram of an OLED display device provided in a first embodiment. In the OLED display device 100 according to the first embodiment, multiple pixel units arranged in a matrix are disposed in a display region AA, and a power supply driver chip 10 is disposed at one side of the multiple pixel units.

The power supply driver chip 10 is configured to supply an input voltage PVDD to the multiple pixel units. The power supply driver chip 10 supplies the input voltage to the multiple pixel units through three input paths P1, P2 and P3, respectively. In the first embodiment, the input terminals for the input voltage PVDD of each column of the pixel units are connected with one wire 11, and all the wires 11 are connected together outside the display region AA.

**[0017]** In the first embodiment, the input point A1 of the input path P1 is located at the pixel unit which is the nearest to the power supply driver chip 10, and at the input point A1 the input path and the pixel unit are connected. The input point A3 of the input path P3 is located at the pixel unit which is the farthest to the power supply driver chip 10, and the input point A2 of the input path P2 is located at the pixel unit which is in the middle of the display region AA. The input points of respective input paths are disposed on the same side of the matrix of the pixel units, and the input points of the multiple input paths P1, P2 and P3 are distributed evenly with respect to the matrix of the pixel units, i.e. the input points are spaced by equal number of rows of pixel units. Furthermore, the power supply driver chip 10 supplies an equal input voltage PVDD to the input paths P1, P2 and P3.

**[0018]** The power supply driver chip 10 supplies the input voltage PVDD to the display region AA through the three input paths, and all of the pixel units at different locations may have an approximately equal input voltage. Therefore, the situation that from the side nearest to the power supply driver chip 10 to the side farthest to the power supply driver chip 10 the voltages of the pixel units decrease sequentially from one pixel unit to another is optimized, the entire display region AA of the OLED display device may have a uniform brightness and the display performance is improved.

## Second embodiment

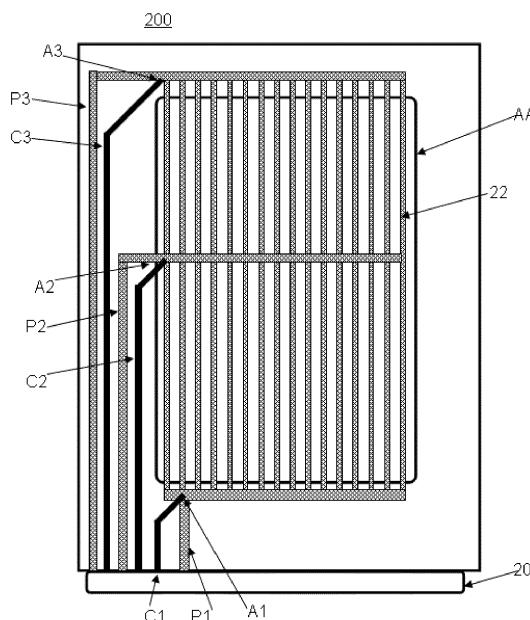

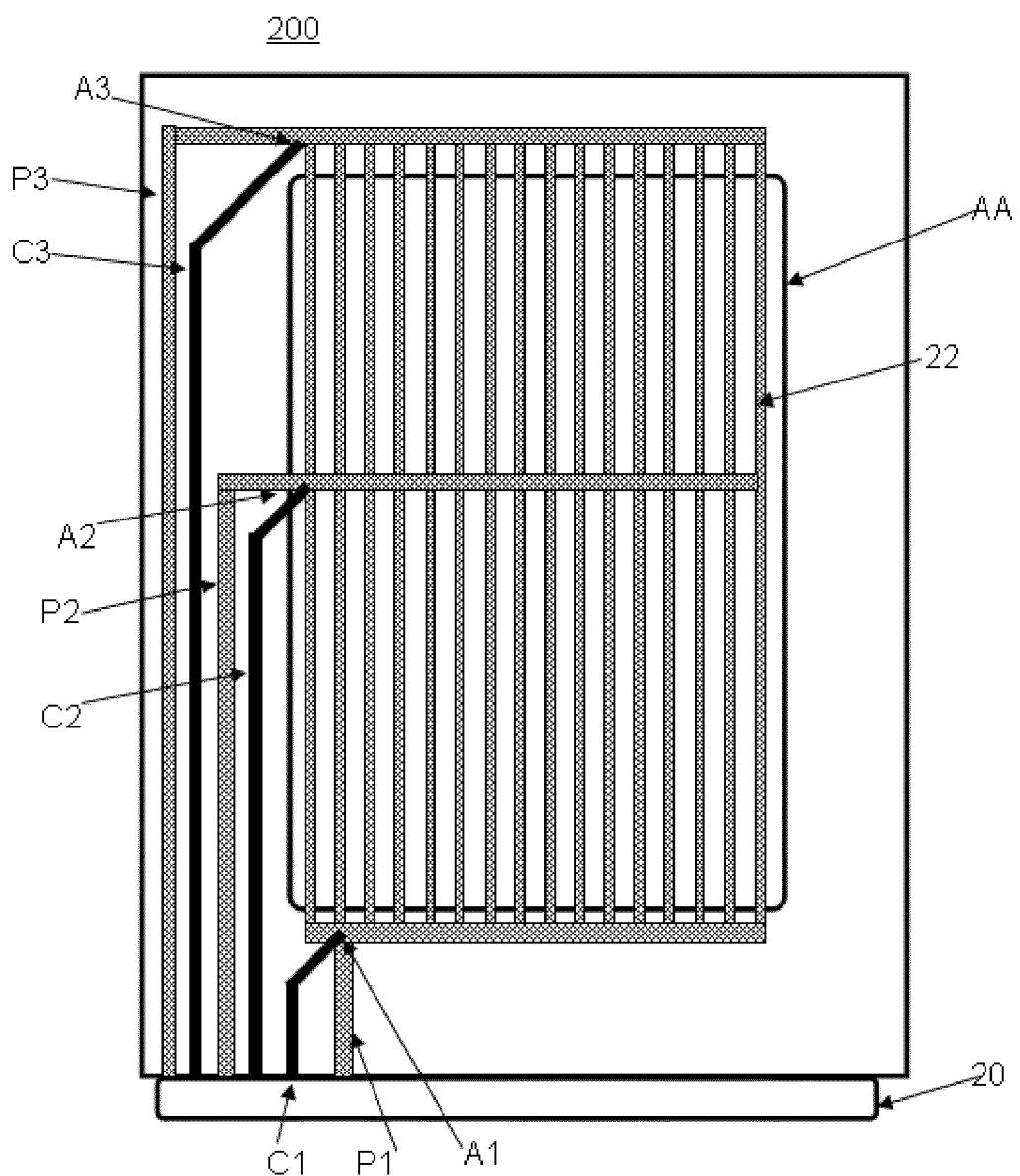

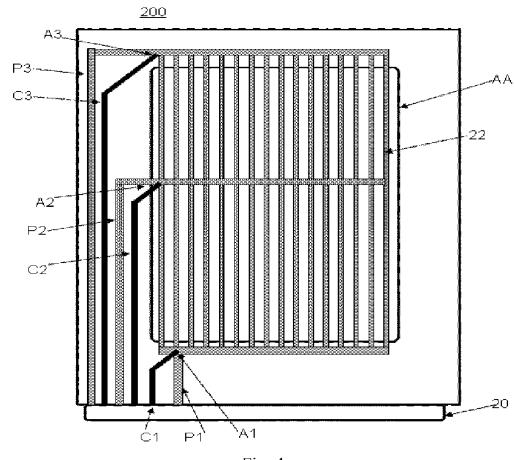

**[0019]** Reference is made to FIG. 4, which is a schematic diagram of an OLED display device provided in a second embodiment. In the OLED display device 200 provided according to the second embodiment, multiple pixel units arranged in a matrix are disposed in a display region AA, and a power supply driver chip 20 is disposed at one side of the multiple pixel units. The power supply driver chip 20 supplies input voltages to the multiple pixel units through three input paths P1, P2 and P3 respectively. The power supply driver chip 20 supplies an input voltage PVDD1 to the input path P1, an input voltage PVDD2 to the input path P2, and an input voltage PVDD3 to the input path P3. The input point A1 of the input path P1 is located at the pixel unit which is the nearest to the power supply driver chip 20; the input point A3 of the input path P3 is located at the pixel unit which is the farthest to the power supply driver chip 20; and the input point A2 of the input path P2 is located at the pixel unit which is in the middle of the display region AA. In the second embodiment, input terminals for the input voltages PVDDs of each column of the pixel units are connected with one wire 22, and all the wires 22 are connected together at outside of display region AA.

**[0020]** As a preferable embodiment, in the OLED display device 200 according to the second embodiment, detecting wires C1, C2 and C3, corresponding to the input paths P1, P2 and P3 respectively, are provided. The respective detecting wires C1, C2 and C3 transfer the respective voltages at the input points A1, A2 and A3 of the input paths P1, P2 and P3 to a detecting point. In the second embodiment, the detecting point is located within the power supply driver chip 20. For example, the detecting wire C1 transfers the voltage at the input point A1 of the input path P1 to the detecting point located within the power supply driver chip 20.

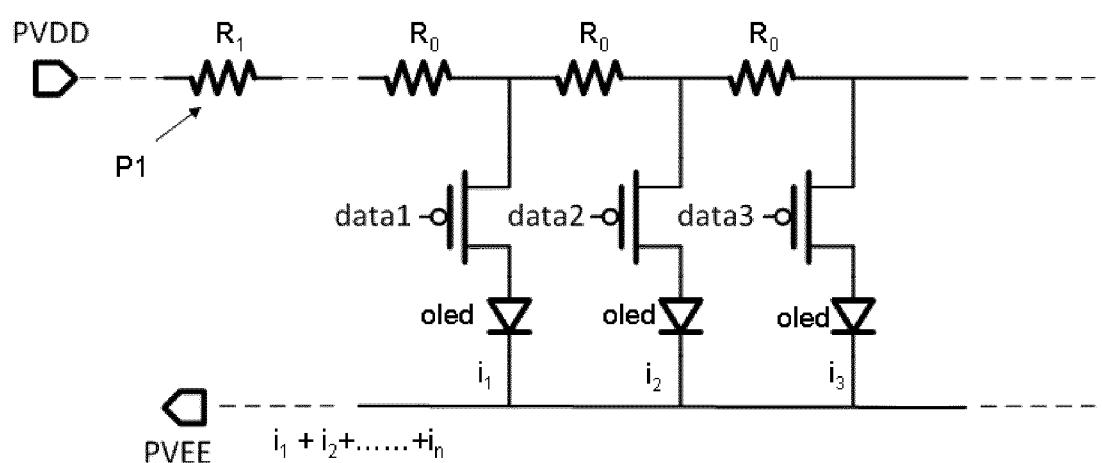

**[0021]** Reference is made to FIG. 5, which is a schematic diagram of an equivalent circuit for the input path P1 and the display region AA. As shown in FIG. 5, multiple pixel units are connected in parallel between the input path P1 and a low voltage input terminal PVEE, and each of the pixel units is equivalent to a serial connection of a resistor  $R_0$  and an organic light emitting diode "oled", in which the current of the organic light emitting diode "oled" is controlled by a data signal "data", and the cathodes of all organic light emitting diodes "oleds" are connected together to the low voltage input terminal PVEE.

**[0022]** The current  $i_1$  flowing through a first pixel unit, the current  $i_2$  flowing through a second pixel unit, the current  $i_3$  flowing through a third pixel unit, ..., and the current  $i_n$  flowing through a  $n^{\text{th}}$  pixel unit, decrease gradually from one to another, due to the voltage drop generated when the current flowing through each pixel unit. The total current  $i_1 + i_2 + i_3 + \dots + i_n$  has a value generally ranging from tens of milliamperes to hundreds of milliamperes. Because the total current flowing through the input path P1 is large, and the input path P1 has a certain resistance although it is a metal wire, assuming that the resistance of the input path P1 is  $R_1$ , the voltage drop of the input voltage PVDD1 in the input path P1 is  $R_1 \times (i_1 + i_2 + i_3 + \dots + i_n)$ . As a result, the voltage at the input point A1 is  $PVDD1 - R_1 \times (i_1 + i_2 + i_3 + \dots + i_n)$ , which is the exact voltage transferred to the pixel units and is smaller than the input voltage PVDD1 supplied to the input path P1 by the power supply driver chip 20.

**[0023]** Because the input path P2 is longer than the input path P1, the resistance of the input path P2 is larger than the resistance  $R_1$  of the input path P1. Assuming that the resistance of the input path P2 is  $R_2$  and the total current flowing through the input path P2 is  $(i_1 + i_2 + i_3 + \dots + i_n)$ , then in the same way, the voltage drop generated from the current flowing through the input path P2 is  $R_2 \times (i_1 + i_2 + i_3 + \dots + i_n)$ , i.e. the voltage at the input point A2 is  $PVDD2 - R_2 \times (i_1 + i_2 + i_3 + \dots + i_n)$ , which is also smaller than the original input voltage PVDD2. Similarly, the voltage at the input point A3 is smaller than the input voltage PVDD3.

[0024] If the input voltages PVDD1, PVDD2 and PVDD3 supplied to the input paths P1, P2 and P3 respectively by the power supply driver chip 20 are equal to each other, the voltages at the input points A1, A2 and A3 of the input paths are not equal. Furthermore, the voltage at the input point A1 is higher than that at the input point A2, and the voltage at the input point A2 is higher than that at the input point A3.

5 [0025] It can be seen from the above that for the pixel units in the entire display region AA of the OLED display device 200, although the input points of the input paths are disposed evenly, the voltages at the input points are different.

[0026] In the second embodiment, the respective detecting wires C1, C2 and C3 transfer the respective voltages at the input points A1, A2 and A3 of the input paths P1, P2 and P3 to a detecting point located within the power supply driver chip 20. The detecting wires C1, C2 and C3 are only used in the measurement of the voltages and the voltage drops on the detecting wires are very small and negligible. Also, the power supply driver chip 20 supplies a reference voltage P0, which is compared to the voltages at the respective input points. In the case that there is a voltage difference between the voltage at an input point of an input path and the reference voltage P0, the power supply driver chip 20 supplies a compensation voltage to the input path to change the value of the original input voltage, so as to reduce the voltage difference, i.e., to make the voltages at the input points to be equal or have smaller difference in the best possibility.

10 [0027] The compensation voltage may be either a positive or a negative value. In the case that the voltage at the input point of the input path is higher than the reference voltage P0, the power supply driver chip 20 supplies a negative compensation voltage to the input path to decrease the value of the original input voltage of the input path, so as to reduce the voltage difference. In the case that the voltage at the input point of the input path is smaller than the reference voltage P0, the power supply driver chip 20 supplies a positive compensation voltage to the input path to increase the 15 value of the original input voltage of the input path, so as to reduce the voltage difference.

20 [0028] For example, at a certain moment, the power supply driver chip 20 detects that the voltage at the input point A2 of the input path P2 is higher than the reference voltage P0 and the voltage difference is +0.05V; meanwhile, the power supply driver chip 20 also detects that the voltage at the input point A3 of the input path P3 is higher than the reference voltage P0 and the voltage difference is -0.03V. Then when providing voltages to the input paths for the next 25 time, the power supply driver chip 20 supplies a compensation voltage  $\Delta V2$  of -0.05V to the input path P2, that is, the voltage supplied to the input path P2 by the power supply driver chip 20 for the next time is changed and is smaller than that for the last time by 0.05V; meanwhile, the power supply driver chip 20 supplies a compensation voltage  $\Delta V3$  of +0.03V to the input path P3, that is, the voltage supplied to the input path P3 by the power supply driver chip 20 for the next time is changed and is higher than that for the last time by 0.03V. In this way, the voltage differences between the 30 reference voltage P0 and the voltages at the input points A2 and A3 may be reduced. In the next detecting, the voltages at the input points will be compared with the reference voltage P0 again and will be corrected again, until the difference is desirable.

35 [0029] Since the OLED display device provided in the second embodiment has the function of detecting and correcting the input voltages, the voltages at the input points may be consistent or approximate. That is, for all of the pixel units in the entire display region AA, not only the input points are disposed evenly, but also the voltages at the input points are the same or approximate, which may further improve the brightness uniformity of the OLED display device.

40 [0030] Preferably, in the case that the voltage difference between the voltage at the input point and the reference voltage P0 is greater than 0.1V, the power supply driver chip 20 supplies a compensation voltage to the input path to change the original input voltage of the input path, so as to reduce the voltage difference to be smaller or equal to 0.1V. When the voltage difference between the voltage at the input point and the reference voltage is smaller than 0.1V, the display uniformity of the entire matrix of pixel units is still acceptable; however, when the voltage difference raises to 0.1V or above, the uneven brightness of the entire matrix of pixel units can be sensed by human eyes. Therefore, when the voltage difference is larger than 0.1V, the OLED display device 200 may start the correcting function for input voltages to reduce the voltage difference to be equal to or smaller than 0.1V.

45 [0031] Preferably, the power supply driver chip 20 detects the voltages of the respective input points before the beginning or after the end of each frame scanning. This is because before the beginning or after the end of each frame scanning, in each pixel unit of the entire matrix of the pixel units, the current flowing through the organic light emitting diode "oled" is determined and the voltage drop in each pixel unit is also determined, so the voltages at the respective input points to be detected are stable at this time. In order to reduce the computation and the power consumption of the power supply driver chip 20, the voltages at the respective input points may be detected at a frequency of every several frames.

50 [0032] In another embodiment, the detecting wire is not provided for the input path P1 of which the input point is the nearest to the power supply driver chip 20, and the voltage at the input point A1 of the input path P1 is equal to the input voltage PVDD1 supplied to the input path P1 by the power supply driver chip 20. Furthermore, the reference voltage P0 may also be equal to the input voltage PVDD1 supplied to the input path P1 by the power supply driver chip 20. Because the input point of the input path P1 is nearest to the power supply driver chip 20 and the length of the input path P1 is much smaller than that of other paths, the resistance R1 of the input path P1 is also the smallest and the voltage drop generated by the input path P1 is ignorable. Therefore, the detecting wire may not be provided for the input path P1 and

the input voltage PVDD1 of the input path P1 may be used as the reference voltage. In such a design one detecting wire may be omitted, facilitating the wiring on the panel. Also, the comparison between the voltage at the input point of the input path P1 and the reference voltage is omitted, so the computation of the power supply driver chip is reduced and the power consumption is decreased.

**[0033]** Certainly, the voltage at the input point of any of the input paths may be served as the reference voltage P0. For example, the voltage at the input point A2 of the input path P2 or at the input point A3 of the input path P3 may be served as the reference voltage, and in this way, once of the comparison between the voltage at the input point of one input path and the reference voltage may be omitted, and the computation of the power supply driver chip is reduced.

**[0034]** In the second embodiment three input paths are provided; and in other embodiments depending on the size of the panel, two or more input paths can be selectively provided to supply input voltages for the pixel units.

### Third embodiment

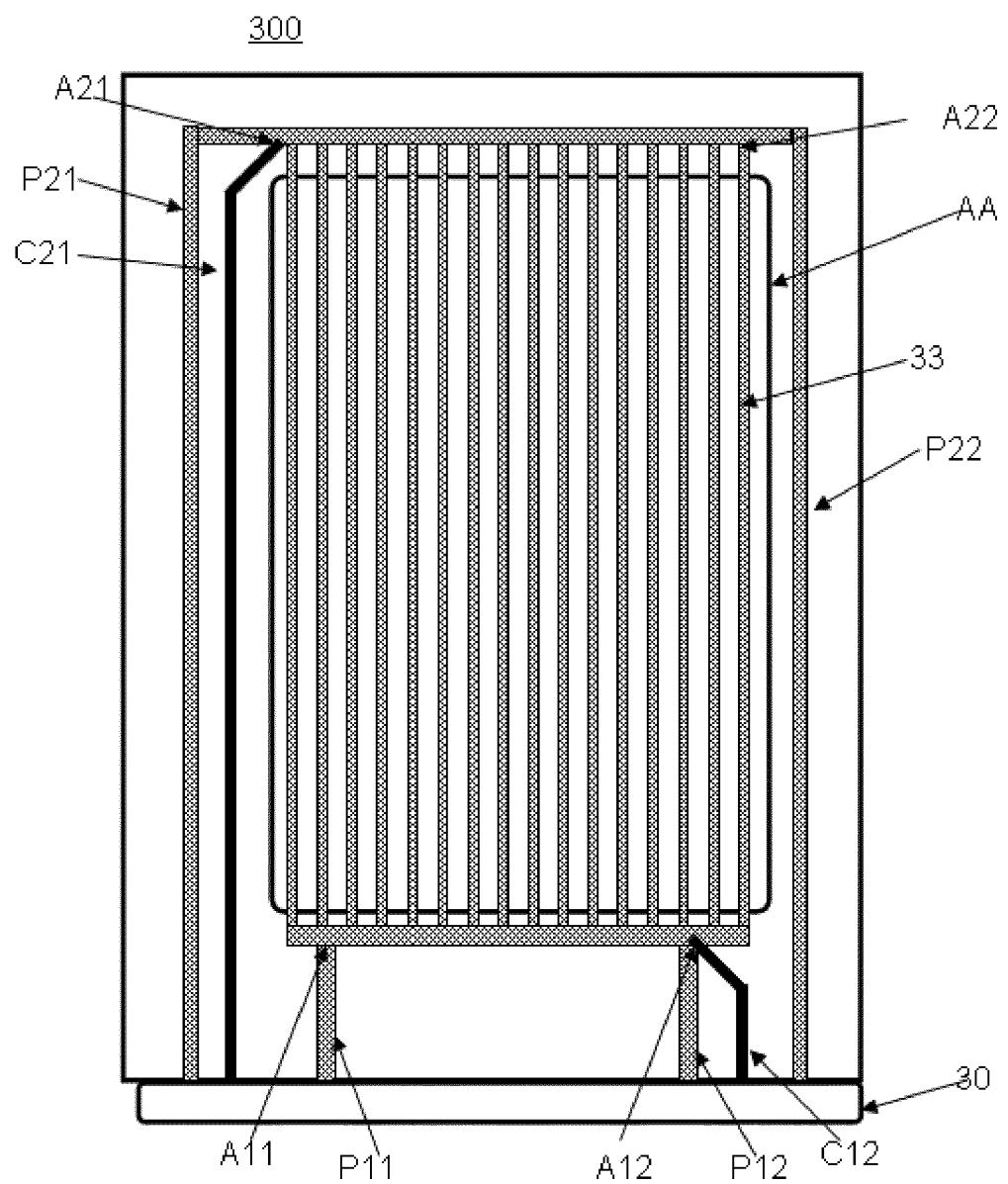

**[0035]** Reference is made to FIG. 6, which is a schematic diagram of an OLED display device provided in a third embodiment. In the OLED display device 300 provided according to the third embodiment, multiple pixel units arranged in a matrix are disposed in a display region AA, and a power supply driver chip 30 is located at one side of the multiple pixel units. The power supply driver chip 30 is configured to supply input voltages to the multiple pixel units. The power supply driver chip 30 supplies input voltages to the multiple pixel units through two input paths P1 and P2 respectively. The input point of the input path P1 is located at the pixel unit which is the nearest to the power supply driver chip 30, and the input point of the input path P2 is located at the pixel unit which is the farthest to the power supply driver chip 30. At the respective one of the input points, the input path and the pixel unit are connected. In the third embodiment, input terminals for the input voltages of each column of the pixel units are connected with one wire 33, and all the wires 33 are connected together outside the display region AA..

**[0036]** The input path P1 includes two branches P11 and P12, which have the same length from the power supply driver chip 30 to the respective input points A11 and A12. The power supply driver chip 30 supplies equal input voltages to the branches P11 and P12. The branches P11 and P12 converge within the matrix of the pixel units, and the input point A11 of the branch P11 and input point A12 of the branch P12 are symmetrically disposed with respect to the center line of the matrix of the pixel units. In the third embodiment, the input point A11 of the branch P11 is located at the left side of the matrix of the pixel units and the input point A12 of the branch P12 is located at the right side of the matrix of the pixel units, and the input points A11 and A12 correspond to a same row of pixel units. A detecting wire C12 is disposed for the branch P12 to transfer the voltage at the input point A12 to a detecting point for detecting.

**[0037]** Similarly, the input path P2 includes two branches P21 and P22, which have the same length from the power supply driver chip 30 to the respective input points A21 and A22. The power supply driver chip 30 supplies equal input voltages to the branches P21 and P22. Furthermore, the input point A21 of the branch P21 and the input point A22 of the branch P22 are symmetrically disposed with respect to the center line of the matrix of the pixel units. A detecting wire C21 is disposed for the branch P21 to transfer the voltage at the input point A21 to a detecting point for detecting. The power supply driver chip 30 corrects the respective input voltages supplied to the respective input paths according to detection results, to ensure that the voltages at the respective input points of the input paths are substantially consistent.

**[0038]** Each of the input paths includes two symmetrical branches, and the power supply driver chip 30 corrects the respective input voltages supplied to the input paths according to the detection results, so the input voltages are more balanced and the brightness uniformity is better for the matrix of the pixel units.

**[0039]** Furthermore, since the two branches are symmetrical, the detecting wire is needed for only one of the two branches. The detecting wires for different input paths may be disposed on different sides, facilitating the structural design of the OLED display device 300.

**[0040]** In the second embodiment, the detecting point is disposed within the power supply driver chip, and the power supply driver chip may detect the voltages at the respective input points through the detecting point for every frame or every several frames, and then perform the compensation. The detection and compensation are performed continuously, and hence the method for detecting and compensating as described above can be regarded as a dynamic method.

**[0041]** In the third embodiment, all of the detecting points of the input paths are disposed on the panel of the OLED display device 300, and the detecting is performed during the procedure for producing the OLED display device 300. Specifically, in the module process for the OLED display device 300, input voltages PVDD1 and PVDD2 are firstly supplied to the branches P11 and P12 of the input path P1 and the branches P21 and P22 of the input path P2, respectively, in which the input voltage PVDD2 may be higher than or equal to the input voltage PVDD1. Then, an detecting apparatus may detect the voltages at the input points A12 and A21 through the detecting wires C12 and C21, respectively, and obtain respective compensation voltages after comparing the detected voltages with the reference voltage P0. For example, a compensation voltage for the input path P1 is  $\Delta V1$ , and a compensation voltage for the input path P2 is  $\Delta V2$ .

**[0042]** In the third embodiment, the method for determining a compensation voltage for each input path may be as

follows. Firstly, multiple sets of compensation voltages are determined based on measurements performed on multiple images. For example, a set of compensation voltages is measured when the OLED display device 300 is in the brightest state, another set of compensation voltages is measured when the OLED display device 300 is in the darkest state, and so on. Then a middle value or an average value of the multiple sets of compensation voltages or another appropriate value is taken as a compensation voltage  $\Delta V_1$ , which may result in a best image display effect. Subsequently a value obtained by adding the compensation voltage  $\Delta V_1$  with the original input voltage PVDD1 is burned into the power supply driver chip 30 of the type of OTP(One Time Programmable).

**[0043]** During the display process of the OLED display device 300, the power supply driver chip 30 supplies a corrected input voltage for each of input paths. For example, an input voltage supplied for the input path P1 is (PVDD1+ $\Delta V_1$ ), and an input voltage supplied for the input path P2 is (PVDD2+ $\Delta V_2$ ), to keep the voltages at the input points of the input paths P1 and P2 to be consistent, enabling the matrix of the pixel units to display with a uniform brightness.

**[0044]** In the third embodiment, the input voltage supplied to each of the input paths by the power supply driver chip 30 is corrected and the detecting is performed by an external apparatus during the producing procedure, so the above method for detecting and compensating as described above may be regarded as a static method. Compare with the dynamic method for detecting and compensating, in the static method for detecting and compensating the computation of the power supply driver chip 30 is reduced. Moreover, the static method for detecting and compensating may be applied to a batch production. Specifically, several OLED display devices are selected from a batch of OLED display devices as samples, for each of which, an appropriate compensation voltage  $\Delta V$  for each of the input paths is determined based on a detection, and the sum of the compensation voltage  $\Delta V$  and the input voltage supplied to the input path by the power supply driver chip during the detection is burned into the power supply driver chips of the batch of OLED display devices. For the batch production of the OLED display devices, convenient correction of the compensation voltages may be achieved with the static method for detecting and compensating, resulting in a higher operability and a lower cost.

#### 25 Fourth embodiment

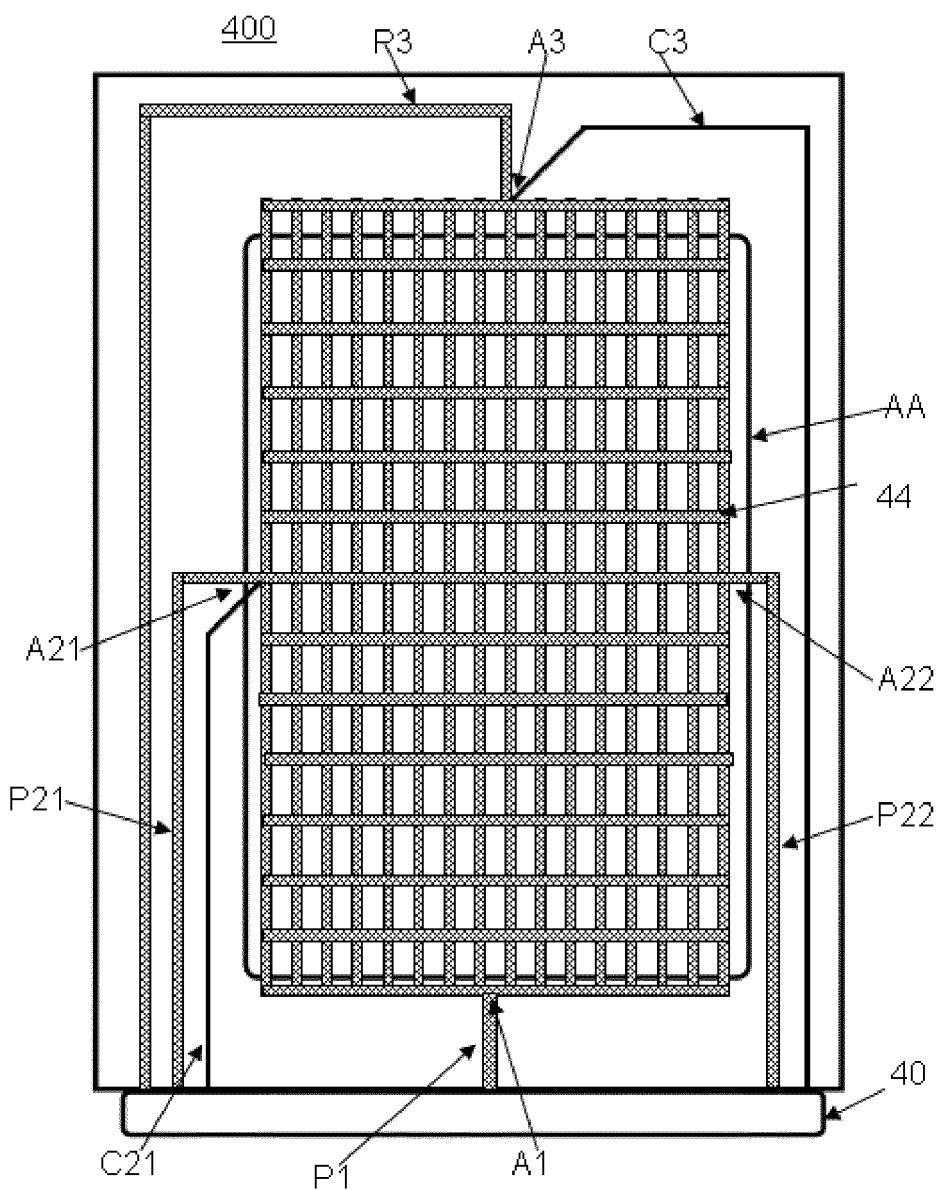

**[0045]** Reference is made to FIG. 7, which is a schematic diagram of an OLED display device provided in a fourth embodiment. In an OLED display device 400 provided according to the fourth embodiment, multiple pixel units arranged in a matrix are disposed in a display region AA, and a power supply driver chip 40 is located at one side of the multiple pixel units. The power supply driver chip 40 is configured to supply input voltages PVDDs to the multiple pixel units. The power supply driver chip 40 supplies input voltages to the multiple pixel units through three input paths P1, P2 and P3 respectively. In the fourth embodiment, input terminals for the input voltages PVDDs of the pixel units are connected together within the display region AA, to form a net shaped wiring 44.

**[0046]** The three input paths P1, P2 and P3 are located at different sides of the matrix of the pixel unit. The input path P2 includes two branches P21 and P22, and the input point A21 of the branch P21 and the input point A22 of the branch P22 are symmetrically disposed with respect to the center line of the matrix of the pixel units. The OLED display device 400 further includes detecting wires C21 and C3, which respectively transfer voltages at the input point A21 and A3 to the power supply driver chip 40 for detection and compensation. The method for detecting and compensating is the same as that in the second embodiment, which will not be repeated herein.

**[0047]** In the fourth embodiment, the input paths P1, P3 and the two branches P21 and P22 of the input path P2 are distributed evenly with respect to the matrix of the pixel units, and therefore more stable input voltages may be supplied to the matrix of the pixel units.

**[0048]** In the OLED display device provided in the invention, the power supply driver chip supplies the input voltages to the matrix of the pixel units through two or more input paths, and the pixel units at different locations may have an approximately equal input voltage. Therefore, the problem that from the nearest side to the farthest side to the power supply driver chip voltages of the pixel units are sequentially reduced from one pixel unit to another is resolved, enabling the entire display region of the OLED display device to display with a uniform brightness and improving the display performance. Further, the OLED display device provided in the invention has the function of detecting and correcting the input voltages, and hence the voltages at the respective input points may be consistent or approximate. That is, for all of the pixel units in the entire display region AA, not only the input points are disposed evenly, but also the voltages at the respective input points are the same or approximate, which may further improve the brightness uniformity of the OLED display device.

**[0049]** Obviously, various modifications and variations may be made by those skilled in the art without departing the spirit and scope of the present invention. Therefore, these modifications and variations made within the scope of the appending claims and the equivalent are intended to be included in the present invention.

## Claims

1. An Organic Light-Emitting Diode display device, comprising a plurality of pixel units arranged in a matrix and a power supply driver chip located at one side of the multiple pixel units, wherein the power supply driver chip is configured to supply input voltages to the multiple pixel units through a plurality of input paths, an input point of each of the input paths corresponds to a pixel unit at a different location, and at the input point the input path is connected to the pixel unit.

2. The Organic Light-Emitting Diode display device according to claim 1, wherein:

- 10 a reference voltage is set for the Organic Light-Emitting Diode display device and a detecting wire is disposed for each of the input paths, and the detecting wire is configured to transfer a voltage at the input point of the input path to a detecting point for being compared with the reference voltage; and

- 15 in the case that a voltage difference exists between the voltage at the input point and the reference voltage, the power supply driver chip supplies a compensation voltage to the input path to change the input voltage of the input path, so as to reduce the voltage difference.

3. The Organic Light-Emitting Diode display device according to claim 2, wherein the reference voltage is equal to the input voltage supplied to the input path of which the input point is the nearest to the power supply driver chip, or the reference voltage is equal to a voltage at the input point of any of the input paths.

4. The Organic Light-Emitting Diode display device according to one of claims 2 to 3, wherein the detecting wire is not disposed for the input path of which the input point is the nearest to the power supply driver chip, and the voltage at the input point of the input path is equal to the input voltage supplied to the input path by the power supply driver chip.

5. The Organic Light-Emitting Diode display device according to one of claims 2 to 4, wherein the power supply driver chip is configured to supply a negative compensation voltage to an input path for which the voltage at the input point is higher than the reference voltage, to reduce the input voltage of the input path, so as to reduce the voltage difference; or the power supply driver chip is configured to supply a positive compensation voltage to an input path for which the voltage at the input point is lower than the reference voltage, to increase the input voltage of the input path, so as to reduce the voltage difference.

6. The Organic Light-Emitting Diode display device according to one of the previous claims, wherein the input points of the plurality of input paths are distributed evenly with respect to the matrix of the pixel units.

7. The Organic Light-Emitting Diode display device according to claim 6, wherein the input points of the plurality of input paths are disposed on a same side of the matrix of the pixel units, and input points of the plurality of input paths are spaced by equal number of rows of pixel units.

8. The Organic Light-Emitting Diode display device according to claim 6 or 7, wherein the input path comprises two branches which have an equal path length and are supplied with an equal input voltage by the power supply driver chip, and the input points of the two branches are symmetrically disposed with respect to the center line of the matrix of the pixel unit.

9. The Organic Light-Emitting Diode display device according to claim 8, wherein the input point of at least one of the two branches is connected to a detecting point through a detecting wire.

10. The Organic Light-Emitting Diode display device according to claim 6 or 8 or 9, wherein the input points of the plurality of input path are disposed on different sides of the matrix of the pixel units, and the input points are disposed in left-right asymmetry or in top-bottom asymmetry.

11. The Organic Light-Emitting Diode display device according to one of claims 2 to 10, wherein the detecting point is located inside the power supply driver chip and the comparison between the voltage at the input point and the reference voltage is performed by the power supply driver chip; or the detecting point is located at a panel and the comparison between the voltage at the input point and the reference voltage is performed by an external detecting apparatus.

Fig. 1

Fig. 2

Fig. 3

Fig. 4

Fig. 5

Fig. 6

Fig. 7

## EUROPEAN SEARCH REPORT

Application Number

EP 13 19 4052

5

10

15

20

25

30

35

40

45

50

55

| DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                               |                                                   | CLASSIFICATION OF THE APPLICATION (IPC) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------|

| Category                                                                                                                                                                                                                                                                              | Citation of document with indication, where appropriate, of relevant passages                                                                                                                                                                                 | Relevant to claim                                 |                                         |

| X                                                                                                                                                                                                                                                                                     | US 2013/106676 A1 (ONO SHINYA [JP] ET AL)<br>2 May 2013 (2013-05-02)                                                                                                                                                                                          | 1-7,11                                            | INV.<br>G09G3/32                        |

| Y                                                                                                                                                                                                                                                                                     | * paragraphs [0005], [0012], [0092] - [0093], [0096] - [0100], [0103] - [0106], [0110], [0128] - [0129]; figures 1-4 *                                                                                                                                        | 9                                                 |                                         |

| X                                                                                                                                                                                                                                                                                     | -----<br>US 2001/043168 A1 (KOYAMA JUN [JP] ET AL)<br>22 November 2001 (2001-11-22)<br>* paragraphs [0129] - [0165]; figures 1-5 *                                                                                                                            | 1,2,5,6                                           |                                         |

| X                                                                                                                                                                                                                                                                                     | -----<br>US 2005/117410 A1 (SHIN DONG-YONG [KR])<br>2 June 2005 (2005-06-02)                                                                                                                                                                                  | 1,6,8,10                                          |                                         |

| Y                                                                                                                                                                                                                                                                                     | * paragraphs [0009], [0053] - [0057]; figure 4 *                                                                                                                                                                                                              | 9                                                 |                                         |

| X                                                                                                                                                                                                                                                                                     | -----<br>JP 2008 046393 A (SEIKO EPSON CORP)<br>28 February 2008 (2008-02-28)<br>* paragraphs [0020], [0022] - [0023], [0025], [0026], [0029], [0036], [0038]; figures 3,4,7,9 *                                                                              | 1,6,7                                             |                                         |

| X                                                                                                                                                                                                                                                                                     | -----<br>US 2007/182672 A1 (HOPPENBROUWERS JURGEN J L [NL] ET AL HOPPENBROUWERS JURGEN JEAN LOUIS) 9 August 2007 (2007-08-09)<br>* paragraphs [0004], [0008], [0010] - [0013], [0017], [0021], [0035] - [0037], [0039], [0041], [0044], [0048]; figures 1-4 * | 1,6                                               | TECHNICAL FIELDS<br>SEARCHED (IPC)      |

| X                                                                                                                                                                                                                                                                                     | -----<br>US 2010/141630 A1 (KIMURA HAJIME [JP])<br>10 June 2010 (2010-06-10)<br>* paragraphs [0153] - [0156]; figures 10a,10b,10c,10d *                                                                                                                       | 1                                                 | G09G                                    |

|                                                                                                                                                                                                                                                                                       | -----<br>-----<br>-----                                                                                                                                                                                                                                       | -/-                                               |                                         |

| 1                                                                                                                                                                                                                                                                                     | The present search report has been drawn up for all claims                                                                                                                                                                                                    |                                                   |                                         |

| 1                                                                                                                                                                                                                                                                                     | Place of search<br>Munich                                                                                                                                                                                                                                     | Date of completion of the search<br>28 April 2014 | Examiner<br>Taron, Laurent              |

| CATEGORY OF CITED DOCUMENTS                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                               |                                                   |                                         |

| X : particularly relevant if taken alone<br>Y : particularly relevant if combined with another document of the same category<br>A : technological background<br>O : non-written disclosure<br>P : intermediate document                                                               |                                                                                                                                                                                                                                                               |                                                   |                                         |

| T : theory or principle underlying the invention<br>E : earlier patent document, but published on, or after the filing date<br>D : document cited in the application<br>L : document cited for other reasons<br>.....<br>& : member of the same patent family, corresponding document |                                                                                                                                                                                                                                                               |                                                   |                                         |

## EUROPEAN SEARCH REPORT

Application Number

EP 13 19 4052

| DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   | CLASSIFICATION OF THE APPLICATION (IPC) |                 |                                  |          |        |               |                |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------|-----------------|----------------------------------|----------|--------|---------------|----------------|

| Category                            | Citation of document with indication, where appropriate, of relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Relevant to claim |                                         |                 |                                  |          |        |               |                |

| X                                   | US 2010/245324 A1 (MINAMI TETSUO [JP] ET AL) 30 September 2010 (2010-09-30)<br>* paragraphs [0009], [0041] - [0042], [0056] *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1,6,7<br>-----    |                                         |                 |                                  |          |        |               |                |

| 20                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                                         |                 |                                  |          |        |               |                |

| 25                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                                         |                 |                                  |          |        |               |                |

| 30                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   | TECHNICAL FIELDS<br>SEARCHED (IPC)      |                 |                                  |          |        |               |                |

| 35                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                                         |                 |                                  |          |        |               |                |

| 40                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                                         |                 |                                  |          |        |               |                |

| 45                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                                         |                 |                                  |          |        |               |                |

| 50                                  | <p>The present search report has been drawn up for all claims</p> <table border="1"> <tr> <td>Place of search</td> <td>Date of completion of the search</td> <td>Examiner</td> </tr> <tr> <td>Munich</td> <td>28 April 2014</td> <td>Taron, Laurent</td> </tr> </table>                                                                                                                                                                                                                                                                                                                                         |                   |                                         | Place of search | Date of completion of the search | Examiner | Munich | 28 April 2014 | Taron, Laurent |

| Place of search                     | Date of completion of the search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Examiner          |                                         |                 |                                  |          |        |               |                |

| Munich                              | 28 April 2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Taron, Laurent    |                                         |                 |                                  |          |        |               |                |

| 55                                  | <p>EPO FORM 1503 03.82 (P04C01)</p> <p>CATEGORY OF CITED DOCUMENTS</p> <p>X : particularly relevant if taken alone<br/>Y : particularly relevant if combined with another document of the same category<br/>A : technological background<br/>O : non-written disclosure<br/>P : intermediate document</p> <p>T : theory or principle underlying the invention<br/>E : earlier patent document, but published on, or after the filing date<br/>D : document cited in the application<br/>L : document cited for other reasons<br/>.....<br/>&amp; : member of the same patent family, corresponding document</p> |                   |                                         |                 |                                  |          |        |               |                |

5

**ANNEX TO THE EUROPEAN SEARCH REPORT

ON EUROPEAN PATENT APPLICATION NO.**

EP 13 19 4052

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

10

28-04-2014

|    | Patent document cited in search report |    | Publication date |    | Patent family member(s) |  | Publication date |

|----|----------------------------------------|----|------------------|----|-------------------------|--|------------------|

| 15 | US 2013106676                          | A1 | 02-05-2013       | CN | 102834858 A             |  | 19-12-2012       |

|    |                                        |    |                  | US | 2013106676 A1           |  | 02-05-2013       |

|    |                                        |    |                  | WO | 2012014477 A1           |  | 02-02-2012       |

| 20 | US 2001043168                          | A1 | 22-11-2001       | JP | 2011034090 A            |  | 17-02-2011       |

|    |                                        |    |                  | JP | 2012078841 A            |  | 19-04-2012       |

|    |                                        |    |                  | KR | 20060063837 A           |  | 12-06-2006       |

|    |                                        |    |                  | KR | 20070092694 A           |  | 13-09-2007       |

|    |                                        |    |                  | TW | 554637 B                |  | 21-09-2003       |

|    |                                        |    |                  | TW | 554638 B                |  | 21-09-2003       |

| 25 |                                        |    |                  | US | 2001043168 A1           |  | 22-11-2001       |

|    |                                        |    |                  | US | 2004257312 A1           |  | 23-12-2004       |

|    |                                        |    |                  | US | 2007080917 A1           |  | 12-04-2007       |

| 30 | US 2005117410                          | A1 | 02-06-2005       | CN | 1658262 A               |  | 24-08-2005       |

|    |                                        |    |                  | JP | 4324021 B2              |  | 02-09-2009       |

|    |                                        |    |                  | JP | 2005157269 A            |  | 16-06-2005       |

|    |                                        |    |                  | KR | 20050051309 A           |  | 01-06-2005       |

| 35 |                                        |    |                  | US | 2005117410 A1           |  | 02-06-2005       |

|    | JP 2008046393                          | A  | 28-02-2008       | JP | 4997867 B2              |  | 08-08-2012       |

|    |                                        |    |                  | JP | 2008046393 A            |  | 28-02-2008       |

| 40 | US 2007182672                          | A1 | 09-08-2007       | CN | 1930603 A               |  | 14-03-2007       |

|    |                                        |    |                  | EP | 1728236 A1              |  | 06-12-2006       |

|    |                                        |    |                  | JP | 2007528513 A            |  | 11-10-2007       |

|    |                                        |    |                  | KR | 20070034457 A           |  | 28-03-2007       |

| 45 |                                        |    |                  | US | 2007182672 A1           |  | 09-08-2007       |

|    |                                        |    |                  | WO | 2005088593 A1           |  | 22-09-2005       |

| 50 | US 2010141630                          | A1 | 10-06-2010       | CN | 101833915 A             |  | 15-09-2010       |

|    |                                        |    |                  | JP | 2010156962 A            |  | 15-07-2010       |

|    |                                        |    |                  | US | 2010141630 A1           |  | 10-06-2010       |

| 55 | US 2010245324                          | A1 | 30-09-2010       | CN | 101866615 A             |  | 20-10-2010       |

|    |                                        |    |                  | JP | 2010224416 A            |  | 07-10-2010       |

|    |                                        |    |                  | KR | 20100107395 A           |  | 05-10-2010       |

|    |                                        |    |                  | TW | 201106321 A             |  | 16-02-2011       |

|    |                                        |    |                  | US | 2010245324 A1           |  | 30-09-2010       |

**REFERENCES CITED IN THE DESCRIPTION**

*This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.*

**Patent documents cited in the description**

- CN 201310242553 [0001]

|                |                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | OLED显示器件                                                                    |         |            |

| 公开(公告)号        | <a href="#">EP2816546A1</a>                                                 | 公开(公告)日 | 2014-12-24 |

| 申请号            | EP2013194052                                                                | 申请日     | 2013-11-22 |

| [标]申请(专利权)人(译) | 上海天马微电子有限公司<br>天马微电子股份有限公司                                                  |         |            |

| 申请(专利权)人(译)    | 上海天马微电子有限公司.<br>天马微电子股份有限公司.                                                |         |            |

| 当前申请(专利权)人(译)  | 上海天马微电子有限公司.<br>天马微电子股份有限公司.                                                |         |            |

| [标]发明人         | GU HANYU<br>TSENG CHANG HO                                                  |         |            |

| 发明人            | GU, HANYU<br>TSENG, CHANG-HO                                                |         |            |

| IPC分类号         | G09G3/32                                                                    |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0426 G09G2320/0223 G09G2320/0233 G09G2330/02 G09G3/3258 |         |            |

| 优先权            | 201310242553.3 2013-06-18 CN                                                |         |            |

| 其他公开文献         | EP2816546B1                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                   |         |            |

#### 摘要(译)

一种OLED显示装置，包括以矩阵排列的多个像素单元和位于所述多个像素单元的一侧的电源驱动芯片。电源驱动器芯片被配置为向多个像素单元提供输入电压。电源驱动器芯片通过多个输入路径向多个像素单元提供输入电压。每个输入路径的输入点对应于不同位置处的像素单元，并且在输入点处，输入路径连接到像素单元。在本发明提供的OLED显示装置中，不同位置的所有像素单元可以具有近似相等的输入电压，使得OLED显示装置的整个显示区域能够以均匀的亮度显示并提高显示性能。

Fig. 4