### (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

# (43) International Publication Date 6 March 2008 (06.03.2008)

(51) International Patent Classification: *G09G 3/32* (2006.01)

(21) International Application Number:

PCT/GB2007/003279

- (22) International Filing Date: 30 August 2007 (30.08.2007)

- (25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

0617111.0

31 August 2006 (31.08.2006) G

- (71) Applicant (for all designated States except US): CAMBRIDGE DISPLAY TECHNOLOGY LIMITED [GB/GB]; c/o IP Department, Building 2020, Cambourne Business Park, Cambridgeshire Cambridgeshire CB23 6DW (GB).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): SMITH, Euan [GB/GB]; c/o IP Department, Cambridge Display Technology Ltd, Building 2020, Cambourne Business Park, Cambourne Cambridgeshire CB23 6DW (GB).

# WO 2008/025985 A1

- (74) Agent: GILANI, Anwar; c/o IP Department, Cambridge Display Technology Ltd, Building 2020 Cambourne Business Park, Cambridgeshire, Cambridgeshire CB23 6DW (GB).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI,

[Continued on next page]

#### (54) Title: DISPLAY DRIVE SYSTEMS

(57) Abstract: This invention generally relates to methods, apparatus and computer program code for improved OLED (organic light emitting diode) display drive systems, in particular to compensate for burn-in. A method of compensating an OLED display device for burn-in of pixels of the OLED display, the method comprising: measuring a first voltage drop across at least one test pixel of the display; measuring a second voltage drop across at least one other pixel of the display; determining, from said first and second voltages and a from value (V1) representing a drive voltage increase for a loss in efficiency of said display due to burn-in, an estimated reduction in efficiency of said display due to burn-in; and compensating a drive to said display using said estimated efficiency reduction.

## WO 2008/025985 A1

$FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL, \quad \textbf{Published:} \\$ PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, — with international search report GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Display Drive Systems**

This invention generally relates to methods, apparatus and computer program code for improved OLED (organic light emitting diode) display drive systems, in particular to compensate for burn-in.

Organic light emitting diodes, which here include organometallic LEDs, may be fabricated using materials including polymers, small molecules and dendrimers, in a range of colours which depend upon the materials employed. Examples of polymer-based organic LEDs are described in WO 90/13148, WO 95/06400 and WO 99/48160; examples of dendrimer-based materials are described in WO 99/21935 and WO 02/067343; and examples of so called small molecule based devices are described in US 4,539,507. A typical OLED device comprises two layers of organic material, one of which is a layer of light emitting material such as a light emitting polymer (LEP), oligomer or a light emitting low molecular weight material, and the other of which is a layer of a hole transporting material such as a polythiophene derivative or a polyaniline derivative.

Organic LEDs may be deposited on a substrate in a matrix of pixels to form a single or multi-colour pixellated display. A multicoloured display may be constructed using groups of red, green, and blue emitting sub-pixels. So-called active matrix displays have a memory element, typically a storage capacitor and a transistor, associated with each pixel whilst passive matrix displays have no such memory element and instead are repetitively scanned to give the impression of a steady image. Other passive displays include segmented displays in which a plurality of segments share a common electrode and a segment may be lit up by applying a voltage to its other electrode. A simple segmented display need not be scanned but in a display comprising a plurality of segmented regions the electrodes may be multiplexed (to reduce their number) and then scanned.

2

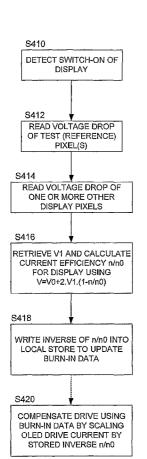

Figure 1a shows a vertical cross section through an example of an OLED device 100. In an active matrix display part of the area of a pixel is occupied by associated drive circuitry (not shown in Figure 1a). The structure of the device is somewhat simplified for the purposes of illustration.

The OLED 100 comprises a substrate 102, typically 0.7 mm or 1.1 mm glass but optionally clear plastic or some other substantially transparent material. An anode layer 104 is deposited on the substrate, typically comprising around 150 nm thickness of ITO (indium tin oxide), over part of which is provided a metal contact layer. Typically the contact layer comprises around 500nm of aluminium, or a layer of aluminium sandwiched between layers of chrome, and this is sometimes referred to as anode metal. Glass substrates coated with ITO and contact metal are available from Corning, USA. The contact metal over the ITO helps provide reduced resistance pathways where the anode connections do not need to be transparent, in particular for external contacts to the device. The contact metal is removed from the ITO where it is not wanted, in particular where it would otherwise obscure the display, by a standard process of photolithography followed by etching.

A substantially transparent hole transport layer 106 is deposited over the anode layer, followed by an electroluminescent layer 108, and a cathode 110. The electroluminescent layer 108 may comprise, for example, a PPV (poly(p-phenylenevinylene)) and the hole transport layer 106, which helps match the hole energy levels of the anode layer 104 and electroluminescent layer 108, may comprise a conductive transparent polymer, for example PEDOT:PSS (polystyrene-sulphonate-doped polyethylene-dioxythiophene) from Bayer AG of Germany. In a typical polymer-based device the hole transport layer 106 may comprise around 200 nm of PEDOT; a light emitting polymer layer 108 is typically around 70 nm in thickness. These organic layers may be deposited by spin coating (afterwards removing material from unwanted areas by plasma etching or laser ablation) or by inkjet printing. In this latter case banks 112 may be formed on the substrate, for example using photoresist, to define wells into which the organic layers may be deposited. Such wells define light emitting areas or pixels of the display.

3

Cathode layer 110 typically comprises a low work function metal such as calcium or barium (for example deposited by physical vapour deposition) covered with a thicker, capping layer of aluminium. Optionally an additional layer may be provided immediately adjacent the electroluminescent layer, such as a layer of barium fluoride, for improved electron energy level matching. Mutual electrical isolation of cathode lines may be achieved or enhanced through the use of cathode separators (not shown in Figure 1a).

The same basic structure may also be employed for small molecule and dendrimer devices. Typically a number of displays are fabricated on a single substrate and at the end of the fabrication process the substrate is scribed, and the displays separated before an encapsulating can is attached to each to inhibit oxidation and moisture ingress.

To illuminate the OLED power is applied between the anode and cathode, represented in Figure 1a by battery 118. In the example shown in Figure 1a light is emitted through transparent anode 104 and substrate 102 and the cathode is generally reflective; such devices are referred to as "bottom emitters". Devices which emit through the cathode ("top emitters") may also be constructed, for example by keeping the thickness of cathode layer 110 less than around 50-100 nm so that the cathode is substantially transparent.

It will be appreciated that the foregoing description is merely illustrative of one type of OLED display, to assist in understanding some applications of embodiments of the invention. There is a variety of other types of OLED, including reverse devices where the cathode is on the bottom such as those produced by Novaled GmbH. Moreover application of embodiments of the invention are not limited to displays, OLED or otherwise.

Organic LEDs may be deposited on a substrate in a matrix of pixels to form a single or multi-colour pixellated display. A multicoloured display may be constructed using groups of red, green, and blue emitting pixels. In such displays the individual elements are generally addressed by activating row (or column) lines to select the pixels, and rows (or columns) of pixels are written to, to create a display. So-called active matrix

4

displays have a memory element, typically a storage capacitor and a transistor, associated with each pixel whilst passive matrix displays have no such memory element and instead are repetitively scanned, somewhat similarly to a TV picture, to give the impression of a steady image.

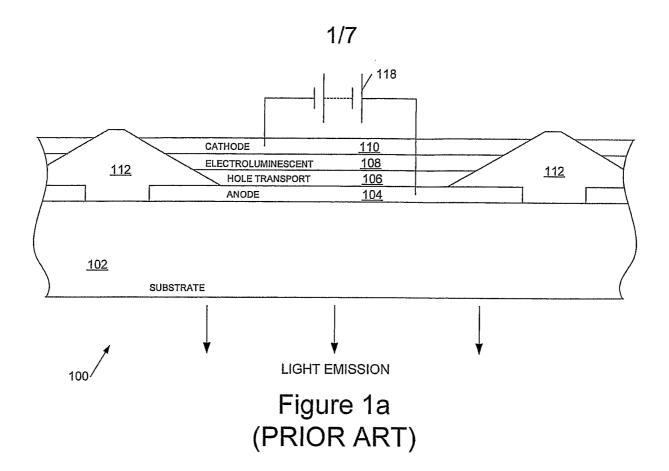

Referring now to Figure 1b, this shows a simplified cross-section through a passive matrix OLED display device 150, in which like elements to those of figure 1a are indicated by like reference numerals. As shown the hole transport 106 and electroluminescent 108 layers are subdivided into a plurality of pixels 152 at the intersection of mutually perpendicular anode and cathode lines defined in the anode metal 104 and cathode layer 110 respectively. In the figure conductive lines 154 defined in the cathode layer 110 run into the page and a cross-section through one of a plurality of anode lines 158 running at right angles to the cathode lines is shown. An electroluminescent pixel 152 at the intersection of a cathode and anode line may be addressed by applying a voltage between the relevant lines. The anode metal layer 104 provides external contacts to the display 150 and may be used for both anode and cathode connections to the OLEDs (by running the cathode layer pattern over anode metal lead-outs). The above mentioned OLED materials, in particular the light emitting polymer and the cathode, are susceptible to oxidation and to moisture and the device is therefore encapsulated in a metal can 111, attached by UV-curable epoxy glue 113 onto anode metal layer 104, small glass beads within the glue preventing the metal can touching and shorting out the contacts.

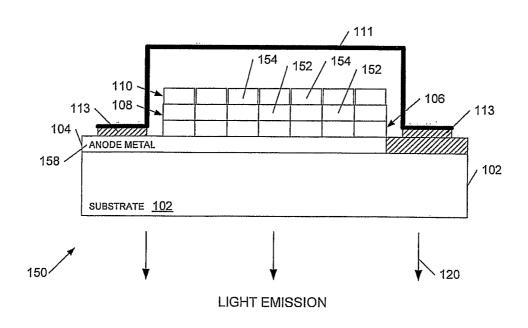

Referring now to Figure 2, this shows, conceptually, a driving arrangement for a passive matrix OLED display 150 of the type shown in Figure 1b. A plurality of constant current generators 200 are provided, each connected to a supply line 202 and to one of a plurality of column lines 204, of which for clarity only one is shown. A plurality of row lines 206 (of which only one is shown) is also provided and each of these may be selectively connected to a ground line 208 by a switched connection 210. As shown, with a positive supply voltage on line 202, column lines 204 comprise anode connections 158 and row lines 206 comprise cathode connections 154, although the connections would be reversed if the power supply line 202 was negative and with respect to ground line 208.

As illustrated pixel 212 of the display has power applied to it and is therefore illuminated. To create an image connection 210 for a row is maintained as each of the column lines is activated in turn until the complete row has been addressed, and then the next row is selected and the process repeated. Preferably, however, to allow individual pixels to remain on for longer and hence reduce overall drive level, a row is selected and all the columns written in parallel, that is a current driven onto each of the column lines simultaneously to illuminate each pixel in a row at its desired brightness. Each pixel in a column could be addressed in turn before the next column is addressed but this is not preferred because, inter alia, of the effect of column capacitance.

The skilled person will appreciate that in a passive matrix OLED display it is arbitrary which electrodes are labelled row electrodes and which column electrodes, and in this specification "row" and "column are used interchangeably.

It is usual to provide a current-controlled rather than a voltage-controlled drive to an OLED because the brightness of an OLED is determined by the current flowing through the device, this determining the number of photons it generates. In a voltage-controlled configuration the brightness can vary across the area of a display and with time, temperature, and age, making it difficult to predict how bright a pixel will appear when driven by a given voltage. In a colour display the accuracy of colour representations may also be affected.

The conventional method of varying pixel brightness is to vary pixel on-time using Pulse Width Modulation (PWM). In a conventional PWM scheme a pixel is either full on or completely off but the apparent brightness of a pixel varies because of integration within the observer's eye. An alternative method is to vary the column drive current.

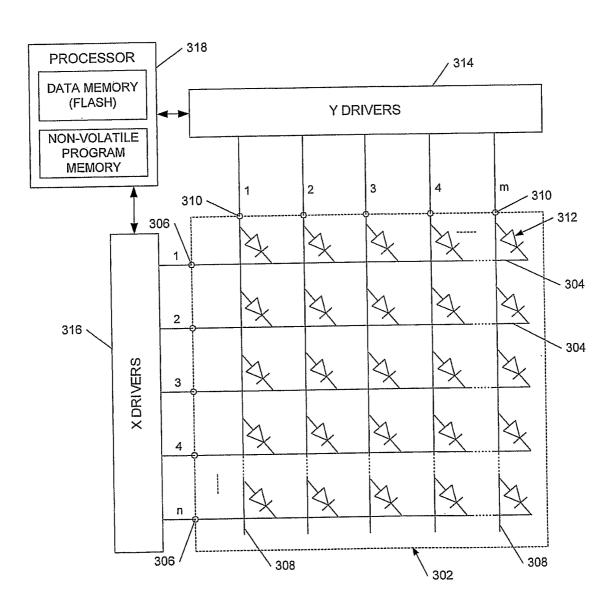

Figure 3 shows a schematic diagram 300 of a driver for a passive matrix OLED display suitable for implementing embodiments of the invention, as described further later. The OLED display is indicated by dashed line 302 and comprises a plurality n of row lines 304 each with a corresponding row electrode contact 306 and a plurality m of column lines 308 with a corresponding plurality of column electrode contacts 310. An OLED is

6

connected between each pair of row and column lines with, in the illustrated arrangement, its anode connected to the column line. A y-driver 314 drives the column lines 308 with a constant current and an x-driver 316 drives the row lines 304, selectively connecting the row lines to ground. The y-driver 314 and x-driver 316 are typically both under the control of a processor 318. A power supply 320 provides power to the circuitry and, in particular, to y-driver 314.

Some examples of OLED display drivers are described in US 6,014,119, US 6,201,520, US 6,332,661, EP 1,079,361A and EP 1,091,339A and OLED display driver integrated circuits employing PWM are sold by Clare Micronix of Clare, Inc., Beverly, MA, USA. Some examples of improved OLED display drivers are described in the Applicant's copending applications WO 03/079322 and WO 03/091983. In particular WO 03/079322, hereby incorporated by reference, describes a digitally controllable programmable current generator with improved compliance.

One problem associated with OLED displays is that, over time, the pixels "burn-in", that is the drive voltage required for a given drive current (and hence luminosity) increases with use. In particular, luminosity at a given current may fall sharply during initial driving of an OLED display, with subsequent luminosity decaying more uniformly. Thus two different but related problems can arise from burn-in: firstly a general aging of the display with use, and secondly image burn-in, where persistent display of an image can cause differential aging of pixels of the display. Screen savers provide one technique for addressing this problem, but only in the context of computer monitor display and, for example, it is becoming more common for television channels to display a persistent logo or other branding discreetly in a corner of the screen. A further problem associated with OLED displays is that displays that are stored but not driven for an extended period of time may suffer from decreased luminosity as compared to a display that is driven without having been stored for extended periods. Possible reasons for this decreased luminosity may be ingress of moisture and oxygen into an imperfectly encapsulated display or migration of chemical species from one layer of the display to another (for example, migration of metal ions from a cathode layer into an organic layer).

7

For many OLED material systems the increase in drive voltage with driven time for a given current and temperature can be correlated to the decay in device efficiency. One could attempt to implement a compensation scheme which monitors the voltage drop across an OLED and which corrects the drive signal accordingly. However this approach suffers from a drawback in that the voltage drop across the OLED also varies with temperature, and this could result in a brightness variation across the display proportional to temperature across the display.

#### SUMMARY OF THE INVENTION

According to the present invention there is therefore provided a method of compensating an OLED display device for burn-in of pixels of the OLED display, the method comprising: measuring a first voltage drop across at least one test pixel of the display; measuring a second voltage drop across at least one other pixel of the display; determining, from said first and second voltages and a from value (V<sub>1</sub>) representing a drive voltage increase for a loss in efficiency of said display due to burn-in, an estimated reduction in efficiency of said display due to burn-in; and compensating a drive to said display using said estimated efficiency reduction.

Preferably the value representing a voltage increase for a loss in the efficiency of the display represents an increase in a pixel drive voltage needed to compensate for a defined level of efficiency reduction, for example 50% (corresponding to a 50% drop in OLED brightness). This defined level of efficiency reduction can be used to define an (arbitrary) end of life for the OLED pixel. With this example, because the response of the human eye is non-linear a 50% reduction in actual brightness corresponds to something like an 80% reduction in perceived brightness. The determining of the estimated reduction in efficiency of the display (which may be defined as a ratio of end-of-life efficiency to initial efficiency) may then employ a relationship dependent upon this defined level of efficiency reduction – that is, in effect, the increase in pixel drive voltage is defined in relation to a predetermined level of efficiency reduction such as the aforementioned 50%. The increase in the pixel drive voltage is preferably stored, for example on a driver integrated circuit; the value may be initially derived from

8

laboratory measurements made for a device or on one of a batch of manufactured devices.

Broadly speaking, in embodiments of the method the voltage drop across the test pixel comprises a temperature-dependent voltage drop and thus by taking this into account the method can automatically compensate for temperature variations of the display. (The end-of-life increase in pixel drive voltage is not particularly temperature dependent). Nonetheless it is strongly preferable that the first and second voltage drops are measured at (immediately or soon after) switch-on of the display, that is when the display is at a substantially uniform temperature. In a more sophisticated implementation provision may be made to determine whether the display has been switched off for a sufficiently long period to have cooled down so that the reduction in efficiency may be estimated only when the pixels of the display have reached approximately the same temperature. This may be implemented in practice using, for example, a low-leakage capacitor as a timing element.

In preferred embodiments of the method the compensating for reduced efficiency comprises increasing a drive current to a pixel of the display by a factor dependent upon an inverse of the estimated efficiency reduction. This is because OLEDs are preferably operated as current-controlled devices, when there is a substantially linear relationship between the current through the device and the OLED brightness.

In some embodiments of the method the efficiency reduction may be estimated based upon just two measurements, that on the test pixel and that on one other pixel, and this estimated efficiency reduction may be used to compensate drive signals for the whole display. This may provide sufficiently accurate compensation for the burn-in. However in other embodiments of the method a said second voltage drop may be measured for a plurality of pixels of the display and an average calculated for use in determining the efficiency reduction. Alternatively a number of different efficiency reduction values may be determined from the measured pixels and these may then be used to compensate those pixels and regions in their vicinity. For example a display could be subdivided into two, four or more partitions for separate compensation in this way.

9

In one embodiment of the method the test pixel comprises a dummy pixel, not used for displaying information. For example the test pixel may be in an unused, edge portion of the display. In other embodiments the test pixel may be in an active region of the display, that is a part of the display used for displaying information under normal operating conditions. In these embodiments the other pixels are corrected relative to the selected test pixel or pixels. In some versions of these embodiments the test pixel is selected from the 20% of pixels of the display having least aging. Thus in some preferred embodiments a test pixel may comprise a substantially least aged pixel of the display. The one or more least aged pixels of the display may be identified by measuring a current voltage drop for a given, test drive current, the least aged pixel having the least current voltage drop. Alternatively the time for which a pixel is on at greater than a threshold value, for example 50%, may be monitored to find the least aged pixel or pixels.

The skilled person will understand that multiple test pixels (either active or dummy) may be employed. Then either an average first voltage drop may be determined or separate efficiency reduction estimations may be made based upon the multiple test pixels, these being used to compensate the display, for example in different respective regions of the display.

٠:

In embodiments of the method where the test pixel comprises a pixel which is active in normal display use the method may compensate the drive to the display by determining the reduction (or otherwise) in efficiency of one or more other pixels in relation to the monitored pixel. In particular the method may include measuring a time for which an active test pixel is on, for example at greater than a threshold drive level, say 50%. Knowing this on-time the estimated drive voltage increase may be predicted (by predicting an estimated reduction in efficiency of the test pixel) and since the actual voltage drop is measured this may be employed to provide an indirect measure of the temperature of the test pixel or, more generally, of the display. Optionally an actual estimated temperature for the display may be determined, although this is not necessary. This information may then be used to compensate the drive to other pixels of the display by compensating for the temperature of the display using the measured on-time, more particularly by comparing the measured voltage drop of the test pixel with the predicted

10

voltage drop. With embodiments of such a method multiple test pixels across the display may be employed to provide improved compensation taking account of possible temperature differences across the display, in embodiments by averaging voltage drops across a plurality of "active" test pixels.

The skilled person will understand that the above-described techniques may be applied to both monochrome and colour displays; thus references to a pixel include sub-pixels of a colour display. In a colour display two or three of the different colours, typically red, blue and green, may be monitored and compensated separately, or an average compensation may be determined and applied to all the colours, optionally with a colour-dependent adjustment factor. It may be desirable, for example, to estimate and compensate for efficiency reduction in blue sub-pixels separately to red and/or green coloured sub-pixels.

In a related aspect the invention provides a method of controlling a drive to a pixel of an OLED display, the method comprising determining a drive voltage, V, for said pixel using:

$$V = V_0 + \frac{1}{1 - \alpha} V_1 \left( 1 - \frac{\eta}{\eta_0} \right)$$

where  $V_0$  and  $\eta_0$  are a voltage drive to said pixel at a test drive current and a luminance efficiency of said pixel at said test drive current at an initial time; and  $V_1$  is an end of life voltage increase in said voltage drive for said test drive current; and wherein said end of life is defined as a point at which an efficiency,  $\eta$ , of said pixel has fallen to  $\alpha$  of an initial efficiency value ( $\eta_0$ ) at said initial time.

In a further related aspect the invention provides an OLED display driver, the display driver comprising: an input for measuring a first voltage drop across at least one test pixel of the display; an input for measuring a second voltage drop across at least one other pixel of the display; a store storing a value  $(V_1)$  representing a drive voltage increase for a loss in efficiency of said display; a system for determining an estimated

11

reduction in efficiency of said display from said first and second voltages and said value  $(V_1)$  representing said drive voltage increase for a loss in efficiency of said display; and a system for compensating a drive to said display using said estimated efficiency reduction.

Embodiments of the above display driver may be employed in combination with an OLED display, in particular an active matrix OLED display. Preferably such an active matrix OLED display is configured for measuring a voltage across an OLED device of a pixel of the display.

Thus in a further aspect the invention provides an active matrix OLED display pixel driver circuit said pixel driver circuit including a transistor having an input connection coupled to an OLED device of the pixel for measuring a voltage across said OLED device, an output coupled to a first electrode line of said display and a control connection coupled to a second electrode line of said display.

In embodiments the extra transistor of the pixel driver circuit need not be implemented in every pixel of an active matrix display, but only on a few of the pixels, that is those for which voltage drop measurements are desired. In embodiments the pixel driver circuit is implemented in a row (or column) of the display and the second electrode line comprises a power supply line of an adjacent row (or column) of the display. Preferably the second electrode line comprises a positive supply line and the transistor is controlled on by pulling the control connection low. In this way there is no need for an additional select line because the voltage supply line for, say, the row of pixels below the pixel to be measured can be used as a select line.

In a passive matrix display the voltage drop across an OLED device is generally accessible substantially directly via the relevant row and column lines. In both an active and a passive matrix display optionally provision may be made to compensate for electrode line resistance, for example by performing a calibration at the design stage and incorporating a line resistance compensation factor in the display driver/method.

As previously mentioned, preferably the system for measuring the voltage drops is responsive to switch-on of the display so that the measurements can be made at or soon after switch-on. The measurements need not be made every time the display is switched on and may be made, for example, every tenth switch on.

The invention further provides a carrier medium carrying processor control code to implement the above-described methods and display drivers. This code may comprise conventional program code, for example source, object or executable code in a conventional programming language (interpreted or compiled) such as C, or assembly code, code for setting up or controlling an ASIC (Application Specific Integrated Circuit) or FPGA (Field Programmable Gate Array), or code for a hardware description language such as Verilog (Trade Mark) or VHDL (Very high speed integrated circuit Hardware Description Language). Such code may be distributed between a plurality of coupled components. The carrier medium may comprise any conventional storage medium such as a disk or programmed memory (for example firmware such as Flash RAM or ROM), or a data carrier such as an optical or electrical signal carrier.

These and other aspects of the of the invention will now be further described, by way of example only, with the reference to the accompanying figures in which:

Figures 1a and 1b show, respectively, a vertical cross section through an OLED device, and a simplified cross section through a passive matrix OLED display;

Figure 2 shows conceptually a driving arrangement for a passive matrix OLED display;

Figure 3 shows a block diagram of a passive matrix OLED display driver suitable for embodying an aspect of the present invention;

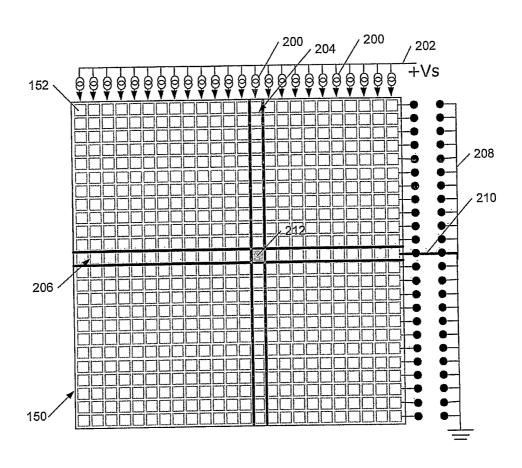

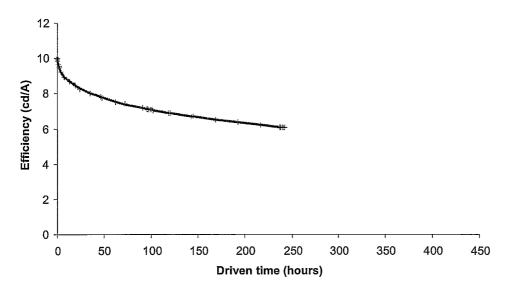

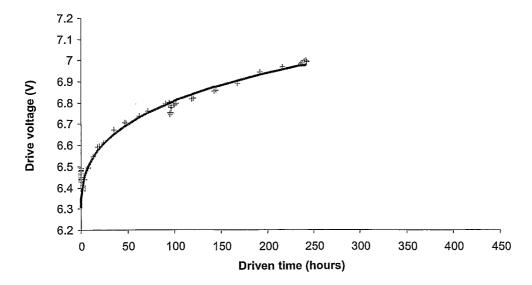

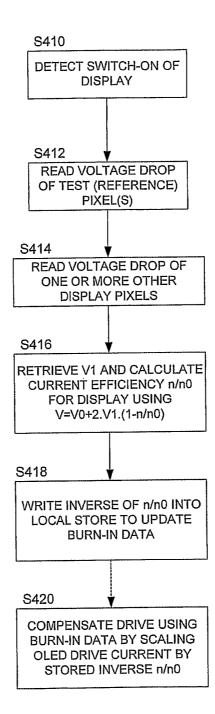

Figures 4a to 4c show, respectively, a graph of OLED efficiency against time, a graph of OLED drive voltage against time, and a flow diagram of a procedure for compensating an OLED display device for burn-in; and

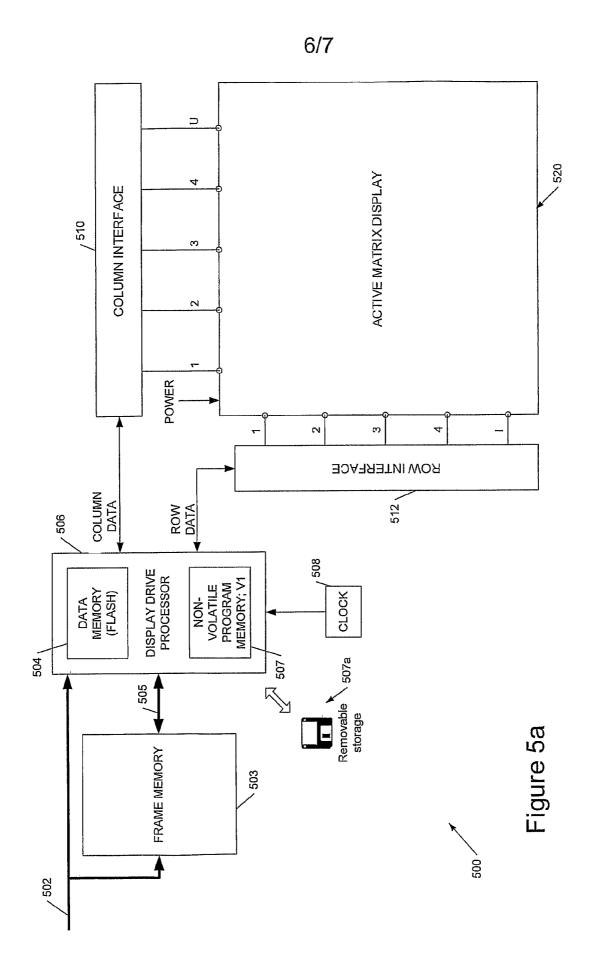

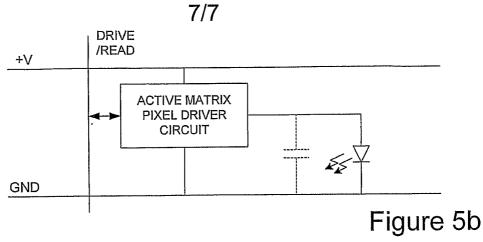

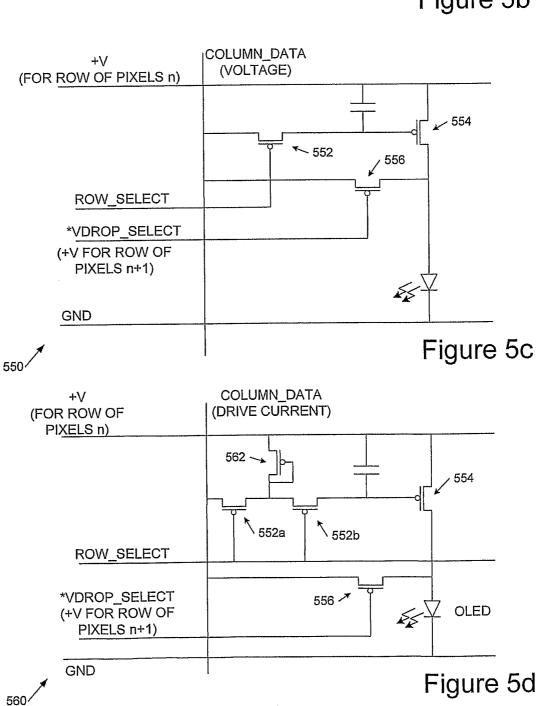

Figures 5a to 5d show, respectively, an active matrix display driver embodying an aspect of the present invention, a conceptual diagram of a first example of an active matrix pixel driver circuit suitable for measuring the voltage drop across an OLED device of the pixel, a detailed example of a voltage-controlled active matrix pixel driver circuit configured for measuring the voltage drop across an OLED device of the pixel, and, a detailed example of a current-controlled active matrix pixel driver circuit configured for measuring the voltage drop across an OLED device of the pixel.

#### DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

Referring to Figures 4a and 4b these show, respectively, the efficiency of an OLED (in candelas per amp) and the drive voltage of an OLED (in volts) against driven time (in hours). Both graphs have been fitted with the same stretched exponential function,

$$\exp -\left(\frac{t}{\tau}\right)^n$$

or  $1 - \exp -\left(\frac{t}{\tau}\right)^n$

and it can be seen that there is a strong correlation between the fall-off in efficiency of the OLED device and the increased drive voltage needed for the same drive current/light output. The drive voltage, *V*, can be expressed as follows:

$$V = V_0 = 2V_1 \left( 1 - \frac{\eta}{\eta_0} \right) \tag{1}$$

where  $V_0$  and  $\eta_0$  are the voltage and efficiency at time t=0, and  $V_1$  is the end-of-life voltage increase. As previously mentioned in embodiments of the invention we arbitrarily define the end-of-life as the half-efficiency point so that in Equation (1) above at the end-of-life point  $\eta/\eta_0 = 1/2$  and thus  $V = V_0 + V_1$ .

In Equation (1)  $V_0$  is dependent upon the temperature, T, of the OLED device and may be specified, for example, at 25°C; to make this clearer  $V_0$  may be written as  $V_0$  (T).

Nonetheless we will describe how, in embodiments of the invention, it is not necessary to know the temperature in order to make use of Equation (1). The value of  $V_1$  is not very temperature dependent. We will describe a number of techniques which may be employed to correct burn-in, in particular image burn-in, on an OLED display, based upon the above observations and upon Equation (1). In general these techniques employ monitoring of OLED current-voltage characteristics, for example a voltage drop across an OLED device at a given drive current, preferably at switch-on. Broadly speaking the techniques use the increase in drive voltage, compared between pixels on the display, at a test current, to correct for burn-in. In this way burn-in effects on the display may be reduced.

A first technique is to include one or a number of test pixels around the edge of the display which are used as a reference. At turn-on the voltage drop over one, some or all OLEDs in the display is measured and compared to the test device(s). This can substantially remove the dependence on temperature, although it is preferable that this test takes place at initial turn-on, when the whole display is at a uniform temperature.

A second method does not use external reference devices, but rather compares OLEDs in the display to each other, in particular by using the device with the smallest voltage drop (i.e. the least aged) as the reference and correcting one, some or all the other efficiency drop(s) as if this device were pristine. This gives, to first order, a correction for image burn-in although not for overall display aging. However it is image burn-in which is generally by far the most significant of the two issues.

A further method is to pick one (or more) particular pixel(s) in the display and to accurately track its use and voltage drop. The voltage drops of one, some or all other pixels in the display are compared to this one and, since the degree of aging experienced by this pixel is known, the aging of the others can be ascertained.

A modification of this method is to use a selection of pixels across the display as references. Each other pixel may then be referenced to the tracked pixel closest to it. This can help to reduce the impact of possible temperature variations over the display area.

15

All these techniques are applicable to both active and passive matrix displays. Optimally voltage drops due to track resistances can be corrected for.

Referring again to Equation (1) above, consider first the case of a dummy (unused) test pixel. Since this is not aged  $\eta = \eta_0$  and hence a measurement of the voltage drop across this test pixel,  $V_{now}^{test}$ , at a set drive current provides a value for  $V_0$  (at the current temperature). Thus for another pixel of the display the voltage drop is given by

$$V_{now}^{test} = V_{now}^{other} + 2V_1 \left( 1 - \frac{\eta}{\eta_0} \right)$$

(2)

This can be used to calculate a value of  $\frac{\eta}{\eta_0}$  for the display or, for multiple other pixels, an average value of  $\eta/\eta_0$  or, alternatively, a value of  $\eta/\eta_0$  for each pixel of the display (or each colour sub-pixel) or for regions of the display. Once this value has been obtained the inverse,  $\frac{\eta}{\eta_0}$  can be used to scale the drive current or, for a voltage-controlled pixel, to determine a desired drive current from which a drive voltage can be obtained. Thus in embodiments a drive signal can be scaled as follows:

$$DRIVE_{now} = DRIVE_{requested} \times \left(\frac{\eta_0}{\eta}\right)$$

(3)

Referring now to Figure 4c, this shows a procedure to implement the above-described method, for example in computer program code. Thus at step S410 the procedure detects switch-on of the display and then reads a voltage drop across one or more test (reference) pixels and a voltage drop across one or more other, display pixels (S412, S414). Then the procedure retrieves a value for  $V_1$ , for example stored on a driver chip at manufacture, and calculates a current efficiency for the display,  $\frac{\eta}{\eta_0}$ , using Equation

(1) above (S416). An average value of  $\frac{\eta}{\eta_0}$  may be calculated for the whole display but

16

in some preferred embodiments a value of  $\frac{\eta}{\eta_0}$  may be calculated for each pixel or sub-

pixel of the display. This data is written into local storage, for example Flash memory to update the burn-in compensation data (S418). This concludes the burn-in calibration. Subsequently during operation of the display a requested drive, for example a drive current, is compensated using the stored efficiency data, either separately for each pixel or using the global value for the display, in particular by scaling a pixel drive in accordance with Equation (3).

In the second of the above-described methods an active pixel of the display rather than a dummy pixel is used as the test pixel for the calibration. In particular a least aged pixel is employed as may be determined by measuring the on-time of each pixel or as may be determined by identifying a pixel with a minimum voltage drop. The latter determination is straightforward in a passive matrix display; in an active matrix display the determination may be made by providing circuitry to allow the voltage drop of each pixel (more precisely an OLED image pixel) to be monitored, as described further below. The voltage drop across the OLED of this least-aged pixel,  $V_{now}^{min}$ , is given by:

$$V_{now}^{min} = V_0 = 2V_1 \left( 1 - \frac{\eta^m}{\eta_0} \right)$$

(4)

where  $\eta^m$  is the current efficiency of the minimum-aged pixel. Now subtracting Equation 2 from Equation 4 we have:

$$V_{now}^{other} - V_{now}^{min} = \left[ \left( 1 - \frac{\eta}{\eta_0} \right) - \left( 1 - \frac{\eta^m}{\eta_0} \right) \right] 2V_1 \tag{5}$$

Rearranging:

$$\frac{\square V}{2V_1} = \frac{\eta^m}{\eta_0} - \frac{\eta}{\eta_0} \tag{6}$$

where  $\Delta V = V_{now}^{other}$  -  $V_{now}^{min}$  . Thus:

$$1 - \frac{\Box V}{2V_1} = 1 - \frac{\eta^m}{\eta_0} + \frac{\eta}{\eta_0} \perp \frac{\eta}{\eta_0}$$

(7)

if

$$\frac{\eta^m}{n_c} \sqcup 1$$

We have measured  $\Delta V$  and know  $V_1$  and can therefore calculate the scaling factor  $\frac{\eta}{\eta_0}$  as the left hand side of Equation (7), for use in Equation (3) above.

Referring again to Equation (7), the scaling factor is:

$$\left(1 - \frac{\eta^{m}}{\eta_{0}} + \frac{\eta}{\eta_{0}}\right)^{-1} = \left(\frac{\eta + \eta_{0} - \eta^{m}}{\eta_{0}}\right)^{-1}$$

and therefore the scaled luminance for the "other" pixel is:

$$L^{other} = \eta \left( rac{\eta + \eta_0 - \eta^m}{\eta_0}

ight)^{\!-1} J = rac{\eta \eta_0}{\eta + \eta_0 - \eta^m} J \square \eta^m J$$

where J is current density (equivalent to drive current). From this it can be seen that the luminance of the other pixel is scaled approximately to that of the minimum aged pixel (although here there is no overall age compensation).

The error in assuming that  $\frac{\eta^m}{\eta_0}$  is approximately unity can be calculated and for a ratio of 0.9 is approximately 1%, for a ratio of 0.8 is approximately 5% and for a ratio of .0.7 is approximately 10%. In terms of an error in the compensation applied, as opposed to the actual drive signal, this is acceptable in many circumstances.

18

The above-described method may be implemented by substantially the same procedure as shown in Figure 4c and described above.

In a further alternative method the use of one or more active test pixels in the display is monitored to determine an on-time,  $t_{ON}$ , from which a drop in efficiency may be predicted according to Equation (8) below in which  $\tau$  and n are known, for example having previously been measured for the relevant OLED material and stored on-chip:

$$\frac{\eta}{\eta_0} = \exp\left(\frac{t_{ON}}{\tau}\right)^n \tag{8}$$

From this a value for  $V_0$  may be calculated:

$$V_{now}^{test} = V_0(T) + \left(1 - \frac{\eta}{\eta_0}\right)_{calc} 2V_1 \tag{9}$$

where the temperature dependence of  $V_0$  is shown explicitly. Then a value for the current efficiency of another pixel,  $\frac{\eta}{\eta_0}$ , may be determined as follows:

$$V_{now}^{other} = V_0 (T) + \left(1 - \frac{\eta}{\eta_0}\right) 2V_1$$

(10)

Optionally an average over multiple test pixels may be employed to determine  $V_0(T)$ . Additionally or alternatively different values of  $V_0(T)$  may be determined for different regions of the display. In either case better robustness against temperature changes across the display may be achieved.

Again embodiments of this method may be implemented by a procedure similar to that in Figure 4c, with the addition of a step to predict an efficiency drop of a test pixel based upon its tracked use.

19

Referring back once more to Figure 3, the skilled person will readily appreciate that the voltage drop across an OLED is effectively directly available via the row and column electrodes of the display, albeit preferably with line resistance calibrated out. In Figure 3 the non-volatile programme memory may be employed to store a procedure for implementing embodiments of the invention for example as shown Figure 4c, and the data memory may be employed, for example, to store pixel efficiency value data.

Figure 5a shows an example of an active matrix OLED display controller 500 which may, likewise, include code for implementing a procedure according to an embodiment of the invention in the non-volatile programme memory (preferably also stores data defining a value of  $V_I$ ) and data memory, for example Flash memory storing pixel efficiency value or other drive compensation data.

In more detail the OLED driver system 500 comprises a data and control bus 502, which may be either serial or parallel, to receive data for display. In the example illustrated this provides an input to a frame store memory 503 which stores luminance and optionally colour data for pixels of the display and which provides an interface via a second bus 505 to a display drive processor 506. Processor 506 may be implemented entirely in hardware or in software using, for example, a digital signal processing core, or in a combination of the two such as software with hardware acceleration. In the illustrated embodiment a processor 506 has a clock 508 and includes programme memory 507 and data/working memory 504; some or all of the contents of either or both of these memories may be provided on a carrier medium, illustratively shown by removal storage medium 507a.

Processor 506 has bidirectional connections 509, 511 with column interface circuitry 510 and row interface circuitry 512 for an active matrix display 520. The bidirectional connections allow row and column data to be provided to the display 520 and voltage drop data to be read from the display 520. (In other arrangements only the connection to one of the row and column interfaces is bidirectional; in still others a separate connection is provided to receive voltage drop data from the display).

20

In the above-described embodiments a voltage drop of at least one active display pixel is read. There is a number of ways to achieve this for an active matrix OLED display.

One option is to include dedicated sensing circuitry and associated connections in the space between pixel circuits in a top-emitting display, where the pixel drive circuitry is not precisely aligned with the overlying OLED pixels, as described in more detail in our co-pending UK patent application no. 0612973.8 filed 30 June 2006 and equivalents thereof hereby incorporated by reference in its entirety.

Another technique is similar to that described in the applicant's international patent applications WO 03/107313 and WO 03/107318 (hereby incorporated by reference in their entirety).

The overall power supply voltage to the active matrix display (or to a specific row or column thereof) is controlled and the current drawn by the display is monitored, whilst displaying a pattern of pixels which are to be monitored. The voltage drop across the source-drain connections of a field effect transistor is substantially constant at a known value (dependent upon the current) whilst the transistor is in saturation. Thus the overall power supply to the active matrix display can be reduced until a knee in the supply current is identified, that is identifying the point at which the total supply current begins to drop significantly. At this point the drain-source voltage drop across the transistor is known, the overall power supply voltage is known and therefore the voltage drop across the OLED device can be calculated by subtracting the drain-source voltage from the total supply voltage. This technique can also be applied for each row and/or column of the display separately.

Figure 5b show, conceptually, a further alternative approach in which a capacitor is connected across the OLED and then afterwards discharged, a measurement of the charge during the discharge being proportional to the voltage across the OLED device.

Figure 5c shows an example of a voltage-controlled active matrix pixel driver circuit 550 in which a first select transistor 552 couples the column data line to the gate of a drive transistor 554, and in which a second select transistor 556 couples the column data

21

line to a terminal of the OLED device driven by the drive transistor (the other terminal being connected to ground). Bringing the gate of transistor 556 low switches the transistor on and in embodiments this select line may be coupled to a supply line for the next row of pixels in order that an additional select line is not required.

Figure 5d shows another example of an active matrix pixel drive circuit 560 incorporating a similar select transistor (like elements are indicated by like reference numerals), but in this case illustrating a current-controlled rather than a voltage-controlled circuit (transistor 562 forms a current mirror with drive transistor 554). In a still further example circuit (not shown) transistor 562 may be replaced with a photodiode so that the column drive programmes a light output from the OLED device.

No doubt many other effective alternatives will occur to the skilled person. It will be understood that the invention is not limited to the described embodiments and encompasses modifications apparent to those skilled in the art lying within the spirit and scope of the claims appended hereto.

#### **CLAIMS:**

WO 2008/025985

- 1. A method of compensating an OLED display device for burn-in of pixels of the OLED display, the method comprising:

- measuring a first voltage drop across at least one test pixel of the display; measuring a second voltage drop across at least one other pixel of the display; determining, from said first and second voltages and a from value  $(V_1)$  representing a drive voltage increase for a loss in efficiency of said display due to burnin, an estimated reduction in efficiency of said display due to burn-in; and compensating a drive to said display using said estimated efficiency reduction.

- 2. A method as claimed in claim 1 wherein said value  $(V_1)$  representing said loss in efficiency of said display comprises a stored value representing an increase in a pixel drive voltage needed to compensate for a defined level of efficiency reduction, and wherein said determining comprises determining said reduction in efficiency using a relationship dependent on said defined level of efficiency reduction.

- 3. A method as claimed in claim 1 or 2 wherein said measuring of said first and second voltage drops is performed at switch-on of said display.

- 4. A method as claimed in claim 1, 2 or 3 wherein said compensating comprises increasing a drive current to a pixel of said display by a factor dependent upon an inverse of said estimated efficiency reduction.

- 5. A method as claimed in any one of claims 1 to 4 comprising measuring said second voltage drop for a plurality of pixels of said display and calculating an average from said measured second voltage drops for use in said determining of said efficiency reduction.

- 6. A method as claimed in any one of claims 1 to 4 comprising measuring said second voltage drop for a plurality of pixels of said display, wherein said determining of said efficiency reduction comprises determining a plurality of efficiency reduction values for said plurality of pixels, and wherein said compensating uses respective ones

23

of said efficiency values for compensating a drive for respective ones of said plurality of pixels.

- 7. A method as claimed in any one of claims 1 to 6 wherein said test pixel comprises a pixel of the display which is not used for displaying information.

- 8. A method as claimed in any one of claims 1 to 6 wherein said test pixel comprises a pixel in a region of said display used for displaying information.

- 9. A method as claimed in claim 8 wherein said test pixel is selected from the 20% of pixels of said display having least aging.

- 10. A method as claimed in claim 9 wherein said test pixel comprises a substantially least aged pixel of said display.

- 11. A method as claimed in any one of claims 8 to 10 further comprising measuring a time for which said test pixel is on at greater than threshold drive level; and wherein said determining of said estimated efficiency reduction comprises compensating for temperature using said measured on-time.

- 12. A method as claimed in any one of claims 1 to 11 comprising measuring said first voltage drop for a plurality of pixels of said display and calculating an average from said measured first voltage drops for use in said determining of said efficiency reduction.

- 13. A method as claimed in any one of claims 1 to 11 comprising measuring said first voltage drop for a plurality of pixels of said display, wherein said determining of said efficiency reduction comprises determining a plurality of efficiency reduction values for said plurality of pixels, and wherein said compensating uses respective ones of said efficiency values for compensating pixel drives to different respective regions of said display.

14. A method of controlling a drive to a pixel of an OLED display, the method comprising determining a drive voltage, *V*, for said pixel using:

$$V = V_0 + \frac{1}{1 - \alpha} V_1 \left( 1 - \frac{\eta}{\eta_0} \right)$$

where  $V_0$  and  $\eta_0$  are a voltage drive to said pixel at a test drive current and a luminance efficiency of said pixel at said test drive current at an initial time; and  $V_1$  is an end of life voltage increase in said voltage drive for said test drive current; and wherein said end of life is defined as a point at which an efficiency,  $\eta$ , of said pixel has fallen to  $\alpha$  of an initial efficiency value ( $\eta_0$ ) at said initial time.

- 15. A carrier carrying processor control code for implementing the method of any preceding claim.

- 16. An OLED display driver, the display driver comprising:

an input for measuring a first voltage drop across at least one test pixel of the display;

an input for measuring a second voltage drop across at least one other pixel of the display;

a store storing a value  $(V_1)$  representing a drive voltage increase for a loss in efficiency of said display;

a system for determining an estimated reduction in efficiency of said display from said first and second voltages and said value  $(V_1)$  representing said drive voltage increase for a loss in efficiency of said display; and

a system for compensating a drive to said display using said estimated efficiency reduction.

17. A combination of the OLED display driver of claim 16 and an active matrix OLED display, and wherein said active matrix OLED display is configured for measuring a voltage across an OLED device of a pixel of said display.

25

- 18. An active matrix OLED display pixel driver circuit for use with the method of any one of claims 1 to 13 or the display driver of claim 14, said pixel driver circuit including a transistor having an input connection coupled to an OLED device of the pixel for measuring a voltage across said OLED device, an output coupled to a first electrode line of said display and a control connection coupled to a second electrode line of said display.

- 19. An active matrix OLED display pixel driver circuit as claimed in claim 18 wherein for a pixel driver circuit in a row or column of said display said second electrode line comprises a power supply line of an adjacent row or column of said display.

- 20. An active matrix OLED display pixel driver circuit as claimed in claim 19 wherein said second electrode line comprises a positive supply line and wherein said transistor is controlled on by pulling said control connection low.

Figure 1b

2/7

Figure 2

3/7

Figure 3

# Device efficiency vs time

Figure 4a

## Drive voltage vs time

Figure 4b

5/7

Figure 4c

#### INTERNATIONAL SEARCH REPORT

International application No PCT/GB2007/003279

A. CLASSIFICATION OF SUBJECT MATTER INV. G09G3/32

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

$\begin{tabular}{lll} Minimum documentation searched (classification system followed by classification symbols) \\ G09G \end{tabular}$

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data

| Catacasit                                                                           | UMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |  |  |  |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| Category*                                                                           | Citation of document, with indication, where appropriate, of                                                                                                                                                       | the relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Relevant to claim No.                              |  |  |  |

| <b>X</b>                                                                            | EP 1 158 483 A (EASTMAN KODAK<br>28 November 2001 (2001-11-28)<br>paragraphs [0020], [0025],<br>figure 2                                                                                                           | 1-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |  |  |  |

| 1                                                                                   | US 2005/110786 A1 (INOUE MASU<br>AL) 26 May 2005 (2005-05-26)<br>figures 1,2,9,10                                                                                                                                  | 1-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |  |  |  |

| Ą                                                                                   | US 2003/201727 A1 (YAMAZAKI S<br>ET AL) 30 October 2003 (2003-                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |  |  |  |

| A                                                                                   | EP 1 079 361 A (HARNESS SYST [JP]; SUMITOMO WIRING SYSTEMS SUMITOMO) 28 February 2001 (20 paragraph [0169]; claims 12,1:                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |  |  |  |

| X Furt                                                                              | her documents are listed in the continuation of Box C.                                                                                                                                                             | X See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |  |  |  |

| A" docume consic E" earlier of filing of L" docume which citatio O' docume other of | ent which may throw doubts on priority claim(s) or<br>is cited to establish the publication date of another<br>n or other special reason (as specified)<br>ent referring to an oral disclosure, use, exhibition or | <ul> <li>"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</li> <li>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</li> <li>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</li> <li>"&amp;" document member of the same patent family</li> </ul> |                                                    |  |  |  |

| Date of the                                                                         | actual completion of the international search                                                                                                                                                                      | Date of mailing of the international sea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date of mailing of the international search report |  |  |  |

| 2                                                                                   | 9 October 2007                                                                                                                                                                                                     | 07/11/2007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 07/11/2007                                         |  |  |  |

| lame and r                                                                          | nailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL – 2280 HV Hijswijk                                                                                                             | Authorized officer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |  |  |  |

|                                                                                     | Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                                                                               | LE CHAPELAIN, B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |  |  |  |

# INTERNATIONAL SEARCH REPORT

international application No PCT/GB2007/003279

| C(Continua | tion). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                               | PC1/GB200 |                       |

|------------|--------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------|

| Category*  | Citation of document, with indication, where appropriate, of the relevant passages                                       |           | Relevant to claim No. |

| P,A        | WO 2007/053783 A (EASTMAN KODAK CO [US];<br>COK RONALD STEVEN [US]; LEON FELIPE<br>ANTONIO [US) 10 May 2007 (2007-05-10) |           |                       |

|            |                                                                                                                          |           |                       |

|            |                                                                                                                          |           |                       |

|            |                                                                                                                          |           |                       |

|            |                                                                                                                          |           |                       |

| •          |                                                                                                                          |           |                       |

|            |                                                                                                                          |           |                       |

|            |                                                                                                                          |           |                       |

|            |                                                                                                                          |           |                       |

|            | 210 (continuation of second sheet) (April 2005)                                                                          |           |                       |

#### **INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/GB2007/003279

| Patent document cited in search report |    | Publication<br>date | Patent family Publication member(s) date              | •  |

|----------------------------------------|----|---------------------|-------------------------------------------------------|----|

| EP 1158483                             | A  | 28-11-2001          | JP 2002023686 A 23-01-20<br>US 2004070558 A1 15-04-20 |    |

| US 2005110786                          | A1 | 26-05-2005          | CN 1604163 A 06-04-20<br>JP 2005107059 A 21-04-20     |    |

| US 2003201727                          | A1 | 30-10-2003          | NONE                                                  |    |

| EP 1079361                             | Α  | 28-02-2001          | NONE                                                  |    |

| WO 2007053783                          | Α  | 10-05-2007          | US 2007103411 A1 10-05-20                             | 07 |

|                                        |    |                     |                                                       |    |

| 专利名称(译)        | 显示驱动系统                                                                                             |         |            |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号        | EP2057620A1                                                                                        | 公开(公告)日 | 2009-05-13 |  |  |  |

| 申请号            | EP2007804088                                                                                       | 申请日     | 2007-08-30 |  |  |  |

| [标]申请(专利权)人(译) | · · · · · · · · · · · · · · · · · · ·                                                              |         |            |  |  |  |

| 申请(专利权)人(译)    | 剑桥显示科技有限公司                                                                                         |         |            |  |  |  |

| 当前申请(专利权)人(译)  | 剑桥显示科技有限公司                                                                                         |         |            |  |  |  |

| [标]发明人         | SMITH EUAN                                                                                         |         |            |  |  |  |

| 发明人            | SMITH, EUAN                                                                                        |         |            |  |  |  |

| IPC分类号         | G09G3/32                                                                                           |         |            |  |  |  |

| CPC分类号         | G09G3/3216 G09G3/3233 G09G3/3241 G09G2300/0842 G09G2320/029 G09G2320/043 G09G2320/045 G09G2320/048 |         |            |  |  |  |

| 代理机构(译)        | 机构(译) SHARP,ALAN COOPER                                                                            |         |            |  |  |  |

| 优先权            | 2006017111 2006-08-31 GB                                                                           |         |            |  |  |  |

| 其他公开文献         | EP2057620B1                                                                                        |         |            |  |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                   |         |            |  |  |  |

#### 摘要(译)

本发明一般涉及用于改进的OLED(有机发光二极管)显示器驱动系统的方法,装置和计算机程序代码,特别是用于补偿老化。一种补偿OLED显示装置以烧蚀OLED显示器的像素的方法,该方法包括:测量显示器的至少一个测试像素上的第一电压降;测量显示器的至少一个其他像素上的第二电压降;根据所述第一和第二电压以及表示由于老化引起的所述显示器的效率损失的驱动电压增加的值(V1)确定由于老化导致的所述显示器的效率的估计降低;并且使用所述估计的效率降低来补偿对所述显示器的驱动。