(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2013/062707 A1

(43) International Publication Date

2 May 2013 (02.05.2013)

(51) International Patent Classification:

G09G 3/32 (2006.01)

(21) International Application Number:

PCT/US2012/057225

(22) International Filing Date:

26 September 2012 (26.09.2012)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

13/284,096 28 October 2011 (28.10.2011) US

(71) Applicant (for all designated States except US): APPLE INC. [US/US]; 1 Infinite Loop, M/S 36-2PAT, Cupertino, CA 95014 (US).

(72) Inventors; and

(71) Applicants (for US only): WRIGHT, Derek, W. [US/US]; 5 Infinite Loop, M/S 305-2PD, Cupertino, CA 95014 (US). ROTHKOPF, Fletcher, R. [US/US]; 5 Infinite Loop, M/S 305-1PII, Cupertino, CA 95014 (US). MYERS, Scott, A. [US/US]; 5 Infinite Loop, M/S 305-1DR, Cupertino, CA 95014 (US).

(74) Agent: TREYZ, G., Victor; Treyz Law Group, 870 Market Street, Suite 984, San Francisco, CA 94102 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

— with international search report (Art. 21(3))

(54) Title: DISPLAY WITH VIAS FOR CONCEALED PRINTED CIRCUIT AND COMPONENT ATTACHMENT

FIG. 1

(57) Abstract: An electronic device may include a display. The display may be an organic light-emitting diode display. The organic light-emitting diode display may have a substrate layer, a layer of organic light-emitting diode structures, and a layer of sealant. Vias may be formed in the substrate layer by laser drilling. The vias may be filled with metal using electroplating or other metal deposition techniques. The vias may be connected to contacts on the rear surface of the display. Components such as flexible printed circuits, integrated circuits, connectors, and other circuitry may be mounted to the contacts on the rear surface of the display.

Display with Vias for Concealed

Printed Circuit and Component Attachment

This application claims priority to United States patent application No. 13/284,096 filed on October 28, 2011, which is hereby incorporated by reference herein in its entirety.

Background

This relates generally to electronic devices, and more particularly, to displays for use in electronic devices.

Electronic devices such as portable computers and other electronic equipment may have displays. Driver circuitry may be used to control operation of the displays. In some displays, such as liquid crystal displays, a layer such as a thin-film transistor layer may have a ledge portion on which a display driver integrated circuit is mounted. The minimum size needed for the ledge

is at least partly dictated by the size of the driver integrated circuit. In some device designs, such as designs for compact portable devices, the inclusion of this type of driver ledge may give rise to a border region 5 for a liquid crystal display that is larger than desired. In other displays, driver circuitry may be coupled to the display using a flexible printed circuit cable. The attachment structures needed to accommodate attachment of the flexible printed circuit cable to the display may 10 consume more area than desired, particularly in compact devices and in arrangements where thin display borders are desired.

It would therefore be desirable to provide improved ways to interconnect displays with associated 15 circuitry such as display driver circuitry.

#### Summary

An electronic device may include a display. The display may be an organic light-emitting diode display. 20 The organic light-emitting diode display may, for example, have a substrate layer, a layer of organic light-emitting diode structures, and a layer of sealant.

Vias may be formed in a display substrate layer by laser drilling or other via hole formation techniques. 25 The vias may be filled with a conductive material such as metal using electroplating or other metal deposition techniques. The vias may be connected to contacts on the rear surface of the display. Components such as flexible printed circuits, integrated circuits, connectors, and 30 other circuitry may be mounted to the contacts on the rear surface of the display. Conductive materials such as solder and conductive adhesive may be used in mounting components to the contacts.

Further features of the invention, its nature

and various advantages will be more apparent from the accompanying drawings and the following detailed description.

5

Brief Description of the Drawings

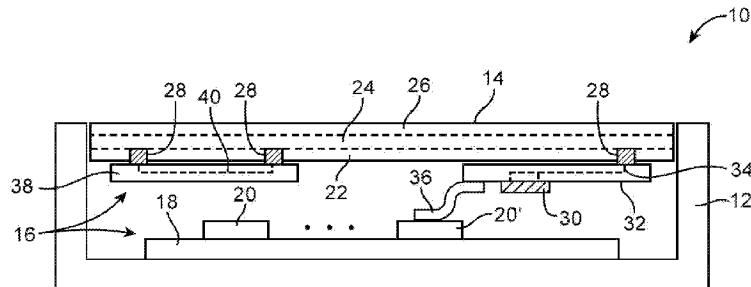

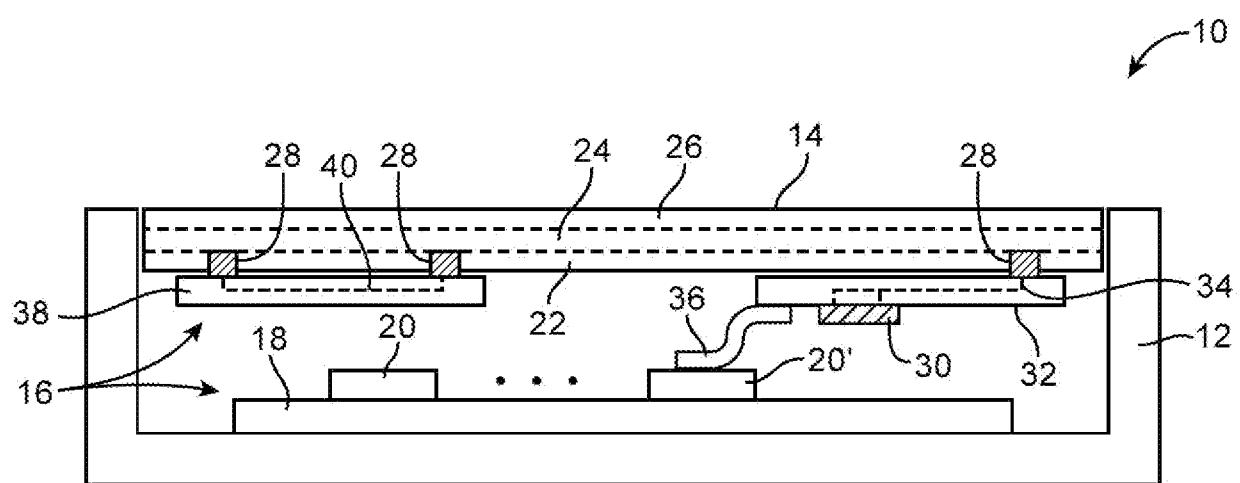

FIGS. 1 and 2 are cross-sectional side views of illustrative electronic devices with displays in accordance with embodiments of the present invention.

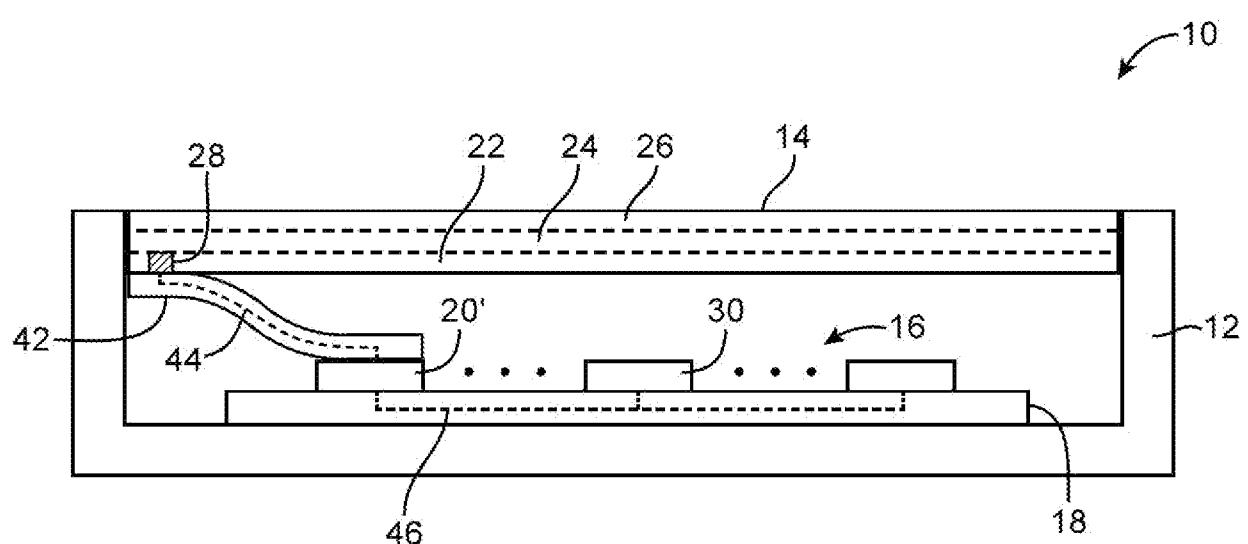

10 FIG. 3 is a top view of an illustrative display showing how vias may be used in distributing signals for the display in accordance with an embodiment of the present invention.

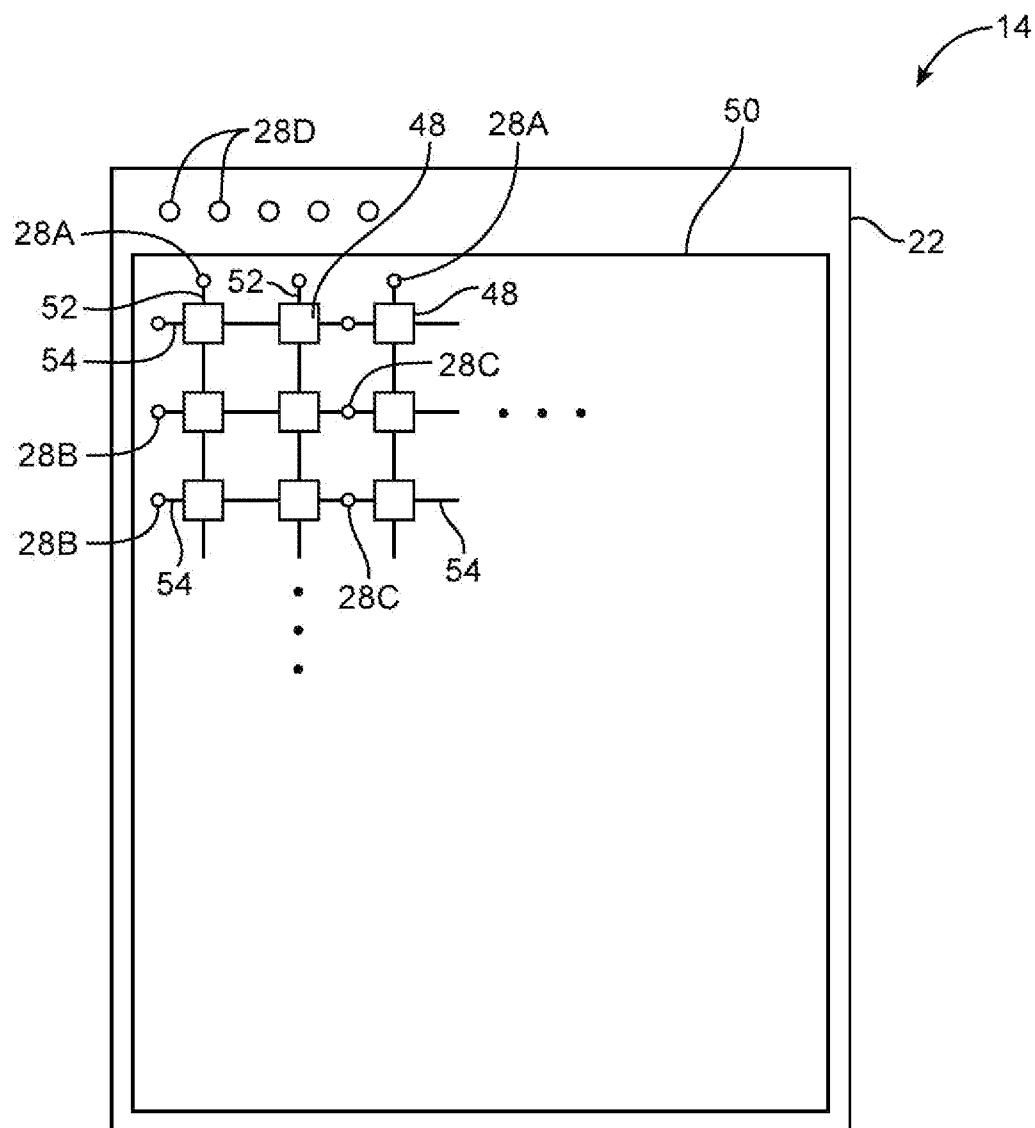

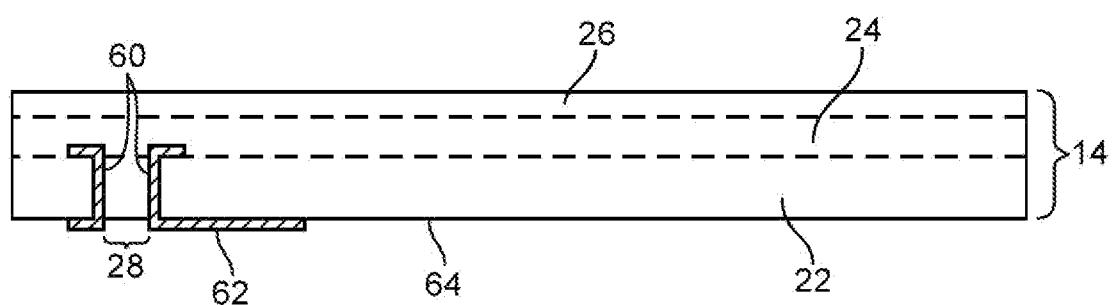

15 FIG. 4 is a cross-sectional side view of a portion of a display showing how a via may be formed through the rear surface of the display in accordance with an embodiment of the present invention.

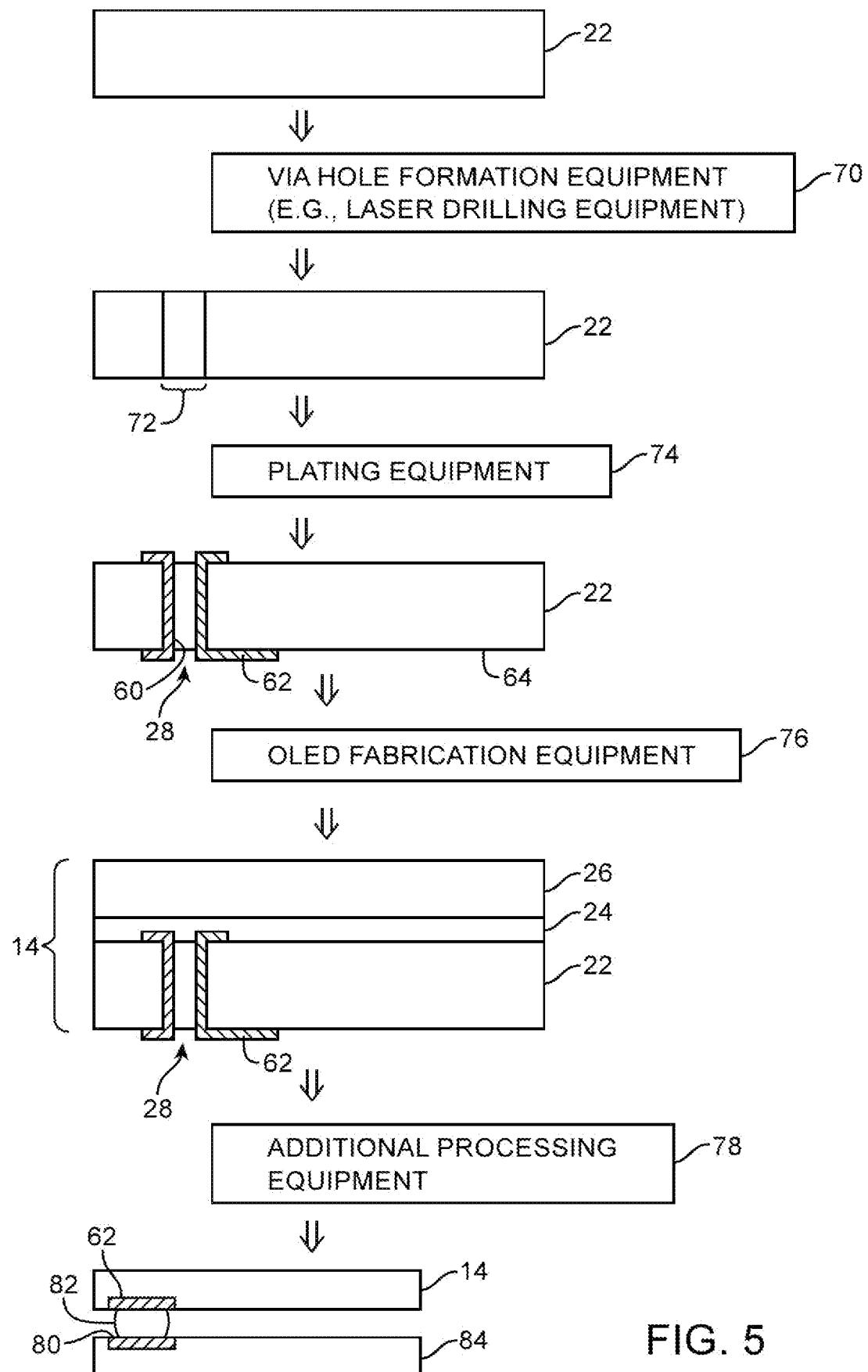

20 FIG. 5 is a diagram showing how a display may be provided with vias so that circuitry can be attached to the rear of the display in accordance with an embodiment of the present invention.

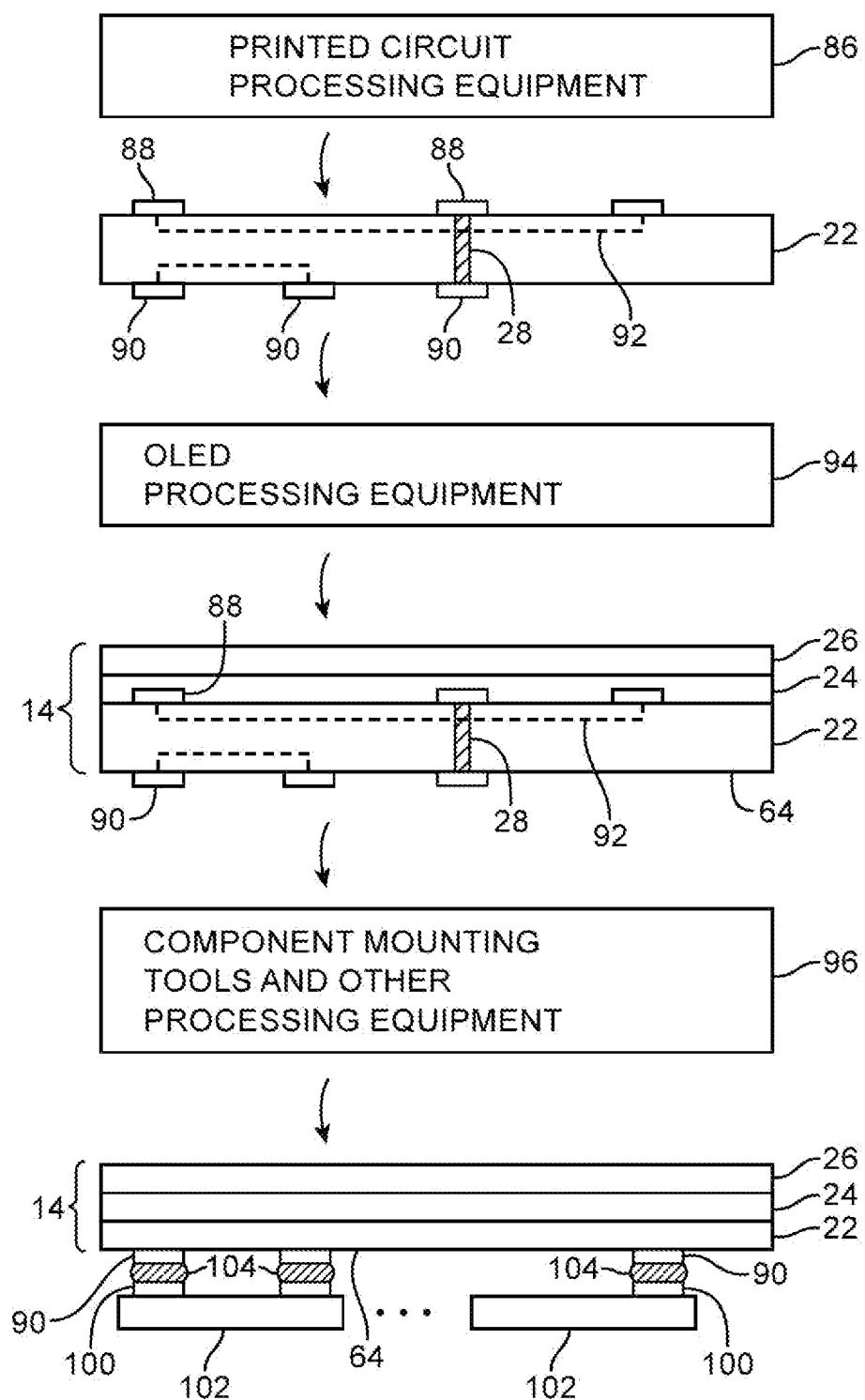

25 FIG. 6 is a diagram showing how a display may be formed from a substrate such as a flexible printed circuit substrate that has backside contacts in accordance with an embodiment of the present invention.

Detailed Description

30 Electronic devices may be provided with displays having vias. An illustrative electronic device of the type that may be provided with a display having vias is shown in FIG. 1. Electronic device 10 of FIG. 1 may be a computer, a personal computer, a tablet computer, a cellular telephone, a media player, a gaming device, a

navigation device, or other electronic equipment. As shown in the cross-sectional view of device 10 in FIG. 1, electronic device 10 may include housing 12, a display such as display 14, and internal components such as 5 components 16.

Housing 12 may be formed from plastic, metal, fiber-composite materials, glass, ceramic, other materials, or combinations of these materials. Display 14 may be a liquid crystal display, an organic light-emitting 10 diode display, a plasma display, an electrochromic display, an electrophoretic ink display, an electrowetting display, or other suitable display. Examples in which display 14 is implemented as an organic light-emitting diode display are sometimes described herein as an 15 example. This is, however, merely illustrative. Display 14 may be formed using any suitable display if desired. If desired, display 14 may be covered with a cover layer of glass or plastic or other protective display layer. In the example of FIG. 1, the cover layer has been omitted.

Internal components 16 may include printed 20 circuits such as rigid printed circuit boards (e.g., fiberglass-filled epoxy printed circuit boards), flexible printed circuits ("flex circuits") formed from flexible sheets of polymers such as polyimide, "rigid flex" printed 25 circuits (e.g., printed circuit boards including rigid printed circuit portions with integral flex circuit tails), or other printed circuit structures. As an example, device 10 may include a printed circuit such as printed circuit board 18 on which one or more components 30 such as electrical components 20 or other internal components 16 have been mounted. Components 20 may include switches, connectors, discrete components such as capacitors, resistors, and inductors, integrated circuits, and other electronic components.

As shown in FIG. 1, display 14 may have multiple layers. For example, display 14 may be an organic light-emitting diode display having a substrate layer such as substrate layer 22, a layer of thin-film transistor structures (e.g., polysilicon transistors and/or amorphous silicon transistors) and organic emissive material such as layer 24, and a sealant layer such as layer 26. Substrate layer 22 may be formed from a rigid or flexible dielectric such as glass, ceramic, or plastic. As an example, 5 substrate 22 in display 14 may be formed from a flexible sheet of polymer such as a layer of polyimide.

10

Vias such as vias 28 may be formed in display 14. As shown in FIG. 1, for example, vias 28 may be formed through substrate layer 22 so that electrical 15 contacts may be formed on the rear (inner) surface of substrate 22 and display 14. Vias 28 may be formed by laser drilling and electroplating or using other fabrication techniques. Conductive material in vias 28 such as metal (e.g., gold plated copper) may be used to 20 form signal paths in display 14. The signal paths may, for example, be used to route signals between the circuitry of layer 24 (e.g., thin-film transistors) and external circuitry such as display driver circuitry.

In the example of FIG. 1, display driver 25 circuitry for display 14 has been provided using display driver integrated circuit 30. Display driver integrated circuit 30 (in the FIG. 1 example) has been mounted on printed circuit 32. Printed circuit 32 may be a rigid printed circuit board or a flex circuit. For example, 30 printed circuit 32 may be a flex circuit that includes one or more layers of patterned interconnect lines such as traces 34. Traces 34 may be electrically connected between one or more vias in substrate layer 22 of display 14 and driver integrated circuit 30. If desired, traces

34 may be connected to a communications path formed from flex circuit 36 (e.g., a flex circuit that is connected to printed circuit board 18 directly or, as shown in FIG. 1, a flex circuit that is connected to components 20 on printed circuit board 18 via flex circuit connector 20'). The connection between flex circuit 36 and printed circuit 32 may be formed using a connector or by directly attaching flex circuit 36 to traces 34 on printed circuit 32.

10 By using vias 28 in layer 22, the need to form flex circuit attachments or driver circuit attachments to the front (upper/exterior) surface of display 14 may be avoided, allowing the edge regions surrounding the active display pixels in display 14 to be minimized. More area 15 in display 14 may therefore be available for forming the array of pixels that displays images to a user.

If desired, a jumper structure such as structure 38 may be attached to vias on the backside of substrate 22 and may be used to route signals between two or more 20 different locations in display 14. Structure 38 may be formed from a printed circuit such as a flex circuit or rigid printed circuit board. Traces 40 in structures 38 may be used to help distribute signals for display 14. Any suitable signals may be routed through flex circuits 25 or other jumper structures on the rear of display 14. For example, structures 38 may be used to carry gate line signals, data line signals, power supply signals, or other information or power signals associated with operating display 14. By implementing at least some of the 30 interconnect resources associated with display 14 using structures located on the rear surface of display 14, more room may be made available on the front surface of display 14 for active pixel structures and the size of any inactive border regions on the front side of display 14

may be minimized.

In the illustrative arrangement of FIG. 1, flex circuit 32 is being used to support display driver integrated circuit 30 and a separate flex circuit such as 5 flex circuit 36 is being used to couple flex circuit 32 to printed circuit board 18 (using connector 20'). Other arrangements may be used if desired. For example, flex circuit 32 may be connected directly to traces on printed circuit board 18 (e.g., using anisotropic conductive film 10 or solder connections) or flex circuit 32 may be connected directly to connector 20'. There may be more than one flex circuit such as flex circuit 32 that is interconnected between rear surface vias 28 on display 14 and circuitry such as circuitry in components 20 on 15 printed circuit board 18. Supplemental interconnection pathways such as traces 40 of flex circuit 38 may be provided on one or more, two or more, or three or more integrated circuits. Flex circuits such as flex circuit 32 may include mounted circuits such as display driver 20 integrated circuit 30 for controlling the operation of display 14 and may, if desired, include supplemental interconnect lines for forming gate line paths, data line paths, power lines paths, or other signal paths in device 10. Supplemental interconnect lines for forming gate line 25 paths, data line paths, power lines paths, or other signal paths in device 10 may also be formed using jumper structures 38.

As shown in FIG. 2, a printed circuit such as flex circuit 42 may have traces such as traces 44 that 30 form a path between vias 28 in substrate 22 of display 14 and circuitry on printed circuit board 18. A connector such as connector 20' of FIG. 2 or a direct attachment scheme (e.g., using solder or anisotropic conductive film) may be used to interconnect traces 44 to traces on printed

circuit board 18 such as traces 46. Display driver circuitry 30 (e.g., a display driver integrated circuit) may, if desired, be mounted on printed circuit 18 and may be coupled to traces 44 in printed circuit 42 via traces 5 46.

An arrangement that may be used for providing vias 28 in display 14 is shown the top view of illustrative display 14 of FIG. 3. As shown in FIG. 3, display 14 may display pixels such as display pixels 48. 10 Display pixels 48 may each contain an organic light-emitting diode structure for emitting light for display 14. Display pixels 48 may be organized in an array such as array 50. Array 50 may contain any suitable number or rows and columns of display pixels 48. For example, array 15 50 may have hundreds of rows and/or hundreds of columns of display pixels 48 (as an example). Vertical and horizontal control lines may be used in supplying control signals to display pixels 48. For example, signals may be applied to respective columns of display pixels 48 using 20 vertical signal lines such as lines 52 and may be applied to respective rows of display pixels 48 using horizontal signal lines such as lines 54.

If desired, signal lines such as lines 52 may be coupled to vias in substrate layer 22 of display 14 such 25 as vias 28A. Signal lines such as lines 54 may be coupled to vias in substrate layer 22 of display 14 such as vias 28B. Vias in substrate layer 22 such as vias 28C may be formed within array 50 (e.g., at intermediate locations in the rows or columns of display pixels 48). Edge vias such 30 as vias 28D may also be formed in substrate 22 and may be used for handling signals associated with operating display pixels 48 (e.g., signals for lines 52 and/or 54).

A cross-sectional side view of a portion of display 14 containing a via is shown in FIG. 4. Via 28

may be one of vias 28 of FIGS. 1 and 2, one of vias 28A, 28B, 28C, or 28D of FIG. 3, or other vias formed through substrate 22 of display 14. As shown in FIG. 4, via 28 may include tubular metal sidewalls such as sidewalls 60 that coat the cylindrical inner surface of a through hole in layer 22. Sidewalls 60 may be formed by any suitable fabrication technique. For example, sidewalls 60 may be formed using electrodeposition (e.g., formation of a thin seed layer followed by electroplating of a metal such as 5 copper and, if desired, a subsequent coating of a metal such as gold). With a via structure of the type shown in FIG. 4, via 28 is formed from a hole (e.g., a cylindrical hole) in substrate 22 and is lined with a tubular layer of metal. Other types of vias may be formed in layer 22 if 10 desired (e.g., via holes that are plugged with solid metal, etc.).

If desired, traces may be formed on the surface of substrate 22. As shown in FIG. 4, for example, contact pad 62 may be formed on rear surface 64 of display 14. 20 Contact 62 may be formed from a metal trace that is electrically shorted to sidewalls 60 of via 28. Additional patterned conductive structures may be formed on surface 64 of substrate 22 if desired. The example of FIG. 4 is merely illustrative.

FIG. 5 is a diagram showing how a display may be provided with vias. Initially, a display substrate such as substrate 22 may be provided. Substrate 22 may be, for example, a layer of polymer such as a layer of polyimide.

Via hole formation equipment 70 such as laser drilling equipment may be used to form one or more via holes such as via hole 72 in substrate 22.

Following formation of via holes such as via hole 72, conductive material deposition equipment such as metal plating equipment 74 may be used to form conductive

structures for vias 28 such as conductive sidewalls 60. Traces such as contact trace 62 may also be formed on lower surface 64 of substrate 22.

Organic light-emitting diode (OLED) fabrication equipment 76 or other display fabrication equipment may be used to complete display 14. For example, OLED fabrication equipment 76 may be used to form thin-film transistor structures and interconnects in layer 24. Layer 24 may include organic emissive material and light-emitting diode structures that are used to form display pixels such as display pixels 48 of FIG. 3. A sealant layer such as sealant layer 26 (e.g., a polymer layer) may then be formed over the front (upper) surface of display 14 to protect the structures of layer 24.

Additional processing equipment 78 may then be used to form electrical connections to additional circuitry 84. As shown in FIG. 5, conductive material 82 may be used in forming electrical connections between contacts such as contact 62 on display 14 (e.g., contacts on surface 64 of substrate 22) and associated contacts such as contact 80 on additional circuitry 84. Conductive material 82 may be solder, metal associated with a weld, part of a connector, conductive adhesive (e.g., anisotropic conductive film), or other suitable material for forming an electrical connection between via 28 and additional circuitry 84. Additional circuitry 84 may be a printed circuit or other circuitry. For example, additional circuitry 84 may be a flex circuit on which integrated circuits and/or other electrical components are mounted, a flex circuit cable that is attached to a printed circuit board with components, a rigid printed circuit board, or other suitable circuitry (see, e.g., the illustrative arrangements of FIGS. 1, 2, and 3).

FIG. 6 is a diagram showing how display 14 may

be formed from a two-sided printed circuit layer that serves as substrate 22.

Initially, printed circuit processing equipment 86 may be used to produce patterned two-sided printed circuit 22. Patterned two-sided printed circuit 22 may include patterned traces 88 and patterned traces 90 on opposing first (upper) and second (lower) surfaces. If desired, one or more layers of internal printed circuit traces such as traces 92 may be used to interconnect upper surface traces 88 and lower surface traces 90 (i.e., printed circuit layer 22 may include multiple sublayers of dielectric such as polyimide and one or more corresponding sublayers of patterned traces). Traces 92 may include vias 28.

Following formation of a multilayer printed circuit such as a two-sided printed circuit substrate or a multilayer printed circuit substrate that includes one or more patterned internal layers of traces and/or one or two exposed surfaces covered with of external traces such as substrate 22, OLED processing equipment 94 may be used to complete the formation of OLED display 14 by forming organic emissive material and light-emitting diode structures in layer 24 and covering layer 24 with sealant layer 26.

Component mounting tools and other processing equipment 96 may be used to mount components 102 to substrate 22. In particular, conductive material 104 such as solder, welds, conductive material associated with connector structures, anisotropic conductive film or other conductive adhesive, or other conductive material may be used to connect traces (contacts) 100 on components 102 to corresponding traces 90 on rear surface 64 of display 14. Examples of components 102 that equipment 96 may attach to traces 90 include integrated circuits, discrete components

such as resistors, capacitors, and inductors, connectors, flex circuit cables and other printed circuit structures, and other circuitry. Components 102 may be, for example, surface mount technology (SMT) components and equipment 96 5 may be a pick-and-place tool.

In accordance with an embodiment, an electronic device is provided that includes a display with vias; and electroplated metal sidewalls in the vias.

In accordance with another embodiment, the display comprises an organic light-emitting diode display.

In accordance with another embodiment, the organic light-emitting diode display includes a substrate layer in which the vias are formed; a light-emitting diode layer on the substrate layer that includes organic emissive material and light-emitting diode structures; and a sealant layer on the light-emitting diode layer.

In accordance with another embodiment, the sealant forms a front surface for the display and the substrate layer includes an opposing rear surface with contacts.

In accordance with another embodiment, the electronic device further includes at least one component mounted to the contacts.

In accordance with another embodiment, the at least one component includes a component selected from the group consisting of a connector, an integrated circuit, a flexible printed circuit, a resistor, a capacitor, and an inductor.

In accordance with another embodiment, the at least one component includes an integrated circuit.

In accordance with another embodiment, the electronic device further includes solder with which the integrated circuit is mounted to the contacts on the substrate layer.

In accordance with another embodiment, the at least one component comprises a flexible printed circuit.

In accordance with another embodiment, the electronic device further includes anisotropic conductive film with which the flexible printed circuit is mounted to the contacts on the substrate layer.

In accordance with another embodiment, the substrate layer includes a two-sided flexible printed circuit having conductive traces on at least opposing first and second surfaces.

In accordance with another embodiment, the substrate layer includes a flexible layer of polymer.

In accordance with another embodiment, the vias include laser-drilled vias.

In accordance with an embodiment, an electronic device is provided that includes a housing; and a display mounted in the housing, where the display has opposing front and rear surfaces, where the front surface is viewable from outside of the housing, and where the display includes a substrate layer with electroplated vias, a light-emitting diode layer, and a sealant layer, and where the light-emitting diode layer is interposed between the sealant layer and the substrate layer.

In accordance with another embodiment, the electronic device further includes a flexible printed circuit that is electrically connected to the electroplated vias.

In accordance with another embodiment, the electronic device further includes a display driver integrated circuit mounted to the flexible printed circuit.

In accordance with another embodiment, the vias include metal sidewalls, the substrate layer includes a flexible sheet of polymer, and the vias include laser-

drilled vias.

In accordance with an embodiment, an apparatus is provided that includes an organic light-emitting diode display having a substrate layer, a layer of light-emitting diodes on the substrate layer, and a sealant layer on the light-emitting diode layer, the substrate layer includes vias.

In accordance with another embodiment, the apparatus includes at least one electrical component that is electrically connected to the vias.

In accordance with another embodiment, the substrate layer includes a layer of polymer, the vias comprise laser-drilled vias, and the electrical component is electrically connected to the laser-drilled vias.

In accordance with another embodiment, the electrical component includes a flexible printed circuit that is electrically connected to the laser-drilled vias with conductive adhesive.

In accordance with another embodiment, the electrical component includes an integrated circuit that is electrically connected to the laser-drilled vias with solder.

The foregoing is merely illustrative of the principles of this invention and various modifications can be made by those skilled in the art without departing from the scope and spirit of the invention.

What is Claimed is:

1. An electronic device comprising:

a display with vias; and

electroplated metal sidewalls in the vias.

2. The electronic device defined in claim 1

wherein the display comprises an organic light-emitting

diode display.

3. The electronic device defined in claim 1

wherein the organic light-emitting diode display

comprises:

a substrate layer in which the vias are

formed;

a light-emitting diode layer on the

substrate layer that includes organic emissive material

and light-emitting diode structures; and

a sealant layer on the light-emitting diode

layer.

4. The electronic device defined in claim 3

wherein the sealant forms a front surface for the display

and wherein the substrate layer comprises an opposing rear

surface with contacts.

5. The electronic device defined in claim 4

further comprising at least one component mounted to the

contacts.

6. The electronic device defined in claim 5

wherein the at least one component comprises a component

selected from the group consisting of: a connector, an

integrated circuit, a flexible printed circuit, a

resistor, a capacitor, and an inductor.

7. The electronic device defined in claim 6 wherein the at least one component comprises an integrated circuit.

8. The electronic device defined in claim 7 further comprising solder with which the integrated circuit is mounted to the contacts on the substrate layer.

9. The electronic device defined in claim 6 wherein the at least one component comprises a flexible printed circuit.

10. The electronic device defined in claim 9 further comprising anisotropic conductive film with which the flexible printed circuit is mounted to the contacts on the substrate layer.

11. The electronic device defined in claim 3 wherein the substrate layer comprises a two-sided flexible printed circuit having conductive traces on at least opposing first and second surfaces.

12. The electronic device defined in claim 11 wherein the substrate layer comprises a flexible layer of polymer.

13. The electronic device defined in claim 12 wherein the vias comprise laser-drilled vias.

14. An electronic device, comprising:

a housing; and

a display mounted in the housing, wherein

the display has opposing front and rear surfaces, wherein

the front surface is viewable from outside of the housing, and wherein the display includes a substrate layer with electroplated vias, a light-emitting diode layer, and a sealant layer, and wherein the light-emitting diode layer is interposed between the sealant layer and the substrate layer.

15. The electronic device defined in claim 14 further comprising a flexible printed circuit that is electrically connected to the electroplated vias.

16. The electronic device defined in claim 15 further comprising a display driver integrated circuit mounted to the flexible printed circuit.

17. The electronic device defined in claim 16 wherein the vias comprise metal sidewalls, wherein the substrate layer comprises a flexible sheet of polymer, and wherein the vias comprise laser-drilled vias.

18. Apparatus, comprising:

an organic light-emitting diode display having a substrate layer, a layer of light-emitting diodes on the substrate layer, and a sealant layer on the light-emitting diode layer, wherein the substrate layer comprises vias.

19. The apparatus defined in claim 18 further comprising at least one electrical component that is electrically connected to the vias.

20. The apparatus defined in claim 19 wherein the substrate layer comprises a layer of polymer, wherein the vias comprise laser-drilled vias, and wherein the

electrical component is electrically connected to the laser-drilled vias.

21. The apparatus defined in claim 20 wherein the electrical component comprises a flexible printed circuit that is electrically connected to the laser-drilled vias with conductive adhesive.

22. The apparatus defined in claim 20 wherein the electrical component comprises an integrated circuit that is electrically connected to the laser-drilled vias with solder.

1 / 6

FIG. 1

2 / 6

FIG. 2

3 / 6

FIG. 3

416

FIG. 4

5 / 6

FIG. 5

6 / 6

FIG. 6

# INTERNATIONAL SEARCH REPORT

International application No

PCT/US2012/057225

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. G09G3/32

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

G09G

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                    | Relevant to claim No.              |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| X         | US 5 880 705 A (ONYSKEVYCH LUBOMYR STEPHEN [US] ET AL) 9 March 1999 (1999-03-09)                                                                                                      | 1                                  |

| Y         | column 1, line 11 - line 14<br>column 3, line 32 - column 4, line 59;<br>figures 3-5                                                                                                  | 1-13, 17,<br>20-22                 |

| X         | -----<br>WO 2009/089105 A1 (NANOLUMENS [US]; COPE RICHARD C [US]; LIU GUO [CA]; SILZARS ARIS K [US] 16 July 2009 (2009-07-16)<br>page 21, line 17 - page 24, line 8;<br>figures 33-37 | 14, 18, 19                         |

| Y         | -----<br>US 6 421 033 B1 (WILLIAMS GEORGE M [US] ET AL) 16 July 2002 (2002-07-16)<br>column 10, line 39 - column 11, line 27;<br>figures 5,6                                          | 1-13,<br>15-17,<br>20-22           |

|           | -----<br>-----<br>-/-                                                                                                                                                                 | 18, 19<br>1-13,<br>15-17,<br>20-22 |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

10 December 2012

17/12/2012

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Harke, Michael

**INTERNATIONAL SEARCH REPORT**

International application No

PCT/US2012/057225

C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                 | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y         | US 2003/011298 A1 (PALANISAMY PONNUSAMY [US]) 16 January 2003 (2003-01-16)<br>paragraph [0012] - paragraph [0015];<br>figure 1<br>-----                            | 8,22                  |

| Y         | US 6 498 592 B1 (MATTHIES DENNIS LEE [US])<br>24 December 2002 (2002-12-24)<br>column 8, line 51 - line 59<br>column 22, line 11 - line 23; figure 16<br>-----     | 9,15-17,<br>21        |

| Y         | US 2004/016568 A1 (PALANISAMY PONNUSAMY [US]) 29 January 2004 (2004-01-29)<br>paragraphs [0020], [0021], [0028],<br>[0050], [0054]; figures 1a,1b,3a,3b,7<br>----- | 9,10,<br>15-17,21     |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2012/057225

| Patent document cited in search report |    | Publication date |      | Patent family member(s) |  | Publication date |

|----------------------------------------|----|------------------|------|-------------------------|--|------------------|

| US 5880705                             | A  | 09-03-1999       | EP   | 0834169 A1              |  | 08-04-1998       |

|                                        |    |                  | JP   | 4189887 B2              |  | 03-12-2008       |

|                                        |    |                  | JP   | H11510640 A             |  | 14-09-1999       |

|                                        |    |                  | US   | 5644327 A               |  | 01-07-1997       |

|                                        |    |                  | US   | 5880705 A               |  | 09-03-1999       |

|                                        |    |                  | WO   | 9641327 A1              |  | 19-12-1996       |

| <hr/>                                  |    |                  |      |                         |  |                  |

| WO 2009089105                          | A1 | 16-07-2009       | NONE |                         |  |                  |

| <hr/>                                  |    |                  |      |                         |  |                  |

| US 6421033                             | B1 | 16-07-2002       | EP   | 1218873 A1              |  | 03-07-2002       |

|                                        |    |                  | JP   | 2003510661 A            |  | 18-03-2003       |

|                                        |    |                  | TW   | 476055 B                |  | 11-02-2002       |

|                                        |    |                  | US   | 6421033 B1              |  | 16-07-2002       |

|                                        |    |                  | WO   | 0124153 A1              |  | 05-04-2001       |

| <hr/>                                  |    |                  |      |                         |  |                  |

| US 2003011298                          | A1 | 16-01-2003       | NONE |                         |  |                  |

| <hr/>                                  |    |                  |      |                         |  |                  |

| US 6498592                             | B1 | 24-12-2002       | EP   | 1332487 A2              |  | 06-08-2003       |

|                                        |    |                  | EP   | 2330627 A2              |  | 08-06-2011       |

|                                        |    |                  | JP   | 2004515810 A            |  | 27-05-2004       |

|                                        |    |                  | JP   | 2009110014 A            |  | 21-05-2009       |

|                                        |    |                  | US   | 6498592 B1              |  | 24-12-2002       |

|                                        |    |                  | WO   | 0247310 A2              |  | 13-06-2002       |

| <hr/>                                  |    |                  |      |                         |  |                  |

| US 2004016568                          | A1 | 29-01-2004       | US   | RE41669 E1              |  | 14-09-2010       |

|                                        |    |                  | US   | RE42542 E1              |  | 12-07-2011       |

|                                        |    |                  | US   | 2004016568 A1           |  | 29-01-2004       |

|                                        |    |                  | US   | 2005095878 A1           |  | 05-05-2005       |

|                                        |    |                  | WO   | 2004105131 A1           |  | 02-12-2004       |

| <hr/>                                  |    |                  |      |                         |  |                  |

|                |                                                                             |         |            |

|----------------|-----------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示带隐藏印刷电路和元件附件的过孔                                                           |         |            |

| 公开(公告)号        | <a href="#">EP2754147A1</a>                                                 | 公开(公告)日 | 2014-07-16 |

| 申请号            | EP2012787933                                                                | 申请日     | 2012-09-26 |

| [标]申请(专利权)人(译) | 苹果公司                                                                        |         |            |

| 申请(专利权)人(译)    | 苹果公司.                                                                       |         |            |

| 当前申请(专利权)人(译)  | 苹果公司.                                                                       |         |            |

| [标]发明人         | THE DESIGNATION OF THE INVENTOR HAS NOT YET BEEN FILED                      |         |            |

| 发明人            | THE DESIGNATION OF THE INVENTOR HAS NOT YET BEEN FILED                      |         |            |

| IPC分类号         | G09G3/32                                                                    |         |            |

| CPC分类号         | G09G3/3208 G09G2300/0426 H01L27/3276 H01L51/52 G09G3/32 H01L51/50 H05K1/115 |         |            |

| 优先权            | 13/284096 2011-10-28 US                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                   |         |            |

#### 摘要(译)

电子设备可以包括显示器。显示器可以是有机发光二极管显示器。有机发光二极管显示器可以具有基底层，一层有机发光二极管结构和一层密封剂。可以通过激光钻孔在衬底层中形成通孔。可以使用电镀或其他金属沉积技术用金属填充通孔。通孔可以连接到显示器后表面上的触点。诸如柔性印刷电路，集成电路，连接器和其他电路的组件可以安装到显示器后表面上的触点。