Europäisches

Patentamt

European

Patent Office

Office européen

des brevets

(11)

EP 3 648 189 A1

(12)

**EUROPEAN PATENT APPLICATION**

published in accordance with Art. 153(4) EPC

(43) Date of publication:

**06.05.2020 Bulletin 2020/19**

(51) Int Cl.:

**H01L 51/52 (2006.01)**

(21) Application number: **18811433.4**

(86) International application number:

**PCT/CN2018/091952**

(22) Date of filing: **20.06.2018**

(87) International publication number:

**WO 2019/001317 (03.01.2019 Gazette 2019/01)**

(84) Designated Contracting States:

**AL AT BE BG CH CY CZ DE DK EE ES FI FR GB

GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO

PL PT RO RS SE SI SK SM TR**

Designated Extension States:

**BA ME**

Designated Validation States:

**KH MA MD TN**

(30) Priority: **30.06.2017 CN 201710558592**

(71) Applicant: **BOE Technology Group Co., Ltd.

Beijing 100015 (CN)**

(72) Inventor: **HOU, Wenjun

Beijing 100176 (CN)**

(74) Representative: **Brötz, Helmut et al

Rieder & Partner mbB

Patentanwälte - Rechtsanwalt

Corneliusstrasse 45

42329 Wuppertal (DE)**

**(54) ELECTROLUMINESCENT DIODE ARRAY SUBSTRATE, PREPARATION METHOD THEREOF AND DISPLAY PANEL**

(57) An electroluminescent diode array substrate, a method of manufacturing the electroluminescent diode array substrate and a display panel are provided, and the electroluminescent diode array substrate includes: a base substrate (201); and an auxiliary electrode (202), a pixel definition layer (208), a first electrode (204), a functional layer (205) and a second electrode (206) disposed on the base substrate (201), the pixel definition layer (208) is provided with a via hole structure (207), the auxiliary electrode (202) is disposed on at least one side of the via hole structure (207), and the second electrode

(206) is electrically connected with the auxiliary electrode (202). In the electroluminescent diode array substrate, by changing the structural design of the auxiliary electrode (202), the electrical connection between the second electrode (206) and the auxiliary electrode (202) is ensured, the problem that the large voltage drop caused by the large resistance of the second electrode (206) in a case where the second electrode (206) made of metallic silver with a thinner thickness is avoided, and further the problem of damaging to an organic light-emitting display panel due to the large voltage drop is avoided.

Fig.2

## Description

**[0001]** The present application claims the priority of the Chinese Patent Application No. 201710558592.2, filed on June 30, 2017, which is incorporated herein by reference as part of the disclosure of the present application.

## TECHNICAL FIELD

**[0002]** Embodiments of the present disclosure relate to an electroluminescent diode array substrate, a method of manufacturing the electroluminescent diode array substrate, and a display panel.

## BACKGROUND

**[0003]** Electroluminescent diodes have advantages of simple manufacturing process, low production cost, high light-emitting efficiency, being easy to form flexible structures, low power consumption, high color saturation, wide viewing angle, and so on. A display technology by using electroluminescent diodes has become an important display technology.

**[0004]** An electroluminescent diode comprises an organic light-emitting diode (OLED), a quantum dot light-emitting diode (QLED) or the like. For example, an organic light-emitting diode (OLED) array substrate comprises a plurality of pixel units, and each of the pixel units comprises a switching transistor, a driving transistor, an OLED display device and so on. The OLED display device is a current-driven light-emitting device, and the OLED display device mainly comprises an anode, a cathode and an organic material functional layer. The working principle of the OLED display device is that the organic material functional layer is driven by an electric field formed by the anode and the cathode, then carriers are injected and recombined to emit light. The quantum dot light-emitting diode (QLED) has a similar structure to the organic light-emitting diode (OLED). The main difference between the quantum dot light-emitting diode (QLED) and the organic light-emitting diode is that the luminescence center of the QLED is composed of quantum dots, and the light-emitting principle of the quantum dot light-emitting diode (QLED) is that electrons and holes are combined to form photons in a quantum dot layer, then the photons are recombined to emit light.

## SUMMARY

**[0005]** At least one embodiment of the present disclosure provides an electroluminescent diode array substrate, and the electroluminescent diode array substrate includes: a base substrate, and an auxiliary electrode, a pixel definition layer, a first electrode, a functional layer, and a second electrode which are disposed on the base substrate, and the pixel definition layer is provided with a via hole structure; the auxiliary electrode is disposed on at least one side of the via hole structure; and the

second electrode is electrically connected with the auxiliary electrode.

**[0006]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, an upper surface of the auxiliary electrode is higher than an upper surface of the functional layer in the via hole structure.

**[0007]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, the auxiliary electrode is a structure in a U shape.

**[0008]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, the auxiliary electrode is a plate-type structure; or there are a plurality of auxiliary electrodes which are spaced apart from each other.

**[0009]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, a conductive polymer layer is provided in the via hole structure, and the second electrode is electrically connected with the auxiliary electrode by the conductive polymer layer.

**[0010]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, a thickness of the conductive polymer layer is less than a thickness of the pixel definition layer.

**[0011]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, a conductivity of the conductive polymer layer is greater than  $10^{-6}$  S/m.

**[0012]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, a material of the conductive polymer layer comprises at least one of polypyrrole, polyphenylene sulfide, polyphthalocyanine, polyaniline and polythiophene.

**[0013]** For example, the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, further includes a planarization layer disposed between the base substrate and the pixel definition layer, and the via hole structure extends from the pixel definition layer and penetrates through the planarization layer.

**[0014]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, a thickness of the conductive polymer layer is larger than a thickness of the planarization layer, and the thickness of the conductive polymer layer is smaller than a sum of the thickness of the planarization layer and a thickness of the pixel definition layer.

**[0015]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, an upper surface of the conductive polymer layer is flush with an upper surface of the pixel definition layer.

**[0016]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of

the present disclosure, there are a plurality of via hole structures penetrating through the planarization layer and the pixel definition layer, and the second electrode is electrically connected with the auxiliary electrode by the plurality of via hole structures.

**[0017]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, a thickness of the functional layer is from about 100 nm to about 300 nm, a thickness of the auxiliary electrode is from about 0.5  $\mu\text{m}$  to about 1  $\mu\text{m}$ , a thickness of the planarization layer is from about 1  $\mu\text{m}$  to about 3  $\mu\text{m}$ , a thickness of the pixel definition layer is from about 1  $\mu\text{m}$  to about 3  $\mu\text{m}$ , and a thickness of the conductive polymer layer is from about 2  $\mu\text{m}$  to about 5.7  $\mu\text{m}$ .

**[0018]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, the functional layer comprises at least one of a light-emitting layer, an electron injection layer, an electron transmission layer, a hole injection layer and a hole transmission layer.

**[0019]** At least one embodiment of the present disclosure further provides a display panel, and the display panel includes any one of the electroluminescent diode array substrate described above.

**[0020]** At least one embodiment of the present disclosure further provides a method of manufacturing an electroluminescent diode array substrate, and the method includes: providing a base substrate, forming an auxiliary electrode, a pixel definition layer, a first electrode, a functional layer and a second electrode on the base substrate, and the pixel definition layer is provided with a via hole structure; the auxiliary electrode is disposed on at least one side of the via hole structure; and the second electrode is electrically connected with the auxiliary electrode.

**[0021]** For example, in the method provided by at least one embodiment of the present disclosure, an upper surface of the auxiliary electrode which is formed on at least one side of the via hole structure is higher than an upper surface of the functional layer in the via hole structure.

**[0022]** For example, the method provided by at least one embodiment of the present disclosure, before forming the auxiliary electrode, further includes: forming a planarization layer on the base substrate, wherein the via hole structure extends from the pixel definition layer and penetrates through the planarization layer.

**[0023]** For example, the method provided by at least one embodiment of the present disclosure, further includes: forming a conductive polymer layer in the via hole structure, wherein the second electrode is electrically connected with the auxiliary electrode by the conductive polymer layer.

**[0024]** For example, in the method provided by at least one embodiment of the present disclosure, the conductive polymer layer is formed by an inkjet printing method.

## BRIEF DESCRIPTION OF THE DRAWINGS

**[0025]** In order to clearly illustrate the technical solution of the embodiments of the disclosure, the drawings of the embodiments will be briefly described. It is apparent that the described drawings are only related to some embodiments of the disclosure and thus are not limitative of the disclosure.

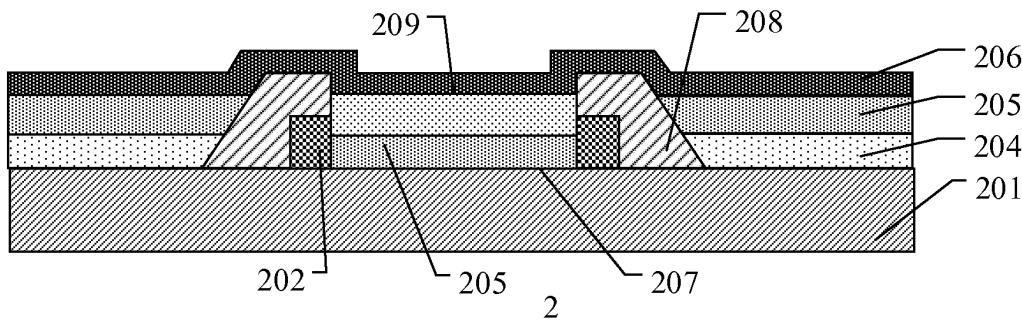

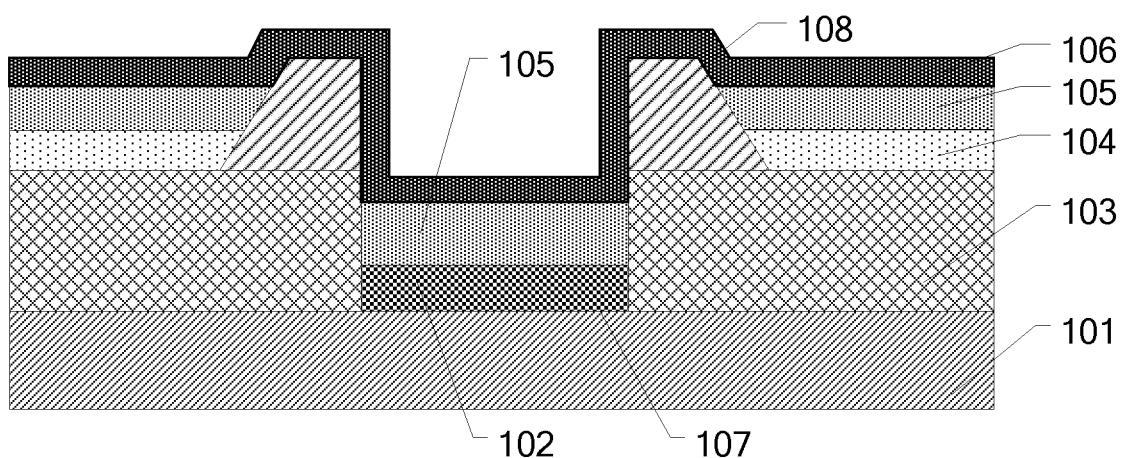

- 5 10 Fig. 1 is a schematic sectional view of an organic light-emitting diode (OLED) array substrate;

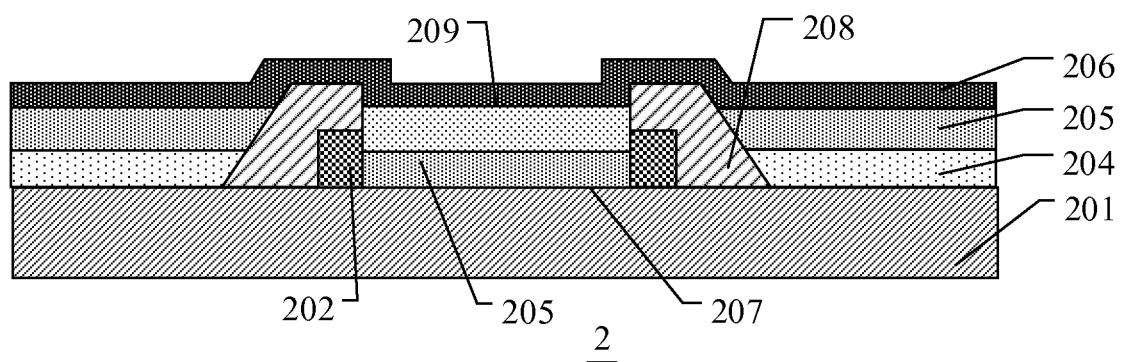

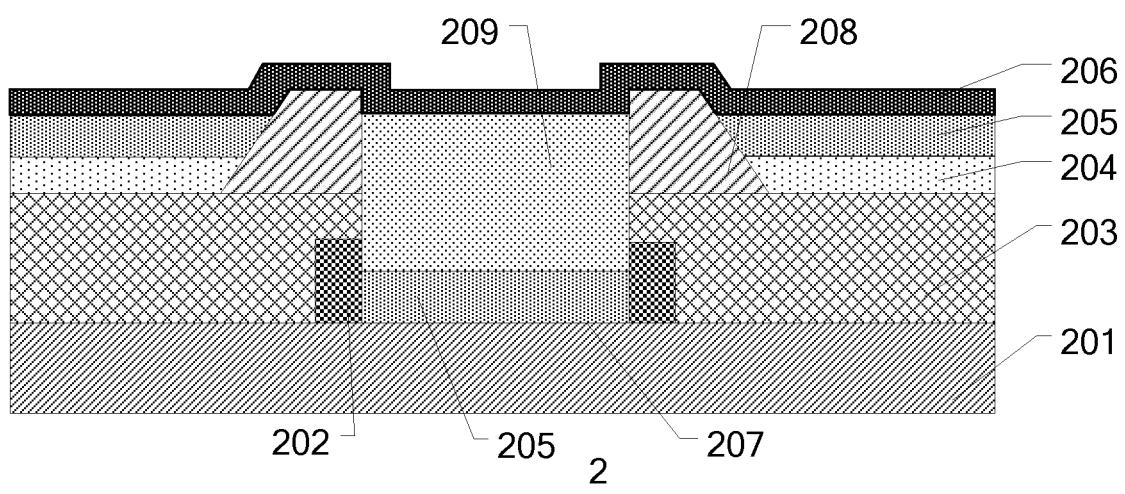

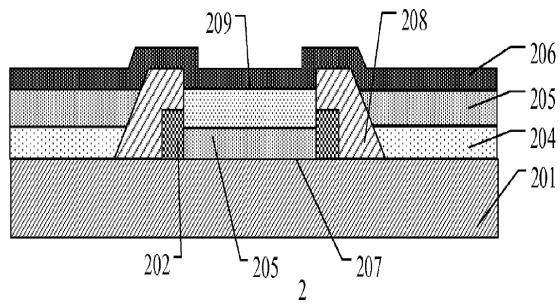

- 15 Fig. 2 is a schematic sectional view of an OLED array substrate provided by an embodiment of the present disclosure;

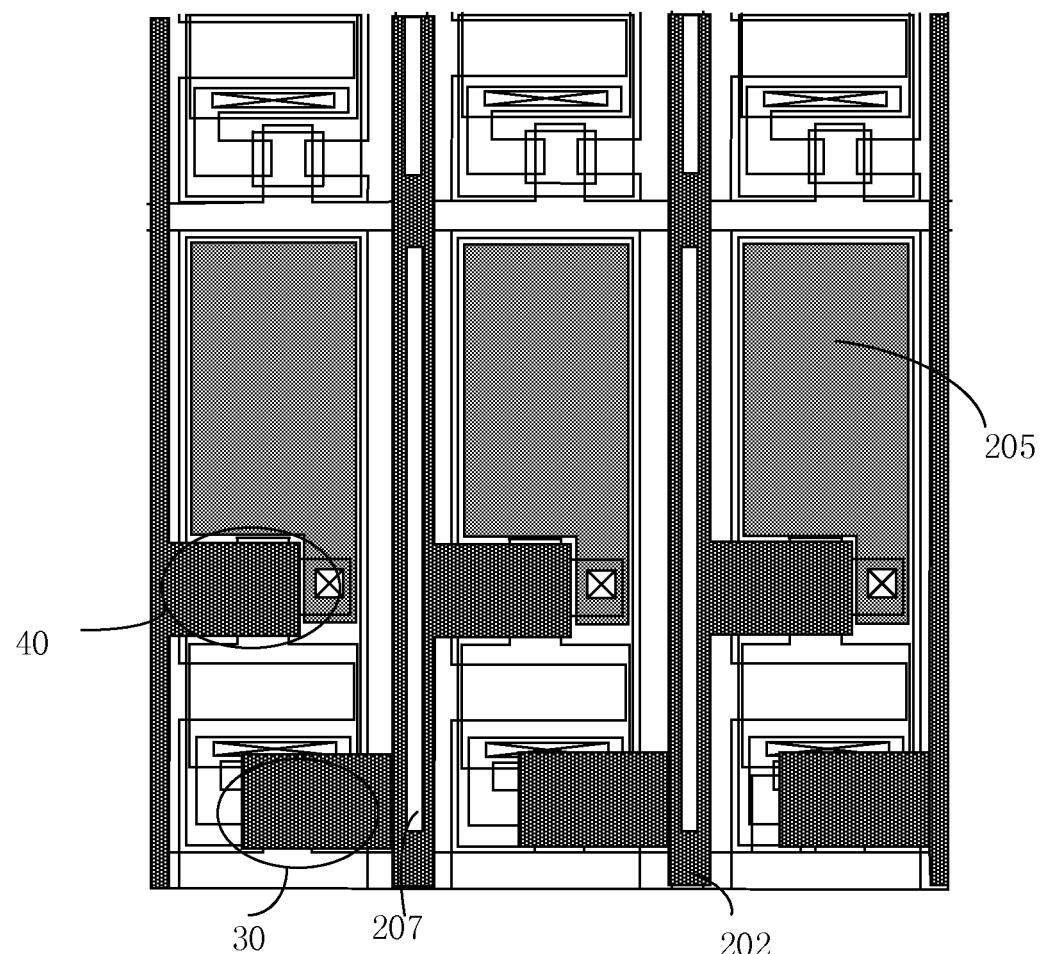

- 20 Fig. 3 is a schematic view of a planar structure of an OLED array substrate provided by an embodiment of the present disclosure;

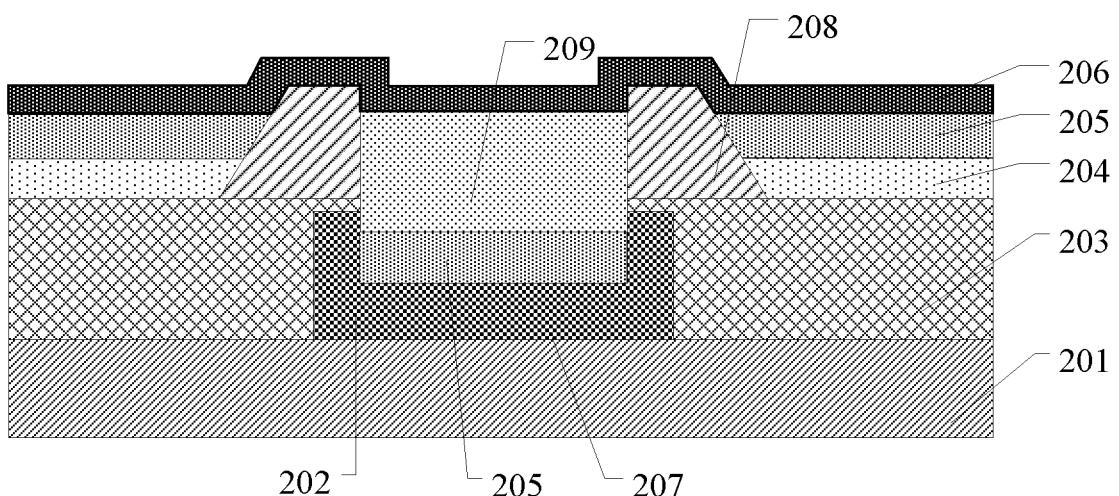

- 25 Fig. 4 is a schematic sectional view of an OLED array substrate provided by another embodiment of the present disclosure;

- 30 Fig. 5 is a schematic sectional view of an OLED array substrate provided by still another embodiment of the present disclosure;

- 35 Fig. 6 is a schematic sectional view of an OLED array substrate provided by still another embodiment of the present disclosure;

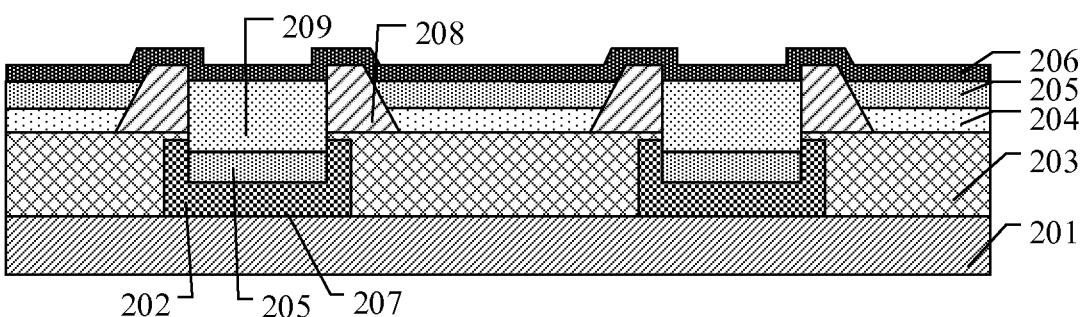

- 40 Fig. 7 is a schematic sectional view of an OLED array substrate provided by still another embodiment of the present disclosure;

- 45 Fig. 8 is a block diagram of a display panel provided by an embodiment of the present disclosure; and

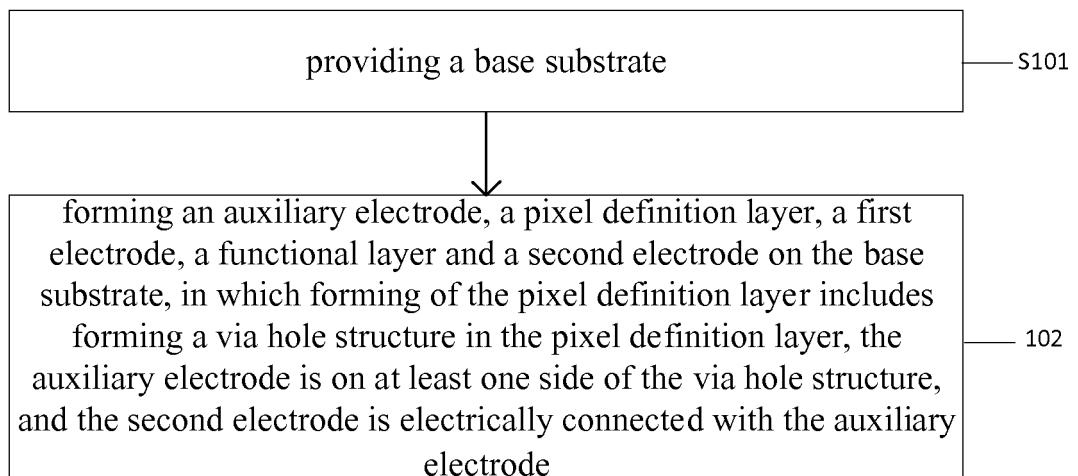

- 50 Fig. 9 is a flow diagram of a manufacturing method of an OLED array substrate provided by an embodiment of the present disclosure.

## Reference numerals:

**[0026]** 101, 201 - base substrate; 102, 202 - auxiliary electrode; 103, 203 - planarization layer; 104, 204 - first electrode; 105 - organic material functional layer; 205 - functional layer; 106, 206 - second electrode; 107, 207 - via hole structure; 108, 208 - pixel definition layer; 209 - conductive polymer layer; 1 - display panel; 2 - electroluminescent diode array substrate; 20 - OLED device; 30 - switching transistor; 40 - driving transistor.

## DETAILED DESCRIPTION

**[0027]** In order to make objects, technical details and advantages of embodiments of the disclosure clear, the technical solutions of the embodiments will be described in a clearly and fully understandable way in connection with the related drawings. It is apparent that the described embodiments are just a part but not all of the embodiments of the disclosure. Based on the described embodiments herein, those skilled in the art can obtain, without any inventive work, other embodiment(s) which should be within the scope of the disclosure.

**[0028]** Unless otherwise defined, all the technical and scientific terms used herein have the same meanings as commonly understood by one of ordinary skill in the art to which the present invention belongs. The terms "first," "second," etc., which are used in the description and claims of the present application, are not intended to indicate any sequence, amount or importance, but distinguish various components. The terms "comprises," "comprising," "includes," "including," etc., are intended to specify that the elements or the objects stated before these terms encompass the elements or the objects listed after these terms as well as equivalents thereof, but do not exclude other elements or objects. The phrases "connect", "connected", etc., are not intended to define a physical connection or mechanical connection, but may include an electrical connection which is direct or indirect. The terms "on," "under," "right," "left" and the like are only used to indicate relative position relationship, and when the position of an object is described as being changed, the relative position relationship may be changed accordingly.

**[0029]** Electroluminescent diodes, for example, organic light-emitting diodes (OLED) and quantum dot light-emitting diodes (QLED) are mostly current-driven devices. In a case where an external circuit used for providing a driving current is too long or too thin, the external circuit leads to a serious voltage gradient (a voltage drop). To reduce the voltage drop, an auxiliary electrode is usually added in an electroluminescent diode display device. For example, the auxiliary electrode is formed on the electroluminescent diode array substrate, and the auxiliary electrode is electrically connected with a cathode by a via hole structure. However, in the process of manufacturing an OLED device, especially in the process of manufacturing a large-sized OLED panel, an organic material is evaporated at the via hole structure, and the organic material separates the cathode from the auxiliary electrode. In the process of manufacturing a QLED device, especially in the process of manufacturing a large-sized QLED panel, a quantum dot light-emitting layer is printed at the via hole structure, and the quantum dot light-emitting layer separates the cathode from the auxiliary electrode.

**[0030]** For example, the organic light-emitting diode array substrate is taken for an example. Fig. 1 is a schematic sectional view of an organic light-emitting diode (OLED) array substrate. As illustrated in Fig. 1, the organic light-emitting diode array substrate comprises: a base substrate 101; and an auxiliary electrode 102, a planarization layer 103, a first electrode 104, an organic material functional layer 105, a second electrode 106 and a pixel definition layer 108 disposed on the base substrate; and the planarization layer 103 is provided with a via hole structure 107.

**[0031]** For example, the second electrode 106 of the OLED array substrate is generally made of metallic silver with a thinner thickness, and the first electrode 104 is generally made of indium tin oxide (ITO), and both the

resistivity of the metal silver with a thinner thickness and the resistivity of the indium tin oxide (ITO) are high, and especially for the second electrode 106 with a large area, the second electrode 106 made of the thin metal silver has a higher resistivity, and the voltage drop (IR drop) is larger; in this case, the actual driving voltage of the OLED array substrate is greatly different from a power voltage, and in a large-sized OLED display device, a large area of uneven brightness phenomenon occurs, which affects the display effect. As illustrated in Fig. 1, the auxiliary electrode 102 formed on the base substrate 102 reduces the resistance of the second electrode 106. However, the subsequently formed organic material functional layer 105 separates the auxiliary electrode 102 from the second electrode 106, thus the auxiliary electrode 102 can't be in parallel connect with the second electrode 106, and can't reduce the voltage drop effectively.

**[0032]** The inventor of the present disclosure notes that changing the structural design of the auxiliary electrode can ensure that the second electrode is electrically connected with the auxiliary electrode, in this way, the auxiliary electrode electrically connected with the second electrode increases the equivalent thickness of the second electrode, thereby the resistance of the second electrode is reduced, and the problem that the large voltage drop caused by the large resistance of the second electrode in a case where the second electrode made of metallic silver with a thinner thickness is avoided, furthermore, the problem of damaging an organic light-emitting display panel due to the large voltage drop is avoided as well.

**[0033]** At least one embodiment of the present disclosure provides an electroluminescent diode array substrate, and the electroluminescent diode array substrate comprises: a base substrate, and an auxiliary electrode, a pixel definition layer, a first electrode, a functional layer, and a second electrode, which are disposed on the base substrate; the pixel definition layer is provided with a via hole structure; the auxiliary electrode is disposed on at least one side of the via hole structure; and the second electrode is electrically connected with the auxiliary electrode. The embodiment of the present disclosure ensures that the second electrode is electrically connected with the auxiliary electrode by changing the structural design of the auxiliary electrode, thereby the problem of the large voltage drop in the external circuit is avoided.

**[0034]** At least one embodiment of the disclosure provides an electroluminescent diode array substrate, and the electroluminescent diode array substrate is an organic light-emitting diode (OLED) array substrate or a quantum dot light-emitting diode (QLED) array substrate. The following is illustrated by taking the electroluminescent diode array substrate as the organic light-emitting diode (OLED) array substrate for example.

**[0035]** For example, Fig. 2 is a schematic sectional view of an OLED array substrate provided by at least one embodiment of the present disclosure. As illustrated in Fig. 2, the organic light-emitting diode array substrate 2

comprises: a base substrate 201, and an auxiliary electrode 202, a pixel definition layer 208, a first electrode 204, a functional layer 205 (for example, an organic material functional layer) and a second electrode 206 disposed on the base substrate 201, the pixel definition layer 208 is provided with a via hole structure 207, the auxiliary electrode 202 is disposed on at least one side of the via hole structure 207, and the second electrode 206 is electrically connected with the auxiliary electrode 202.

**[0036]** It should be noted that, the auxiliary electrode disposed on at least one side of the via hole structure not means that the auxiliary electrode is disposed on the outside or the inside of the via hole structure, but means that the auxiliary electrode is disposed on a side wall of at least one direction of the outside side of the via hole structure.

**[0037]** For example, an upper surface of the auxiliary electrode 202 is higher than an upper surface of the functional layer 205 of the via hole structure 207.

**[0038]** For example, the OLED array substrate includes a display region and a peripheral region outside the display region. The display region is also referred to as an AA (Active Area), and the display region is generally used for displaying. The peripheral region may be used for arranging a driving circuit, packaging a display panel, and the like. For example, in the peripheral region, the second electrode 206 is electrically connected with the auxiliary electrode 202, and in the display region, the second electrode 206 is electrically connected with the auxiliary electrode 202, in this way, the second electrode 206 and the auxiliary electrode 202 are connected at both ends respectively to form a parallel-connected circuit, or both ends that the second electrode 206 and the auxiliary electrode 202 connected to each other are located in the display region. In a case where the second electrode 206 receives a voltage signal and transmits the voltage signal, and the voltage signal reaches the auxiliary electrode 202 that electrically connected to the second electrode 206, the auxiliary electrode 202 transmits the voltage signal simultaneously with the second electrode 206 as a branch of the voltage signal, which is equivalent to that the second electrode 206 and the auxiliary electrode 202 form the parallel-connected circuit, in this way, the resistance in the process of electrical signal transmission is reduced; or the auxiliary electrode 202 receives the voltage signal firstly, in a case where the voltage signal reaches the second electrode 206 electrically connected to the auxiliary electrode 202, the second electrode 206 as a branch for transmitting the voltage signal simultaneously with the auxiliary electrode 202; or the second electrode 206 and the auxiliary electrode 202 receives the voltage signal simultaneously, the second electrode 206 and the auxiliary electrode 202 transmit the voltage signal simultaneously as two branches.

**[0039]** For example, as illustrated in Fig. 3, the OLED array substrate 2 further includes a power line, a data line and a gate line (not shown in Fig. 3) disposed on the base substrate 201, a pixel structure is disposed in a

region defined by the gate line and the data line intersecting with each other, for example, the pixel structure includes a switching transistor 30, a driving transistor 40, and an OLED device 20, and the switching transistor 30 is connected to the gate line and the data line, the driving transistor 40 is connected to the switching transistor 30, the power line, and the OLED device.

**[0040]** For example, as illustrated in Fig. 2 and Fig. 3, the pixel definition layer 208 is located between the first electrode 204 and the second electrode 206, and the pixel definition layer 208 is used for isolating two sub-pixel units adjacent to each other.

**[0041]** For example, the pixel structure, the gate line and the data line are located in the display region, in addition to the gate line and the data line, the OLED array substrate may further include a detection compensation line connecting a pixel unit and a detection integrated circuit. The detection compensation line is located in the display region.

**[0042]** For example, as illustrated in Fig. 2, the upper surface of the auxiliary electrode 202 on at least one side of the via hole structure 207 is higher than the upper surface of the functional layer 205 in the via hole structure 207, in this way, the auxiliary electrode 202 is electrically connected to the second electrode 206 through the portion of the auxiliary electrode that higher than the upper surface of the functional layer 205 in the via hole structure 207.

**[0043]** For example, Fig. 4 is a schematic sectional view of an OLED array substrate provided by another embodiment of the present disclosure. As illustrated in Fig. 4, the organic light-emitting diode array substrate further includes a planarization layer 203 disposed between the base substrate 201 and the pixel definition layer 208, in which the via hole structure 207 extends from the pixel definition layer 208 and penetrates through the planarization layer 203.

**[0044]** For example, as illustrated in Fig. 4, the via hole structure 207 extends from pixel definition layer 208 and penetrates through planarization layer 203. In this way, the depth of the via hole structure 207 is approximately equal to the sum of the thickness of the pixel definition layer 208 and the thickness of the planarization layer 203.

**[0045]** For example, in the embodiment of the present disclosure, the thickness of the functional layer 205 is from about 100 nm to about 300 nm, for example, the thickness of the functional layer 205 is 100 nm, 200 nm or 300 nm, etc.

**[0046]** For example, the thickness of auxiliary electrode 202 is from about 0.5  $\mu$ m to about 1  $\mu$ m, such as 0.5  $\mu$ m, 0.6  $\mu$ m, 0.7  $\mu$ m, 0.8  $\mu$ m, 0.9  $\mu$ m or 1  $\mu$ m, etc.

**[0047]** For example, the thickness of planarization layer 203 is from about 1  $\mu$ m to about 3  $\mu$ m, such as 1  $\mu$ m, 2  $\mu$ m or 3  $\mu$ m, etc.

**[0048]** For example, the thickness of the pixel definition layer 208 is from about 1  $\mu$ m to about 3  $\mu$ m, such as 1  $\mu$ m, 2  $\mu$ m or 3  $\mu$ m, etc.

**[0049]** For example, the thickness of the first electrode

204 is from about 200  $\mu\text{m}$  to about 300  $\mu\text{m}$ , for example, 200  $\mu\text{m}$ , 250  $\mu\text{m}$ , or 300  $\mu\text{m}$ , etc.

**[0050]** For example, the thickness of the second electrode 206 is from about 100  $\mu\text{m}$  to about 200  $\mu\text{m}$ , for example, 100  $\mu\text{m}$ , 150  $\mu\text{m}$ , or 200  $\mu\text{m}$ , etc.

**[0051]** For example, in a case where the second electrode 206 is directly connected to the auxiliary electrode 202, the second electrode 206 may have a segment difference (step), that is, the second electrode 206 is broken. A conductive polymer layer 209 is arranged in the via hole structure 207 to raise the functional layer 205 so as to prevent the second electrode 206 from breaking, as illustrated in Fig. 2 and Fig. 4, the conductive polymer layer 209 is formed between the auxiliary electrode 202 and the second electrode 206. The second electrode 206 is electrically connected with the auxiliary electrode 202 through the conductive polymer layer 209 to reduce the risk of forming a segment difference of the second electrode 206.

**[0052]** For example, the thickness of the conductive polymer layer 209 is larger than the thickness of the planarization layer 203, and the thickness of the conductive polymer layer 209 is smaller than the sum of the thickness of the planarization layer 203 and the thickness of the pixel definition layer 208.

**[0053]** For example, the upper surface of the conductive polymer layer 209 is flush with the upper surface of the pixel definition layer 208, in this way, the risk that the second electrode 206 having a segment difference is basically eliminated.

**[0054]** For example, the thickness of the conductive polymer layer 209 is from about 2  $\mu\text{m}$  to about 5.7  $\mu\text{m}$ . For example, the thickness of the conductive polymer layer is 2  $\mu\text{m}$ , 3  $\mu\text{m}$ , 4  $\mu\text{m}$  or 5  $\mu\text{m}$ , etc.

**[0055]** For example, the conductivity of the conductive polymer layer is greater than  $10^{-6}$  S/m, which ensures that the auxiliary electrode 202 is electrically connected with the second electrode 206.

**[0056]** For example, a material of the conductive polymer layer 209 comprises at least one of polypyrrole, polyphenylene sulfide, polyphthalocyanine, polyaniline and polythiophene.

**[0057]** For example, Fig. 5 is a schematic sectional view of an OLED array substrate provided by still another embodiment of the present disclosure. As illustrated in Fig. 5, the auxiliary electrode 202 in the via hole structure 207 is a structure in a U shape, it is equivalent to two side walls of the auxiliary electrode 202 being raised so that the second electrode 206 is directly electrically connected with the auxiliary electrode 202 at the via hole structure 207, thus the step of forming the conductive polymer layer is reduced, and the risk of forming a segment difference of the second electrode 206 reduced.

**[0058]** It should be noted that, the auxiliary electrode 202 is a structure in a U shape means that in the direction perpendicular to the surface of the base substrate 201, the cross-section structure of the auxiliary electrode (for example, the longitudinal cross-section of the auxiliary

electrode) is in a concave shape.

**[0059]** For example, Fig. 6 is a schematic sectional view of an OLED array substrate provided by still another embodiment of the present disclosure. For example, the conductive polymer layer 209 is formed on the auxiliary electrode 202 in a U shape, which further reduces the risk of forming the segment difference of the second electrode 206.

**[0060]** For example, the auxiliary electrode 202 is a plate-type structure, and the via hole structure 207 is at least covered with the auxiliary electrode 202; or, on a plane parallel to the surface of the base substrate 201 and along the extension direction of the via hole structure 207, there are a plurality of auxiliary electrodes 202, and the plurality of auxiliary electrodes 202 are spaced apart from each other.

**[0061]** For example, Fig. 7 is a schematic sectional view of an OLED array substrate provided by still another embodiment of the present disclosure. As illustrated in Fig. 7, the electroluminescent diode array substrate comprises a plurality of via hole structures 207 penetrating through the planarization layer 203 and the pixel definition layer 208, and the second electrode 206 is electrically connected with the auxiliary electrodes 202 by the plurality of via hole structures 207, so that the second electrode 206 is connected in parallel with the auxiliary electrodes 202 respectively. Fig. 7 shows two via hole structures 207. Obviously, the number of the via hole structures in the embodiments of the present disclosure is not limited to the above example, and more via hole structures 207 can be formed to further reduce the resistance of the second electrode and the auxiliary electrodes, in addition, the second electrode 206 connected in parallel with the auxiliary electrodes 202 through the plurality of via hole structures 207 increases the thickness of the second electrode 206, which is equivalent to increasing of the cross-sectional area of the second electrode 206, and the resistance of the second electrode 206 is further reduced.

**[0062]** For example, the pixel definition layer 208 is made of an organic insulating material (for example, an acrylic resin) or an inorganic insulating material (for example, silicon nitride SiNx or silicon oxide SiOx), the pixel definition layer 208 has an insulating property. The pixel definition layer 208 may be considered as the insulating structure disposed between the second electrode 206 and the auxiliary electrode 202.

**[0063]** For example, the first electrode 205 is made of a transparent conductive material, and the transparent conductive material includes indium tin oxide (ITO), indium zinc oxide (IZO), indium gallium oxide (IGO), zinc gallium oxide (GZO), Indium oxide ( $\text{In}_2\text{O}_3$ ), aluminum zinc oxide (AZO) and carbon nanotubes.

**[0064]** For example, the first electrode 205 is made of a metal conductive material, and the metal conductive material includes a single metal such as Cu, Cr, Mo, Au, Ag and Pt metal, or an alloy material formed of the above metals, for example, a copper chromium alloy (CuCr) or

a chromium molybdenum alloy (CrMo).

**[0065]** For example, the first electrode 205 is a stacked structure formed by any combination of the above-mentioned transparent conductive material and the metal conductive material. For example, the first electrode 205 is in a structure that the metal conductive material is sandwiched between two transparent conductive materials, such as ITO-Mo-IZO, ITO-Cr-In2O3, ITO-Cu-ZnO and ITO-Pt-IGO, or the first electrode 205 is a stacked double-layer structure made of the metal conductive material and the transparent conductive material, such as IZO-Mo, ITO-Cr, ZnO-Mg and ITO-Au. For example, the stacked structure formed of any combination of the transparent conductive material and the metal conductive material is not limited to the stacked double-layer structure and the stacked triple-layer structure. It may also be a stacked structure with multiple layers of other layers, for example, a stacked structure of four layers, a stacked structure of five layers, etc.

**[0066]** It should be noted that, because the work function of the metal material or the work function of the alloy material for forming the first electrode is relatively low, the first electrode has poor compatibility with the organic material functional layer in the OLED array substrate. The transparent conductive material formed on a side of the first metal layer close to the functional layer formed of the organic material improves the work function of the first metal, so that the first electrode is better matched with the functional layer formed of the organic material. In addition, the first electrode of the double-layer structure or the triple-layer structure has a lower resistance than the first electrode of the single-layer structure, and the resistance of the first electrode is lower, in this way, the resistance of the first electrode is reduced.

**[0067]** For example, the material of the second electrode 206 includes magnesium, aluminum, lithium or other single metal, or magnesium aluminum alloy (MgAl), lithium aluminum alloy (LiAl), and the like.

**[0068]** For example, in the electroluminescent diode array substrate provided by at least one embodiment of the disclosure, taking the array substrate as the organic light-emitting diode (OLED) array substrate as an example, this functional layer includes a light-emitting layer, an electron injection layer, an electron transmission layer, a hole injection layer and a hole transmission layer.

**[0069]** For example, the method of manufacturing the functional layer in the organic light-emitting diode (OLED) array substrate includes a vacuum evaporation method and a solution method. The vacuum evaporation method is suitable for small organic molecules without solvent, and the thicknesses of each layers of organic material functional layer is uniform. The solution method includes a spin coating method, an inkjet printing method and a nozzle coating method, and the solution method is suitable for polymer materials and soluble small molecules, it has the advantage of low cost in production equipment, and has outstanding advantages in the production of large-scale and large-sized products, especially, the

inkjet printing technology can accurately spray solution to the pixel region.

**[0070]** It should be noted that, unlike the organic light-emitting diode (OLED) array substrate, the quantum dots in the self-luminescent quantum dots light-emitting diodes (QLED) cannot adopt the same evaporation method as the self-luminescent OLEDs, due to the phenomenon that the quantum dots are easy to be affected by heat and moisture, and therefore only the ink-jet printing can be used.

**[0071]** At least one embodiment of the present disclosure further provides a display panel, and the display panel includes any one of the electroluminescent diode array substrate described above.

**[0072]** For example, Fig. 8 is a block diagram of a display panel provided by an embodiment of the present disclosure. As illustrated in Fig. 8, the display panel 1 includes an electroluminescent diode array substrate 2 disposed therein. For example, the display panel 1 can be applied to a display apparatus, for example, the display apparatus is a mobile phone, a tablet computer, a television, a display, a notebook computer, a digital picture frame, a navigation system and any other product or component having a display function. The embodiments of the display apparatus can be referred to the above embodiments of the electroluminescent diode array substrate, which is omitted herein.

**[0073]** At least one embodiment of the present disclosure further provides a method of manufacturing an electroluminescent diode array substrate, and the electroluminescent diode array substrate is an organic light-emitting diode (OLED) array substrate or a quantum dot light-emitting diode (QLED) array substrate. The following is illustrated by taking the electroluminescent diode array substrate as the organic light-emitting diode (OLED) array substrate for example.

**[0074]** For example, Fig. 9 is a flow diagram of a manufacturing method of an OLED array substrate provided by an embodiment of the present disclosure. For example, the manufacturing method comprises the following steps:

S101: providing a base substrate.

S102: forming an auxiliary electrode, a pixel definition layer, a first electrode, a functional layer and a second electrode on the base substrate, in which forming of the pixel definition layer includes forming a via hole structure in the pixel definition layer, the auxiliary electrode is on at least one side of the via hole structure, and the second electrode is electrically connected with the auxiliary electrode.

**[0075]** For example, in the manufacturing method provided by at least one embodiment of the present disclosure, the upper surface of the auxiliary electrode on at least one side of the via hole structure is higher than the upper surface of the functional layer in the via hole structure, in this way, the auxiliary electrode is electrically con-

nected to the second electrode through the portion of the auxiliary electrode that higher than the upper surface of the functional layer in the via hole structure.

**[0076]** For example, a planarization layer is formed before forming the pixel definition layer, and the via hole structure extends from the pixel definition layer to penetrate through the planarization layer, and the pixel definition layer is used for isolating two sub-pixel units adjacent to each other.

**[0077]** For example, the second electrode is electrical- 10 ly connected with the auxiliary electrodes by the plurality of via hole structures, so that the second electrode is connected in parallel with the auxiliary electrodes respectively. In addition, the second electrode connected in parallel with the auxiliary electrodes through the plurality of via hole structures increases the thickness of the second electrode, which is equivalent to increasing of the cross-sectional area of the second electrode, and the resistance of the second electrode 206 is further reduced.

**[0078]** For example, the pixel definition layer is made of an organic insulating material (for example, an acrylic resin) or an inorganic insulating material (for example, silicon nitride SiNx or silicon oxide SiOx), the pixel definition layer has an insulating property. The pixel definition layer may be considered as the insulating structure disposed between the second electrode and the auxiliary electrode.

**[0079]** For example, the manufacturing method provided by at least one embodiment of the present disclosure further includes forming a conductive polymer layer in the via hole structure, and the second electrode is electrically connected with the auxiliary electrode by the conductive polymer layer. In a case where the second electrode is directly connected to the auxiliary electrode, the second electrode may have a segment difference, that is, the second electrode is broken. The conductive polymer layer is arranged in the via hole structure to raise the functional layer so as to prevent the second electrode from breaking.

**[0080]** For example, the thickness of the conductive polymer layer is larger than the thickness of the planarization layer, and the thickness of the conductive polymer layer is smaller than the sum of the thickness of the planarization layer and the thickness of the pixel definition layer.

**[0081]** For example, the upper surface of the conductive polymer layer is flush with an upper surface of the pixel definition layer, in this way, the risk that the second electrode having a segment difference is basically eliminated.

**[0082]** For example, the thickness of the conductive polymer layer is from about 2  $\mu\text{m}$  to about 5.7  $\mu\text{m}$ . For example, the thickness of the conductive polymer layer is 2  $\mu\text{m}$ , 3  $\mu\text{m}$ , 4  $\mu\text{m}$  or 5  $\mu\text{m}$ , etc.

**[0083]** For example, the conductivity of the conductive polymer layer is greater than  $10^{-6} \text{ S/m}$ , which ensures that the auxiliary electrode is electrically connected with the second electrode.

**[0084]** For example, the material of the conductive polymer layer comprises at least one of polypyrrole, polyphenylene sulfide, polyphthalocyanine, polyaniline and polythiophene.

5 **[0085]** For example, in the manufacturing method provided by the embodiment of the present disclosure, the conductive polymer layer is formed by an inkjet printing method.

10 **[0086]** For example, in an embodiment of the present disclosure, the thickness of the functional layer is from about 100 nm to about 300 nm, for example, the thickness of the functional layer is 100 nm, 200 nm or 300 nm, etc.

15 **[0087]** For example, the thickness of auxiliary electrode 202 is from about 0.5  $\mu\text{m}$  to about 1  $\mu\text{m}$ , such as 0.5  $\mu\text{m}$ , 0.6  $\mu\text{m}$ , 0.7  $\mu\text{m}$ , 0.8  $\mu\text{m}$ , 0.9  $\mu\text{m}$  or 1  $\mu\text{m}$ , etc.

20 **[0088]** For example, the thickness of planarization layer 203 is from about 1  $\mu\text{m}$  to about 3  $\mu\text{m}$ , such as 1  $\mu\text{m}$ , 2  $\mu\text{m}$  or 3  $\mu\text{m}$ , etc.

25 **[0089]** For example, the thickness of the pixel definition layer 208 is from about 1  $\mu\text{m}$  to about 3  $\mu\text{m}$ , such as 1  $\mu\text{m}$ , 2  $\mu\text{m}$  or 3  $\mu\text{m}$ , etc.

30 **[0090]** For example, thickness of the first electrode 204 is from about 200  $\mu\text{m}$  to about 300  $\mu\text{m}$ , for example, 200  $\mu\text{m}$ , 250  $\mu\text{m}$ , or 300  $\mu\text{m}$ , etc.

35 **[0091]** For example, the thickness of the second electrode 206 is from about 100  $\mu\text{m}$  to about 200  $\mu\text{m}$ , for example, 100  $\mu\text{m}$ , 150  $\mu\text{m}$ , or 200  $\mu\text{m}$ , etc.

40 **[0092]** The electroluminescent diode array substrate, the method of manufacturing the electroluminescent diode array substrate and the display panel provided by the embodiments of the present disclosure have at least one of the following beneficial effects:

45 (1) in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, by changing the structural design of the auxiliary electrode, the electrical connection between the second electrode and the auxiliary electrode is ensured, in this way, the auxiliary electrode electrically connected with the second electrode increases the equivalent thickness of the second electrode.

50 (2) in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, the resistance of the second electrode is reduced, and the problem that the large voltage drop caused by the large resistance of the second electrode in a case where the second electrode made of metallic silver with a thinner thickness is avoided.

55 (3) in the electroluminescent diode array substrate provided by at least one embodiment of the present disclosure, the problem of damaging an organic light-emitting display panel due to the large voltage drop is avoided.

**[0093]** The following points need to be explained:

(1) The drawings of the embodiments of the present

disclosure are only related to the structures related to the embodiments of the present disclosure, and other structures can refer to general designs.

(2) For clarity, in the drawings for describing the embodiments of the present disclosure, a thickness of a layer or a thickness of a region is exaggerated or reduced, that is, these drawings are not drawn according to an actual scale. It should be understood that: in a case where an element such as a layer, a film, a region or a substrate is referred to as being disposed "on" or "beneath" another element, the element may be "directly" disposed "on" or "beneath" another element, or an intermediate element may be provided.

(3) In the absence of conflict, the embodiments of the present disclosure and the features in the embodiments can be combined with each other to obtain new embodiments.

**[0094]** What is described above is related to the illustrative embodiments of the disclosure only and not limitative to the scope of the disclosure. Therefore, the scopes of the disclosure are defined by the accompanying claims.

## Claims

1. An electroluminescent diode array substrate, comprising:

a base substrate, and

an auxiliary electrode, a pixel definition layer, a first electrode, a functional layer, and a second electrode which are disposed on the base substrate,

wherein the pixel definition layer is provided with a via hole structure;

the auxiliary electrode is disposed on at least one side of the via hole structure; and

the second electrode is electrically connected with the auxiliary electrode.

2. The electroluminescent diode array substrate according to claim 1, wherein an upper surface of the auxiliary electrode is higher than an upper surface of the functional layer in the via hole structure.

3. The electroluminescent diode array substrate according to claim 1 or 2, wherein the auxiliary electrode is a structure in a U shape.

4. The electroluminescent diode array substrate according to claim 1 or 2, wherein the auxiliary electrode is a plate-type structure; or there are a plurality of auxiliary electrodes which are spaced apart from each other.

5. The electroluminescent diode array substrate according to claim 3 or 4, wherein a conductive polymer layer is provided in the via hole structure, and the second electrode is electrically connected with the auxiliary electrode by the conductive polymer layer.

6. The electroluminescent diode array substrate according to claim 5, wherein a thickness of the conductive polymer layer is less than a thickness of the pixel definition layer.

7. The electroluminescent diode array substrate according to claim 5, wherein a conductivity of the conductive polymer layer is greater than  $10^{-6}$  S/m.

8. The electroluminescent diode array substrate according to claim 5 or 6, wherein a material of the conductive polymer layer comprises at least one of polypyrrole, polyphenylene sulfide, polyphthalocyanine, polyaniline and polythiophene.

9. The electroluminescent diode array substrate according to any one of claims 5 to 8, further comprising a planarization layer disposed between the base substrate and the pixel definition layer,

wherein the via hole structure extends from the pixel definition layer and penetrates through the planarization layer.

10. The electroluminescent diode array substrate according to claim 9, wherein a thickness of the conductive polymer layer is larger than a thickness of the planarization layer, and the thickness of the conductive polymer layer is smaller than a sum of the thickness of the planarization layer and a thickness of the pixel definition layer.

11. The electroluminescent diode array substrate according to claim 9, wherein an upper surface of the conductive polymer layer is flush with an upper surface of the pixel definition layer.

12. The electroluminescent diode array substrate according to claim 9, wherein there are a plurality of via hole structures penetrating through the planarization layer and the pixel definition layer, and the second electrode is electrically connected with the auxiliary electrode by the plurality of via hole structures.

13. The electroluminescent diode array substrate according to claim 9, wherein a thickness of the functional layer is from about 100 nm to about 300 nm, a thickness of the auxiliary electrode is from about 0.5  $\mu$ m to about 1  $\mu$ m, a thickness of the planarization layer is from about 1  $\mu$ m to about 3  $\mu$ m, a thickness of the pixel definition layer is from about 1  $\mu$ m to about 3  $\mu$ m, and a thickness of the conductive

polymer layer is from about 2  $\mu\text{m}$  to about 5.7  $\mu\text{m}$ .

14. The electroluminescent diode array substrate according to claim 13, wherein the functional layer comprises at least one of a light-emitting layer, an electron injection layer, an electron transmission layer, a hole injection layer and a hole transmission layer. 5

15. A display panel, comprising the electroluminescent diode array substrate according to any one of claims 1 to 14. 10

16. A method of manufacturing an electroluminescent diode array substrate, comprising: 15

providing a base substrate,

forming an auxiliary electrode, a pixel definition layer, a first electrode, a functional layer and a second electrode on the base substrate,

wherein the pixel definition layer is provided with a via hole structure; 20

the auxiliary electrode is disposed on at least one side of the via hole structure; and

the second electrode is electrically connected with the auxiliary electrode. 25

17. The manufacturing method according to claim 16, wherein an upper surface of the auxiliary electrode which is formed on at least one side of the via hole structure is higher than an upper surface of the functional layer in the via hole structure. 30

18. The manufacturing method according to claim 16 or 17, before forming the auxiliary electrode, further comprising: 35

forming a planarization layer on the base substrate, wherein the via hole structure extends from the pixel definition layer and penetrates through the planarization layer.

40

19. The manufacturing method according to any one of claims 16 to 18, further comprising:

forming a conductive polymer layer in the via hole structure, wherein the second electrode is electrically connected with the auxiliary electrode by the conductive polymer layer. 45

20. The manufacturing method according to claim 19, wherein the conductive polymer layer is formed by an inkjet printing method. 50

Fig. 1

Fig.2

Fig. 3

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig. 8

Fig.9

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/CN2018/091952

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |                                                              |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 5  | <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>H01L 51/52(2006.01)i<br><br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                    |                                                              |

| 10 | <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>H01L51/-;H01L27/-;H05B33/-<br><br>Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                    |                                                              |

| 15 | Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>CNABS; CNTXT; SIPOABS; VEN; USTXT; EPTXT; WOTXT; CNKI: 有机, 发光, 电极, 阴极, 辅助, 像素, 象素, 限定, 定义, 界定, 坝, 堤, 孔, 槽, 凹, 填充; organic, light, emit, electroluminescence, electrode, cathode, auxiliary, pixel, limit, define, bank, dam, bar, hole, groove, trough, concave, fill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                    |                                                              |

| 20 | <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    |                                                              |

| 20 | Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Citation of document, with indication, where appropriate, of the relevant passages                                                 | Relevant to claim No.                                        |

| 25 | PX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CN 107331691 A (BOE TECHNOLOGY GROUP CO., LTD.) 07 November 2017<br>(2017-11-07)<br>description, paragraphs 37-76, and figures 1-6 | 1-4, 15-18                                                   |

| 30 | PY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CN 107331691 A (BOE TECHNOLOGY GROUP CO., LTD.) 07 November 2017<br>(2017-11-07)<br>description, paragraphs 37-76, and figure 1    | 5-14, 19-20                                                  |

| 35 | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | US 2015090989 A1 (JAPAN DISPLAY INC.) 02 April 2015 (2015-04-02)<br>description, paragraphs 31-44, and figures 4-7                 | 1-4, 15-18                                                   |

| 40 | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | US 2015090989 A1 (JAPAN DISPLAY INC.) 02 April 2015 (2015-04-02)<br>description, paragraphs 31-44, and figures 4-7                 | 5-14, 19-20                                                  |

| 45 | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | US 2016043341 A1 (LG DISPLAY CO., LTD.) 11 February 2016 (2016-02-11)<br>description, paragraphs 51-113, and figures 2-5F          | 1-4, 15-18                                                   |

| 50 | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | US 2016043341 A1 (LG DISPLAY CO., LTD.) 11 February 2016 (2016-02-11)<br>description, paragraphs 51-113, and figures 2-5F          | 5-14, 19-20                                                  |

| 55 | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CN 106057844 A (LG DISPLAY CO., LTD.) 26 October 2016 (2016-10-26)<br>description, paragraphs 49-94, and figures 5-20              | 1-4, 15-18                                                   |

|    | <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                    | <input checked="" type="checkbox"/> See patent family annex. |

|    | <p>* Special categories of cited documents:</p> <p>“A” document defining the general state of the art which is not considered to be of particular relevance</p> <p>“E” earlier application or patent but published on or after the international filing date</p> <p>“L” document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)</p> <p>“O” document referring to an oral disclosure, use, exhibition or other means</p> <p>“P” document published prior to the international filing date but later than the priority date claimed</p> <p>“T” later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</p> <p>“X” document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</p> <p>“Y” document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art</p> <p>“&amp;” document member of the same patent family</p> |                                                                                                                                    |                                                              |

|    | Date of the actual completion of the international search<br><br><b>18 August 2018</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date of mailing of the international search report<br><br><b>10 September 2018</b>                                                 |                                                              |