EP 1 649 442 B1

(12)

## EUROPEAN PATENT SPECIFICATION

(45) Date of publication and mention

of the grant of the patent:

20.01.2016 Bulletin 2016/03

(51) Int Cl.:

G09G 3/32 (2006.01)

(21) Application number: 05745906.7

(86) International application number:

PCT/JP2005/010104

(22) Date of filing: 26.05.2005

(87) International publication number:

WO 2005/116968 (08.12.2005 Gazette 2005/49)

### (54) OLED DISPLAY WITH PING PONG CURRENT DRIVING CIRCUIT AND SIMULTANEOUS SCANNING OF LINES

OLED-DISPLAY MIT PINGPONG-STROMANSTEUERSCHALTUNG UND GLEICHZEITIGEM SCANNEN VON LINIEN

SYSTEM D'AFFICHAGE ÉLECTROLUMINESCENT ORGANIQUE AVEC CIRCUIT DE COMMANDE DE COURANT EN MODE PING-PONG ET LE BALAYAGE SIMULTANÉE DES LIGNES

(84) Designated Contracting States:

**DE FI FR GB NL**

- **OZAKI, Tsuyoshi**

Hamura-shi

Tokyo 205-8555 (JP)

- **OGURA, Jun**

Hamura-shi

Tokyo 205-8555 (JP)

(30) Priority: 28.05.2004 JP 2004160140

14.09.2004 JP 2004266441

(74) Representative: **Grünecker Patent- und Rechtsanwälte**

PartG mbB

Leopoldstraße 4

80802 München (DE)

(43) Date of publication of application:

**26.04.2006 Bulletin 2006/17**

(56) References cited:

**EP-A- 0 837 445** EP-A- 0 911 796

**EP-A- 1 207 511** WO-A-2004/086347

**US-A1- 2003 001 870** US-A1- 2003 132 931

(73) Proprietor: **CASIO COMPUTER CO., LTD.**

Shibuya-ku,

Tokyo 151-8543 (JP)

(72) Inventors:

• **SHIRASAKI, Tomoyuki**

Hamura-shi

Tokyo 205-8555 (JP)

EP 1 649 442 B1

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

## Description

### Technical Field

**[0001]** The present invention relates to a display drive apparatus, a display apparatus and a drive control method thereof, and more particularly to a display drive apparatus which can be applied to a display panel having a plurality of display pixels arranged therein, each display pixel comprising a current controlled type light emitting element which emits a light with a predetermined luminance gradation by supplying a current corresponding to display data thereto, and a display apparatus comprising the display drive apparatus, and a drive control method thereof.

### Background Art

**[0002]** There has been conventionally known a light emitting element type display (a display apparatus) comprising a display panel in which display pixels each comprising a current controlled type light emitting element which emits a light with a predetermined luminance gradation in accordance with a current value of a drive current supplied thereto are two dimensionally arranged like an organic electroluminescence element (which will be referred to as an "organic EL element" hereinafter) or a light emitting diode (LED).

**[0003]** In particular, a light emitting element type display adopting an active matrix drive mode has a higher display response speed and no field angle dependence and can realize high luminance/high contrast, high definition of a display image quality, a reduction in power consumption and others as compared with a liquid crystal display apparatus (an LCD) which has greatly spread in recent years. Further, the light emitting element type display comprises light emitting element type display pixels and hence does not require a backlight like a liquid crystal display apparatus. Therefore, the light emitting element type display has very excellent characteristics that a further reduction in thickness and weight is possible, and it has been keenly studied and developed as a next-generation display.

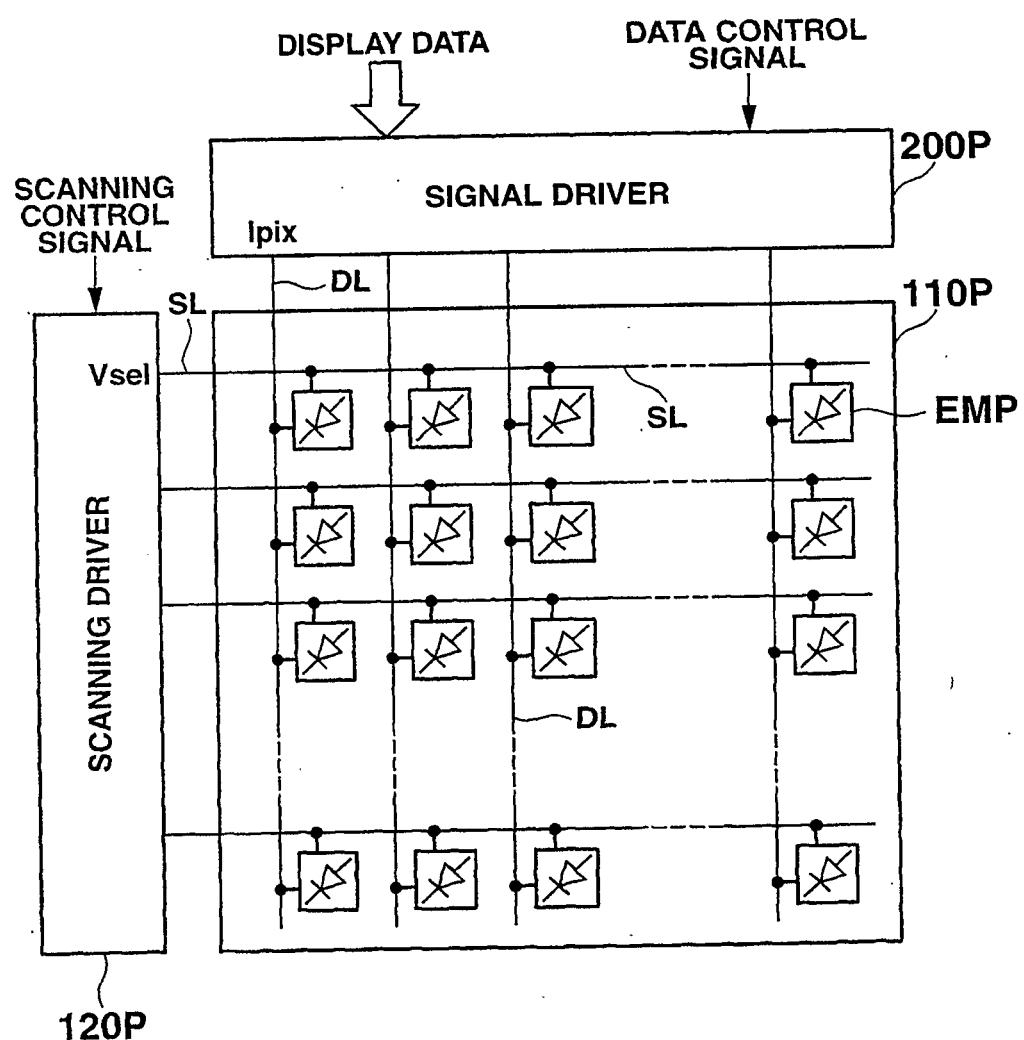

**[0004]** FIG. 18 is a schematic view showing a structural example of a primary part of a light emitting element type display adopting an active matrix drive mode in a prior art.

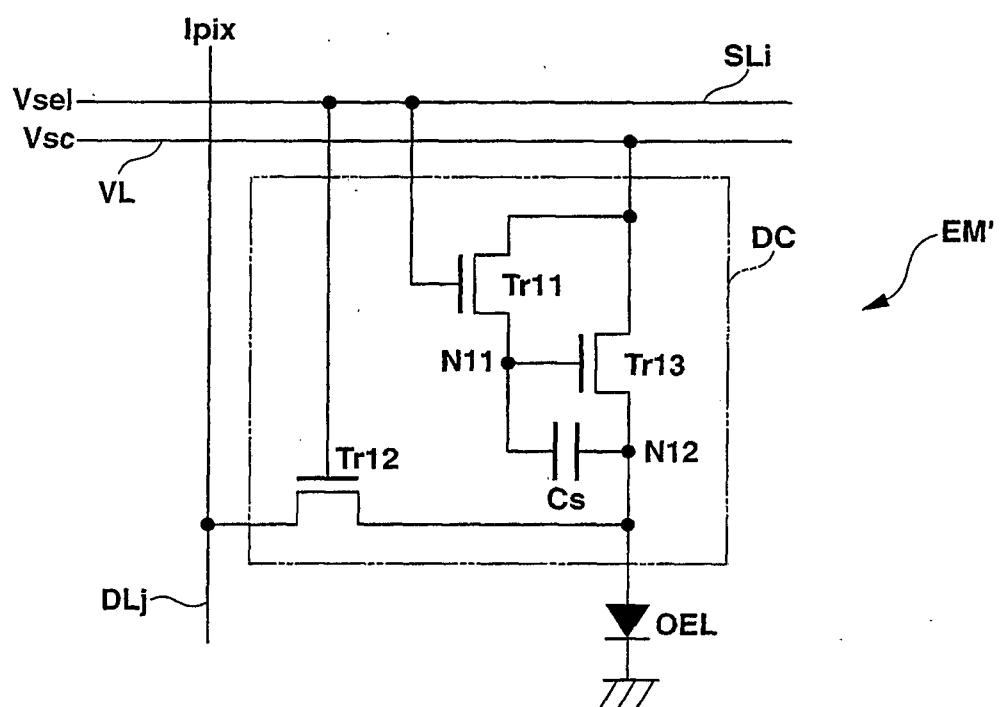

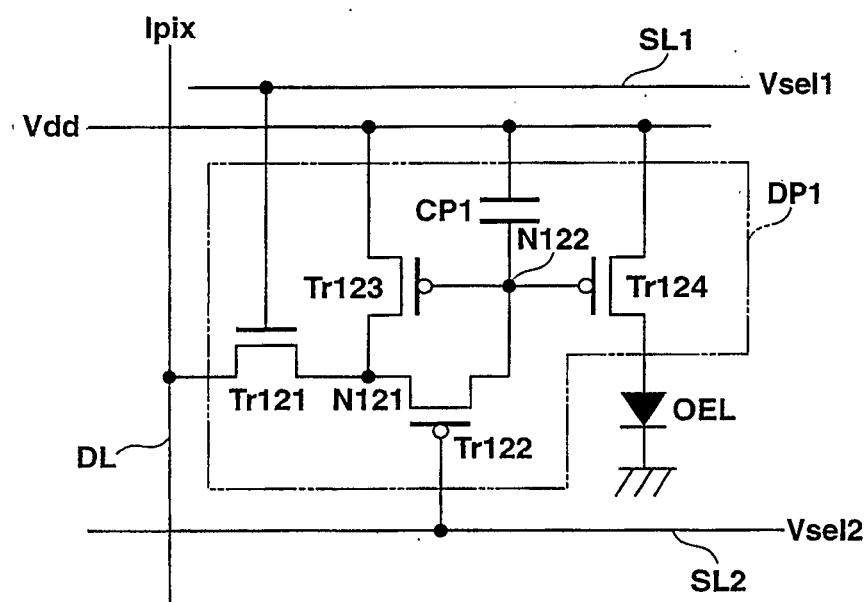

**[0005]** FIG. 19 is an equivalent circuit diagram showing a structural example of a display pixel applied to the light emitting type display adopting the active matrix drive mode in the prior art.

**[0006]** As shown in FIG. 18, the light emitting element type display adopting the active matrix drive mode in the prior art has a structure comprising: a display panel 110P in which a plurality of display pixels EMP are arranged in a matrix form (n rows  $\times$  m columns). Each display pixel EMP includes e.g., a later-described pixel drive circuit and a current controlled type light emitting element (e.g., an organic EL element) in the vicinity of each of intersec-

tions of a plurality of scanning lines SL and a plurality of data lines DL which are arranged to be substantially orthogonal to each other. A scanning driver 120P is connected to the scanning lines SL of the display panel 110P and sets the display pixels EMP in each row in a selected state by sequentially applying a scanning signal Vsel to each scanning line SL at a predetermined timing. A signal driver 200P is connected with the data lines DL of the display panel 110P, and fetches display data and supplies a gradation current Ipix corresponding to the display data to each data line DL at a predetermined timing.

**[0007]** In such a display, operating states of the scanning driver 120P and the signal driver 200P are controlled by, e.g., a scanning control signal, a data control signal and the like which are generated based on a timing signal supplied from the outside, and a gradation current corresponding to the display data is written in the display pixels in each row set in the selected state by application of the scanning signal. As a result, the respective display pixels emit lights with a predetermined luminance gradation, thereby displaying desired image information.

**[0008]** In such a light emitting element type display adopting the active matrix drive mode, various kinds of drive control mechanisms or control methods which control light emission of the above-described current controlled type light emitting elements have been proposed. For example, there has been known a display comprising a pixel drive circuit which is constituted of a plurality of switching means which control light emission of the light emitting elements as well as the light emitting elements in accordance with each display pixel constituting the display panel.

**[0009]** For example, as shown in FIG. 19, such a pixel drive circuit specifically comprises: a pixel drive circuit DP1; and an organic EL element OEL having an anode terminal connected to a drain terminal of a transistor Tr124 of the pixel drive circuit DP1 and a cathode terminal to which a ground potential is applied. The pixel drive circuit DP 1 includes in the vicinity of each intersection of a pair of scanning lines SL1 and SL2 arranged in parallel with each other and a data line DL: a first transistor Tr121 having a gate terminal connected to the scanning line SL1 and a source terminal and a drain terminal connected to the data line DL and a contact point N121; a second transistor Tr122 having a source terminal and a drain terminal connected to the contact point N121 and a contact point N122; a third transistor Tr123 having a gate terminal connected to the contact point N122, a drain terminal connected to the contact point N121, and a source terminal to which a high power supply voltage Vdd is applied; a fourth transistor Tr124 having a gate terminal connected to the contact point N122 and a source terminal to which the high power supply voltage Vdd is applied.

**[0010]** In this example, in FIG. 19, the first transistor Tr121 comprises an n-channel type field effect thin film transistor, and each of the second to fourth transistors Tr122 to Tr124 comprises a p-channel type field effect

thin film transistor. Furthermore, CP1 represents a parasitic capacitance formed between a gate and a source of the third and fourth transistors Tr123 and Tr124.

**[0011]** In the pixel drive circuit DP1 having such a configuration, the organic EL element OEL is subjected to a light emission control as follows by turning on/off the four transistors (switching means) comprising the transistors Tr121 to Tr124 at a predetermined timing.

**[0012]** That is, in the pixel drive circuit DP1, when the display pixel is set in the selected state by respectively applying a high-level scanning signal Vsel1 to the scanning line SL1 and a low-level scanning signal Vsel2 to the scanning line SL2 by the scanning drive 120P, the transistors Tr121, Tr122 and Tr123 are turned on, and the gradation current Ipix corresponding to display data which has been supplied to the data line DL by the signal driver 200P flows through the transistors Tr121 and Tr123. At this moment, since a part between the gate and the drain of the transistor Tr123 is electrically short-circuited by the transistors Tr122 and Tr123 operates in a saturated region. As a result, a current level of the gradation current Ipix is converted into a voltage level by the transistor Tr123, and a predetermined voltage is thereby generated between the gate and the source (a write operation). The transistor Tr124 is turned on in accordance with the voltage generated between the gate and the source of the transistor Tr123, and a predetermined drive current flows to the ground potential from the high power supply voltage Vdd through the transistor Tr124 and the organic EL element OEL, thereby emitting a light from the organic EL element (a light emitting operation).

**[0013]** Subsequently, when, e.g., the high-level scanning signal Vsel2 is applied to the scanning line SL2, the transistor Tr122 is turned off. As a result, the voltage generated between the gate and the source of the transistor Tr123 is held by the parasitic capacitance CP1. Then, when the low-level scanning signal Vsel1 is applied to the scanning line SL1, the transistor Tr121 is turned off. As a result, the data line DL and the pixel drive circuit DP1 are electrically shut off. Consequently, the fourth transistor Tr124 continuously maintains the ON state by a potential difference based on the voltage held in the parasitic capacitance CP1, a predetermined drive current flows to the ground potential from the high power supply voltage Vdd through the transistor Tr124 and the organic EL element OEL, and hence the light emitting operation of the organic EL element OEL continues.

**[0014]** Here, the drive current supplied to the organic EL element OEL through the transistor Tr124 is controlled to have a current value based on a luminance gradation of the display data, and this light emitting operation is controlled to continue for, e.g., one frame period until a gradation current corresponding to the next display data is written in each display pixel.

**[0015]** The drive control method in the pixel drive circuit having such a circuit configuration supplies a gradation current having a specified current value corresponding to the display data to each display pixel (the gate terminal

of the third transistor Tr123), and controls the drive current which is passed to the organic EL element based on a voltage held in accordance with the current value, thereby effecting the light emitting operation with a predetermined luminance gradation. Therefore, this method is called a current application mode (or a current specification mode).

**[0016]** Like FIG. 19, there has been also known a drive control method adopting a voltage application mode (or a voltage specification mode) which applies a gradation voltage having a specified voltage value corresponding to display data to each display pixel comprising a pixel drive circuit and an organic EL element, and controls a drive current which is passed to the organic EL element OEL in accordance with the voltage value of the gradation voltage, thereby effecting a light emitting operation with a predetermined luminance gradation. In a pixel drive circuit adopting such a voltage specification mode, irregularities or fluctuations (deterioration) are generated in element characteristics (a channel resistance of a transistor and others) of a switch element which has a selection function or a light emission drive function in dependence on an external environment (an ambient temperature and others), a utilization time and the like, a drive current is affected. Thus, the pixel drive circuit has a problem that desired light emission characteristics (display with a predetermined luminance gradation) cannot be stably realized for a long period in time. Alternatively, when each display pixel is finely formed in order to realize the high definition of the display panel, irregularities in operation characteristics (a current between the source and the drain of the transistor and others) of a switch element constituting the pixel drive circuit become large, and hence an appropriate gradation control cannot be performed. Accordingly, the pixel drive circuit has a drawback that generation of irregularities in light emission characteristics of each display pixel results in deterioration of a display image quality.

**[0017]** On the contrary, the pixel drive circuit adopting the current specification mode comprises a third transistor Tr123 (a current/voltage conversion transistor) which converts a current level of a gradation current corresponding to display data supplied to each display pixel into a voltage level and a fourth transistor Tr124 (a light emission drive transistor) which supplies a drive current having a predetermined current value to the organic EL element OEL. This pixel drive circuit can suppress an influence of irregularities in operation characteristics of the respective transistors Tr123 and Tr124 by setting a current value of a drive current supplied to the organic EL element OEL, and hence has an advantage that the problems of the pixel drive circuit adopting the voltage specification mode can be solved.

**[0018]** However, the pixel drive circuit adopting the current specification mode has the following problems.

**[0019]** In case of writing a gradation current based on display data having a lowest luminance or a relatively low luminance in each display pixel (at the time of low-

gradation display), a signal current having a small current value corresponding to a luminance gradation of display data must be supplied to each display pixel.

**[0020]** Here, since an operation of writing a gradation current in each display pixel corresponds to charging a capacitance component which is parasitic on the data line (a retention capacitance constituting a wiring capacitance and a display pixel) to a predetermined voltage, a wiring length of the data line becomes long due to, e.g., an increase in size of the display panel. Moreover, when the number of display pixels connected to this data line is increased, a time required to charge the data line becomes long as a current value of the gradation current becomes small, i.e., as display is effected with a lower gradation, and hence a time required for a write operation with respect to each display pixel is increased. The write operation with respect to each display pixel cannot be completed in a preset write time, and there occurs a so-called insufficient write state in which a stable state (a saturation state) is not reached. As a result, there is a display pixel which cannot emit a light with an appropriate luminance gradation corresponding to display data, resulting in deterioration in a display image quality.

**[0021]** Additionally, when the number of scanning lines arranged on the display panel is increased and a selection period (i.e., a write time) of each scanning line is set short in order to realize the high definition of the display panel, the sufficient write operation with respect to each display pixel cannot be performed as a current value of the gradation current is reduced, and the insufficient write state is generated, which leads to deterioration in a display image quality or a restriction in high definition of the display panel.

**[0022]** US 2003/132931 A1 discloses several modes of driving a display using different semiconductor circuit configurations connected to a source signal line for image signal output and gate signals for controlling the circuit operation. The image signal is input into a display row when the first gate signal of said row is selected. Here, the periods of the first gate signal of two adjacent rows do not overlap. The second gate signal coincides with the light emitting period of the light emitting element.

**[0023]** WO 2004/086347 A, EP-A-0 837 445, and EP-A-1 207 511 relate to driving of a display device supplying gradation signals to the selected rows. At the same time, plurality of rows are selected in accordance with the structure of the display device that connects more rows to a single scanning line. The selection periods of two adjacent rows selected at the same time are fully overlapping. The selection periods of two adjacent rows that are not selected at the same time are not overlapping at all.

**[0024]** US 2003/001870 A1 relates to a display driving wherein the scanning lines are selected sequentially without overlapping periods between rows. The image data is then supplied as gradation voltage to output lines, in accordance with trigger pulses output to the trigger lines.

**[0025]** EP 0 911 796 A relates to driving a liquid crystal

display. Pre-charging is applied to the pixels before writing the image signal therein. In particular, the signals V1 to V4 in Figure 3 are pre-charged in an initial period which causes the total pixel writing period to double. Thus the respective pulse pairs V1 and V2, V2 and V3, V3 and V4, etc. overlap in a half of their period.

#### Disclosure of Invention

10 **[0026]** In a display drive apparatus which drives display pixels of a display panel based on display data and a display apparatus comprising this display drive apparatus, the present invention has an advantage that occurrence of an insufficient write state in an operation of writing a gradation current in each display pixel can be suppressed and the high definition of the display panel can be excellently realized.

15 **[0027]** This is achieved by the features of the independent claims.

#### Brief Description of Drawings

##### **[0028]**

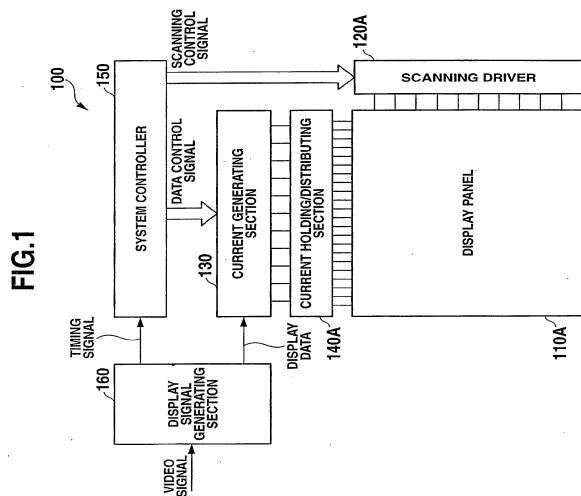

25 FIG. 1 is a schematic block diagram showing an entire configuration of a display apparatus according to a comparative example;

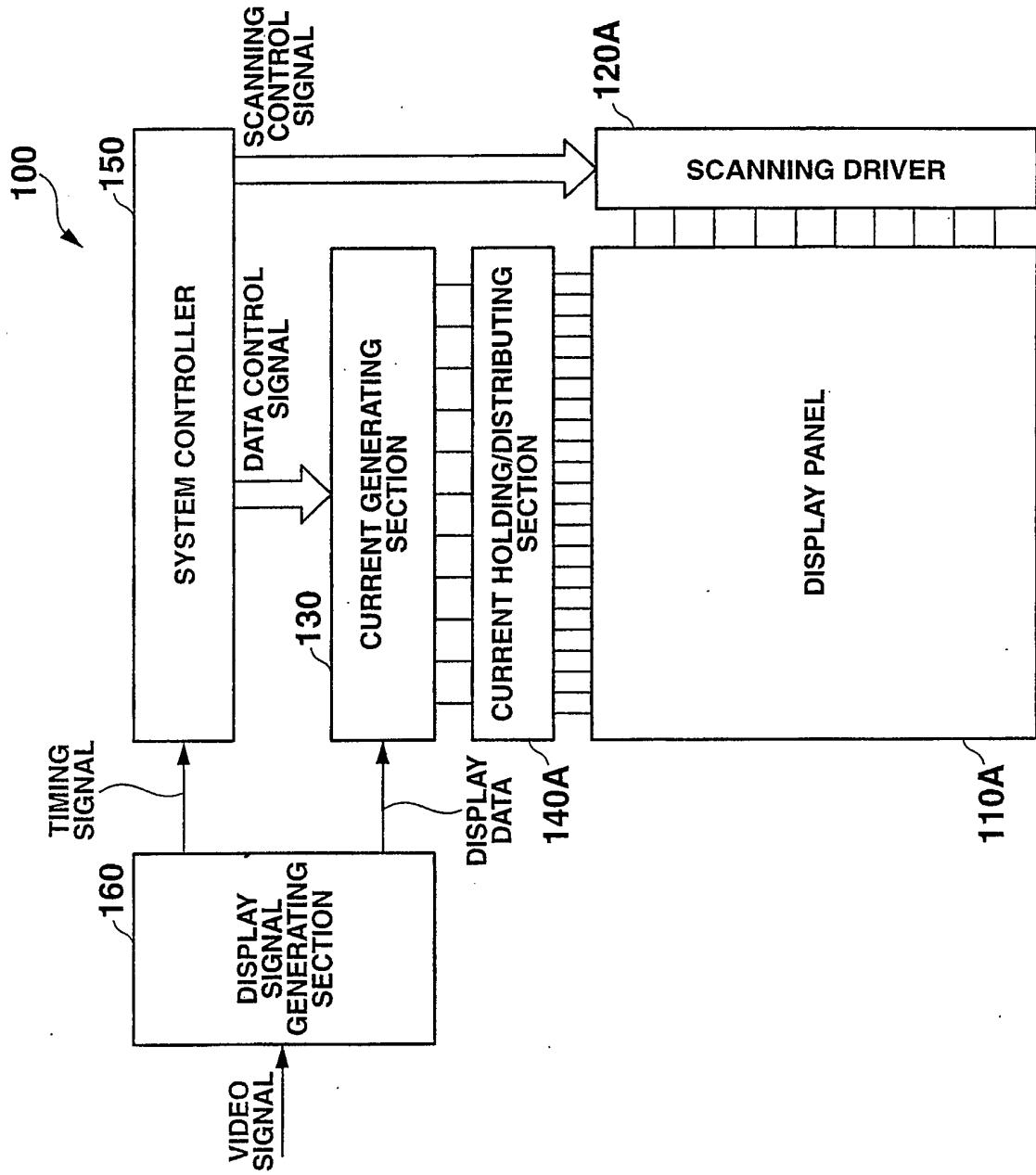

30 FIG. 2 is a structural view showing a part of the display apparatus according to the example depicted in FIG. 1;

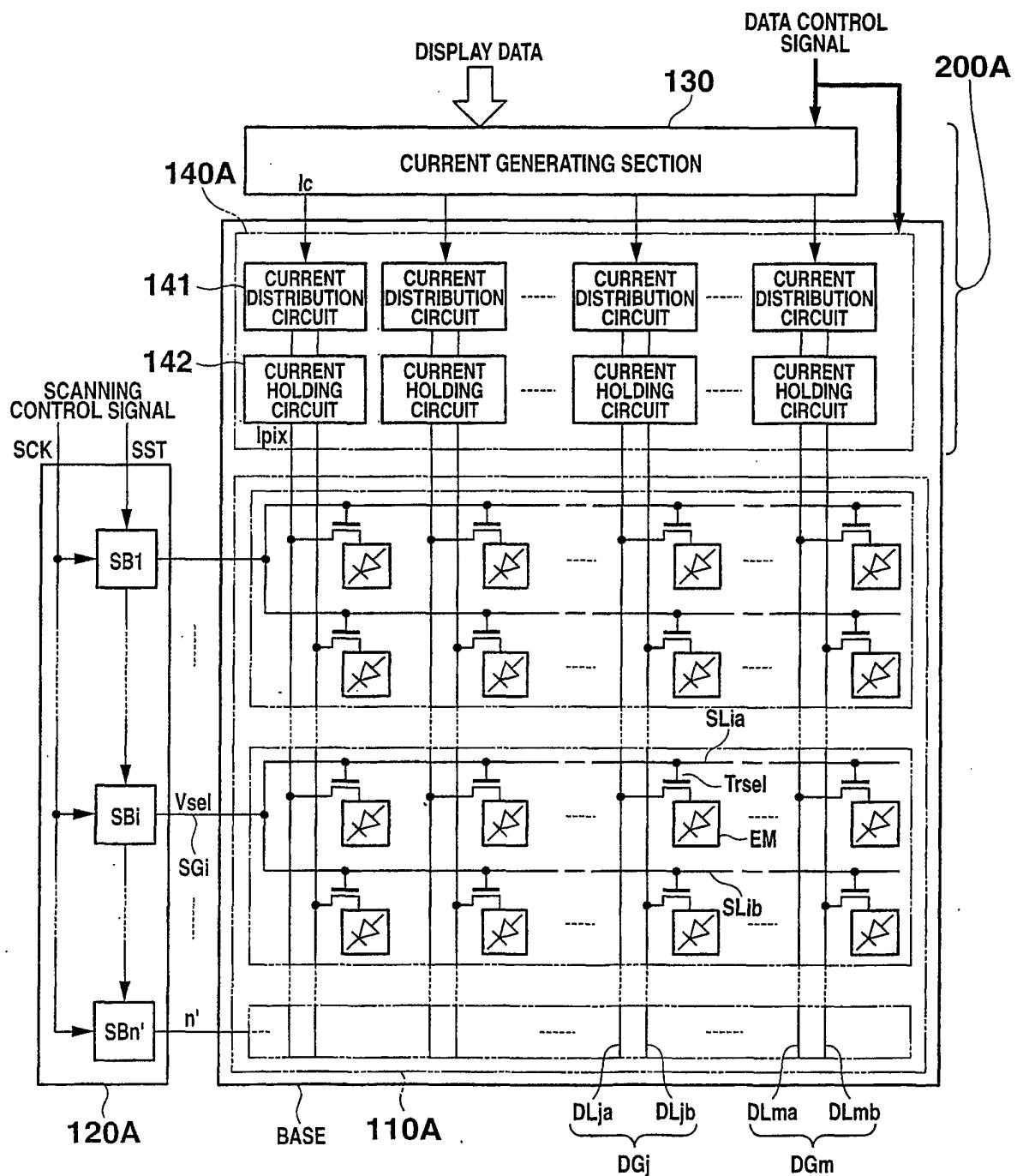

35 FIG. 3 is a block diagram showing a structural example of a current generating section which can be applied to the display apparatus according to the example depicted in FIG. 1;

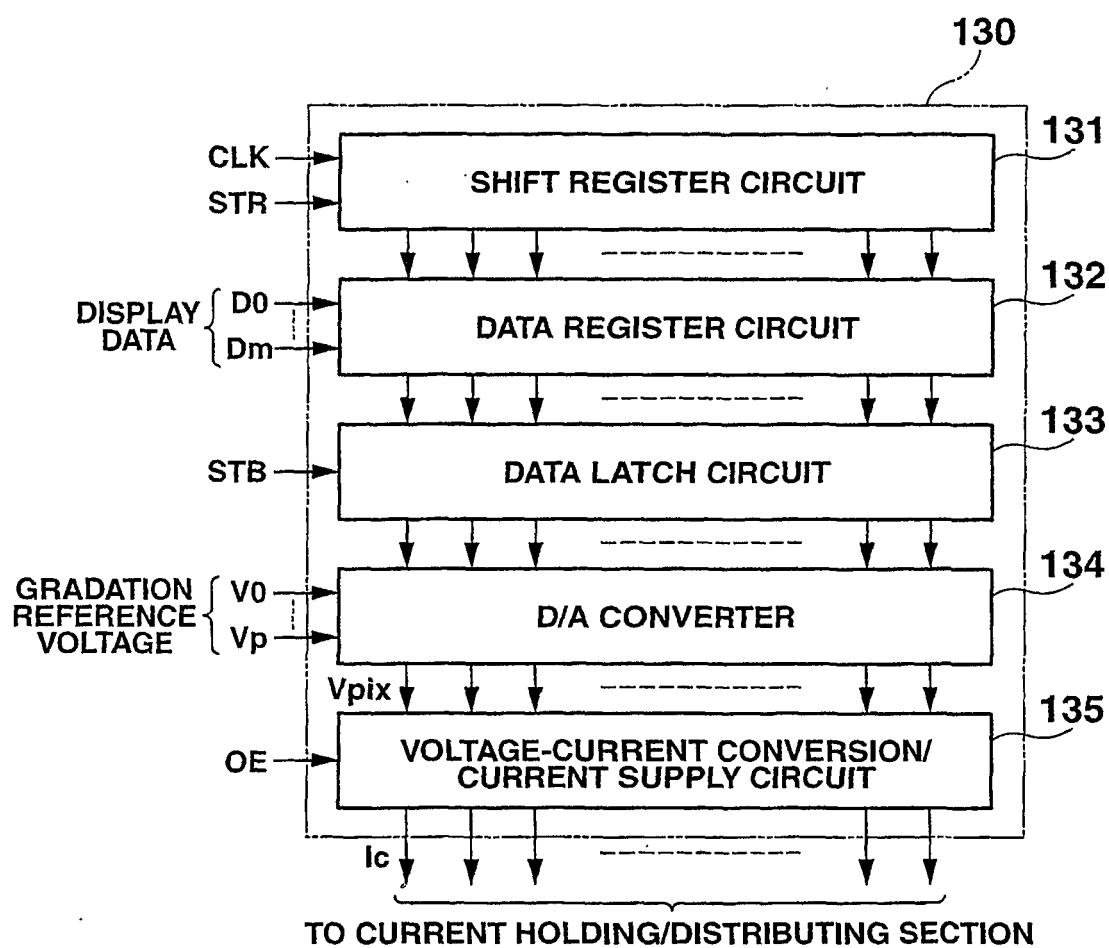

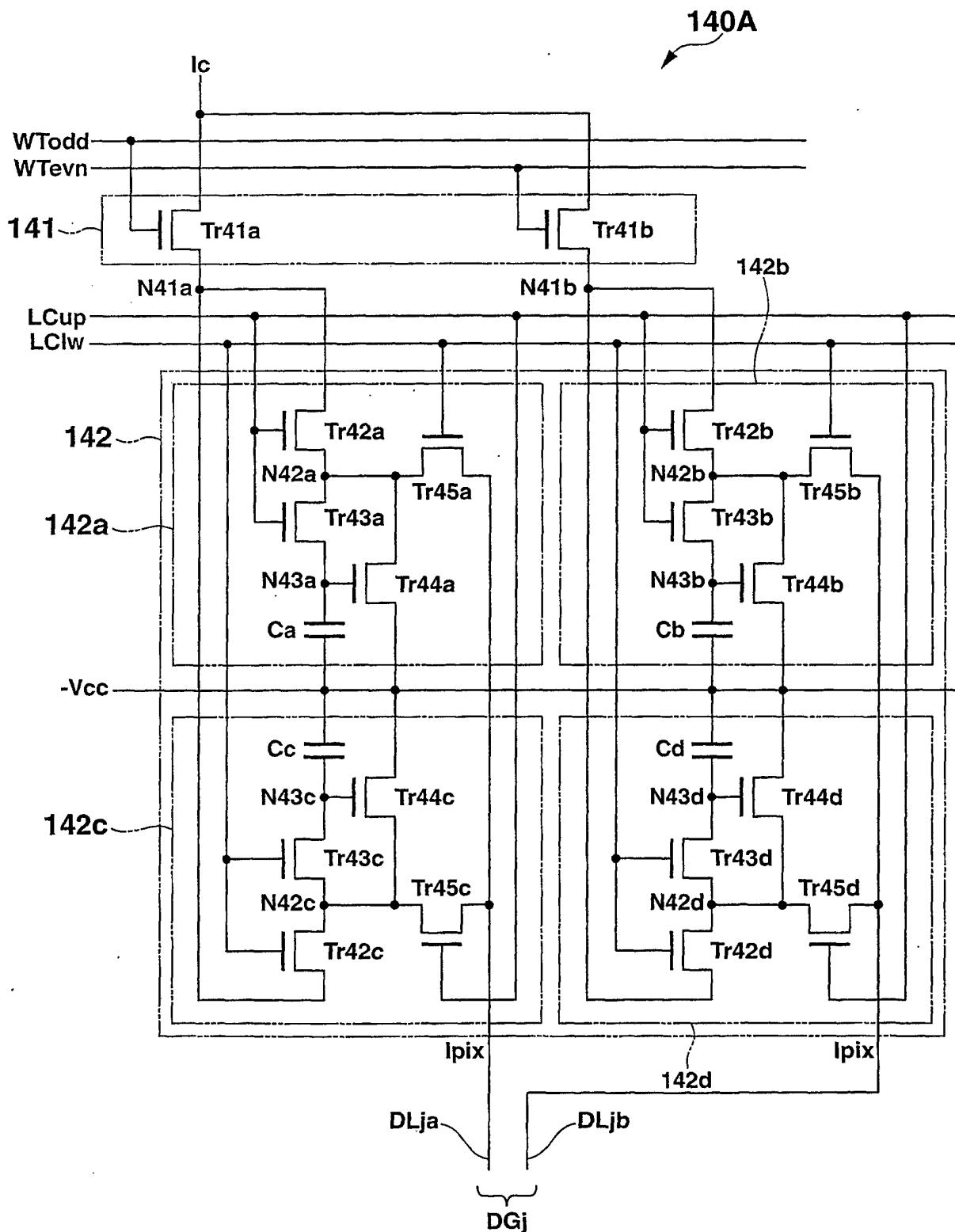

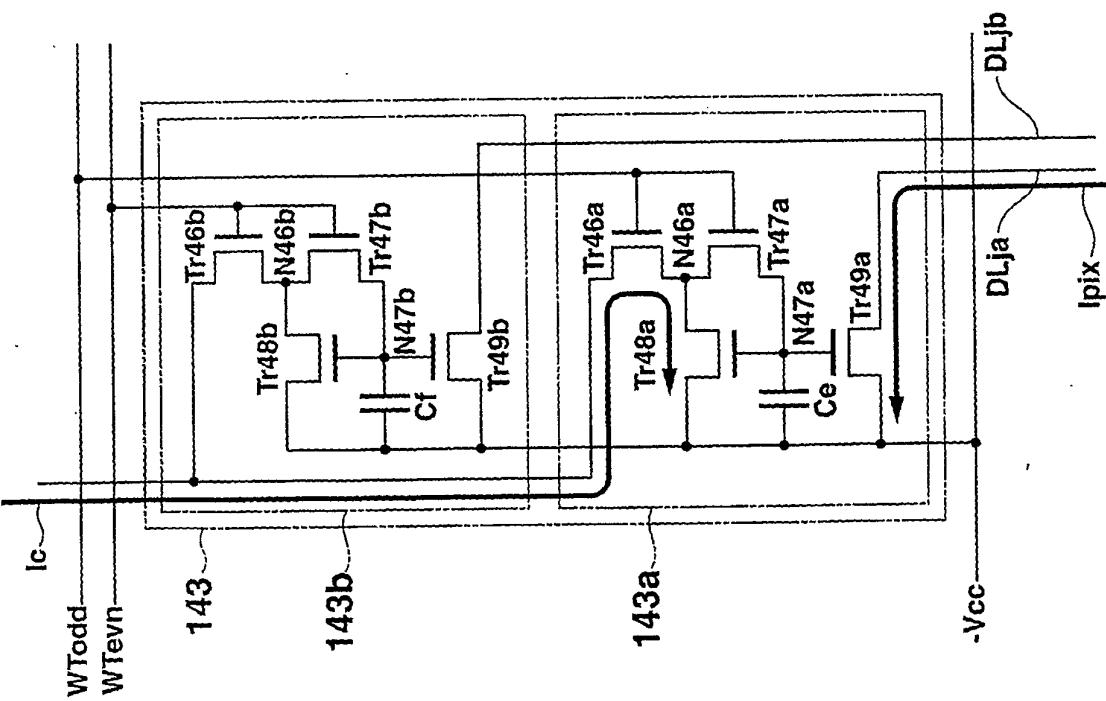

40 FIG. 4 is a circuit block diagram showing a structural example of a current holding/distributing section which can be applied to the display apparatus according to the example depicted in FIG. 1;

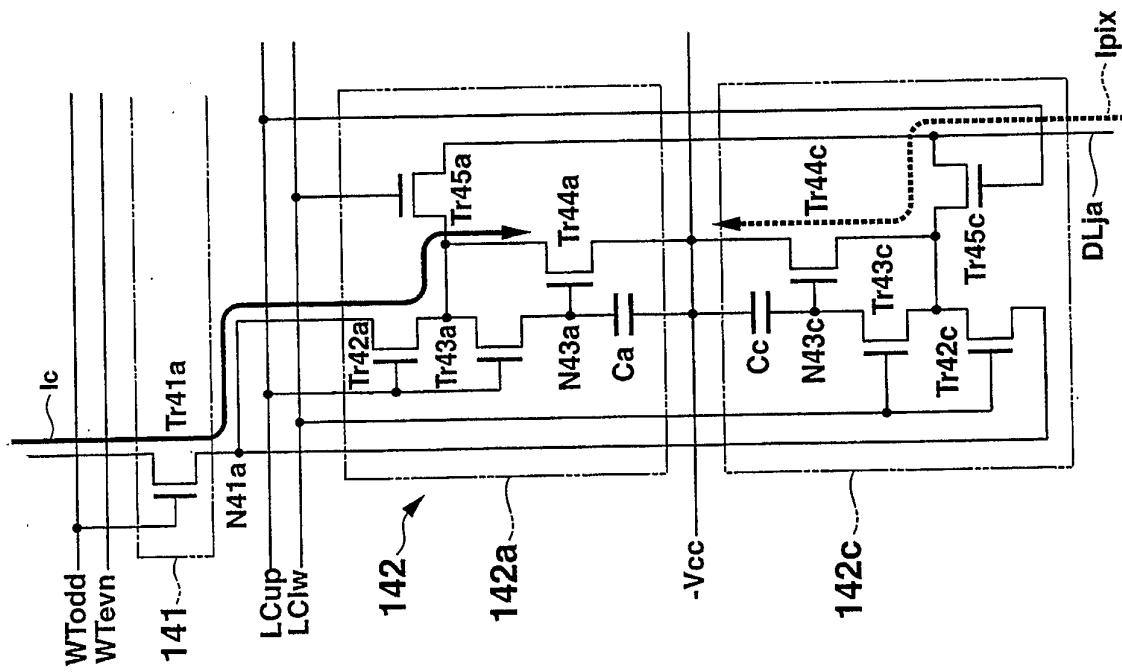

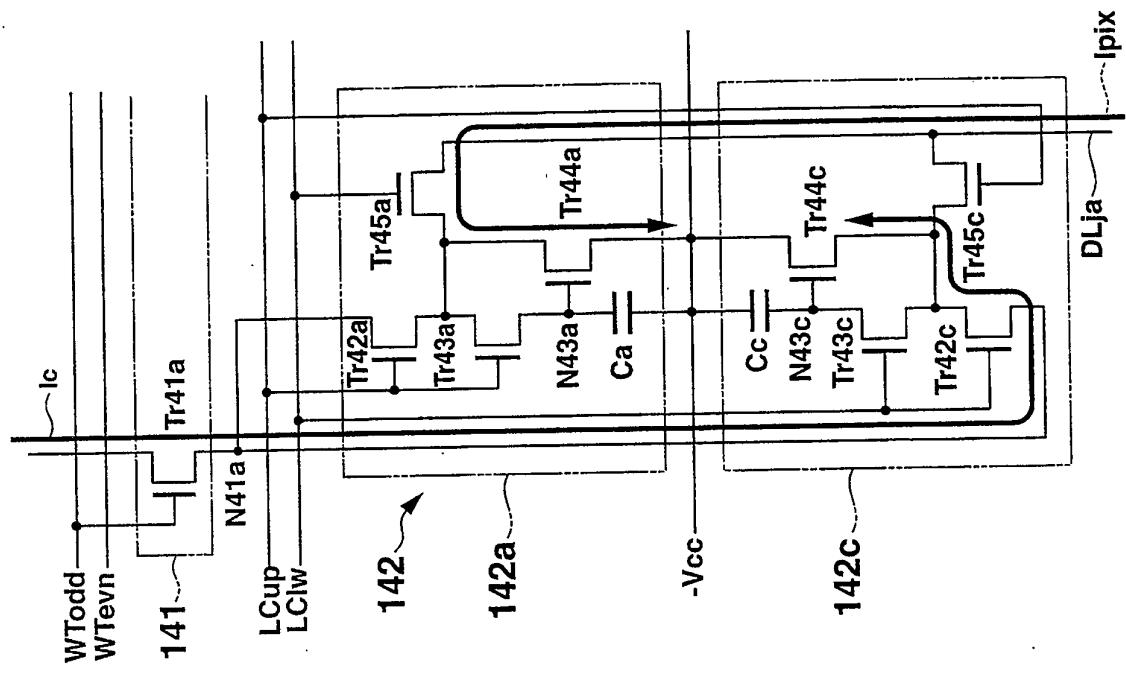

45 FIGS. 5A and 5B are conceptual views showing a schematic operation of the current holding/distributing section which can be applied to the example depicted in FIG. 1;

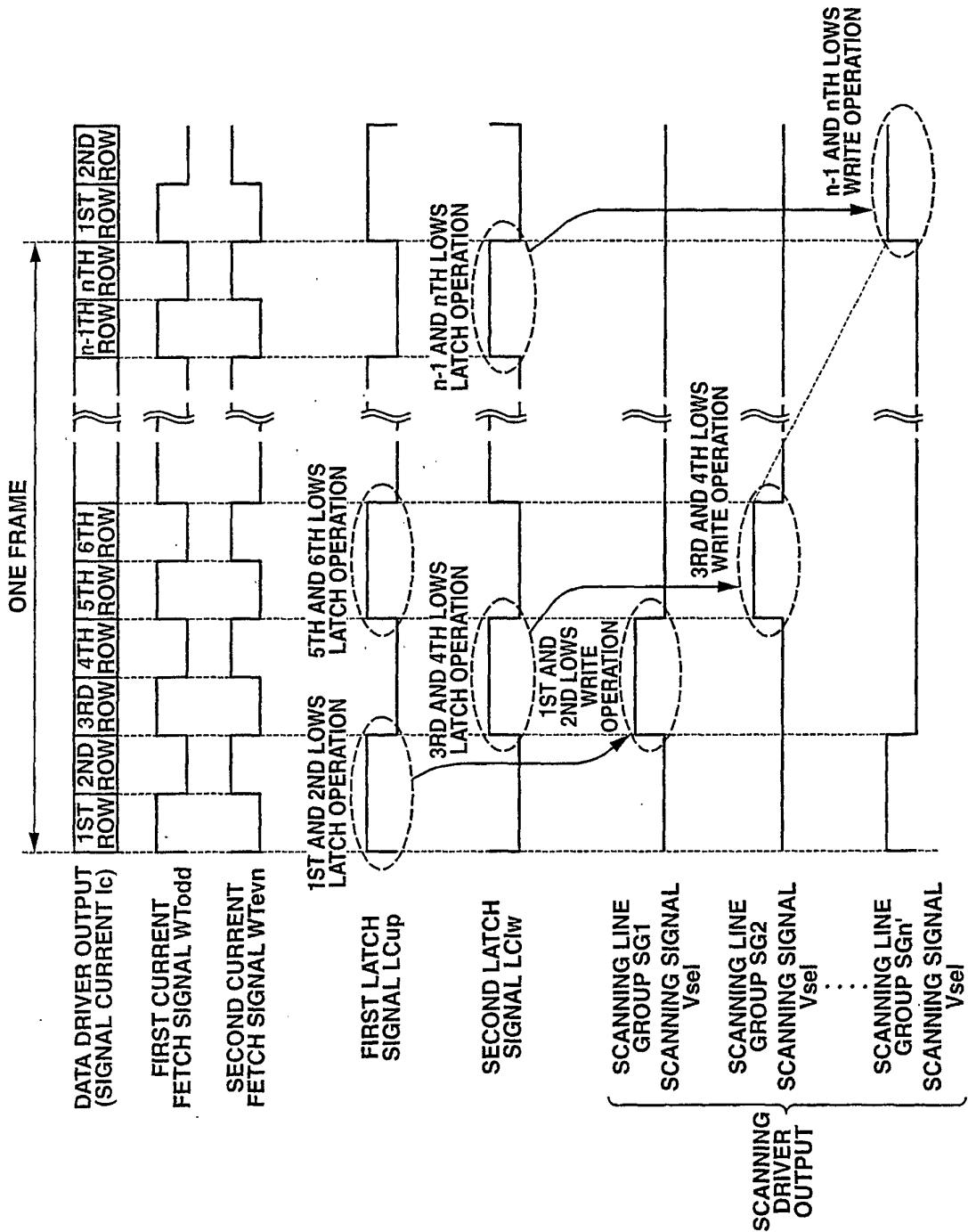

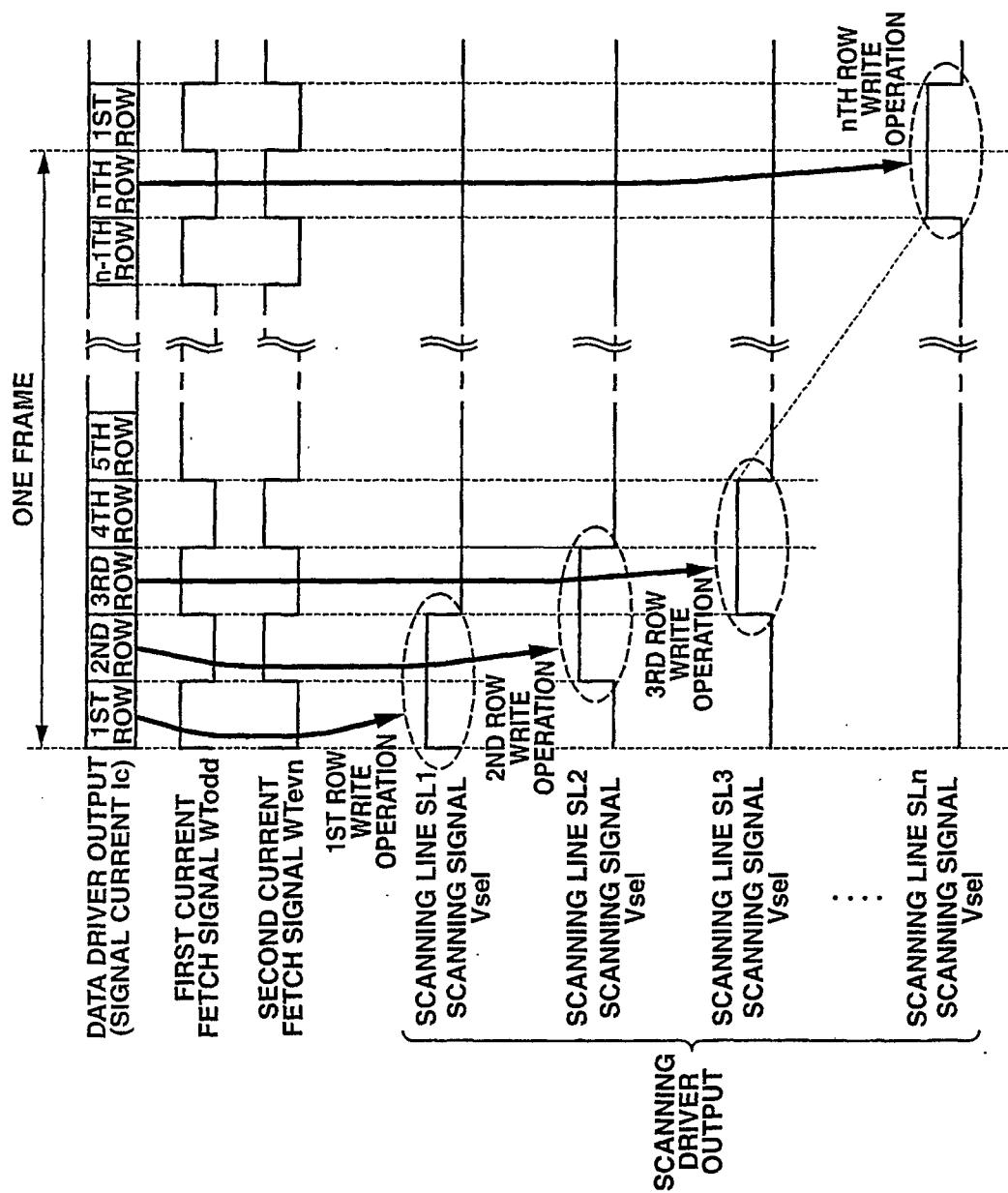

50 FIG. 6 is a timing chart illustrating a drive control operation (a drive control method) in the display apparatus according to the example depicted in FIG. 1; FIG. 7 is a schematic structural view showing a primary part of another structural example of the display apparatus according to the example depicted in FIG. 1;

55 FIG. 8 is a schematic structural view showing a primary part of still another example of the display apparatus according to the example depicted in FIG. 1;

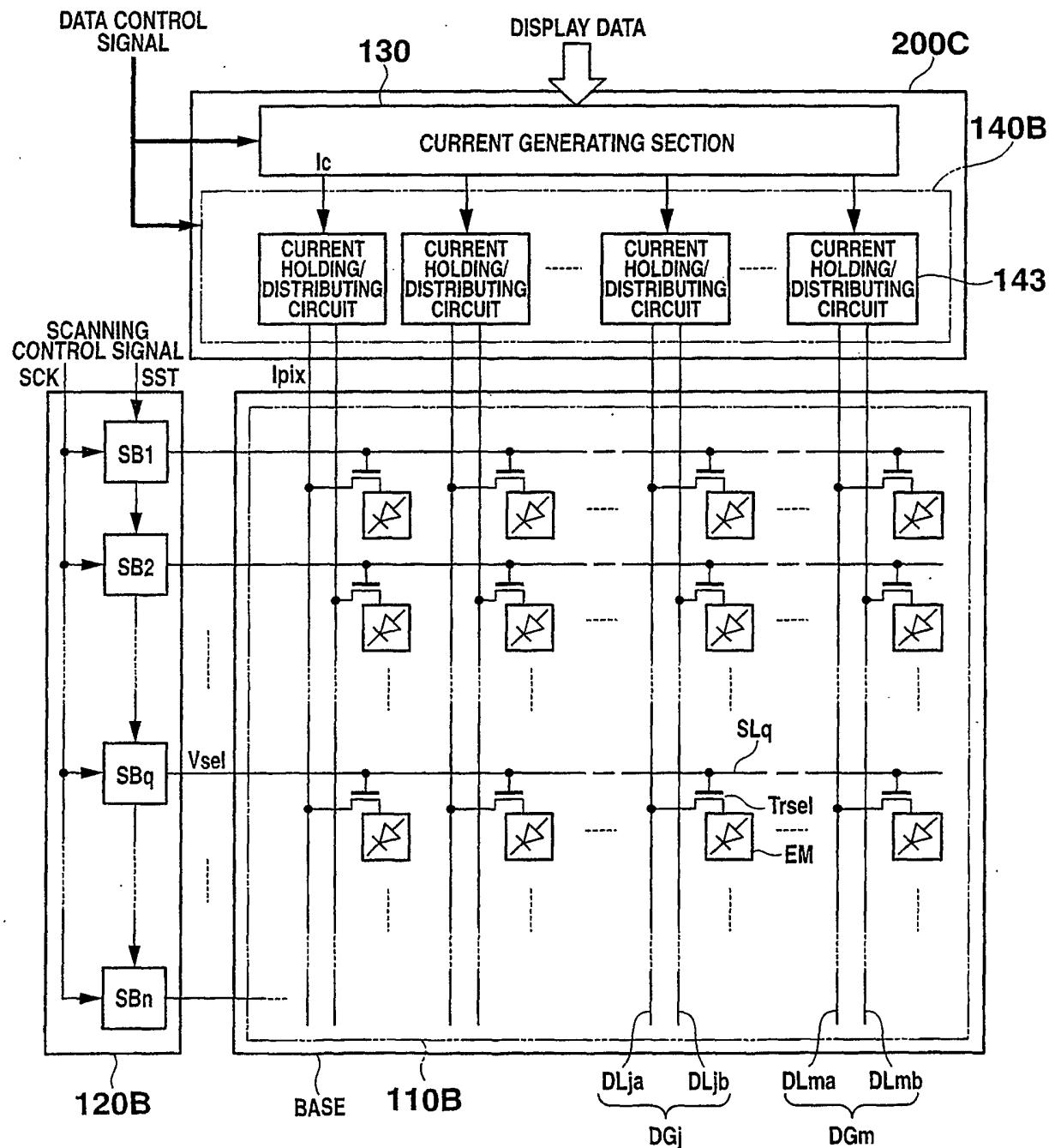

FIG. 9 is a structural view showing a part of an embodiment of a display apparatus according to the present invention;

FIG. 10 is a circuit block diagram showing a structural example of a current holding/distributing section which can be applied to the display apparatus ac-

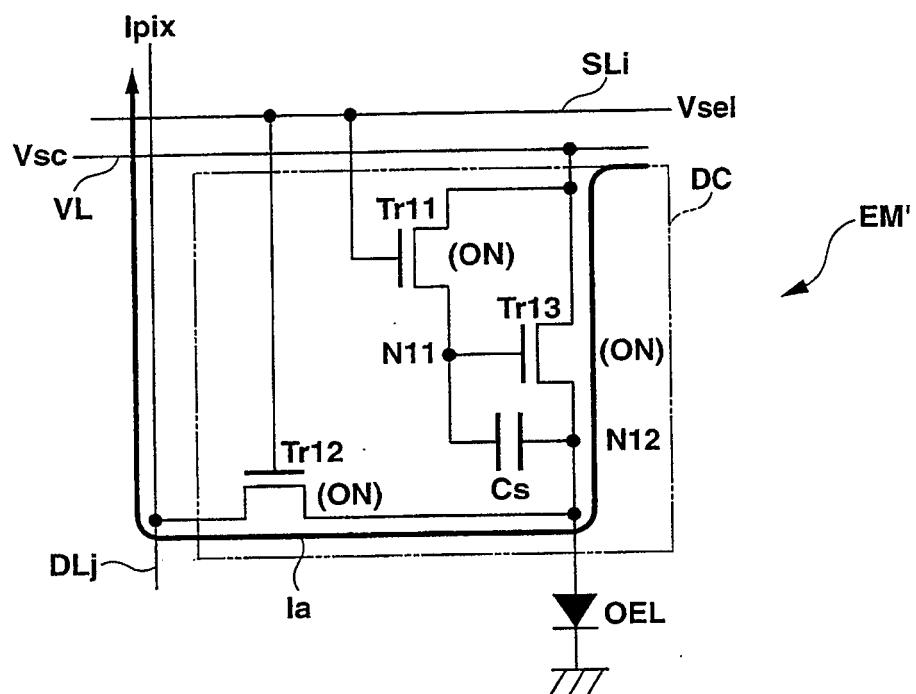

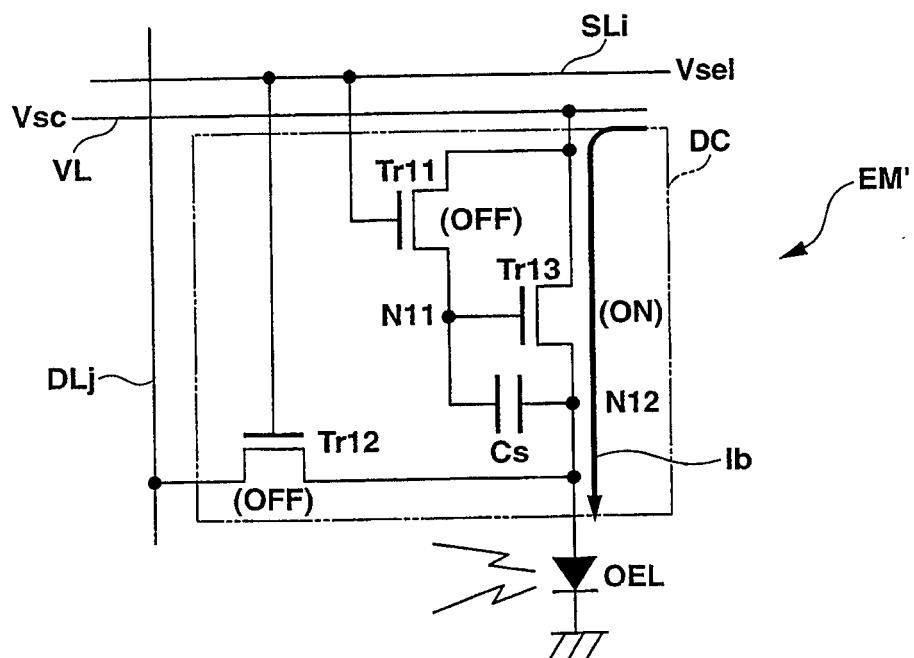

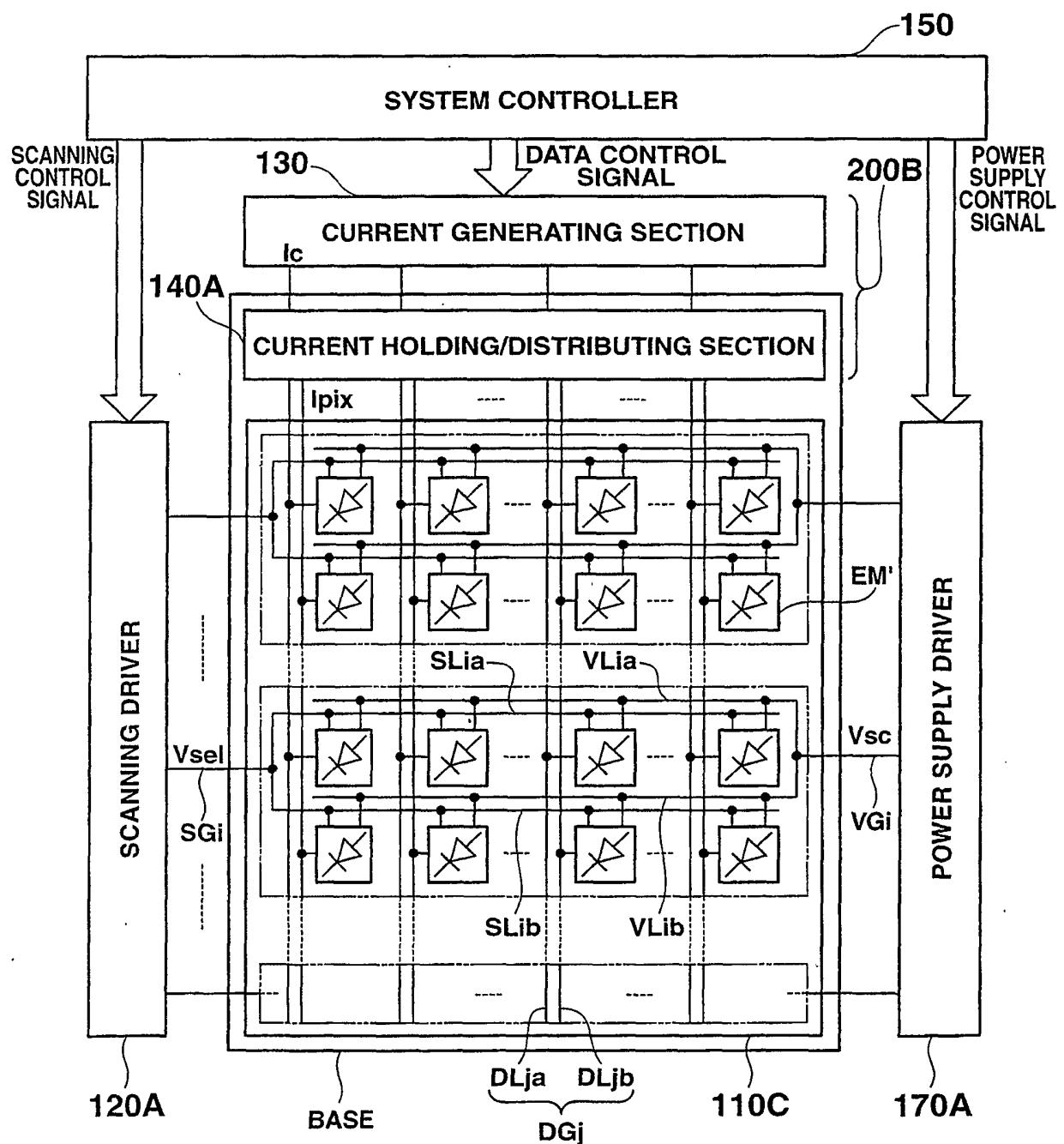

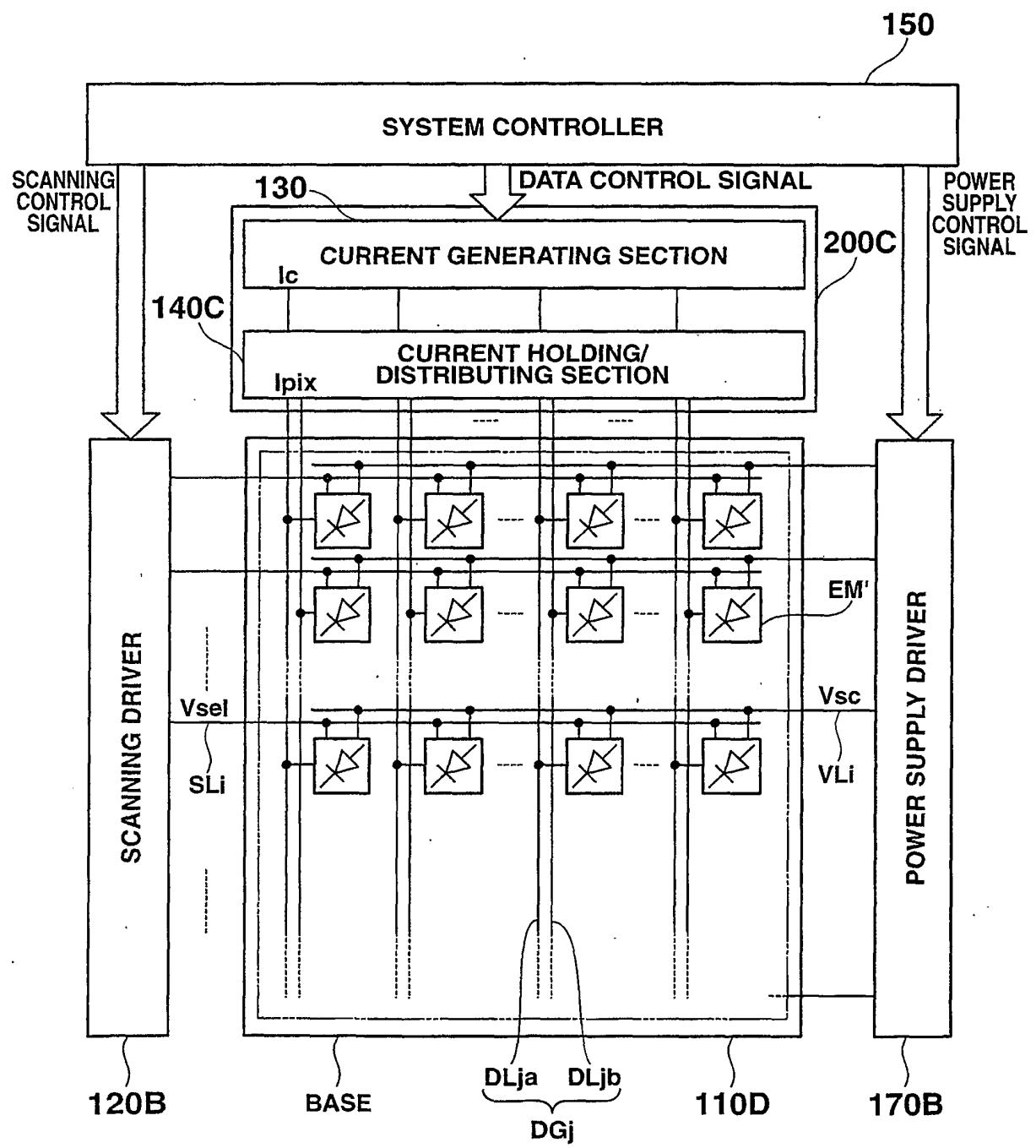

cording to the embodiment depicted in FIG. 9; FIGS. 11A and 11B are conceptual views showing a schematic operation of the current holding/distributing section which can be applied to the embodiment depicted in FIG. 9; FIG. 12 is a timing chart showing a drive control method of the display apparatus according to the embodiment depicted in FIG. 9; FIG. 13 is a schematic structural view showing a primary part of another structural example in the embodiment of the display apparatus according to the present invention; FIG. 14 is a circuit block diagram showing a concrete circuit example of a display pixel which can be applied to the display apparatus according to the present invention; FIGS. 15A and 15B are conceptual views showing a drive control operation of a pixel drive circuit according to the embodiment depicted in FIG. 9; FIG. 16 is a schematic block diagram showing a structural example of the display apparatus to which a display pixel according to the embodiment depicted in FIG. 14 is applied; FIG. 17 is a schematic block diagram showing still another structural example of the display apparatus to which the display pixel according to the embodiment depicted in FIG. 14 is applied; FIG. 18 is a schematic view showing a structural example of a primary part of a light emitting element type display adopting an active matrix drive mode in a prior art; and FIG. 19 is an equivalent circuit diagram showing a structural example of a display pixel applied to the light emitting element type display adopting the active matrix drive mode in the prior art.

#### Best Mode for Carrying Out the Invention

**[0029]** A display apparatus and a drive control method thereof according to the present invention will now be described hereinafter based on illustrated embodiments.

#### Comparative Example of Display Apparatus>

**[0030]** A schematic configuration of a display apparatus to which a display drive apparatus can be applied will be first described.

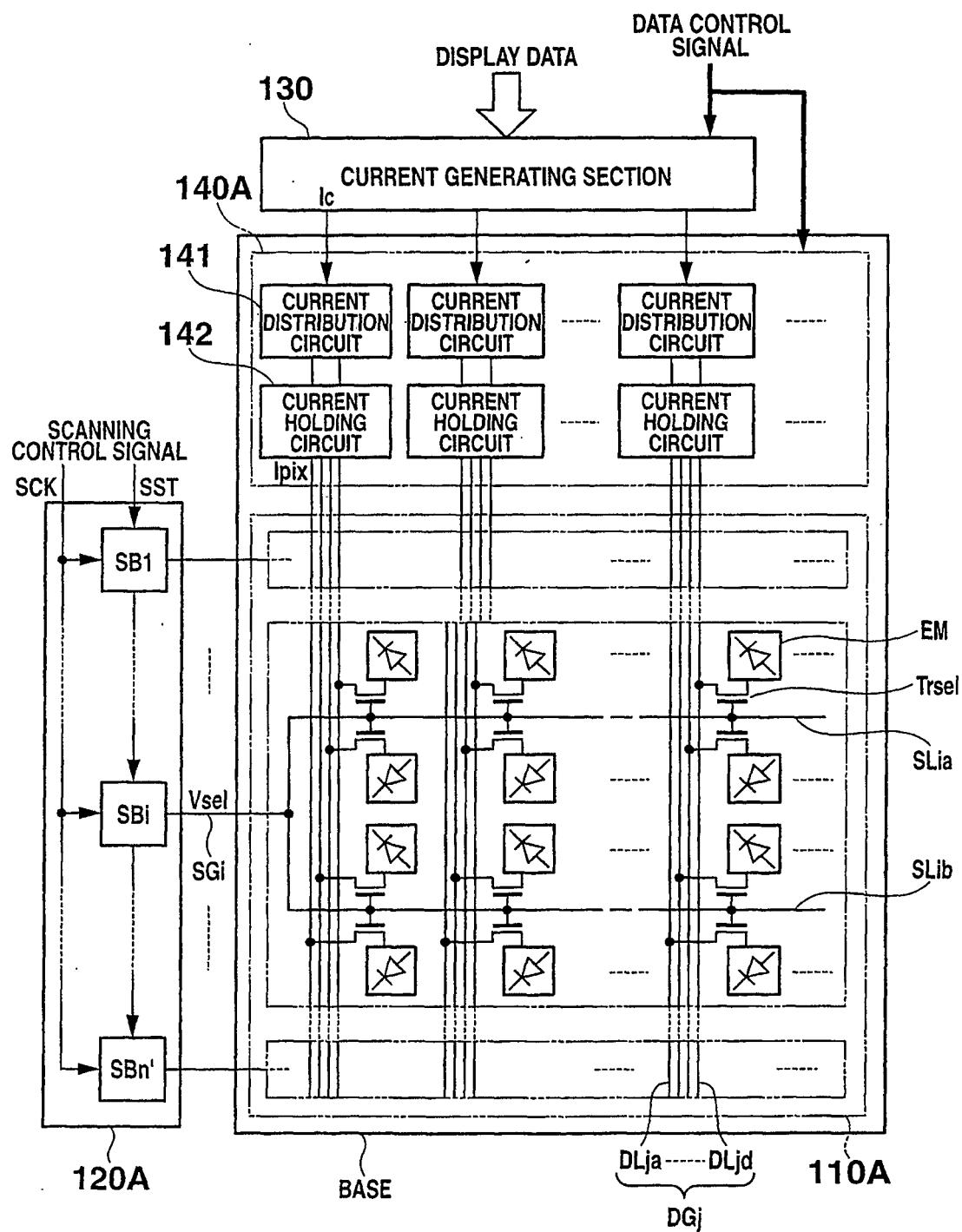

**[0031]** FIG. 1 is a schematic block diagram showing an entire configuration of a display apparatus according to a comparative example.

**[0032]** FIG. 2 is a structural view showing a primary part of the display apparatus according to this example.

**[0033]** As shown in FIG. 1, a display apparatus 100 roughly has a display panel 110A, a scanning driver (a selection circuit) 120A, a current generating section (a gradation signal generation circuit) 130, a current holding/distributing section (a current write circuit) 140A, a system controller 150 and a display signal generating

section 160.

**[0034]** As shown in FIG. 2, the display panel 110A substantially has a plurality of display pixels EM which are two-dimensionally arranged (n rows  $\times$  m columns) and connected to selection transistors Trsel. A plurality of scanning line groups SGi are arranged in accordance with the display pixels EM in a plurality of rows (two rows in this example) and in which a plurality of (two in this example) scanning lines SLia and SLib (i is a positive integer falling within a range of  $1 \leq i \leq n$ , e.g., a divisor of the total number n of rows provided in the display panel 110A; n' and n are positive integers) are determined as one set. A plurality of data line groups DGj are arranged in accordance with the display pixels EM in each column corresponding to each scanning line groups SGi and in which a plurality of (two in this example) data lines DLja and DLjb (j is a positive integer falling within a range of  $1 \leq j \leq m$ ; m is a positive integer and the total number of pixel columns set in the display panel 110) are determined as one set. Each display pixel EM is provided in the vicinity of each intersection of the scanning lines SLia and SLib constituting each scanning line group SGi and the data lines DLja and DLjb constituting each data line group DGj.

**[0035]** The scanning driver (the selection circuit) 120A is generally connected with the scanning line groups SGi of the display panel 110A, and sequentially applies a scanning signal Vsel to each scanning line group SGi at a predetermined timing to simultaneously set the display pixels EM corresponding to a plurality of rows (two rows in this example) connected to the scanning line group SGi.

**[0036]** The current generating section (the gradation signal generation circuit) 130 generally fetches display data corresponding to the display pixels corresponding to a plurality of rows (two rows in this example) of the scanning line group SGi supplied from the later-described display signal generating section 160, and sequentially supplies a signal current (a gradation signal) Ic for the plurality of corresponding rows to the current holding/distributing section 140A in time series.

**[0037]** The current holding/distributing section (the current write circuit) 140A is generally connected with each data line group DGj of the display panel 110A, distributes the signal current Ic corresponding to a plurality of rows (two rows in this example) sequentially supplied from the current generating section 130 in time series at a predetermined timing and holds this current in accordance with each row, and simultaneously supplies a gradation current Ipix based on the held signal current Ic to the display pixels EM in a plurality of rows (two rows in this embodiment). In this example, the current generating section 130 and the current holding/distributing section 140A constitute a signal driver 200A.

**[0038]** The system controller 150 generates and outputs a scanning control signal and a data control signal which control operating states of at least the scanning driver 120A, the current generating section 130 and the

current holding/distributing section 140A based on, e.g., a timing signal supplied from the display signal generating section 160.

**[0039]** The display signal generating section 160 generates display data (e.g., digital data) based on, e.g., a video signal supplied from the outside of the display apparatus 100 and supplies the display data to the current generating section 130, further generates or extracts a timing signal (a system clock or the like) which displays as an image the display data in the display panel 110A and supplies this timing signal to the system controller 150.

**[0040]** In the configuration shown in FIG. 2, as a structural example, the current holding/distributing section 140A is integrally formed with a pixel array on an insulating substrate BASE on which the plurality of display pixels EM (i.e., the pixel array) constituting the display panel 110A are formed. For example, the signal driver 200A may also have a conformation of a driver chip and be mounted (packaged) on the substrate BASE.

**[0041]** A concrete configuration of each structure will now be described.

#### (Display Panel)

**[0042]** For example, as shown in FIG. 2, the display panel 110A which can be applied to the display apparatus according to this example has a configuration in which each scanning line group SG<sub>i</sub> corresponding to two rows in which two diverging scanning lines SLia and SLib are determined as one set and each data line group DG<sub>j</sub> corresponding to one pixel column in which two data lines DLja and DLjb are determined as one set are arranged to be orthogonal to each other. Each display pixel EM is connected to each intersection of each scanning line SLia and each data line DLja and an intersection of each scanning line SLib and each data line DLjb.

**[0043]** In this example, in the configuration shown in FIG. 2, the display pixels EM in odd-numbered rows are connected to the scanning line SLia in each scanning line group SG<sub>i</sub>, and the display pixels EM in even-numbered rows are connected to the scanning line SLib.

**[0044]** As shown in FIG. 2, as to the number of rows corresponding to the scanning lines constituting each scanning line group SG<sub>i</sub>, this example is not restricted to the configuration in which each scanning line group SG<sub>i</sub> corresponds to the display pixels EM for two rows. For example, it is possible to adopt a configuration in which each scanning line group SG<sub>i</sub> corresponds to the display pixels EM for  $k$  rows ( $k$  is a divisor of the total number  $n$  of rows provided in the display panel 110) and which has  $n/k$  sets (that is,  $n'$  sets mentioned above) of scanning line groups alternately, there may be used a configuration in which one (single) scanning line group is provided in accordance with rows ( $n$  rows) constituting the display panel 110A and all the display pixels EM for one screen are connected with the scanning line group in common, for example. In this case, all the display pixels EM for

one screen are altogether set in a selected state by a single scanning signal output from the scanning driver 120A.

**[0045]** Each display pixel EM has a gate terminal connected with each scanning line SLia or SLib and a source terminal connected with a drain terminal of each selection transistor Trsel connected with each data line DLja or DLjb. Each display pixel EM includes a current controlled type light emitting element which emits a light with a pre-determined luminance gradation based on a gradation current I<sub>pix</sub> supplied from the current holding/distributing section 140 through each data line DLja or DLjb and the selection transistor Trsel.

**[0046]** In the display panel 110A having such a configuration, by applying a scanning signal V<sub>sel</sub> to a specific scanning line group SG<sub>i</sub> from the later-described scanning driver 120A, the selection transistors Trsel connected to the plurality of (two) scanning lines SLia and SLib constituting the scanning line group SG<sub>i</sub> are simultaneously turned on, and the display pixels EM corresponding to the plurality of row (two rows) are altogether set in the selected state. In the state where the scanning signal V<sub>sel</sub> is applied to the specific scanning line group SG<sub>i</sub> (the selected state), by supplying the gradation current I<sub>pix</sub> corresponding to display data to each data line group DG<sub>j</sub> from the later-described current generating section 130 and the current holding/distributing section 140A all at once, the display data is written in the display elements EM corresponding to the plurality of rows (two rows) which are set in the selected state at the same time through the selection transistors Trsel which has been turned on. A concrete circuit example or a circuit operation of the display pixel EM including the selection transistor will be described later in detail.

#### (Scanning Driver)

**[0047]** The scanning driver 120A simultaneously sets the display pixels EM corresponding to the plurality of rows (two rows in this embodiment) connected to the scanning lines SLia and SLib constituting each scanning line group SG<sub>i</sub> in the selected state by executing the operation of sequentially applying the scanning signal V<sub>sel</sub> which is in a selection level (e.g., a high level) to each scanning line group SG<sub>i</sub> based on a scanning control signal supplied from the system controller 150. That is, for example, as shown in FIG. 2, the scanning driver 120A comprises shift blocks SB<sub>1</sub>, SB<sub>2</sub>, ... SB<sub>i</sub>, ... SB<sub>n'</sub> each including a shift register and a buffer on a plurality of stages (in FIG. 2,  $n' = n/2$ ;  $n$  is the total number of rows provided in the display panel 110A) in accordance with the respective scanning line groups SG<sub>i</sub>. A shift signal which is output while sequentially shifting from the upper part to the lower part of the display panel 110A by the shift registers is sequentially applied to each scanning line group SG<sub>i</sub> as the scanning signal V<sub>sel</sub> having a pre-determined selection level (a high level) through the buffers based on the scanning control signal (a scanning

start signal SST, a scanning clock signal SCK and the like) supplied from the later-described system controller 150.

**[0048]** As described above, for example, when there is adopted the configuration in which all the display pixels EM constituting the display panel 110A are connected to the single line group SGI, such shift blocks as shown in FIG. 2 are not necessary, and all the display pixels EM for one screen are altogether set in the selected state by applying the single scanning signal Vsel to the scanning line group SGI based on the scanning control signal at a predetermined timing.

(Current Generating Section)

**[0049]** The current generating section 130 sequentially fetches display data corresponding to the display pixels for the plurality of rows (two rows in this embodiment) in the data line group DGj corresponding to the scanning line group SGI supplied from the later-described display signal generating section 160 based on a data control signal fed from the system controller 150 at a predetermined timing to generate a signal current (a gradation signal) Ic having a current value corresponding to a gradation value of the display data, and sequentially supplies the signal current Ic for the plurality of rows to the current holding/distributing section 140A in accordance with each column in time series. The current generating section 130 sequentially and repeatedly executes this operation for one screen. The concrete configuration and operation of the current generating section 130 will be described later in detail.

(Current Holding/distributing Section)

**[0050]** The current holding/distributing section 140A sequentially fetches the signal current Ic for the plurality of rows corresponding to each scanning line group SGI supplied from the current generating section 130 in time series based on the data control signal fed from the system controller 150 at a predetermined timing, individually holds the signal current Ic in accordance with the plurality of display pixels EM in each column of each data line group DGj, and simultaneously supplies a gradation current Ipix based on the held signal current Ic to the display pixels EM for the plurality of rows (two rows in this embodiment) of each data line group DGj in accordance with a timing of setting each scanning line group SGI in the selected state by using the above-described scanning driver 120.

**[0051]** Specifically, for example, as shown in FIG. 2, the current holding/distributing section 140A comprises at least a plurality of current distribution circuits 141 each of which is provided in accordance with each data line group DGj arranged in the display panel 110A, and distributes the signal current Ic supplied from the current generating section 130 in time series in accordance with each of the plurality of (two in this embodiment) data lines

DLja and DLjb of each data line group DGi, and a plurality of current holding circuits 142 each of which is provided to be connected with each data line group DGj arranged in the display panel 110A and holds the signal current Ic corresponding to the plurality of (two in this example) data lines distributed by the current distribution circuit 141 in parallel.

**[0052]** This current holding/distributing section 140A sequentially fetches the signal current Ic for the plurality of rows (two rows in this example) connected with the scanning lines SLia and SLib constituting each scanning line group SGI at a timing based on the data control signal, and distributes and holds the signal current Ic in accordance with each data line in each data line group SGI. The section 140A also generates a gradation current Ipix based on the held signal current Ic, and simultaneously supplies the gradation current Ipix to the display pixels EM for the plurality of rows (two rows in this embodiment) through each data line group DGi at a timing of setting the scanning line group SGI in the selected state. The concrete configuration and operation of the current holding/distributing section 140A will be described later in detail.

25 (System Controller)

**[0053]** The system controller 150 allows the scanning driver 120A, the current generating section 130 and the current holding/distributing section 140A to operate at a predetermined timing in order to generate/output the scanning signal Vsel, the signal current Ic and the gradation current Ipix by outputting the scanning control signal and the data control signal which control the operating states to the scanning driver 120A and the current generating section 130 and to the current holding/distributing section 140 through this current generating section 130, writes display data generated by the display signal generating section 160 in each display pixel EM to emit a light therefrom, and controls the display panel 110A to display predetermined image information based on a video signal.

(Display Signal Generating Section)

**[0054]** The display signal generating section 160 extracts a luminance gradation signal component from, e.g., a video signal supplied from the outside of the display apparatus 100, and supplies the luminance gradation signal component to the current generating section 130 as display data in accordance with each row of the display panel 110A. In this example, when the video signal includes a timing signal component which defines a display timing of image information like a television broadcast signal (a composite video signal), the display signal generating section 160 may have the function of extracting the luminance gradation signal component as well as a function of extracting a timing signal component and supplying it to the system controller 150. In this case,

the system controller 150 generates a scanning control signal and a data control signal which are supplied to the scanning driver 120A, the current generating section 130 or the current holding/distributing section 140 based on a timing signal supplied from the display signal generating section 160.

<Concrete Example of Current Generating Section>

**[0055]** A concrete structural example of the current generating section which can be applied to the display apparatus according to this example will now be described.

**[0056]** FIG. 3 is a block diagram showing a structural example of the current generating section which can be applied to the display apparatus according to this example.

**[0057]** For example, as shown in FIG. 3, the current generating section 130 has includes a shift register circuit 131, a data register circuit 132, a data latch circuit 133, a D/A converter 134, and a voltage-current converting/current supply circuit 135. The shift register circuit 131 outputs a shift signal while sequentially shifting a sampling start signal STR based on a shift clock signal CLK supplied as a data control signal from the system controller 150. The data register circuit 132 sequentially fetches display data D0 to Dm (digital data) for one row supplied from the display signal generating section 160 based on an input timing of the shift signal. The data latch circuit 133 holds the display data D0 to Dm for one row fetched by the data register circuit 132 based on a data latch signal STB. The D/A converter 134 converts the held display data D0 to Dm into a predetermined analog signal voltage (a gradation voltage Vpix) based on gradation reference voltages V0 to Vp supplied from non-illustrated power supplying means. The voltage-current conversion/current supply circuit 135 which generates a signal current (a gradation signal) Ic corresponding to the display data converted into the analog signal voltage, and sequentially supplies to the current holding/distributing section 140A in time series a signal current Ic corresponding to the display pixels EM in each column for the plurality of rows connected to each scanning line group SGi based on an output enable signal OE supplied from the system controller 150 in accordance with each data line group DGj arranged in the display panel 110.

<Concrete Example of Current Holding/distributing Section>

**[0058]** A concrete example of the current holding/ distributing section which can be applied to the display apparatus according to this example will now be described.

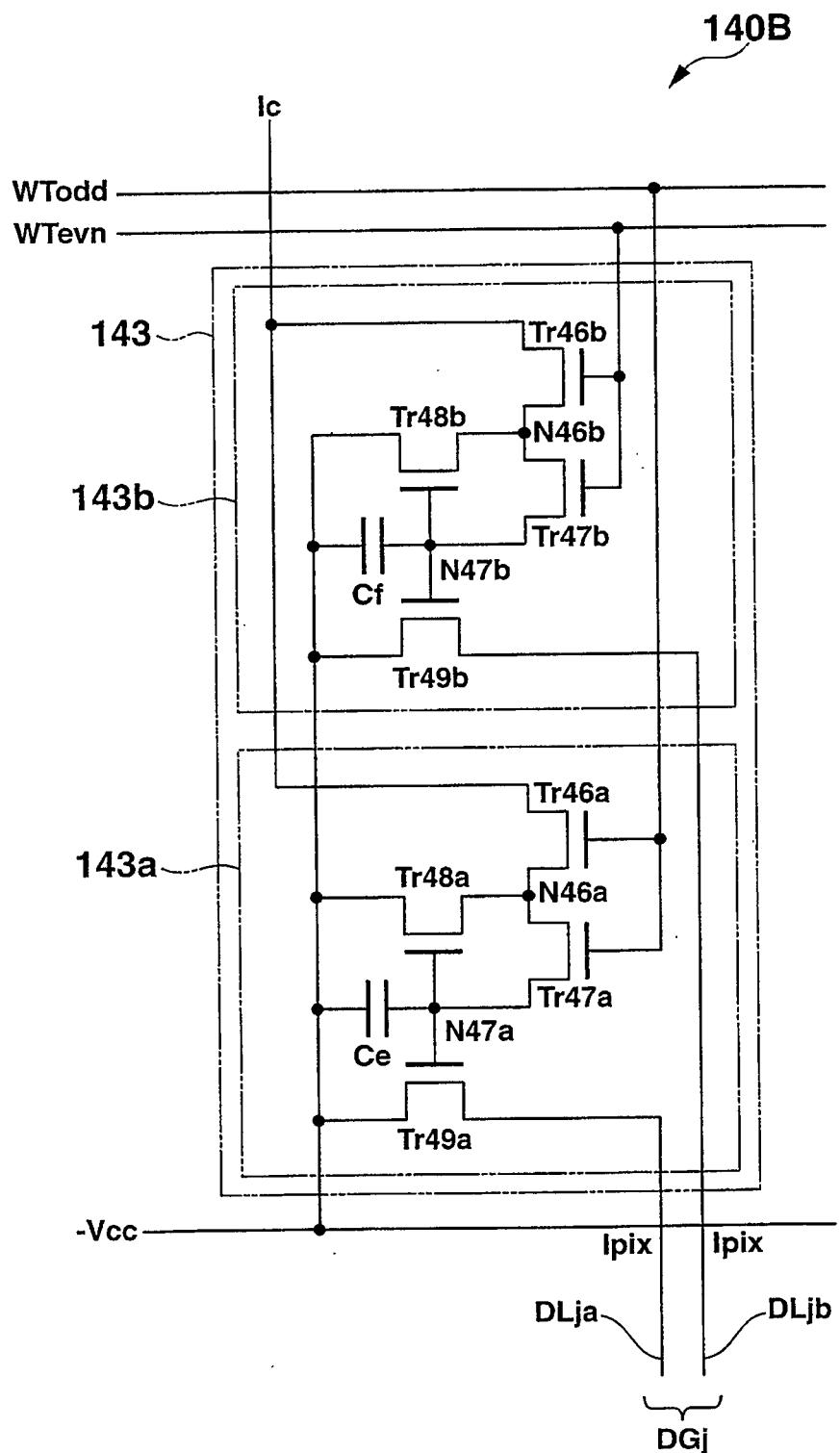

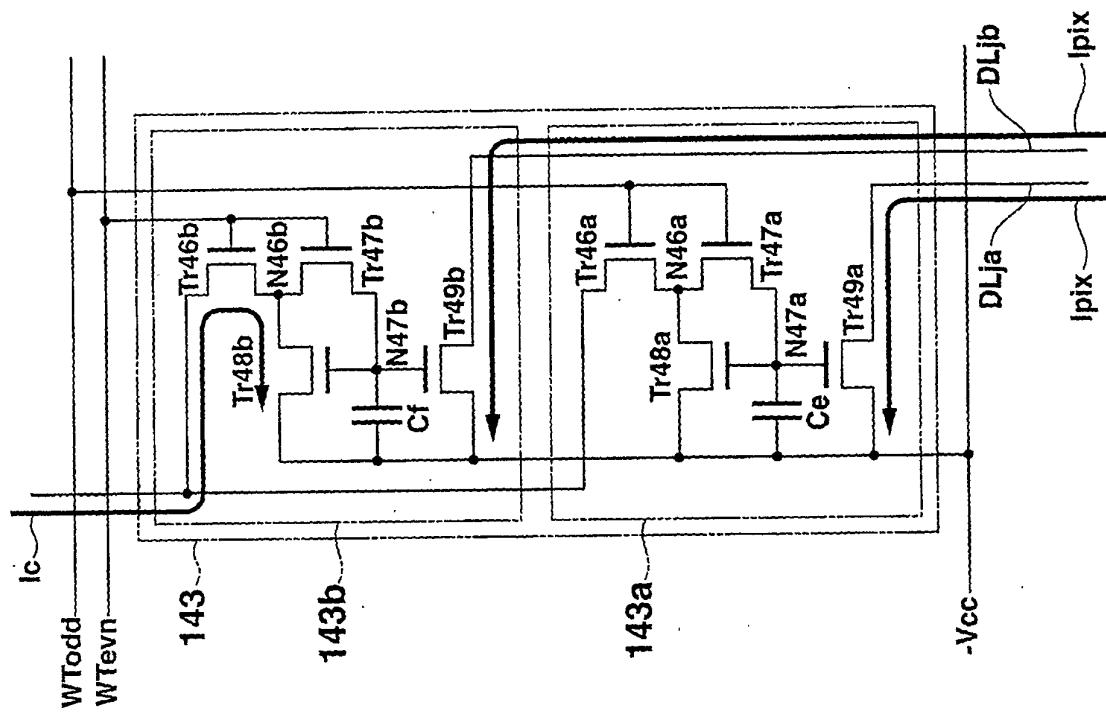

**[0059]** FIG. 4 is a circuit block diagram showing a structural example of the current holding/distributing section which can be applied to the display apparatus according to this example.

**[0060]** In this example, just a structural example which

can be applied to the display apparatus according to this embodiment is illustrated.

**[0061]** For example, as shown in FIG. 4, each current distribution circuit (a signal distributing section) 141 constituting the current holding/distributing section 140A comprises a switch transistor Tr41a and a switch transistor Tr41b. In the switch transistor Tr41a, the signal current Ic output from the current generating section 130 is supplied to one end side (a source terminal) of a current path, the other end side (a drain terminal) of the current path is connected with a first output contact point N41a extending to the current holding circuit 142, and a first current fetch signal WTodd supplied as a data control signal from the system controller 150 is applied to a control terminal (a gate terminal). In the switch transistor Tr41b, a signal current Ic output from the current generating section 130 is supplied to one end side (a source terminal) of a current path, the other end side (a drain terminal) of the current path is connected with a second output contact point N41b extending to the current holding circuit 142, and a second current fetch signal WTevn supplied as a data control signal is applied to a control terminal (a gate terminal).

**[0062]** Each current holding circuit 142 constituting the current holding/distributing section 140A has a configuration in which latch sections (signal holding/ outputting sections) 142a and 142c on two stages which are connected with the data line DLja in parallel in common and to which the signal current Ic output from the current distribution circuit 141 through the first output contact point N41a is supplied in common are provided in parallel with latch sections (signal holding/outputting sections) 142b and 142d on two stages which are connected with the data line DLjb in common and to which the signal current Ic output from the current distribution circuit 141 through the second output contact point N41b is supplied in common.

**[0063]** For example, as shown in FIG. 4, each latch section 142a (or 142c) comprises: a transistor Tr42a (or Tr42c) which has a current path (a source - a drain) connected between the output contact point N41a and the contact point N42a (or N42c) of the current distribution circuit 141 and has a control terminal (a gate) to which a first latch signal LCup (or a second latch signal LCiw) is applied; a transistor Tr43a (or Tr43c) which has a current path connected between the contact point N42a (or N42c) and the contact point N43a (or N43c) and has a control terminal to which a first latch signal LCup (or a second latch signal LCiw) is applied; a transistor Tr44a (or Tr44c) in which one end side of a current path is connected with the contact point N42a (or N42c) while a predetermined low-potential voltage (-Vcc) is applied to the other end side of the same and a control terminal is connected with the contact point N43a (or N43c); a transistor Tr45a (or Tr45c) in which one end side of a current path is connected with the contact point N42a (or N42c) while the other end side of the same is connected with the data line DLja and a second latch signal LCiw (or a first latch

signal LCup) is applied to a control terminal; and a storage capacitance  $C_a$  (or  $C_c$ ) connected between the contact point N43a (or N43c) and the low-potential voltage (- $V_{cc}$ ).

**[0064]** For example, as shown in FIG. 4, like the latch sections 142a and 142c, each latch section 142b (or 142d) mentioned above comprises: a transistor Tr42b (or Tr42d) in which a current path (a source - a drain) is connected between the output contact N41b of the current distribution circuit 141 and the contact point N42b (or N42d) and a first latch signal LCUp (or a second latch signal LClw) is applied to a control terminal (a gate); a transistor Tr43b (or Tr43c) in which a current path is connected between the contact point N42b (or N42d) and the contact point N43b (or N43d) and a first latch signal LCUp (or a second latch signal LClw) is applied to a control terminal; a transistor Tr44b (or Tr44d) in which one end side of a current path is connected with the contact point N42b (or N42d) while a predetermined low-potential voltage (-Vcc) is applied to the other end side of the same, and a control terminal is connected with the contact point N43b (or N43d); a transistor Tr45b (or Tr45d) in which one end side of a current path is connected with the contact point N42b (or N42d) while the other end side of the same is connected with the data line DLjb, and a second latch signal LClw (or a first latch signal LCUp) is applied to a control terminal; and a storage capacitance Cb (or Cd) connected between the contact point N43b (or N43d) and the low-potential voltage (-Vcc).

**[0065]** In this example, although the respective transistors Tr41a, Tr41b in the current distribution circuit 141 according to this example and the respective transistors Tr42a to Tr45a, Tr42b to Tr45b, Tr42c to Tr45c and Tr42d to Tr45d in the current holding circuit 142 are not restricted to specific types, it is possible to apply an n-channel type field effect thin film transistor in which an amorphous silicon layer is a channel layer or a field effect thin film transistor in which a polysilicon layer is a channel layer, for example. In this case, as shown in FIG. 2, the current holding/distributing section 140A can be integrally formed with the pixel array on an insulating substrate BASE constituting the display panel 110A. Further, each of the storage capacitances Ca to Cd provided in the respective latch sections 142a to 142d may be a parasitic capacitance formed between the gate and the source of each of the transistors Tr44a to Tr44d or an individually provided capacitance element.

**[0066]** In the above-described current holding circuit 142, the storage capacitances  $C_a$  to  $C_d$  constitute the signal holding section and the charges storage circuit, and the transistors  $Tr44a$  to  $Tr44d$  and  $Tr45a$  to  $Tr45d$  constitute the gradation current outputting section.

### **<Operations of Current Holding/distributing Section>**

**[0067]** Operations in the current holding/distributing section having such a configuration will now be described.

**[0068]** FIGS. 5A and 5B are conceptual views showing general operations of the current holding/distributing section which can be applied to this example.

**[0069]** In this example, of the latch sections 142a to 142d constituting each current holding circuit 142, the illustration and description will be given as to the side where the latch sections 142 and 142c are provided for the convenience' sake, but the same operations are executed on the side where the latch sections 142b and 142d are provided.

**[0070]** Operations in the current holding/distributing section 140A (the current distribution circuit 141 and the current holding circuit 142) according to this embodiment has: a current distributing operation of distributing a sig-

nal current (a gradation signal)  $I_c$  which is supplied from the current generating section 130 in time series and based on display data written in the display pixels for the plurality of rows (two rows in this embodiment) corresponding to the respective scanning lines  $SL_{1a}$  and  $SL_{1b}$

constituting the scanning line group SGi to the output contact point N41a side and the output contact point N41b side by the current distribution circuit 141; a current holding operation of fetching and holding the distributed signal current  $I_S$  in either the latch sections 142a and

signal current  $I_C$  in either the latch sections 142a and 142b or the latch sections 142c and 142d constituting the current holding circuit 142 in synchronization with the current distributing operation; and a current output operation of simultaneously outputting the gradation current

Ipix based on the signal current  $I_C$  held in the current holding operation to the respective data lines  $DL_{ja}$  and  $DL_{jb}$  constituting the data line group  $DG_j$  from the other one of the latch sections 142a and 142b and the latch sections 142c and 142d constituting the current holding

sections 142a and 142b constituting the current holding circuit 142 in synchronization with the current holding operation. The current holding operation and the current output operation are controlled to be alternately repeatedly executed between the latch sections 142a and 142b

and the latch sections 142c and 142d constituting the current holding circuit 142 while repeating the current distributing operation in accordance with all the scanning line groups SGi in the display panel 110A.

**[0071]** That is, in a period where the signal current  $I_C$  supplied from the current generating section 130 based on the display data in accordance with each column is fetched and held on one latch section side constituting

the current holding circuit 142, the gradation current  $I_{pix}$  is read and output from the other latch section side at the same time. Therefore, the operation of fetching the signal current  $I_C$  based on the display data and outputting the gradation current  $I_{pix}$  to the data line group DGj of each column is substantially executed.

[0072] Each of the operations will now be concretely described with reference to each circuit configuration of the current holding/distributing section.

(Current Distributing Operation)

[0073] In the current distributing operation, by selec-

tively setting first and second current fetch signals WTodd and WTevn supplied as data control signals from the system controller 150 to the high level in the current distribution circuit 141, one of the switches Tr41a and Tr41b is sequentially turned on, and the signal current  $I_c$  corresponding to the display pixels EM in each row is output from the current generating section 130 in time series in synchronization with the timing of turning on the switch. As a result, the signal current  $I_c$  is distributed in accordance with each row and output to the individual latch sections 142a and 142c or 142b and 142d constituting the later-described current holding section 142 through each output contact point N41a or N41b.

(Current Holding Operation/current Output Operation)

**[0074]** In the current holding circuit 142 (the latch sections 142a to 142d), by selectively setting first and second latch signals LCup and LClw supplied as data control signals from the system controller 150 to the high level, one (the latch sections 142a and 142b or the latch sections 142c and 142d) of the latch sections 142a and 142c connected with the output contact point N41a in parallel and the latch sections 142b and 142d connected with the output contact point N41b in parallel is set in a current holding operation state, and the remaining latch sections (the latch sections 142c and 142d or the latch sections 142a and 142b) are set in a later-described current output operation state.

**[0075]** In the current holding operation, as shown in FIG. 5A (the latch sections 142a and 142c alone are illustrated for the convenience's sake), the first latch signal LCup is set to the high level, and the second latch signal LClw is set to the low level. As a result, in the latch section 142a connected with the output contact point N41a, the transistors Tr42a, Tr43a and Tr44a are turned on, and the transistor Tr45a is turned off. At this time, since the part between the gate and the drain of the transistor Tr44a is electrically short-circuited by the transistor Tr43a, the transistor Tr44a operates in a saturation region. Consequently, the signal current  $I_c$  supplied from the current generating section 130 and output to the output contact point N41a through the switch Tr41a of the current distribution circuit 141 flows to the low-potential voltage (-Vcc) side through the transistors Tr42a and Tr44a of the latch section 142a, and a current level of the signal current  $I_c$  is converted into a voltage level between the gate and the source of the transistor Tr44a so that the signal current  $I_c$  is stored as the electric charges in the storage capacitance  $C_a$ .

**[0076]** In the current output operation, as shown in FIG. 5B, the first latch signal LCup is set to the low level, and the second latch signal LClw is set to the high level. As a result, the transistors Tr42a and Tr43a are turned off and the transistor Tr45a is turned on in the latch section 142a. At this time, a potential (a high voltage) based on the electric charges (the signal current  $I_c$ ) stored in the storage capacitance  $C_a$  by the current holding operation

is held in the contact point N43a, and hence the transistor Tr44a continues the ON operation. Consequently, the data line DLja arranged in the display panel 110 (not shown) is connected with the low-potential voltage (-Vcc) through the transistors Tr45a and Tr44a of the latch section 142a, and the gradation current  $I_{pix}$  flows in such a manner that it is drawn from the data line DLja side (i.e., the display pixel EM side) toward the latch section 142a (the current holding circuit 142).

**[0077]** Further, in a state where the first latch signal LCup is set to the low level and the second latch signal LClw is set to the high level (i.e., the current output operation state of the latch section 142a mentioned above), the transistors Tr42c and Tr43c are turned on, the part between the gate and the drain of the transistor Tr44c is electrically short-circuited by the transistor Tr43a so that the transistor Tr44c is turned on in the saturation region and the transistor Tr45c is turned off in the latch section 142c connected with the output contact point N41a in parallel. Therefore, the signal current  $I_c$  output to the output contact point N41a flows to the low-potential voltage (-Vcc) side through the transistors Tr42c and Tr44c of the latch section 142c, and a current level of the signal current  $I_c$  is converted into a voltage level between the gate and the source of the transistor Tr44c so that the signal current  $I_c$  is stored as the electric charges in the storage capacitance  $C_c$ .

**[0078]** That is, in a period that one of the latch sections 142a and 142c is set in the current holding operation state, the other one is simultaneously set in the current output operation state. Such an operation state is likewise executed in a combination of the non-illustrated latch sections 142b and 142d.

**[0079]** The description has been given as to the example where the function (a current polarity reversing section) which generates (converts a current direction) the negative gradation current  $I_{pix}$  corresponding to the signal current  $I_c$  with the positive polarity supplied from the current generating section 130 is provided and the gradation current  $I_{pix}$  is drawn from the data line (the display pixels) side in order to cope with the circuit configuration of the later-described pixel drive circuit provided to the display pixel EM in the current holding/distributing section 140A according to this example. However, the present invention is not restricted thereto, and it may have a configuration in which the gradation current  $I_{pix}$  with the positive polarity is generated and the gradation current  $I_{pix}$  is passed to the data line (the display pixels) in accordance with a circuit configuration of the display pixels EM.

**[0080]** It is to be noted that nearly all known current driver circuits (corresponding to the current generating section) which are distributed and available in the marketplace have a configuration of outputting the gradation signal (the signal current)  $I_c$  having the positive polarity, and hence the gradation current whose current direction is converted can be readily generated by known current drivers by applying the current holding/distributing section having the above-described configuration.

## &lt;Drive Control Method of Display Apparatus&gt;

**[0081]** A drive control operation (a drive control method) in the display apparatus having the above-mentioned configuration will now be described.

**[0082]** FIG. 6 is a timing chart illustrating a drive control operation (a drive control method) in the display apparatus according to this example.

**[0083]** In this example, the description will be given with reference to each structure of the display apparatus described above.

**[0084]** In the display apparatus having the above-described structure, display data consisting of digital data which allows each display pixel (a light emitting element) EM constituting the display panel 110A to emit a light with a predetermined luminance gradation is first extracted from a video signal by using the display signal generating section 160, and the extracted display data is sequentially supplied to the current generating section 130 as serial data corresponding to each row of the display panel 110A.

**[0085]** The display data (the digital data) supplied to the current generating section 130 is converted into a signal current (a gradation signal)  $I_c$  corresponding to the display data at a timing based on a data control signal fed from the system controller 150, and output to the current holding/distributing section 140A provided in accordance with the data line group DG<sub>j</sub> of each column arranged in the display panel 110A.

**[0086]** In this example, the signal current  $I_c$  output from the current generating section 130 is output in time series in units of the data line group DG<sub>j</sub> corresponding to each column in the display panel 110A in accordance with each row for the respective display pixels EM connected to the respective data lines DL<sub>j</sub>a and DL<sub>j</sub>b constituting the data line group DG<sub>j</sub>, for example.

**[0087]** As shown in FIG. 6, the current distributing operation is executed in the current holding/distributing section 140A. In the current distributing operation, the signal current  $I_c$  corresponding to the display pixels EM arranged in the plurality of rows (two rows in this embodiment) in accordance with each column is sequentially fetched, the transistors or switches Tr41a and Tr41b of the current distribution circuit 141 are selectively turned on at the timing based on data control signals (first and second current fetch signals WT<sub>odd</sub> and WT<sub>even</sub>) supplied from the system controller 150, and the signal current  $I_c$  is sequentially supplied to the latch section 142a (or 142c) and the latch section 142b (or 142d) of the current holding circuit 142.

**[0088]** Then, in synchronization with this timing, the latch sections 142a and 142b of the current holding circuit 142 are set in the current holding operation state based on the data control signals (the first latch signal LC<sub>up</sub> at the high level and the second latch signal LC<sub>lw</sub> at the low level) supplied from the system controller 150. As a result, only in a period that the signal current  $I_c$  is supplied to the respective latch sections 142a and 142b, the cur-

rent holding operation is sequentially executed. In the current holding operation, the electric charges based on the signal current  $I_c$  corresponding to the display pixels EM in the respective rows (e.g., the first row and the second row) is stored in the respective storage capacitances Ca and Cb.

**[0089]** As shown in FIG. 6, such a current distributing operation and current holding operation are alternately repeated in the latch sections 142a and 142b and the latch sections 142c and 142d with the signal levels of the first and second current fetch signals WT<sub>odd</sub> and WT<sub>even</sub> and the first and second latch signals LC<sub>up</sub> and LC<sub>lw</sub> being appropriately set. Consequently, the signal current  $I_c$  corresponding to the display pixels EM in the two rows based on the display data is sequentially held in each current holding circuit 142.

**[0090]** Subsequently, after the current holding operation, the latch sections 142a and 142b of the current holding circuit 142 are set in the current output operation state based on the data control signals (the first latch signal LC<sub>up</sub> at the low level and the second latch signal LC<sub>lw</sub> at the high level) supplied from the system controller 150. As a result, the current output operation is executed in the respective latch sections 142a and 142b. In the current output operation, the gradation current  $I_{pix}$  based on the electric charges stored in the respective storage capacitances Ca and Cb is simultaneously supplied to the display pixels EM in the respective rows (e.g., the first row and the second row) through the respective data lines DL<sub>j</sub>a and DL<sub>j</sub>b constituting the data line group DG<sub>j</sub>.

**[0091]** Therefore, the gradation current  $I_{pix}$  is output from the current holding/distributing section 140A through the data line group DG<sub>j</sub> of each column, and the scanning signal V<sub>sel</sub> at the high level is applied to a specific scanning line group SG<sub>i</sub> from the scanning driver 120A at the timing based on the scanning control signal supplied from the system controller 150. As a result, all the selection transistors Tr<sub>sel</sub> connected to the respective scanning lines SL<sub>ia</sub> and SL<sub>ib</sub> constituting this scanning line group SG<sub>i</sub> are turned on, the gradation current  $I_{pix}$  supplied to the display pixels EM in the plurality of rows (e.g., two rows including the first row and the second row) through the data lines DL<sub>j</sub>a and DL<sub>j</sub>b of each data line group DG<sub>j</sub> is written in the respective display pixels EM, thereby executing the light emission operation with a predetermined luminance gradation based on the gradation current  $I_{pix}$ .

**[0092]** Furthermore, in the respective latch sections 142a and 142b, in a period where the current output operation is executed, as shown in FIG. 6, the latch sections 142c and 142d of the current holding circuit 142 are set in the current holding operation state based on the data control signals (the first latch signal LC<sub>up</sub> at the low level and the second latch signal LC<sub>lw</sub> at the high level) supplied from the system controller 150. As a result, the current holding operation is sequentially executed. In this operation, the signal current  $I_c$  for each row continuously supplied from the current generating section 130 is

fetched in the respective latch sections 142c and 142d, and the electric charges based on the signal current  $I_C$  corresponding to the display pixels EM in the respective rows (e.g., the third row and the fourth row) are stored in the respective storage capacitances  $C_c$  and  $C_d$ .

**[0093]** Then, after the current output operation in the latch sections 142a and 142b, the system controller 150 again sets the first latch signal  $LC_{up}$  to the high level and the second latch signal  $LC_{lw}$  to the low level. As a result, the latch sections 142a and 142b are again set in the current holding operation state. Consequently, the current output operation is executed in the respective latch sections 142a and 142b. In the current output operation, the electric charges based on the signal current  $I_C$  corresponding to the display pixels EM in the respective rows (e.g., the fifth row and the sixth row) are stored in the respective capacitances  $C_a$  and  $C_b$ .

**[0094]** Moreover, at this time, when the latch sections 142c and 142d of the current holding circuit 142 are set in the current output operation state, there is executed the current output operation in which the gradation current  $I_{pix}$  based on the electric charges stored in the respective storage capacitances  $C_c$  and  $C_d$  at the foregoing timing is simultaneously supplied to the display pixels EM in respective rows (e.g., the third row and the fourth row) through the respective data lines  $DL_{ja}$  and  $DL_{jb}$  constituting the data line group  $DG_j$ .

**[0095]** As a result, in the latch sections 142a and 142b and the latch sections 142c and 142d on the two stages constituting the respective current holding circuits 142 provided in accordance with respective columns in the current holding/distributing section 140A, the controls of simultaneously executing the current holding operation and the current output operation are alternately repeated in accordance with a predetermined operation cycle. Consequently, there is executed the operation in which the signal current  $I_C$  corresponding to the display data of each row output from the current generating section 130 is continuously fetched and held in the current holding circuit and simultaneously supplied to the display pixels in the plurality of rows as the gradation current  $I_{pix}$ .

**[0096]** Therefore, this example is configured in such a manner that the display pixels in a plurality of rows (two rows in this embodiment) are altogether set in the selected state by applying a single scanning signal from the scanning driver to the display panel in which the plurality of display pixels are two-dimensionally arranged and that display data corresponding to the display pixels in the plurality of rows is sequentially fetched and held by the signal driver and the gradation current corresponding to the plurality of rows is simultaneously supplied to the respective display pixels at a predetermined timing (e.g., one scanning period). Therefore, as compared with a known drive control method which applies one scanning signal to one scanning line, the number of scanning lines driven at a single scanning timing (the number of rows of the display pixels to be selected) becomes severalfold, and a time required to write the gradation current in the

display pixels can be set to be substantially severalfold (twofold in this example).

**[0097]** Additionally, since the data lines arranged in each column are formed as a data line group in which a plurality of (two in this example) data lines are determined as one set, a capacitance component consisting of a holding capacitance which is parasitic to each data line and provided in each display pixel or a parasitic capacitance of a drive transistor can be greatly reduced (1/2 in this example) as compared with a configuration of a known display apparatus in which one data line is arranged in one column. Therefore, a time required to write the gradation current supplied to each data line in each display pixel can be reduced, or a delay of this write time can be suppressed.

**[0098]** As a result, a sufficiently long time to write display data in each display pixel can be assured. Therefore, when the display panel is increased in size or the high definition is realized, or even when an image is displayed with a low gradation, the wiring capacitance of the data lines can be satisfactorily charged to a predetermined voltage, thereby eliminating the insufficient write state of display data. Further, each display pixel can be allowed to emit a light with an appropriate luminance gradation corresponding to display data, and a luminance gradient (display irregularities) generated in the display panel can be greatly reduced, thereby improving the display image quality.

**[0099]** This example is configured in such a manner that the scanning lines arranged in the respective rows are formed of the scanning line group in which a plurality of (two in this example) scanning lines are determined as one set and that the display pixels for a plurality of rows (two rows in this example) are altogether set in the selected state by using a single scanning signal. Therefore, the number of scanning signals output from the scanning driver to the display panel can be greatly reduced (1/2 in this example), and the number of the connection terminals between the display panel and the scanning driver can be largely decreased (1/2 in this example). As a result, even if the high definition is realized in the display panel, an increase in number of the output terminals of a driver chip can be suppressed, and a pitch (a gap) between the terminals can be prevented from being small, thereby simplifying the positional accuracy in a connection step of the driver chip or reducing the number of steps.

**[0100]** Furthermore, when a field effect thin film transistor in which an amorphous silicon layer or a polysilicon layer is a channel layer is applied as each transistor constituting the current holding/ distributing section, the current holding/distributing section can be integrally formed with the display panel (the pixel array) on the same substrate, and an increase in the number of components can be suppressed, thereby keeping a product cost of the display apparatus down.

**[0101]** The above has described the example in which the scanning line group is arranged to correspond to the

display pixels in, e.g., two rows and the data line group corresponding to the display pixels in the two rows is arranged so that the display pixels in the two rows can be simultaneously set in the selected state by using a single scanning signal as the comparative example of the display apparatus. Another structural example of the display apparatus according to this example will now be described.

**[0102]** FIG. 7 is a schematic structural view showing a primary part of still another structural example of the display apparatus according to this comparative example.

**[0103]** FIG. 8 is a schematic structural view showing a primary part of yet another structural example of the display apparatus according to this comparative example.

**[0104]** That is, for example, as shown in FIG. 7, the display panel 110A may be configured to have each scanning line group SG<sub>i</sub> arranged to correspond to two or more rows (four rows) and each data line group DG<sub>j</sub> which comprises a plurality of (four) data lines DL<sub>j</sub>a to DL<sub>j</sub>d whose number (four) corresponds to the plurality of rows and is arranged in accordance with each pixel row. Display pixels EM in the plurality of rows (four rows) can be simultaneously set in the selected state by using a single scanning signal Vsel.

**[0105]** Furthermore, as shown in FIG. 8, as a configuration (a layout format of scanning lines) of a scanning line group arranged to correspond to a plurality of rows, for example, one scanning line SL<sub>i</sub> may be drawn (turned) within the display panel 110A without divergence and connected to the display pixels EM in a plurality of rows (two rows) in common.

<Embodiment of Display Apparatus according to the invention>

**[0106]** An embodiment of a display apparatus according to the present invention will now be described with reference to the accompanying drawings.

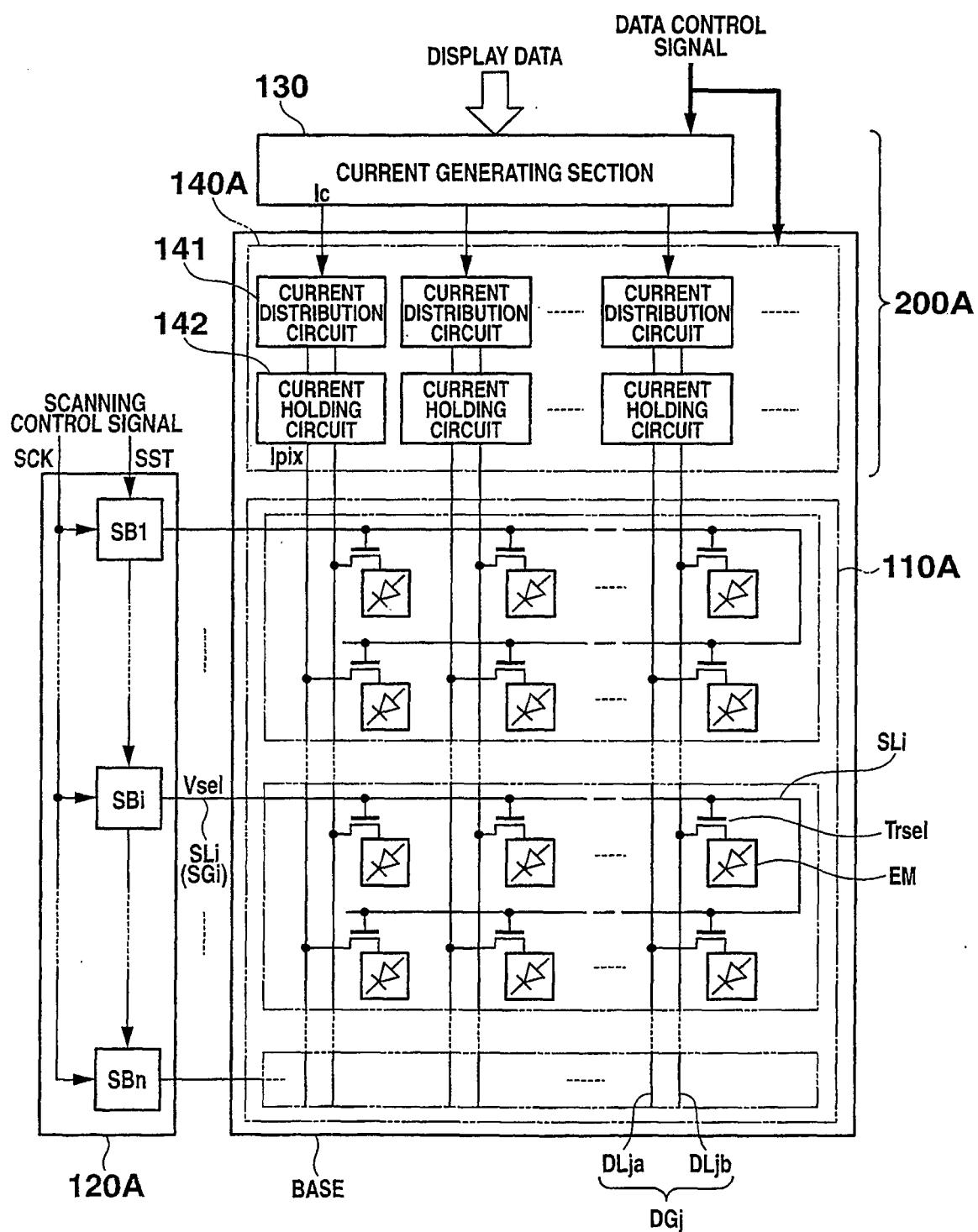

**[0107]** FIG. 9 is a structural view showing a primary part of an embodiment of a display apparatus according to the present invention.

**[0108]** Here, structures equal to those in the comparative example are denoted by equal or like reference numerals, thereby eliminating the explanation thereof.

**[0109]** The display apparatus according to the above-mentioned comparative example comprises: the display panel in which each scanning line group SG<sub>i</sub> corresponding to a plurality of rows and each data line group DG<sub>j</sub> consisting of a plurality of data lines corresponding to the plurality of rows are arranged; and peripheral circuits (the scanning driver and the signal driver comprising the current generating section and the current holding/distributing section) corresponding to the display panel. The display apparatus according to the embodiment comprises: a display panel in which each scanning line provided in accordance with each row and each data line group consisting of a plurality of data lines corresponding to a plurality of rows are arranged; and peripheral circuits (a

scanning driver and a signal driver comprising a current generating section and a current holding/distributing section) corresponding to the display panel.

**[0110]** As shown in FIG. 9, a display panel 110B according to this embodiment generally comprises: a plurality of display pixels EM which are two-dimensionally arranged (n rows × m columns) and connected to each other through selection transistors Trsel; a plurality of scanning lines SL<sub>q</sub> (q is a positive integer falling within a range of  $1 \leq q \leq n$ ; n is a positive integer and the total number of pixel rows set in the display panel 110) arranged in accordance with the display pixels EM in respective rows; and a plurality of data line groups DG<sub>j</sub> which are arranged in accordance with the display pixels EM in respective columns and in which a plurality of (two in this embodiment) data lines DL<sub>j</sub>a and DL<sub>j</sub>b (j is a positive integer falling within a range of  $1 \leq j \leq m$ ; m is a positive integer and the total number of pixel columns set in the display panel 110) are determined as one set. Each display pixel EM is provided at each intersection of the scanning line SL<sub>q</sub> and the data lines DL<sub>j</sub>a and DL<sub>j</sub>b constituting each data line group DG<sub>j</sub>.

**[0111]** The scanning driver (the selection circuit) 120B is generally connected with the scanning lines SL<sub>q</sub> in the display panel 110B, and sequentially applies a scanning signal Vsel to each scanning line SL<sub>q</sub> at a predetermined timing to sequentially set the display pixels EM in each row (one row) connected with the scanning line SL<sub>i</sub> in a selected state.

**[0112]** The current generating section 130 generally generates a signal current (a gradation signal) I<sub>c</sub> having a current value corresponding to a luminance gradation value based on display data in accordance with the display data supplied from the display signal generating section 160.

**[0113]** The current holding/distributing section 140B is generally connected with each data line group DG<sub>j</sub> in the display panel 110B. The section 140B fetches the signal current I<sub>c</sub> corresponding to a plurality of rows (two rows in this embodiment) supplied from the current generating section 130 in time series, and sequentially supplies a gradation current I<sub>pix</sub> based on the signal current I<sub>c</sub> to the display pixels EM in a plurality of rows (two rows in this embodiment) at a predetermined timing. In this embodiment, the current generating section 130 and the current holding/distributing section 140B constitute a signal driver 200B.

**[0114]** It is to be noted that, in the configuration shown in FIG. 9, the current holding/distributing section 140B is integrally formed with a pixel array on an insulating substrate BASE on which the plurality of display pixels EM (i.e., the pixel array) constituting the display panel 110B are formed as a structural example, but the present invention is not restricted thereto. For example, the signal driver 200B may have a conformation of a driver chip and mounted (packaged) on the substrate BASE. The detail will be described later.

**[0115]** A concrete configuration of each structure will

now be described.

(Display Panel)

**[0116]** For example, as shown in FIG. 9, the display panel 110 which can be applied to the display apparatus according to this embodiment has a configuration in which each scanning line SL<sub>q</sub> corresponding to each pixel row and each data line group DG<sub>j</sub> having two data lines DL<sub>j</sub>a and DL<sub>j</sub>b determined as one set and corresponding to one pixel column are arranged to be orthogonal to each other and the display pixel EM is connected at each intersection of an odd-numbered scanning line SL<sub>i</sub> and the data line DL<sub>j</sub>a in each column and at each intersection of an even-numbered scanning line SL<sub>i</sub> and the data line DL<sub>j</sub>b in each column.

**[0117]** In this embodiment, in the configuration depicted in FIG. 9, although the data line group DG<sub>j</sub> arranged in each column is configured with the two data lines DL<sub>j</sub>a and DL<sub>j</sub>b being determined as one set, the present invention is not restricted thereto, and two or more data lines may be determined as one set. In this case, when the number of data lines constituting the data line group DG<sub>j</sub> is q (i.e., the number of the data lines DL<sub>j</sub>1 to DL<sub>j</sub>q is q), there is provided a configuration in which the display pixel EM is connected at each intersection of the scanning line in each row which can be calculated by dividing a line number by q with a remainder of 1 (each scanning line in the first, q+1th, 2q+1th, ... rows) and the first data line DL<sub>j</sub>1 in each column, the display pixel EM is connected at each intersection of the scanning line in each row which can be calculated in the same manner with a remainder of 2 (each scanning line in the second, q+2th, 2q+2th, ... rows) and the second data line DL<sub>j</sub>2 in each column, the display pixel and the data line are then connected in the same relationship, and the display pixel EM is connected at each intersection of the scanning line in each row which can be calculated in the same manner with a remainder of 0 (each scanning line in the qth, 2qth, 3qth, ... rows) and the qth (last) data line DL<sub>j</sub>q in each column.

**[0118]** Further, like the display pixel EM in FIG. 2, each display pixel EM generally has a configuration in which a gate terminal is connected with each scanning line SL<sub>i</sub> and a source terminal is connected with a drain terminal of the selection transistor Trsel connected to each data line DL<sub>j</sub>a or DL<sub>j</sub>b, and comprises a current controlled type light emitting element which emits a light with a predetermined luminance gradation based on a gradation current I<sub>pix</sub> supplied through the selection transistor Trsel.