Europäisches

Patentamt

European

Patent Office

Office européen

des brevets

(11)

**EP 2 067 135 B1**

(12)

## EUROPEAN PATENT SPECIFICATION

(45) Date of publication and mention

of the grant of the patent:

**01.08.2018 Bulletin 2018/31**

(51) Int Cl.:

**G09G 3/3275 (2016.01)**

**G09G 3/3233 (2016.01)**

(21) Application number: **07828894.1**

(86) International application number:

**PCT/JP2007/069154**

(22) Date of filing: **25.09.2007**

(87) International publication number:

**WO 2008/038819 (03.04.2008 Gazette 2008/14)**

---

**(54) DISPLAY DRIVING APPARATUS AND METHOD FOR DRIVING DISPLAY DRIVING APPARATUS,

AND DISPLAY APPARATUS AND METHOD FOR DRIVING DISPLAY APPARATUS**

ANZEIGENANTRIEBSVORRICHTUNG UND VERFAHREN ZUM ANTREIBEN EINER

ANZEIGENANTRIEBSVORRICHTUNG SOWIE ANZEIGEVORRICHTUNG UND VERFAHREN ZUM

ANTREIBEN EINER ANZEIGEVORRICHTUNG

APPAREIL DE COMMANDE D'AFFICHAGE ET PROCÉDÉ DE COMMANDE DE L'APPAREIL DE

COMMANDE D'AFFICHAGE, ET DISPOSITIF D'AFFICHAGE ET PROCÉDÉ DE COMMANDE DU

DISPOSITIF D'AFFICHAGE

(84) Designated Contracting States:

**DE FR GB**

(72) Inventor: **OGURA, Jun**

**Hamura-shi**

**Tokyo 205-8555 (JP)**

(30) Priority: **25.09.2006 JP 2006258717**

**26.03.2007 JP 2007078963**

(74) Representative: **Peterreins Schley**

**Patent- und Rechtsanwälte**

**Hermann-Sack-Strasse 3**

**80331 München (DE)**

(43) Date of publication of application:

**10.06.2009 Bulletin 2009/24**

(56) References cited:

**EP-A- 1 191 512** **WO-A-2005/069267**

**WO-A-2006/000101** **US-A1- 2004 239 596**

**US-A1- 2005 088 103** **US-A1- 2005 269 958**

(73) Proprietor: **Solas OLED Ltd**

**County Roscommon (IE)**

**EP 2 067 135 B1**

---

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

**Description**

## Technical Field

5 [0001] The present invention relates to a display driving apparatus and a method for driving a display driving apparatus as well as a display apparatus and a method for driving a display apparatus.

## Background Art

10 [0002] There exists a display apparatus that includes a display panel in which current driving-type light-emitting elements (e.g., organic electroluminescence (EL) element, inorganic EL elements, light-emitting diodes (LED)) are arranged in a matrix manner.

[0003] For example, Unexamined Japanese Patent Application KOKAI Publication No. H8-330600 discloses an active matrix-type driving display apparatus that is current-controlled by a voltage signal. This driving display apparatus is structured so that a current control thin film transistor and a switching thin film transistor are provided for each pixel. The current control thin film transistor flows current in an organic EL element when a voltage signal corresponding to image data is applied to a gate, and the switching thin film transistor turns ON or OFF the supply of the voltage signal to the gate of the current control thin film transistor. The driving display apparatus disclosed by Unexamined Japanese Patent Application KOKAI Publication No. H 8-330600 controls the brightness when an organic EL element emits light by controlling a voltage value of the voltage signal applied to the gate of the current control thin film transistor.

[0004] However, a threshold voltage of a transistor generally varies as time passes. Thus, in the case of the driving display apparatus of Unexamined Japanese Patent Application KOKAI Publication No. H 8-330600, a threshold voltage of a current control thin film transistor for supplying current to an organic EL element varies as time passes, which causes a variation in a value of current flowing in the organic EL element. As a result, there is a risk that brightness during the light emission by the organic EL element may vary.

[0005] Patent document US 2005/0088103 relates to a pixel driving circuit having the capability of taking into account the variation in threshold voltage of the transistor driving the light emitting device. More specifically, as can be seen in Fig. 1, the pixel driving circuit includes three switches 25, 26 and 27, a capacitor 24, an adder 23 and a digital to analog converter 22. Upon receiving video signal data, a driving voltage is generated by means of the digital to analog converter 22. The generated driving voltage is corrected by means of adder 23 thanks to the addition of a correction voltage stored in capacitor 24. More specifically, a precharge voltage is applied to the pixel driving circuit by means of switch 27; subsequently, a response voltage is read and stored by means of capacitor 24 and switch 25. The correction voltage consists in the current threshold voltage of the driving transistor. More specifically, by waiting until the correction voltage converges to the value of the threshold voltage, the correction circuit is capable of directly reading the actual threshold voltage of the driving transistor; add the actual threshold voltage to the driving voltage obtained through the digital to analogue converter 22 by means of adder 23; and apply the corrected driving voltage by means of switch 26.

## Disclosure of Invention

40 [0006] The present invention has been made in view of the above disadvantage. It is an objective of the invention to provide a display apparatus in which a light-emitting element displays an image with an appropriate gradation level even when variation is caused in a threshold voltage of a transistor for supplying light-emitting current to the light-emitting element.

[0007] The above mentioned object is achieved by the teaching of the independent claims.

45 [0008] According to the present invention, even when variation is caused in a threshold voltage of a transistor for supplying a light-emitting current to an organic EL element, the light-emitting element can emit light with desired brightness of gradation level.

## Brief Description of Drawings

50 [0009] These objects and other objects and advantages of the present invention will become more apparent upon reading of the following detailed description and the accompanying drawings in which:

55 Fig. 1 illustrates the main structure of a display pixel used in a display apparatus according an embodiment not forming part of the present invention;

Fig. 2 illustrates a signal waveform in the respective operations of a display pixel;

Fig. 3A illustrates an operation status in a writing operation of a display pixel;

Fig. 3B illustrates an equivalent circuit in a writing operation of a display pixel;

Fig. 4A shows an example of an operating characteristic of a driving transistor in a writing operation of a display pixel;

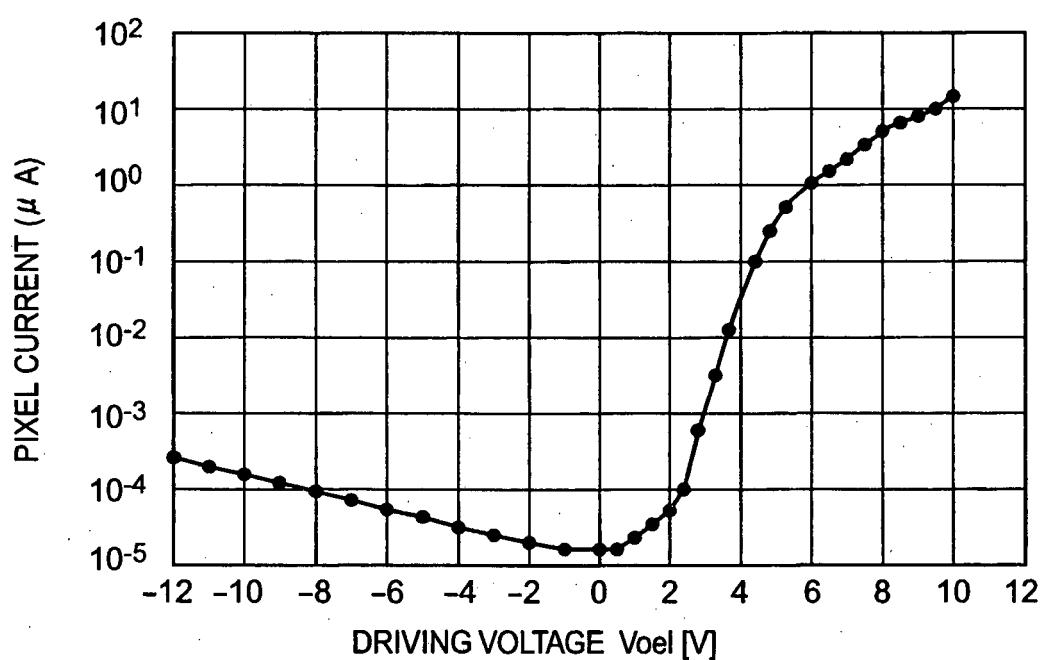

Fig. 4B shows an example of a relation between the driving current of an organic EL element and a driving voltage in a writing operation;

5 Fig. 5A illustrates an operation status in a retention operation of a display pixel;

Fig. 5B illustrates an equivalent circuit in a retention operation of a display pixel;

Fig. 6 illustrates an operating characteristic of a driving transistor in a retention operation of a display pixel;

Fig. 7A illustrates an operation status in a light-emitting operation of a display pixel;

Fig. 7B illustrates an equivalent circuit in a light-emitting operation of a display pixel;

10 Fig. 8A shows an example of an operating characteristic of a driving transistor in a light-emitting operation of a display pixel;

Fig. 8B shows an example of a load characteristic of the organic EL element in a light-emitting operation;

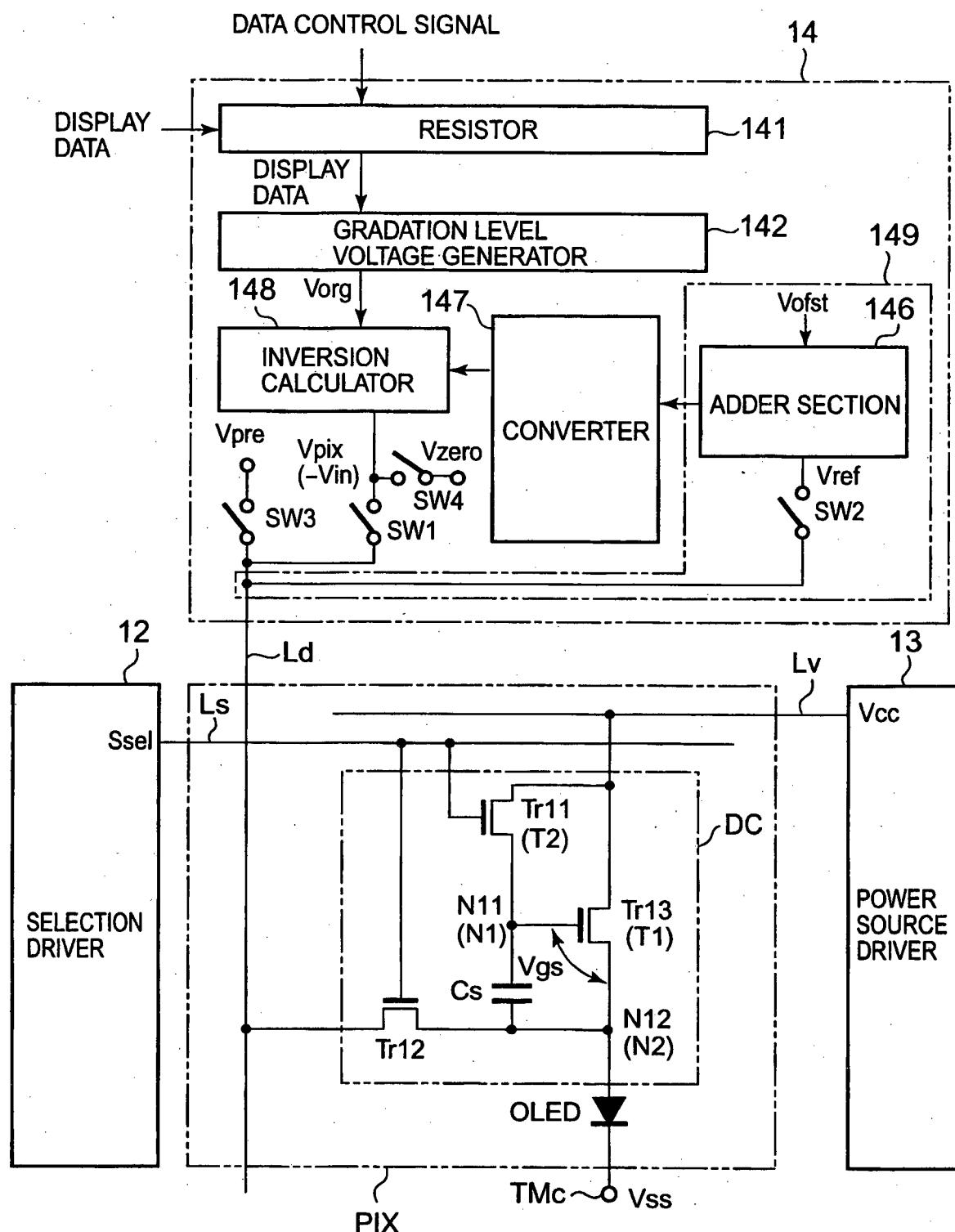

Fig. 9 is a block diagram showing the structure of the display apparatus in Embodiment 1;

15 Fig. 10 shows the structure of the main part of the data driver and the display pixel (pixel driving circuit, light-emitting element) in Embodiment 1;

Fig. 11 shows the respective steps from a selection operation to a light-emitting operation;

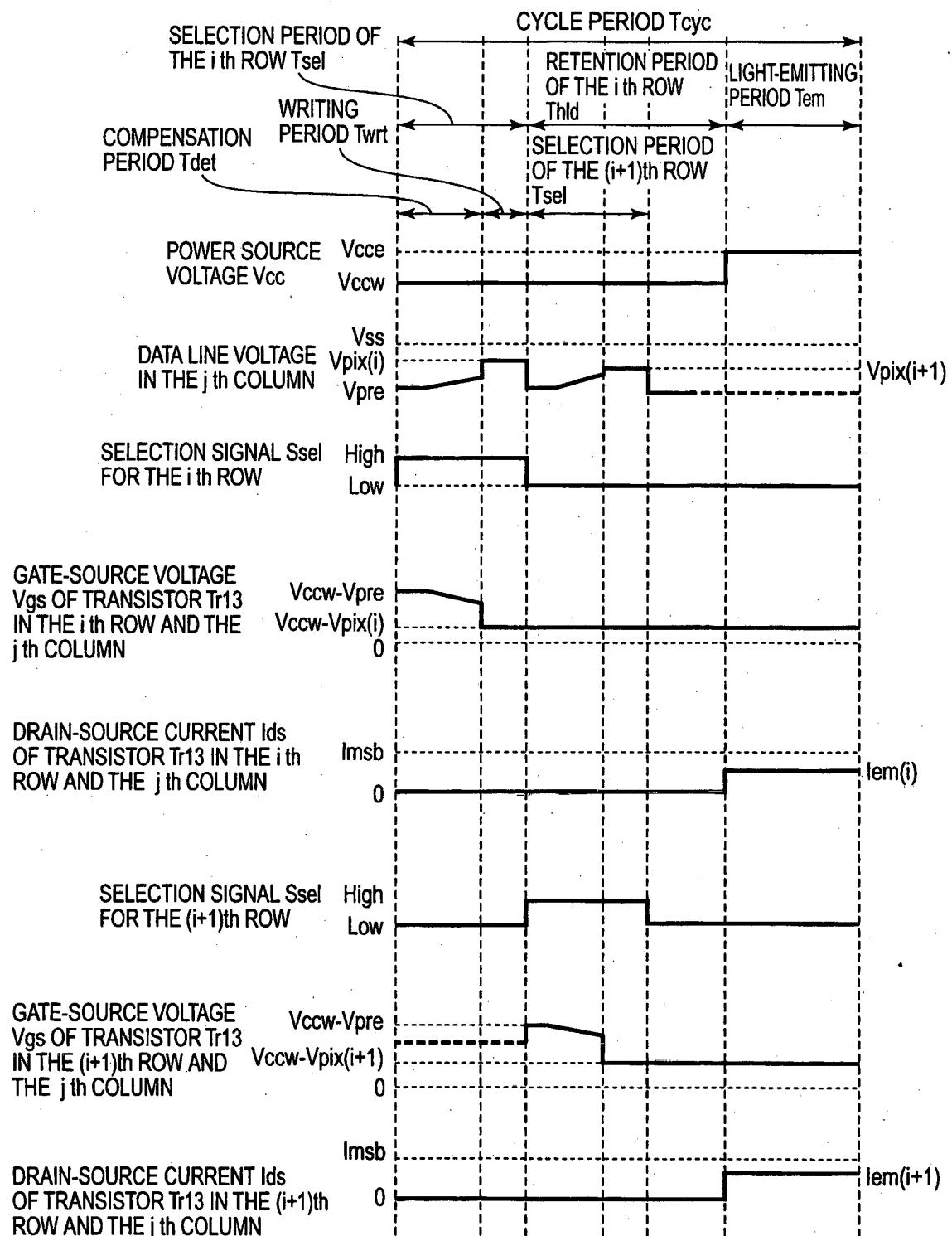

Fig. 12 illustrates a timing chart in a driving control of the display apparatus;

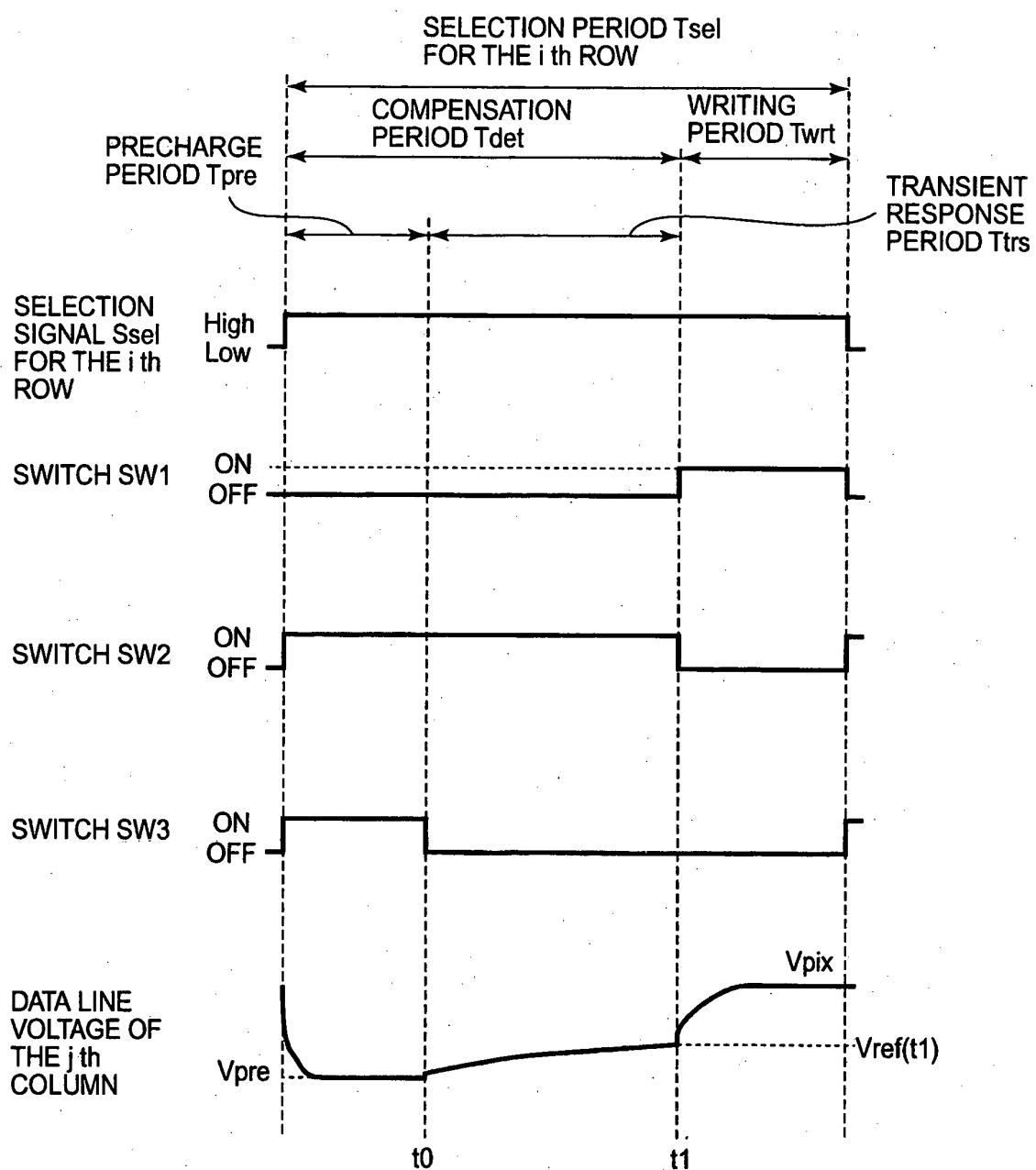

FIG. 13 illustrates a timing diagram in the selection operation of the display apparatus;

Fig. 14 illustrates operation statuses of the data driver and the display pixel in the precharge operation;

20 Fig. 15 illustrates the operation statuses of the data driver and the display pixel in the reading operation of a reference voltage;

Fig. 16 illustrates the operation statuses of the data driver and the display pixel in the writing operation of the display apparatus;

Fig. 17 illustrates the operation statuses of the data driver and the display pixel in the retention operation of the display apparatus;

25 Fig. 18 illustrates the operation statuses of the data driver and the display pixel in the light-emitting operation of the display apparatus;

Fig. 19 shows an example of a voltage applied to the data line in the selection period;

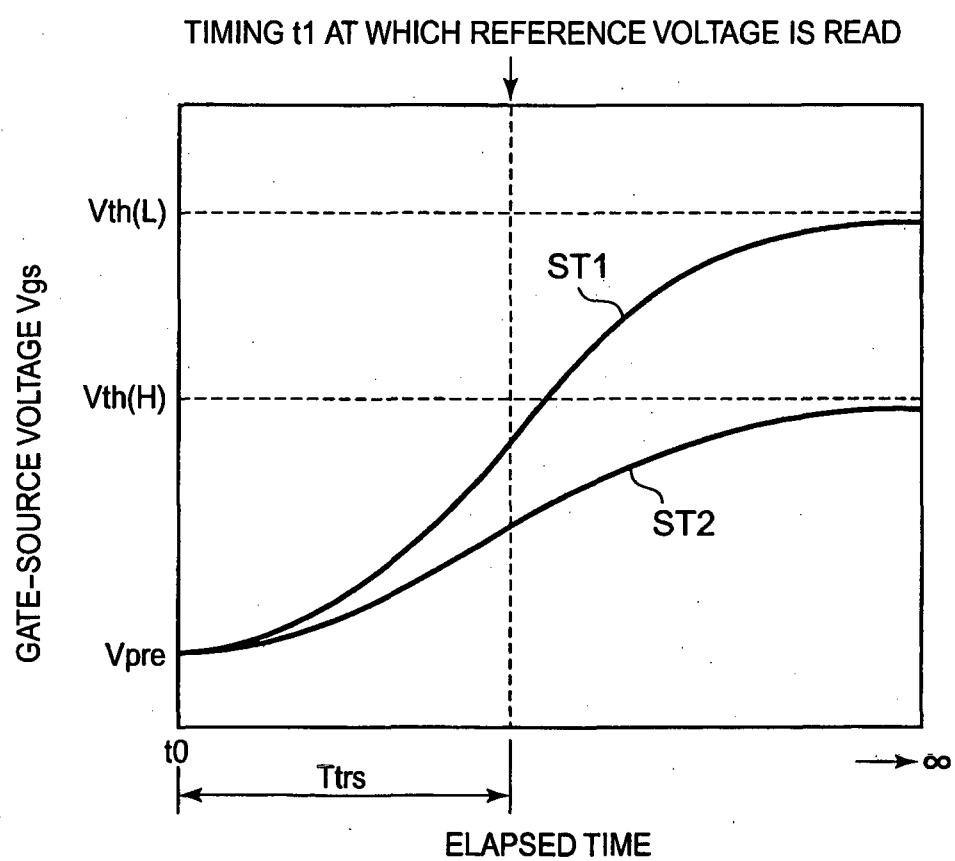

Fig. 20 illustrates a relation between an elapsed time and a potential change of a source terminal of a driving transistor during a transient response period;

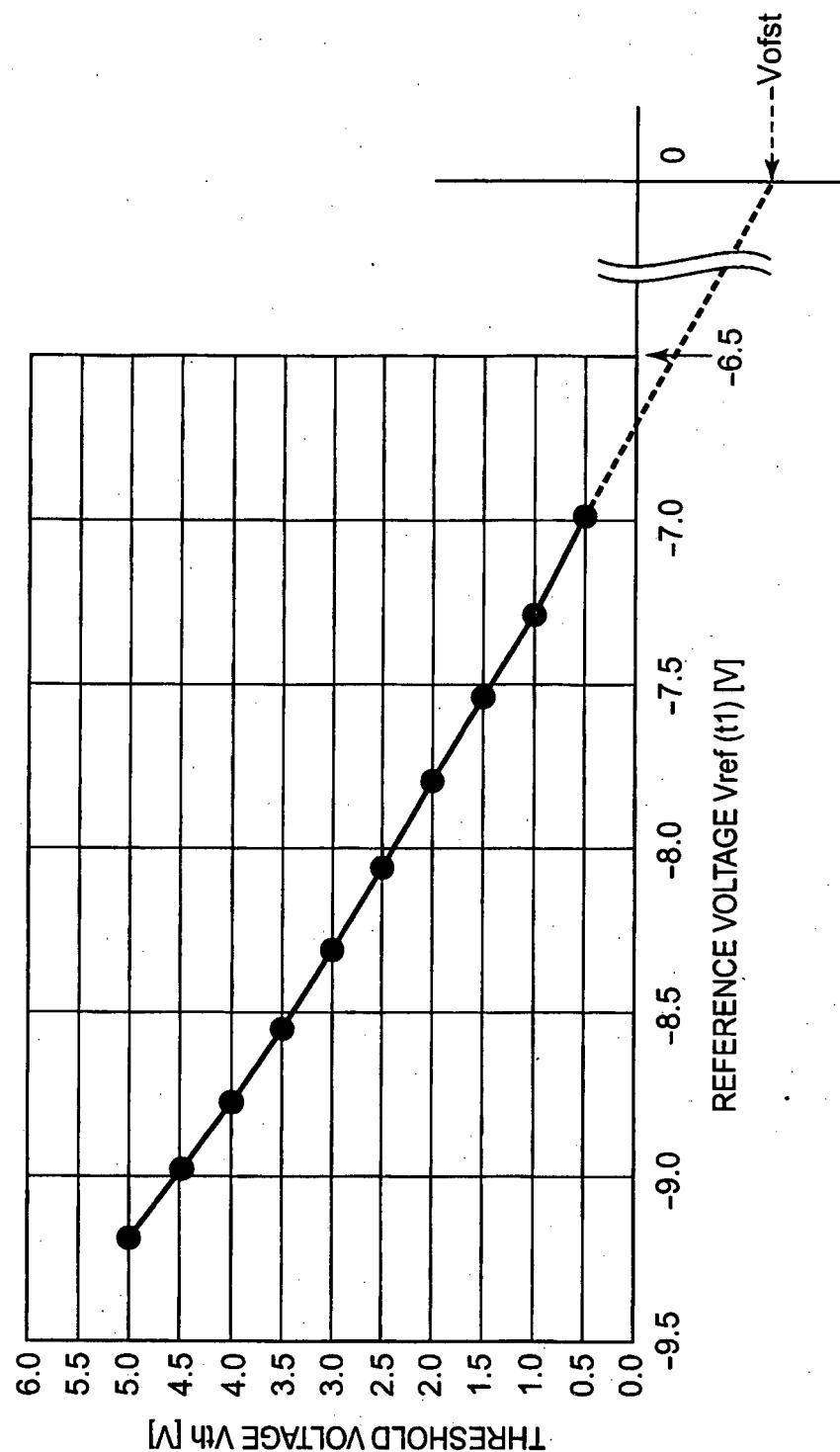

30 Fig. 21 illustrates a relation between a threshold voltage of a driving transistor and a difference to a reference voltage;

Fig. 22 shows an example of a circuit structure of a data driver;

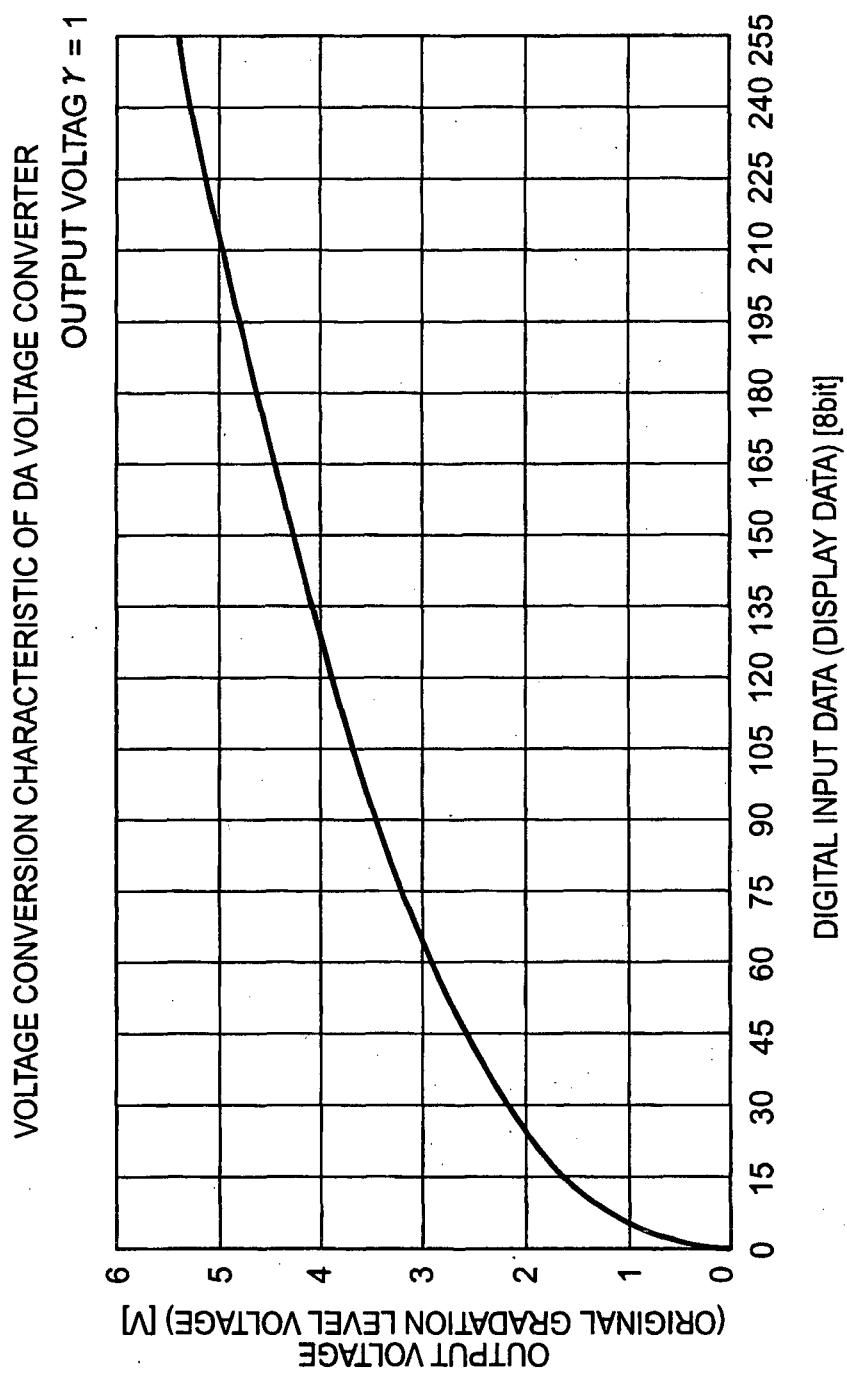

Fig. 23 shows a characteristic when a digital voltage of a digital-analog converter used as a data driver is converted to an analog voltage;

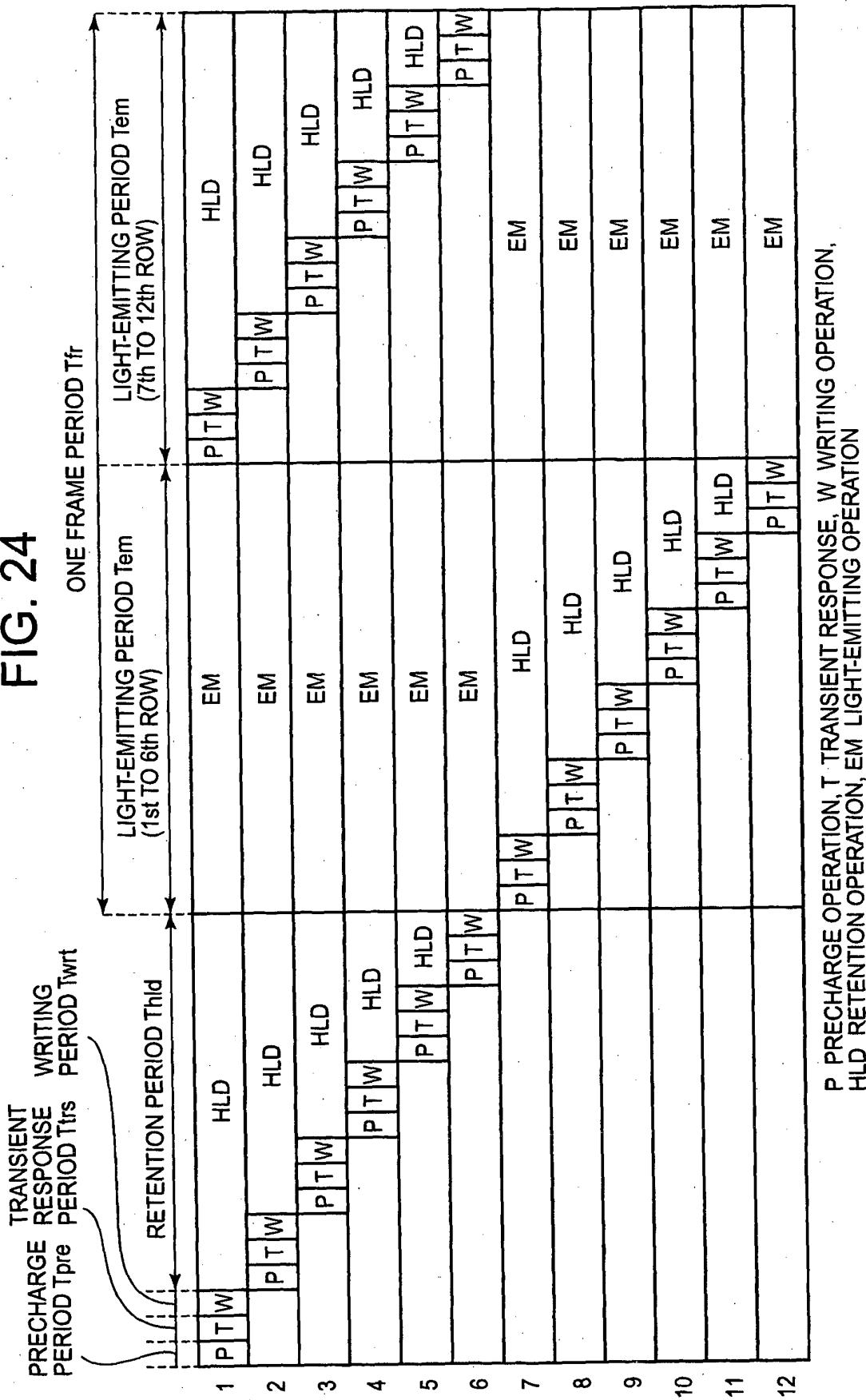

35 Fig. 24 illustrates an operation timing in a method for driving a display apparatus including a display zone of this embodiment;

Fig. 25 illustrates the structure of the main part of a data driver and a display pixel of Embodiment 2 (pixel driving apparatus, light-emitting element);

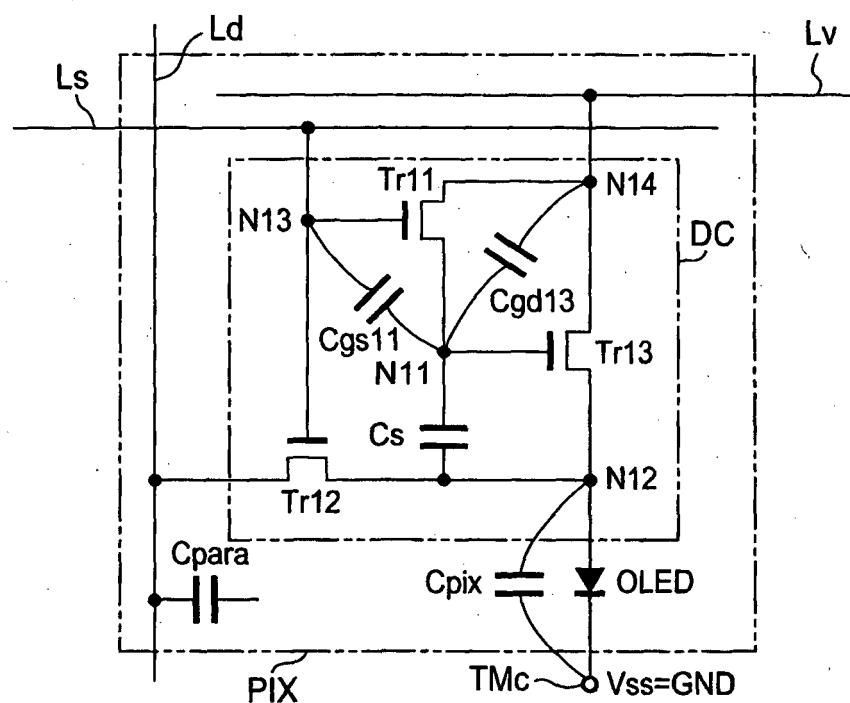

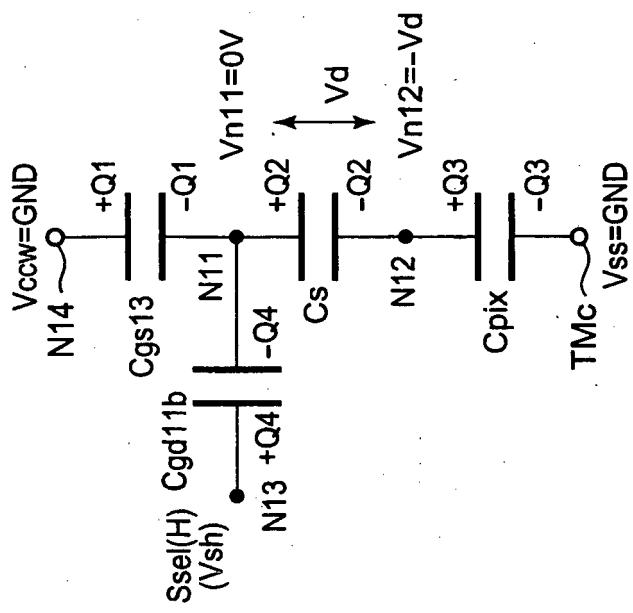

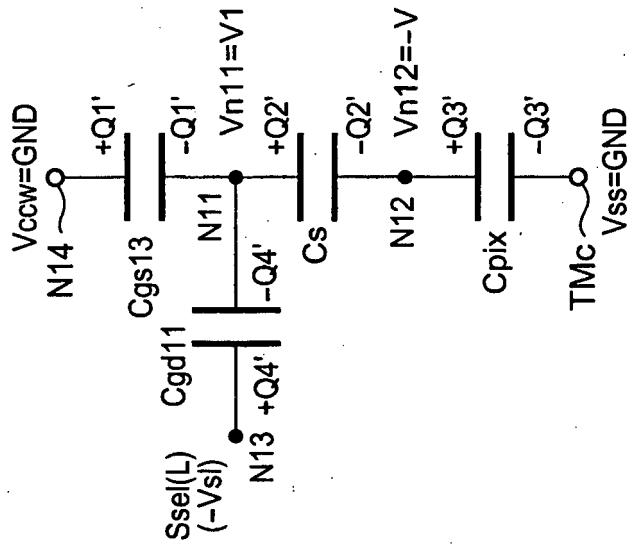

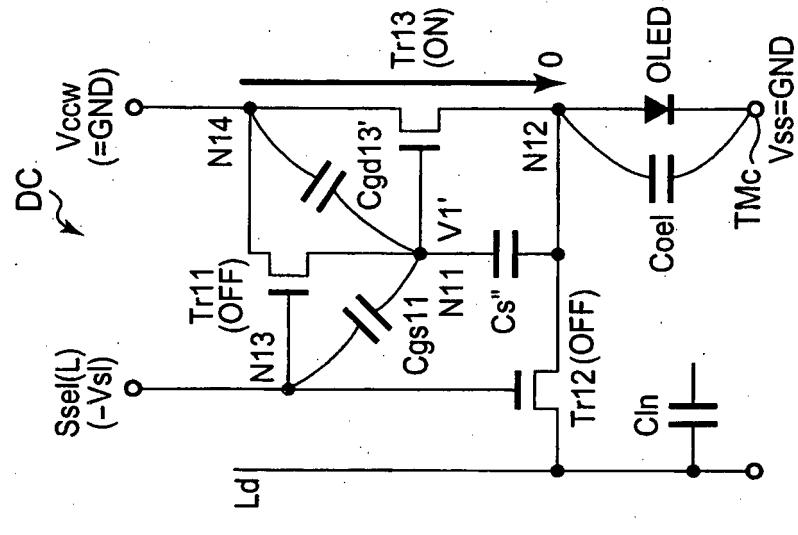

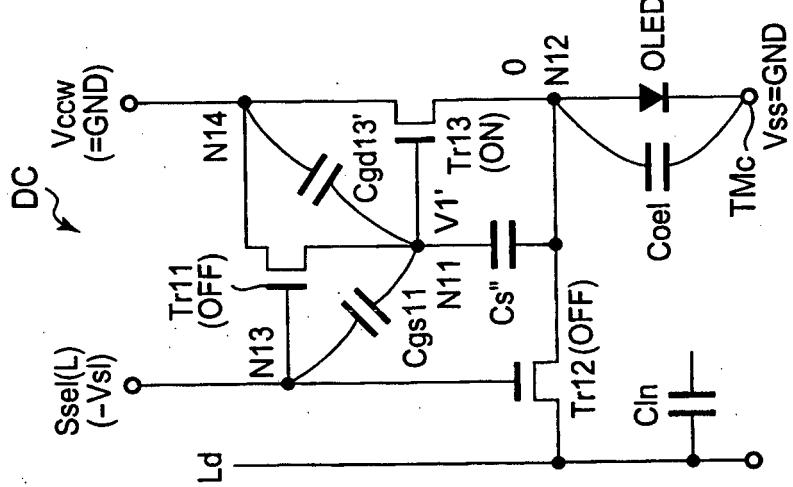

Fig. 26A illustrates an equivalent circuit including a capacity component parasitic on the pixel driving circuit;

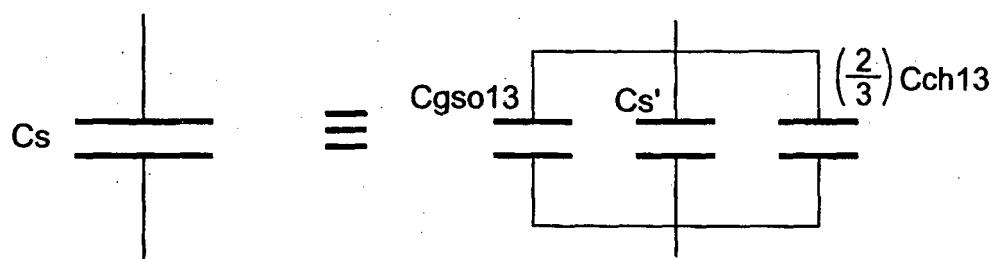

Fig. 26B illustrates an equivalent circuit corresponding to the capacity component  $C_s$  shown in Fig. 27A;

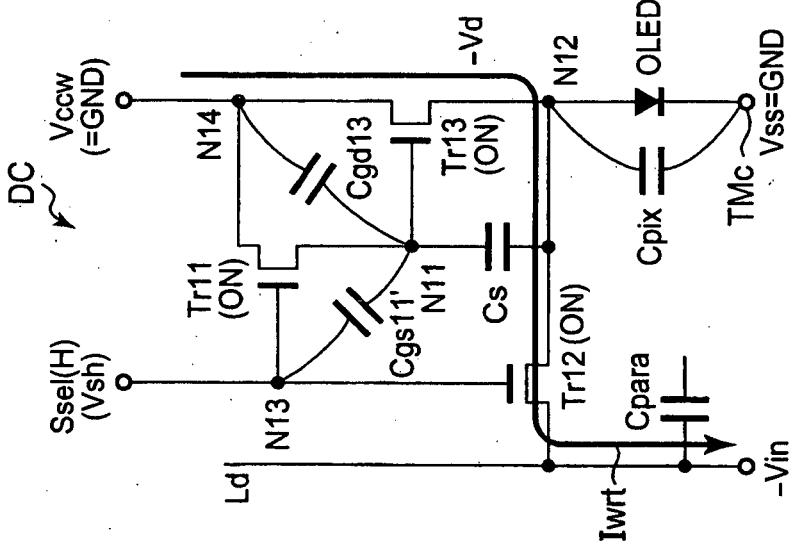

40 Fig. 27A illustrates an equivalent circuit in a writing operation of a display pixel in Embodiment 2 not forming part of the present invention;

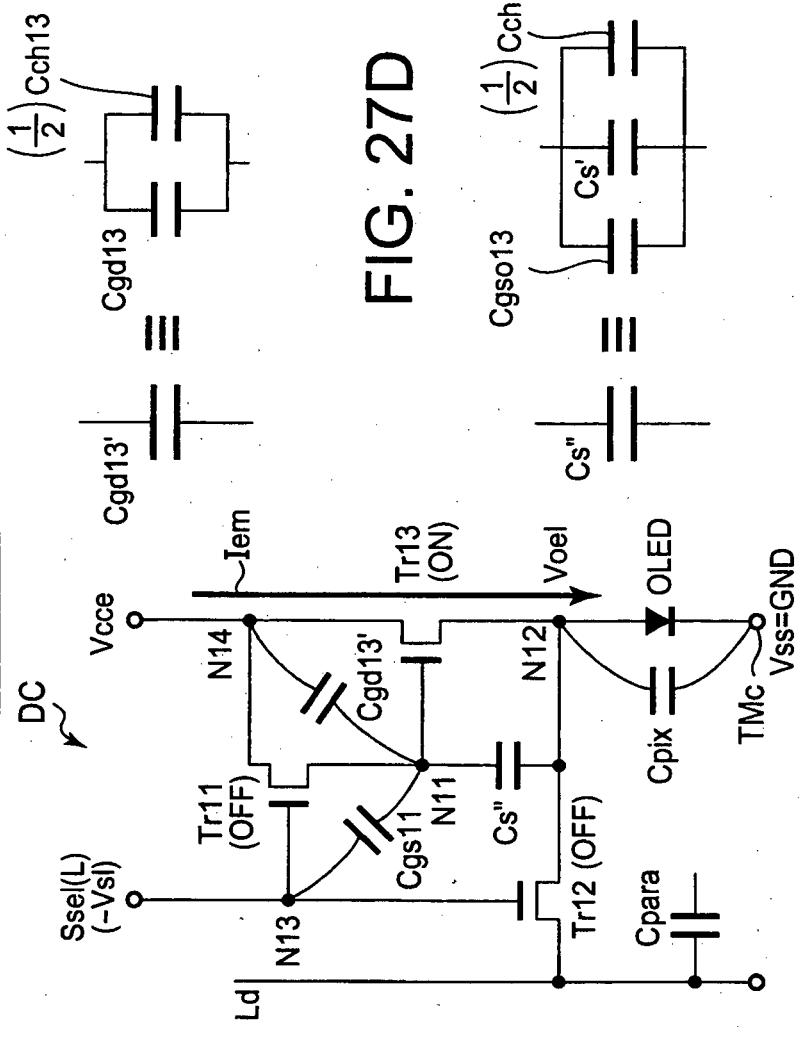

Fig. 27B illustrates an equivalent circuit in a light-emitting operation of a display pixel in Embodiment 2 not forming part of the present invention;

Fig. 27C illustrates an equivalent circuit corresponding to the capacity component  $C_{gd13'}$  shown in Fig. 27B;

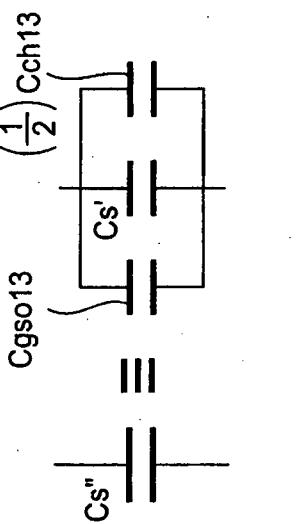

45 Fig. 27D illustrates an equivalent circuit corresponding the capacity component  $C_s''$  shown in Fig. 27B;

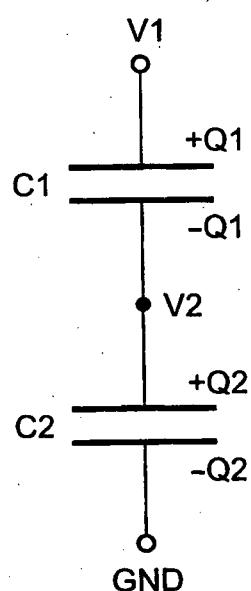

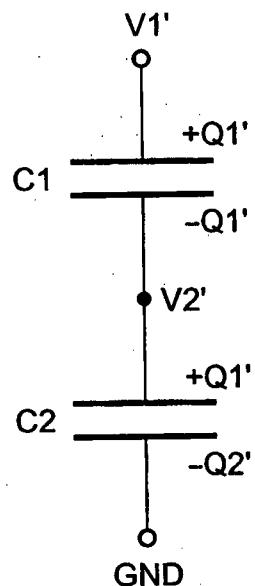

Fig. 28A illustrates the first model for describing law of conservation of charge amount;

Fig. 28B illustrates the second model for describing law of conservation of charge amount;

Fig. 29A illustrates a model for describing a status in which charge is retained in a display pixel when a high level selection signal is applied thereto;

50 Fig. 29B illustrates a model for describing a status in which charge is retained in a display pixel when a low level selection signal is applied thereto;

Fig. 30A illustrates a voltage in the equivalent circuit in a selection step;

Fig. 30B illustrates a voltage in the equivalent circuit in a not-selected status switching step;

Fig. 31A illustrates a voltage change when the selection step (writing operation) shifts to the not-selected status;

55 Fig. 31B illustrates a voltage change in the not-selected status retention step;

Fig. 32A illustrates a voltage in the equivalent circuit of the not-selected status retention step;

Fig. 32B illustrates a voltage in the equivalent circuit of the power source voltage switching step;

Fig. 32C illustrates a voltage in the equivalent circuit of the light-emitting step;

Fig. 33 illustrates a voltage in the equivalent circuit during a writing operation;

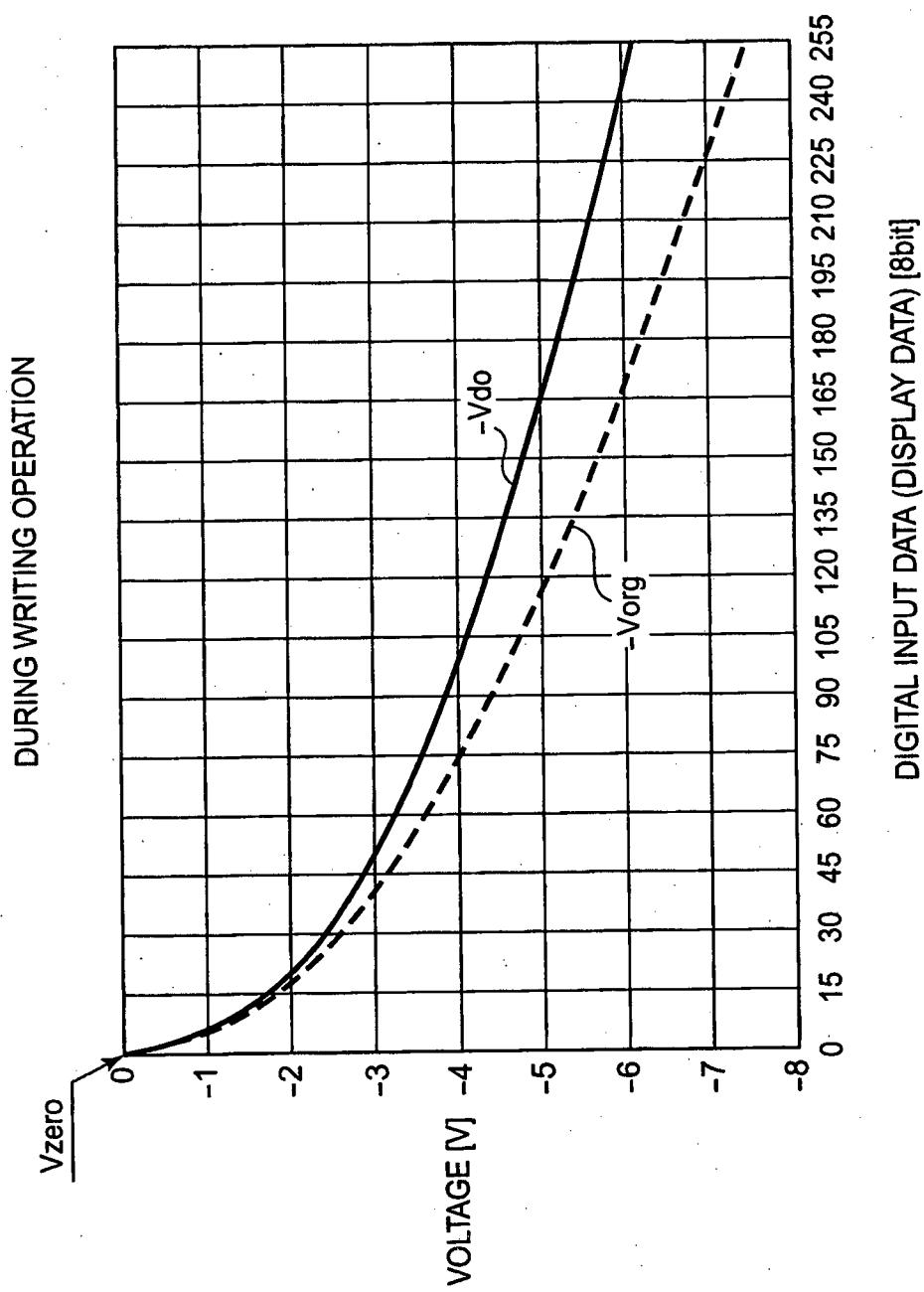

Fig. 34 illustrates a relation between input data and a data voltage and an original gradation level voltage in a writing operation;

Fig. 35 illustrates a relation between input data and a compensated gradation level voltage and a threshold voltage in a writing operation;

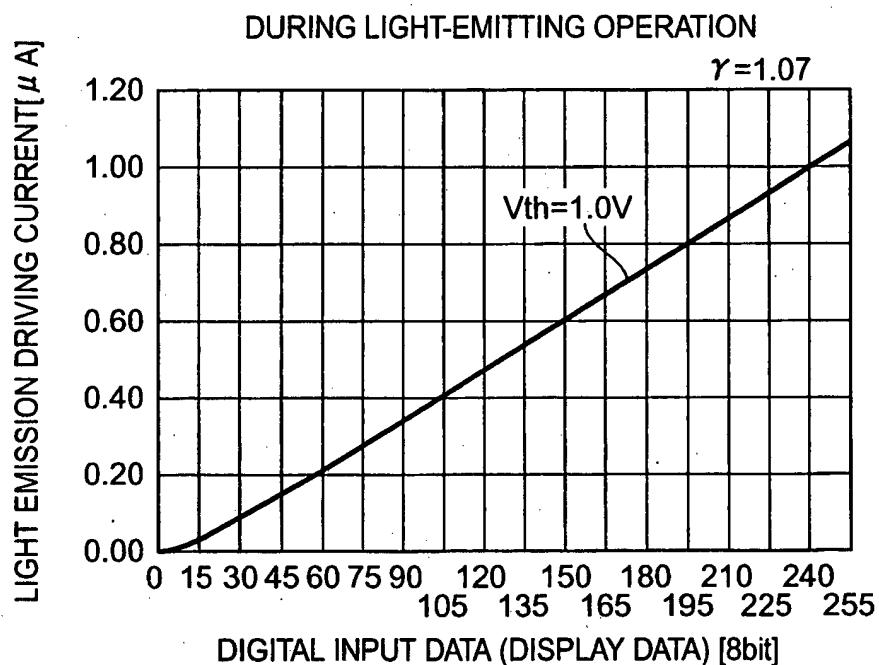

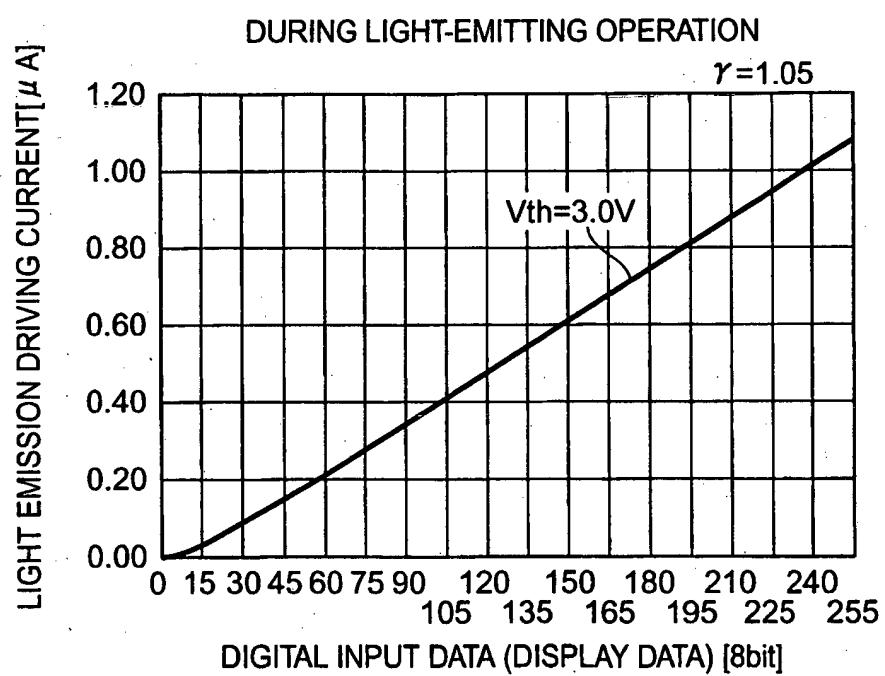

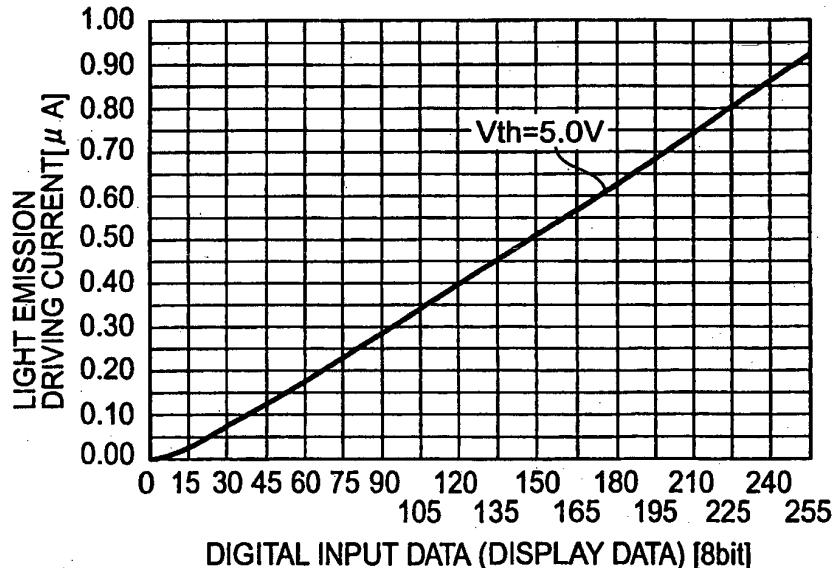

Fig. 36A illustrates the first example of a relation between input data and a light emission driving current and a threshold voltage in a light-emitting operation;

Fig. 36B illustrates the second example of a relation between input data and a light emission driving current and a threshold voltage in a light-emitting operation;

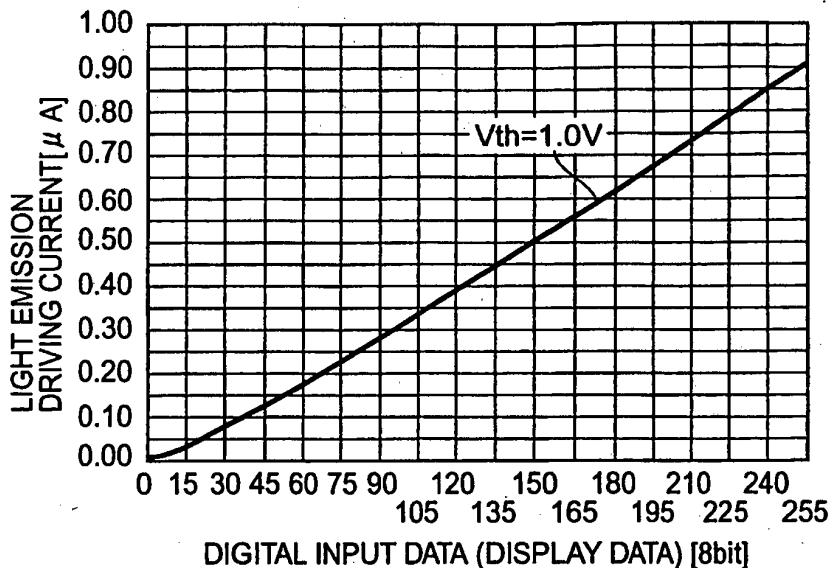

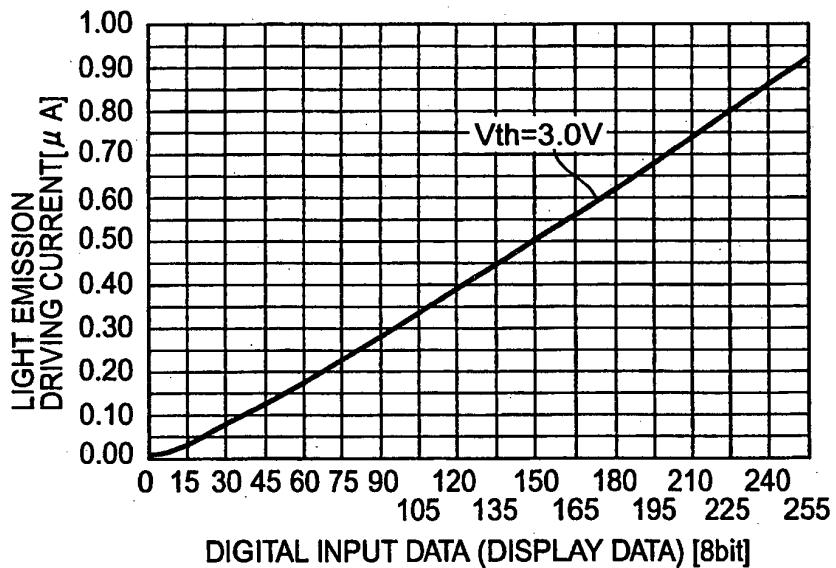

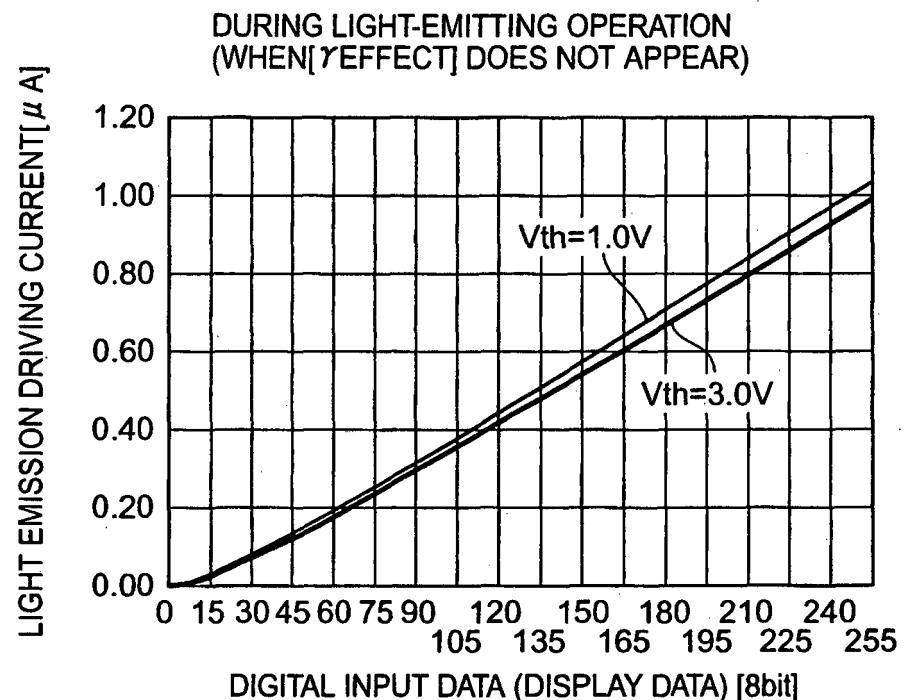

Fig. 37A illustrates the first example of a relation between the input data and the light emission driving current and variation in the threshold voltage in a light-emitting operation;

Fig. 37B illustrates the second example of a relation between the input data and the light emission driving current and variation in the threshold voltage in a light-emitting operation;

Fig. 37C illustrates the third example of a relation between the input data and the light emission driving current and variation in the threshold voltage in a light-emitting operation;

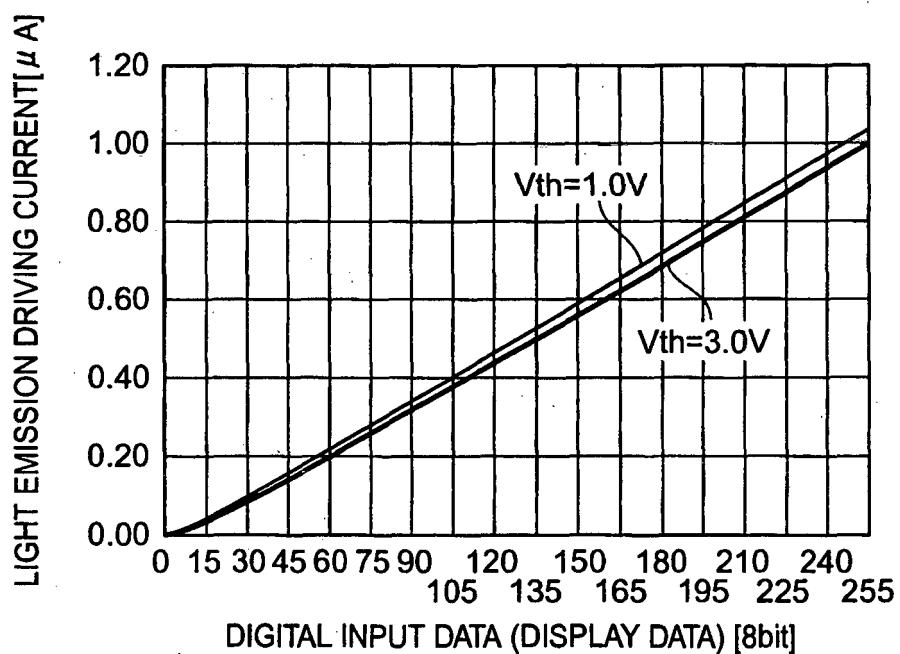

Fig. 38A illustrates the first example of the relation between the input data and the light emission driving current and the threshold voltage when a "y effect" is not provided;

Fig. 38B illustrates the second example of the relation between the input data and the light emission driving current and the threshold voltage when a "y effect" is not provided;

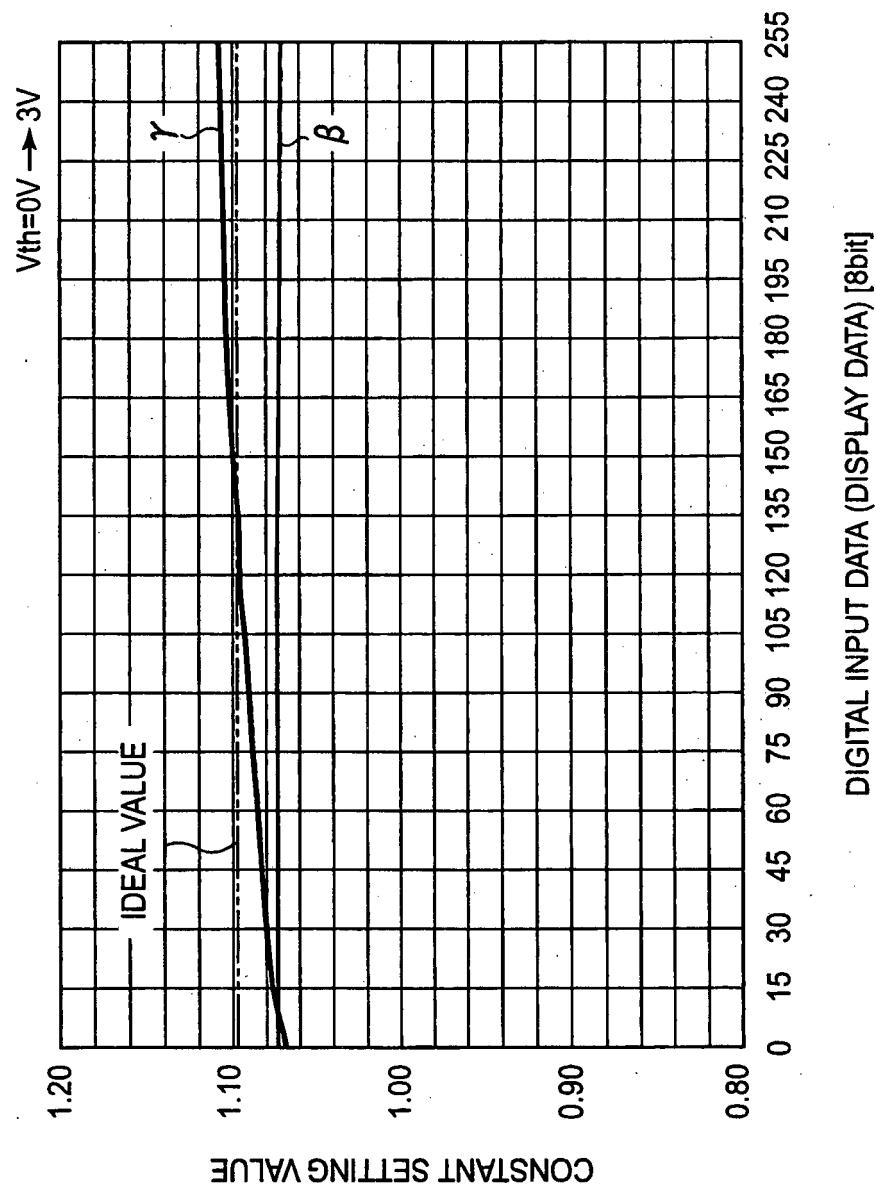

Fig. 39 illustrates a relation between a constant and input data set to cause the effect of the present invention;

Fig. 40 illustrates a relation between a voltage and a current of the organic EL element used for a test for checking the effect of the present invention; and

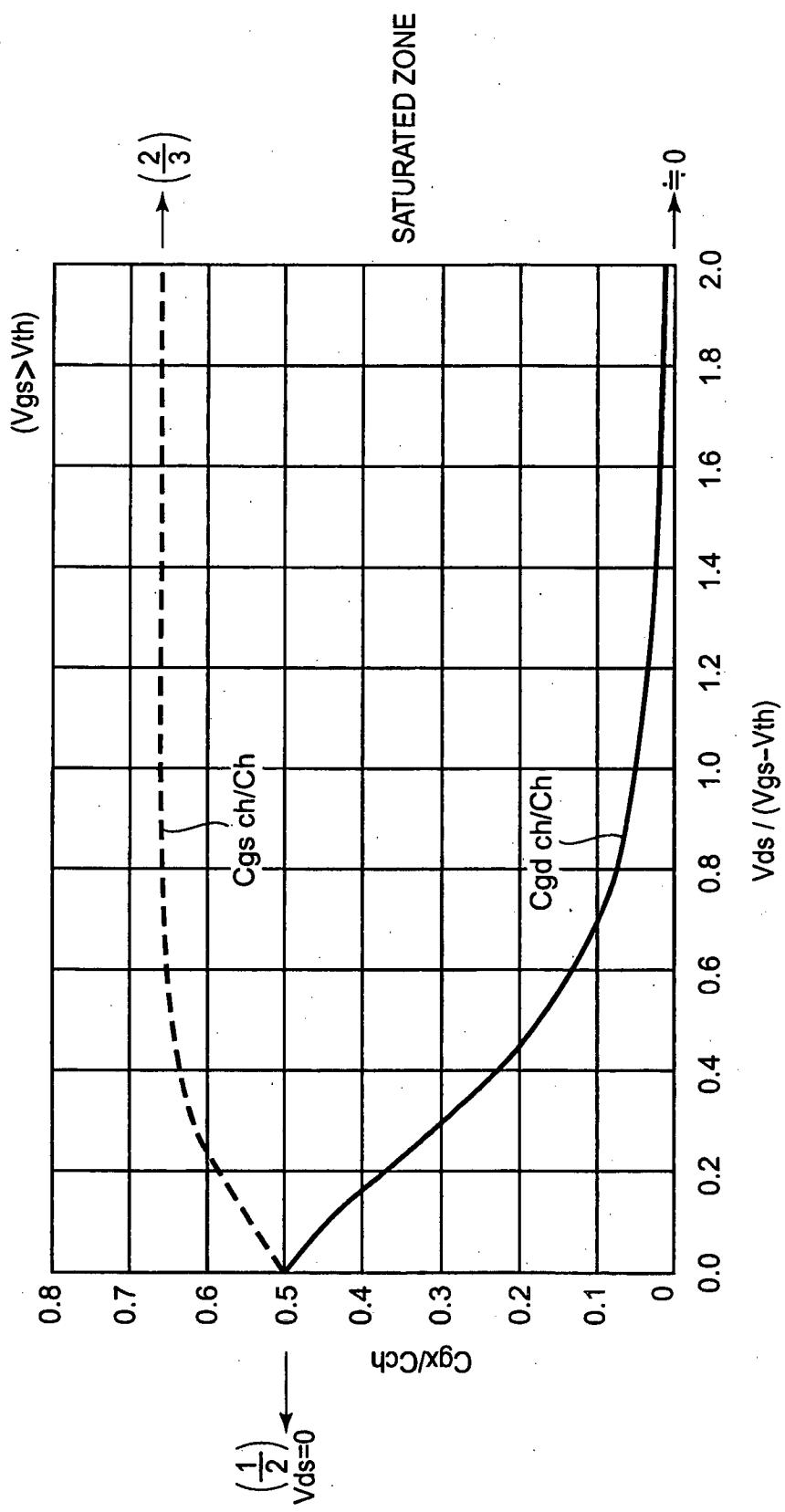

Fig. 41 illustrates a relation between an in-channel parasitic capacitance and a voltage of a transistor used for a display pixel (pixel driving circuit).

#### Best Mode for Carrying Out the Invention

**[0010]** Hereinafter, a display apparatus and a display driving apparatus according to an embodiment of the present invention will be described. This embodiment is an example in which the display apparatus of the present invention is a display apparatus 1 using a current driving-type light-emitting element to display an image. This light-emitting element may be an arbitrary light-emitting element. However, the following will describe a case where the light-emitting element is an organic EL element.

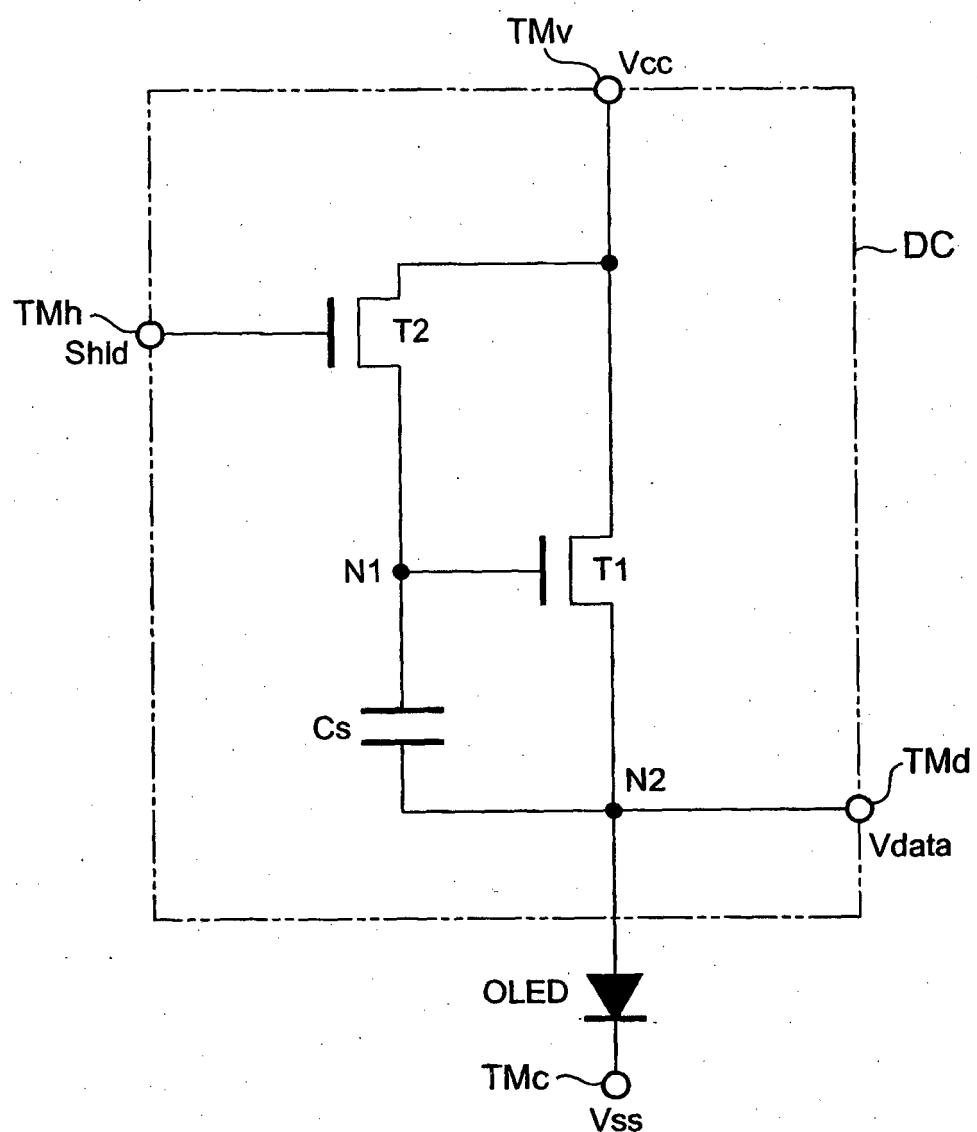

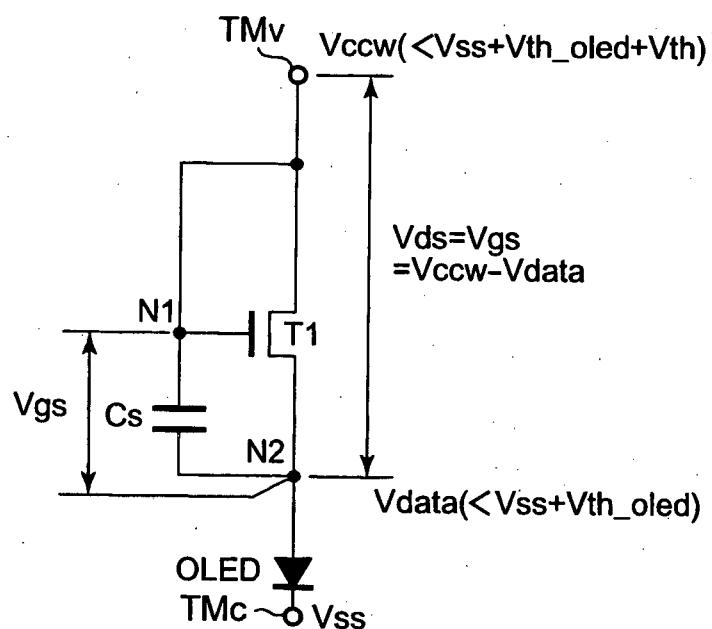

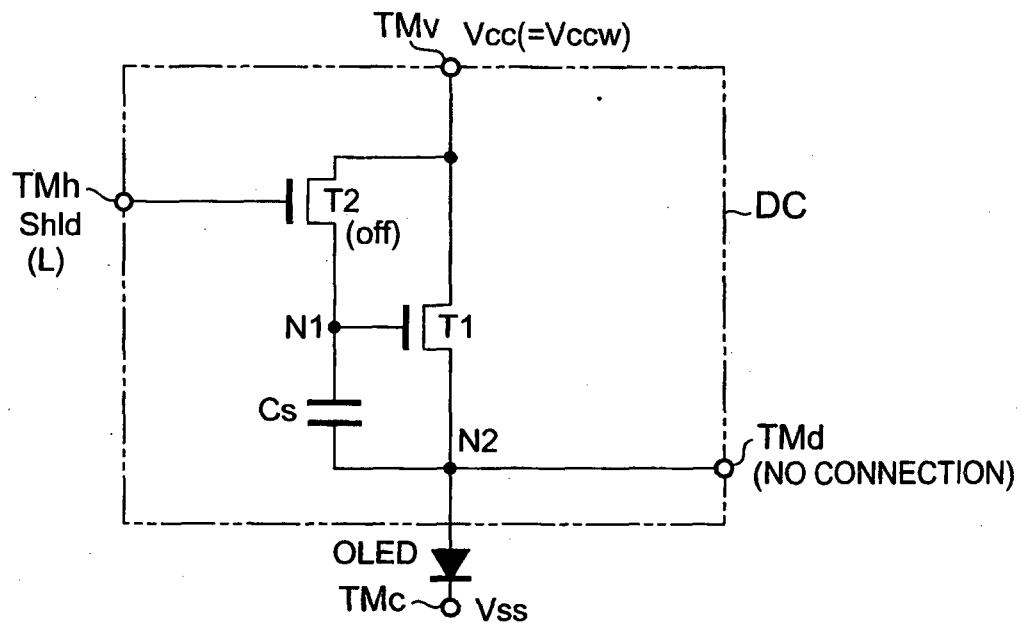

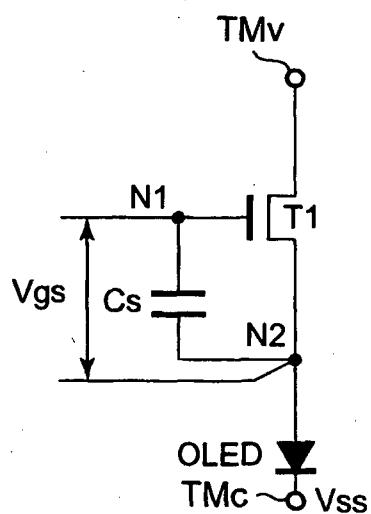

**[0011]** First, a display pixel PIX of the display apparatus 1 of this embodiment will be described. As shown in Fig. 1, the display pixel PIX includes a pixel driving circuit DC and an organic EL element OLED. The pixel driving circuit DC has a transistor T1, a transistor T2, and a capacitor Cs. The transistor T1 and the transistor T2 may have arbitrary element structures and characteristics. However, the following will describe a case where the transistor T1 and the transistor T2 are n channel-type thin film transistors.

**[0012]** The transistor T1 is an n channel-type thin film transistor (hereinafter referred to as "driving transistor") for driving the organic EL element OLED to emit light. The driving transistor T1 is structured so that a drain terminal is connected to a power source terminal TMv, a source terminal is connected to a contact point N2, and a gate terminal is connected to a contact point N1. This power source terminal TMv is applied with a power source voltage Vcc having different voltage values depending on an operation status of the pixel driving circuit DC.

**[0013]** The transistor T2 is an n channel-type thin film transistor that is hereinafter referred to as a "retention transistor". The retention transistor T2 is structured so that a drain terminal is connected to the power source terminal TMv (a drain terminal of the driving transistor T1), a source terminal is connected to the contact point N1, and a gate terminal is connected to the control terminal TMh. The control terminal TMh is applied with a retention control signal Shld.

**[0014]** The capacitor Cs is connected between the gate terminal and the source terminal of the driving transistor T1 (between the contact point N1 and the contact point N2). The capacitor Cs may be parasitic capacitance formed between the gate and source terminals of the driving transistor T1 or also may be the parasitic capacitance connected with a capacitative element in parallel thereto.

**[0015]** The organic EL element OLED is an organic EL element that emits light with a gradation level depending on supplied current. The organic EL element OLED is structured so that an anode terminal is connected to the contact point N2 and a cathode terminal TMc is applied with a reference voltage Vss. This reference voltage Vss has a fixed value. A data terminal TMD is connected to the contact point N2 is applied with a data voltage Vdata corresponding to the gradation level value of display data.

**[0016]** Next, a method for controlling the display pixel PIX having the above structure will be described.

**[0017]** The pixel driving circuit DC applies a voltage corresponding to the gradation level value of display data to the capacitor Cs to charge the capacitor Cs (hereinafter referred to as a "writing operation"). After the writing operation, the

capacitor Cs retains the written voltage (hereinafter referred to as a "retention operation"). Based on the charging voltage retained by the capacitor Cs, gradation level current corresponding to the gradation level of the display data flows in the organic EL element OLED and the organic EL element OLED emits light (hereinafter referred to as a "light-emitting operation"). The brightness of the light emitted by the organic EL element OLED corresponds to the gradation level of the display data.

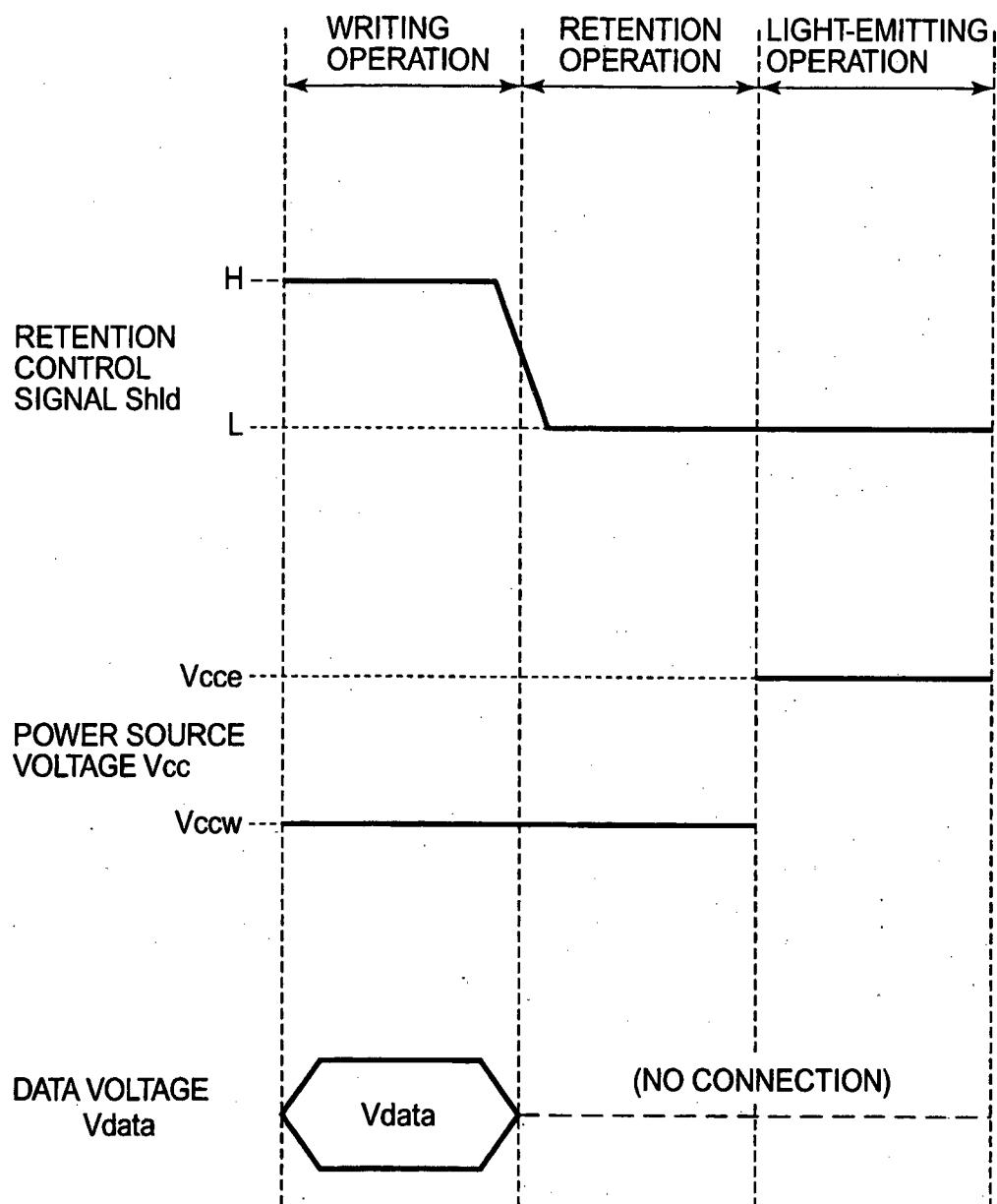

[0018] As shown in Fig. 2, the pixel driving circuit DC sequentially performs the above-described writing operation, retention operation, and light-emitting operation. The following will describe conditions required for the display pixel PIX to perform the respective operations.

10 (Writing operation)

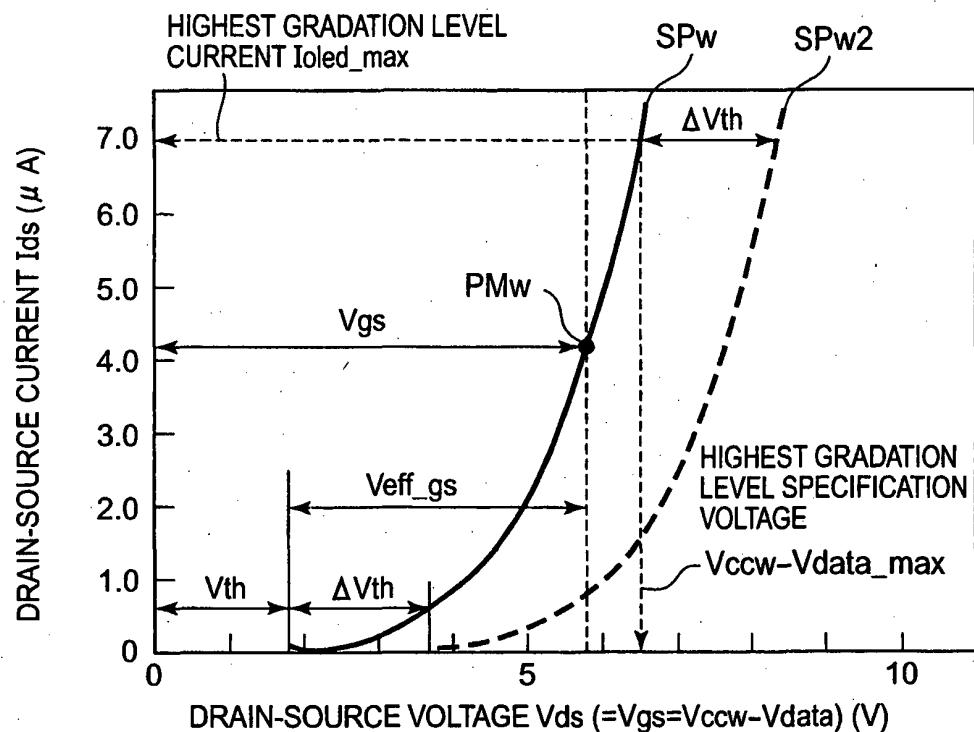

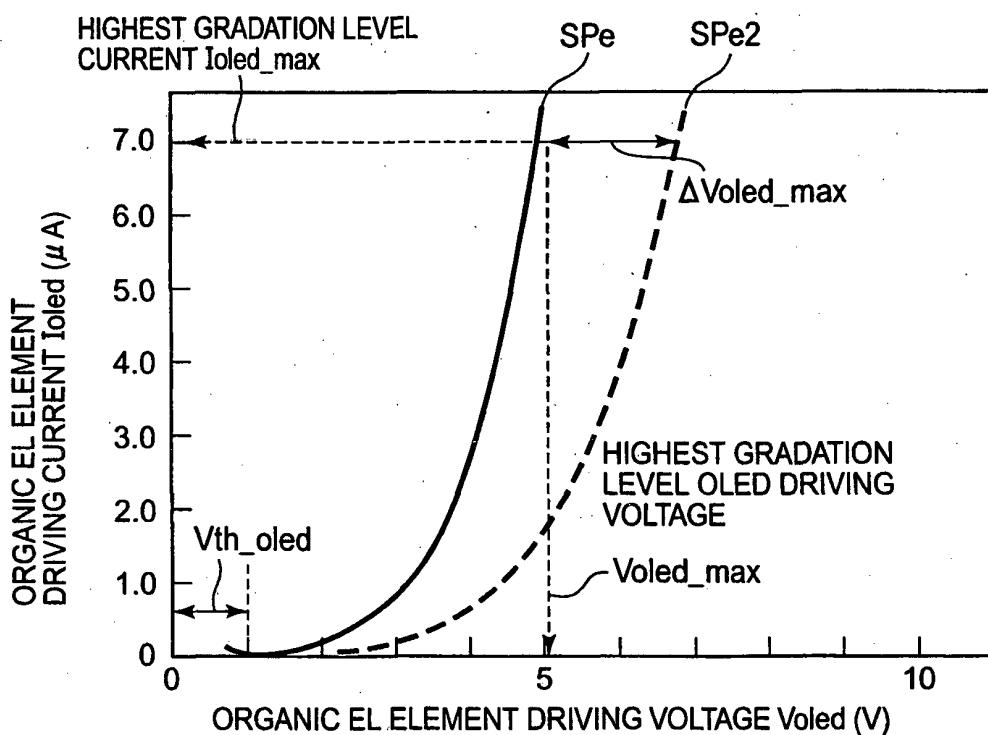

[0019] In the writing operation, the capacitor Cs is written with a voltage corresponding to the gradation level value of the display data. During the writing operation, the organic EL element OLED is in a light-off status in which the organic EL element OLED does not emit light. During the writing operation by the pixel driving circuit DC, the driving transistor T1 shows an operating characteristic illustrated in Fig. 4A,

[0020] In Fig. 4A, a characteristic line SPw, shown by a solid line, shows a relation between the drain-source voltage Vds and a drain-source current Ids in an initial state in which the n channel-type thin film transistor used as the driving transistor T1 is diode-connected. A point PMw on the characteristic line SPw is an operation point of the driving transistor T1. A characteristic line SPw2 shown by a broken line in Fig. 4A, shows a relation between the drain-source voltage Vds and the drain-source current Ids when the driving transistor T1 has a characteristic change due to its driving history. As shown in Fig. 4A, the drain-source voltage Vds is a sum of a threshold voltage Vth and a voltage Veff\_gs, as shown in the following formula (1).

25

$$V_{ds} = V_{th} + V_{eff\_gs} \quad (1)$$

[0021] When the drain-source voltage Vds exceeds the threshold voltage Vth (a threshold voltage between a gate and a source = a threshold voltage between a drain and a source), the drain-source current Ids nonlinearly increases with an increase of the drain-source voltage Vds as shown by the characteristic line SP2. Thus, Veff\_gs in Fig. 4A represents a voltage effectively forming the drain-source current Ids.

[0022] During the writing operation shown in Fig. 2, the driving current and the driving voltage of the organic EL element OLED show the characteristic shown in Fig. 4B. In Fig. 4B, the characteristic line SPe shown by the solid line shows a relation in an initial state between a driving voltage Voled applied between an anode and a cathode of the organic EL element OLED and a driving current Ioled flowing between the anode and the cathode. When the driving voltage Voled exceeds the threshold voltage Vth\_oled, the driving current Ioled nonlinearly increases with an increase of the driving voltage Voled as shown by the characteristic line SPe. In Fig. 4B, a characteristic line SPe2 represents an example of a relation between the driving voltage Voled and the driving current Ioled when the characteristic changes in accordance with the driving history of the organic EL element OLED.

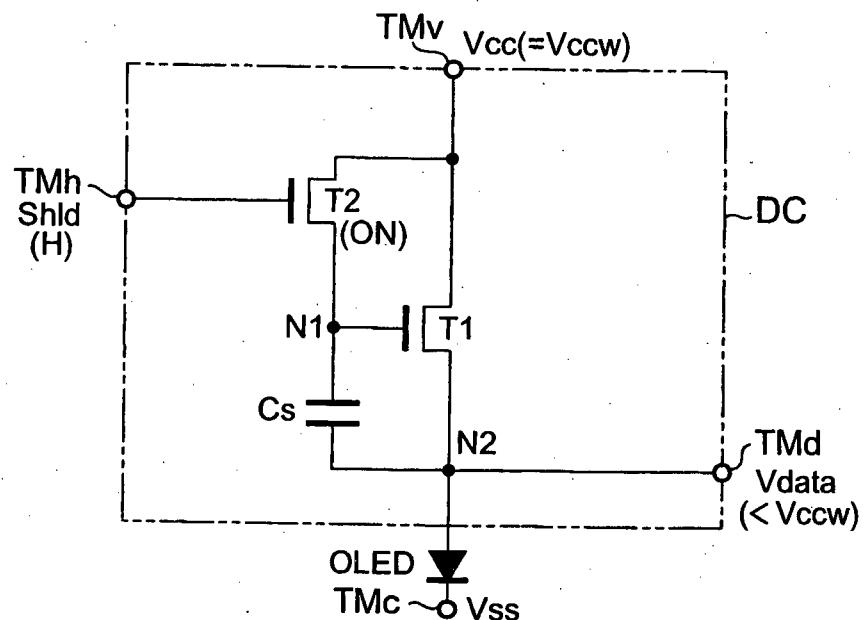

[0023] As shown in Fig. 3A, during the writing operation, the control terminal TMh of the retention transistor T2 is applied with a retention control signal Shld of an ON-level (high level H) to turn ON the retention transistor T2. As a result, the connection (short-circuiting) between the gate and the drain of the driving transistor T1 is established to cause the driving transistor T1 to be in a diode-connected state. The power source terminal TMv is applied with the first power source voltage Vccw for a writing operation and the data terminal TMD is applied with a data voltage Vdata corresponding to the gradation level value of the display data.

[0024] Then, the drain and source of the driving transistor T1 have therebetween current Ids corresponding to the potential difference between the drain and the source (Vccw - Vdata) (hereinafter referred to as "expected value current"). The data voltage Vdata is set to include this expected value current Ids as a voltage value required for obtaining a current value that is required for the organic EL element OLED to emit light with an appropriate brightness depending on the gradation level value of the display data. At this timing, as mentioned above short-circuiting is caused between the gate and the drain of the driving transistor T1 and the drain of the driving transistor T1 is in a diode-connected status. Thus, as shown in Fig. 3B, the drain-source voltage Vds of the driving transistor T1 equals the gate-source voltage Vgs and is represented by the following formula (2). It is noted that the capacitor Cs is written (or charged) with this gate-source voltage Vgs.

55

$$V_{ds} = V_{gs} = V_{ccw} - V_{data} \quad (2)$$

5 [0025] Next, the first power source voltage  $V_{ccw}$  will be described. The driving transistor T1 is an n channel-type transistor. Thus, in order to flow the drain-source current  $I_{ds}$  of the driving transistor T1 the gate potential must be higher than the source potential (positive potential). As shown in Fig. 3B, the gate potential equals the drain potential (the first power source voltage  $V_{ccw}$ ) and the source potential equals the data voltage  $V_{data}$ . Thus, to flow the drain-source current  $I_{ds}$ , the following formula (3) must be established.

$$V_{data} < V_{ccw} \quad (3)$$

10 [0026] In order for the organic EL element OLED to be in a light-off state, a difference between a voltage of the anode terminal of the organic EL element OLED and a voltage of the cathode terminal  $T_{Mc}$  must be equal to or less than the light-emitting threshold voltage  $V_{th\_oled}$  of the organic EL element OLED. As shown in Fig. 3B, the contact point N2 is connected to the anode terminal of the organic EL element OLED. The contact point N2 is connected to the data terminal  $T_{Md}$  and is applied with the data voltage  $V_{data}$ . On the other hand, the cathode terminal  $T_{Mc}$  is applied with the reference voltage  $V_{ss}$  having a fixed value.

15 [0027] Therefore, in order to cause the organic EL element OLED to be in a light-off state in the writing operation, a difference between the data voltage  $V_{data}$  and the reference voltage  $V_{ss}$  must be equal to or less than the light-emitting threshold voltage  $V_{th\_oled}$  of the organic EL element OLED. In this case, the contact point N2 has the potential  $V_{data}$ ; therefore the following formula (4) must be satisfied in order for the organic EL element OLED to be in a light-off state during the writing operation. It is noted that, when the reference voltage  $V_{ss}$  is set to a ground potential of 0V, the formula (4) can be represented by the following formula (5).

$$V_{data} - V_{ss} = V_{th\_oled} \quad (4)$$

25 [0028] Thus, in order to cause the capacitor  $C_s$  to be written with the gate-source voltage  $V_{gs}$  of the driving transistor T1 and to cause the organic EL element OLED not to emit light off during a writing operation, a relation shown in the following formula (6) based on the above-described formula (2) and formula (5) must be established.

$$V_{ccw} - V_{gs} = V_{th\_oled} \quad (6)$$

30 [0029] Then, the relation of the formula (1) established for the gate-source voltage  $V_{gs}$  when the driving transistor  $T_{r1}$  is diode-connected ( $V_{gs} = V_{ds} = V_{th} + V_{eff\_gs}$ ) is substituted into the formula (6) to provide the following formula (7).

$$V_{ccw} = V_{th\_oled} + V_{th} + V_{eff\_gs} \quad (7)$$

40 [0030] When voltage  $V_{eff\_gs} = 0$  is established at which the drain-source current  $I_{ds}$  is formed, the formula (7) is represented by the following formula (8). As shown by this formula (8), during a writing operation, the first power source voltage  $V_{ccw}$  at a writing level must have a value that is equal to or lower than the sum of the light-emitting threshold voltage  $V_{th\_oled}$  and the threshold voltage  $V_{th}$  of the driving transistor T1 (a gate-source threshold voltage=a drain-source threshold voltage).

$$V_{ccw} = V_{th\_oled} + V_{th} \quad (8)$$

50 [0031] Generally, the characteristic of the driving transistor T1 of Fig. 4A and the characteristic of the organic EL element shown in Fig. 4B change in accordance with the driving history. The following will describe an influence of the change in the characteristic of the driving transistor T1 and the organic EL element OLED in accordance with the driving history in a writing operation.

55 [0032] First, the characteristic of the driving transistor T1 will be described. As shown in Fig. 4A, the threshold voltage  $V_{th}$  of the driving transistor T1 in the initial state increases in accordance with the driving history, by a threshold voltage change amount  $\Delta V_{th}$ . When the threshold voltage varies in accordance with the driving history, the characteristic line

becomes a characteristic line SPw2 line obtained by substantially translating the initial characteristic line SPw to a higher voltage side. In this case, in order to obtain gradation level current (drain-source current  $I_{ds}$ ) in accordance with the gradation level value of the display data, the data voltage  $V_{data}$  must be increased by the threshold voltage change amount  $\Delta V_{th}$ .

**[0033]** Next, the following will describe an influence of the change in the characteristic of the organic EL element OLED during a writing operation. Generally, the organic EL element has resistance that increases in accordance with the driving history. As shown in Fig. 4B, in the characteristic line SPe2 after a change in the resistance of the organic EL element OLED, a rate at which the driving current  $I_{oled}$  increases with regards to an increase in the driving voltage  $V_{oled}$  (increase rate) decreases when compared with the initial characteristic line SPe before the resistance change.

**[0034]** In order to allow the organic EL element OLED to emit light with an appropriate brightness depending on the gradation level value of the display data even when the resistance is high, the driving current  $I_{oled}$  in accordance with the gradation level value must be supplied to the organic EL element OLED. In order to supply such a driving current  $I_{oled}$ , the driving voltage  $V_{oled}$  must be increased by a difference between the voltage corresponding to the necessary driving current  $I_{oled}$  for the gradation level in the characteristic line SPe2 and the voltage corresponding to the necessary driving current  $I_{oled}$  for the gradation level in the characteristic line SPe. It is noted that this difference voltage reaches the maximum value  $\Delta V_{oled\_max}$  when the driving current  $I_{oled}$  is the maximum value  $I_{oled\_max}$ . When the writing operation is completed to satisfy the above-described conditions, the display pixel PIX carries out a retention operation.

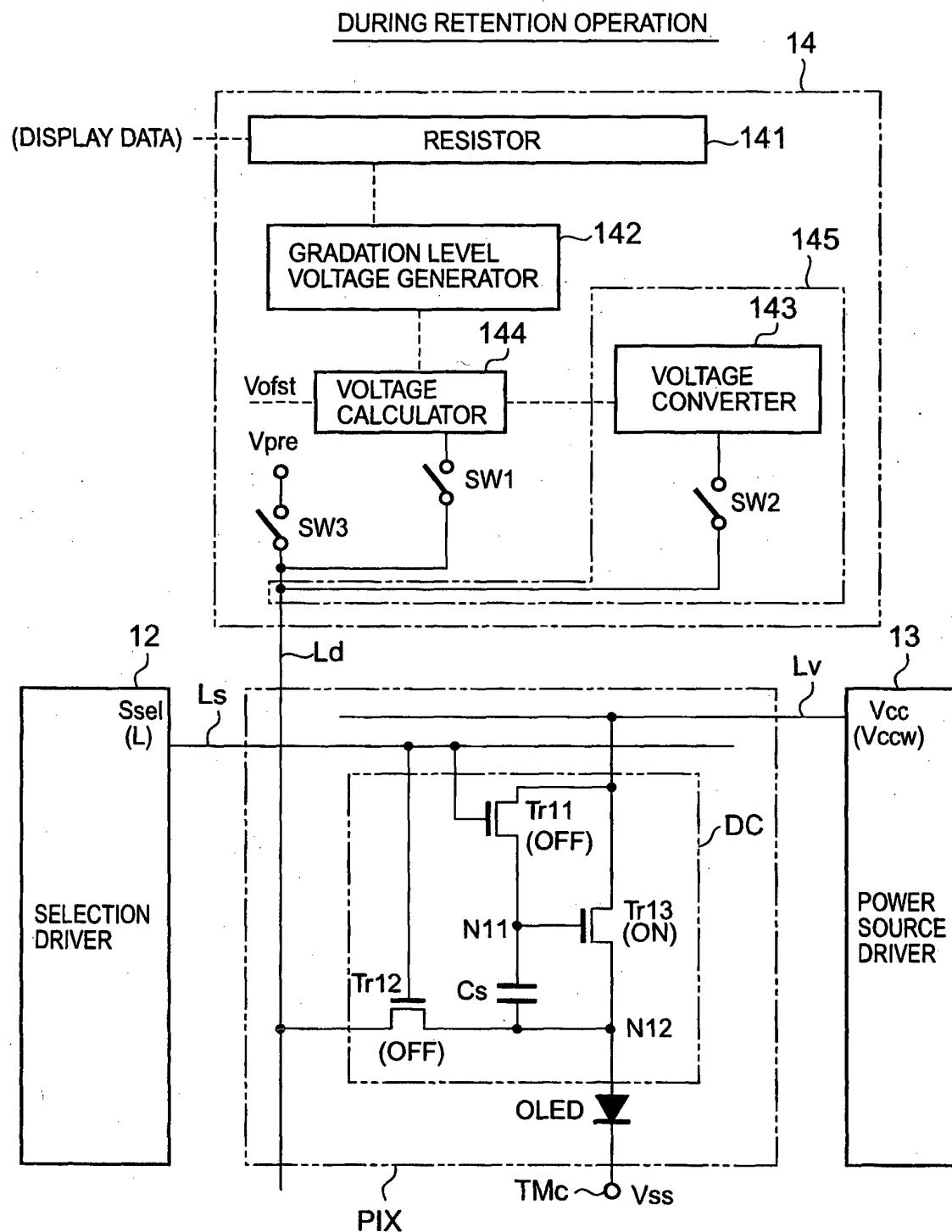

(Retention operation)

**[0035]** During the retention operation, as shown in Fig. 5A, the control terminal TMh is applied with the retention control signal Shld of an OFF level (low level L). As a result, the retention transistor T2 is turned OFF to block electric connection between the gate and the drain of the driving transistor T1. Thus, the diode connection of the driving transistor T1 is cancelled to stop the charging of the capacitor Cs. As shown in Fig. 5B, the capacitor Cs retains the drain-source voltage  $V_{ds}$  of the driving transistor T1 (=gate-source voltage  $V_{gs}$ ) charged during the writing operation.

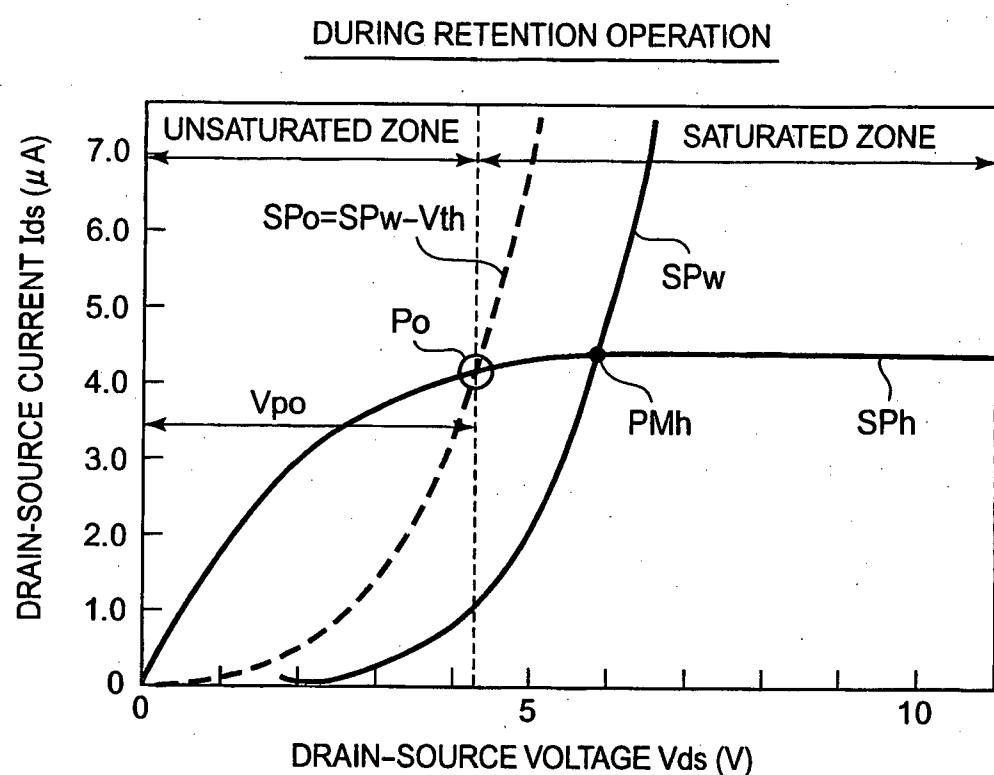

**[0036]** The relation between the drain-source voltage  $V_{ds}$  and the drain-source current  $I_{ds}$  when the diode connection of the driving transistor T1 is cancelled follows the characteristic line SPh shown by the solid line in Fig. 6. The gate-source voltage  $V_{gs}$  in this case is maintained to have a fixed value (e.g., a value of a voltage retained by the capacitor Cs during the retention operation).

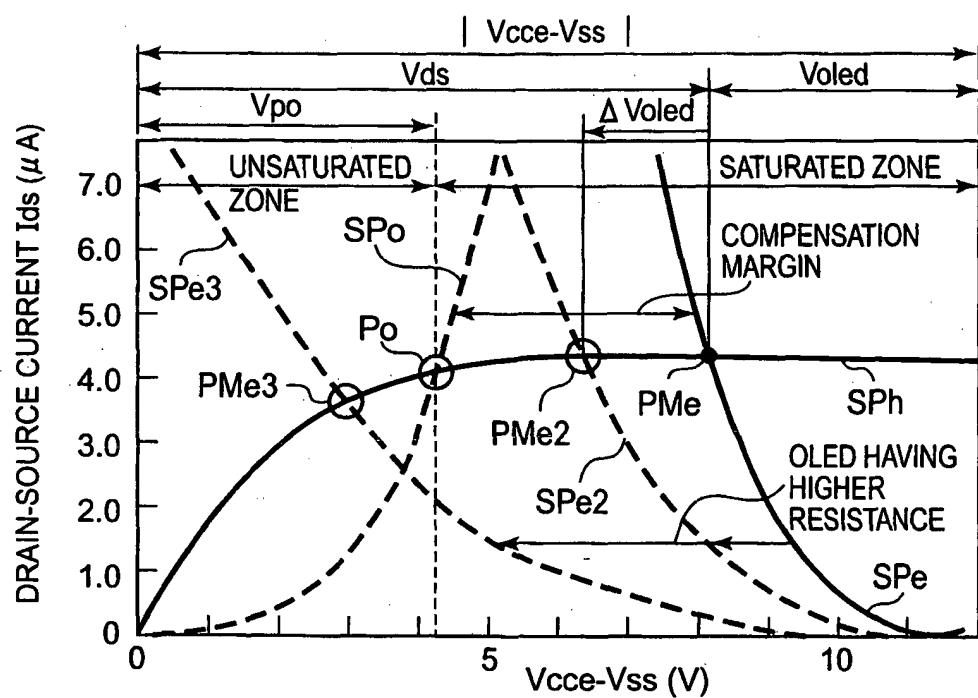

**[0037]** The characteristic line SPw in Fig. 6 is substantially the same as the characteristic line SPw during the writing operation shown in Fig. 4A and shows the characteristic when the driving transistor T1 is diode-connected. An intersecting point of the characteristic line SPh and the characteristic line SPw is at the operation point PMh during the retention. The characteristic line SPo in Fig. 6 is obtained by deducting the threshold voltage  $V_{th}$  from the voltages  $V_{gs}$  of the characteristic line SPw. At the intersecting point Po of the characteristic line SPo and the characteristic line SPh, the drain-source voltage  $V_{ds}$  has a pinch-off voltage  $V_{po}$ .

**[0038]** When the driving transistor T1 operates in accordance with the characteristic line SPh, a zone within which the drain-source voltage  $V_{ds}$  changes from 0V to a pinch-off voltage  $V_{po}$  is an unsaturated zone. In the unsaturated zone, the drain-source current  $I_{ds}$  increases with an increase of the drain-source voltage  $V_{ds}$ . A zone within which the voltage  $V_{ds}$  is equal to or higher than the pinch-off voltage  $V_{po}$  is a saturated zone. In the saturated zone, there is substantially no change in the drain-source current  $I_{ds}$  even when the drain-source voltage  $V_{ds}$  increases.

**[0039]** It is noted that the retention control signal Shld may be switched from an ON-level to an OFF level when the power source voltage  $V_{cc}$  is switched from the first power source voltage  $V_{ccw}$  for a writing operation to the second power source voltage  $V_{cce}$  for a light-emitting operation (when the retention operation is switched to the light-emitting operation). When the retention operation is completed in the manner described above, the display pixel PIX carries out a light-emitting operation.

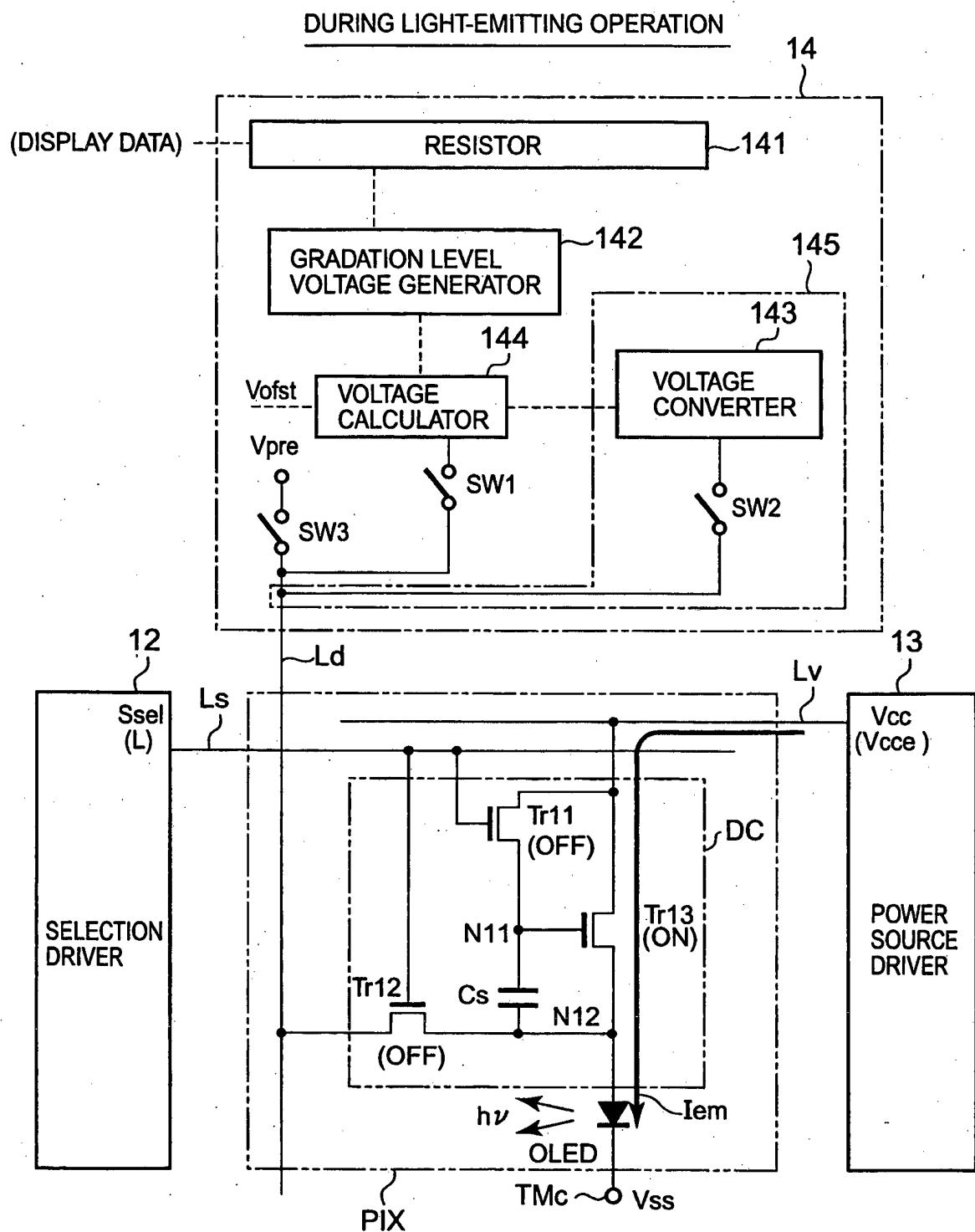

(Light-emitting operation)

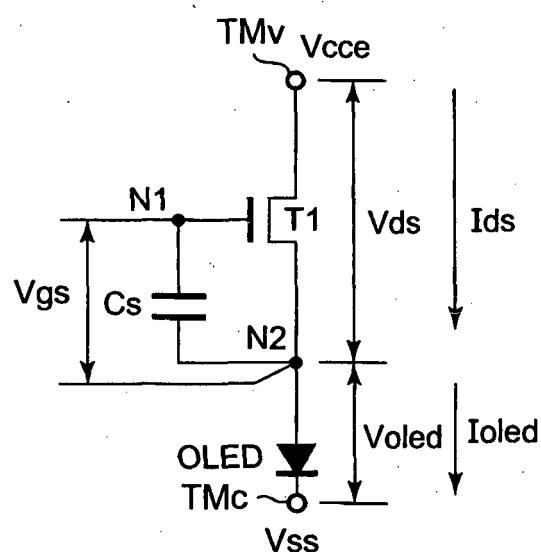

**[0040]** As shown in Fig. 7A, during a light-emitting operation, after the above-described retention operation, such that the diode connection of the driving transistor T1 remains cancelled. The power source terminal TMv is applied with the second power source voltage  $V_{cce}$  for a light-emitting operation as the terminal voltage  $V_{cc}$  instead of the first power source voltage  $V_{ccw}$  for a writing operation. This second power source voltage  $V_{cce}$  has a higher potential than that of the first power source voltage  $V_{ccw}$ .

**[0041]** As a result, as shown in Fig. 7B, the current  $I_{ds}$  in accordance with the value of the gate-source voltage  $V_{gs}$  flows between the drain and source of the driving transistor T1. This current  $I_{ds}$  is supplied to the organic EL element OLED to allow the organic EL element OLED to emit light with a brightness in accordance with the value of the current  $I_{ds}$ . During the light-emitting operation, the current  $I_{ds}$  can be maintained at a fixed level by maintaining the gate-source voltage  $V_{gs}$  at a fixed level. Thus, a voltage retained by the capacitor Cs (a voltage applied to the capacitor Cs from a

retention operation period to a light-emitting operation period) may be applied between the gate and the source for example.

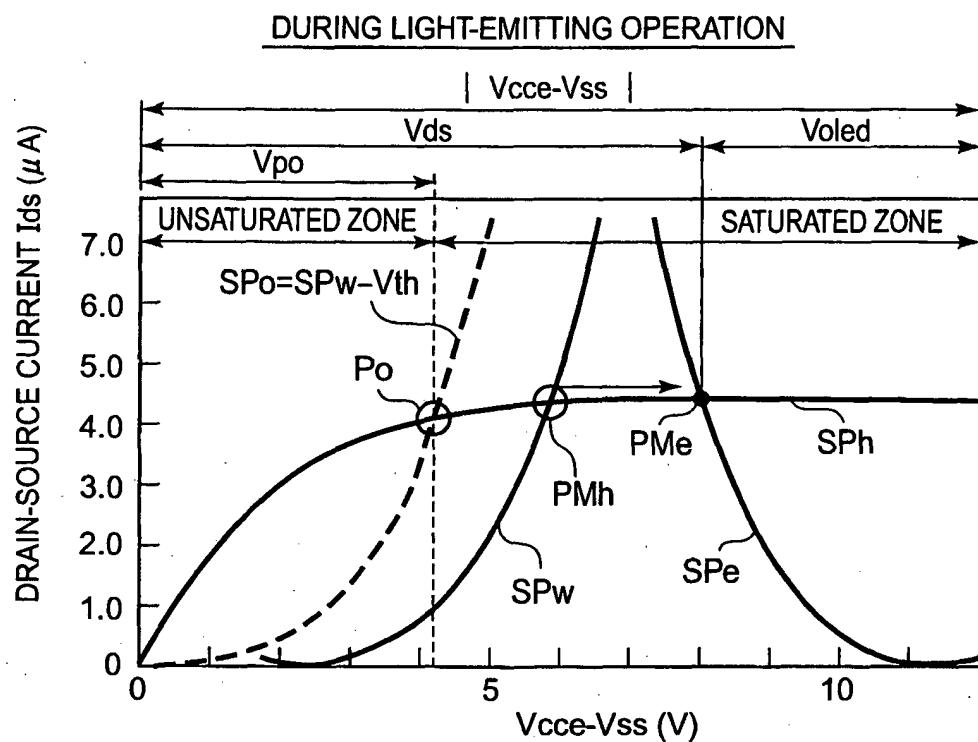

[0042] During the light-emitting operation, when the gate-source voltage  $V_{gs}$  is fixed, the organic EL element OLED operates based on a load line  $SPe$  shown by the solid line in Fig. 8A. The load line  $SPe$  represents an inverted relation between the driving voltage  $V_{oled}$  and the driving current  $I_{oled}$  of the organic EL element OLED with regards to a value of a potential difference ( $V_{cce} - V_{ss}$ ) between the power source terminal  $TMv$  and the cathode terminal  $TMc$  of the organic EL element OLED as reference. In Fig. 8A, the characteristic line  $SPh$  is substantially the same as the characteristic line  $SPh$  shown in Fig. 6 during the retention operation.

[0043] As shown in Fig. 8A, when processing proceeds from the retention operation to the light-emitting operation, the operation point of the driving transistor  $T1$  moves from the operation point  $PMh$  during the retention operation to an operation point  $PMe$  during the light-emitting operation (an intersecting point during the retention operation of the characteristic line  $SPh$  and the load line  $SPe$  of the organic EL element OLED). As shown in Fig. 8A, this operation point  $PMe$  is a point at which a potential difference ( $V_{cce} - V_{ss}$ ) between the power source terminal  $TMv$  and the cathode terminal  $TMc$  of the organic EL element is distributed between the drain and the source of the driving transistor  $T1$  and between the anode and the cathode of the organic EL element OLED. Specifically, at the operation point  $PMe$  during the light-emitting operation, the voltage  $V_{ds}$  is applied between the drain and the source of the driving transistor  $T1$  and the driving voltage  $V_{oled}$  is applied between the anode and the cathode of the organic EL element OLED as shown in Fig. 7B.

[0044] When the expected value current  $I_{ds}$  flowing between the drain and the source of the driving transistor  $T1$  during the writing operation is equal to the driving current  $I_{oled}$  supplied to the organic EL element OLED during the light-emitting operation, the organic EL element OLED emits light having a brightness depending on the gradation level value of the display data. To realize this, the operation point  $PMe$  of the driving transistor  $T1$  during the light-emitting operation must be maintained within the saturated zone shown in Fig. 8A.

[0045] On the other hand, the driving voltage  $V_{oled}$  of the organic EL element OLED has the maximum value  $V_{oled\_max}$  when the highest display gradation level is reached. Specifically, in order to allow the organic EL element OLED to emit light with brightness depending on the gradation level value of the display data, the second power source voltage  $V_{cce}$  for a light-emitting operation may be set to satisfy a relation shown in the following formula (9). It is noted that the left-hand side of the formula (9) represents a voltage applied between the above-described power source terminal  $TMv$  and the cathode terminal  $TMc$  of the organic EL element OLED. When the reference voltage  $V_{ss}$  applied to the cathode terminal of the organic EL element OLED is set to have the ground potential of 0V, the formula (9) can be represented by the following formula (10).

$$V_{cce} - V_{ss} = V_{po} + V_{oled\_max} \quad (9)$$

$$V_{cce} = V_{po} + V_{oled\_max} \quad (10)$$

[0046] Next, the following will describe an influence of a change in the characteristic of the organic EL element OLED during the light-emitting operation.

[0047] As shown in Fig. 4B, the organic EL element OLED has higher resistance in accordance with the driving history and as a result the increase rate of the driving current  $I_{oled}$  with respect to the driving voltage  $V_{oled}$  decreases. Then, the load line  $SPe$  of the organic EL element OLED more gently inclines as shown by  $SPe2$  and  $SPe3$  in Fig. 8B. Specifically, the load line of the organic EL element OLED changes in accordance with the driving history to cause a change in the load line from  $SPe$  through  $SPe2$  to  $SPe3$ . As a result, the operation point of the driving transistor  $T1$  changes on the characteristic line  $SPh$  from  $PMe$  through  $PMe2$  to  $PMe3$ .

[0048] When the operation point of the driving transistor  $T1$  exists in the saturated zone ( $PMe$  to  $PMe2$ ), the driving current  $I_{oled}$  maintains a value of the expected value current  $I_{ds}$  during the writing operation. When the operation point exists in the unsaturated zone (when the operating point moves from  $PMe2$  to  $PMe3$ , for example) however, the driving current  $I_{oled}$  decreases and is lower than the expected value current  $I_{ds}$  during the writing operation. The decrease in the driving current  $I_{oled}$  causes the light-emitting element to emit light with a gradation level lower than the brightness corresponding to the gradation level value of the display data.

[0049] In the example of Fig. 8B, the pinch-off point  $Po$  exists at a boundary between the unsaturated zone and the saturated zone. Thus, a potential difference between the operation point  $PMe$  and the pinch-off point  $Po$  during the light-emitting operation functions, when the organic EL element has higher resistance, as a compensation margin for maintaining a driving current  $I_{oled}$  during the light-emitting operation. In other words, a compensation margin corresponding to the current value of the driving current  $I_{oled}$  functions as a potential difference on the characteristic line  $SPh$  between

a pinch-off point trajectory SPo and the load line SPe of the organic EL element. It is noted that the compensation margin decreases with an increase of the driving current  $I_{oled}$ . The compensation margin increases when a voltage increases that is applied between the power source terminal TMv and the cathode terminal TMc of the organic EL element OLED ( $V_{cce} - V_{ss}$ ) increases.

5 [0050] In the above-described illustrative embodiment, a transistor voltage is used to control brightness of the respective light-emitting elements (hereinafter referred to as "voltage gradation level control"). Then, the data voltage  $V_{data}$  is set based on initial characteristics of the previously determined transistor drain-source voltage  $V_{ds}$  and the drain-source current  $I_{ds}$ . However, the data voltage  $V_{data}$  set based on the method as described above causes an increase in the threshold voltage  $V_{th}$  in accordance with the driving history. Thus, the driving current supplied to the light-emitting element fails to correspond to the display data (data voltage) and thus the light-emitting element does not emit light with preferred brightness. When the transistor is an amorphous transistor in particular, the element characteristic remarkably varies.

10 [0051] In an n-channel-type amorphous silicon transistor, a driving history or temporal change causes carrier trap to a gate insulating film. This carrier trap offsets a gate field and the characteristic between the drain-source voltage  $V_{ds}$  and the drain-source current  $I_{ds}$  have an increased threshold voltage  $V_{th}$ . In the example of Fig. 4A, during the writing operation, the threshold voltage  $V_{th}$  shifts from the characteristic SPw in an initial state to the characteristic SPw2 at a higher voltage. When the drain-source voltage  $V_{ds}$  is fixed in this case, the drain-source current  $I_{ds}$  decreases and the light-emitting element has reduced brightness. It is noted that the amorphous transistor in the example shown in Fig. 4A is designed to have a gate insulating film thickness of 300nm (3000Å), a channel width of 500μm, a channel length of 6.28μm, and a threshold voltage of 2.4V.

15 [0052] When the element characteristic of the transistor varies, the threshold voltage  $V_{th}$  mainly increases. After the variation in the element characteristic, the characteristic line SPw2 showing the relation between the drain-source voltage  $V_{ds}$  and the drain-source current  $I_{ds}$  is a substantial translation of the characteristic line SPw in the initial state. Thus, a characteristic substantially corresponding to the varied characteristic line SPw2 can be obtained by adding a fixed voltage (hereinafter referred to as "OFFSET voltage  $V_{ofst}$ ") corresponding to the change amount  $\Delta V_{th}$  of the initial threshold voltage  $V_{th}$  to the drain-source voltage  $V_{ds}$  of the initial characteristic line SPw. Specifically, during an operation for writing the display data to the pixel driving circuit DC, the source terminal of the driving transistor T1 (contact point N2) is applied with a voltage obtained by the drain-source voltage  $V_{ds}$  on the characteristic line SPw with and an OFFSET voltage  $V_{ofst}$  (hereinafter referred to as "compensated gradation level voltage  $V_{pix}$ ").

20 [0053] By doing this, a change in the element characteristic due to the variation in the threshold voltage  $V_{th}$  can be compensated. Specifically, the light emission driving current  $I_{em}$  having a value depending on display data can be supplied to the organic EL element OLED. The organic EL element OLED having received the light emission driving current  $I_{em}$  emits light with brightness in accordance with the display data.

35 (Embodiment 1)

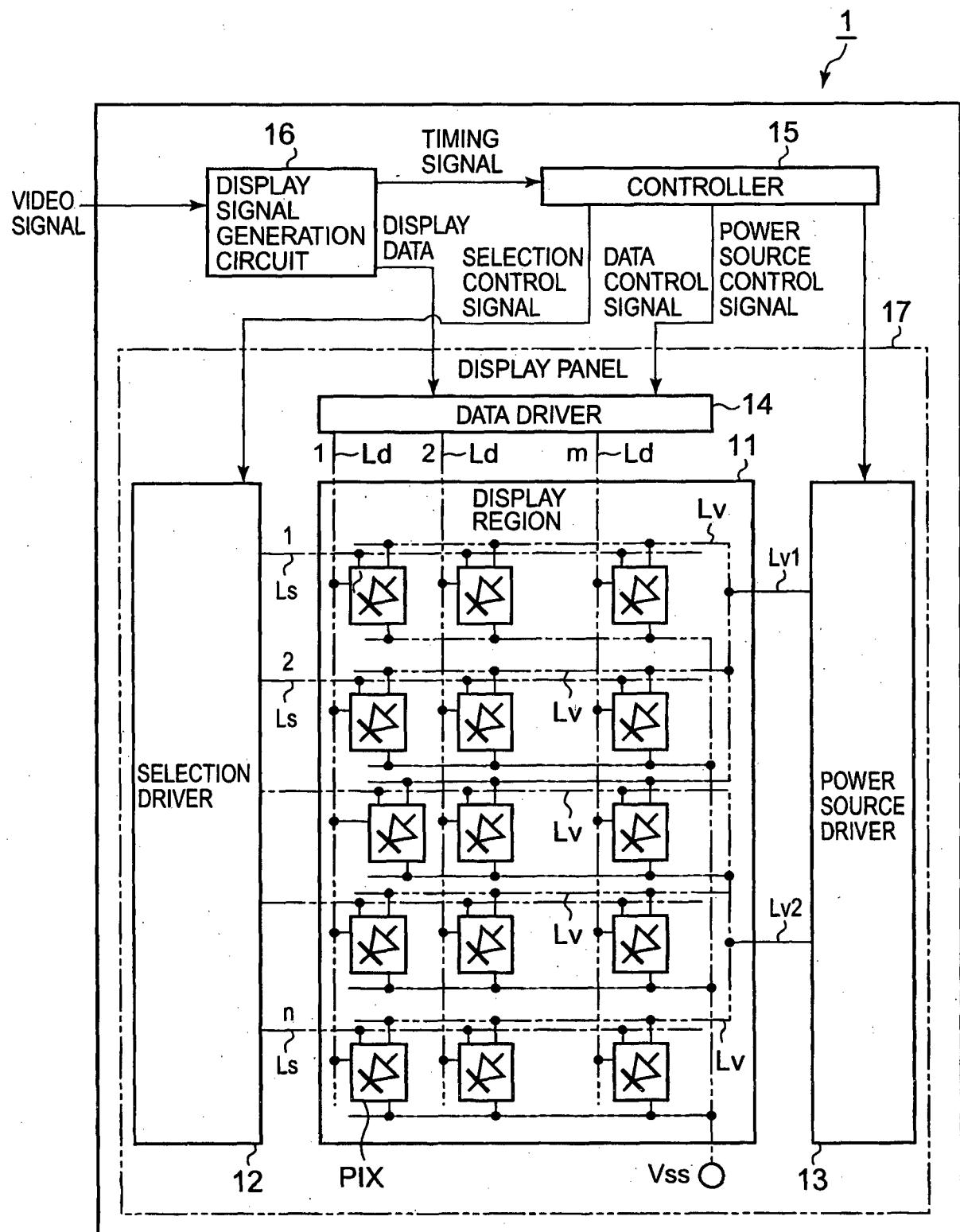

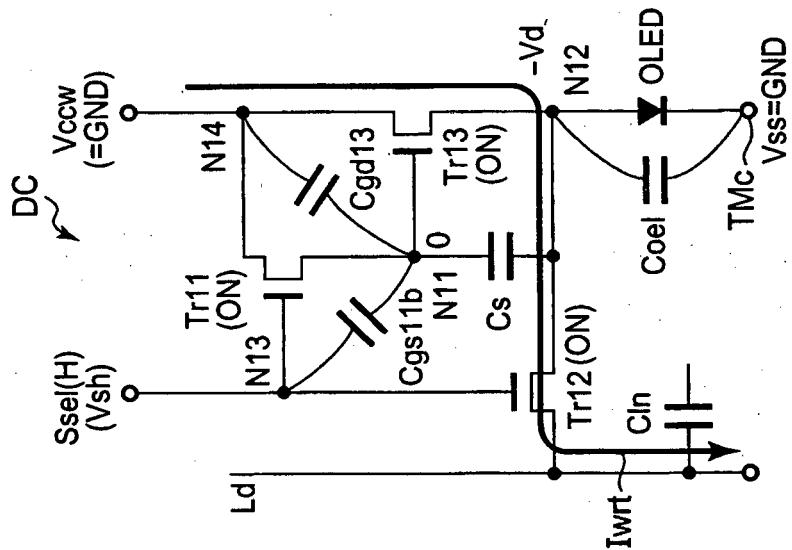

[0054] The following section will describe the display apparatus 1 of Embodiment 1 for displaying an image by the above-described display pixel PIX. First, the structure of the display apparatus 1 will be described. As shown in Fig. 9, the display apparatus 1 includes: a display zone 11; a selection driver 12; a power source driver 13; a data driver (display driving apparatus) 14; a controller 15; a display signal generation circuit 16; and a display panel 17.

40 [0055] The display zone 11 includes: a plurality of selection lines  $L_s$ ; a plurality of data lines  $L_d$ ; and a plurality of display pixels PIX. The respective selection lines  $L_s$  are arranged in the row direction of the display zone 11 (left-and-right direction in Fig. 9). The respective selection lines  $L_s$  are parallel to one another. The respective data lines  $L_d$  are arranged in the column direction of the display zone 11 (up-and-down direction in Fig. 9). The respective data lines  $L_d$  are parallel to one another. The respective display pixels PIX are arranged in the vicinity of the respective intersecting points of the respective selection lines  $L_s$  and the respective data lines  $L_d$  and in a lattice-like manner in "n" rows × "m" columns (n and m are a positive integer).

45 [0056] The selection driver 12 supplies a selection signal  $S_{sel}$  to the respective selection lines  $L_s$  with a predetermined timing. This selection signal  $S_{sel}$  is a signal for instructing the capacitor  $C_s$  with regards to the display pixel PIX to which a voltage corresponding to the gradation level value of the display data should be written. The selection driver 12 may be structured by any of an Integrated Circuit (IC) chip or a transistor.

50 [0057] The power source driver 13 supplies, with a predetermined timing, the power source voltage  $V_{cc}$  of the predetermined voltage level to a plurality of power source voltage lines  $L_v$  arranged in the selection line  $L_s$  in parallel with the selection line  $L_s$ .

55 [0058] The data driver (display driving apparatus) 14 applies, with a predetermined timing, the compensated gradation level voltage  $V_{pix}$  (e.g.,  $V_{pix}(i)$ ,  $V_{pix}(i+1)$ ) to the respective data lines  $L_d$ .

[0059] The controller 15 generates, based on a timing signal supplied from the display signal generation circuit 16, a signal for controlling the operations of the respective members to supply the signal to the respective members. For

example, the controller 15 supplies a selection control signal for controlling the operation of the selection driver 12, a power source control signal for controlling the operation of the power source driver 13, and a data control signal for controlling the operation of the data driver 14.

[0060] The display signal generation circuit 16 generates display data (data for brightness) based on a video signal inputted from the exterior of the display apparatus 1 to supply the display data to the data driver 14. The display signal generation circuit 16 also extracts, based on the generated display data, a timing signal (e.g., system clock) for displaying an image in the display zone 11 to supply the timing signal to the controller 15. This timing signal also may be generated by the display signal generation circuit 16.

[0061] The display panel 17 is a board having thereon the display zone 11, the selection driver 12, and the data driver 14. This board also may have thereon the power source driver 13. The display panel 17 also may have thereon a part of the data driver 14 and the remaining part of the data driver may be provided at the exterior of the display panel 17. In this case, a part of the data driver 14 in the display panel 17 may include an IC chip or a transistor.

[0062] The display panel 17 has, at the center thereof, the display panel 17 in which the respective display pixels PIX are arranged in a lattice-like manner. The respective display pixels PIX are divided into a group positioned at an upper zone of the display zone 11 and a group positioned at a lower zone. The display pixels PIX included in each group are connected to branched power source voltage lines Lv, respectively. It is noted that the group at the upper zone in Embodiment 1 includes the first to (n/2)th display pixels PIX ("n" is an even number). The group at the lower zone includes the (n/2+1) to "n"th display pixels PIX.

[0063] The respective power source voltage lines Lv in the group at the upper zone are connected to the first power source voltage line Lv1. The respective power source voltage lines Lv in the group at the lower zone are connected to the second power source voltage line Lv2. The first power source voltage line Lv1 and the second power source voltage line Lv2 are connected to the power source driver 13 in an independent manner. Thus, the power source voltage Vcc is commonly applied to the first to (n/2)th display pixels PIX via the first power source voltage line Lv1. The (n/2+1) to "n"th display pixels PIX are commonly applied with the power source voltage Vcc via the second power source voltage line Lv2. The power source driver 13 applies the power source voltage Vcc via the first power source voltage line Lv1 at a timing different from a timing at which the power source driver 13 applies the power source voltage Vcc via the second power source voltage line Lv2.

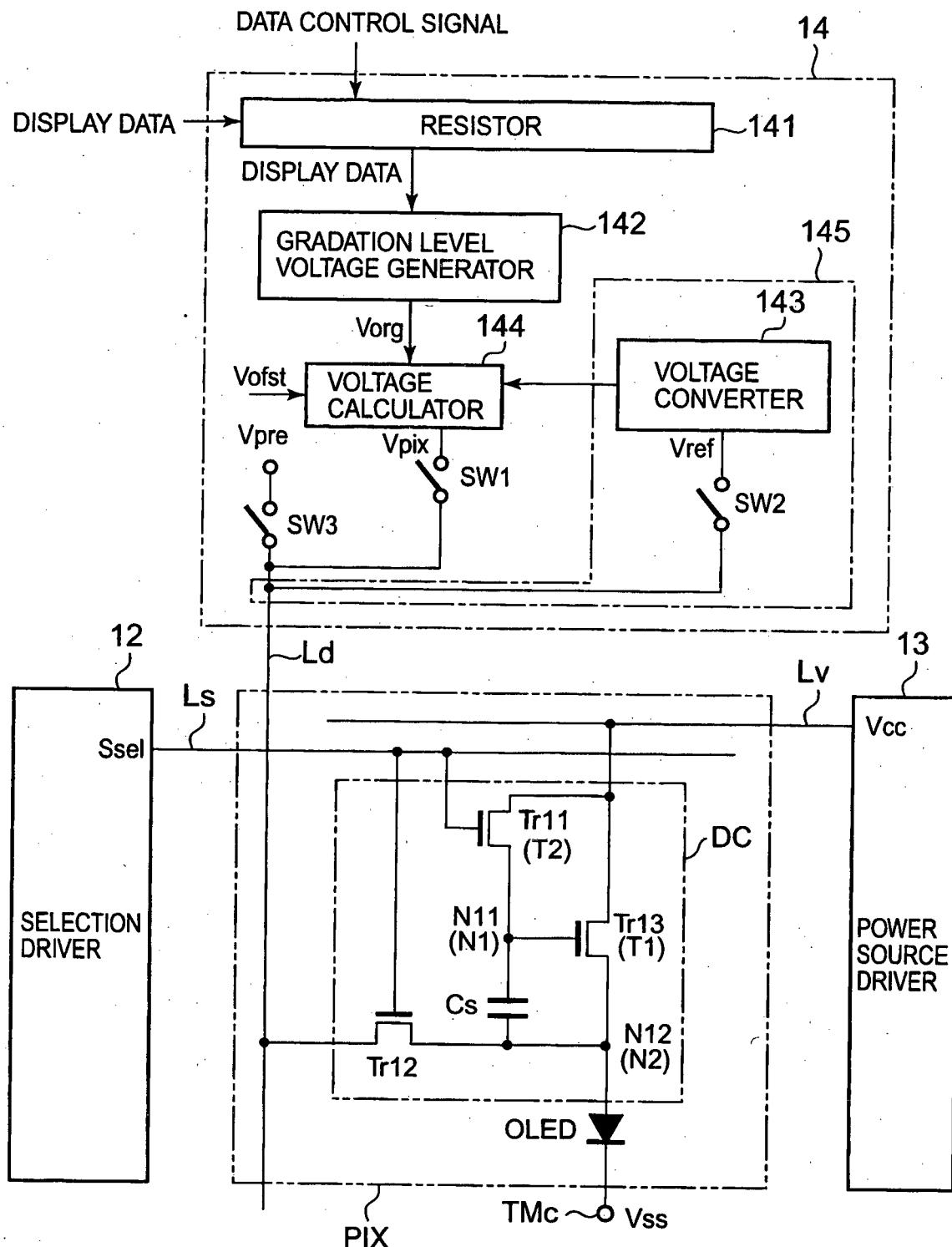

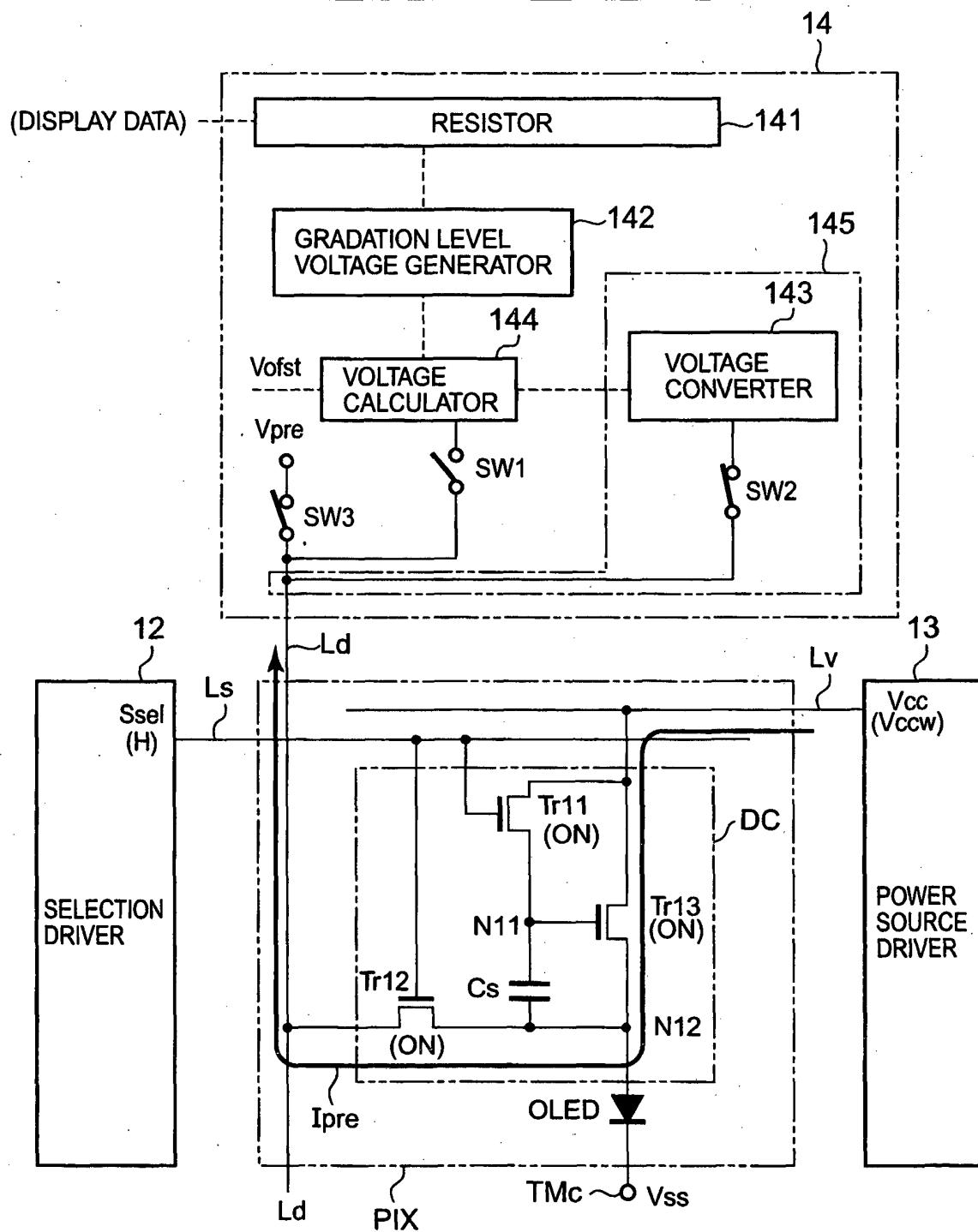

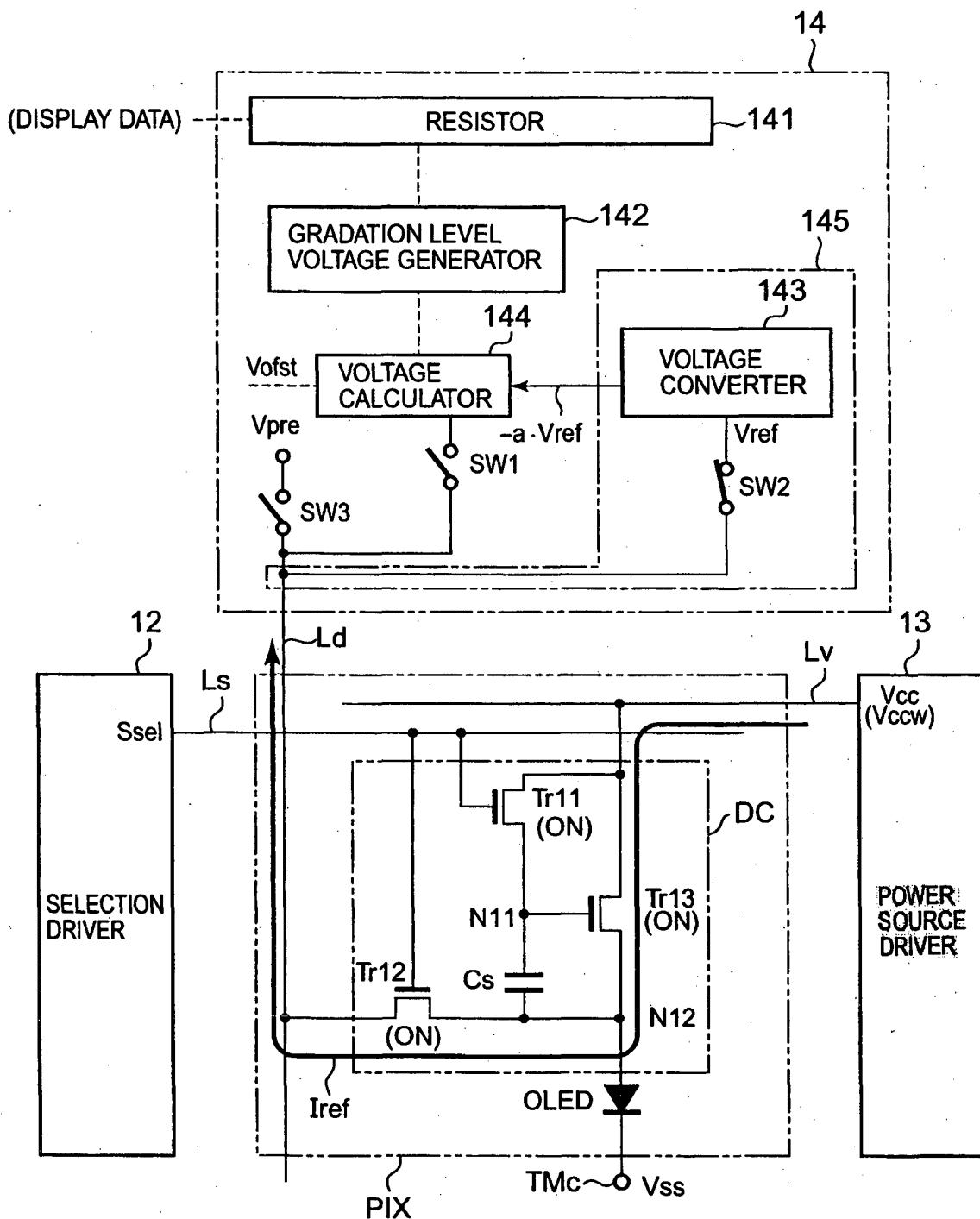

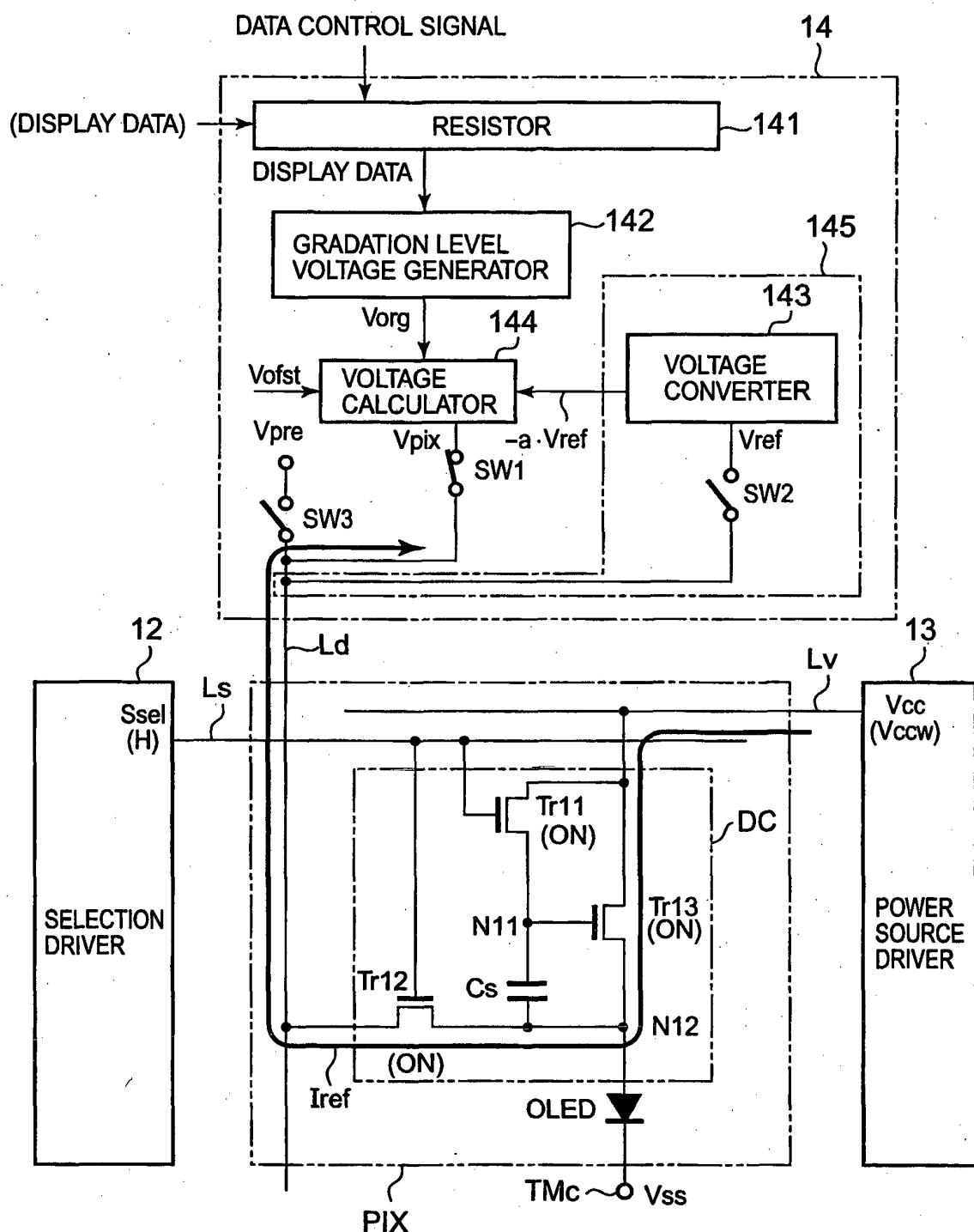

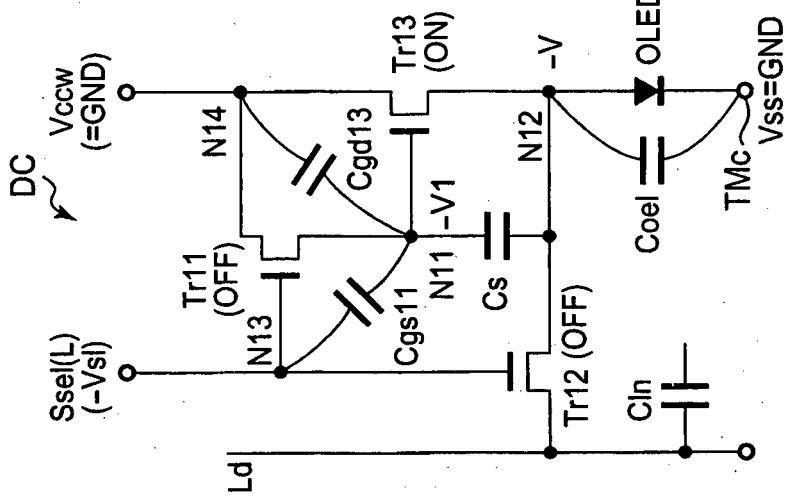

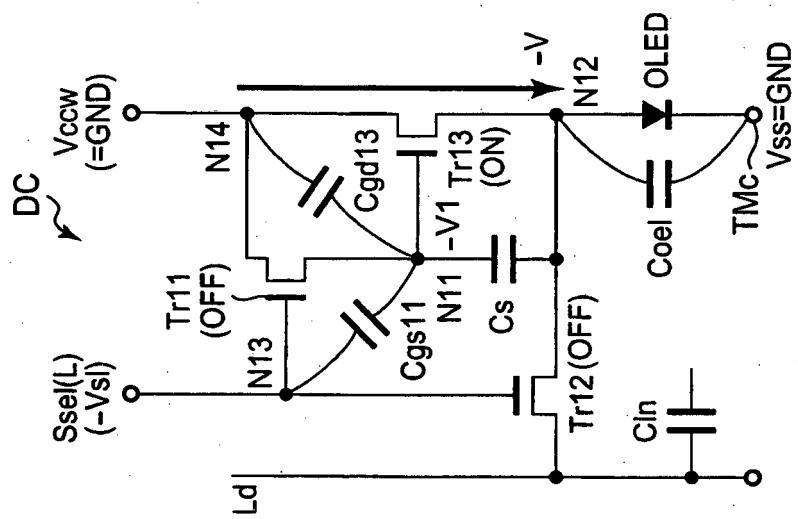

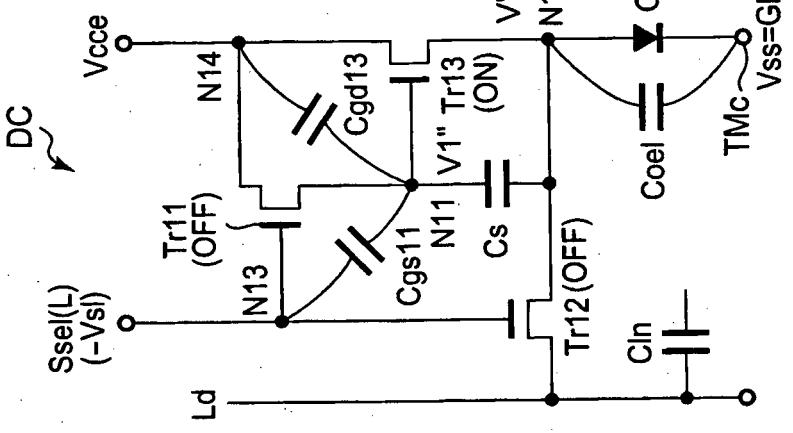

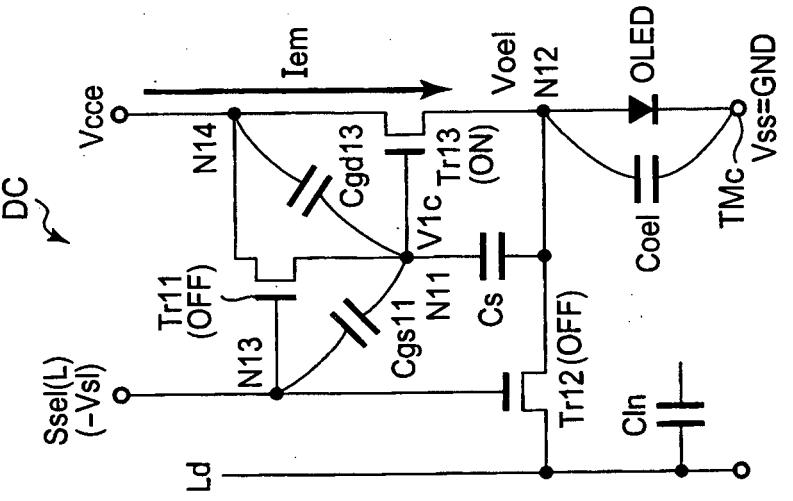

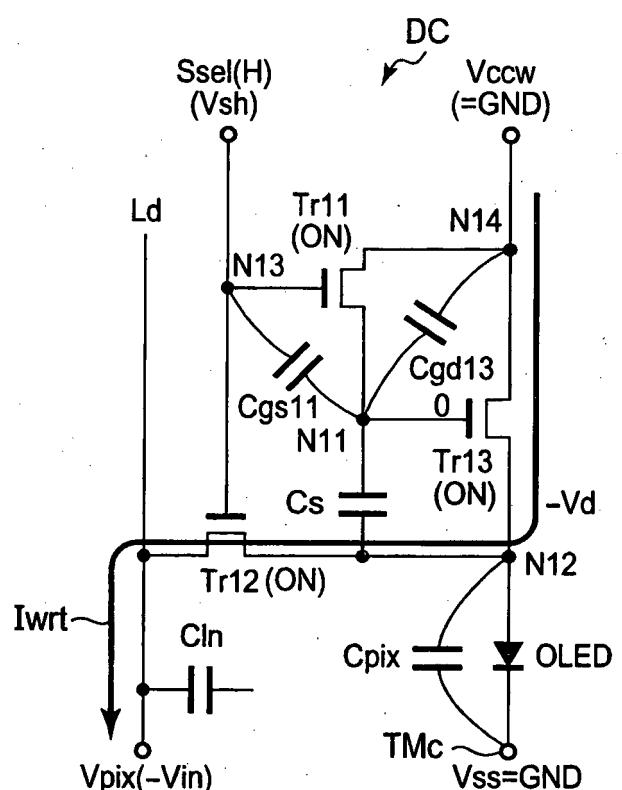

[0064] The display pixel PIX shown in Fig. 9 includes, as shown in Fig. 10, the pixel driving circuit DC and the organic EL element OLED. The pixel driving circuit DC has a transistor Tr11, a selection transistor Tr12, a driving transistor Tr13, and a capacitor Cs. This transistor Tr11 corresponds to the retention transistor T2 shown in Fig. 1 and the driving transistor Tr13 corresponds to the driving transistor T1 shown in Fig. 1. It is noted that the respective transistors Tr11 to Tr13 may be an arbitrary type of transistor but the respective transistors Tr11 to Tr13 in the following description are all an n channel-type field effect-type transistor.

[0065] The retention transistor Tr11 is a transistor for diode connection of the driving transistor Tr13. The retention transistor Tr11 is structured so that a gate terminal is connected to the selection line Ls, a drain terminal is connected to the power source voltage line Lv, and a source terminal is connected to the contact point N11. The selection line Ls is applied with the selection signal Ssel. This selection signal Ssel is identical with the retention control signal Shld shown in Fig. 2.

[0066] The selection transistor Tr12 shown in Fig. 10 is structured so that a gate terminal is connected to the selection line Ls, a source terminal is connected to the data line Ld, and a drain terminal is connected to the contact point N12. This contact point N12 corresponds to the contact point N2 shown in Fig. 1. The driving transistor Tr13 is structured so that a gate terminal is connected to the contact point N11, a drain terminal is connected to the power source voltage line Lv, and a source terminal is connected to the contact point N12. The contact point N11 corresponds to the contact point N1 shown in Fig. 1.

[0067] The capacitor Cs is an identical as that shown in Fig. 1. The capacitor Cs shown in Fig. 10 is connected between the contact point N11 and the contact point N12 (between the gate and the source of the driving transistor Tr13). The organic EL element OLED is structured so that an anode terminal is connected to the contact point N12 and the cathode terminal TMc is applied with a fixed reference voltage Vss.

[0068] During the writing operation, the compensated gradation level voltage Vpix corresponding to the gradation level value of the display data is applied to the capacitor Cs in the pixel driving circuit DC. Then, the compensated gradation level voltage Vpix, the reference voltage Vss, and the power source voltage Vcc (Vcce) having a high potential applied to the power source voltage line Lv for a light-emitting operation satisfy the relations of the above-described formulae (3) to (10). Thus, during the writing operation, the organic EL element OLED is in a light-off status. It is noted that pixel driving circuit DC is not limited to the structure shown in Fig. 10 and also may have any structure so long as that structure has elements corresponding to the respective elements shown in Fig. 1 and has a current path of the driving transistor T1 that has thereon current driving-type light-emitting elements OLED arranged in series. The light-emitting element is not limited to the organic EL element OLED and also may be other current driving-type light-emitting element such as a light-emitting diode.

[0069] The selection driver 12 includes, for example, a shift register and an output circuit section (output buffer). The shift register sequentially outputs, based on the selection control signal from the controller 15, shift signals corresponding to selection lines Ls of the respective rows. The output circuit section converts the level of this shift signal to a predetermined selected level (high level H or low level L). After the conversion, the output circuit section sequentially outputs the converted shift signals to the selection lines Ls of the respective rows as the selection signals Ssel.

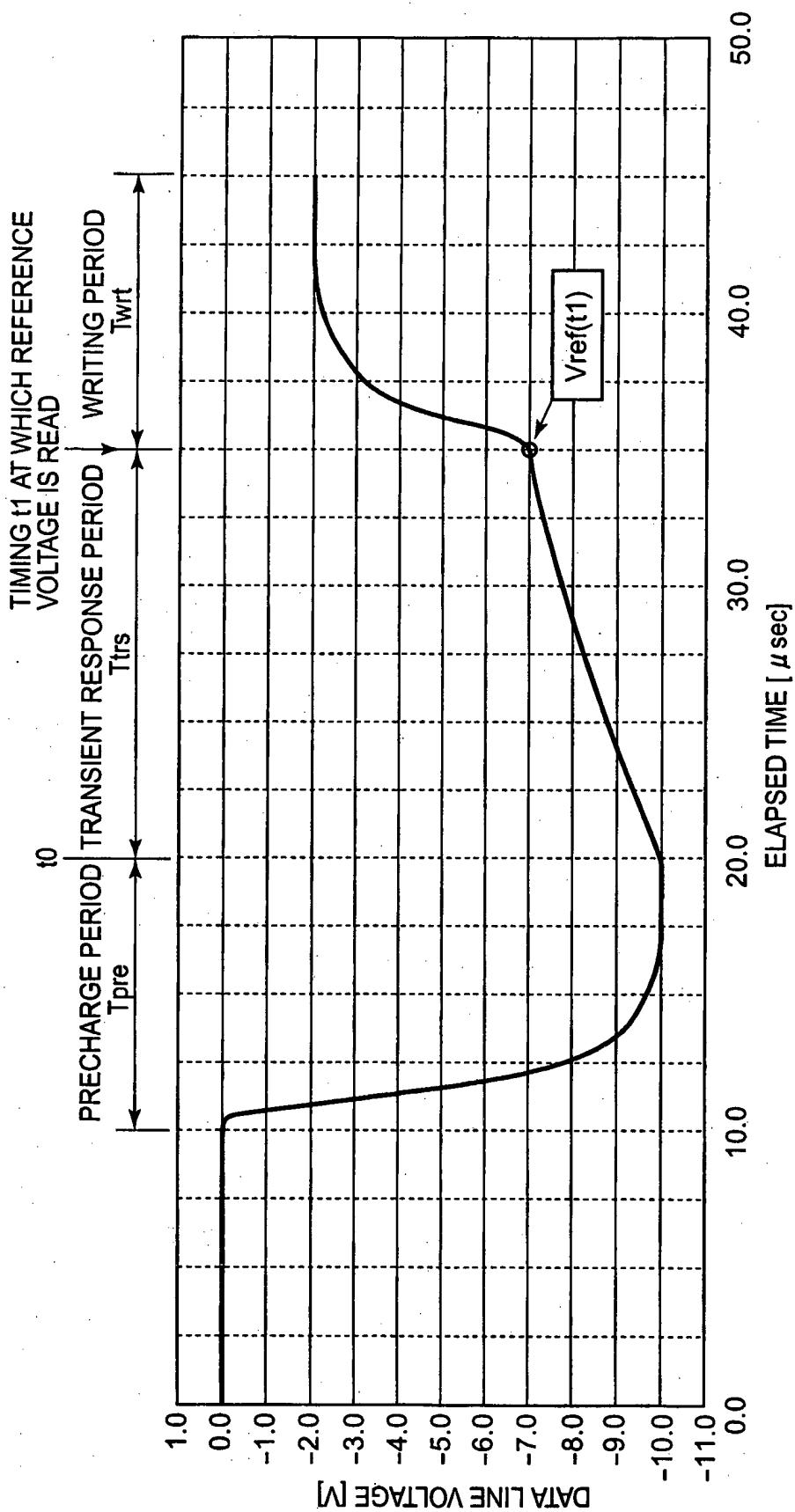

[0070] For example, during a selection period Tsel shown in Fig. 13 (a period including a precharge period Tpre, a transient response period Ttrs, and a writing period Twrt), the selection driver 12 supplies the selection signal Ssel of a high level to the selection lines Ls of the respective rows connected with the display pixels PIX. The selection driver 12 supplies the selection signal Ssel to the selection line Ls in each row with a predetermined timing to sequentially set the display pixel PIX in each row to a selected status. The selection driver 12 may include a transistor that is the same as those of the respective transistors Tr11 to Tr13 in the pixel driving circuit DC.

[0071] During the selection period Tse, the power source driver 13 applies, based on the power source control signal from the controller 15, the power source voltage Vcc of a low potential (=Vccw) to the respective power source voltage lines Lv. During the light-emitting period, the power source driver 13 applies the power source voltage Vcc of a high potential (=Vcce) to the respective power source voltage lines Lv. In the example of Fig. 9, the power source driver 13 applies, during the operation of the display pixels PIX included in the group at the upper zone, the power source voltage Vcc to these display pixels PIX via the first power source voltage line Lv1. The power source driver 13 also applies, during the operation of the display pixels PIX included in the group at the upper zone, the power source voltage Vcc to these display pixels PIX via the second power source voltage line Lv2.

[0072] The lower source driver 13 may include a timing generator and an output circuit section. The timing generator generates, based on a power source control signal from the controller 15, timing signals corresponding to the respective power source voltage lines Lv. The timing generator is a shift register that sequentially outputs a shift signal for example. The output circuit section converts a timing signal to a predetermined voltage level (voltage values Vccw and Vcce) to apply the power source voltage Vcc suitable for this voltage level to the respective power source voltage lines Lv. When the number of the power source voltage lines Lv is small, the power source driver 13 may be provided in the controller 15 instead of the display panel 17.

[0073] The data driver (display driving apparatus) 14 generates a signal voltage (original gradation level voltage Vorg) corresponding to the display data (brightness corresponding to an emitting color) for each display pixel PIX supplied from the display signal generation circuit 16 for compensation. By the compensation of the original gradation level voltage Vorg, the data driver 14 generates a compensated gradation level voltage Vpix corresponding to the element characteristic (threshold voltage) of the driving transistor Tr13 provided in each display pixel PIX. After the generation, the data driver 14 applies the compensated gradation level voltage Vpix to the respective display pixels PIX via the data line Ld.

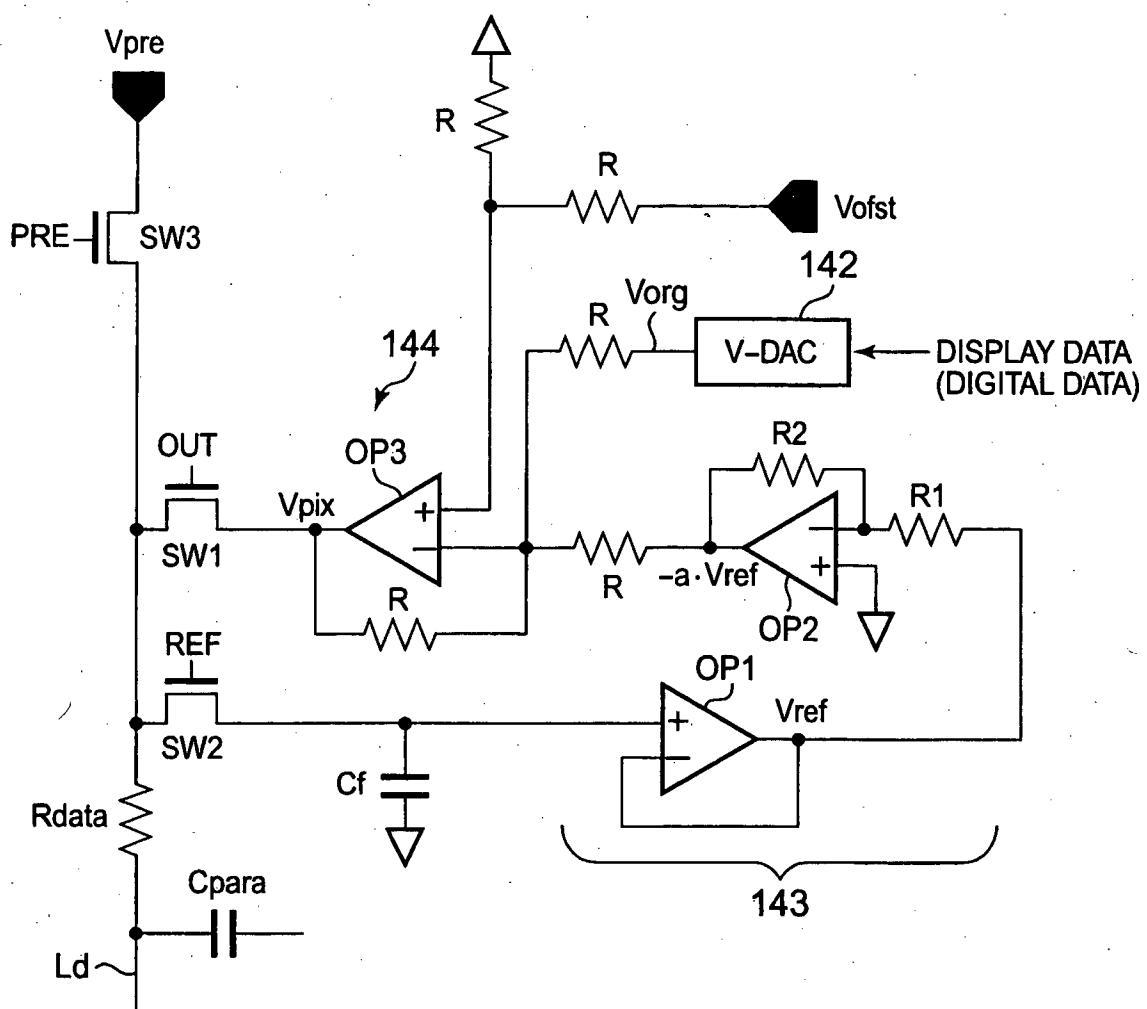

[0074] As shown in Fig. 10, the data driver 14 includes: a resistor 141, a gradation level voltage generator 142, a voltage converter 143, a voltage calculator 144, and changing-over switches SW1 to SW3. The gradation level voltage generator 142, the voltage calculator 144, and the changing-over switches SW1 to SW3 are provided in the data line Ld of each column and are provided in a quantity of "m" in the entire data driver 14.

[0075] A voltage reader 145 includes the voltage converter 143 and the changing-over switch SW2. The voltage converter 143 and the changing-over switch SW2 are connected to the data line Ld. It is noted that wiring resistances and capacities from the data line Ld to the respective changing-over switches SW1 to SW3 are structured so as to be equal to one another. Thus, a voltage drop due to the data line Ld is substantially equal to any of the respective changing-over switches SW1 to SW3.

[0076] The resistor 141 has a shift register and a data register. The shift register sequentially outputs a shift signal based on a data control signal from the controller 15. The data register acquires, based on the outputted shift signal, data for brightness of the gradation level to transfer the data to the gradation level voltage generators 142 provided in the respective columns in a parallel manner. The data register acquires data for gradation level by acquiring data corresponding to the display pixels PIX in one row on the display zone 11.

[0077] The gradation level voltage generator 142 generates and outputs the original gradation level voltage Vorg. This original gradation level voltage Vorg is a voltage that has a value corresponding to display data for each display pixel PIX and that shows brightness of the gradation level of each organic EL element OLED. It is noted that the original gradation level voltage Vorg is applied between an anode and a cathode of the organic EL element OLED and thus does not depend on the threshold voltage Vth of the transistor Tr13. When the driving transistor Tr13 operates based on the characteristic line SPw shown in Fig. 4A, the gradation level voltage generator 142 outputs, to the data line Ld, an absolute voltage value obtained by adding this original gradation level voltage Vorg to the threshold voltage Vth (|Vorg+Vth|). Then, by the potential difference between the power source voltage line Lv and the data line Ld, current for allowing the organic EL element OLED to emit light with brightness depending on the display data flows in the transistor Tr13.

[0078] During the writing operation, when current flows from the power source voltage line Lv to the data line Ld, the gradation level voltage generator 142 calculates a value obtained by multiplying, with -1, a voltage having a sum of the

original gradation level voltage  $V_{org}$  and the threshold voltage  $V_{th}$  to output the value. When current flows from the data line  $L_d$  to the power source voltage line  $L_v$ , the gradation level voltage generator 142 directly outputs the voltage having the sum of the original gradation level voltage  $V_{org}$  and the threshold voltage  $V_{th}$  without multiplying the voltage with a coefficient. It is noted that the original gradation level voltage  $V_{org}$  is set to have a higher voltage with an increase of gradation level of display data.

**[0079]** The gradation level voltage generator 142 also may include, for example, a Digital to Analogue Converter (DAC) and an output circuit. The DAC converts, based on a gradation level reference voltage supplied from a power supply section (not shown), a digital signal voltage of display data to an analog signal voltage. It is noted that this gradation level reference voltage is a reference voltage based on the values of gradation level. The output circuit outputs, with a predetermined timing, the analog signal voltage converted by the DAC as the original gradation level voltage  $V_{org}$ .

**[0080]** The voltage converter 143 applies the predetermined precharge voltage to the data line  $L_d$ . After the application, after a transient response period (natural relaxation period), the voltage of the capacitor  $C_s$  (reference voltage  $V_{ref}$ ) is read via the data line  $L_d$ .

**[0081]** After the reading, the voltage converter 143 determines a coefficient  $a$  to estimate a threshold voltage of the transistor  $Tr_{13}$  after the characteristic variation. Next, the voltage converter 143 multiplies the coefficient  $a$  with the reference voltage  $V_{ref}$  to generate the first compensation voltage  $a \cdot V_{ref}$  to output the first compensation voltage  $a \cdot V_{ref}$  to the voltage calculator 144.

**[0082]** In the example of Fig. 10, current flowing in the data line  $L_d$  during the writing operation is set to flow from the data line  $L_d$  to the data driver 14. Thus, the first compensation voltage  $a \cdot V_{ref}$  is set so that  $a \cdot V_{ref} < V_{ccw} - V_{th1} - V_{th2}$  is established. In this formula,  $V_{th1}$  represents a threshold voltage of the transistor  $Tr_{13}$  and  $V_{th2}$  represents a threshold voltage of the transistor  $Tr_{12}$ . Then, current flows from the power source voltage line  $L_v$  via the drain and source of the transistor  $Tr_{13}$ , the drain and source of the transistor  $Tr_{12}$ , and the data line  $L_d$ .

**[0083]** The voltage calculator 144 performs addition and subtraction of the original gradation level voltage  $V_{org}$  from the gradation level voltage generator 142, the first compensation voltage  $a \cdot V_{ref}$  from the voltage converter 143, and the previously-set second compensation voltage  $V_{ofst}$ . When the gradation level voltage generator 142 includes the DAC, the addition and subtraction processings are performed for analog signals. It is noted that the second compensation voltage  $V_{ofst}$  is determined based on an output variation characteristic of the threshold voltage  $V_{th}$  of the transistor  $Tr_{13}$  for example. Next, the voltage calculator 144 outputs the voltage obtained by addition and subtraction as the compensated gradation level voltage  $V_{pix}$  to the data line  $L_d$ . During the writing operation, voltage calculator 144 determines the compensated gradation level voltage  $V_{pix}$  so as to satisfy the following formula (11) for example.

$$V_{pix} = a \cdot V_{ref} - V_{org} + V_{ofst} \quad (11)$$

**[0084]** The respective changing-over switches  $SW_1$  to  $SW_3$  switches ON and OFF based on the data control signal from the controller 15, respectively. The changing-over switch  $SW_1$  turns ON or OFF the application by the voltage calculator 144 of the compensated gradation level voltage  $V_{pix}$  to the data line  $L_d$ . The changing-over switch  $SW_2$  turns ON or OFF an operation in which the voltage converter 143 reads a voltage of the data line  $L_d$ . The changing-over switch  $SW_3$  turns ON or OFF the application of the precharge voltage  $V_{pre}$  to the data line  $L_d$ .

**[0085]** The controller 15 controls the selection driver 12, the power source driver 13, and the data driver 14 to operate the respective drivers with a predetermined timing. The selection driver 12 sequentially sets the display pixel  $PIX$  to the selected status. The power source driver 13 applies the power source voltage  $V_{cc}$  to the respective power source voltage lines  $L_v$ . The data driver 14 applies the compensated gradation level voltage  $V_{pix}$  to the respective display pixels  $PIX$ .

**[0086]** The pixel driving circuits  $DC$  of the respective display pixels  $PIX$  performs a series of driving control operations under the control by the controller 15. This driving control operation including: a compensated gradation level voltage setting operation (precharge operation, transient response, reference voltage reading operation); a writing operation; a retention operation; and a light-emitting operation. By the driving control operation, the pixel driving circuit  $DC$  causes the display zone 11 to display image information based on a video signal.

**[0087]** The display signal generation circuit 16 extracts gradation level signals included in the video signal inputted from the exterior of the display apparatus 1. After the extraction, the display signal generation circuit 16 supplies the gradation data signals to the data driver 14 with regards to every one row of the display zone 11. When the video signal includes a timing signal defining the timing at which the image is to be displayed, the display signal generation circuit 16 may extract the timing signal to output the timing signal to the controller 15. Then, the controller 15 outputs the respective control signals to the respective drivers based on the timing defined by the timing signal.

(Method for driving display apparatus)

**[0088]** Next, a method for driving the display apparatus 1 will be described. It is noted that the following section will represent the respective display pixels PIX placed at positions (i, j) on the display zone 11 (n rows  $\times$  m columns) by display pixels PIX (i, j) (1=i=n, 1=j=m).

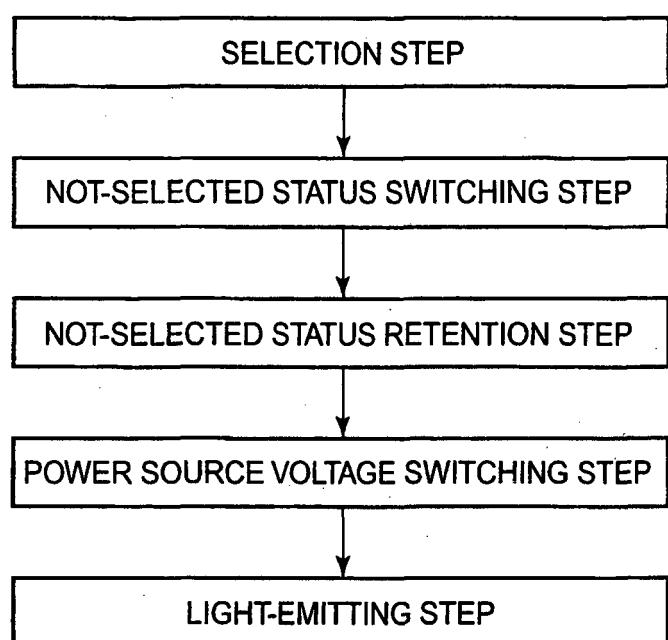

**[0089]** As shown in Fig. 11, the method for driving the display apparatus 1 of Embodiment 1 including: a selection step, a not-selected status switching step, a not-selected status retention step, a power source voltage switching step, and a light-emitting step. The respective steps are operations carried out in the respective display pixels PIX so that the respective display pixels PIX in the entire display zone 11 independently perform the operations of the respective steps. This selection step is a step for carrying out an operation shown in Fig. 13 (precharge operation, compensated gradation level voltage setting operation, writing operation). The not-selected status retention step is a step for performing the retention operation shown in Fig. 2. The light-emitting step is a step for performing the light-emitting operation shown in Fig. 2.

**[0090]** As shown in Fig. 12, the display apparatus 1 repeats a series of operations with a predetermined cycle period Tcyc. The cycle period Tcyc is a period required for one display pixel PIX to display one pixel of an image of one frame for example. In Embodiment 1, the cycle period Tcyc is a period required for the display pixels PIX for one row to display an image of one row of video frames.

**[0091]** First, in the compensation period Tdet in the selection period Tsel, a precharge operation is performed. In the precharge operation, the voltage converter 143 applies the predetermined precharge voltage Vpre to data line Ld of the respective columns. As a result, the precharge current Ipre from the power source voltage line Lv flows in the respective rows to the data line Ld. Thereafter, as shown in Fig. 13, the changing-over switch SW3 is turned OFF and the application of the precharge voltage Vpre by the voltage converter 143 is stopped. As a result, the precharge operation is completed. It is noted that a timing at which the application of the precharge voltage Vpre is completed is included in the compensation period Tdet.

**[0092]** When the read timing t1 shown in Fig. 13 has passed since the stoppage of the application of the precharge voltage Vpre, the voltage converter 143 reads a reference voltage Vref(t1).

**[0093]** In the compensated gradation level voltage setting operation, the gradation level voltage generator 142 generates the original gradation level voltage Vorg corresponding to the display data supplied from the display signal generation circuit 16. The voltage calculator 144 compensates the original gradation level voltage Vorg generated by the gradation level voltage generator 142 to generate the compensated gradation level voltage Vpix. When the voltage calculator 144 generates the compensated gradation level voltage Vpix, the compensated gradation level voltage setting operation is completed. Thereafter, the writing operation is performed.

**[0094]** In the writing operation, the voltage calculator 144 applies the compensated gradation level voltage Vpix to the respective data lines Ld. As a result, the writing current (the drain-source current Ids of the transistor Tr13) flows in the capacitor Cs.

**[0095]** In the retention operation, a voltage depending on the written compensated gradation level voltage Vpix (charge enough to flow writing current) written by a writing operation between the gate and the source of the transistor Tr13 is charged in the capacitor Cs and is retained. Hereinafter, a period during which the retention operation is performed will be referred to as a "retention period Thld".

**[0096]** In the light-emitting operation, as shown in Fig. 12, based on the charging voltage retained by the capacitor Cs, the light emission driving current Iem (e.g., Iem(i), Iem(i+1)) is supplied to the organic EL element OLED. The organic EL element OLED emits light with gradation level depending on display data. Hereinafter, a period during which the light-emitting operation is performed will be referred to as a "light-emitting period Tem". During the light-emitting period Tem, the light emission driving current Iem desirably equals to the drain-source current Ids of the transistor Tr13.

**[0097]** Hereinafter, the respective operations during the above-described selection operation will be described by an example of the display pixels PIX in the "i"th row. The reference voltage reading operation and the compensated gradation level voltage generation operation are performed during the election period Tsel for the display pixels PIX in the "i"th row now being processed.

**[0098]** As shown in Fig. 13, a period during which the precharge operation is performed during the compensation period Tdet will be referred to as a "precharge period Tpre". During this precharge period Tpre, the power source voltage line Lv is applied with the power source voltage Vccw. The voltage converter 143 applies the predetermined precharge voltage Vpre to the respective data lines Ld. As a result, the drain-source current Ids depending on the precharge voltage Vpre flows in the transistor Tr13 of the respective display pixels PIX arranged in a specific row (e.g., the "i"th row). The capacitor Cs accumulates charge depending on the precharge voltage Vpre.

**[0099]** As shown in Fig. 13, when the precharge operation is completed, the display driving apparatus DC turns OFF the changing-over switch SW3 to stop the application of the precharge voltage Vpre. After the completion of the precharge operation, a transient response is started. Thus, a timing at which the precharge operation is completed will be hereinafter referred to as "transient response start timing t0". Hereinafter, a period from the start of the transient response to the

completion will be referred to as a "transient response period Ttrs".

[0100] During the transient response period Ttrs, the data driver 14 performs the reference voltage reading operation. After the time since the transient response start timing t0 has passed and the read timing t1 is reached, the voltage converter 143 reads, via data line Ld, the charging voltage of the capacitor Cs retained between the gate and the source of the transistor Tr13. The read charging voltage is the reference voltage Vref(tl) shown in Fig. 13.

[0101] Next, during the compensation period Tdet shown in Fig. 13, the pixel driving circuit DC performs the compensated gradation level voltage generation operation. In the compensated gradation level voltage generation operation, the voltage calculator 144 sets the compensated gradation level voltage Vpix based on the reference voltage Vref(tl).

[0102] As shown in Fig. 14, during the precharge period Tpre, the power source driver 13 applies the power source voltage Vcc of the writing operation level (=the first power source voltage Vccw = reference voltage Vss) to the power source voltage line Lv connected to the display pixels PIX in the "i"th row. The selection driver 12 applies the selection signal Ssel of the selected level (high level) to the selection line Ls of the "i"th row. The display pixels PIX in the "i"th row are set to the selected status.

[0103] Then, in the respective display pixels PIX of the "i"th row, the respective transistors Tr11 are turned ON and the respective driving transistors Tr13 are in a diode-connected status. As a result, the power source voltage Vcc(=Vccw) is applied to the drain terminal and the gate terminal driving transistor Tr13 (contact point N11; one end of the capacitor Cs). The transistor Tr12 is also turned ON and the source terminal of the transistor Tr13 (contact point N12; the other end of the capacitor Cs) is electrically connected to the data lines Ld of the respective columns.

[0104] In synchronization with this timing, the controller 15 supplies a data control signal. As shown in Fig. 13, the data driver 14 turns OFF the changing-over switch SW1 to ON and turns ON the changing-over switches SW2 to SW3. As a result, the predetermined precharge voltage Vpre is applied to the respective capacitors Cs via the respective data lines Ld.

[0105] During the application of the precharge voltage Vpre, the maximum value of the threshold voltage of the driving transistor Tr13 after the variation in the element characteristic is a sum of the initial threshold voltage Vth0 and the maximum value  $\Delta Vth_{max}$  of the variation value  $\Delta Vth$  of the threshold voltage. The maximum value of the drain-source voltage of the transistor Tr12 is a sum of the initial drain-source voltage Vds12 and the maximum value  $\Delta Vds12_{max}$  of the variation value  $\Delta Vds12$  of the drain-source voltage Vds12 due to increased resistance of the transistor Tr12. It is also assumed that a voltage drop due to the selection transistor Tr12 shown in Fig. 14 and the wiring resistance from the power source voltage line Lv to the data line Ld except for the selection transistor Tr12 is Vvd. Then, the precharge voltage Vpre is set to satisfy the following formula (12). It is noted that the potential difference (Vccw-Vpre) shown at the left-hand side of the formula (12) is a voltage applied to the selection transistor Tr12 and the driving transistor Tr13.

$$Vccw - Vpre = (Vth0 + \Delta Vth_{max}) + (Vds12 + \Delta Vds12_{max}) + Vvd \quad (12)$$

[0106] The selection signal Ssel outputted to the selection line Ls is a positive voltage during the compensation period Tdet and is a negative voltage during periods other than the compensation period Tdet. Then, a voltage applied to the gate terminal of the transistor Tr12 is not remarkably close to the positive voltage. Thus, the maximum value  $\Delta Vds12_{max}$  of the variation value  $\Delta Vds12$  the drain-source voltage is so small that the maximum value  $\Delta Vds12_{max}$  of can be ignored when compared with the maximum value  $\Delta Vth_{max}$  of the variation value  $\Delta Vth$  of the threshold voltage of the driving transistor Tr13. Thus, the formula (12) can be represented by the following formula (12a).

$$Vccw - Vpre = (Vth0 + \Delta Vth_{max}) + Vds12 + Vvd \quad (12a)$$

[0107] Specifically, a voltage depending on the value of the precharge voltage Vpre is applied between both ends of the capacitor Cs (the gate and the source of the transistor Tr13). The voltage applied to the capacitor Cs is higher than the threshold voltage Vth after the variation in the element characteristic of the driving transistor Tr13. Thus, as shown in Fig. 14, the driving transistor Tr13 is turned ON to flow the precharge current Ipre depending on this voltage between the drain and the source of the transistor Tr13. Thus, both ends of the capacitor Cs immediately accumulates the charge based on this precharge current Ipre (voltage based on the precharge voltage Vpre).

[0108] The pixel driving apparatus DC owned by the display pixel PIX has a structure shown in Fig. 10. Thus, in order to flow the precharge current Ipre from the data line Ld in the data driver direction, the precharge voltage Vpre is set to have a negative potential to the power source voltage Vccw of the writing operation level (low level) ( $Vpre < Vccw = 0$ ).

[0109] In the precharge operation, it is assumed that a signal applied to the source terminal of the transistor Tr13 is a current signal. In this case, a risk is caused where the wiring capacity and wiring resistance owned by the data line Ld and/or the capacity component included in the pixel driving apparatus DC may delay a change in a potential (charging

voltage) in the capacitor  $C_s$ . However, the precharge voltage  $V_{pre}$  applied in Embodiment 1 is a voltage signal and thus can be quickly charged with the capacitor  $C_s$  during the initial precharge period  $T_{pre}$ . Then, as shown in Fig. 13, the charging voltage of the capacitor  $C_s$  is rapidly close to the precharge voltage  $V_{pre}$  to subsequently gradually converge to the precharge voltage  $V_{pre}$  within the remaining period of the precharge period  $T_{pre}$ .

**[0110]** It is noted that, during the precharge period  $T_{pre}$ , the voltage of the precharge voltage  $V_{pre}$  applied to the anode terminal of the organic EL element OLED (contact point N12) is set to be lower than the reference voltage  $V_{ss}$  applied to the cathode terminal  $T_{Mc}$ . The power source voltage  $V_{ccw}$  is set to be equal to or lower than the reference voltage  $V_{ss}$ . Thus, the organic EL element OLED is not in a positive bias status and thus has no current therein. Thus, during the precharge period  $T_{pre}$ , the organic EL element OLED does not emit light.

**[0111]** During the transient response period  $T_{trs}$  after the precharge period  $T_{pre}$  (natural relaxation period), the data driver 14 maintains, as shown in Fig. 13, the changing-over switch SW1 in an OFF status and maintains the changing-over switch SW2 in an ON status. The data driver 14 switches the changing-over switch SW3 from ON to OFF. This blocks the application of the precharge voltage  $V_{pre}$  to the data line  $L_d$  and the display pixels PIX in the "i"th row in the selected status (pixel driving circuit DC).

**[0112]** Then, as shown in Fig. 15, the transistors Tr11 and Tr12 maintains an ON status. An electric connection between the pixel driving circuit DC and the data line  $L_d$  is maintained but an application of the voltage to the data line  $L_d$  is blocked. Thus, the other terminal side of the capacitor  $C_s$  (contact point N12) is set to have high impedance.

**[0113]** The gate and the source of the transistor Tr13 (both ends of the capacitor  $C_s$ ) have therebetween, by the above-described precharge operation, a potential difference that is equal to or higher than the threshold voltage after the variation of the transistor Tr13 ( $V_{th0}+\Delta V_{th\_max}$ ). Thus, as shown in Fig. 15, the transistor Tr13 maintains an ON status and a transient current  $I_{ref}$  flows from the power source voltage line  $L_v$  via the transistor Tr13. During the transient response period  $T_{trs}$  (natural relaxation period), as shown in Fig. 13, the source terminal side of the transistor Tr13 (contact point N12; the other end of the capacitor  $C_s$ ) has a gradually-increasing potential toward the potential of the drain terminal side (power source voltage line  $L_v$  side). In accordance with this, the data line  $L_d$  electrically connected via the transistor Tr12 also has a gradually-increasing potential.