(19)

Europäisches Patentamt

European Patent Office

Office européen des brevets

(11)

EP 1 610 291 A1

(12)

## EUROPEAN PATENT APPLICATION

published in accordance with Art. 158(3) EPC

(43) Date of publication:

28.12.2005 Bulletin 2005/52

(51) Int Cl.7: G09G 3/30, G09G 3/28,

G09G 3/20, H05B 33/14

(21) Application number: 03770115.8

(86) International application number:

PCT/JP2003/014042

(22) Date of filing: 31.10.2003

(87) International publication number:

WO 2004/088623 (14.10.2004 Gazette 2004/42)

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

HU IE IT LI LU MC NL PT RO SE SI SK TR

Designated Extension States:

AL LT LV MK

(71) Applicant: SHARP KABUSHIKI KAISHA

Osaka-shi, Osaka 545-8522 (JP)

(72) Inventor: NUMAO, Takaji

Nara-shi, Nara 630-8115 (JP)

(30) Priority: 28.03.2003 JP 2003092534

(74) Representative: Brown, Kenneth Richard et al

R.G.C. Jenkins & Co.

26 Caxton Street

London SW1H 0RJ (GB)

30.07.2003 JP 2003204018

27.10.2003 JP 2003366130

## (54) DISPLAY DEVICE AND DRIVE METHOD THEREOF

(57) A switching transistor 3 is provided between a gate terminal of a driving TFT 1 and a drain terminal thereof. A first capacitor 2 is provided between the gate terminal of the driving TFT 1 and a source terminal thereof. The current control terminal of the driving TFT 1 is connected to a first terminal of a second capacitor 7. A second terminal of the second capacitor 7 is connected to the drain terminal of the driving TFT 1 via a switching transistor 9, and to a predetermined voltage line Va via a switching transistor 8. This allows restraint of variation of a current flowing, during a non-selection period, through a current driving light emitting element of a display apparatus, the current variation being caused by threshold voltage variation and mobility variation of the driving TFT. A specific example of the display apparatus including such a current driving light emitting element is an organic EL display apparatus.

FIG. 1

**Description****TECHNICAL FIELD**

**[0001]** The present invention relates to (i) a display apparatus using a current driving element, such as an organic EL (Electro Luminescence) display and an FED (Field Emission Display); and (ii) a method for driving the display apparatus.

**BACKGROUND ART**

**[0002]** What have been actively carried out in recent years are researches and developments for a current driving light-emitting element such as an organic EL display and an FED. Especially, the organic EL display is such a display that can emit light by a low voltage and less power consumption, so that the organic EL display has drawn attention as a display for a mobile device such as a mobile phone or a PDA (Personal Digital Assistants).

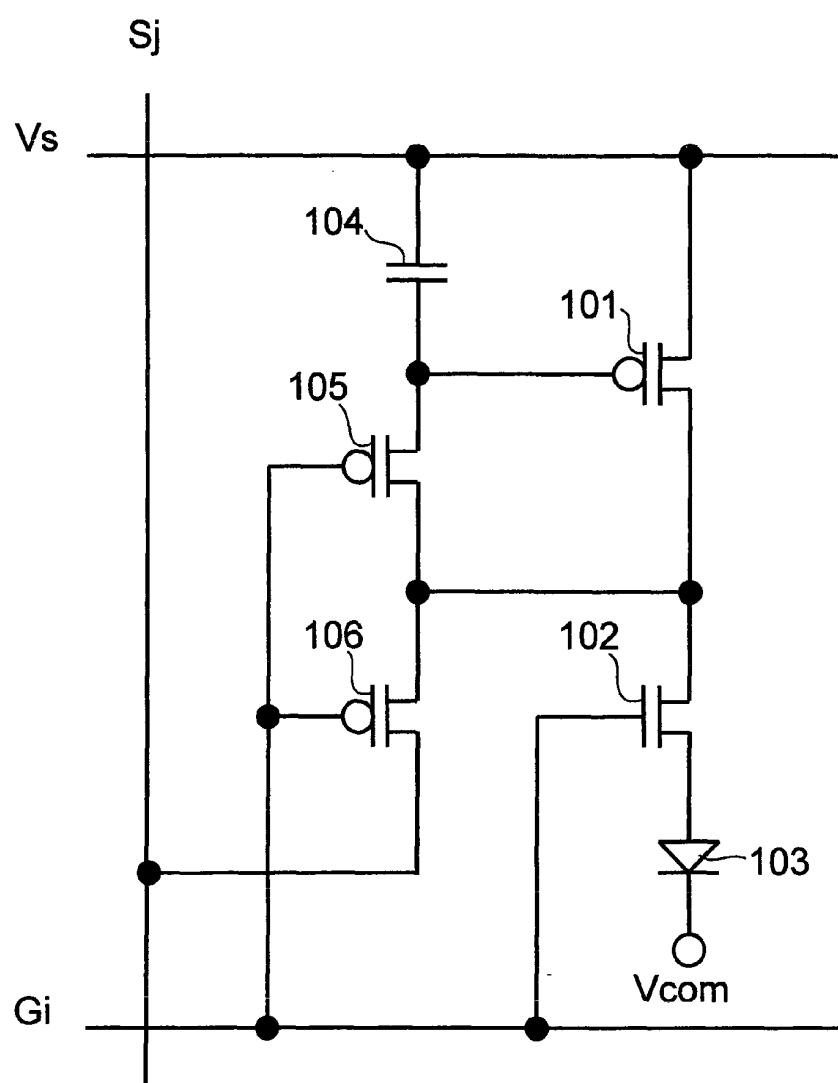

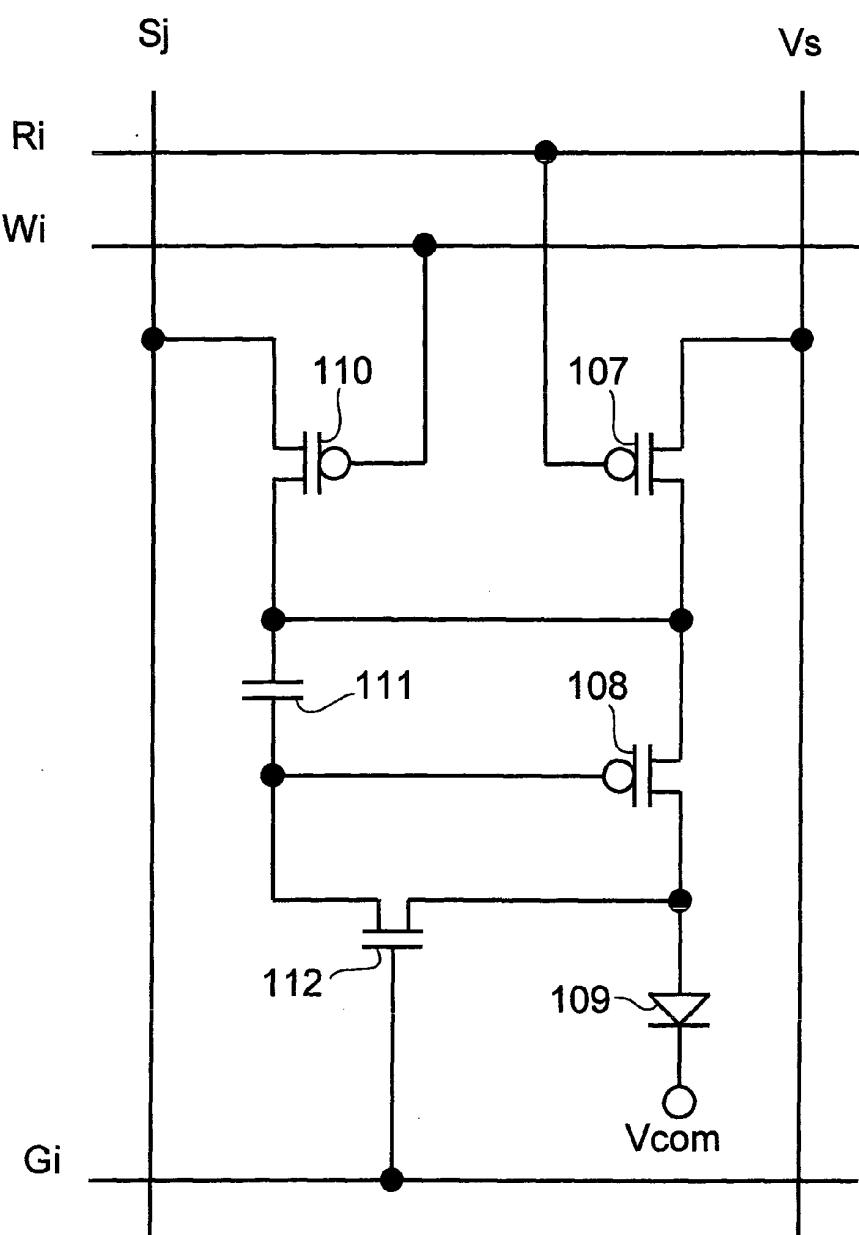

**[0003]** As a structure example of a current driving pixel circuit of such an organic EL display, Fig. 22 illustrates a circuit structure described in "Active Matrix PolyLED Displays" (M. T. Johnson et al., IDW '00, 2000, pp.235-238) and WO 99/65011 (published December 16, 1999).

**[0004]** In the circuit structure shown in Fig. 22, a driving TFT (Thin Film Transistor) 101 has a source terminal connected to a power source wire Vs, and has a gate terminal connected to the power source wire Vs via a capacitor 104.

Moreover, a switching TFT 102 is provided between a drain terminal of the driving TFT 101 and an anode of an organic EL element 103. A cathode of the organic EL element 103 is connected to a common wire Vcom.

Further, a selection TFT 106 and a switching TFT 105 are provided at a node of the driving TFT 101 and the switching TFT 102. The selection TFT 106 has a source terminal connected to a source wire Sj. The switching TFT 105 has a source terminal connected to the gate terminal of the driving TFT 101.

**[0006]** In the structure, when a signal indicative of Low is supplied to a scan wire Gi (selection period), the switching TFT 102 becomes OFF, and the selection TFT 106 and the switching TFT element 105 becomes ON. In this case, a current can flow from the power source wire Vs to the source wire Sj via the driving TFT 101 and the selection TFT 106. In cases where the current thus flowing is controlled by a power source of a source driver circuit (not shown) connected to the source wire Sj, a gate voltage of the driving TFT element 101 is set such that a current specified by the source driver circuit flows into the driving TFT 101.

**[0007]** On the other hand, when the scan wire Gi receives a signal indicative of High (non-selection period), the selection TFT 106 and the switching TFT 105 become OFF, and the switching TFT 102 becomes ON. During this non-selection period, the capacitor 104 retains the gate potential, determined during the selection period, of the driving TFT element 101. With this, during the non-selection period, the driving TFT 101 allows the determined current to flow into the organic EL element 103.

**[0008]** As an example of a current driving pixel circuit structure similar to the above structure, Fig. 23 illustrates a pixel circuit structure described in "Polysilicon TFT Drivers for Light Emitting Polymer Displays" (Simon W-B. Tam et al., IDW '99, 1999, pp.175-178) and WO 98/48403 (published on October 29, 1998).

**[0009]** In the circuit structure shown in Fig. 23, a capacitor 111 is provided between a source terminal of a driving TFT 108 and a gate terminal thereof. Between the gate terminal of the driving TFT 108 and a drain terminal thereof, a switching TFT 112 is provided. The drain terminal of the driving TFT 108 is connected to an anode of an organic EL element 109. Further, a switching TFT 107 is provided between the source terminal of the driving TFT 108 and a power source wire Vs. Moreover, a selection TFT 110 is provided between the source terminal of the driving TFT 108 and a source wire Sj.

**[0010]** The selection TFT 110 has a gate terminal connected to a control wire Wi, and the switching TFT 107 has a gate terminal connected to a control wire Ri, and the switching TFT 112 has a gate terminal connected to a scan wire Gi.

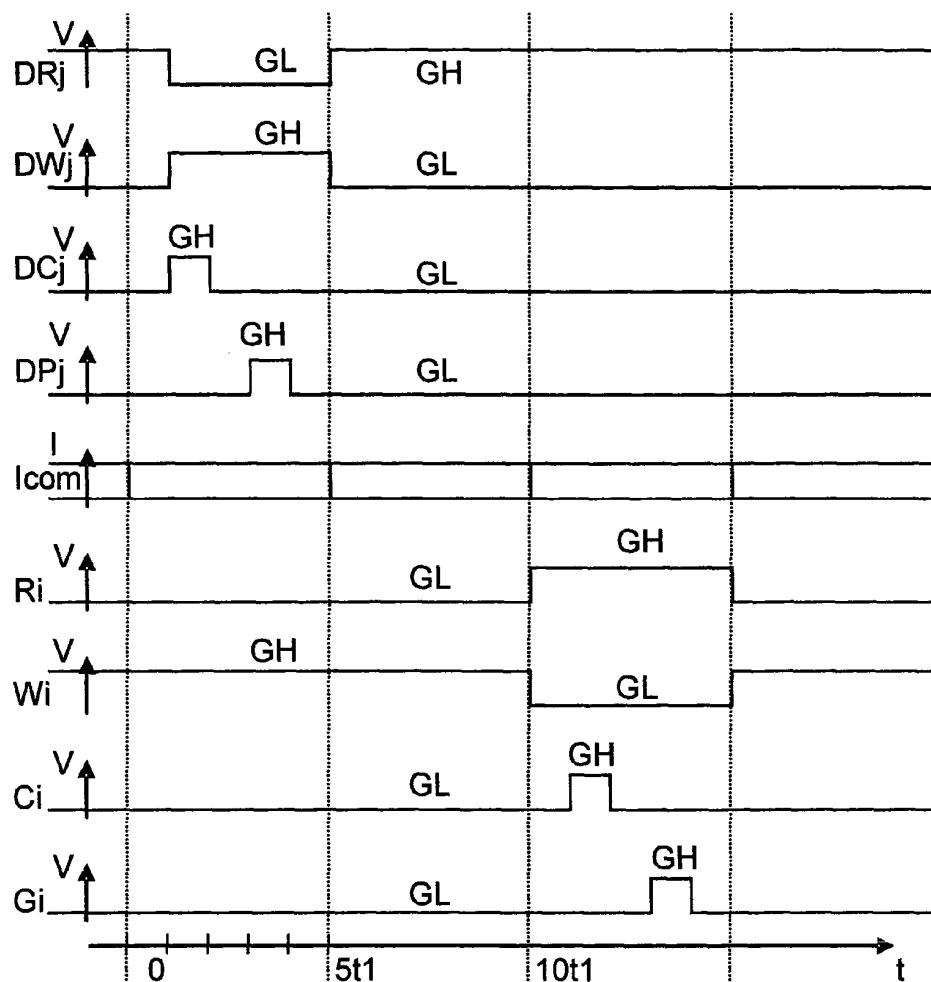

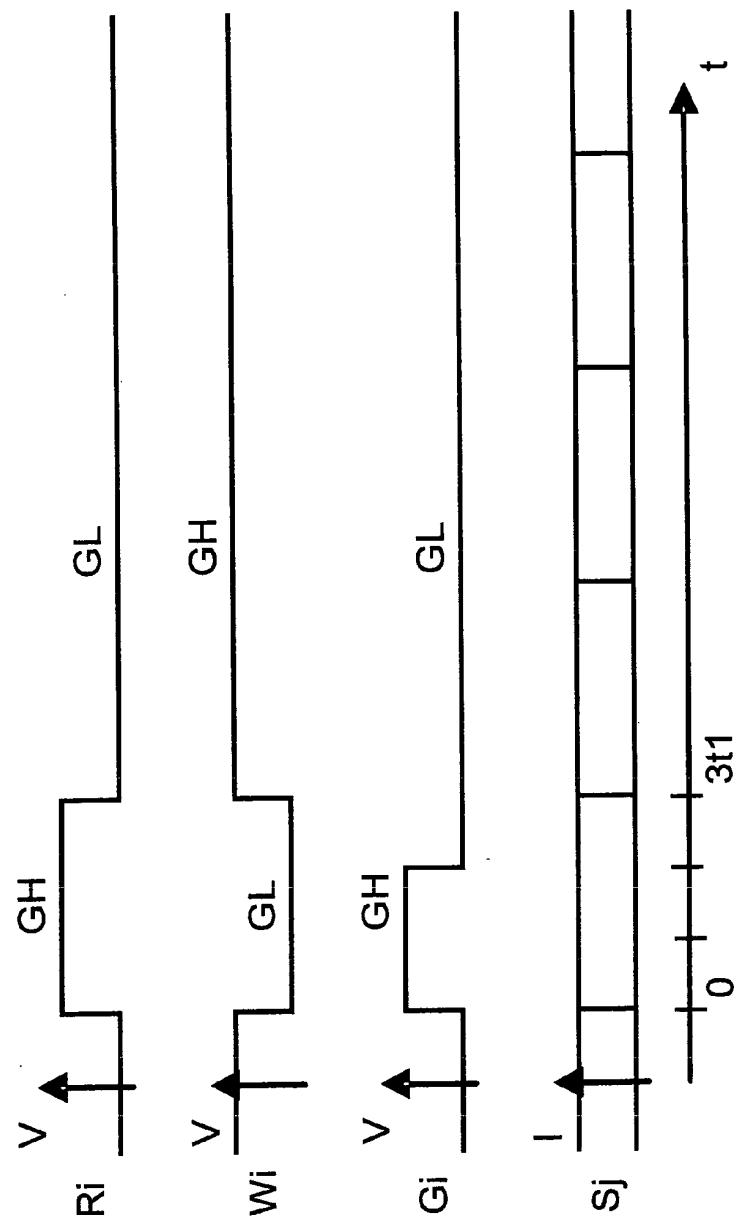

**[0011]** The following explains an operation of the pixel circuit structure with reference to a timing chart shown in Fig. 24. The timing chart illustrates respective timings of supplying signals to the control wires Wi and Ri, the scan wire Gi, and the source wire Sj.

**[0012]** In Fig. 24, the selection period corresponds to a period of time from 0 to 3t1. During the selection period, the control wire Ri has a High (GH) potential, so that the switching TFT 107 is OFF. On this occasion, the control wire Wi has a Low (GL) potential, so that the selection TFT 110 is ON. With this, during the selection period, a current flows from the source wire Sj to the organic EL element 109 via the selection TFT 110 and the driving TFT 108.

**[0013]** During a period of time from 0 to 2t1 within the selection period, the scan wire Gi has a High potential, so that the switching TFT 112 is ON. Accordingly, a current flows from (i) a source driver circuit (not shown) connected to the source wire Sj, to (ii) the organic EL element 109. This determines a gate potential of the driving TFT 108 such that a current specified by the source driver circuit flows into the organic EL element 109. During a period of time from 2t1 to 3t1, the switching TFT 112 is OFF; however, the gate potential of the driving TFT 108 is retained by the capacitor

111. This allows a current to flow from the source wire Sj to the organic EL element 109 during this period, too.

[0014] After the time 3t1 (non-selection period), the switching TFT 110 is OFF, and the switching TFT 107 is ON. With this, during the non-selection period, a determined current is controlled to flow from the power source wire Vs to the organic EL element 109.

[0015] However, the following problem arises in the pixel circuit structure described in "Polysilicon TFT Drivers for Light Emitting Polymer Displays" (IDW '99, pp.175-178). That is, variation in a threshold voltage of the driving TFT 108, and variation in mobility thereof cause variation in the current flowing into the organic EL element 109 during the non-selection period.

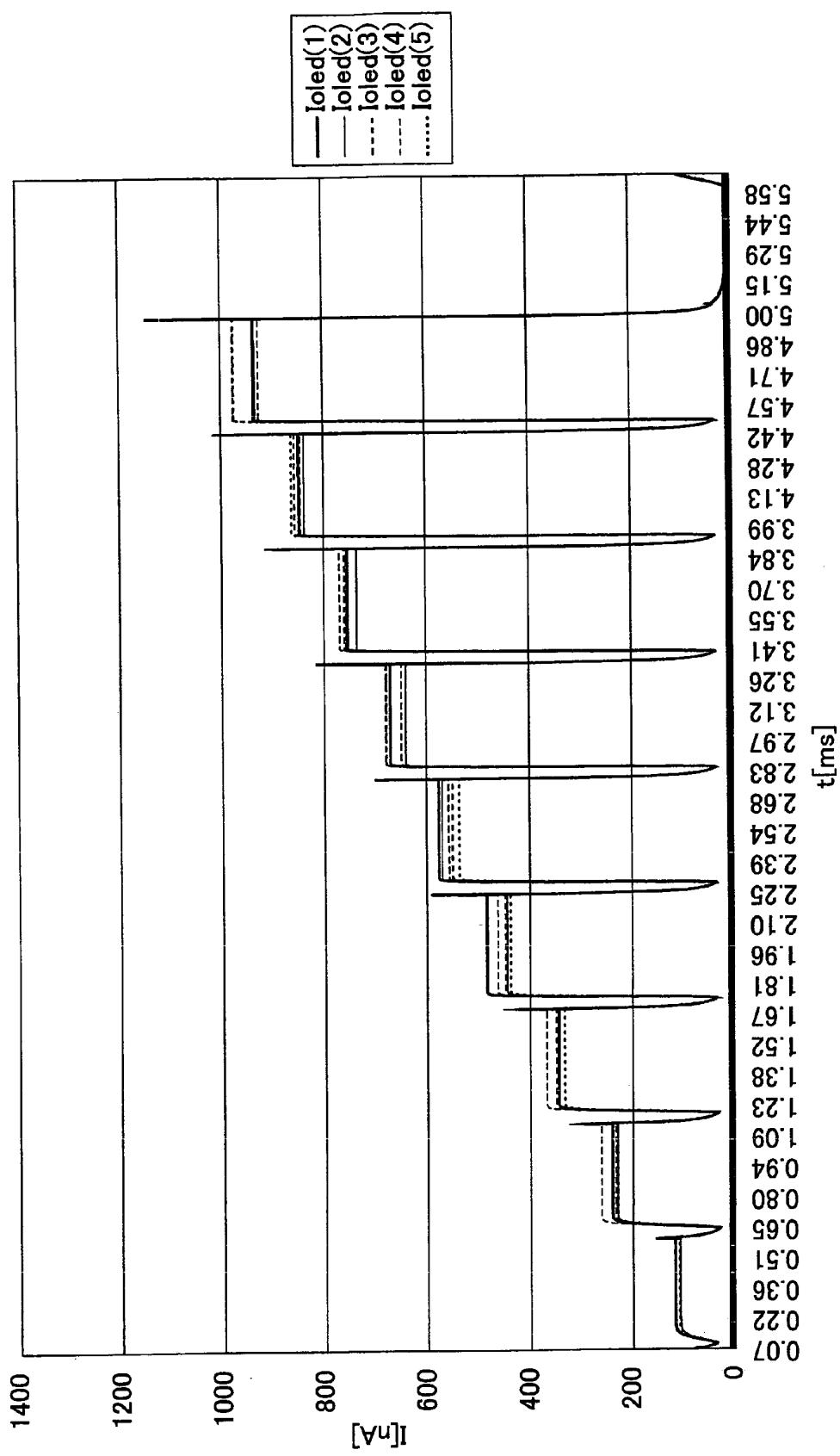

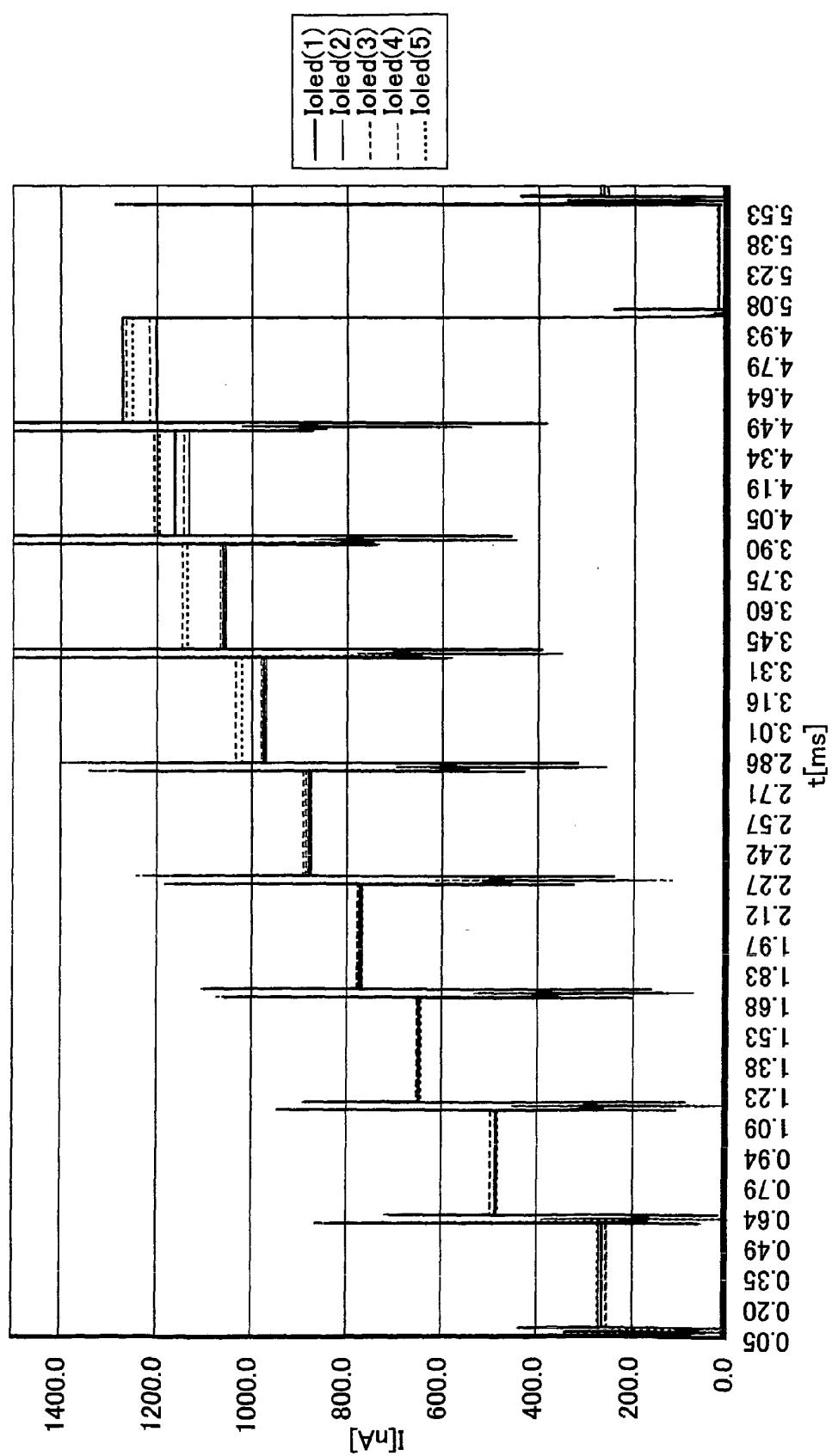

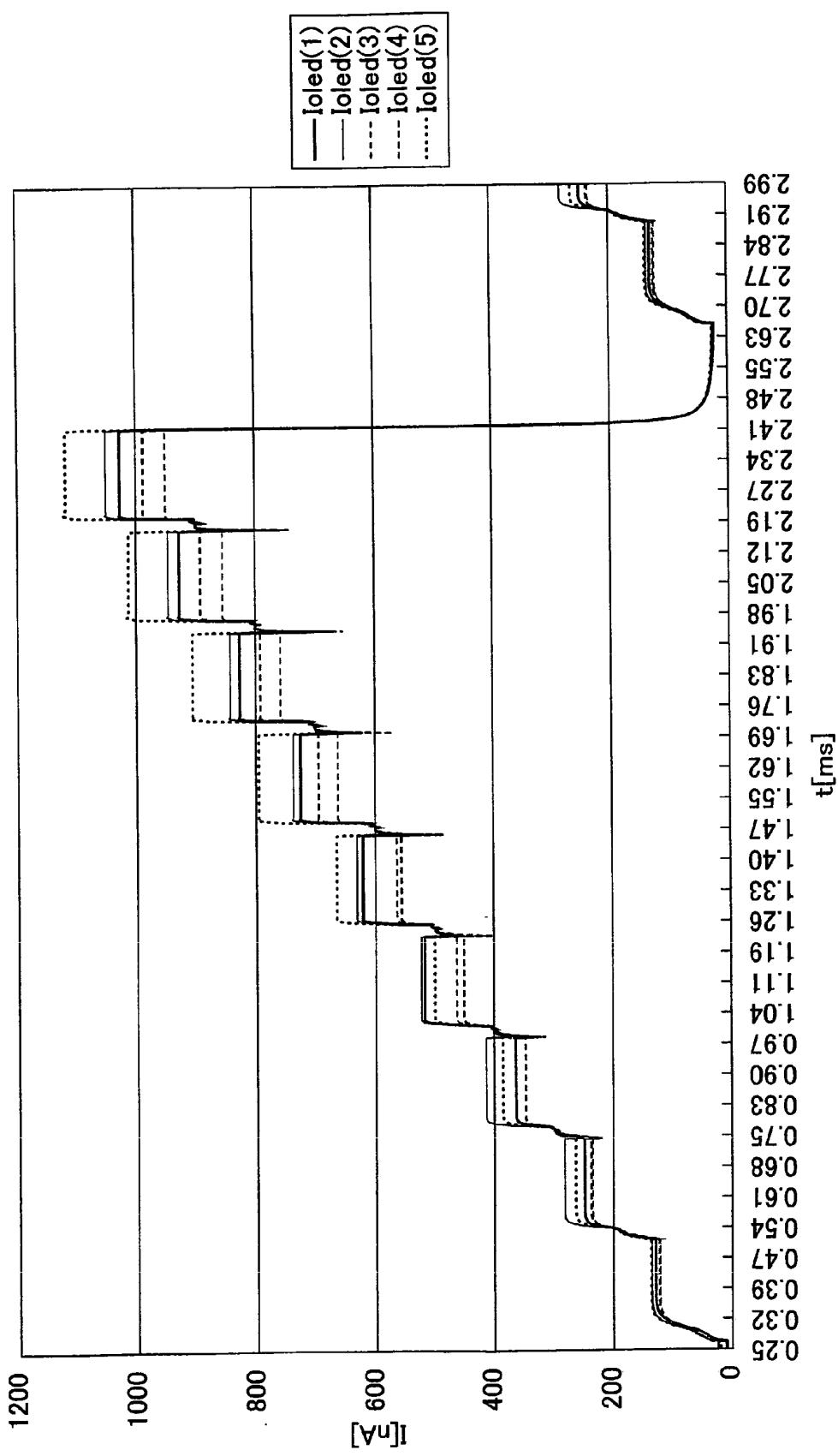

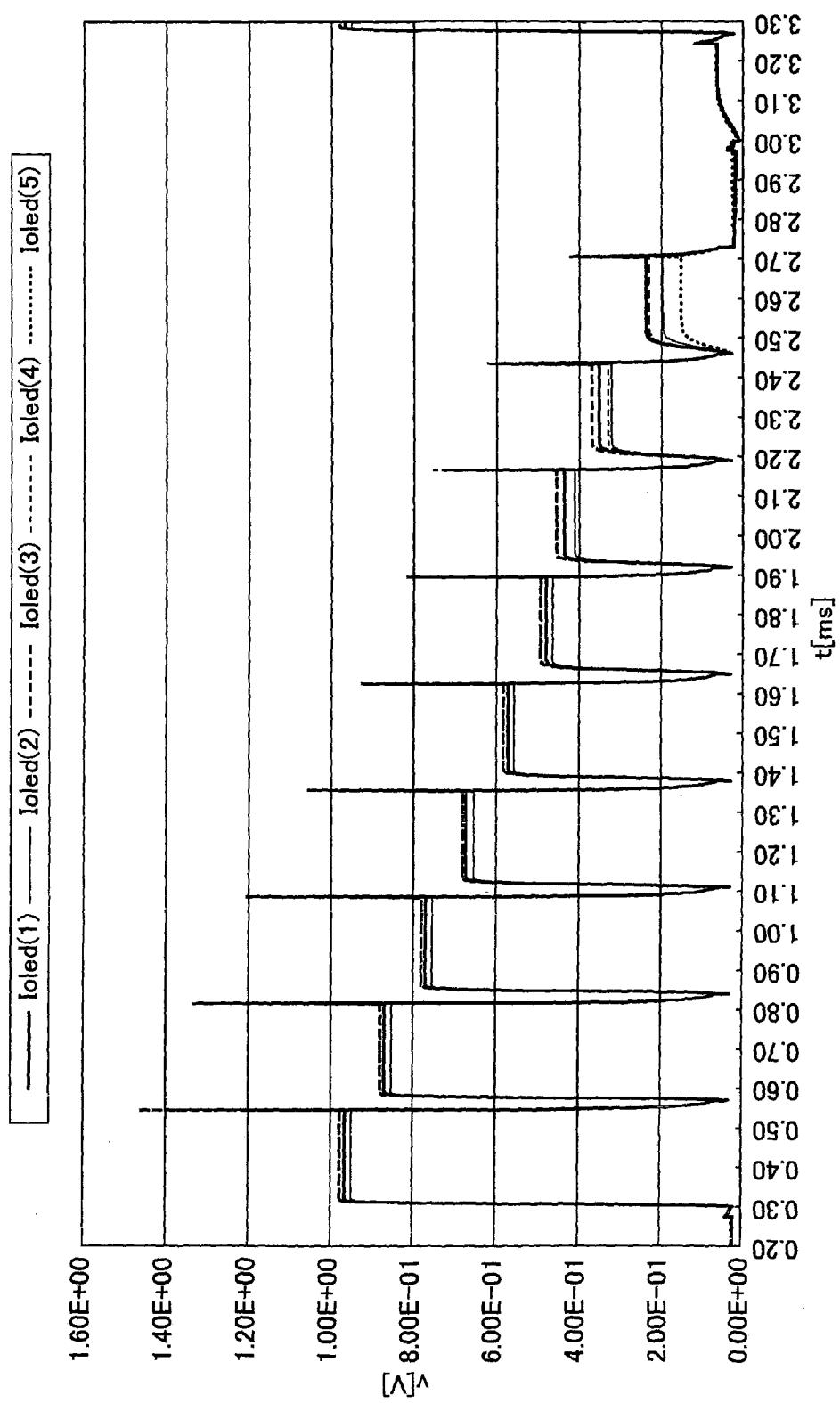

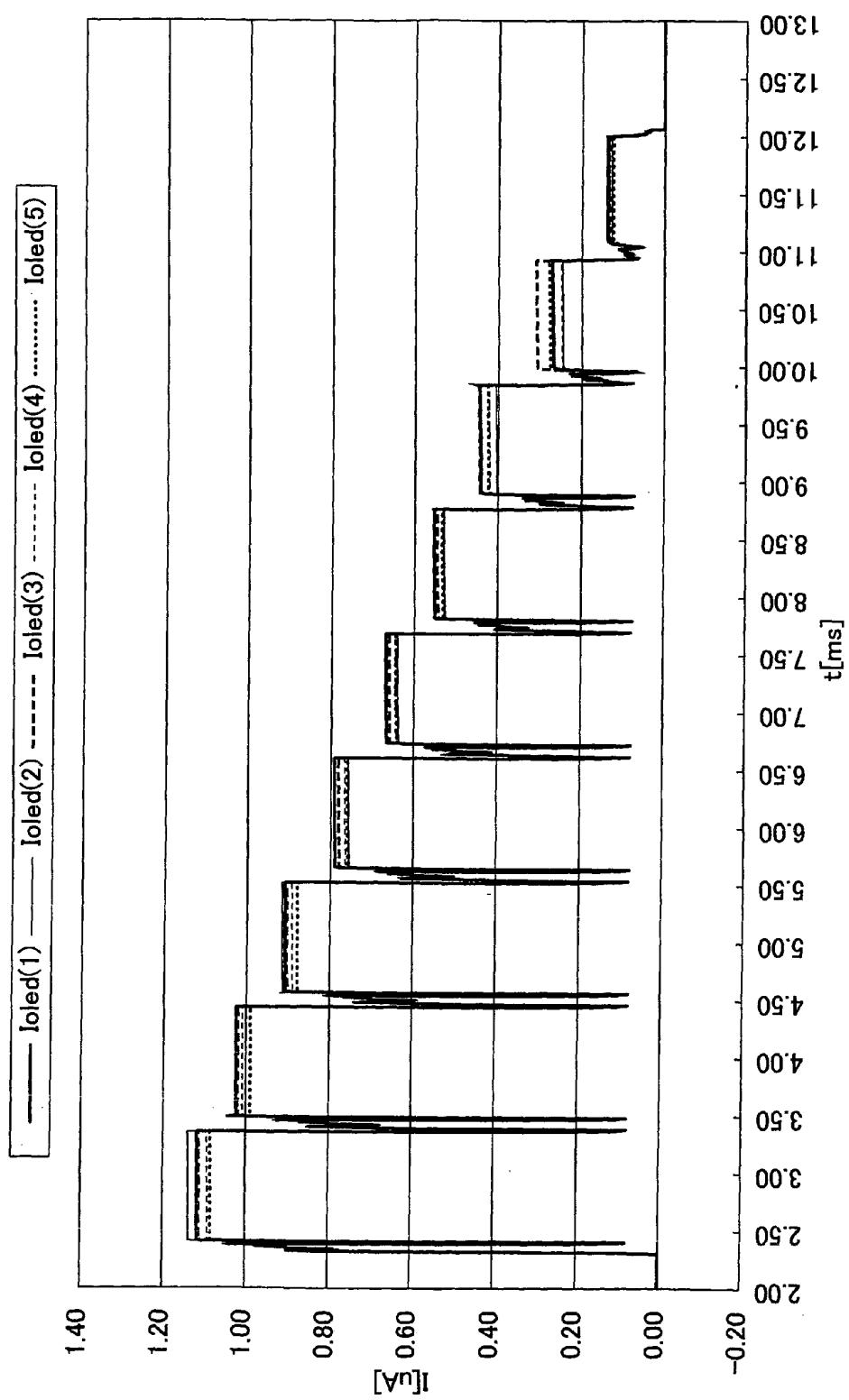

[0016] For the purpose of clarifying an adverse effect of such variation of the current, a simulation was carried out under the following five conditions shown in Table 1 below. The simulation found respective values of currents flowing to the organic EL element 109. The simulation result is shown in Fig. 25.

[Table 1]

|                   | Ioled(1)      | Ioled(2)          | Ioled(3)          | Ioled(4)          | Ioled(5)          |

|-------------------|---------------|-------------------|-------------------|-------------------|-------------------|

| Threshold voltage | Average value | Lower limit value | Upper limit value | Upper limit value | Lower limit value |

| Mobility          | Average value | Lower limit value | Upper limit value | Lower limit value | Upper limit value |

[0017] In the simulation shown in Fig. 25, the selection period came every 0.24 ms. During an initial period of time from 0.27 ms to 0.51 ms, a current of 0.1  $\mu$ A flowed to the source wire Sj. Thereafter, the current was increased by 0.1  $\mu$ A every 0.24 ms until the current had a value of 0.9  $\mu$ A. Then, the current was set at 0. After that, the current was increased again by 0.1  $\mu$ A.

[0018] Specifically, a first selection period corresponds to a period of time from 0.27 ms to 0.30 ms. The current, which had a value of 0.1  $\mu$ A and which was flowing to the source wire Sj during the selection period, determined the potential of the gate terminal of the driving TFT 108. This determined that the current of 0.1  $\mu$ A flowed to the organic EL element 109 only during the selection period. Note that the gate potential on this occasion was retained during a following non-selection period continuing from 0.31 ms to 0.51 ms; however, the current flowing to the organic EL element 109 during the non-selection period varied in a range from 0.12  $\mu$ A to 0.13  $\mu$ A.

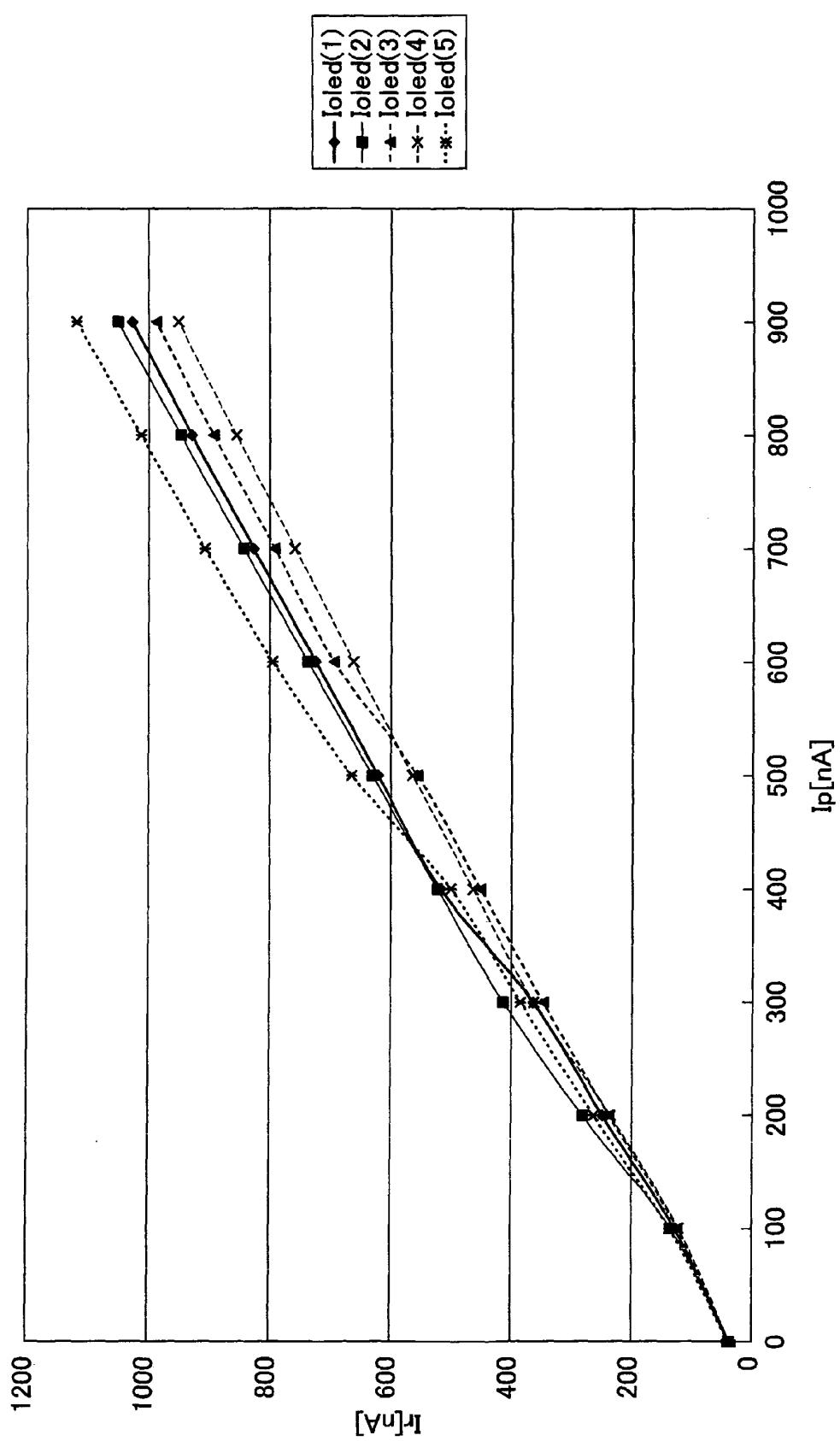

[0019] The variation found by the simulation is illustrated in Fig. 26 whose horizontal axis plots the respective currents (the respective ten currents of 0 to 0.9  $\mu$ A) which flowed to the source wire Sj, and whose vertical axis plots respective currents which flowed to the organic EL element 109 during the non-selection periods, each of which came after each current supply to the source wire Sj. In Fig. 26, during the non-selection period coming after the supply of the current of 0.9  $\mu$ A to the source wire Sj, the current that flowed through the organic EL element 109 varied in a range of about 0.95  $\mu$ A to about 1.12  $\mu$ A (increases by 5% to 24%).

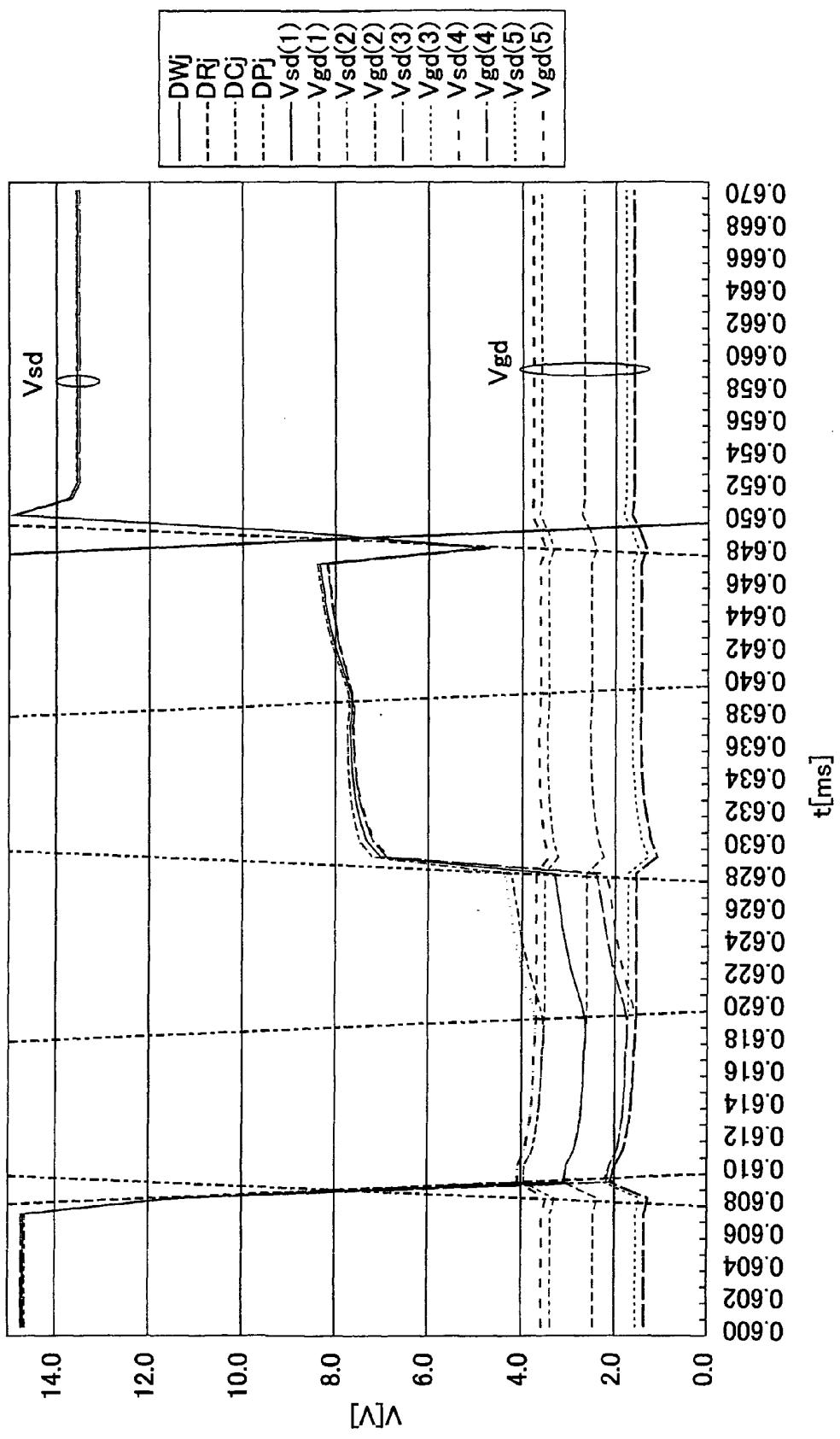

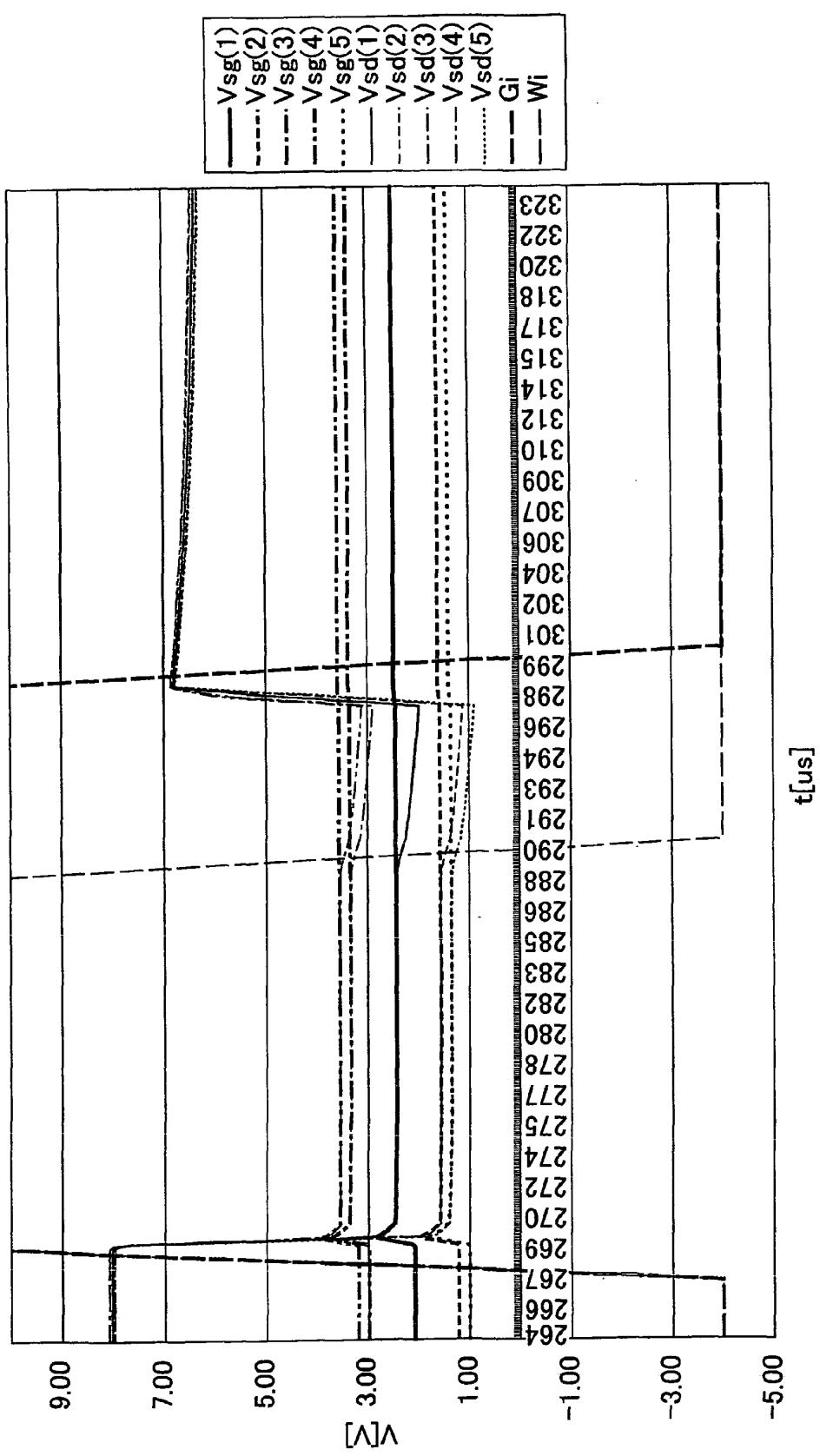

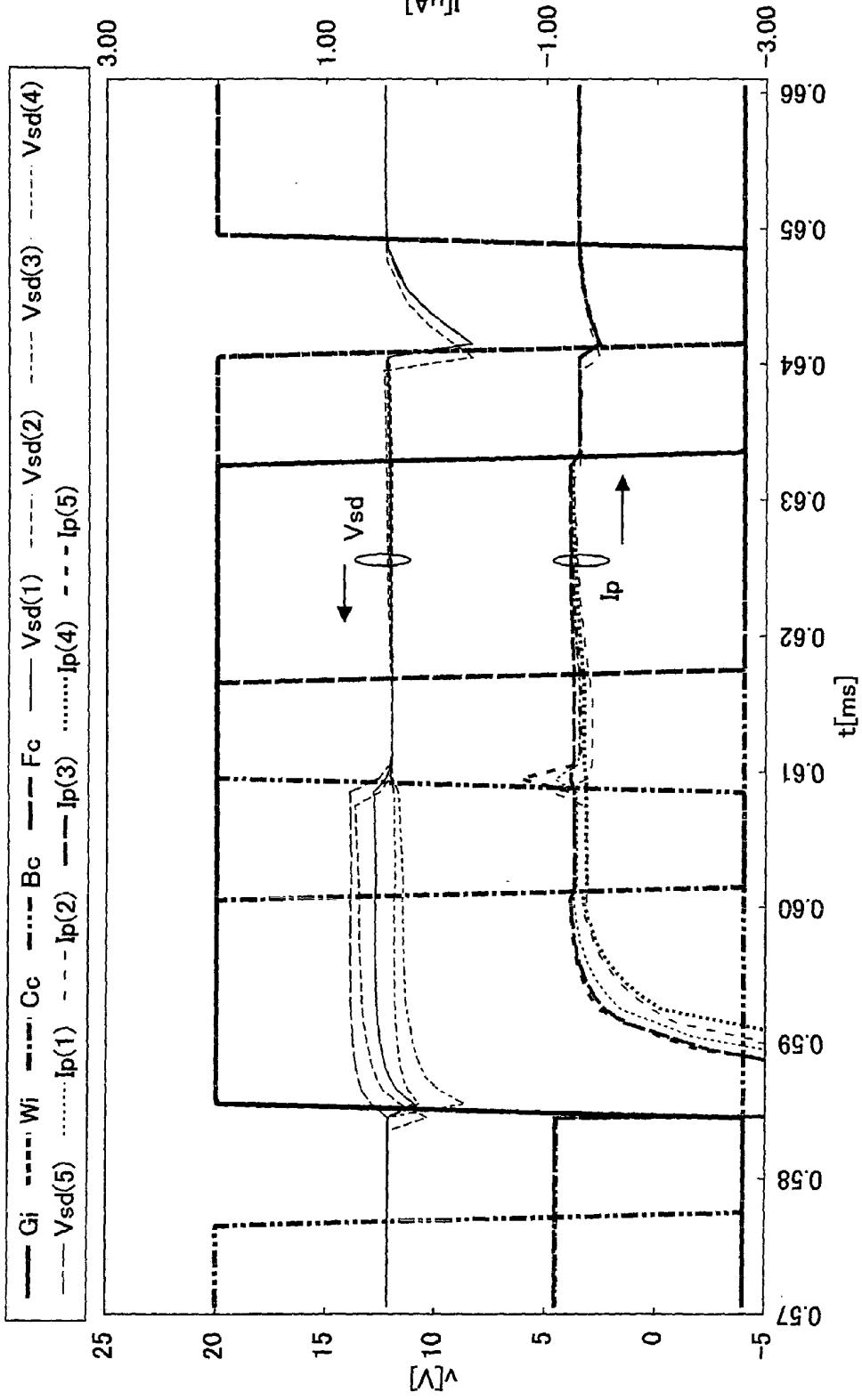

[0020] Such variation is caused by a difference between (i) a source-drain voltage Vsd of the driving TFT 108 during the selection period (period of time from approximately 270  $\mu$ s to approximately 300  $\mu$ s), and (ii) a source-voltage Vs during the non-selection period (period other than the selection period), as shown in Fig. 27. Note that Fig. 27 illustrates a result of a simulation carried out under the five conditions (see Table 2) of the threshold voltage and the mobility of the driving TFT 108. Note also that voltage values Vsg (1) through Vsg (5) respectively correspond to the conditions Ioled (1) through Ioled (5) (see Table 2), and that voltage values Vsd (1) through Vsd (5) respectively correspond to the conditions Ioled (1) through Ioled (5).

[0021] Namely, in the circuit structure shown in Fig. 23, the switching TFT 112 was ON upon the current writing (period of time from 0 to 2t1 in Fig. 24; period of time from about 270  $\mu$ s to about 290  $\mu$ s in Fig. 27) carried out during the selection period, so that each source-drain voltage Vsd coincided with each source-gate voltage Vsg, as shown in Fig. 27.

[0022] The source-gate potential Vsg that the driving TFT 108 had on this occasion was determined according to the threshold voltage of the driving TFT 108 and the mobility thereof. Specifically, comparing (i) a case where the threshold voltage is 1 V with (ii) a case where the threshold voltage is 2V, the source-gate voltages Vsg varies by on the order of 1V. In fact, the above simulation result shows that the source-gate voltage Vsg varied in a range from about 1.4 V to about 3.6 V when the current of 0.1  $\mu$ A was supplied to the source wire Sj.

[0023] Thereafter, when the switching TFT 112 was turned OFF (at about 290  $\mu$ s), the source-gate potential of the driving TFT 108 was retained; however, the source-drain voltage Vsd thereof was changed.

[0024] Especially after the pixel circuit was brought into the non-selection period (at about 300  $\mu$ s), the source-drain voltage Vsd was changed to be approximately 6 V. The voltage Vsd is determined according to "applied-voltage/current property" of the organic EL element 109. The wording "applied-voltage/current property" refers to a property indicating a relation between the applied voltage and the current. In other words, the voltage Vsd is determined according to a

voltage  $V_{oled}$  required for the supply of the current of  $0.1 \mu\text{A}$  to the organic EL element 109. In the simulation, the voltage  $V_{oled}$  had such a property as to satisfy:

$$V_{oled} = V_s - 6V$$

Further, the applied-voltage/current property of the organic EL element 109 is similar to a property of a diode (the current exponentially increases in response to the applied voltage). For this reason, even when the current flowing through the organic EL element 109 varies by several ten percent, the source-drain voltage of the driving TFT 108 does not vary greatly.

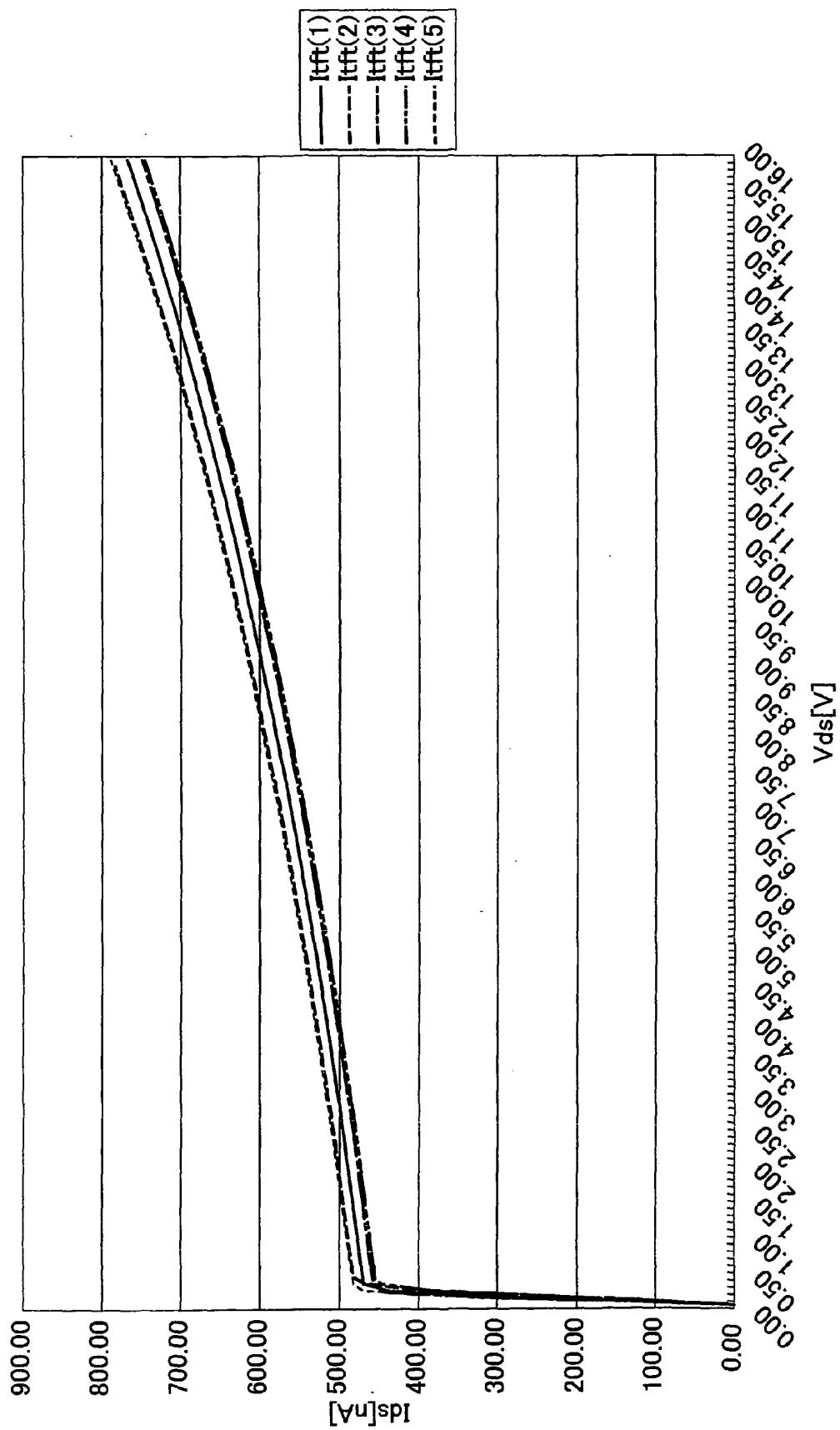

**[0025]** If the driving TFT 108 were an ideal TFT, the change of the source-drain voltage would never cause the change of the current flowing from the source terminal of the driving TFT 108 to the drain terminal thereof, in cases where the gate-source potential  $V_{sg}$  is constant, and where the source-drain voltage  $V_{sd}$  is larger than the gate-source potential  $V_{sg}$ . However, in an actual TFT, even in cases where a gate-source potential  $V_{sg}$  is constant, a current flowing from a source terminal of the TFT to a drain terminal thereof increases as a source-drain voltage  $V_{sd}$  increases, as shown in Fig. 28. Note that Fig. 28 illustrates a result of a simulation carried out under the five conditions (see Table 2) of the threshold and the mobility of the driving TFT 108. Note also that current values  $I_{tft}(1)$  through  $I_{tft}(5)$  respectively correspond to the conditions  $loled(1)$  through  $loled(5)$  (see Table 2).

**[0026]** The result shown in Fig. 28 indicates that the variation of the source-drain voltage  $V_{sd}$  upon the current writing causes the variation of the current flowing from the source to the drain during the non-selection period. This changes the current flowing through the organic EL element 109.

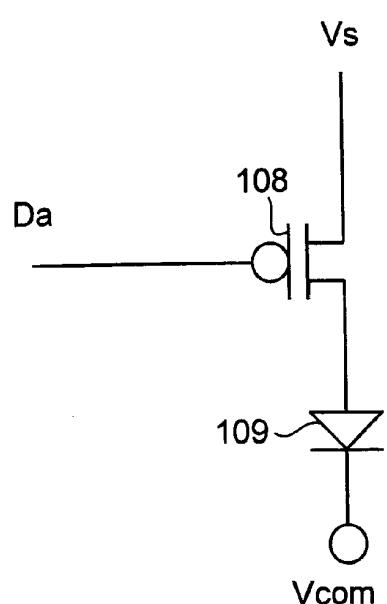

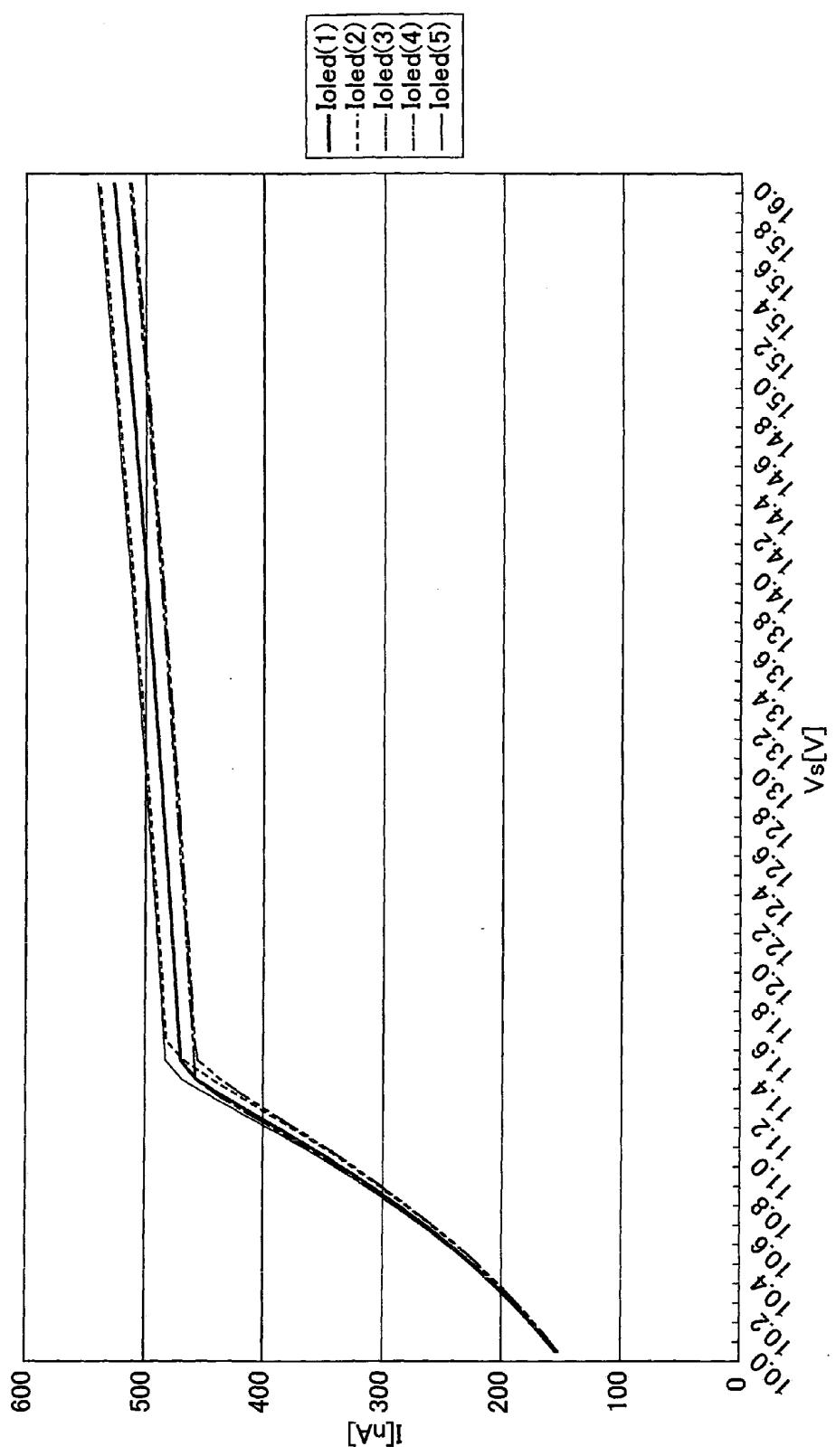

**[0027]** So, an examination was carried out in order to find such current variation between the source terminal of the driving TFT 108 and the drain terminal thereof, with the use of a circuit in which the driving TFT 108 and the organic EL element 109 are provided in series as shown in Fig. 29. The examination is carried out by simulating a current flowing through the organic EL element 109, in the following manner under the aforesaid five conditions of the threshold voltage and the mobility of the driving TFT 108. That is, the simulation is carried out by (i) applying, to the gate terminal of the driving TFT 108, the gate-source potential  $V_{gd}$ , obtained upon the current writing (see Fig. 27), of the driving TFT 108; and (ii) changing a power source voltage  $V_s - V_{com}$ . A result of the simulation is shown in Fig. 30.

**[0028]** Fig. 30 shows a case of the gate-source potential  $V_{gd}$  upon the supply of a current of  $0.5 \mu\text{A}$  to the source wire  $S_j$ . In this case, the potential of the source wire  $S_j$  upon the current writing (See Fig. 27) was changed according to each of the conditions of the threshold voltage of the driving TFT 108 and the mobility thereof. This determined that the current of  $0.5 \mu\text{A}$  was supplied to the organic EL element 109. Therefore, the current flowing through the organic EL element 109 was changed, on condition that the potential of the power wire  $V_s$  is constant (16V).

**[0029]** In this way, the threshold voltage variation of the driving TFT, and the mobility variation thereof cause the variation of the source-drain voltage  $V_{sd}$  upon the current writing, with the result that the current flowing through the organic EL element varies during the non-selection period. Such a phenomenon occurs also in the pixel circuit structure shown in Fig. 22. As such, the conventional circuit structure suffers from such a problem that the threshold voltage variation of the driving TFT and the mobility variation thereof cause the variation of the current flowing through the organic EL element during the non-selection period.

**[0030]** The present invention is made to solve the problem, and its object is to provide a display apparatus that is able to restrain the variation of the current flowing through the organic EL element during the non-selection period, the variation of the current being caused by the threshold voltage variation of the driving TFT, and the mobility variation thereof.

## DISCLOSURE OF INVENTION

[0031] As described above, a first display apparatus of the present invention includes: (1) a first switching transistor, provided between (i) a current control terminal of the driving transistor and (ii) a current output terminal of the driving transistor; (2) a first capacitor, connected to the current control terminal of the driving transistor; and (3) a second capacitor, having a first terminal and a second terminal, the first terminal being connected to the current control terminal of the driving transistor, the second terminal being connected to (i) the current output terminal of the driving transistor via a second switching transistor, and (ii) a predetermined voltage line via a third transistor.

**[0032]** A pixel circuit structure and a source driver circuit structure each using the above structure allows the following effect. That is, during an output current setting period of the driving transistor of the circuit, the first switching transistor is ON, and a predetermined current is supplied to the driving transistor, with the result that the driving transistor is caused to have a current control terminal potential (potential  $V_x$ ) accommodating to threshold voltage variation of the driving transistor and mobility variation thereof. The current control terminal potential is retained by the first capacitor.

[0033] Also on this occasion, the first terminal of the first capacitor is electrically connected to the first terminal of

the second capacitor. Therefore, by turning OFF the second switching transistor and turning ON the third switching transistor, the second terminal of the second capacitor is electrically connected to the predetermined voltage line (which has a constant potential  $V_a$  allowing supply of the predetermined current). Moreover, this causes the second capacitor to retain a potential  $V_a - V_x$ . These operations are carried out during a first period.

**[0034]** Next, the second switching transistor is turned ON, and the third switching transistor is turned OFF, with the result that the second terminal of the second capacitor is electrically connected to the current output terminal (a drain terminal or a source terminal of a TFT) of the driving transistor. In cases where the driving transistor has a default current output terminal potential  $V_a$ , the driving transistor is caused to have the current control terminal potential (a gate potential of a TFT)  $V_x$ .

**[0035]** Thereafter, a desired current is supplied to the driving transistor, thereby changing the potential of the current control terminal (a gate terminal of a TFT) of the driving transistor. This determines the potential of the current control terminal (a gate terminal of a TFT), while the potential of the current input terminal of the driving transistor and the potential of the current output terminal thereof are substantially equal to each other irrespective of the threshold voltage variation and the mobility variation of the driving transistor.

**[0036]** Further, in a pixel circuit including the driving transistor, a supply of the predetermined current to the current driving light emitting element causes potential drops of the current driving light emitting element in the same manner. With this, while the potential of the current input terminal of the driving transistor is substantially equal to the potential of the current output terminal thereof, the potential of the current control terminal (a gate terminal of a TFT) of the driving transistor can be set such that the driving transistor outputs the predetermined current.

**[0037]** In the case of disconnecting the connection between the first capacitor and the second capacitor, the current control terminal potential of the driving transistor is retained by the first capacitor. On the other hand, in the case of maintaining the connection therebetween, the current control terminal potential of the driving transistor is retained by the first capacitor and the second capacitor. These operations are carried out during a second period.

**[0038]** Thereafter, during a non-selection period of the pixel circuit, the current input terminal-current output terminal potential of the driving transistor is changed; however, the changed potential is constant irrespective of the threshold voltage variation and the mobility variation of the driving transistor. This allows restraint of variation of a current flowing from the current input terminal of the driving transistor to the current output terminal thereof. As described above, a second display apparatus of the present invention includes: (1) a first switching transistor, provided between (i) a current control terminal of the driving transistor and (ii) a current input terminal of the driving transistor; (2) a first capacitor, connected to the current control terminal of the driving transistor; and (3) a second capacitor, having a first terminal and a second terminal, the first terminal being connected to the current control terminal of the driving transistor, the second terminal being connected to (i) the current input terminal of the driving transistor via a second switching transistor, and (ii) a predetermined voltage line via a third switching transistor.

**[0039]** A pixel circuit structure and a source driver circuit structure each using the above structure allows the following effect. That is, during an output current setting period of the driving transistor of the circuit, the first switching transistor is ON, and a predetermined current is supplied to the driving transistor, with the result that the driving transistor is caused to have a current control terminal potential (potential  $V_x$ ) accommodating to threshold voltage variation of the driving transistor and mobility variation thereof. The current control terminal potential is retained by the first capacitor.

**[0040]** On this occasion, the first terminal of the first capacitor is electrically connected to the first terminal of the second capacitor. Therefore, by turning OFF the second switching transistor and turning ON the third switching transistor, the second terminal of the second capacitor is electrically connected to the predetermined voltage line (which has a constant potential  $V_a$  allowing supply of the predetermined current). Moreover, this causes the second capacitor to retain a potential  $V_a - V_x$ . These operations are carried out during a first period.

**[0041]** Next, the second switching transistor is turned ON, and the third switching transistor is turned OFF, with the result that the second terminal of the second capacitor is electrically connected to the current input terminal (a drain terminal or a source terminal of a TFT) of the driving transistor. In cases where the driving transistor has a default current input terminal potential  $V_a$ , the driving transistor is caused to have the current control terminal potential (a gate potential of a TFT)  $V_x$ .

**[0042]** Thereafter, a desired current is supplied to the driving transistor, thereby changing the potential of the current control terminal (a gate terminal of a TFT) of the driving transistor. This determines the potential of the current control terminal (a gate terminal of a TFT), while the potential of the current input terminal of the driving transistor and the potential of the current output terminal thereof are substantially equal to each other irrespective of the threshold voltage variation and the mobility variation of the driving transistor.

**[0043]** Further, in a pixel circuit including the driving transistor, a supply of the predetermined current to the current driving light emitting element causes potential drops of the current driving light emitting element in the same manner. With this, while the potential of the current input terminal of the driving transistor is substantially equal to the potential of the current output terminal thereof, the potential of the current control terminal (a gate terminal of a TFT) of the driving transistor can be set such that the driving transistor outputs the predetermined current.

[0044] In the case of disconnecting the connection between the first capacitor and the second capacitor, the current control terminal potential of the driving transistor is retained by the first capacitor. On the other hand, in the case of maintaining the connection therebetween, the current control terminal potential of the driving transistor is retained by the first capacitor and the second capacitor. These operations are carried out during a second period.

5 [0045] Thereafter, during a non-selection period of the pixel circuit, the current input terminal-current output terminal potential of the driving transistor is changed; however, the changed potential is constant irrespective of the threshold voltage variation and the mobility variation of the driving transistor. This allows restraint of variation of a current flowing from the current input terminal of the driving transistor to the current output terminal thereof.

10 [0046] The aforementioned driving circuit structure is applicable to a pixel circuit structure for driving directly the current driving light emitting element, but may be applied to a source driver circuit for setting an output current of a driving transistor provided in a pixel circuit.

15 [0047] In cases where the driver circuit structure is used as the source driver circuit structure, the display apparatus may be arranged such that the first capacitor, the second capacitor, the first switching transistor, the second switching transistor, and the third switching transistor are provided in each source driver circuit.

20 [0048] In the case where the driver circuit structure is used as the source driver circuit structure, it is particularly preferable to provide, in a pixel circuit, another transistor for controlling a current that is to be supplied to a current driving light emitting element provided in the pixel circuit. An output current of the transistor in the pixel circuit is controlled by the driving transistor, a component of the source driver circuit.

25 [0049] On the other hand, in the case where the driver circuit structure is used as the pixel circuit structure, the display apparatus may be arranged such that the first capacitor, the second capacitor, the first switching transistor, the second switching transistor, and the third switching transistor are provided in each pixel circuit.

30 [0050] In the pixel circuit structure, the components, i.e., the first capacitor, the second capacitor, the first switching transistor, the second switching transistor, and the third switching transistor are all provided in the pixel circuit. With this, a conventional source driver circuit can be used as the source driver circuit for driving the pixel circuit.

35 [0051] This allows reduction of a stray capacitance between the first capacitor and the second capacitor, and the current writing period of the driving transistor can be accordingly shorter.

40 [0052] The display apparatus may be arranged such that: one or more of the first capacitor, the second capacitor, the first switching transistor, the second switching transistor, and the third switching transistor are provided in a pixel circuit, and the others are provided in a portion outside the pixel circuit, which portion includes a source driver circuit.

45 [0053] The structure allows restraint of an increase in the number of capacitors and transistors required for each pixel circuit, as compared with a pixel circuit in which all the components are provided. This is because one or more of the first capacitor, the second capacitor, and the first switching transistor, and the second switching transistor, and the third switching transistor are provided in the source driver circuit or the portion outside the pixel circuit. This makes it possible to obtain desired luminance in each unit area without greater emission of each organic EL element of a display apparatus employing the bottom emission structure (such a structure that light is emitted toward a transparent substrate having TFT elements), as compared with the conventional technique. On this account, the organic EL element can have a longer luminance half-life. In contrast, see a case of a display apparatus employing a top emission structure (such a structure that light is emitted toward a side opposite to a transparent substrate having TFT elements). In this case, the number of elements provided in a pixel never increases, so that each pixel size can be as small as a pixel size in the conventional technique.

50 [0054] Further, the display apparatus may be arranged such that: the current driving light emitting element, the driving transistor, and the first capacitor are provided in the pixel circuit; and the second capacitor, the first switching transistor, the second switching transistor, and the third switching transistor are provided in the source driver circuit or the portion outside the pixel circuit, the display apparatus further includes a connecting wire for connecting the current control terminal of the driving transistor to the first terminal of the second capacitor.

55 [0055] The above structure makes it possible to provide a specific structure of a display apparatus in which one or more of the first capacitor, the second capacitor, the first switching transistor, the second switching transistor, and the third switching transistor are provided in the source driver circuit or the portion outside the pixel circuit. Note that a stray capacitance tends to exist in the connecting wire for connecting the current control terminal of the driving transistor to the first terminal of the second capacitor. Therefore, the first capacitor is caused to have a capacitance equal to a total of the stray capacitance and the capacitance of the capacitor provided in the pixel.

[0056] For this reason, when the second capacitor has a small capacitance, the potential of the second terminal of the second capacitor is required to be increased. However, the great change in the potential of the second terminal of the second capacitor causes great variation of the source-drain potential of the driving transistor, so that this is not preferable. Therefore, the second capacitor is required to have a larger capacitance. This causes the current writing period of the driving transistor to be long.

[0057] In consideration of this, a circuit made up of the second capacitor and the first switching transistor is provided adjacent to the pixel so as to be shared with a plurality of pixel, even though this structure suffers from such a problem

that: acquirement of desired luminance in each unit area requires more emission of the organic EL element due to the decrease of the pixel area.

[0058] For example, one structure made up of the second capacitor and the first switching transistor is provided for every two pixels. This makes it possible to shorten a length of the connecting wire for connecting the current control terminal of the driving transistor to the first terminal of the second capacitor.

[0059] As the result, the stray capacitance of the connecting wire can be restrained, so that the source-drain potential of the driving transistor does not vary greatly even when the second capacitor has a small capacitance. With this, the current writing period of the driving transistor can be shortened.

[0060] Further, the display apparatus may be arranged such that: the current driving light emitting element, the driving transistor, the first switching transistor, the first capacitor, and the second capacitor are provided in the pixel circuit; the second switching transistor and the third switching transistor are provided in the source driver circuit or the portion outside the pixel circuit; and the display apparatus further includes a connecting wire for connecting the second terminal of the second capacitor to (i) the current output terminal of the driving transistor, or (ii) the current input terminal of the driving transistor.

[0061] The above structure makes it possible to provide a specific structure of a display apparatus in which one or more of the first capacitor, the second capacitor, the first switching transistor, the second switching transistor, and the third switching transistor are provided in the source driver circuit or the portion outside the pixel circuit. Further, the display apparatus further includes:

an OFF potential line for supplying an OFF potential; wherein: the connecting wire is connected to the OFF potential line via a fourth switching transistor.

[0062] The above structure makes it possible to supply an OFF potential from the OFF potential line, via the fourth switching transistor and the connecting wire or the source wire, to a current control terminal of a driving transistor of a pixel to be brought into a dark state. The OFF potential surely turns OFF the driving transistor. This allows acquirement of sufficiently low luminance in the pixel in the dark state, thereby improving a contrast in the display apparatus.

[0063] Further, as described above, a first driving method of the present invention includes the steps of: (1) electrically connecting a current control terminal of the driving transistor to a first terminal of a first capacitor; (2) electrically connecting, during a current writing period of the driving transistor, the first terminal of the first capacitor to a first terminal of a second capacitor; (3) during a first period, (i) electrically connecting a second terminal of the second capacitor to a predetermined voltage line, and (ii) electrically connecting the current control terminal of the driving transistor to a current output terminal of the driving transistor, and (iii) causing the first capacitor and the second capacitor to retain a current control terminal potential that the driving transistor has on this occasion; (4) during a second period, (i) correcting the current control terminal potential by disconnecting the current control terminal of the driving transistor from the current output terminal of the driving transistor, and by changing electric connection of the second terminal of the second capacitor from the predetermined voltage line to the current output terminal of the driving transistor, and (ii) causing, during the second period, the first capacitor to retain the current control terminal potential that the driving transistor has on this occasion; and (5) controlling, during a current readout period of the driving transistor, an output current of the driving transistor with the use of the current control terminal potential, retained by the first capacitor, of the driving transistor.

[0064] The driving method allows the following effect. That is, during a first period within the output current setting period of the driving transistor of the pixel circuit and the source driver circuit, a predetermined current is supplied to the driving transistor, with the result that the driving transistor is caused to have a current control terminal potential (potential  $V_x$ ) accommodating to threshold voltage variation of the driving transistor and mobility variation thereof. The current control terminal potential is retained by the first capacitor and the second capacitor. On this occasion, the first terminal of the first capacitor is electrically connected to the first terminal of the second capacitor. Therefore, the second terminal of the second capacitor is electrically connected to the predetermined voltage line (which has a constant potential  $V_a$  allowing supply of the predetermined current). This causes the second capacitor to retain a potential  $V_a - V_x$ .

[0065] Next, the second terminal of the second capacitor is electrically connected to the current output terminal (a drain terminal or a source terminal of a TFT) of the driving transistor. In cases where the driving transistor has a current output terminal potential  $V_a$  on this occasion, the driving transistor is caused to have the current control terminal potential (a gate potential of a TFT)  $V_x$ .

[0066] Thereafter, a desired current is supplied to the driving transistor, thereby changing the potential of the current control terminal (a gate terminal of a TFT) of the driving transistor. This determines the potential of the current control terminal (a gate terminal of a TFT), while the potential of the current input terminal of the driving transistor and the potential of the current output terminal thereof are substantially equal to each other irrespective of the threshold voltage variation and the mobility variation of the driving transistor. Further, a supply of the predetermined current to the current driving light emitting element causes potential drops of the current driving light emitting element in the same manner.

With this, while the potential of the current input terminal of the driving transistor is substantially equal to the potential of the current output terminal thereof, the potential of the current control terminal (a gate terminal of a TFT) of the driving transistor can be set such that the driving transistor outputs the predetermined current.

**[0067]** In the case of disconnecting the connection between the first capacitor and the second capacitor, the current control terminal potential that the driving transistor has on this occasion is retained by the first capacitor. On the other hand, in the case of maintaining the connection therebetween, the current terminal potential of the driving transistor is retained by the first capacitor and the second capacitor.

**[0068]** Thereafter, during the current readout period of the driving transistor, the current input terminal-current output terminal potential of the driving transistor is changed; however, the changed potential is constant irrespective of the threshold voltage variation and the mobility variation of the driving transistor. This allows restraint of variation of a current flowing from the current input terminal of the driving transistor to the current output terminal thereof.

**[0069]** Further, a second driving method of the present invention includes the steps of: (1) electrically connecting a current control terminal of the driving transistor to a first terminal of a first capacitor; (2) electrically connecting, during a current writing period of the driving transistor, the first terminal of the first capacitor to a first terminal of a second capacitor; (3) during a first period, (i) electrically connecting a second terminal of the second capacitor to a predetermined voltage line, and (ii) electrically connecting the current control terminal of the driving transistor to a current input terminal of the driving transistor, and (iii) causing the first capacitor and the second capacitor to retain a current control terminal potential that the driving transistor has on this occasion; (4) during a second period, (i) correcting the current control terminal potential by disconnecting the current control terminal of the driving transistor from the current input terminal of the driving transistor, and by changing electric connection of the second terminal of the second capacitor from the predetermined voltage line to the current input terminal of the driving transistor, and (ii) causing the first capacitor to retain the current control terminal potential that the driving transistor has on this occasion; and (5) controlling, during a current readout period of the driving transistor, an output current of the driving transistor with the use of the current control terminal potential, retained by the first capacitor, of the driving transistor.

**[0070]** The driving method allows the following effect. That is, during a first period within the output current setting period of the driving transistor of the pixel circuit and the source driver circuit, a predetermined current is supplied to the driving transistor, with the result that the driving transistor is caused to have a current control terminal potential (potential  $V_x$ ) accommodating to threshold voltage variation of the driving transistor and mobility variation thereof. The current control terminal potential is retained by the first capacitor and the second capacitor. On this occasion, the first terminal of the first capacitor is electrically connected to the first terminal of the second capacitor. Therefore, the second terminal of the second capacitor is electrically connected to the predetermined voltage line (which has a constant potential  $V_a$  allowing supply of the predetermined current). This causes the second capacitor to retain a potential  $V_a - V_x$ .

**[0071]** Next, the second terminal of the second capacitor is electrically connected to the current input terminal (a drain terminal or a source terminal of a TFT) of the driving transistor. In cases where the driving transistor has a current input terminal potential  $V_a$  on this occasion, the driving transistor is caused to have the current control terminal potential (a gate potential of a TFT)  $V_x$ .

**[0072]** Thereafter, a desired current is supplied to the driving transistor, thereby changing the potential of the current control terminal (a gate terminal of a TFT) of the driving transistor. This determines the potential of the current control terminal (a gate terminal of a TFT), while the potential of the current input terminal of the driving transistor and the potential of the current output terminal thereof are equal to each other irrespective of the threshold voltage variation and the mobility variation of the driving transistor.

**[0073]** Further, in cases where the driving transistor is provided in the pixel circuit, the supply of the predetermined current to the current driving light emitting element causes potential drops of the current driving light emitting element in the same manner. With this, while the potential of the current input terminal of the driving transistor is substantially equal to the potential of the current output terminal thereof, the potential of the current control terminal (a gate terminal of a TFT) of the driving transistor can be set such that the driving transistor outputs the predetermined current.

**[0074]** In the case of disconnecting the connection between the first capacitor and the second capacitor, the current control terminal potential of the driving transistor is retained by the first capacitor. On the other hand, in the case of maintaining the connection therebetween, the current terminal potential of the driving transistor is retained by the first capacitor and the second capacitor.

**[0075]** Thereafter, during the non-selection period of the pixel circuit, the current input terminal-current output terminal potential of the driving transistor is changed; however, the changed potential is constant irrespective of the threshold voltage variation and the mobility variation of the driving transistor. This allows restraint of variation of a current flowing from the current input terminal of the driving transistor to the current output terminal thereof.

**[0076]** As such, the first and second driving methods of the present invention are beneficial in reducing the difference between (i) the current flowing during the current writing period of the driving transistor constituting the pixel circuit, and (ii) the current flowing during the current readout period of thereof. Moreover, the methods are beneficial in reducing the difference between (i) the current flowing during the current writing period of the driving transistor constituting the

source driver, and (ii) the current flowing during the current readout period of thereof.

**[0077]** In the latter case, a display by the current driving light emitting element can be uniformly carried out by supplying, to the current driving light emitting element, an output current of each transistor (each transistor, other than the driving transistor, for controlling current supply to the current driving light emitting element of each pixel circuit), which output current is as large as the current flowing through the driving transistor. The transistors and the light emitting element are provided in a matrix manner.

**[0078]** Further, in the first and second driving methods of the present invention, when the second terminal of the second capacitor has the aforesaid potential  $V_a$  during the second period, the potential of the current control terminal (gate terminal of the TFT) of the driving transistor is caused to have the aforesaid potential  $V_x$ . For this reason, it is preferable that: the second terminal of the second capacitor stay electrically connected to the predetermined voltage line even after the start of the second period, and then the electric connection be disconnected. This shortens time taken for the second terminal of the second capacitor to have the final potential. Accordingly, a larger number of gate wires can be driven, with result that a larger number of pixels can be used for a display.

**[0079]** Specifically, the second terminal of the second capacitor will have a final potential as large as the potential  $V_a$  of the predetermined voltage line. Therefore, the time taken for the acquirement of such a final potential can be shortened by causing the second terminal of the second capacitor to have a potential  $V_a$  in advance.

**[0080]** This is a preferable driving example of the driving methods of the present invention. See a case where the driving example is applied to the first driving method. That is, the electric connection is disconnected between the current control terminal of the driving transistor and the current output terminal thereof, and then the second terminal of the second capacitor is electrically connected to the current output terminal of the driving transistor while maintaining the electric connection with the predetermined voltage line. The maintained electric connection with the predetermined voltage line causes the second terminal of the second capacitor to have a potential as large as the potential  $V_a$  of the predetermined voltage line. After this, the second terminal of the second capacitor is electrically disconnected from the predetermined voltage line.

**[0081]** On the other hand, see a case where the driving example is applied to the second driving method. That is, the electric connection is disconnected between the current control terminal of the driving transistor and the current input terminal thereof, and then the second terminal of the second capacitor is electrically connected to the current input terminal of the driving transistor while maintaining the electric connection with the predetermined voltage line. The maintained electric connection with the predetermined voltage line causes the second terminal of the second capacitor to have a potential as large as the potential  $V_a$  of the predetermined voltage line. After this, the second terminal of the second capacitor is electrically disconnected from the predetermined voltage line.

**[0082]** Additional objects, features, and strengths of the present invention will be made clear by the description below. Further, the advantages of the present invention will be evident from the following explanation in reference to the drawings.

#### 35 BRIEF DESCRIPTION OF DRAWINGS

##### **[0083]**

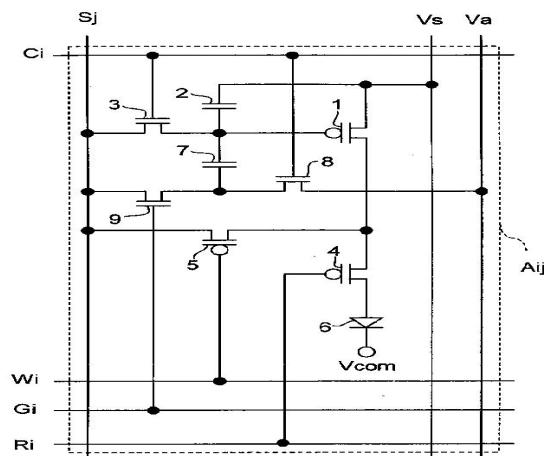

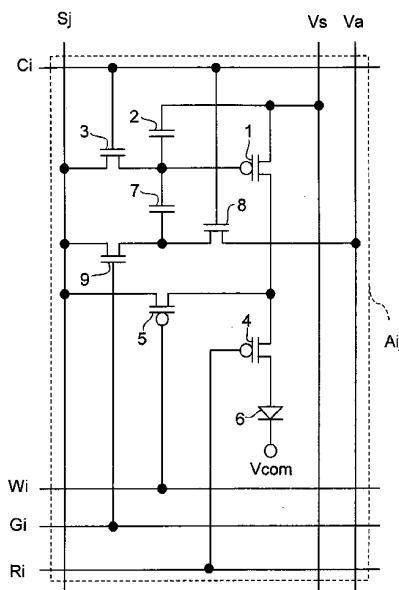

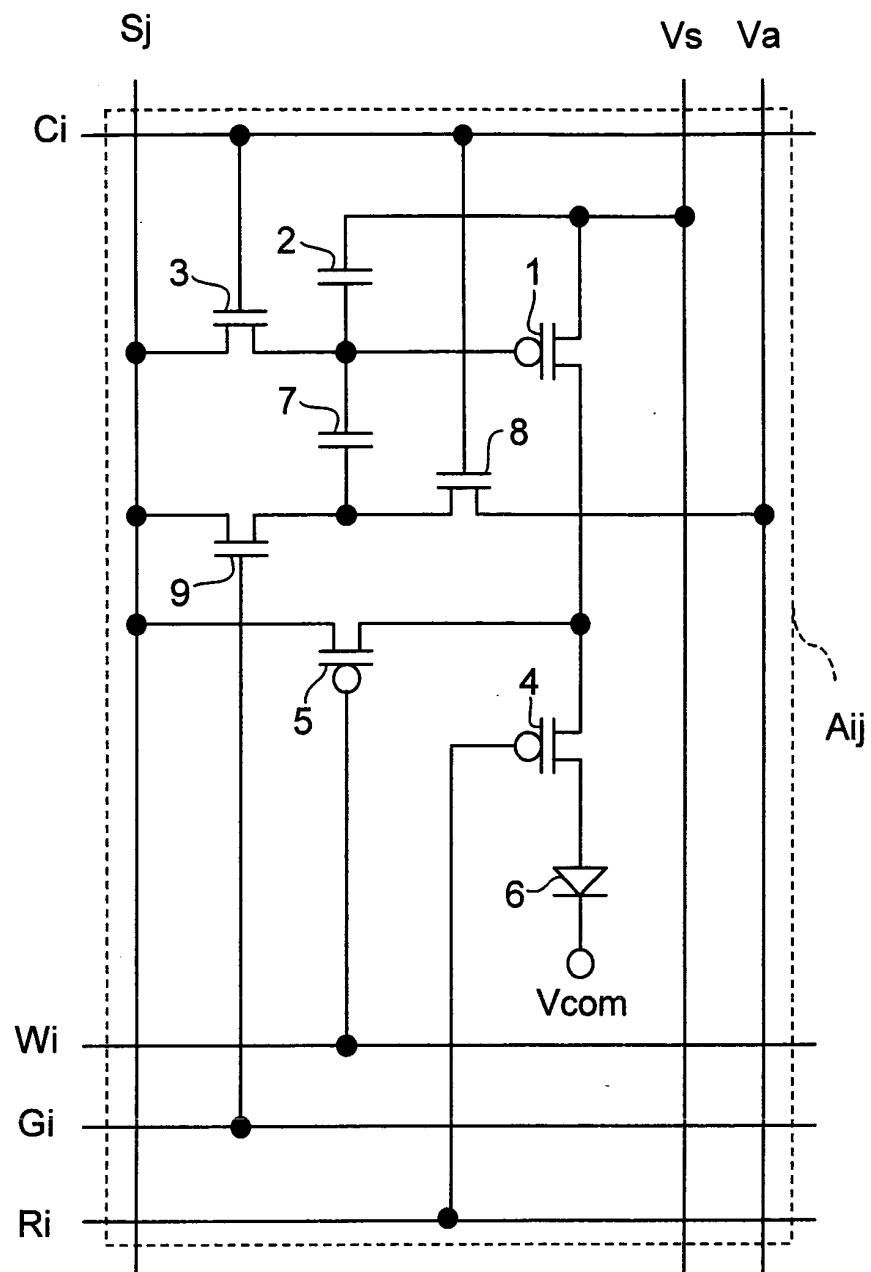

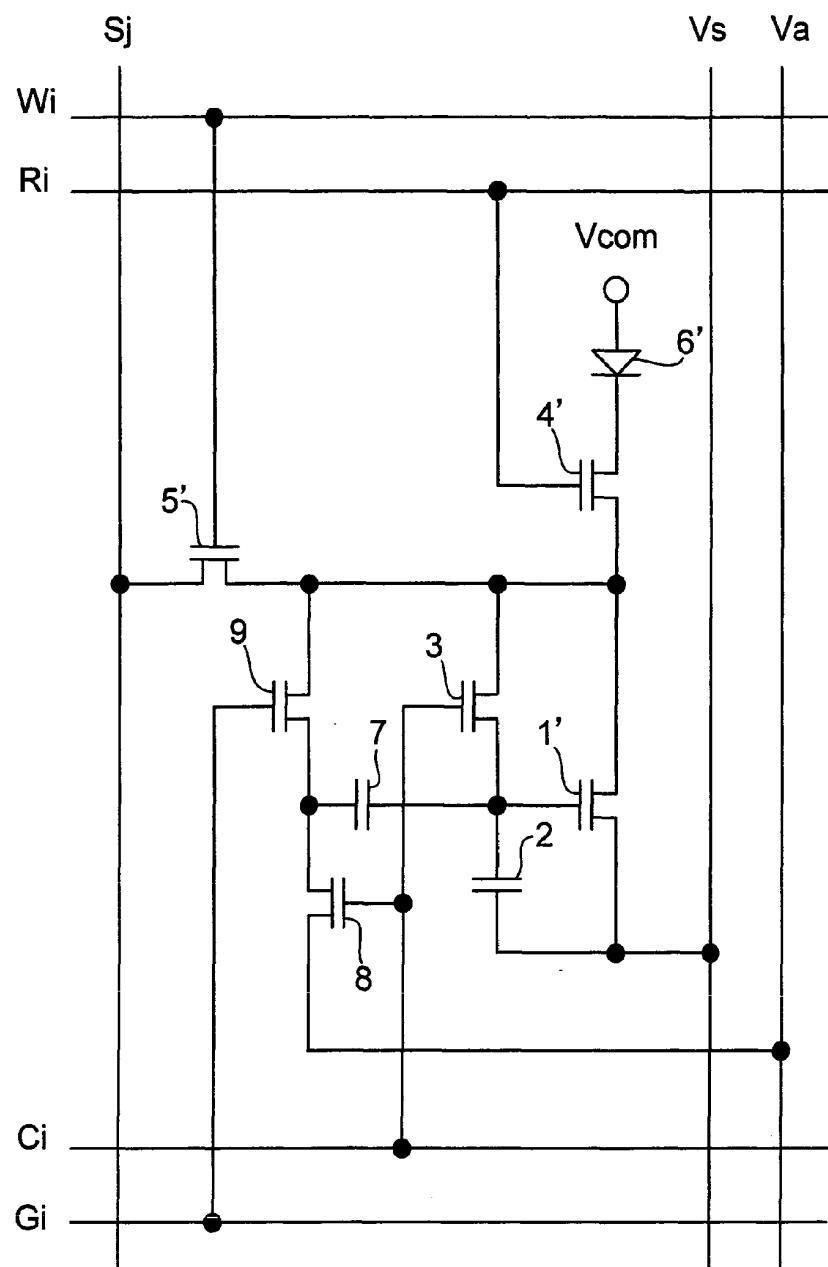

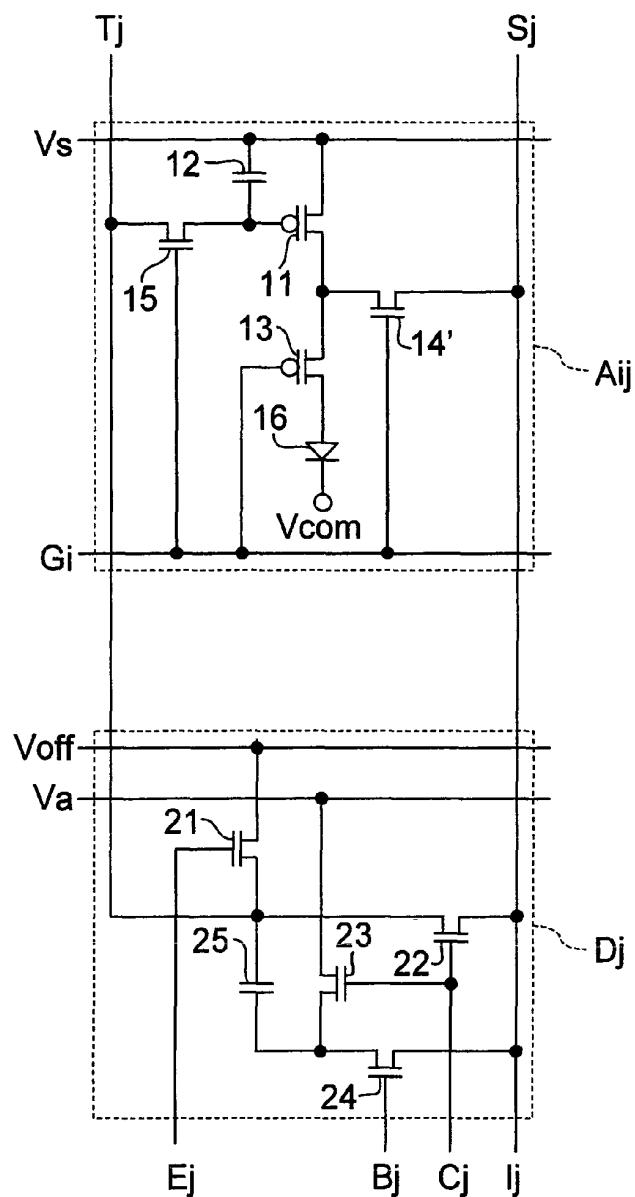

40 Fig. 1 illustrates one embodiment of the present invention, and is a circuit diagram illustrating a structure of a pixel circuit of a display apparatus according to Embodiment 1.

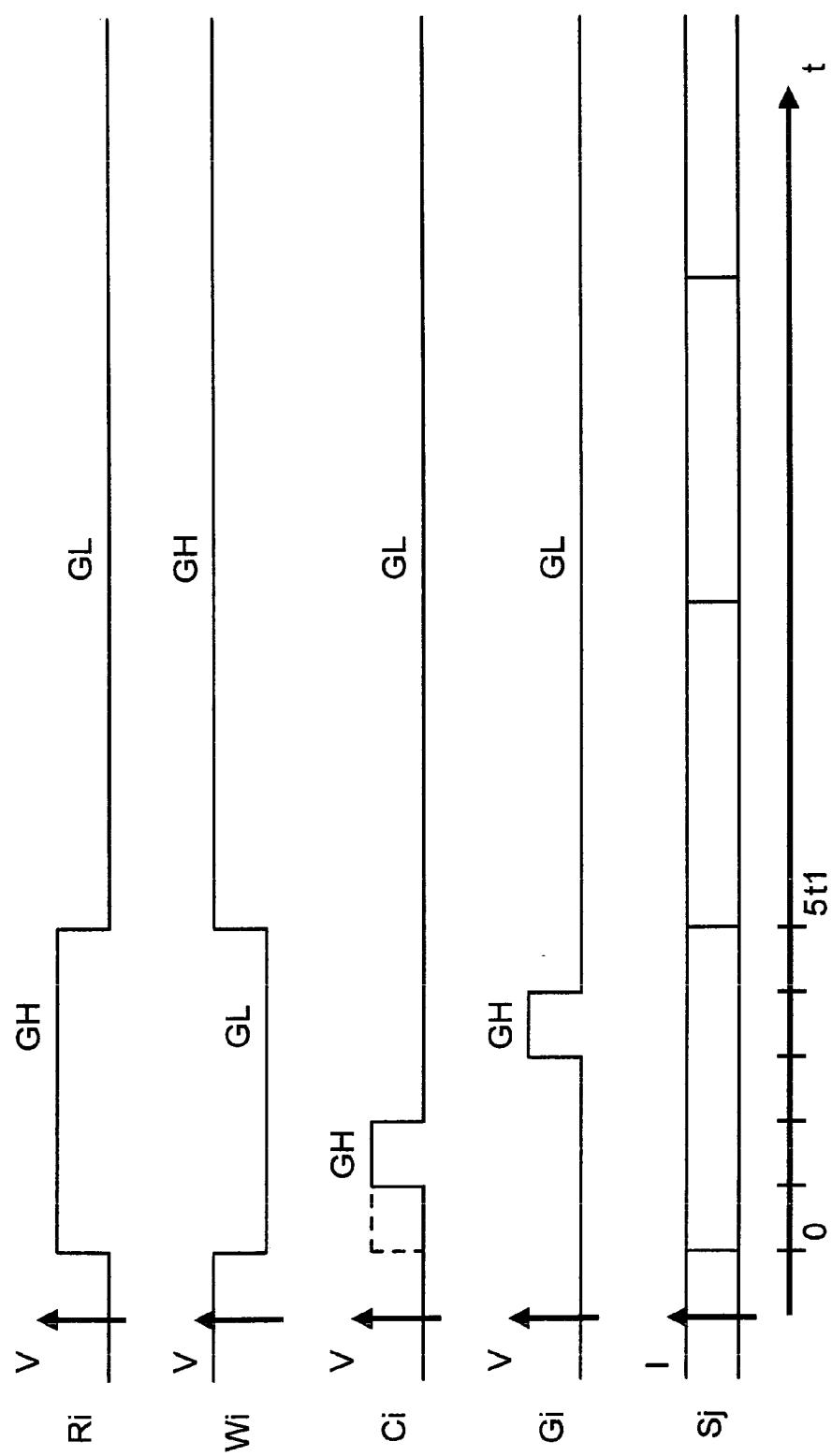

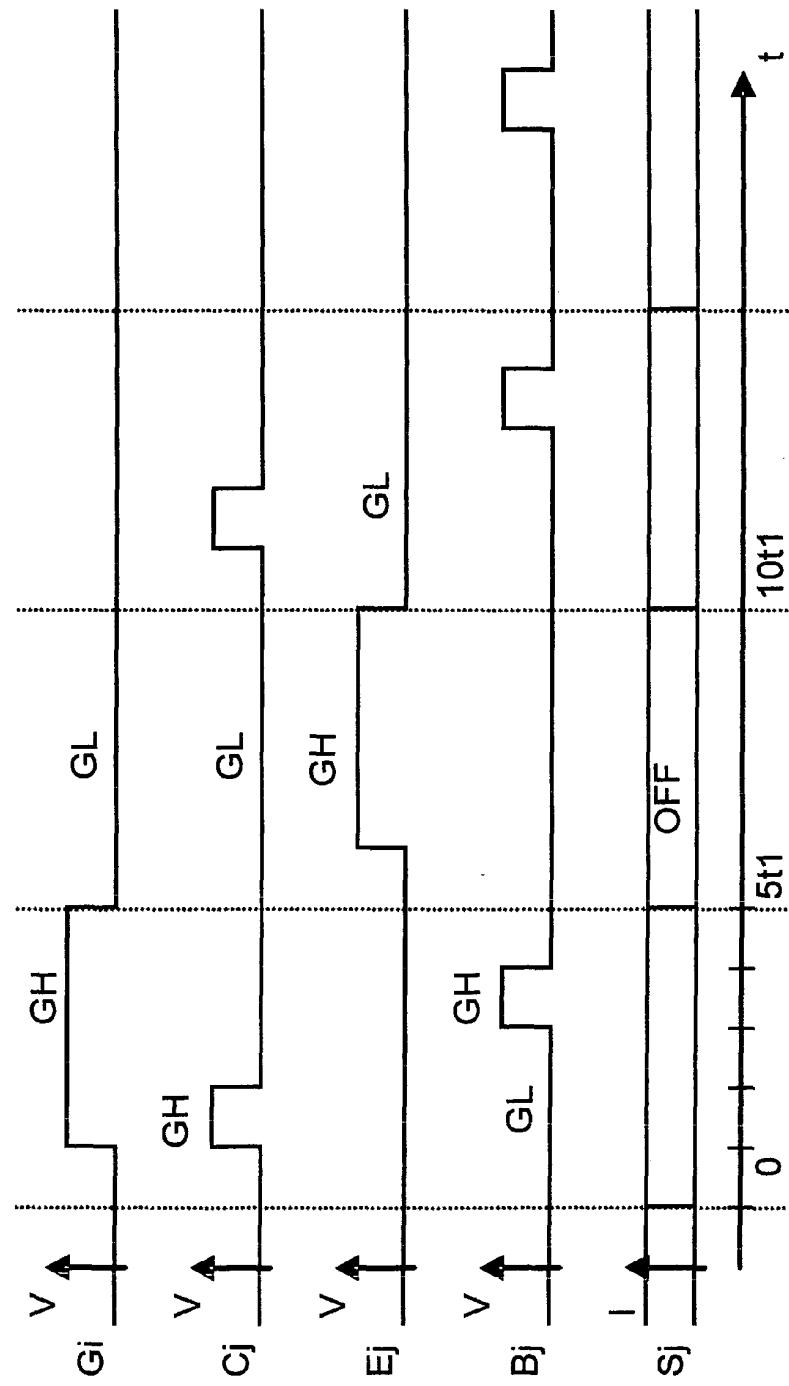

Fig. 2 is a wave form chart illustrating respective operation timings of control wires of the pixel circuit.

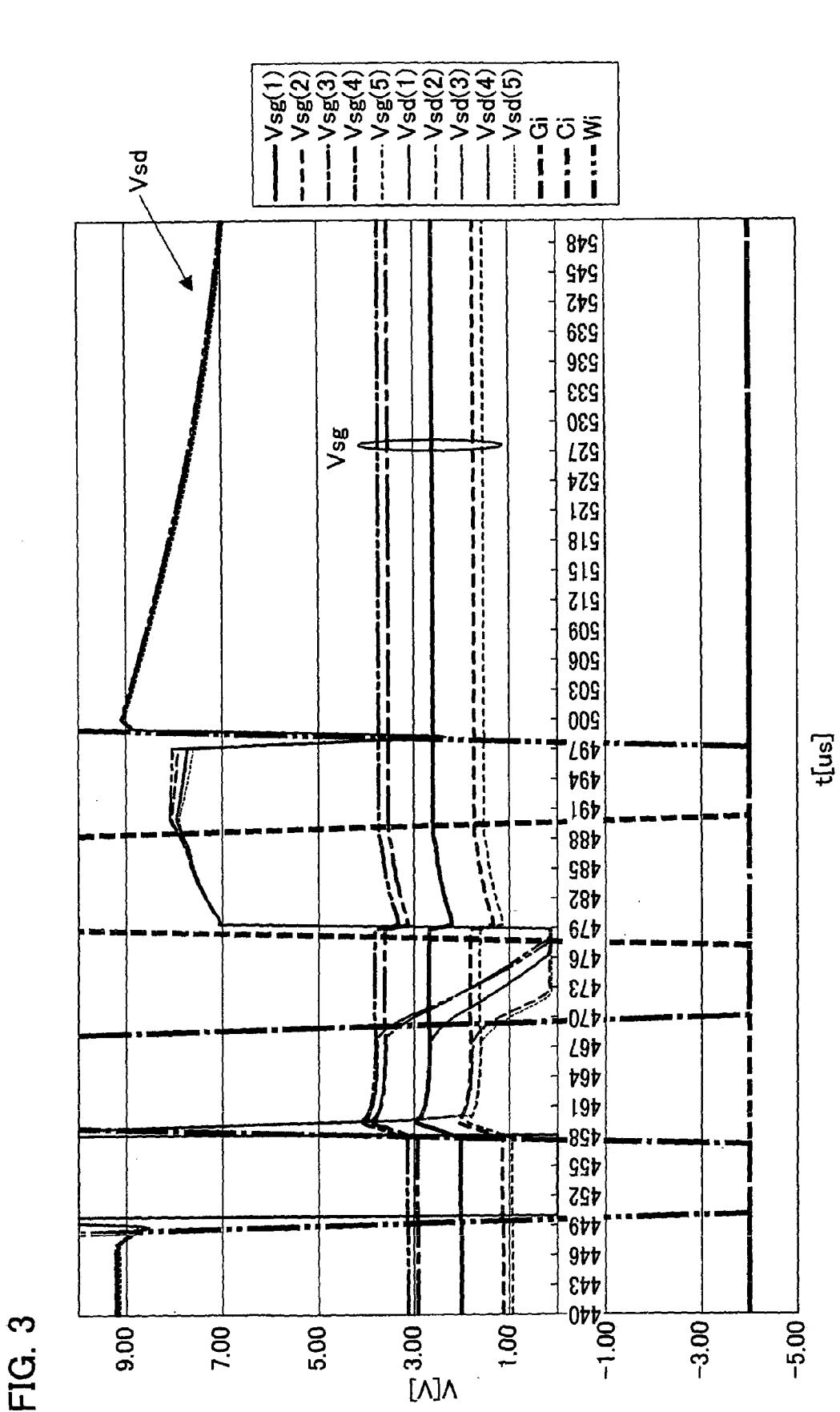

Fig. 3 is a graph illustrating a result of a simulation of respective changes of (i) a source-gate potential and (ii) a source-drain potential of a driving TFT of the pixel circuit.

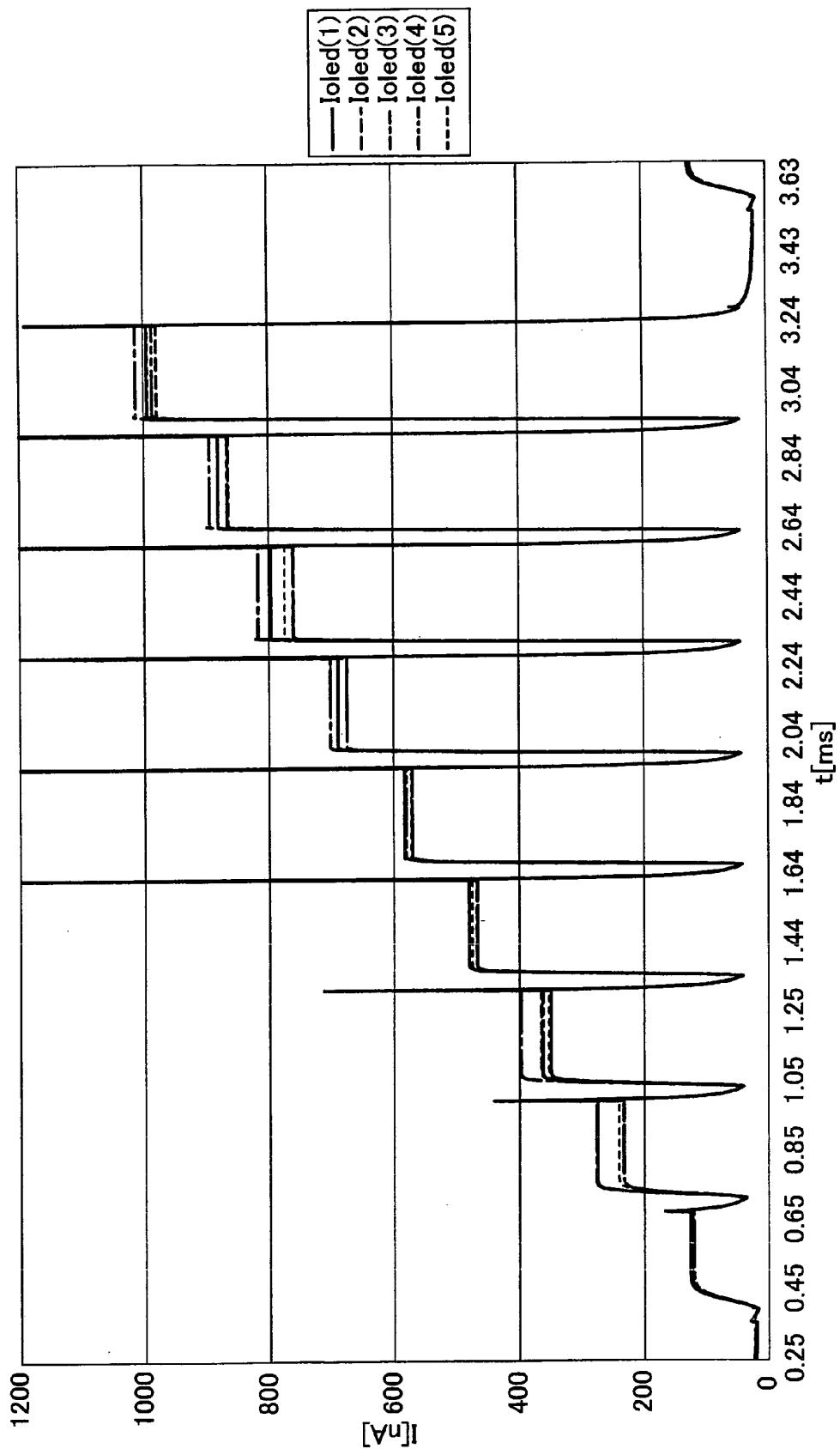

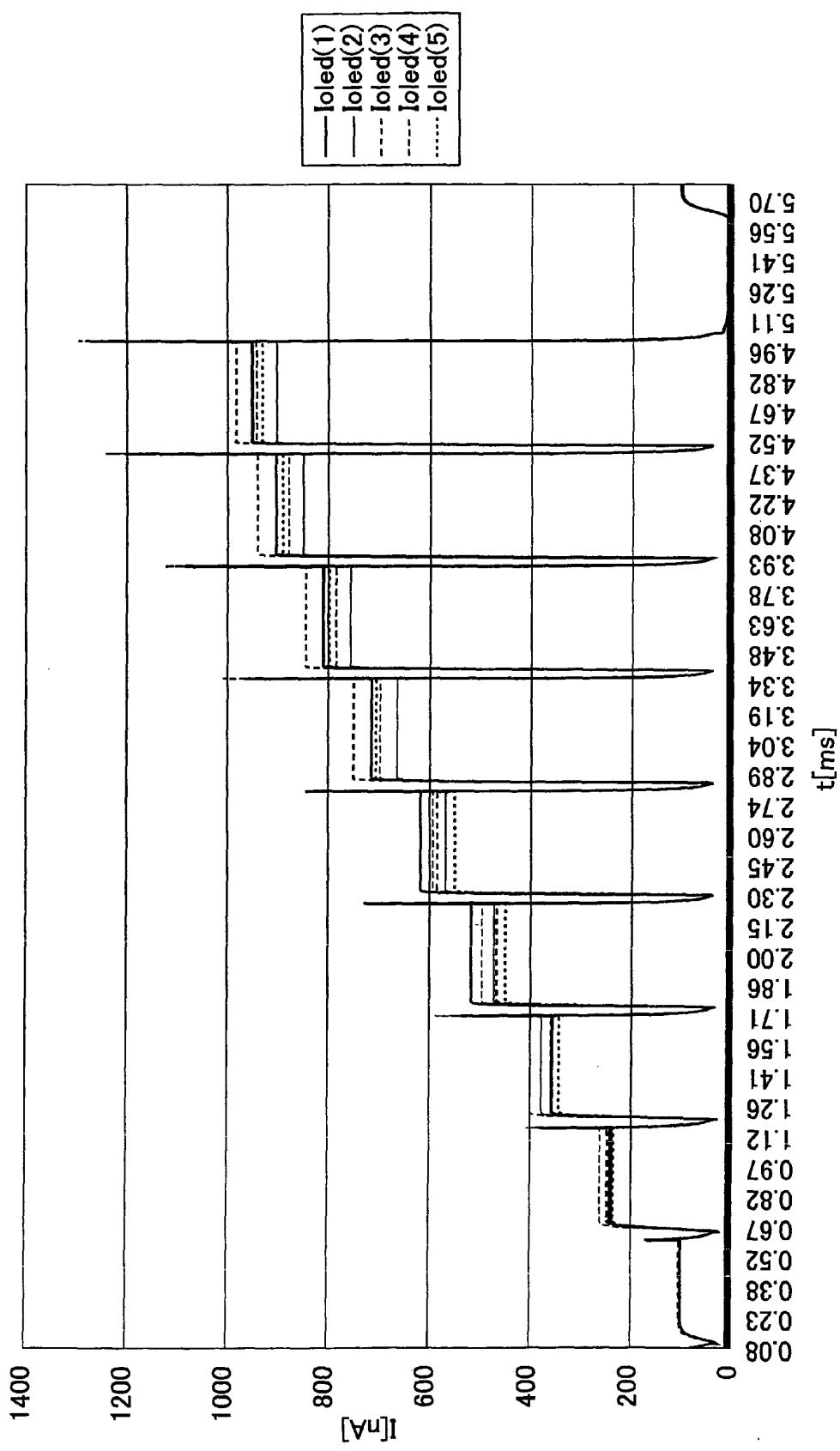

45 Fig. 4 is a graph illustrating a result of simulating a current flowing through an organic EL element in the pixel circuit.

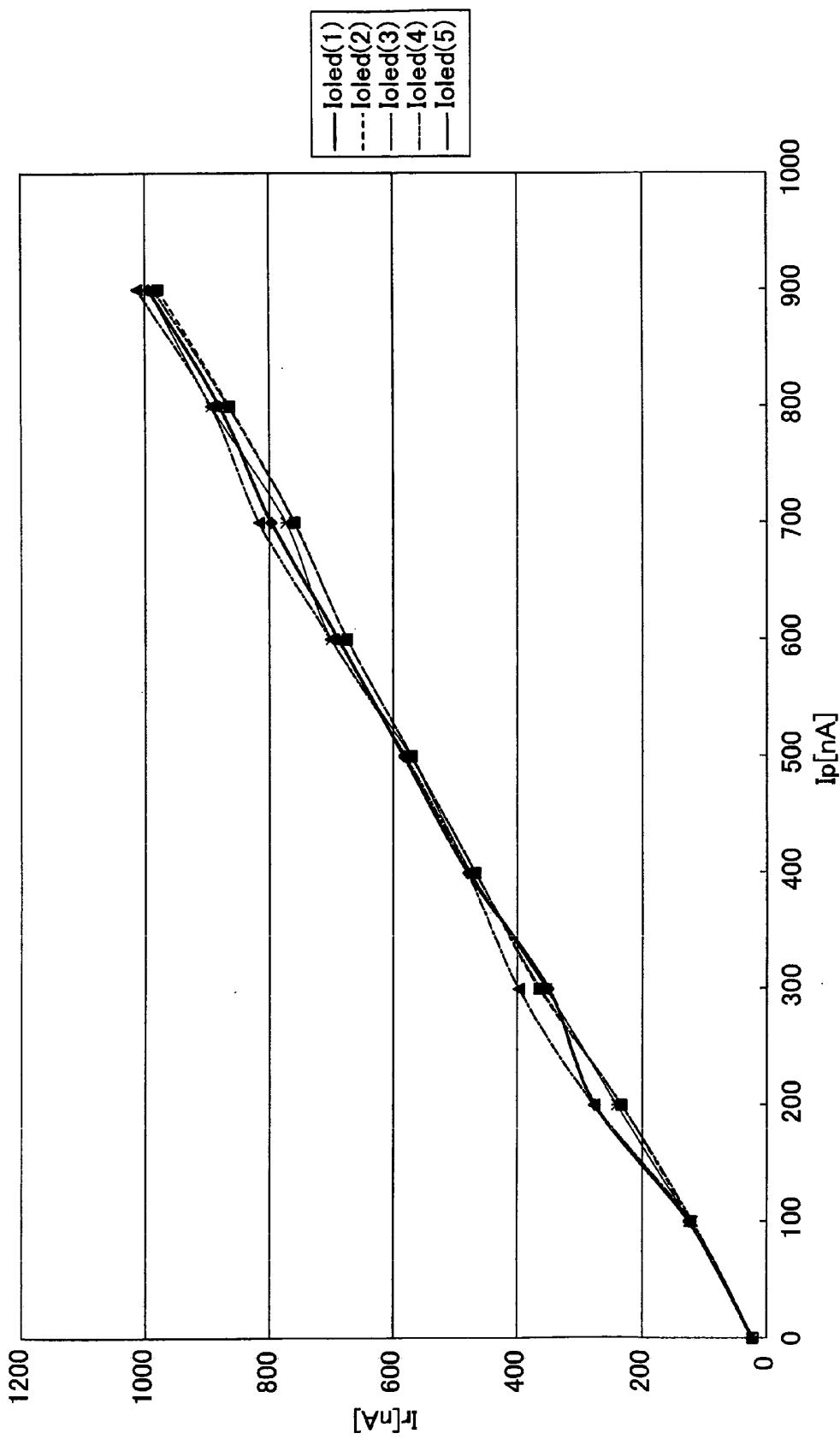

Fig. 5 is a graph illustrating a result of simulating a current flowing through an organic EL element in the pixel circuit.

Fig. 6 is a circuit diagram illustrating a structure of the display apparatus according to Embodiment 1, which structure is different from the pixel circuit shown in Fig. 1.

Fig. 7 is a circuit diagram illustrating a structure of a display apparatus according to Embodiment 2.

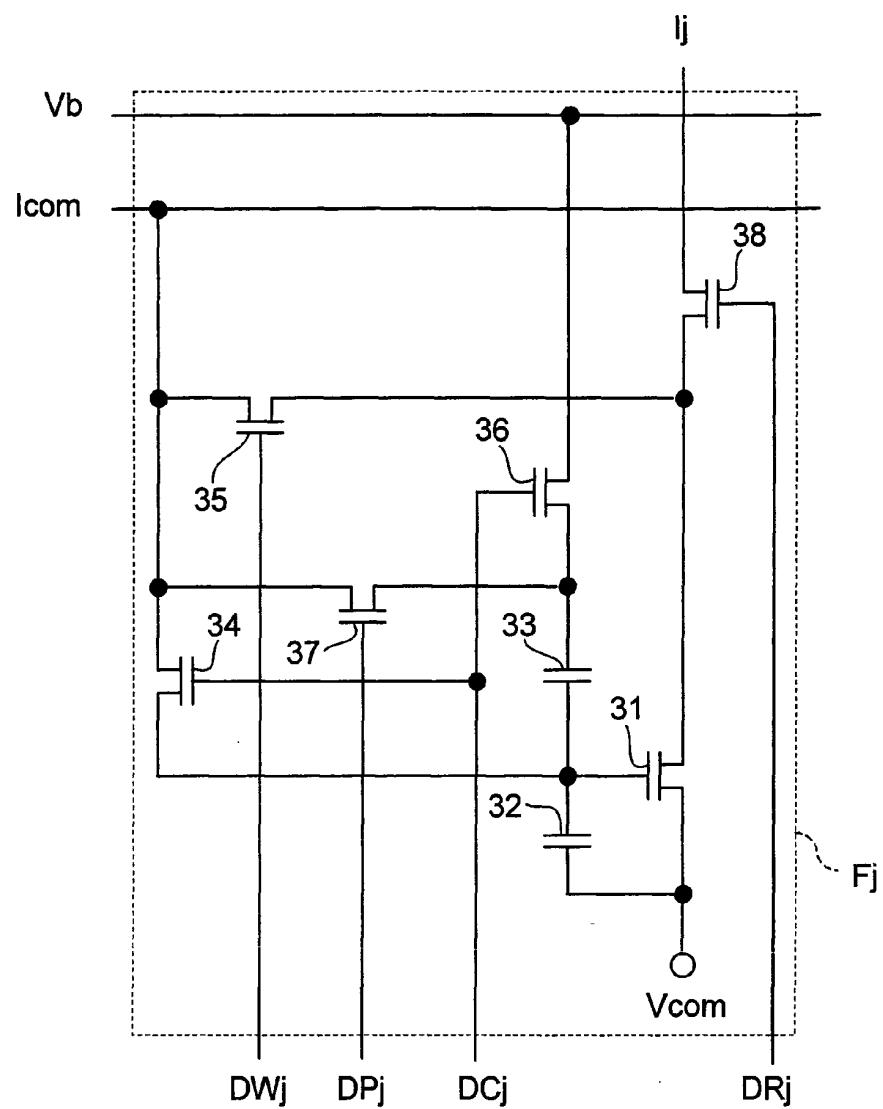

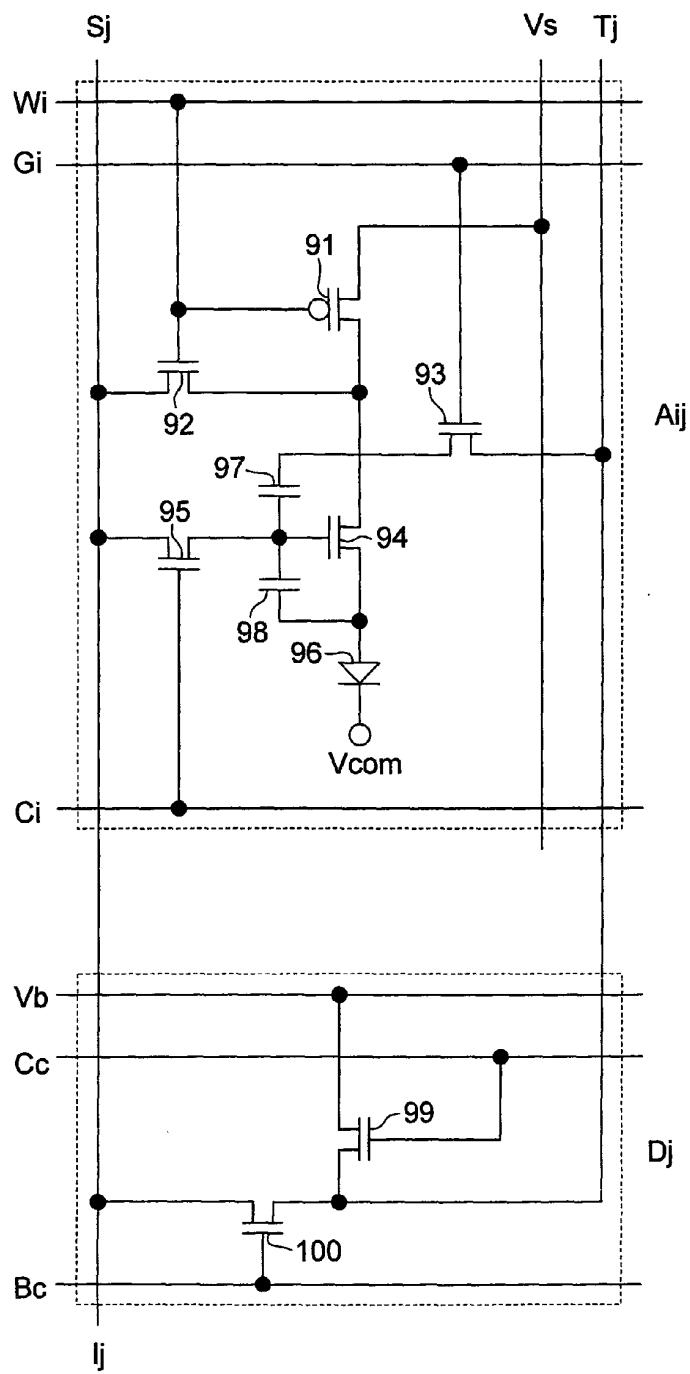

50 Fig. 8 is a circuit diagram illustrating respective structures of a pixel circuit and a source driver circuit in the display apparatus according to Embodiment 2.

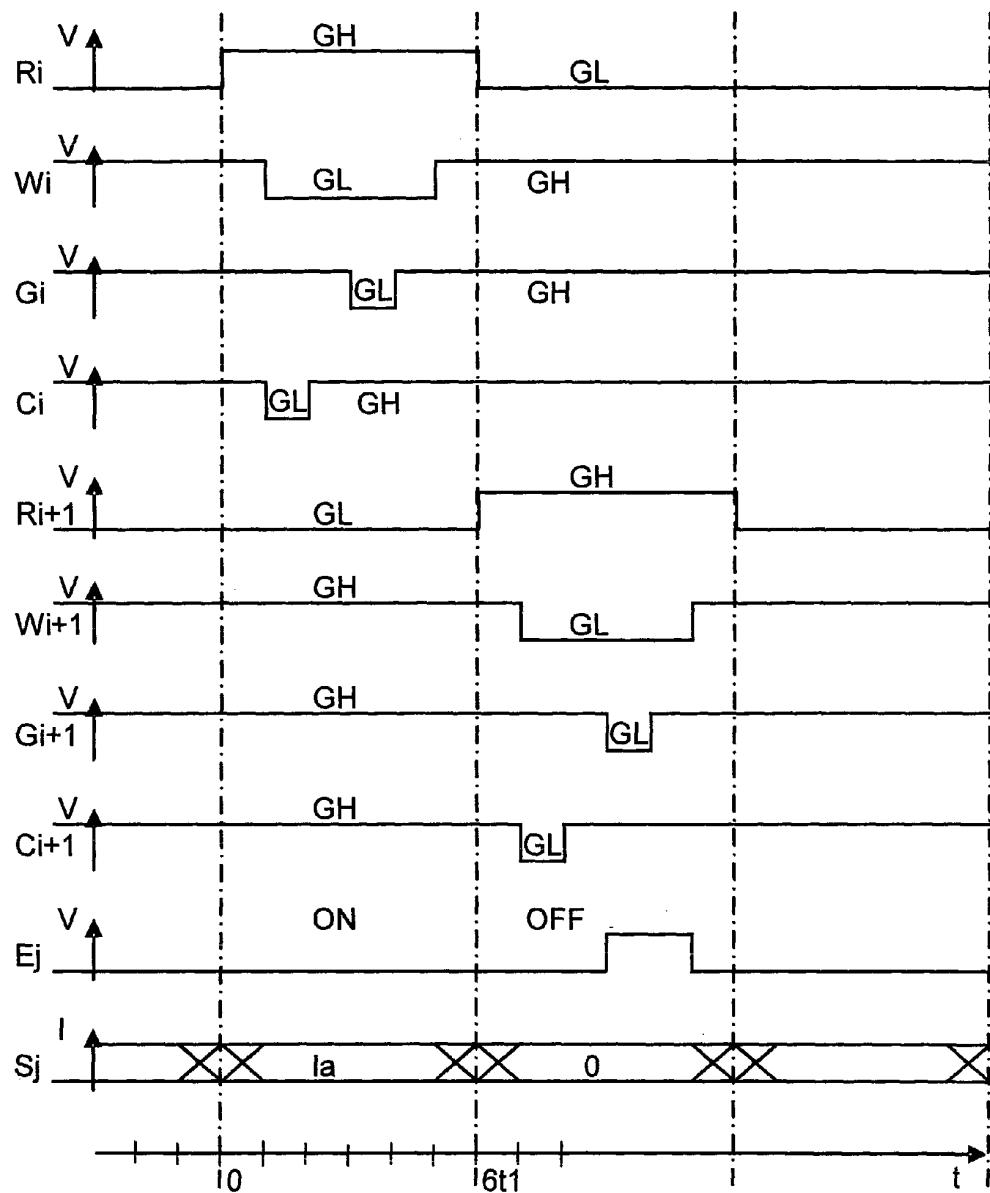

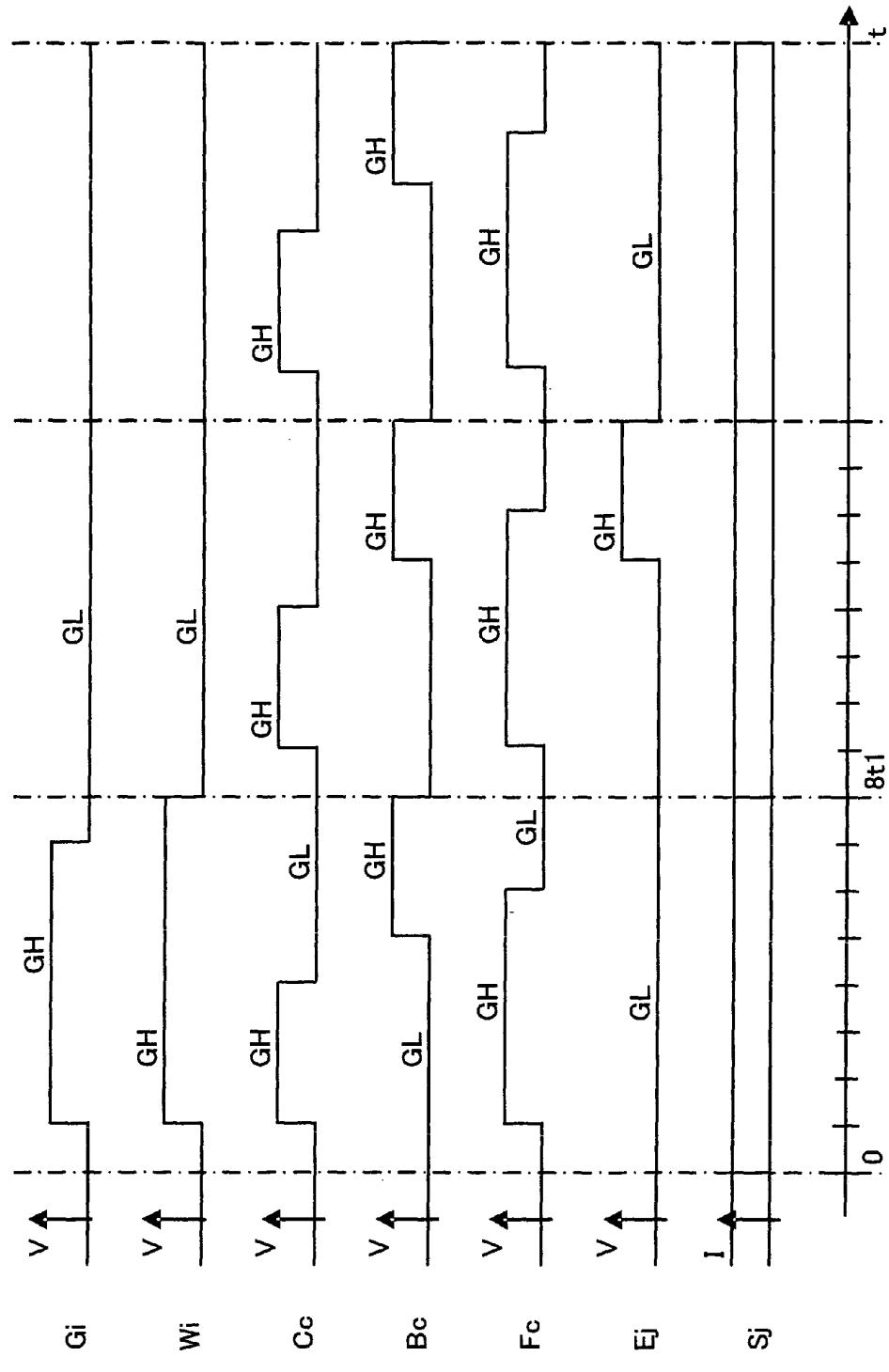

Fig. 9 is a wave form chart illustrating respective operation timings of control wires of the pixel circuit and the source driver circuit.

Fig. 10 is a graph illustrating a result of simulating a current flowing through an organic EL element in the pixel circuit.

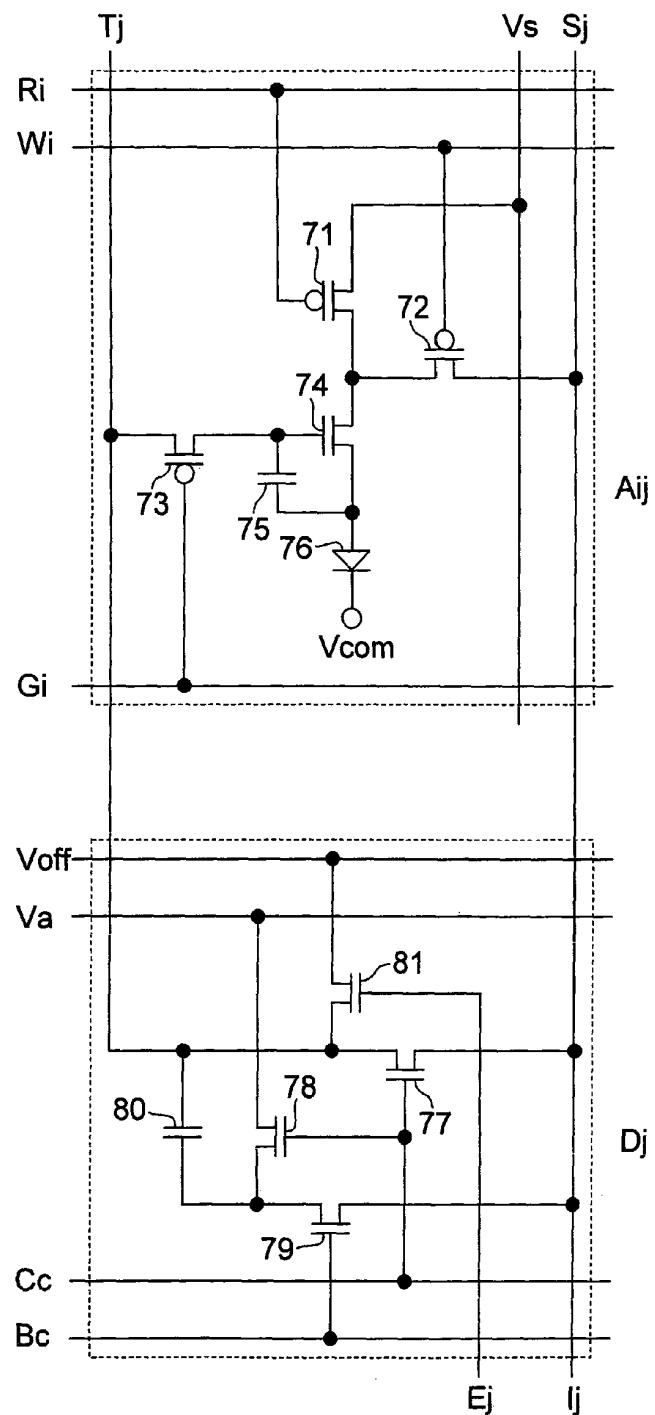

55 Fig. 11 is a circuit diagram illustrating respective structures of a pixel circuit and a source driver circuit in a display apparatus according to Embodiment 3.

Fig. 12 is a wave form chart illustrating respective operation timings of control wires of the pixel circuit and the source driver circuit.

- Fig. 13 is a graph illustrating a result of simulating a current flowing through an organic EL element in the pixel circuit.

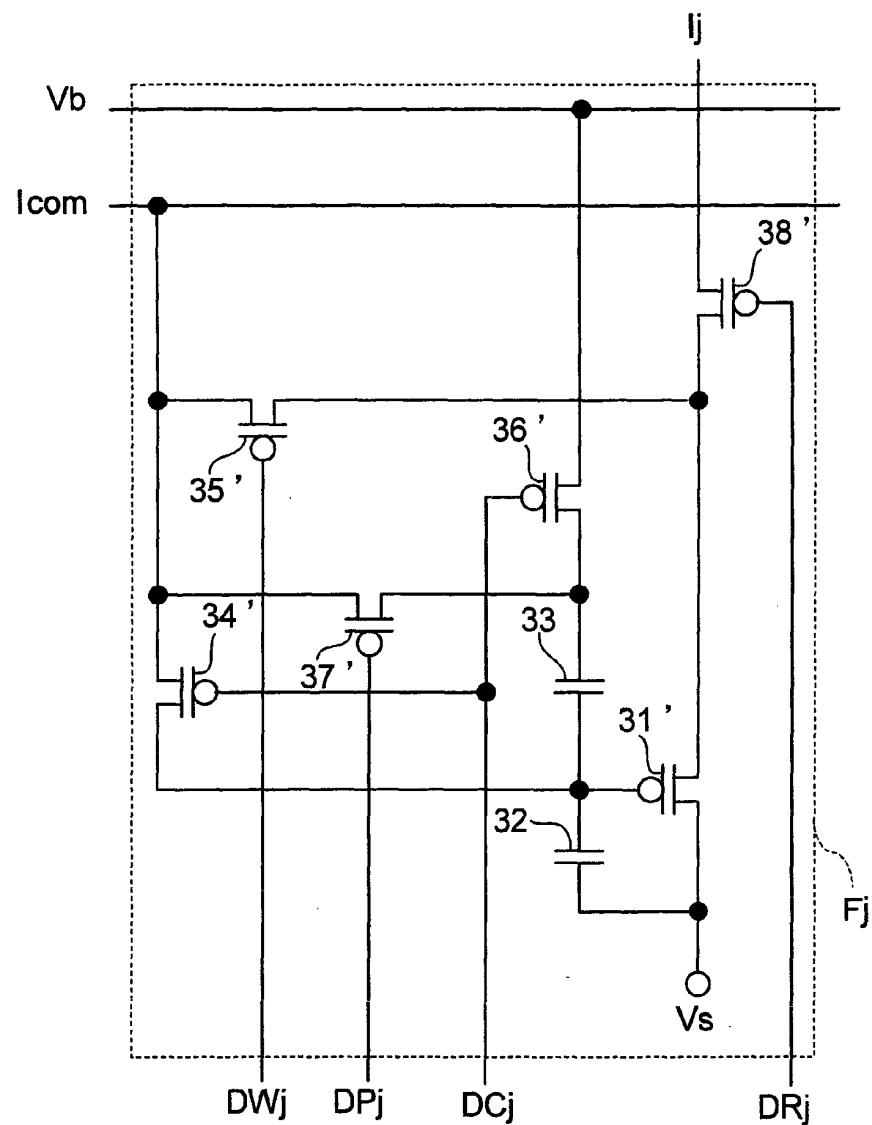

- Fig. 14 is a circuit diagram illustrating a structure of a source driver circuit in a display apparatus according to Embodiment 4.

- 5 Fig. 15 is a wave form chart illustrating respective operation timings of control wires of the source driver circuit.

- Fig. 16 is a graph illustrating a result of simulating respective changes in (i) a source-gate potential and (ii) a source-drain potential of a driving TFT in the source driver circuit.

- 10 Fig. 17 is a graph illustrating a result of simulating a current flowing from a source terminal of the driving TFT to a drain terminal thereof, in the source driver circuit.

- Fig. 18 is a wave form chart illustrating respective operation timings of control wires in a display apparatus in which the source driver circuit shown in Fig. 14 and the pixel circuit shown in Fig. 1 are combined.

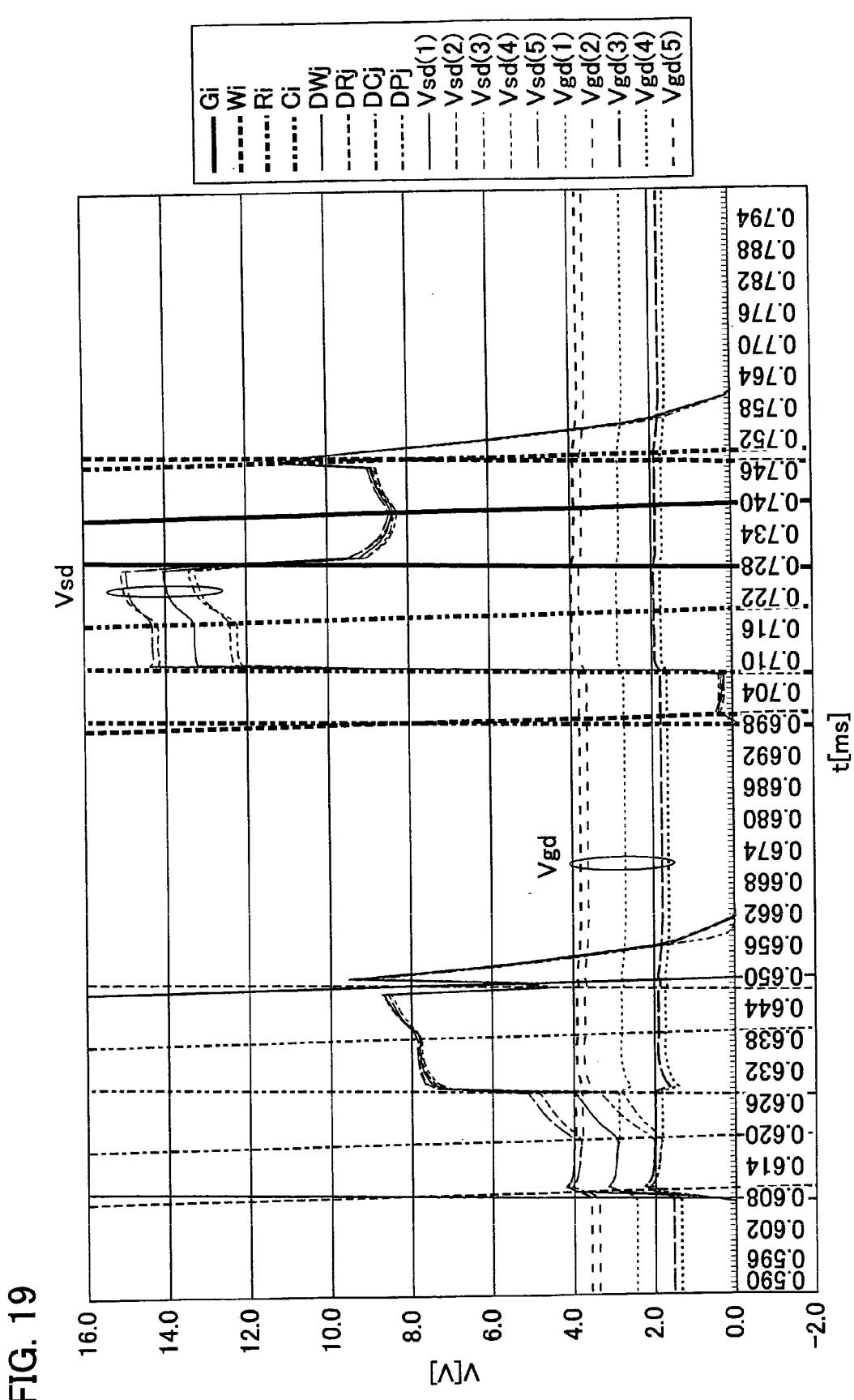

- 15 Fig. 19 is a graph illustrating a result of simulating respective changes in a source-gate potential and a source-drain potential of a driving TFT of the source driver circuit of the circuit structure obtained by combining the source driver circuit shown in Fig. 14 with the pixel circuit shown in Fig. 1.

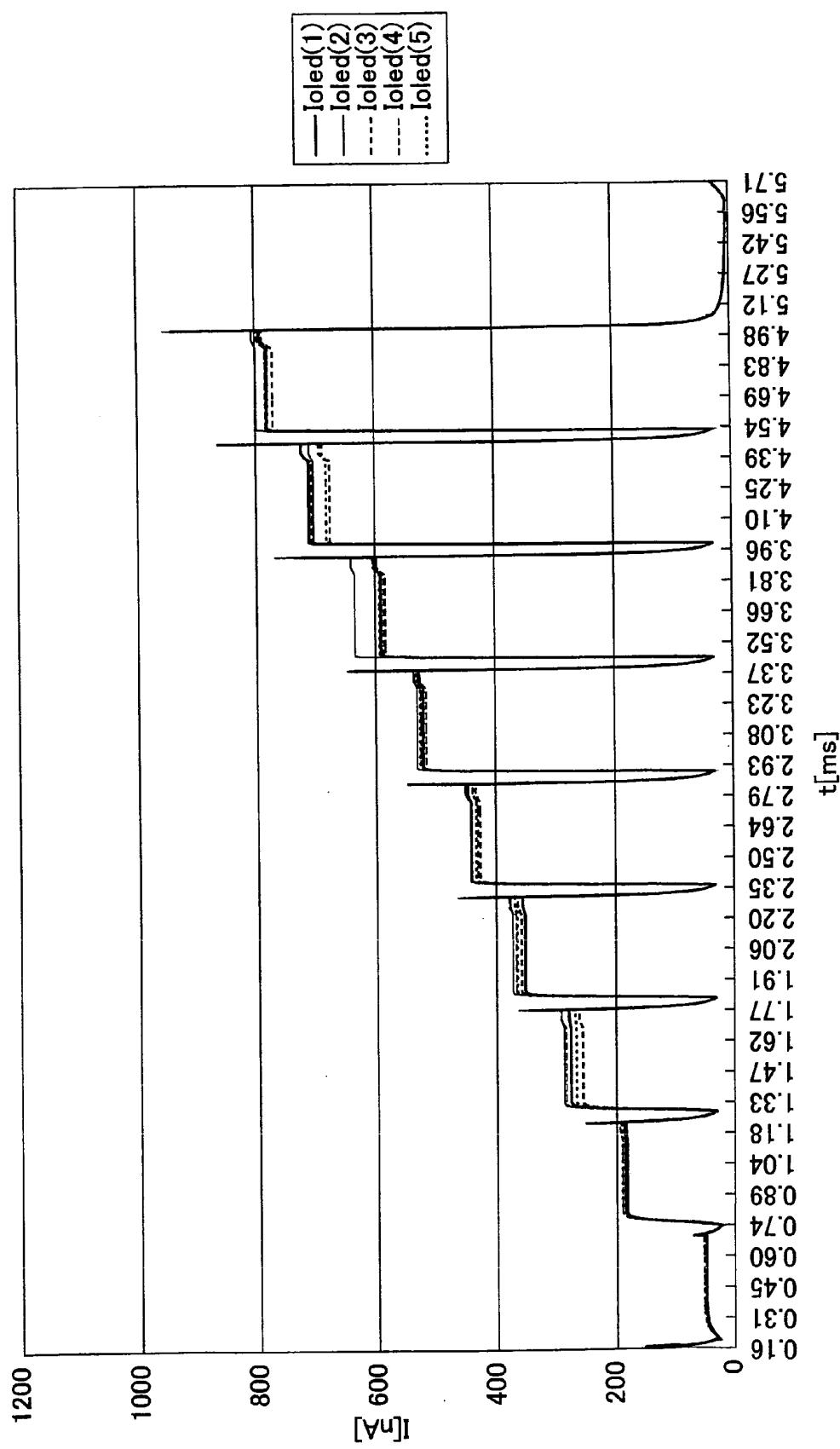

- Fig. 20 is a graph illustrating a result of simulating a current flowing through an organic EL element of the pixel circuit of the circuit structure obtained by combining the source driver circuit shown in Fig. 14 with the pixel circuit shown in Fig. 1.

- 20 Fig. 21 is a circuit diagram illustrating a structure of the display apparatus according to Embodiment 4, which structure is different from the source driver circuit shown in Fig. 14.

- Fig. 22 is a circuit diagram illustrating a structure example of a pixel circuit of a conventional display apparatus.

- 25 Fig. 23 is another structure example of the pixel circuit of the conventional display apparatus.

- Fig. 24 is a wave form chart illustrating respective operation timings of control wires of the conventional pixel circuit.

- Fig. 25 is a graph illustrating a result of simulating a current flowing through an organic EL element in the conventional pixel circuit.

- Fig. 26 is a graph illustrating a result of simulating a current flowing through an organic EL element in the conventional pixel circuit.

- 30 Fig. 27 is a graph illustrating a result of simulating respective changes in a source-gate potential and a source-drain potential of a driving TFT in the conventional pixel circuit.

- Fig. 28 is a graph illustrating a relation between (i) a source-drain potential  $V_{sd}$  of the driving TFT, and (ii) a current flowing from a source of the driving TFT to a drain thereof.

- Fig. 29 is a circuit diagram illustrating a circuit structure in which a driving TFT is provided in series with an organic EL element.

- 35 Fig. 30 is a graph illustrating a result of a simulation for examining variation, during the non-selection period, in a current flowing from (i) a source of the driving TFT of the circuit shown in Fig. 29, to (ii) a drain thereof.

- Fig. 31 is a circuit diagram illustrating respective structures of a pixel circuit and a source driver circuit in a display apparatus according to Embodiment 5.

- 40 Fig. 32 is a wave form chart illustrating respective operation timings of control wires of the pixel circuit and the source driver circuit.

- Fig. 33 is a graph illustrating a result of simulating a current flowing from the source terminal of the driving TFT to the drain terminal of the driving TFT, in the pixel circuit and the source driver circuit.

- 45 Fig. 34 is a circuit diagram illustrating (i) a structure of a pixel circuit, and (ii) a structure of a source driver circuit in a display apparatus according to Embodiment 6.

- Fig. 35 is a wave form chart illustrating respective operation timings of control wires of the pixel circuit and the source driver circuit.

- Fig. 36 is a graph illustrating a result of simulating a current flowing from a source of a driving TFT to a drain thereof in the pixel circuit and the source driver circuit.

- 50 Fig. 37 is a circuit diagram illustrating respective structures of another pixel circuit and another source driver circuit in the display apparatus according to Embodiment 6.

- Fig. 38 is a circuit diagram illustrating respective structures of a pixel circuit and a source driver circuit in a display apparatus according to Embodiment 7.

- 55 Fig. 39 is a wave form chart illustrating respective operation timings of control wires of the pixel circuit and the source driver circuit.

- Fig. 40 is a graph illustrating a result of simulating respective changes in the source-gate potential and the source-drain potential of the driving TFT in the pixel circuit shown in Fig. 8 and the source driver circuit shown therein.

- Fig. 41 illustrates a circuit diagram illustrating respective structures of a pixel circuit, a source driver circuit, and another circuit in a display apparatus according to Embodiment 8.

- Fig. 42 is a wave form chart illustrating respective operation timings of control wires of the pixel circuit and the source driver circuit.

- Fig. 43 is a graph illustrating a result of simulating respective changes in (i) a source-drain potential of the driving

TFT and (ii) a current from the source of the driving TFT to the drain thereof, in the pixel circuit (see Fig. 41) and the source driver circuit (see Fig. 41).

Fig. 44 is a circuit diagram illustrating a pixel circuit, a source driver circuit, and another circuit in a display apparatus according to Embodiment 9.

5 Fig. 45 is a wave form chart illustrating respective operation timings of control wires of the pixel circuit, the source driver circuit, and the aforesaid another circuit.

## BEST MODE FOR CARRYING OUT THE INVENTION

10 [0084] Embodiments of the present invention will be explained with reference to Fig. 1 through Fig. 21, and Fig. 31 through Fig. 45. Note that the present invention is not limited to these.

[0085] Note also that each switching element used in the present invention may be a low temperature polysilicon TFT or a CG (Continuous Grain) silicon TFT; however, Embodiments below uses the CG silicon TFT.

15 [0086] Here, a structure of such a CG silicon TFT is described in, for example, "4.0-in. TFT-OLED Displays and a Novel Digital Driving Method" (SID' 00 Digest, pp.924-927, Semiconductor Energy Laboratory Co., Ltd). Moreover, a manufacturing process of such a CG silicon TFT is described in, for example, "Continuous Grain Silicon Technology and Its Applications for Active Matrix Display" (AM-LCD 2000, pp.25-28, Semiconductor Energy Laboratory Co., Ltd). That is, the structure and the manufacturing process of the CG silicon TFT are publicly well-known, so that detailed explanation thereof is omitted here.

20 [0087] Further, a structure of each organic EL element, used in Embodiments and serving as an electric optical element, is described in, for example, "Polymer Light-Emitting Diodes for use in Flat panel Display" (AM-LCD '01, pp. 211-214, Semiconductor Energy Laboratory Co., Ltd). Therefore, the structure is publicly well-known, so that detailed explanation thereof is omitted here.

### 25 [Embodiment 1]

[0088] Embodiment 1 will explains a case where a first characteristic structure according to the present invention is applied to a pixel circuit.

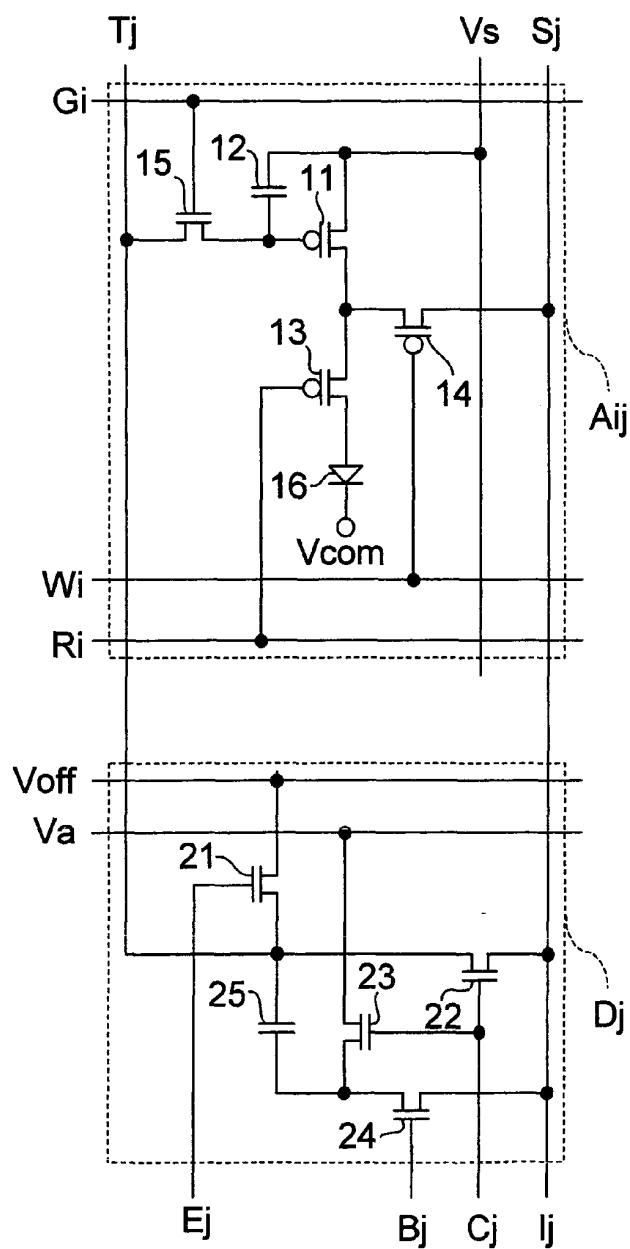

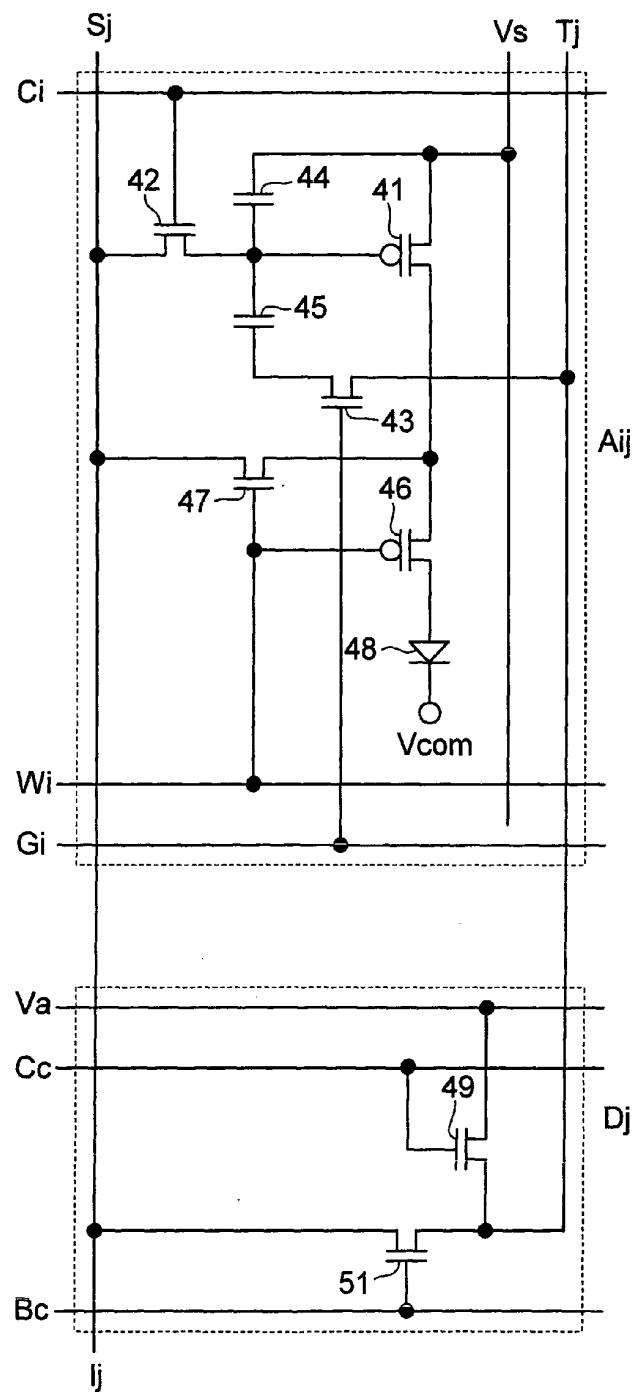

30 [0089] As shown in Fig. 1, in each of pixel circuits  $A_{ij}$  of a display apparatus according to Embodiment 1, a driving TFT 1 is provided in series with a organic EL element (current driving light-emitting element) 6 between a power source wire  $V_s$  and a common wire  $V_{com}$ . The driving TFT 1 serves as a driving TFT, and the organic EL element 6 serves as an electric optical element. The driving TFT 1 controls a current that is to be supplied to the organic EL element 6.

35 [0090] The driving TFT 1 has a gate terminal (current control terminal) connected to a source wire  $S_j$  via a switching TFT 3, serving as a first switching transistor. Moreover, the gate terminal (current control terminal) of the driving TFT 1 is connected to one terminal of a first capacitor 2, and to one terminal of a second capacitor 7. The other terminal of the first capacitor 2 is connected to (i) a source terminal (current input terminal) of the driving TFT 1 and (ii) the power source wire  $V_s$ . The other terminal of the second capacitor 7 is connected to a predetermined voltage line  $V_a$  via a switching TFT 8, which serves as a third switching transistor. Moreover, the other terminal of the second capacitor 7 is connected to the source wire  $S_j$  via a switching TFT 9, which serves as a second switching transistor. Note that, 40 the following explanation assumes that a first terminal of the first capacitor 2 refers to its terminal connected to the gate terminal of the driving TFT 1, and a second terminal of the first capacitor 2 refers to the other terminal of the first capacitor 2; and that a first terminal of the second capacitor 7 refers to its terminal connected to the gate terminal of the driving TFT 1, and a second terminal of the second capacitor 7 refers to the other terminal of the second capacitor 7.

45 [0091] Respective gate terminals of the switching TFT 3 and the switching TFT 8 are connected to a control wire  $C_i$ , and a gate terminal of the switching TFT 9 is connected to a control wire  $G_i$ .

[0092] A switching TFT 4 is provided between (i) a drain terminal (current output terminal) of the driving TFT 1, and (ii) an anode of the organic EL element 6. The switching TFT 4 has a gate terminal connected to a control wire  $R_i$ . A node of the driving TFT 1 and the switching TFT 4 is connected to the source wire  $S_j$  via a switching TFT 5. The switching TFT 5 has a gate terminal connected to a control wire  $W_i$ .

50 [0093] Any of the control wires  $C_i$ ,  $G_i$ , and  $W_i$  may serve as a second wire (gate wire), and any of the switching TFTs 3, 9, and 5 may serve as a selection TFT. Note that, in the present embodiment, the control wire  $G_i$  is also referred to as "gate wire  $G_i$ ".

[0094] In the circuit structure, the gate terminal of the driving TFT 1 is connected to the drain terminal thereof via The switching TFT 3, the source wire  $S_j$ , and the switching TFT 5. Further, the second terminal of the second capacitor 7 is connected to the drain terminal of the driving TFT 1 via the switching TFT 9, the source wire  $S_j$ , and the switching TFT 5.

[0095] As such, the means of the present invention encompasses not only a case where the switching TFT 3 serving as the first switching TFT directly connects the current control terminal of the driving TFT to the current output terminal

thereof, but also a case where the switching TFT 3 indirectly connects the current control terminal of the driving TFT to the current output terminal thereof via the source wire Sj and the switching TFT5.

[0096] Likewise, the means of the present invention encompasses not only a case where the switching TFT 9 serving as the second switching TFT directly connects the second terminal of the second capacitor to the current output terminal of the driving TFT, but also a case where the switching TFT 9 indirectly connects the second terminal of the second capacitor to the current output terminal of the driving TFT via the source wire Sj and the switching TFT 5.

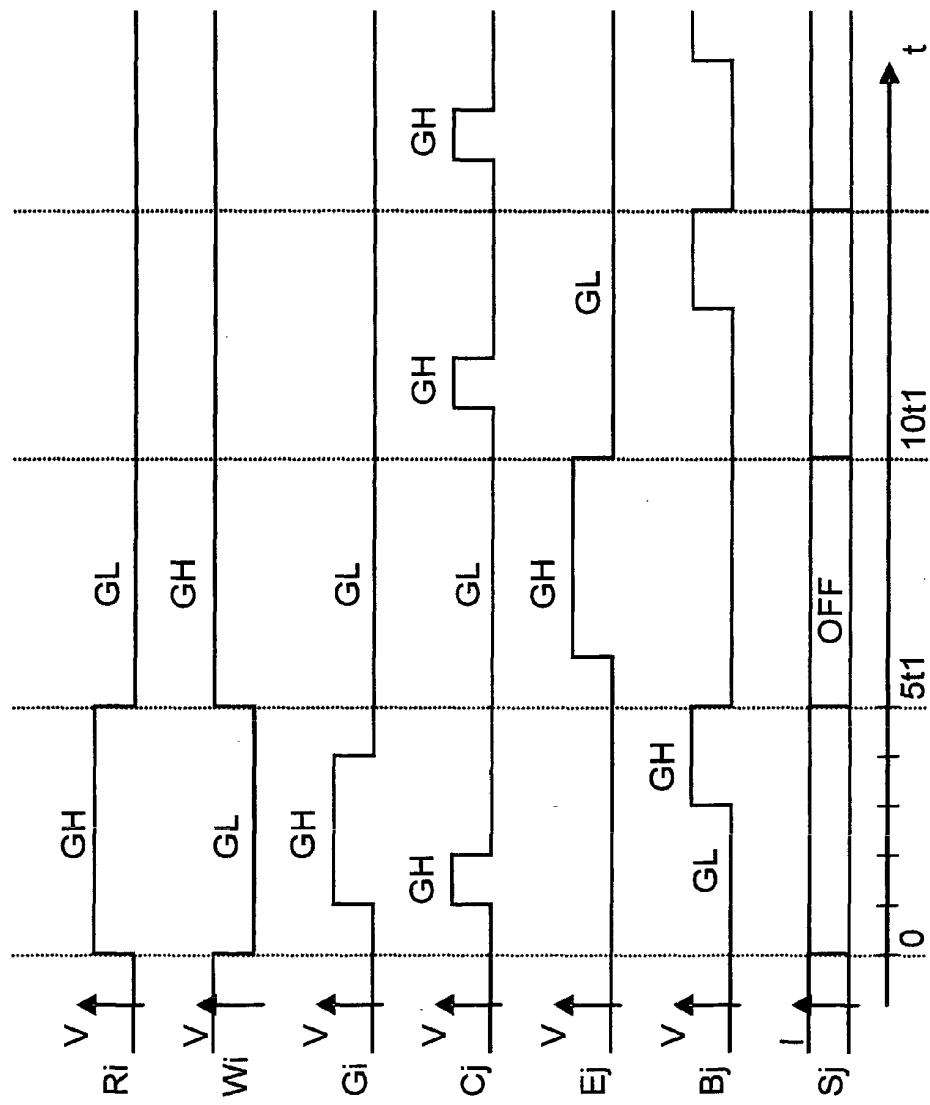

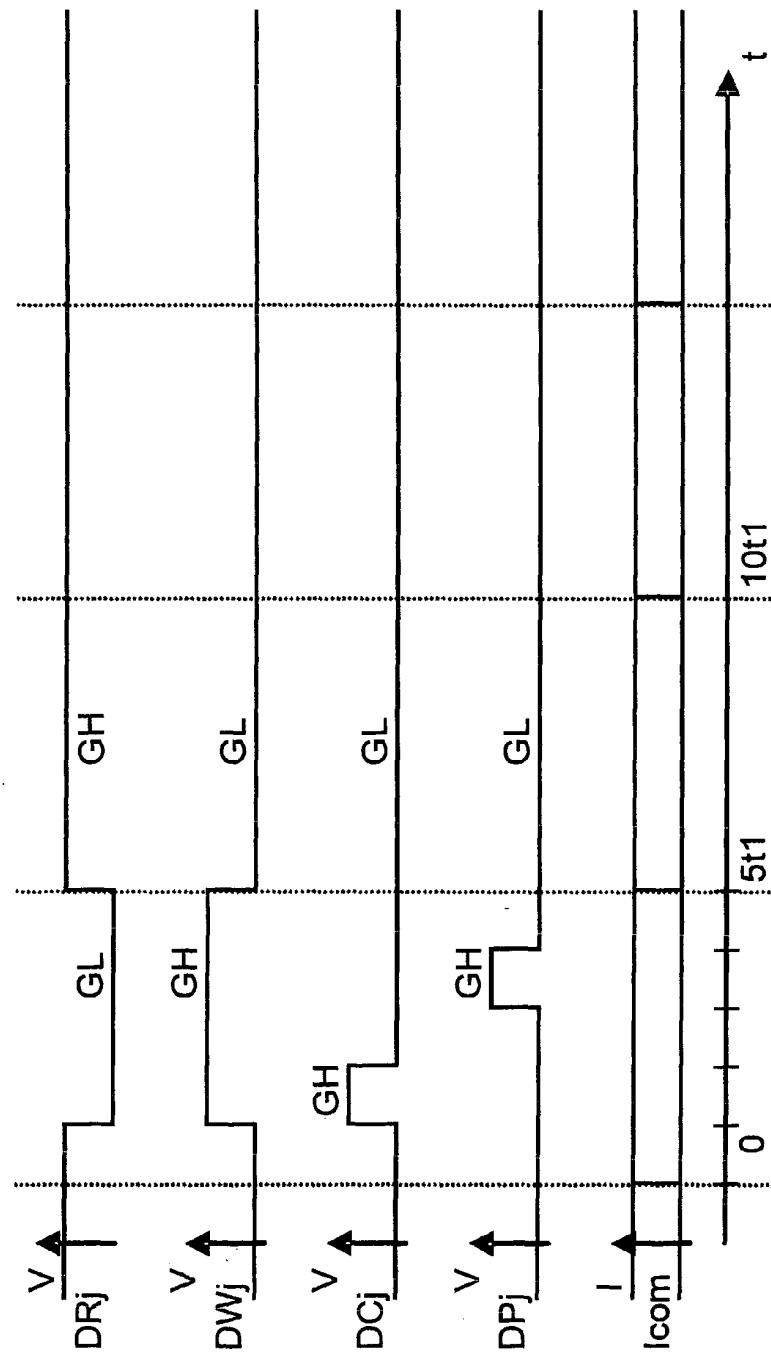

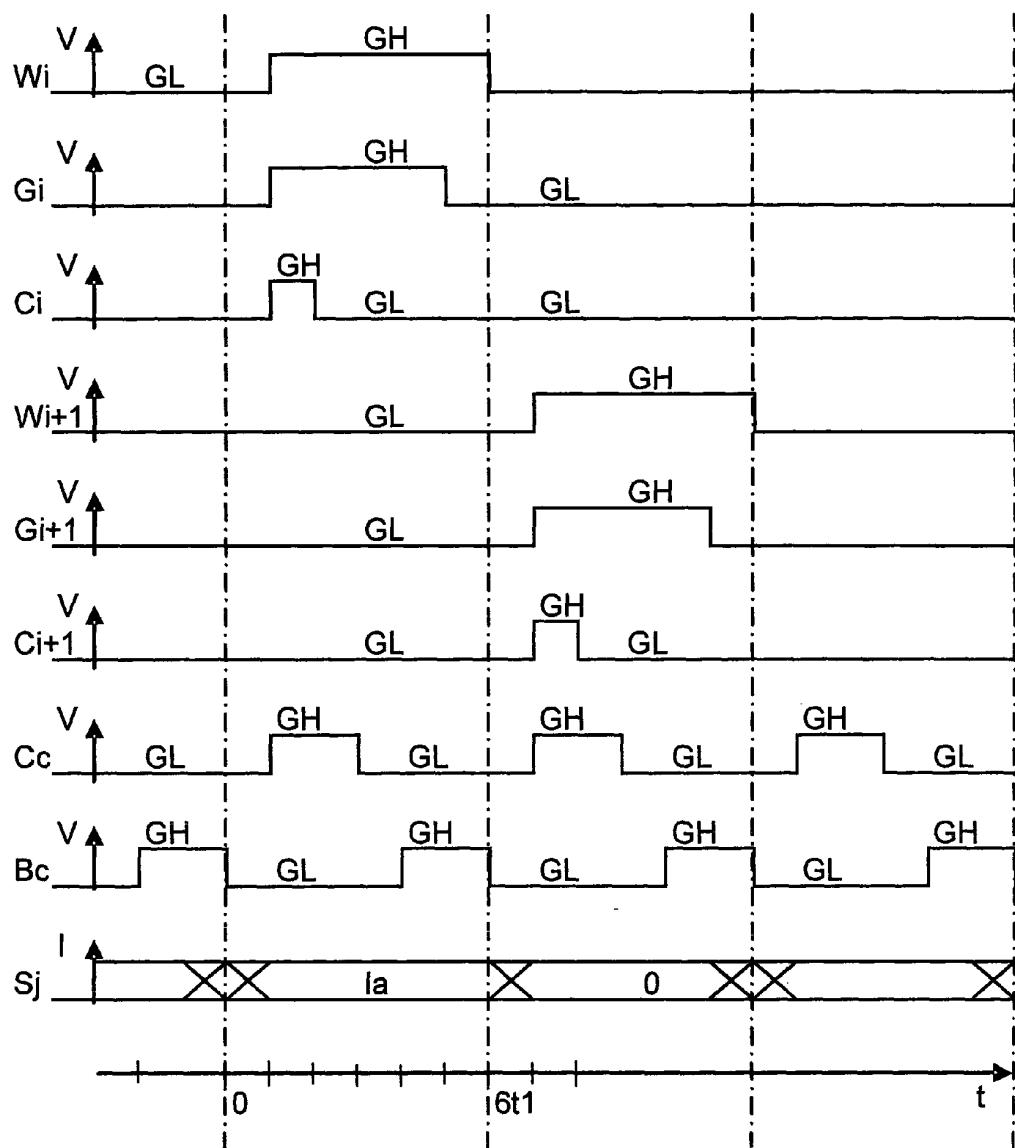

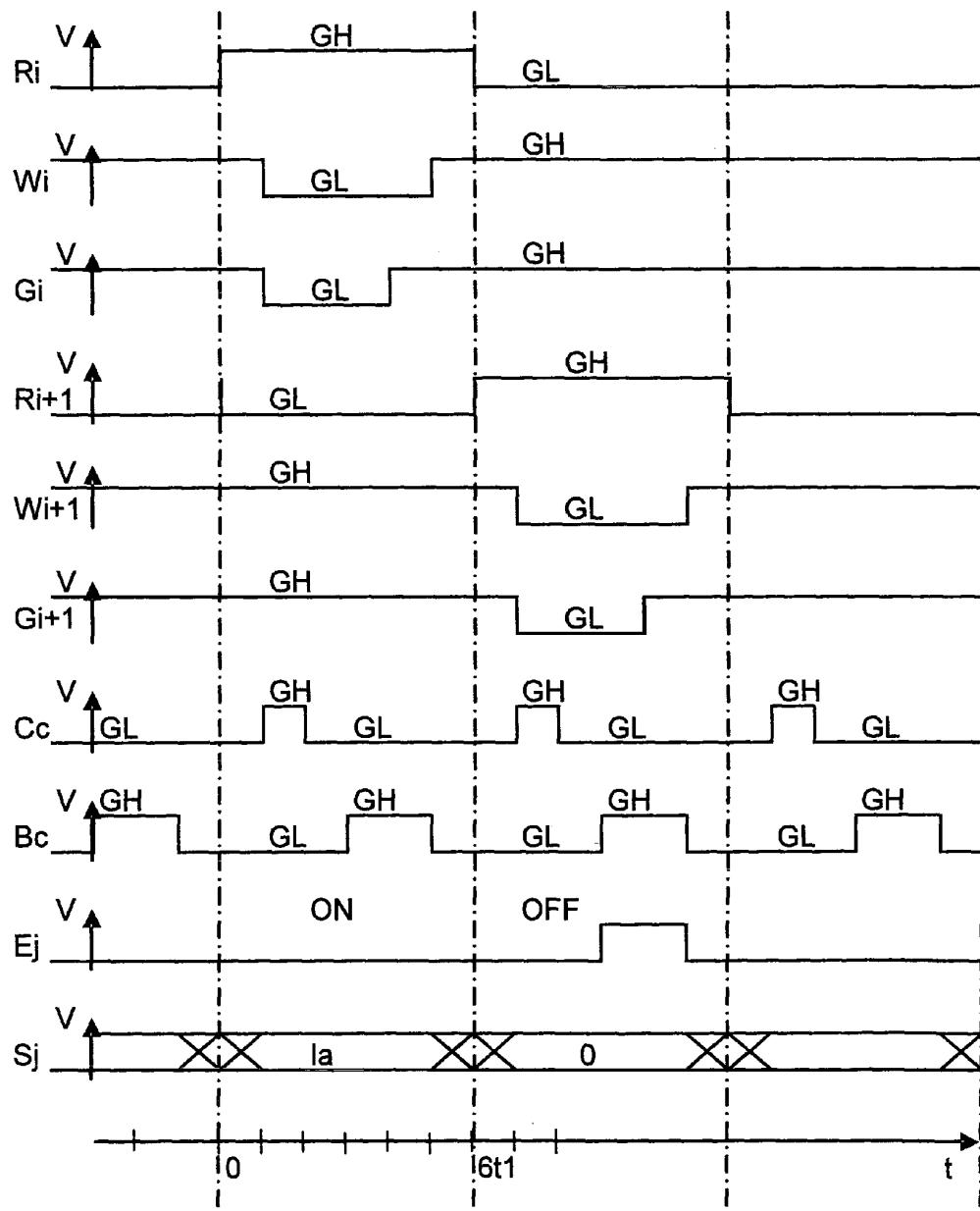

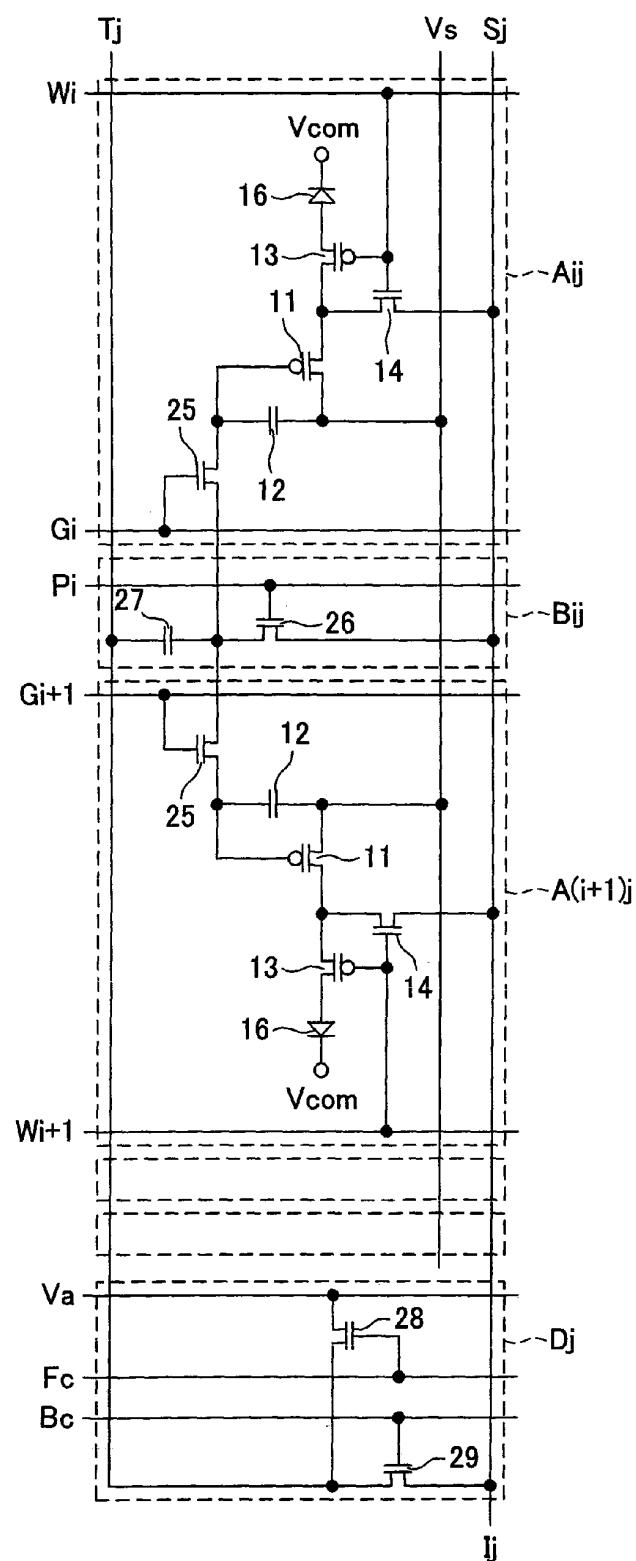

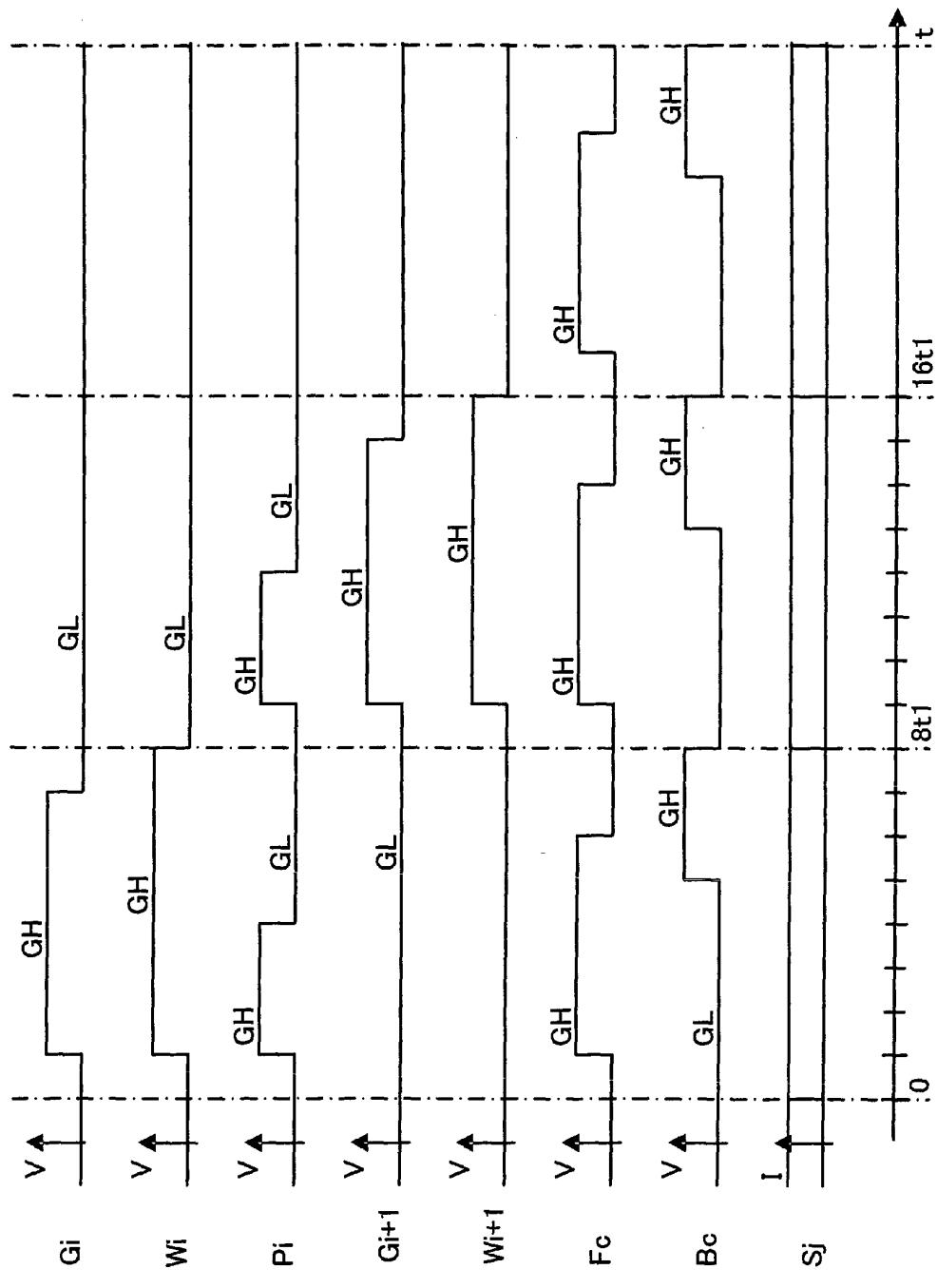

[0097] The following explains an operation of the pixel circuit Aij of the display apparatus with reference to Fig. 2. Fig. 2 illustrates respective operation timings of the control wires Ri, Wi, Ci, and Gi, and the source wire Sj.

[0098] In a driving method according to Embodiment 1 (first driving method of the present invention), during a selection period (i.e., a current writing period of the driving transistor) corresponding to a period of time from 0 to 5t1, a potential of the control wire Ri is set at High (GH) such that the switching TFT 4 is OFF, and a potential of the control wire Wi is set at Low (GL) such that the switching TFT 5 is ON.

[0099] During a first period (time t1 to time 2t1), a potential of the control wire Ci is set at High such that the switching TFTs 3 and 8 are ON. This connects the gate terminal (current control terminal) of the driving TFT 1 to the drain terminal (current output terminal) thereof via the switching TFTs 3 and 5. Moreover, this connects the second terminal of the second capacitor 7 to the predetermined voltage line Va via the switching TFT 8. Accordingly, a current is constantly supplied from the power source wire Vs to a source driver circuit (not shown) via the driving TFT 1, the switching TFT 5, the source wire Sj.

[0100] Note that the first period may start from the time 0 as a broken line in Fig. 2 indicates.

[0101] Thereafter (at the time 2t1), the potential of the control wire Ci is set at Low such that the switching TFTs 3 and 8 become OFF. This is done to prevent the switching TFTs 3 and 9 from becoming ON simultaneously. Such an OFF operation actually requires time shorter than t1. At the moment of the turning OFF, the first capacitor 2 and the second capacitor 7 retains the potential, determined during the first period, of the source wire Sj.

[0102] Next, during a second period (time 3t1 to time 4t1), the potential of the control wire Gi is set at High such that the switching TFT 9 is ON. This connects the second terminal of the second capacitor 7 to the drain terminal of the driving TFT 1 via the switching TFTs 9 and 5. Accordingly, a predetermined current is supplied from the power source wire Vs to the source driver circuit (not shown) via the driving TFT 1, the switching TFT 5, and the source wire Sj.

[0103] The source-gate potential of the driving TFT 1 is determined in this way during the second period. Then (at time 4t1), the potential of the control wire Gi is set at Low such that the switching TFT 9 becomes OFF. This causes the first capacitor 2 and the second capacitor 7 to retain the source-gate potential of the driving TFT 1. Note that a period of time from 4t1 to 5t1 after this, i.e., a period of time until the control wire Ri becomes Low and the control wire Wi becomes High is secured such that the selection period is finished after the switching TFT 9 surely becomes OFF. For this reason, this period may be shorter than t1.

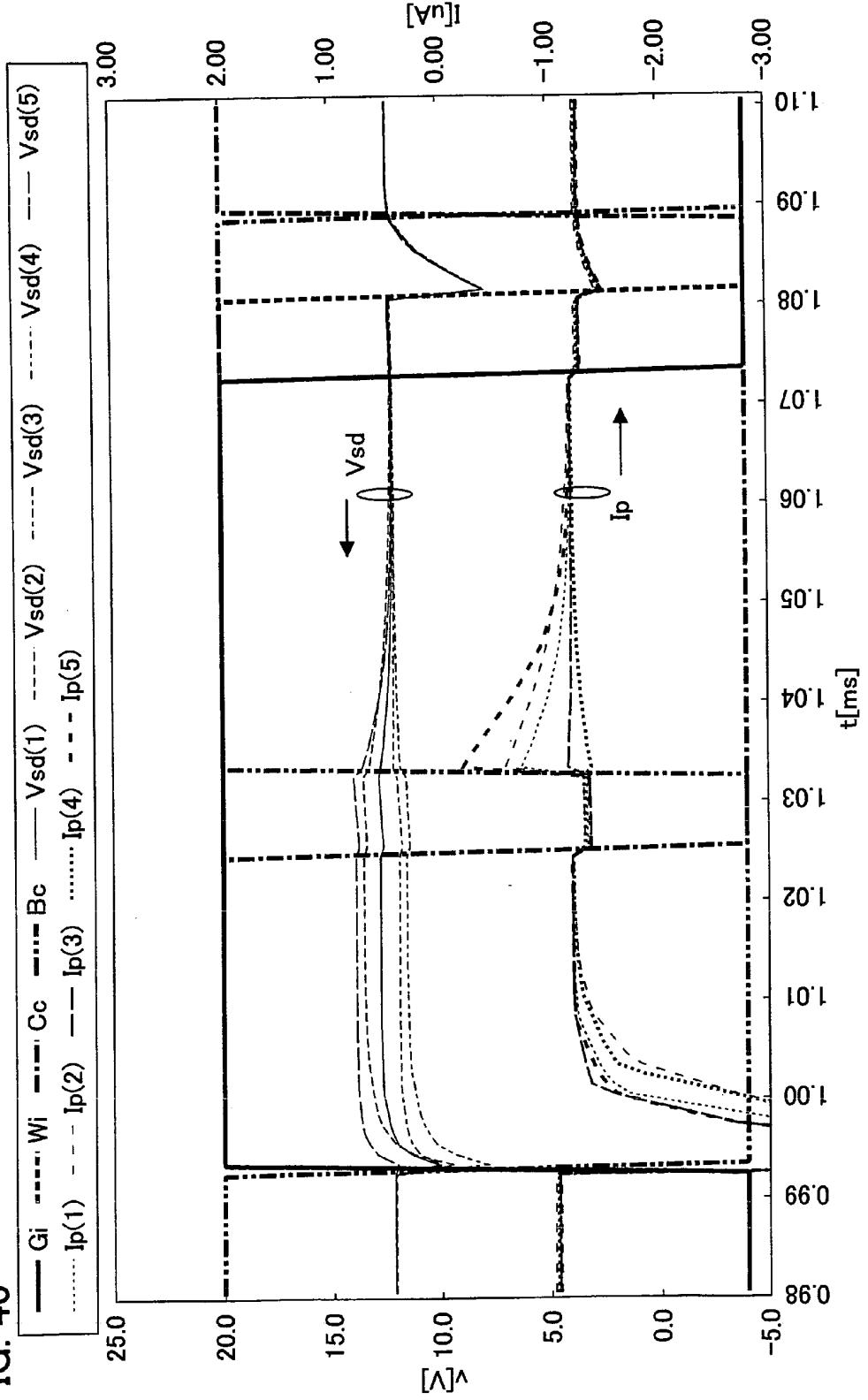

[0104] Now, the selection period of the pixel circuit Aij is over, and then a following pixel circuit A(i+1)j is selected. Here, Fig. 3 illustrates a result of simulating respective changes in (i) the source-gate potential Vsg of the driving TFT 1 of the pixel circuit Aij, and (ii) the source-drain potential Vsd thereof. Note that source-drain potentials Vsd (1) through Vsd (5), and source-gate potentials Vsg (1) through Vsg (5) respectively correspond to the following conditions (see Table 2 below) of the threshold voltage of the driving TFT 1, and of the mobility property thereof.

Table 2

|                   | Ioled(1)      | Ioled(2)          | Ioled(3)          | Ioled(4)          | Ioled(5)          |

|-------------------|---------------|-------------------|-------------------|-------------------|-------------------|

| Vsg(1)            | Vsg(2)        | Vsg(3)            | Vsg(4)            | Vsg(5)            |                   |

| Vsd(1)            | Vsd(2)        | Vsd(3)            | Vsd(4)            | Vsd(5)            |                   |

| Threshold voltage | Average value | Lower limit value | Upper limit value | Upper limit value | Lower limit value |

| Mobility          | Average value | Lower limit value | Upper limit value | Lower limit value | Upper limit value |

[0105] In Fig. 3, a period of time from 460 µs to 470 µs corresponds to the aforesaid first period. As shown in Fig. 3, the source-drain potentials Vsd (1) through Vsd (5) coincided with the source-gate potential Vsg (1) through Vsg (5), respectively.

[0106] Further, a period of time from 480 µs to 490 µs in Fig. 3 corresponds to the aforesaid second period. As shown in Fig. 3, the source-drain potentials Vsd had almost the same value during the period, irrespective of the differences in the conditions of the threshold voltage and the mobility of the driving TFT 1.

[0107] The reason of this is as follows. That is, during the foregoing first period, the second terminal of the second capacitor 7 was connected to the predetermined voltage line Va having a constant potential Va, and then the second

terminal was connected to the drain terminal of the driving TFT 1. This caused the first capacitor and the second capacitor to store a charge allowing the driving TFT 1 to have, when the source-drain potential of the TFT 1 was  $V_s - V_a$ , a source-gate potential equal to the source-gate potential (see Fig. 1 2 ) that the driving TFT 1 had during the first period.

**[0108]** This made it possible to cause the driving TFT 1 to have, when the source-drain potential of the driving TFT 1 was the potential  $V_s - V_a$ , a source-gate potential equal to the source-gate potential that the driving TFT 1 had during the first period, irrespective of the threshold voltage variation and the mobility variation of the driving TFT 1. With the driving TFT 1 thus set, a predetermined current was supplied from the power wire  $V_s$  to the source driver circuit (not shown) via the driving TFT 1, the switching TFT 5, and the source wire  $S_j$ . A source-gate potential  $V_{sg}$  resulting from the current supply allowed a current to constantly flow through the driving TFT 1, irrespective of the threshold voltage variation and the mobility variation of the driving TFT 1, as long as the source-drain potential of the driving TFT 1 was constant.

**[0109]** Thereafter, during a non-selection period (i.e., current readout of the driving transistor; time at and after approximately 500  $\mu s$ ), the source-drain potentials of the driving TFT 1 were changed as shown in Fig. 3. Although the current values were different to some extent, the potential drops occurred in substantially the same manner. This is because the organic EL element 6, which is a load of the driving TFT 1, has a diode-like property. With this, the potential of the drain terminal of the driving TFT 1 was substantially constant irrespective of the threshold voltage variation and the mobility variation of the driving TFT 1. Accordingly, the source-drain voltage of the driving TFT 1 became constant. This allowed a restraint of the variation of the current flowing through the organic EL element, irrespective of the threshold voltage and the mobility of the driving TFT 1.

**[0110]** Note that, it is preferable that the constant potential  $V_a$  is set at a value (an anode potential, which corresponds to the current, of the organic EL) predictable from an applied-voltage / current property of the organic EL element 6. With this, the source-drain voltage of the driving TFT 1 upon the current writing therein becomes substantially equal to the source-drain voltage upon the current readout therefrom.

**[0111]** A simulation was carried out to find the current flowing through the organic EL element 6. A result of the simulation is shown in Fig. 4 and Fig. 5.

**[0112]** In the simulation shown in Fig. 4, the selection period came every 0.32 ms. During an initial period of time from 0.35 ms to 0.67 ms, a current of 0.1  $\mu A$  was set to flow into the source wire  $S_j$ . Thereafter, the current was increased by 0.1  $\mu A$  every 0.32 ms until the current had a value of 0.9  $\mu A$ . Then, the current was set at 0. After that, the current was increased again by 0.1  $\mu A$ .

**[0113]** The current variation found by the simulation is illustrated in Fig. 5 whose horizontal axis plots the respective currents (the respective ten currents of 0  $\mu A$  to 0.9  $\mu A$ ) that flowed to the source wire  $S_j$ , and whose vertical axis plots respective currents that flowed to the organic EL element 6 during each non-selection period, which came after each current supply to the source wire  $S_j$ . In Fig. 5, during the non-selection period coming after the supply of the current of 0.9  $\mu A$  to the source wire  $S_j$ , the current that flowed through the organic EL element varies in a range of about 0.97  $\mu A$  to about 1.01  $\mu A$  (increased by 8% to 13%).

**[0114]** The variation is sufficiently reduced as compared with the result (the current was increased by 5 % to 24 %; in other words, was varied in a range of 19%) of the simulation using the conventional technique shown in Fig. 26. This proves that the means of the present invention is efficient (the current was increased by 8 % to 13%; in other words, was varied in a range of 5%).

**[0115]** Note that an effective way of further restraining the variation in the pixel circuit structure according to the present invention is to optimize (i) respective absolute capacitances of the first capacitor 2 and the second capacitor 7, (ii) a relative ratio of the absolute capacitances, (iii) the constant potential  $V_a$ , (iv) a gate width of the driving TFT 1, and the like.

**[0116]** For example, the variation of the source-drain potential required for the change of the source-gate potential  $V_{sg}$  during the second period can be restrained better as a ratio ( $C_2/C_1$ ) of capacitance  $C_2$  of the second capacitor 7 to capacitance  $C_1$  of the first capacitor 2 is larger. This allows restraint of (i) the variation of the source-drain potential depending on the threshold voltage of the driving TFT 1 and the mobility thereof, and (ii) the variation of the current flowing to the organic EL element 6 during the non-selection period. This is preferable.

**[0117]** When the respective absolute capacitances of the capacitors are too small, the respective potentials retained by the capacitors are affected by the changes of the potentials of the gate terminals of the switching TFTs 3, 8, and 9, each of which is connected to the capacitors. This causes the variation of the current flowing to the organic EL element 6 during the non-selection period. For this reason, this is not preferable.

**[0118]** Further, it is preferable that the constant potential  $V_a$  supplied during the first period be set such that the potential value difference  $V_s - V_a$  between the predetermined voltage line  $V_a$  and the power source wire  $V_s$  is slightly larger than or substantially equal to the source-drain potential  $V_{sd}$  that is to be expected during the non-selection period. That is, too large a potential difference  $V_s - V_a$  causes too large a difference between (i) the source-drain potential  $V_{sd}$  during the current writing period, and (ii) the source-drain potential  $V_{sd}$  during the non-selection period.

Accordingly, the current actually flowing to the organic EL element 6 becomes too small as compared with the current supplied from the source wire Sj. This is not preferable.

[0119] Further, a driving TFT 1 having a too large gate width W causes the driving TFT 1 to have a too small source-gate potential, with the result that the change in the gate potential causes the variation of the current flowing into the organic EL element 6 during the non-selection period. This is not preferable. On the other hand, a driving TFT having a too small gate width W requires a too large source-drain potential for the acquirement of the required current. This is not preferable, either.

[0120] The variation of the current flowing to the organic EL is the least (approximately 1%) in the organic EL element used in Embodiment 1 when C1 is 1000 fF, C2 is 500fF, Vs is 16V, Va is 10 V, and W is 12  $\mu$ m in the pixel circuit Aij shown in Fig. 1. This is suitable.

[0121] Note that the absolute capacitance C1 of the first capacitor 2, the absolute capacitance C2 of the second capacitor 7, the relative ratio of the absolute capacitances, the constant potential Va, and the gate width W of the driving TFT 1 are dependent on (i) the property of the organic EL element to be driven, (ii) a required luminescence, and (iii) the property of the driving TFT 1 to be used. For this reason, such a simulation is required to be carried out several times again upon actually designing a panel.

[0122] Note also that, in the pixel circuit structure shown in Fig. 1, the switching TFT 3 is connected to the source wire Sj so as to connect the gate terminal of the driving TFT 1 to the drain terminal thereof; however, the switching TFT 3 may be directly connected to the drain terminal of the driving TFT 1. This is also true of the switching TFT 9 for connecting the second terminal of the second capacitor 7 to the drain terminal of the driving TFT 1. That is, the switching TFTs 3 and 9 may be directly connected to the drain terminal of the driving TFT 1.

[0123] Further, the organic EL element may be so provided as to be associated with the source terminal of the driving TFT. In such a structure, a driving TFT 1' is an n-type TFT, and has a source terminal connected to a cathode of an organic EL element 6', as shown in Fig. 6. Moreover, in the structure shown in Fig. 6, switching TFTs 4' and 5' are n-type TFTs unlike those in the pixel circuit structure shown in Fig. 1.

[0124] Further, the switching TFTs 3 and 9 are connected to a drain terminal of the driving TFT 1'.

[0125] The other wires and operations in the pixel circuit structure shown in Fig. 6 are the same as those in the structure shown in Fig. 1. Therefore, structures equivalent to those shown in Fig. 1 are given the same reference symbols, and explanation thereof is omitted here.

### 30 [Embodiment 2]

[0126] Embodiment 2 will explain a first example in which the first characteristic structure according to the present invention is applied to a pixel circuit and a source driver circuit.

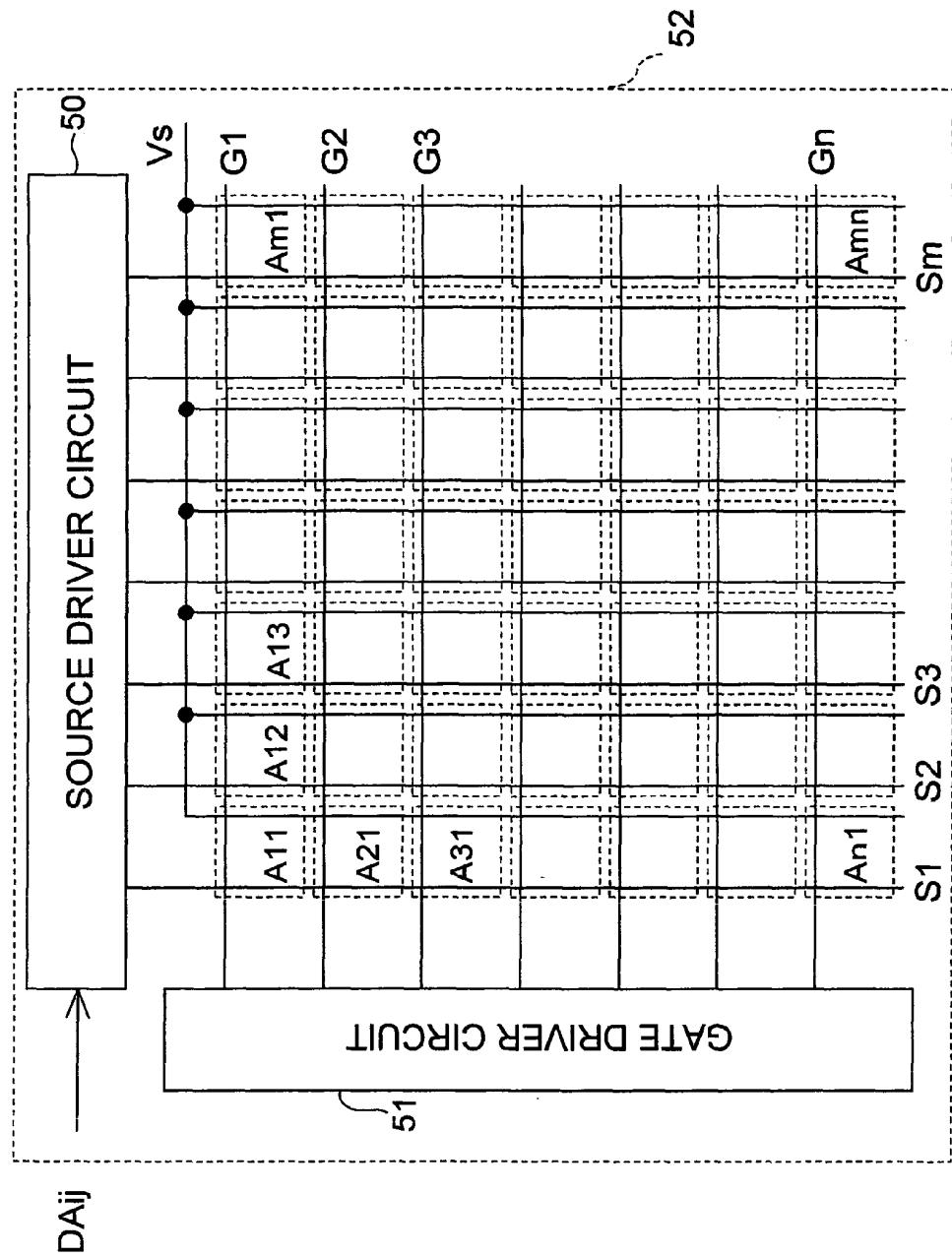

[0127] A display apparatus according to Embodiment 2 is so arranged that components of the characteristic structure of the present invention are provided separately in the pixel circuit and the source driver circuit. See Fig. 7. In the structure of the display apparatus, pixel circuits Aij are provided in regions in which source wires Sj (j is an integer falling within a range from 1 to m) intersect with gate wires Gi (i is an integer falling within a range from 1 to n), respectively. The source wires Sj are connected to a source driver circuit 50, and the gate wires Gi are connected to a gate driver circuit 51. Each of the source wires Sj serves as the first wire, and each of the gate wires Gi serves as the second wire.

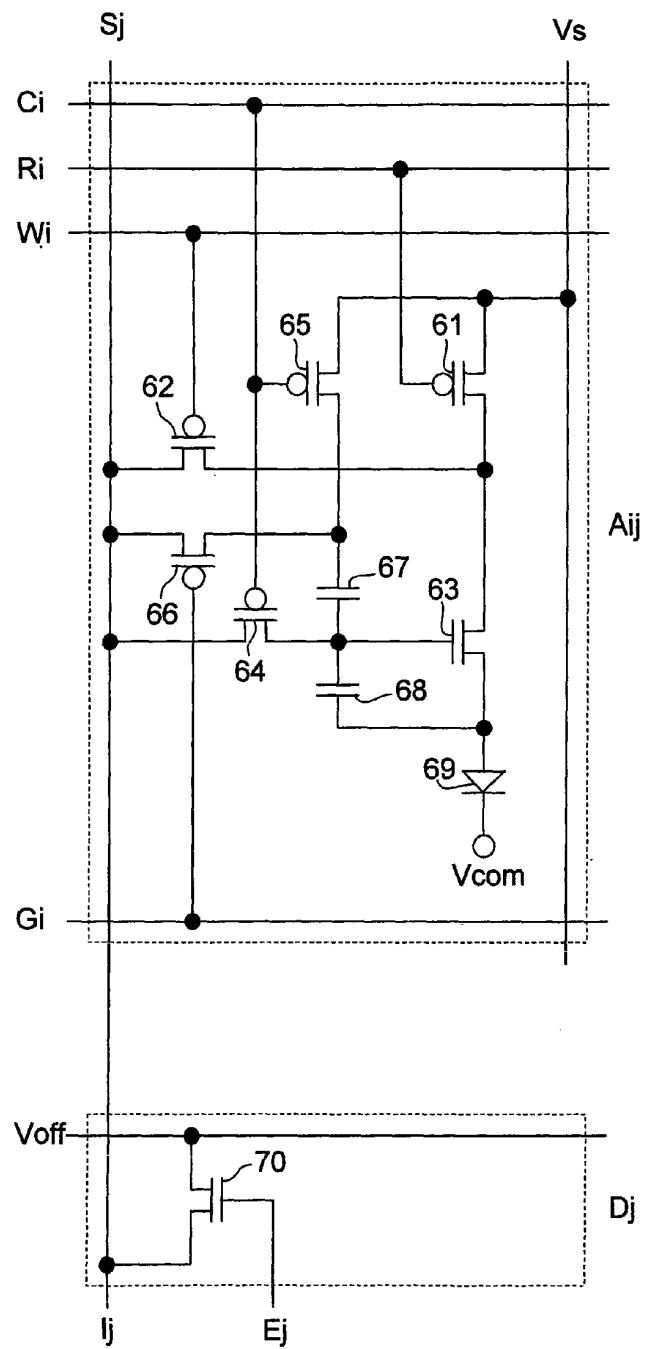

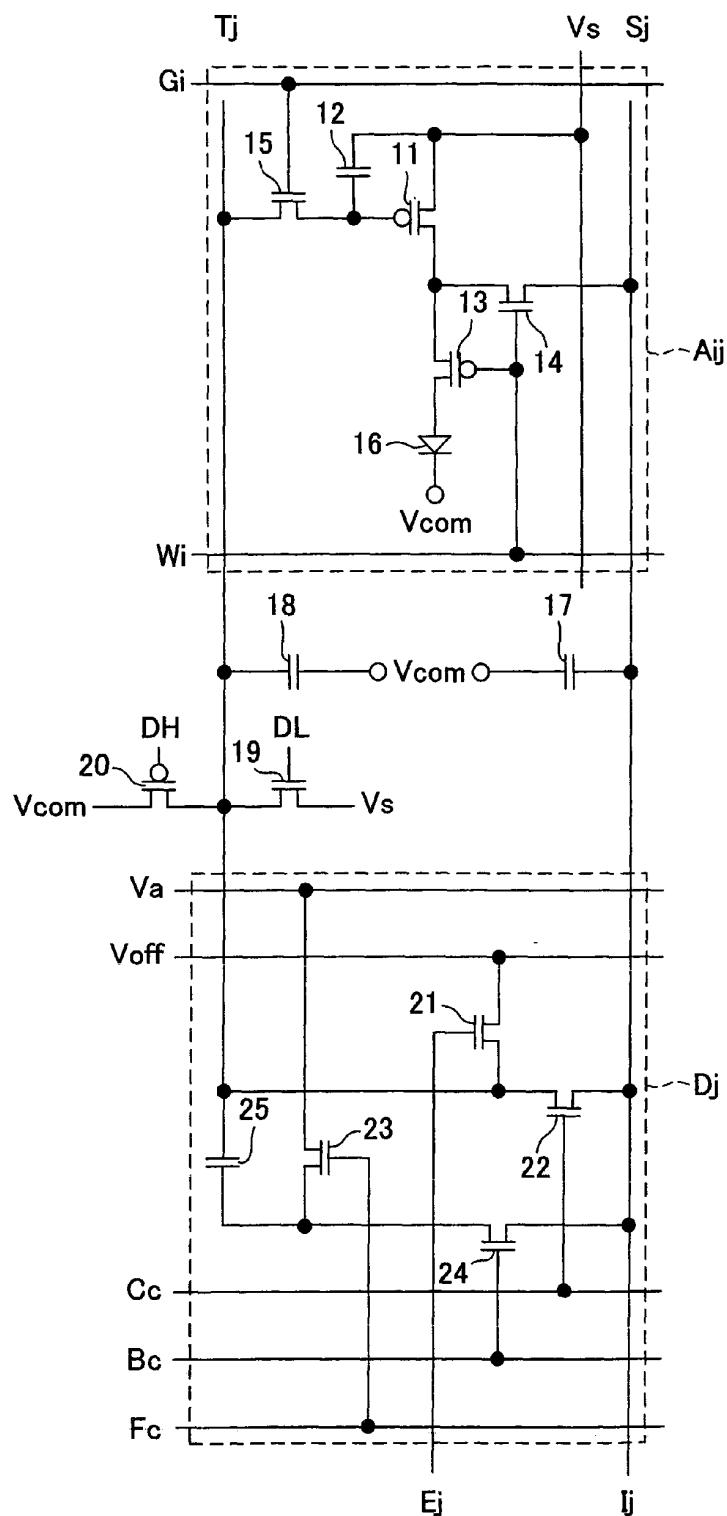

[0128] Fig. 8 illustrates respective structures of each pixel circuit Aij and a source driver output terminal circuit Dj, serving as an output stage of the source driver circuit 50. Each of the pixel circuit Aij and the source driver output terminal circuit Dj includes the characteristic structure of the present invention.

[0129] As shown in Fig. 8, in the display apparatus according to Embodiment 2, the pixel circuit Aij is provided in the region in which the source wire Sj and the gate wire Gi intersect with each other. Provided in the pixel circuit Aij are: (i) a driving TFT 11, which serves as an active element; (ii) an organic EL element 16, which serves as an electric optical element; and (iii), a first capacitor 12. The driving TFT 11 and the organic EL element 16 are provided in series between a power source wire Vs and a common wire Vcom.

[0130] The driving TFT 11 has a gate terminal (current control terminal) connected to one terminal (hereinafter, referred to as "first terminal") of the first capacitor 12. The other terminal (hereinafter, referred to as "second terminal") of the first capacitor 12 is connected to a source terminal (current input terminal) of the driving TFT 11, and to the power source wire Vs.