# (11) **EP 1 341 148 B1**

(12)

# **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication and mention of the grant of the patent: 27.04.2011 Bulletin 2011/17

(51) Int Cl.: **G09G** 3/32<sup>(2006.01)</sup>

(21) Application number: 03004551.2

(22) Date of filing: 28.02.2003

(54) Display device, light emitting device, and electronic equipment

Anzeigegerät, lichtemittierende Vorrichtung und elektronisches Gerät Dispositif d'affichage, dispositif électroluminescent, et appareil électronique

(84) Designated Contracting States: **DE FI FR GB NL**

(30) Priority: **01.03.2002 JP 2002056555 30.08.2002 JP 2002256232**

- (43) Date of publication of application: 03.09.2003 Bulletin 2003/36

- (73) Proprietor: SEMICONDUCTOR ENERGY LABORATORY CO., LTD.

Atsugi-shi,

Kanagawa-ken 243-0036 (JP)

- (72) Inventor: Inukai, Kazutaka, Semiconductor Energy Laboratory Atsugi-shi, Kanagawa-ken 243-0036 (JP)

- (74) Representative: Grünecker, Kinkeldey, Stockmair & Schwanhäusser Anwaltssozietät Leopoldstrasse 4 80802 München (DE)

(56) References cited:

EP-A- 1 170 718 WO-A-99/65012

- YUMOTO A ET AL: "PIXEL-DRIVING METHODS FOR LARGE-SIZED POLY-SI AM-OLED DISPLAYS" ASIA DISPLAY / IDW'01.

PROCEEDINGS OF THE 21ST INTERNATIONAL DISPLAY RESEARCH CONFERENCE IN CONJUCTION WITH THE 8TH INTERNATIONAL DISPLAY WORKSHOPS. NAGOYA, JAPAN, OCT. 16 19, 2001, INTERNATIONAL DISPLAY RESEARCH CONFERENCE. IDRC, SAN JOSE, CA: SI, vol. CONF. 21 / 8, 16 October 2001 (2001-10-16), pages 1395-1398, XP001134248

- WANG Y-W ET AL: "A NEW PIXEL DESIGN FOR IMPROVING THE UNIFORMITY ON ACTIVE MATRIX OLED" ASIA DISPLAY / IDW'01.

PROCEEDINGS OF THE 21ST INTERNATIONAL DISPLAY RESEARCH CONFERENCE IN CONJUCTION WITH THE 8TH INTERNATIONAL DISPLAY WORKSHOPS. NAGOYA, JAPAN, OCT. 16 19, 2001, INTERNATIONAL DISPLAY RESEARCH CONFERENCE. IDRC, SAN JOSE, CA: SI, vol. CONF. 21 / 8, 16 October 2001 (2001-10-16), pages 323-326, XP001134218

P 1 341 148 B1

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

40

50

#### Description

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

[0001] The present invention relates to a light emitting device and to a display device. In addition, the present invention relates to electronic equipment in which the light emitting device or the display device is mounted. The term light emitting device as used in this specification indicates devices that utilize light emitted from a light emitting element. Examples of the light emitting elements include organic light emitting diode (OLED) elements, inorganic material light emitting diode elements, field emission light emitting elements (FED elements) and the like. The term display device as used in this specification indicates devices in which a plurality of pixels are arranged in a matrix shape, and image information is visually transmitted, namely displays.

1

## 2. Description of the Related Art

**[0002]** The importance of display devices that perform display of images and pictures has continued to increase in recent years. Due to their advantages such as high image quality, thin size, and light weight, liquid crystal display devices that perform display of an image by using liquid crystal elements are widely utilized in various types of display devices, such as portable telephones and personal computers.

**[0003]** On the other hand, the development of display devices and light emitting devices that use light emitting elements is also advancing. Elements that use many different types of materials over a wide-ranging area, such as organic materials, inorganic materials, thin film materials, bulk materials, and dispersed materials exist as light emitting elements.

[0004] Organic light emitting diodes (OLEDs) are typical light emitting elements currently seen as promising for all types of display devices. OLED display devices that use OLED elements as light emitting elements are thinner and lighter than existing liquid crystal display devices, and in addition, have characteristics such as high response speed suitable for dynamic image display, a wide angle of view, and low voltage drive. A wide variety of applications are therefore anticipated, from portable telephones and portable information terminals (PDAs) to televisions, monitors, and the like. OLED display devices are under the spotlight as next generation displays.

[0005] In particular, active matrix (AM) OLED display devices are capable of high resolution (large number of pixels), high definition (fine pitch), and a large screen display, all of which are difficult for passive matrix (PM) type displays. In addition, AM-OLED display devices have high reliability at lower electric power consumption operation than that of passive matrix OLEDs, and there are very strong expectations that they will be put into

practical use.

**[0006]** OLED elements are structured by an anode, a cathode, and an organic compound containing layer sandwiched between the anode and the cathode. Normally the brightness of light emitted from the OLED element is roughly proportional to the amount of electric current flowing in the OLED element. A driver transistor that controls the light emission brightness of a pixel OLED element is inserted in series with the OLED element in AM-OLED display device pixels.

[0007] A. Yumoto et al., in a paper entitled "Pixel-Driving Methods for Large-Sized Poly-Si AM-OLED Displays, Asia Display, IDW'01 Proceedings of the 21st International Display Research Conference in Conjunction with the 8th International Display Workshop, Nagojy, Japan, October 16-19, 2001, San Jose, CA, vol. 21/8, pages 1395 - 1398, describe pixel driving techniques and image control schemes realizing a high-quality image on a 13-inch display employing a four transistors pixel driver circuit

**[0008]** EP 1 170 718 A1 describes a pixel circuit in wich multiple drive transistors may be included in order to increase the drive current of the light emitting element over the data write-in current.

**[0009]** Voltage input methods and current input methods exist as driving methods for displaying images in AM-OLED display devices. The voltage input method is a method in which a voltage value data video signal is input to the pixels as an input video signal. On the other hand, the current input method is a method in which a current value video signal is input to the pixels as an input video signal.

**[0010]** The video signal voltage is normally applied directly to a gate electrode of a pixel driver transistor in the voltage input method. If there is dispersion, not uniformity, in the electrical characteristics of the driver transistors across each of the pixels when the OLED elements emit light at a constant current, then dispersion will develop in the OLED element driver current of each of the pixels. Dispersion in the OLED element driver current becomes dispersion in the brightness of light emitted from the OLED elements. Dispersion in the brightness of light emitted by the OLED elements reduces the quality of the displayed image as a sandstorm state or carpet-like pattern unevenness is seen over an entire screen. Stripe shape unevenness is also found, depending upon the manufacturing process.

[0011] In particular, a relatively large electric current is necessary in order to obtain a sufficiently high brightness when OLED elements presently capable of being used, which have low light emission efficiency, are applied as a light emitting device. As a result, it is difficult to use amorphous silicon thin film transistors (TFTs), which have low current capacity, as the driver transistors. Polycrystalline silicon (polysilicon) TFTs are therefore used as the driver transistors. However, there is a problem with polysilicon in that dispersions in the TFT electrical characteristics are likely to develop due to causes

such as faults in the crystal grain boundaries.

**[0012]** The current input method can be used as one effective means in order to prevent dispersion in the OLED element driver current that occurs in this type of voltage input method. A video signal data current value is normally stored with the current input method, and an electric current identical to, or several times as large as, the value of the stored electric current (positive real number multiples, including those less than 1) is supplied as the OLED element driver current.

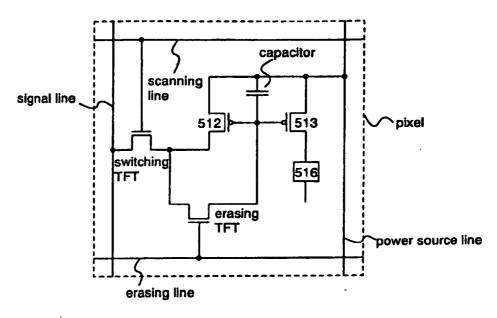

[0013] A typical known example of a pixel circuit of a current input method AM-OLED display device is shown in FIG. 10A (refer to Non-Patent Document 1). Reference numeral 516 denotes an OLED element. This pixel circuit uses a current mirror circuit. Video signal data current values can be accurately stored as long as two transistors structuring the current mirror have identical electrical characteristics. Even if there is dispersion in the electrical characteristics of the driver transistors of different pixels, dispersion in the brightness of light emitted by the OLED elements can be prevented as long as the two transistors within the same pixel each have identical electrical characteristics.

[0014] Another typical known example of a pixel circuit of a current input method AM-OLED display device is shown in FIG. 10B (refer to Non-Patent Document 2). Reference numeral 611 denotes an OLED element. This pixel circuit has a short circuit between a drain electrode, and a gate electrode, of a driver transistor itself when a voltage corresponding to a video signal is written into the gate electrode of the driver transistor. A video signal data current is made to flow in this state, and the gate electrode is then electrically insulated. By doing so, an electric current having a value identical to the data current during write-in is supplied to the OLED element by the driver transistors, provided that the driver transistors are operated in the saturated region. Dispersion in the brightness of light emitted by the OLED elements can therefore be prevented, even if dispersion exists in the electrical characteristics of the driver transistors of each pixel.

[0015] [Non-Patent Document 1] Yumoto, A., et al., Proc. Asia Display / IDW '01, pp. 1395-1398 (2001). [0016] [Not-Patent Document 2] Hunter, I. M., et al.,

Proc. AM-LCD 2000, pp. 249-252 (2000).

[0017] The data current value should be able to be accurately stored with FIGs. 10A and 10B, as discussed above, but there are serious problems as stated below. [0018] First, a problem with the pixel circuit of FIG. 10A is that there is a precondiction in which the two transistors 512 and 513 that structure the current mirror must have identical electrical characteristics. Provided that it is considered during design, it is possible to manufacture both transistors adjacently on a substrate, and dispersion can be reduced to a certain extent. However, dispersions in the electrical characteristics of TFTs, such as threshold voltage and field effect mobility, that exceed a permissible limit normally remain in present-day polysilicon due to causes such as faults in the crystal grain boundaries.

**[0019]** Specifically, it becomes necessary to keep brightness within a range on the order of 1%, for example, if a 64 gray scale image is displayed. However, storing the data current values at a precision of 1% with the pixel circuit of FIG. 10A is difficult to achieve with the polysilicon normally in use at present. In other words, a sufficiently uniform, high quality display image over an entire screen, without irregularities, cannot be obtained by only using the pixel circuit of FIG. 10A.

[0020] Next, the fact that the video signal data current written into the pixel has the identical value to the OLED element driver current when the OLED element emits light is a problem with the pixel circuit of FIG. 10B. The fact that both electric currents must have identical values is a very severe restriction in practice when manufacturing an AM-OLED display device.

**[0021]** Specifically, a large amount of parasitic capacitance and parasitic resistance exists in signal lines and the like in an actual AM-OLED display device. As a result, it often becomes necessary to take steps to make the video signal data current larger than the OLED element driver current. In particular, it becomes extremely difficult to write in the video signal data current of dark portions for cases in which the video signal data current is made into an analog value for gray scale expression.

#### SUMMARY OF THE INVENTION

[0022] The present invention has been made in view of the aforementioned problem points. First, an object of the present invention is to provide an AM-OLED display device in which the ratio between a video signal data current written into a pixel, and an OLED element driver current during OLED element light emission, is not fixed to a value of "1", differing from the pixel circuit of FIG. 10B. Next, the present invention is premised on the fact that it is possible for dispersion in electric characteristics to remain to a certain extent, even between transistors placed adjacently within the same pixel, differing from the pixel circuit of FIG. 10A. Therefore, another object of the present invention is to provide an AM-OLED display device in which dispersion in the OLED element driver currents is sufficiently inhibited compared to pixel circuits that use a current mirror like that of FIG. 10A.

[0023] Note that the constitution of the present invention can be effectively utilized when using current driven elements in display devices and light emitting devices that use elements other than OLED elements.

**[0024]** In order to solve the aforementioned objectives, there is provided a display device according to claim 1. Driver elements are disposed in each pixel of an AM display device or a light emitting device and are structured by a plurality of transistors, the plurality of transistors are placed in a parallel connection state when a data current is written into the pixel, and the plurality of transistors are placed in a series connection state when a light emitting element emits light.

[0025] Note that the constitution of the present inven-

tion can be utilized when using current driven elements in display devices and light emitting devices that use elements other than OLED elements.

[0026] An outline of the pixel structure of this type of display device or light emitting device of the present invention is explained using FIGs. 1A and 1B. FIG. 1A shows a pixel 11 disposed in a j-th row and an i-th column in a pixel portion having a plurality of pixels. The pixel 11 has a signal line (Si), a power source line (Vi), a first scanning line (Gaj), a first switch 12 having a switching function, a third switch 14 having a switching function, a third switch 14 having a switching function, a driver element 15, a capacitor element 16, and a light emitting element 17. Note that it is not always necessary to form the capacitor element 16 for cases such as those where the parasitic capacitance of a node at which the capacitor element 16 is disposed is large.

[0027] An OLED element is typically applied as the light emitting element, and therefore a diode reference symbol may also be used in this specification as a reference symbol that expresses the light emitting element. However, diode characteristics are not necessary in the light emitting element, and the present invention is not limited to light emitting elements that possess diode characteristics. In addition, the light emitting elements in this specification may be current driven display elements, and it is not necessary that the elements have a display function due to emitted light. For example, light shutters such as liquid crystals that can be controlled by electric current values, not voltage values, are also included in the category of light emitting elements in this specification.

[0028] One semiconductor element, or a plurality of semiconductor elements, having a switching function, such as a transistor can be used in the first switch 12, the second switch 13, and the third switch 14. A plurality of semiconductor elements such as transistors can also be used similarly in the driver element 15. On and off states for the first switch 12 and the second switch 13 are determined by signals imparted from the first scanning line (Gaj). It is sufficient that the first switch 12 and the second switch 13 function as switching elements, and therefore no particular limitations are placed on the conductivity type of the semiconductor elements used.

**[0029]** Note that the first switch 12 located between the signal line (Si) and the driver element 15, and plays a role in controlling signal write-in to the pixel 11. Further, the second switch 13 is located between the power source line (Vi) and the driver element 15, and controls the supply of electric current form the power source line to the pixel 11.

**[0030]** A case of additionally disposing a fourth switch 18 and a second scanning line (Gbj) in the pixel 11 of FIG. 1A is shown in FIG. 1B. One semiconductor element, or a plurality of semiconductor elements, having a switching function, such as transistors, can be used in the fourth switch 18. On and off states for the fourth switch 18 are determined by signals imparted from the second scanning line (Gbj). It is sufficient that the first switch 12

and the second switch 13 function as switching elements, and therefore no particular limitations are placed on the conductivity type of the semiconductor elements used.

**[0031]** Note that the fourth switch 18 plays a role as an initialization element for the pixel 11. Electric charge stored in the capacitor element 16 is released if the fourth switch 18 turns on, the driver element 15 turns off, and in addition, light emission by the light emitting element 17 stops.

[0032] The present invention is characterized in that the driver element 15 is structured by a plurality of transistors, and the connection between the plurality of transistors is switched to a parallel connection for cases in which a video signal data current is written into the pixel 11, or to a serial connection for cases in which electric current flows in the light emitting element 17, which thus emits light. On and off control of the first switch 12 and the second switch 13 by signals from the scanning line (Gaj) in FIGs. 1A and 1B becomes a means for switching the plurality of transistors in the driver element 15 between a parallel connection state and a series connection state.

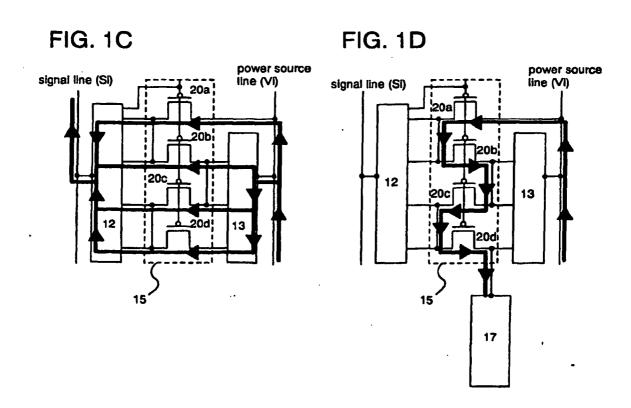

[0033] Examples of the pixel 11 for a case of structuring the driver element 15 by using four transistors 20a, 20b, 20c, and 20d are shown in FIGs. 1C and 1D. Explanations of current pathways in the pixel 11 are provided below. [0034] FIG. 1C shows a case of writing a data current into the pixel 11, and FIG. 1D shows a case of the light emitting element emitting light. Note that elements other than the first switch 12, the second switch 13, the driver element 15, the light emitting element 17, the signal line (Si), and the power source line (Vi) are not shown in FIGs. 1C and 1D.

[0035] A case in which a data current is written into the pixel 11 is explained first. The first switch 12 and the second switch 13 turn on due to a signal imparted from the first scanning line (Gaj) in FIG. 1C. Each transistor in the driver element 15 is thus placed in a diode connected state, and all of the transistors are mutually connected in a parallel connection state. A current pathway exists from the power source line (Vi), through the second switch 13, the driver element 15, and the first switch 12, to the signal line (Si). A current value I<sub>w</sub> at this point is the data current value of the video signal, and is a predetermined current value output to the signal line (Si) by a signal line driver circuit.

[0036] A case in which the light emitting element 17 emits light is explained next. The first switch 12 and the second switch 13 are turned off by a signal imparted from the first scanning line (Gaj) in FIG. 1D. Each of the transistors in the driver element 15 are thus mutually connected in a series connection state. A current pathway exists from the power source line (Vi), through the transistors 20a, 20b, 20c, and 20d, to the light emitting element 17. The brightness of light emitted by the light emitting element 17 is determined by a current value I<sub>E</sub> at this point.

[0037] As discussed above, the transistors 20a to 20d

40

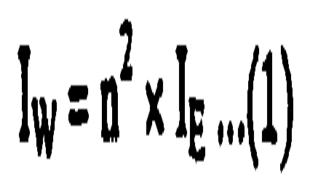

that structure the driver element 15 are used in parallel with the present invention during write-in of the data current to the pixel (see FIG. 1C). In addition, the transistors 20a to 20d that structure the driver element 15 are used in series when electric current flows in the light emitting element 17 of the pixel 11, that is when the light emitting element is driven (see FIG. 1D). The current value  $I_{\mbox{\tiny LW}}$ during write-in therefore becomes 16 times (42 times) the current value I<sub>F</sub> during light emitting element drive, if it is assumed that the electrical characteristics of the transistors 20a to 20d are identical. In general, if the number of transistors structuring the driver element 15 is considered to be n, then a relationship shown by Eq. 1 is established between the current value  $I_{\rm w}$  during video signal write-in and the current value I<sub>E</sub> during light emitting element drive, under the condition that all of the transistors have identical electrical characteristics.

# $I_W = n^2 \times I_E ...(1)$

**[0038]** Here, n is preferably between 3 and 5. Note that, in order to strictly establish Eq. 1, there is a condition that all of the transistors structuring the driver element 15 must possess identical electrical characteristics. However, it is possible in practice to treat Eq. 1 as if approximately established, even for cases involving a slight amount of mutual dispersion in the electrical characteristics of the transistors.

**[0039]** Thus, the present invention is characterized in that the driver element 15 is structured by the plurality of transistors, and the current value  $I_w$  during write-in, and the current value  $I_E$  during light emitting element drive, can therefore be arbitrarily set by switching the connection between the plurality of transistors between parallel and serial for cases of writing a video signal current into the pixel 11 and for cases of the light emitting element emitting light.

**[0040]** Further, the present invention is also characterized in that the influence of slight, mutual differences in the electrical characteristics of each of the transistors structuring the driver element 15 can be greatly reduced from being reflected in the light emitting element drive current  $I_E$ . A specific example of this is taken up and explained in an embodiment mode.

**[0041]** Even with a pixel circuit using a current mirror like that of FIG. 10A, there is a problem in that identical electrical characteristics are required for the two transistors within the pixel. However, even the transistors within the same pixel are already presupposed to have slightly different electrical characteristics in the present invention. That is, the present invention is superior compared to pixel circuits that use current input method current mirrors in that the present invention has tolerance for dispersions in the characteristics of the transistors. As a result, it becomes possible to make the light emitting element driver current  $I_{\rm E}$  uniform to a level at which it can

be put into practical use, even if dispersions in the electrical characteristics of polysilicon TFTs, caused by defects in crystal grain boundaries and the like, exist.

[0042] The display device and the light emitting device of the present invention are display devices provided with a plurality of pixels. The pixels each have a driver element provided with a light emitting element and a plurality of transistors. The display device and the light emitting device of the present invention are characterized by including a means capable of making, at minimum, a state in which the plurality of transistors in the driver element are connected in parallel, and a state in which the plurality of transistors in the driver element are connected in series. The term light emitting device as used in this specification indicates devices that utilize light emitted form a light emitting element. Examples of light emitting elements include organic light emitting diode (OLED) elements, inorganic material light emitting diode elements, and field emission light emitting elements (FED elements). The term display device as used in this specification indicates devices in which a plurality of pixels are arranged in a matrix shape, and image information is transferred visually, namely displays.

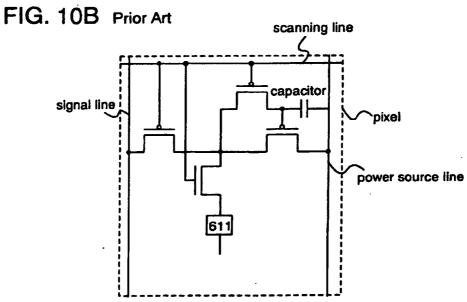

[0043] An outline of a pixel structure of the display device and the light emitting device of the present invention that differs from that of FIGs. 1A and 1B is explained here using FIGs. 11A and 11B. The pixel 11 disposed in the j-th row and the i-th column in the pixel portion having a plurality of pixels is shown in FIG. 11A. The pixel 11 of FIG. 11A is provided with a signal line (Si), a power source line (Vi), a first scanning line (Gaj), a second scanning line (Gbj), a third scanning line (Gcj), a fourth scanning line (Gdj), a first switch 312, a second switch 313, a third switch 314, a fourth switch 318, a driver element 315, a capacitor element 316, a light emitting element 317, and an opposing electrode 319, for example. However, even if the structure with the first switch, the second switch, the third switch, the fourth switch, the first scanning line (Gaj), the second scanning line (Gbj), the third scanning line (Gcj), the fourth scanning line (Gdj), and the like is changed slightly, in practice the same device can be obtained. One example of such is FIG. 11B. The fourth switch is removed, and the third scanning line is unified with the second scanning line in FIG. 11B. This is also identical in practice to FIG. 11A, and in the absence of any specific limitations, is taken as being included in FIG. 11A. Cases of adding components such as initialization elements are also similarly treated.

**[0044]** Note that the capacitor element 316 does not always have to be expressly formed in FIGs. 11A and 11B for cases in which the parasitic capacitance of a node at which the capacitor element 316 is disposed is large, and the like.

**[0045]** A single semiconductor element, or a plurality of semiconductor elements, having a switching function such as transistors, can be used in the first switch 312, the second switch 313, the third switch 314, and the fourth switch 318. A plurality of semiconductor elements such

20

40

as transistors can also be similarly used in the driver element 315. There are no particular limitations placed on the conductivity type (n-channel, p-channel) of the semiconductor elements used in the first switch 312, the second switch 313, the third switch 314, the fourth switch 318, and the driver element 315. This is mostly because n-channel and p-channel types can both be used, and there are cases in which a specified conductivity type is more preferable than another conductivity type for specific applied examples.

[0046] A signal imparted from the first scanning line (Gaj) determines whether the first switch 312 is on or off. Similarly, a signal form the second scanning line (Gbj) determines whether the second switch 313 is on or off, a signal from the third scanning line (Gcj) determines whether the third switch 314 is on or off, and a signal from the fourth scanning line (Gdj) determines whether the fourth switch 318 is on or off. It is of course not necessary for all of the scanning lines, the first scanning line (Gaj), the second scanning line (Gbj), the third scanning line (Gcj), and the fourth scanning line (Gdj), to exist, and a certain scanning line can also be combined with other scanning lines, as is made clear by FIG. 11B.

[0047] The first switch 312 is disposed between the signal line (Si) and the driver element 315 in FIG. 1A, and serves a role for controlling signal write-in to the pixel 11. Further, the second switch 313 and the fourth switch 318 are disposed between the power source line (Vi) and the driver element 315, and perform on and off control of the supply of electric current form the power source line (Vi) to the pixel 11. The third switch 314 is disposed between the driver element 315 and the light emitting element 317, and performs on and off control of the supply of electric current form the driver element 315 to the light emitting element 317.

[0048] In the present invention, the driver element 315 is structured by the plurality of transistors, and the plurality of transistors are connected in parallel when a video signal data current is written into the pixel 11. The plurality of transistors are connected in series when electric current flows in the light emitting element 317, and light is emitted. It becomes possible to place the plurality of transistors in the driver element 315 in a parallel connection state, and also in a series connection state, by controlling the on and off states of the first switch, the second switch, the third switch, and the fourth switch using the signals from the scanning lines (Gaj, Gbj, Gcj, and Gdj) in FIG. 11A.

**[0049]** The pixel 11 is shown in FIGs. 11C and 11D here as an example of a case in which the driver element 315 is structured by four transistors 320a, 320b, 320c, and 320d. Electric current pathways in the pixel 11 are explained below.

**[0050]** FIG. 11C shows a case of writing a data current into the pixel 11, and FIG. 11D shows a case of the light emitting element emitting light. With FIG. 11C, the four transistors 320a, 320b, 320c, and 320d are in a parallel connection state, while the four transistors 320a, 320b,

320c, and 320d are in a series connection state in FIG. 11D. Note that element and wirings other than the first switch 312, the second switch 313, the driver element 315, the light emitting element 317, the source signal line (Si), and the power source line (Vi) are omitted from being shown in FIGs. 11C and 11D.

[0051] A case of writing a data current into the pixel 11 is explained first. The first switch 312 and the second switch 313 are turned on in FIG. 11C by signals imparted from the first scanning line (Gaj) and the second scanning line (Gbj), respectively. Each of the transistors in the driver element 315 is thus placed into a diode connected state, and the transistors are thus mutually placed in a parallel connection state. The third switch 314 and the fourth switch 318 turn off by signals input from the third scanning line (Gcj) and the fourth scanning line (Gdj), respectively. A current pathway exists from the power source line (Vi), through the second switch 313, the driver element 315, and the first switch 312, to the signal line (Si) when the power source line (Vi) has a high electric potential. The opposite is naturally true if the power source line (Vi) has a low electric potential. The current value I<sub>w</sub> is the value of the video signal data current at this point, and is a predetermined current value output to the signal line (Si) from a signal line driver circuit.

[0052] A case of the light emitting element 317 being made to emit light is explained next. The first switch 312 and the second switch 313 are turned off by signals imparted form the first scanning line (Gaj) and the second scanning line (Gbj), respectively, in FIG. 11D. The transistors in the driver element 315 are thus mutually placed in a series connection state. The third switch 314 and the fourth switch 318 turn off due to signals imparted form the third scanning line (Gcj) and the fourth scanning line (Gdj), respectively. A current pathway exists from the power source line (Vi), through the transistors 310a, 320b, 320c, and 320d, and to the light emitting element 317 when the power source line (Vi) has a high electric potential. The opposite is naturally true if the power source line (Vi) has a low electric potential. The current value I<sub>F</sub> determines the brightness of light emitted by the light emitting element 317 at this point.

[0053] The transistors 320a, 320b, 320c, and 320d that structure the driver element 315 are used parallelly when writing a data current into the pixel in the present invention (see FIG. 11C). On the other hand, the transistors 320a, 320b, 320c, and 320d that structure the driver element 315 are used serially when electric current flows in the light emitting element 317 of the pixel 11, that is when the light emitting element is driven (see FIG. 11D). The current value I<sub>w</sub> during write-in therefore becomes 16 (4<sup>2</sup>) times the current value  $I_{\rm E}$  when the light emitting element is driven, provided that the electrical characteristics of the transistors 320a, 320b, 320c, and 320d are presumed to be identical. In general, if the number of transistors structuring the driver element 15 is considered to be n, then the relationship shown by Eq. 1 is established between the current value I<sub>w</sub> during video signal

write-in and the current value I<sub>E</sub> during light emitting element drive, under the condition that all of the transistors have identical electrical characteristics.

#### BRIEF DESCRIPTION OF THE DRAWINGS

#### [0054] In the accompanying drawings:

FIGs. 1A to 1D are diagrams showing a pixel of a display device and a light emitting device of the present invention;

FIGs. 2A and 2B are diagrams showing a pixel of a display device and a light emitting device of the present invention;

FIGs. 3A and 3B are diagrams showing a pixel of a display device and a light emitting device of the present invention;

FIGs. 4A and 4B are diagrams showing a pixel of a display device and a light emitting device of the present invention;

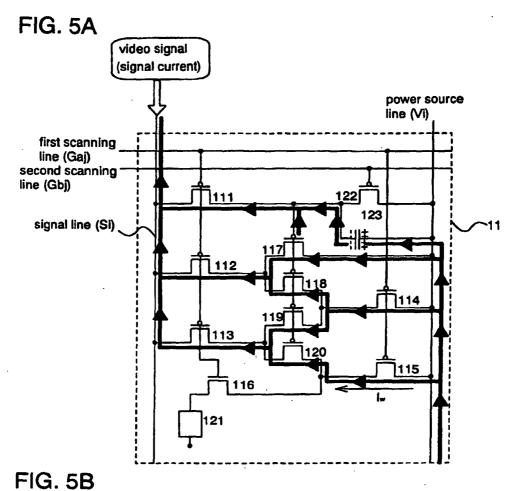

FIGs. 5A and 5B are diagrams showing current pathways in a pixel of a display device and a light emitting device of the present invention;

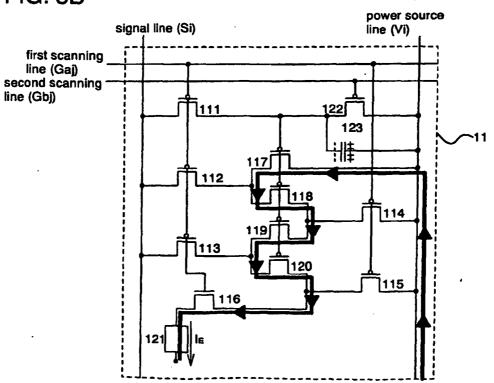

FIG. 6 is a diagram showing a planar layout of a pixel of a display device and a light emitting device of the present invention;

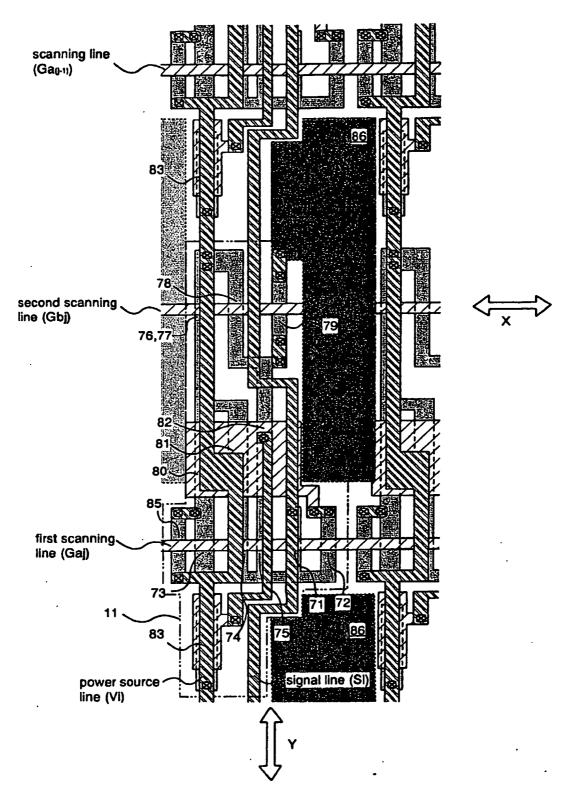

FIGs. 7A to 7C are diagrams showing a display device and a light emitting device of the present invention;

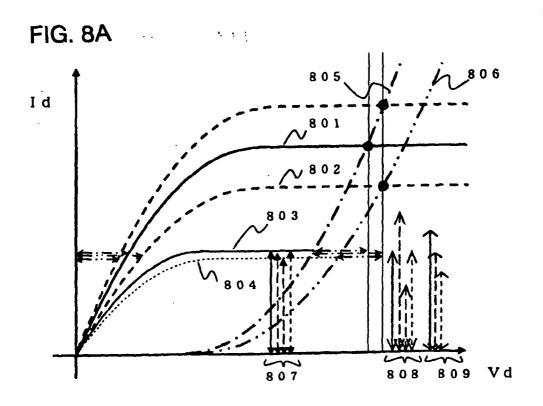

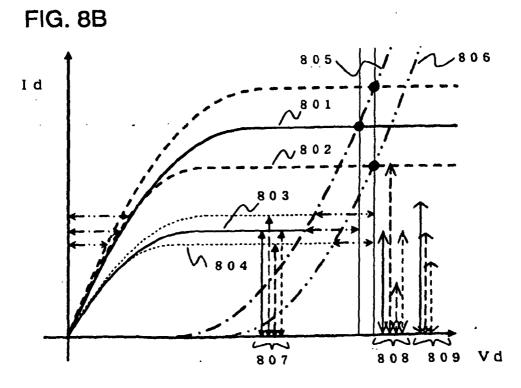

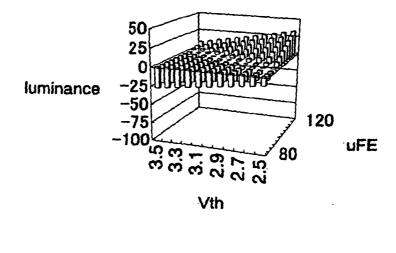

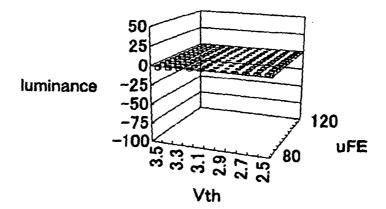

FIGs. 8A and 8B are diagrams showing characteristics of transistors structuring a driver element;

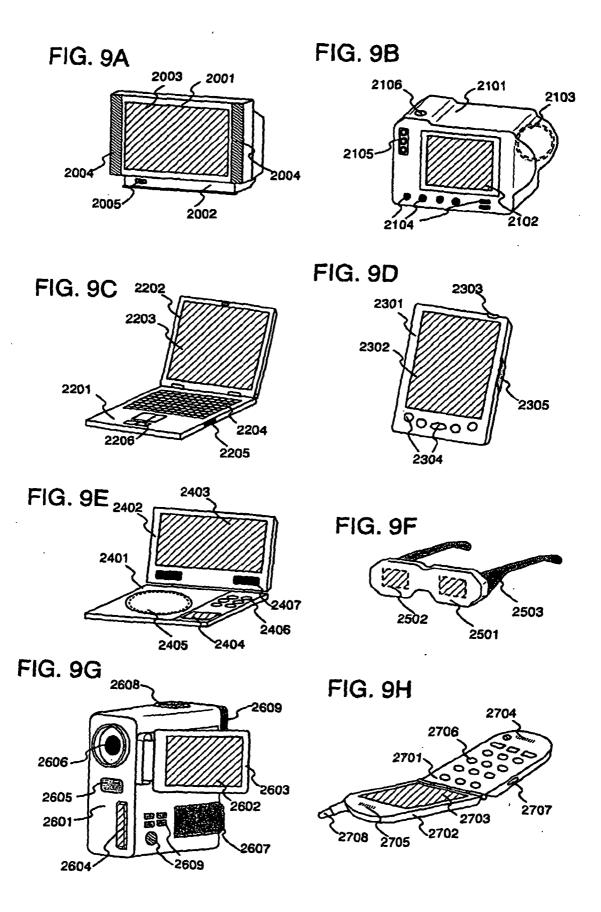

FIGs. 9A to 9H are diagrams showing electronic equipment to which a display device and a light emitting device of the present invention are applied;

FIGs. 10A and 10B are diagrams showing a pixel of a known display device and a known light emitting device:

FIGs. 11A to 11D are diagrams showing a pixel of a display device and a light emitting device of the present invention;

FIGs. 12A to 12E are diagrams showing a pixel of a display device and a light emitting device of the present invention;

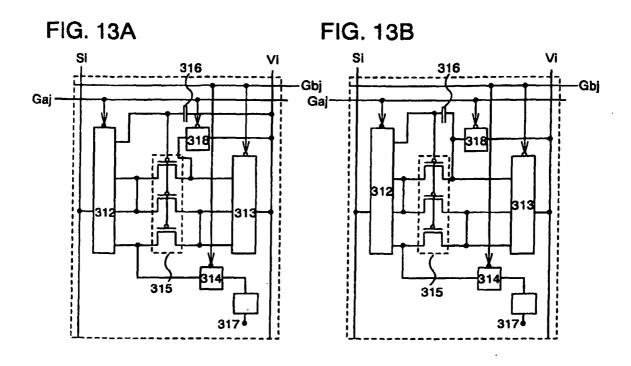

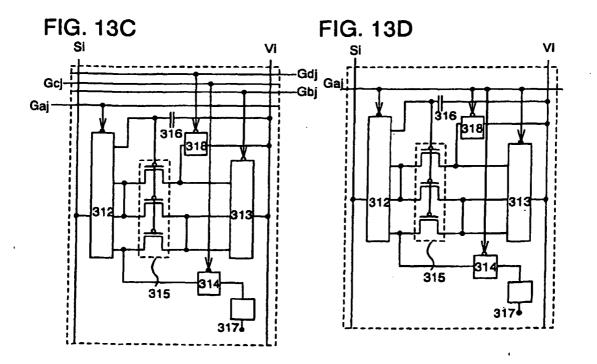

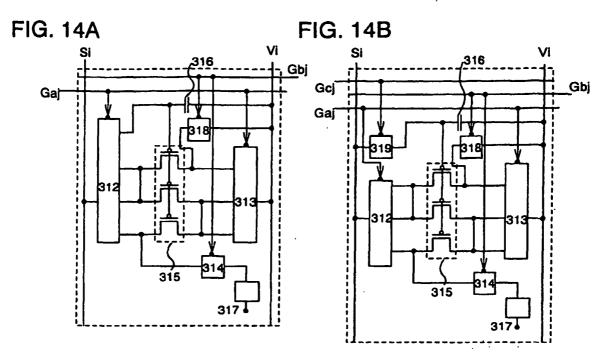

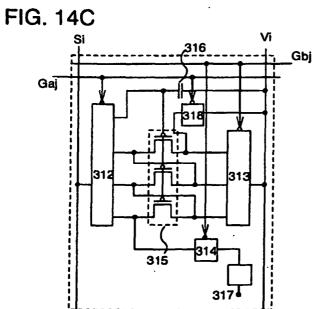

FIGs. 13A to 13D are diagrams showing a pixel of a display device and a light emitting device of the present invention;

FIGs. 14A to 14C are diagrams showing a pixel of a display device and a light emitting device of the present invention;

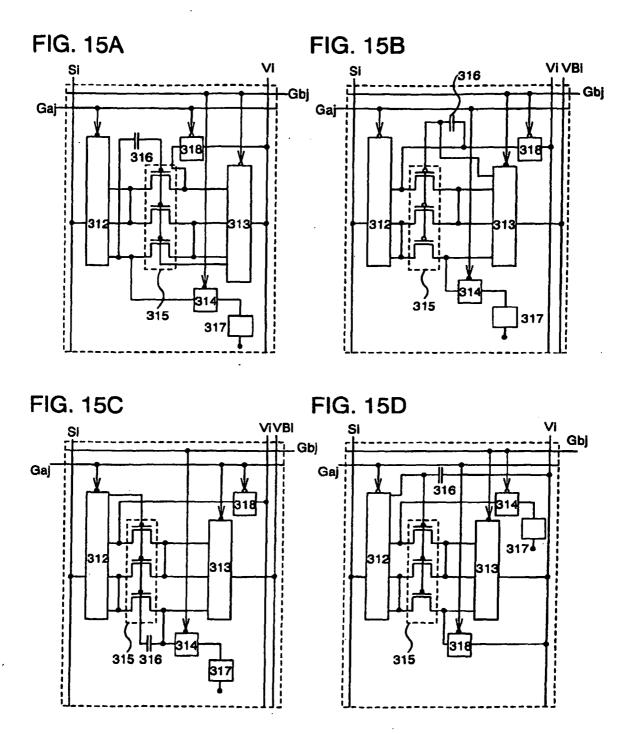

FIGs. 15A to 15D are diagrams showing a pixel of a display device and a light emitting device of the present invention;

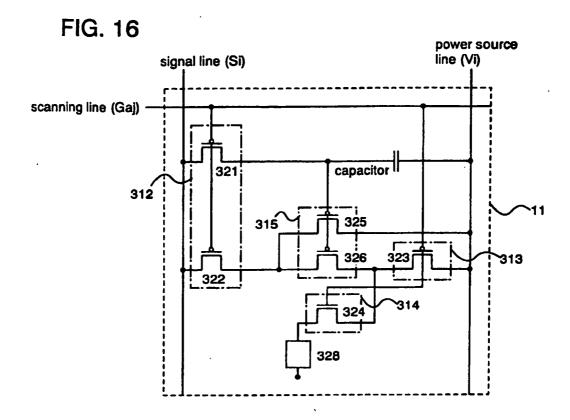

FIG. 16 is a diagram showing a pixel of a display device and a light emitting device of the present invention; and

FIGs. 17A and 17B are diagrams showing the display brightness of a light emitting device of the present invention for a cases in which the characteristics of

transistors structuring a driver element have been changed.

# <u>DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS</u>

#### [Embodiment Mode 1]

**[0055]** An outline of a pixel of a display device and a light emitting device of the present invention has been discussed above using FIGs. 1A to 1D. A specific example of a pixel of a display device and a light emitting device of the present invention is explained in Embodiment Mode 1 using FIGs. 2A to 4B. For simplification, cases in which n, the number of transistors structuring the driver element 15, is from two to four are given as examples.

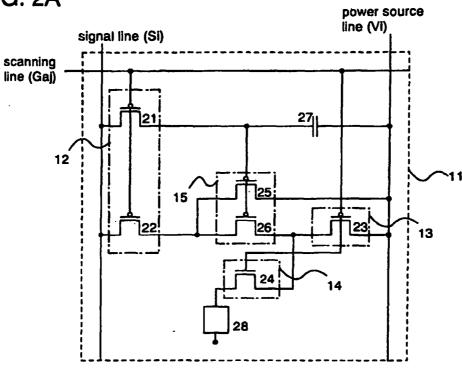

[0056] A first example is explained using FIG. 2A.

[0057] The pixel 11 disposed in the j-th row and the i-th column is shown in FIG. 2A. The pixel 11 has a signal line (Si), a power source line (Vi), a scanning line (Gaj), transistors 21 to 26, a capacitor element 27, and a light emitting element 28. The pixel 11 shown in FIG. 2A is the pixel 11 shown in FIG. 1A, but shown specifically by transistors. The transistors 21 and 22, which are p-channel, correspond to the first switch 12. The transistor 23, which is p-channel, corresponds to the second switch 13, and the transistor 24, which is n-channel, corresponds to the third switch 14. The transistors 25 and 26, which are p-channel, correspond to the driver element 15.

[0058] Each gate electrode of the transistors 21 to 24 is connected to the scanning line (Gaj). The capacitor 27 performs a role in storing the voltage between a gate and a source of the transistor 25. Note that it is not always necessary to form the capacitor element 27 for cases in which the gate capacitances of the transistors 25 and 26 are large, for cases in which the parasitic capacitance of a node is high, and the like.

[0059] A low electric potential signal is sent to the scanning line (Gaj) in the pixel 11 shown in FIG. 2A during write-in of a video signal data current, and the transistors 21 to 23 turn on, while the transistor 24 turns off. A parallel connection relationship between the transistors 25 and 26 is formed at this point, based on the current pathway. On the other hand, a high electric potential signal is sent to the scanning line (Gaj) when electric current flows in the light emitting element 28, and the transistors 21 to 23 turn off, while the transistor 24 turns on. A series connection relationship is formed between the transistors 25 and 26 at this point, based on the current pathway.

**[0060]** Switching of the connection relationship between the transistors 25 and 26 of the driver element 15 is controlled by only the scanning line (Gaj) in the example of FIG. 2A. Further, the first switch is structured by only two transistors, and the second switch is structured by only one transistor, a structure having the least number of transistors. The number of scanning lines and the number of transistors are thus suppressed in the ex-

40

ample of FIG. 2A, and therefore this structure is applicable to cases in which securing a large aperture ratio or reducing the proportion of structural defects generated is important.

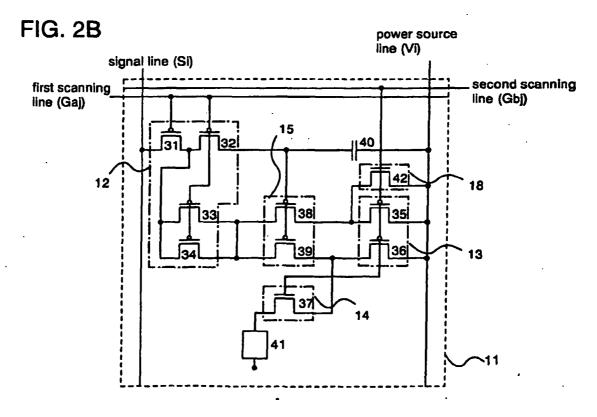

**[0061]** An example that differs from that of FIG. 2A is explained next using FIG. 2B.

[0062] The pixel 11 disposed in the j-th row and the i-th column is shown in FIG. 2B. The pixel 11 has a signal line (Si), a power source line (Vi), a first scanning line (Gaj), a second scanning line (Gbj), transistors 31 to 39, and 42, a capacitor element 40, and a light emitting element 41. The pixel 11 shown in FIG. 2B is the pixel 11 shown in FIG. 1B, but shown specifically by transistors. The transistors 31 to 34, which are p-channel, correspond to the first switch 12. The transistors 35 and 36 which are p-channel, correspond to the second switch 13, and the transistor 37, which is n-channel, corresponds to the third switch 14. The transistors 38 and 39, which are p-channel, correspond to the driver element 15. The transistor 42, which is n-channel, corresponds to the fourth switch 18.

[0063] Each gate electrode of the transistors 31 to 34 is connected to the first scanning line (Gaj). Each gate electrode of the transistors 35 to 37, and 42 is connected to the second scanning line (Gbj). The capacitor element 40 performs a role in storing the voltage between a gate and a source of the transistor 38. Note that it is not always necessary to form the capacitor element 40 for cases in which the gate capacitances of the transistors 38 and 39 are large, for cases in which the parasitic capacitance of a node is high, and the like.

[0064] A low electric potential signal is sent to the first scanning line (Gaj) and the second scanning line (Gbj) in the pixel 11 shown in FIG. 2B during write-in of a video signal data current, and the transistors 31 to 36 turn on, while the transistors 37 and 42 turn off. A parallel connection relationship between the transistors 38 and 39 is formed at this point, based on the current pathway. On the other hand, a high electric potential signal is sent to the scanning line (Gaj) when electric current flows in the light emitting element 41, and the transistors 31 to 36 turn off, while the transistors 37 and 42 turn on. A series connection relationship is formed between the transistors 38 and 39 at this point, based on the current pathway.

[0065] Switching of the connection relationship between the transistors 38 and 39 of the driver element 15 is controlled by using the first scanning line (Gaj) and the second scanning line (Gbj) with the example of FIG. 2B. However, the transistors controlled by the second scanning line (Gbj) are all not connected to the signal line (Si). Further, there is a characteristic that whether or not electric current flows in the light emitting element 41 to emit light can be controlled by only the electric potential of the second scanning line (Gbj), irrespective of the electric potential of the first scanning line (Gaj). The amount of time that the light emitting element 41 emits light can therefore be controlled arbitrarily by sending signals independent of the first scanning line (Gaj) to the second

scanning line (Gbj) in the time other than the time of data current write-in.

[0066] This is extremely important for cases in which intermediate gray scale expression is performed by a time gray scale method. This is because sufficient multigray scale display is difficult without a means for stopping light emission during a column scanning period for cases in which a time gray scale method is applied to an AMOLED having a polysilicon TFT driver circuit. Further, this is also useful for cases in which intermediate gray scale expression is performed using an analog video signal data current, in application to impulse light emission and the like in order to stop dynamic distortions peculiar to hold type displays (refer to Kurita, T., Proc. AM-LCD 2000, pp. 1-4 (2000), for example, regarding dynamic distortions peculiar to hold type displays).

[0067] Further, the example of FIG. 2B is one in which storage of the video signal data current is performed very accurately. With the example of FIG. 2A, the transistor 25 is directly connected to the power source line (Vi) during data current write-in, while the transistor 26 is connected through the transistor 23. An inaccuracy equal to the amount of voltage drop over the transistor 23 therefore occurs during write-in of the data current. On the other hand, the transistor 38 is connected to the power source line (Vi) through the transistor 35, and the transistor 39 is connected to the power source line (Vi) through the transistor 36 with the example of FIG. 2B. If the voltage drops caused by the transistor 35 and the transistor 36 respectively are of the same order, then storage of the video signal data current can be performed very accurately.

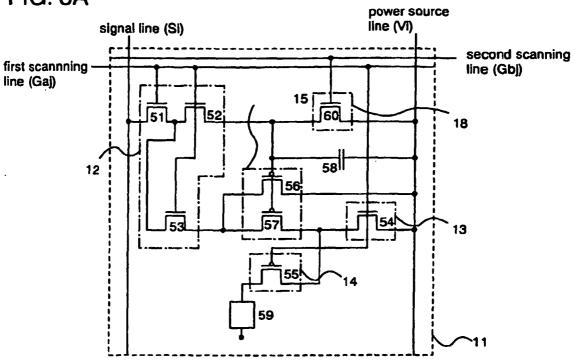

A third example is explained next using FIG. 3A. [0069] The pixel 11 disposed in the j-th row and the ith column is shown in FIG. 3A. The pixel 11 has a signal line (Si), a power source line (Vi), a first scanning line (Gaj), a second scanning line (Gbj), transistors 51 to 57, and 60, a capacitor element 58, and a light emitting element 59. The pixel 11 shown in FIG. 3A is the pixel 11 shown in FIG. 1B, but shown specifically by transistors. The transistors 51 to 53, which are n-channel, correspond to the first switch 12. The transistor 54, which is n-channel, corresponds to the second switch 13, and the transistor 55, which is p-channel, corresponds to the third switch 14. The transistors 56 and 57, which are p-channel, correspond to the driver element 15. The transistor 60, which is n-channel, corresponds to the fourth switch 18.

**[0070]** Each gate electrode of the transistors 51 to 55 is connected to the first scanning line (Gaj). A gate electrode of the transistor 60 is connected to the second scanning line (Gbj). The capacitor element 58 performs a role in storing the voltage between a gate and a source of the transistor 56. Note that it is not always necessary to form the capacitor element 58 for cases in which the gate capacitances of the transistors 56 and 57 are large, for cases in which the parasitic capacitance of a node is high, and the like.

[0071] A high electric potential signal is sent to the first scanning line (Gaj) in the pixel 11 shown in FIG. 3A during write-in of a video signal data current, and the transistors 51 to 54 turn on, while the transistor 55 turns off. A parallel connection relationship between the transistors 56 and 57 is formed at this point, based on the current pathway. On the other hand, a low electric potential signal is sent to the scanning line (Gaj) when electric current flows in the light emitting element 59, and the transistors 51 to 54 turn off, while the transistor 55 turns on. A series connection relationship is formed between the transistors 56 and 57 at this point, based on the current pathway.

**[0072]** Note that a low electric potential signal is sent to the second scanning line (Gbj) during the aforementioned period, turning the transistor 60 off.

[0073] The amount of time that the light emitting element 59 emits light can be arbitrarily controlled by the signal sent to the second scanning line (Gbj), similar to the case of the example of FIG. 2B. Namely, if a high electric potential signal is sent to the second scanning line (Gbj) during light emission by the light emitting element 59, and the transistor 60 turns on, the transistor 56 then turns off and the light emitting element 59 stops emitting light. However, once the light emitting element 59 is made to stop emitting light, the light emitting element 59 will then not emit light unless a video signal data current is again written in, which differs from the example of FIG. 2B.

**[0074]** The features of the fact that the amount of time that the light emitting element 59 emits light can be arbitrarily controlled in the pixel shown by FIG. 3A is similar to the example of FIG. 2B. That is, it becomes possible to perform intermediate gray scale expression by a time gray scale method. Further, this is also useful for cases in which intermediate gray scale expression is performed using an analog video signal data current, in application to impulse light emission and the like in order to stop dynamic distortions peculiar to hold type displays.

**[0075]** The transistors 51 to 54 of the first switch 12 and the second switch 13, and the transistor 60 of the fourth switch 18 are n-channel, and the transistor 55 of the third switch 14 is p-channel in the pixel 11 shown by FIG. 3A. This differs from the examples of FIGs. 2A and 2B. This is only an example, however, and the channel types of the transistors in the switches are not particularly limited to these types.

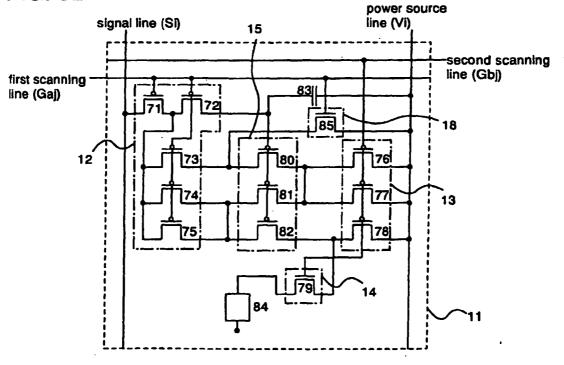

[0076] A fourth example is explained next using FIG. 3B.

[0077] The pixel 11 disposed in the j-th row and the i-th column is shown in FIG. 3B. The pixel 11 has a signal line (Si), a power source line (Vi), a first scanning line (Gaj), a second scanning line (Gbj), transistors 71 to 82, and 85, a capacitor element 83, and a light emitting element 84. The pixel 11 shown in FIG. 3B is the pixel 11 shown in FIG. 1B, but shown specifically by transistors. The transistors 71 to 75, which are p-channel, correspond to the first switch 12. The transistors 76 to 78, which are p-channel, correspond to the second switch

13, and the transistor 79, which is n-channel, corresponds to the third switch 14. The transistors 80 to 82, which are p-channel, correspond to the driver element 15. The transistor 85, which is n-channel, corresponds to the fourth switch 18.

[0078] Each gate electrode of the transistors 71 to 75, and 85 is connected to the first scanning line (Gaj). A gate electrode of the transistors 76 to 79 is connected to the second scanning line (Gbj). The capacitor element 83 performs a role in storing the voltage between a gate and a source of the transistor 80. Note that it is not always necessary to form the capacitor element 83 for cases in which the gate capacitances of the transistors 80 to 82 are large, for cases in which the parasitic capacitance of a node is high, and the like.

**[0079]** A low electric potential signal is sent to the first scanning line (Gaj) and the second scanning line (Gbj) in the pixel 11 shown in FIG. 3B during write-in of a video signal data current, and the transistors 71 to 78 turn on, while the transistors 79 and 85 turn off. A parallel connection relationship between the transistors 80 to 82 is formed at this point, based on the current pathway. On the other hand, a high electric potential signal is sent to the scanning line (Gaj) when electric current flows in the light emitting element 84, and the transistors 71 to 78 turn off, while the transistors 79 and 85 turn on. A series connection relationship is formed between the transistors 80 to 82 at this point, based on the current pathway.

[0080] Switching of the transistors 80 to 82 of the driver element 15 is controlled by using the first scanning line (Gaj) and the second scanning line (Gbj) in the example of FIG. 3B. However, the transistors controlled by the second scanning line (Gbj) are not connected to the signal line (Si). Further, there is a characteristic that whether or not electric current is made to flow in the light emitting element 84 to emit light does not have relation to the electric potential of the first scanning line (Gaj), and can be controlled by only the electric potential of the second scanning line (Gbj). The amount of time during which the light emitting element 84 emits light can therefore be arbitrarily controlled by sending signals independent of the first scanning line (Gaj) to the second scanning line (Gbj) in the time other than the time of data current write-in. This is similar to the example of FIG. 2B.

**[0081]** The following advantages therefore can be obtained since the amount of time that the light emitting element 84 emits light can also be arbitrarily controlled in the pixel 11 shown in FIG. 3B. That is, first, it becomes possible to perform intermediate gray scale expression by using a time gray scale method. Further, this is also useful for cases in which intermediate gray scale expression is performed using an analog video signal data current, in application to impulse light emission and the like in order to stop dynamic distortions peculiar to hold type displays.

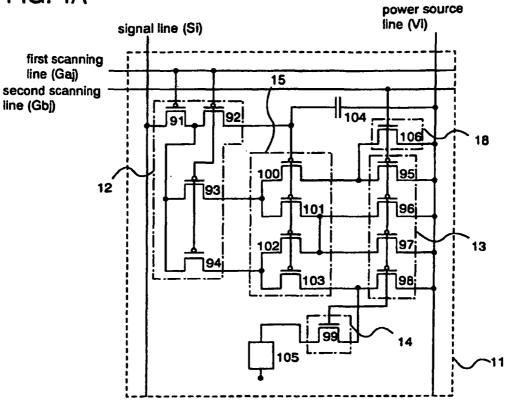

[0082] A fifth example is explained next using FIG. 4A. [0083] The pixel 11 disposed in the j-th row and the i-th column is shown in FIG. 4A. The pixel 11 has a signal

35

20

25

40

50

line (Si), a power source line (Vi), a first scanning line (Gaj), a second scanning line (Gbj), transistors 91 to 103, and 106, a capacitor element 104, and a light emitting element 105. The pixel 11 shown in FIG. 4A is the pixel 11 shown in FIG. 1B, but shown specifically by transistors. The transistors 91 to 94, which are p-channel, correspond to the first switch 12. The transistors 95 to 98 which are p-channel, correspond to the second switch 13, and the transistor 99, which is n-channel, corresponds to the third switch 14. The transistors 100 to 103, which are p-channel, correspond to the driver element 15. The transistor 106, which is n-channel, corresponds to the fourth switch 18.

**[0084]** Each gate electrode of the transistors 91 to 94 is connected to the first scanning line (Gaj). A gate electrode of the transistors 95 to 99 and 106 is connected to the second scanning line (Gbj). The capacitor element 104 performs a role in storing the voltage between a gate and a source of the transistor 100. Note that it is not always necessary to form the capacitor element 104 for cases in which the gate capacitances of the transistors 100 to 103 are large, for cases in which the parasitic capacitance of a node is high, and the like.

[0085] A low electric potential signal is sent to the first

scanning line (Gaj) and the second scanning line (Gbj) in the pixel 11 shown in FIG. 4A during write-in of a video signal data current, and the transistors 91 to 98 turn on, while the transistors 99 and 106 turn off. A parallel connection relationship between the transistors 100 to 103 is formed at this point, based on the current pathway. On the other hand, a high electric potential signal is sent to the scanning line (Gaj) when electric current flows in the light emitting element 105, and the transistors 91 to 98 turn off, while the transistors 99 and 106 turn on. A series connection relationship is formed between the transistors 100 to 103 at this point, based on the current pathway. [0086] Switching of the transistors 100 to 103 of the driver element 15 is controlled by using the first scanning line (Gaj) and the second scanning line (Gbj) in the example of FIG. 4A. However, the transistors controlled by the second scanning line (Gbj) are not connected to the signal line (Si). Further, there is a characteristic that whether or not electric current is made to flow in the light emitting element 105 to emit light does not have relation to the electric potential of the first scanning line (Gaj), and can be controlled by only the electric potential of the second scanning line (Gbj). The amount of time during which the light emitting element 105 emits light can therefore be controlled by sending signals independent of the first scanning line (Gaj) to the second scanning line (Gbj) in the time other than the time of data current write-in. This is similar to the example of FIG. 2B.

[0087] The following advantages can be obtained since the amount of time that the light emitting element 105 emits light can also be controlled in the pixel shown by FIG. 4A. That is, first, it becomes possible to perform intermediate gray scale expression by using a time gray scale method. Further, this is also useful for cases in

which intermediate gray scale expression is performed using an analog video signal data current, in application to impulse light emission and the like in order to stop dynamic distortions peculiar to hold type displays.

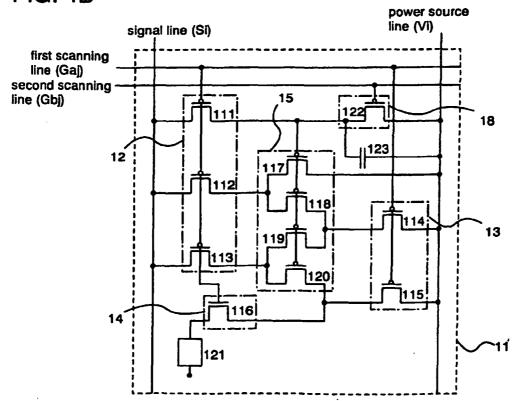

[0088] A sixth example is explained next using FIG. 4B. [0089] The pixel 11 disposed in the j-th row and the ith column is shown in FIG. 4B. The pixel 11 has a signal line (Si), a power source line (Vi), a first scanning line (Gaj), a second scanning line (Gbj), transistors 111 to 120, and 122, a capacitor element 123, and a light emitting element 121. The pixel 11 shown in FIG. 4B is the pixel 11 shown in FIG. 1B, but shown specifically by transistors. The transistors 111 to 113, which are p-channel, correspond to the first switch 12. The transistors 114 and 115, which are p-channel, correspond to the second switch 13, and the transistor 116, which is n-channel, corresponds to the third switch 14. The transistors 117 to 120, which are p-channel, correspond to the driver element 15. The transistor 122, which is p-channel, corresponds to the fourth switch 18.

[0090] Each gate electrode of the transistors 111 to 116 is connected to the first scanning line (Gaj). A gate electrode of the transistor 122 is connected to the second scanning line (Gbj). The capacitor element 123 performs a role in storing the voltage between a gate and a source of the transistor 117. Note that it is not always necessary to form the capacitor element 123 for cases in which the gate capacitances of the transistors 117 to 120 are large, for cases in which the parasitic capacitance of a node is high, and the like.

[0091] A high electric potential signal is sent to the first scanning line (Gaj) in the pixel 11 shown in FIG. 4B during write-in of a video signal data current, and the transistors 111 to 115 turn on, while the transistor 116 turns off. A parallel connection relationship between the transistors 117 to 120 is formed at this point, based on the current pathway. On the other hand, a low electric potential signal is sent to the first scanning line (Gaj) when electric current flows in the light emitting element 121, and the transistors 111 to 115 turn off, while the transistor 116 turns on. A series connection relationship is formed between the transistors 117 to 120 at this point, based on the current pathway.

**[0092]** Note that a low electric potential signal is sent to the second scanning line (Gbj) during the aforementioned period, turning the transistor 122 off.

[0093] The amount of time that the light emitting element 121 emits light can be arbitrarily controlled by the signal sent to the second scanning line (Gbj) in the pixel 11 shown in FIG. 4B, similar to the case of the example of FIG. 2B. Namely, if a high electric potential signal is sent to the second scanning line (Gbj) during light emission by the light emitting element 121, and the transistor 122 turns on, the transistor 117 then turns off and the light emitting element 121 stops emitting light. However, once the light emitting element 121 is made to stop emitting light, the light emitting element 121 will then not emit light unless a video signal data current is again written

25

in, which differs from the example of FIG. 2B.

**[0094]** The features of the fact that the amount of time that the light emitting element 59 emits light can be arbitrarily controlled in the pixel 11 shown by FIG. 4B is similar to the example of FIG. 2B. That is, it becomes possible to perform intermediate gray scale expression by a time gray scale method. Further, this is also useful for cases in which intermediate gray scale expression is performed using an analog video signal data current, in application to impulse light emission and the like in order to stop dynamic distortions peculiar to hold type displays.

**[0095]** Six types of the pixel 11, each having a different structure, have been explained using FIGs. 2A to 4B as examples of the pixel 11 of the display device and the light emitting device of the present invention. Note that the pixel structure of the display device and the light emitting device of the present invention is not limited to these six types.

#### [Embodiment Mode 2]

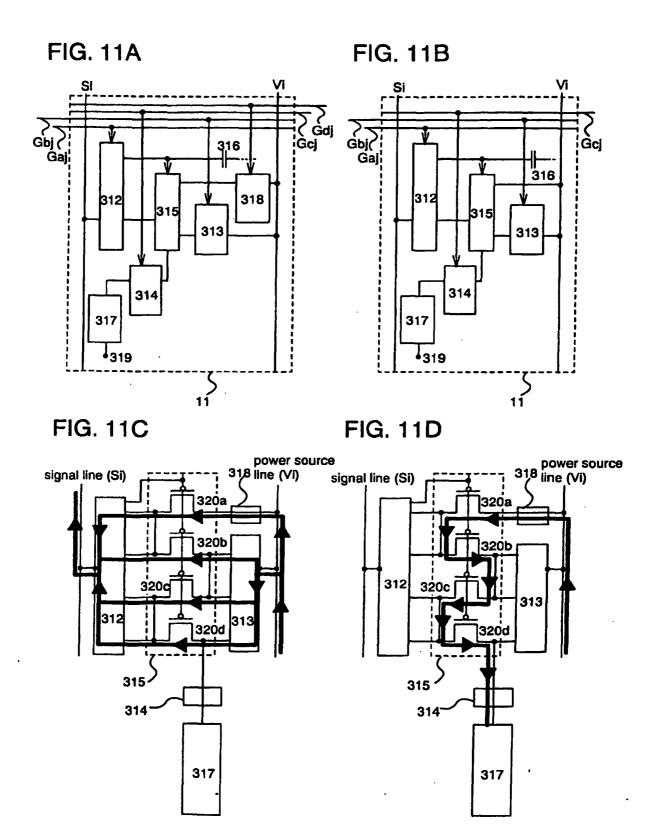

**[0096]** An outline of the pixel of the display device and the led of the present invention has been discussed above using FIGs. 2A to 4B. A specific example of a pixel of the display device and the light emitting device of the present invention that differs from that of Embodiment Mode 1 is explained in Embodiment Mode 2 by using FIGs. 12A to 16A. Examples are given for cases in which the number of transistors n that structure a driver element 315 is three in FIGs. 12A to 15D. Examples in which n is equal to 2 is given in FIG. 16.

**[0097]** A first example is explained by using FIGs. 12A to 12E.

[0098] The pixel 11 of the j-th row and the i-th column is shown in FIG. 12A. The pixel 11 has a signal line (Si), a power source line (Vi), a first scanning line (Gaj), a second scanning line (Gbj), a driver element 315, a first switch 312, a second switch 313, a third switch 314, a fourth switch 318, a capacitor element 316, and a light emitting element 317. The pixel 11 shown in FIG. 12B is an example of the pixel 11 of FIG. 12A shown specifically by transistors.

[0099] A correspondence relationship between FIG. 12A and FIG. 12B is given. N-channel transistors 371 to 375 correspond to the first switch 312. P-channel transistors 376 to 378 correspond to the second switch 313, an n-channel transistor 379 corresponds to the third switch 314, and a p-type transistor 385 corresponds to the fourth switch 318. P-type transistors 380 to 382 correspond to the driver element 315. A capacitor element 383 corresponds to the capacitor element 316, and a light emitting element 384 corresponds to the light emitting element 317.

**[0100]** Each gate electrode of the transistors 371 to 375 is connected to the first scanning line (Gaj). The capacitor element 383 performs a role in storing the voltage between a gate and a source of the transistor 380. Note that the capacitor element 383 may not be specifically

formed for cases in which the gate capacitances of the transistors 380 to 382 are large, for cases in which the parasitic capacitance of a node is high, and the like.

[0101] A high electric potential signal is sent to the first scanning line (Gaj) and a low electric potential signal is sent to the second scanning line (Gbj) in the pixel 11 shown in FIG. 12B during write-in of a video signal data current, and the transistors 371 to 378 turn on, while the transistors 379 and 385 turn off. A parallel connection relationship between the transistors 380 to 382 is formed at this point, based on the current pathway. On the other hand, a low electric potential signal is sent to the first scanning line (Gaj) and a high electric potential signal is sent to the second scanning line (Gbj) when electric current flows in the light emitting element 384, and the transistors 371 to 378 turn off, while the transistors 379 and 385 turn on. A series connection relationship is formed between the transistors 380 and 382 at this point, based on the current pathway.

[0102] FIG. 12A conceptually includes FIG. 12B, but the two are not identical. For example, the first switch 312 may adopt a structure with transistors 331 to 334 of FIG. 12C, instead of the structure with the transistors 371 to 375 of FIG. 12B. Further, the first switch 312 may adopt a structure with transistors 335 to 339 of FIG. 12D, or a structure with transistors 341 to 344 of FIG. 12E. Note that, whichever of the structures of FIGs. 12B to 12E is specifically adopted, for the first switch 312 of FIG. 12A, they can be said to be identical in practice. Therefore block reference symbols like those of FIG. 12A are mainly used in the examples below.

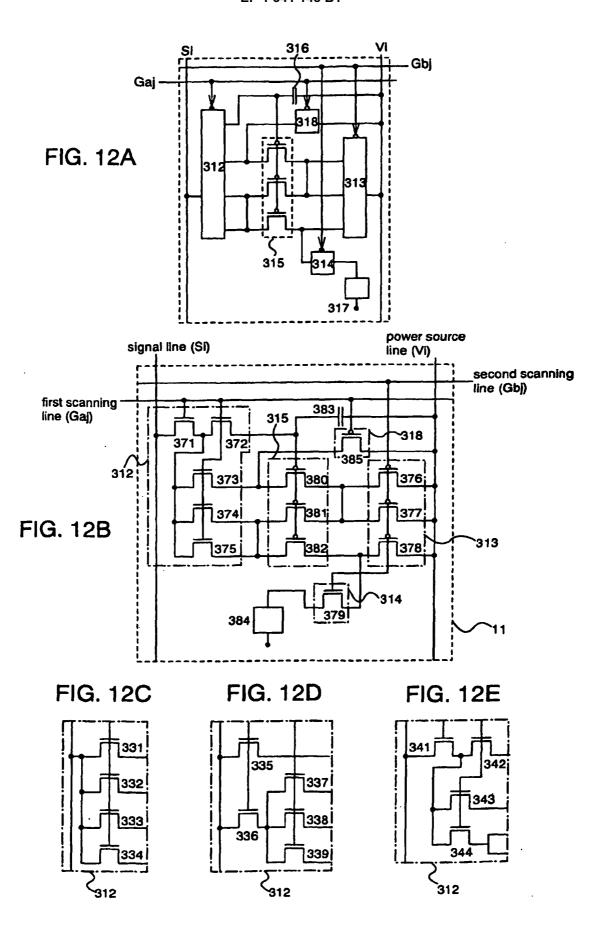

**[0103]** A second example is FIGs. 13A and 14C. Except for the method of connecting the three transistors that structure the driver element 315, these are the same as FIG. 12A.

**[0104]** For example, signals sent to the first scanning line (Gaj) and the second scanning line (Gbj) in pixel circuits of FIGs. 13A and 14C are similar to those of FIGs. 12A to 12E. A high electric potential signal is sent to the first scanning line (Gaj) and a low electric potential signal is sent to the second scanning line (Gbj) during write-in of a video signal data current, and the first switch 312 and the second switch 313 turn on, while the third switch 314 and the fourth switch 318 turn off. A low electric potential signal is sent to the first scanning line (Gaj) and a high electric potential signal is sent to the second scanning line (Gbj) when electric current flows in the light emitting element 317, and the first switch 312 and the second switch 313 turn off, while the third switch 314 and the fourth switch 318 turn on.

**[0105]** FIG. 13A and FIG. 14C differ from FIG. 12A in the method used for connecting the three transistors that structure the driver element 315. FIG. 13A, FIG. 14C, and FIG. 12A can be expected to each possess identical performance provided that the three transistors have source drain symmetry (all the time in terms of electrical characteristics). However, if there is no source drain symmetry (all the time in terms of electrical characteristics),

20

then the performance of FIG. 13A, FIG. 14C, and FIG. 12A will vary slightly. In this case, there is no substitution of the source and the drain (high electric potential side terminal and low electric potential side terminal) in any of the three transistors that structure the driver element 315, both in a parallel connection and a serial connection, and FIG. 14C is the most preferred from in terms of circuit performance. On the other hand, however, FIG. 13A and FIG. 12A, which have the possibility of a slight inferiority in circuit performance, are superior to FIG. 14C in their simplicity when laying out in small pixels.

**[0106]** A third example shown in FIG. 13B differs from FIG. 13A only in the connection position of the capacitor element 316.

[0107] For example, signals sent to the first scanning line (Gaj) and the second scanning line (Gbj) are similar to those of FIGs. 13A. A high electric potential signal is sent to the first scanning line (Gaj) and a low electric potential signal is sent to the second scanning line (Gbj) during write-in of a video signal data current, and the first switch 312 and the second switch 313 turn on, while the third switch 314 and the fourth switch 318 turn off. A low electric potential signal is sent to the first scanning line (Gaj) and a high electric potential signal is sent to the second scanning line (Gbj) when electric current flows in the light emitting element 317, and the first switch 312 and the second switch 313 turn off, while the third switch 314 and the fourth switch 318 turn on.

**[0108]** FIG. 13B also differs from FIG. 13A in the position at which the capacitor element 316 is connected. Firstly, the capacitor element 316 stores the voltage between the gate and the source of the transistor structuring the driver element 315. More precisely, the voltage between the gate and the source of the transistor on the side closest to the source, among the three transistors structuring the driver element 315, is stored. From this viewpoint, a circuit of FIG. 13B can be said to be more unfailing than that of FIG. 13A.

**[0109]** Note that the second switch 313 turns on during write-in of the video signal data current in the circuit of FIG. 13A as well, and that the third switch 314 turns on when electric current flows in the driver element 317. As a result, in FIG. 13A as well, the voltage between the gate and the source of the transistors that structure the driver element 315 during write-in of the video signal data current is recreated when electric current flows in the light emitting element 317. That is, the circuit of FIG. 13A and the circuit of FIG. 13B are the same in that they store the gate-source voltage of the transistors which structure the driver element 315.

**[0110]** From the viewpoint of simplicity in the case of laying out in small pixels, FIG. 13A is generally superior to FIG. 13B.

**[0111]** A fourth example is FIG. 13C, FIG. 13D, FIG. 14A, and FIG. 14B. The method for controlling on/off of the first switch, the second switch, the third switch, and the fourth switch differs from that of FIG. 13A.

[0112] First, the circuit of FIG. 13C uses four scanning

lines, a first scanning line (Gaj), a second scanning line (Gbj), a third scanning line (Gcj), and a fourth scanning line (Gdj), in controlling on/off of the first switch, the second switch, the third switch, and the fourth switch.

[0113] A high electric potential signal is sent to the first scanning line (Gaj) and the fourth scanning line (Gdj) and a low electric potential signal is sent to the second scanning line (Gbj) and the third scanning line (Gcj) during write-in of a video signal data current, and the first switch 312 and the second switch 313 turn on, while the third switch 314 and the fourth switch 318 turn off. A low electric potential signal is sent to the first scanning line (Gaj) and the fourth scanning line (Gdj) and a high electric potential signal is sent to the second scanning line (Gbj) and the third scanning line (Gcj) when electric current flows in the light emitting element 317, and the first switch 312 and the second switch 313 turn off, while the third switch 314 and the fourth switch 318 turn on.

[0114] The first scanning line (Gaj) and the fourth scanning line (Gdj) are assembled into one line, and the second scanning line (Gbj) and the third scanning line (Gcj) are assembled into one line in the circuit of FIG. 13A, but each is a separate scanning line with the circuit of FIG. 13C. This is effective in attaining stable scanning operations. Conversely, the number of scanning lines increases and therefore it is difficult to perform layout in small pixels.

**[0115]** The circuit of FIG. 13D simultaneously controls on/off of the first switch, the second switch, the third switch, and the fourth switch by using only the first scanning line (Gaj).

[0116] A high electric potential signal is sent to the first scanning line (Gaj) during write-in of a video signal data current, and the first switch 312 and the second switch 313 turn on, while the third switch 314 and the fourth switch 318 turn off. A low electric potential signal is sent to the first scanning line (Gaj) when electric current flows in the light emitting element 317, and the first switch 312 and the second switch 313 turn off, while the third switch 314 and the fourth switch 318 turn on.

[0117] While two scanning lines, the first scanning line (Gaj) and the second scanning line (Gbj) are used, in the circuit of FIG. 13A, the two are assembled into one scanning line in the circuit of FIG. 13D. There is an effect in that layout becomes easier in small pixels by the amount that the number of scanning lines is reduced. However, there are weaknesses with only one scanning line. For example, the amount of time that electric current flows in the light emitting element 317 cannot be controlled by devising a scheme for the scanning timing of two scanning lines.

**[0118]** The circuit of FIG. 14A is the same as the circuit of FIG. 13A in that control for turning the first switch, the second switch, the third switch, and the fourth switch on and off is simultaneously performed by the first scanning line (Gaj) and the second scanning line (Gbj). However, the combination of switches for controlling whether each scanning line turns on or off differs from the circuit of FIG.

45

13A. The first scanning line (Gaj) controls the first switch and the second switch with the circuit of FIG. 14A, while the second scanning line (Gbj) controls the third switch and the fourth switch.

**[0119]** A high electric potential signal is sent to the first scanning line (Gaj) and a low electric potential signal is sent to the second scanning line (Gbj) during write-in of a video signal data current, and the first switch 312 and the second switch 313 turn on, while the third switch 314 and the fourth switch 318 turn off. A low electric potential signal is sent to the first scanning line (Gaj) and a high electric potential signal is sent to the second scanning line (Gbj) when electric current flows in the light emitting element 317, and the first switch 312 and the second switch 313 turn off, while the third switch 314 and the fourth switch 318 turn on.

[0120] The circuit of FIG. 14A is one in which the switch that turns on during write-in of a video signal data current, and the switch that turns on when electric current flows in the light emitting element 317 are controlled to turn on and off by different scanning lines. This circuit is therefore superior from the standpoint of stable operation. However, while the circuit of FIG. 13A uses p-channel switches in the second switch 313 and the fourth switch 318, n-channel switches are used by the circuit of FIG. 14A. It is therefore necessary that high electric potential signals of the first scanning line (Gaj) and the second scanning line (Gbj) in the circuit of FIG. 14A be higher than those used for the circuit of FIG. 13A.

**[0121]** The circuit of FIG. 14B divides the first switch 312 of FIG. 14A. That is, a portion for storing and releasing the gate voltage of the transistor that structures the driver element within the first switch 312 of FIG. 14A is divided out as a switch 319. The switch 319 can therefore be controlled to turn on and off independently from the first switch 312 by using the third scanning line (Gcj).

[0122] A high electric potential signal is sent to the first scanning line (Gaj) and the third scanning line (Gcj) and a low electric potential signal is sent to the second scanning line (Gbj) during write-in of a video signal data current, and the first switch 312 and the second switches 313 and 319 turn on, while the third switch 314 and the fourth switch 318 turn off. A low electric potential signal is sent to the first scanning line (Gaj) and the third scanning line (Gcj) and a high electric potential signal is sent to the second scanning line (Gbj) when electric current flows in the light emitting element 317, and the first switch 312 and the second switches 313 and 319 turn off, while the third switch 314 and the fourth switch 318 turn on.

**[0123]** The switch 319 can be turned off earlier than the first switch 312 with the circuit of FIG. 14B when writing in the video signal data current. It is therefore possible to stabilize operation. On the other hand, the number of scanning lines is increased, and therefore layout in small pixels becomes difficult.

**[0124]** The three transistors that structure the driver element in FIG. 15A are n-channel in FIG. 15A which corresponds to a fifth example. This point differs from

FIG. 13A.

[0125] Signals sent to the first scanning line (Gaj) and the second scanning line (Gbj) are similar to those of FIGs. 13A. A high electric potential signal is sent to the first scanning line (Gaj) and a low electric potential signal is sent to the second scanning line (Gbj) during write-in of a video signal data current, and the first switch 312 and the second switch 313 turn on, while the third switch 314 and the fourth switch 318 turn off. A low electric potential signal is sent to the first scanning line (Gaj) and a high electric potential signal is sent to the second scanning line (Gbj) when electric current flows in the light emitting element 317, and the first switch 312 and the second switch 313 turn off, while the third switch 314 and the fourth switch 318 turn on.

[0126] FIG. 15A also differs from FIG. 13A in the position at which the capacitor element 316 is connected. Firstly, the capacitor element 316 stores the voltage between the gate and the source of the transistor structuring the driver element 315. More precisely, the voltage between the gate and the source of the transistor on the side closest to the source, among the three transistors structuring the driver element 315, is stored. While the three transistors that structure the driver element are pchannel in FIG. 13A, the three transistors are n-channel in FIG. 15A. The position at which the capacitor element 316 is connected therefore differs with that of FIG. 13A. [0127] The three transistors that structure the driver element in FIG. 15A are n-channel, and therefore FIG. 15A is more effective than FIG. 13A for cases in which the ideal transistor type is n-channel rather than p-channel due to manufacturing processes. From the standpoint of simplicity in performing laying out in small pixels, FIG. 13A is generally superior to FIG. 15A.

**[0128]** A sixth example is FIG. 15B and FIG. 15C. The direction toward which electric current flows in the driver element of FIGs. 15B and 15C during write-in of a video signal data current becomes opposite to that of the examples shown up through this point. In the circuits of FIGs. 12A to 14C, the first switch 312 side is low electric potential, and the second switch 313 side is high electric potential during write-in of the video signal data current. In the circuits of FIG. 15B and 15C, however, the first switch 312 side is high electric potential, and the second switch 313 side is low electric potential during write-in of the video signal data current. The power source line (Vi) is a high electric potential power source line, and a power source line (Vbi) is a low electric potential power source line.

50 [0129] Signals sent to the scanning lines in a pixel circuit of FIG. 15B are explained. A low electric potential signal is sent to the first scanning line (Gaj) and a high electric potential signal is sent to the second scanning line (Gbj) during write-in of a video signal data current,

55 and the first switch 312 and the second switch 313 turn on, while the third switch 314 and the fourth switch 318 turn off. A high electric potential signal is sent to the first scanning line (Gaj) and a low electric potential signal is

30

40

sent to the second scanning line (Gbj) when electric current flows in the light emitting element 317, and the first switch 312 and the second switch 313 turn off, while the third switch 314 and the fourth switch 318 turn on.

**[0130]** Signals sent to the scanning lines in a pixel circuit of FIG. 15C are also explained. A high electric potential signal is sent to the first scanning line (Gaj) and a low electric potential signal is sent to the second scanning line (Gbj) during write-in of a video signal data current, and the first switch 312 arid the second switch 313 turn on, while the third switch 314 and the fourth switch 318 turn off. A low electric potential signal is sent to the first scanning line (Gaj) and a high electric potential signal is sent to the second scanning line (Gbj) when electric current flows in the light emitting element 317, and the first switch 312 and the second switch 313 turn off, while the third switch 314 and the fourth switch 318 turn on.

**[0131]** A seventh example is FIG. 15D. The direction toward which electric current flows in the circuit of FIG. 15D is opposite to that of the examples shown up through this point. In the circuits of FIGs. 12A to 14C, the third switch 314 side is low electric potential, and the fourth switch 318 side is high electric potential during write-in of the video signal data current. In the circuit of FIG. 15D, however, the third switch 314 side is high electric potential, and the fourth switch 318 side is low electric potential during write-in of the video signal data current.

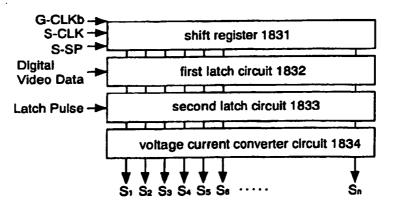

**[0132]** The direction toward which electric current flows in the driver element in FIG. 15D during write-in of the video signal data current is the same direction as that of FIGs. 15B and 15C, and opposite to that of FIGs. 12A to 14C.