# (11) **EP 2 463 849 A1**

(12)

#### **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

13.06.2012 Bulletin 2012/24

(51) Int Cl.:

G09G 3/32 (2006.01)

(21) Application number: 11178920.2

(22) Date of filing: 25.08.2011

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

**Designated Extension States:**

**BA ME**

(30) Priority: 10.12.2010 KR 20100126489

(71) Applicant: Samsung Mobile Display Co., Ltd. Yongin-City, Gyunggi-Do 446-711 (KR)

(72) Inventor: Jeong, Jin-Tae Gyunggi-Do (KR)

(74) Representative: Mounteney, Simon James

Marks & Clerk LLP 90 Long Acre London

WC2E 9RA (GB)

## (54) Pixel, display device including the same, and driving method thereof

(57) A display device includes: a display unit including pixels coupled to scan lines for transmitting scan signals, data lines for transmitting data signals, and light emission control lines for transmitting light emission control signals; a scan driver; a data driver; and a light emission driver. Each pixel includes: an OLED; a driving transistor to transmit a driving current corresponding to a data signal to the OLED; a first transistor to transmit the

data signal to the driving transistor according to a first scan signal; a second transistor to apply a first power source voltage to a first electrode of the driving transistor according to a second scan signal, during an initialization period for initializing a gate electrode voltage of the driving transistor; and a capacitor including a first electrode coupled to a gate electrode of the driving transistor and a second electrode coupled to a first power source supply.

EP 2 463 849 A1

35

40

# BACKGROUND

#### 1. Field

[0001] The present invention relates to a pixel, a display device including the same, and a driving method thereof

#### 2. Description of the Related Art

[0002] Cathode ray tubes (CRTs) have been used to display images. However, CRTs can have the disadvantages of being heavy and large in size. Currently, various flat panel displays are being developed that can reduce the heavy weight and large volume that are drawbacks of CRTs. Examples of flat panel displays include liquid crystal displays (LCDs), field emission displays (FEDs), plasma display panels (PDPs), and organic light emitting diode (OLED) displays.

**[0003]** OLED displays can display images using OLEDs that generate light by recombination of electrons and holes. An OLED display can have a fast response speed, can be driven with low power consumption, and can have the advantages of improved (or excellent) luminous efficiency, luminance, and viewing angle.

**[0004]** Generally, OLED displays can be classified into two types according to the driving method of the OLED display: passive matrix OLEDs (PMOLEDs) and active matrix OLEDs (AMOLEDs).

**[0005]** Of the two types, the active matrix OLED display in which unit pixels are selectively lit is primarily used because of its good resolution, contrast, and operation speed.

[0006] One pixel of an active matrix OLED display may include an OLED, a driving transistor for controlling an amount of current supplied to the OLED, and a switching transistor for transmitting a data signal to the driving transistor to control an amount of light emitted by the OLED. [0007] Recently, research has been underway on a compensation circuit to compensate for a threshold voltage variation (or deviation) of the driving transistor included in the pixel of the active matrix OLED display. However, when the compensation circuit is used to display an image at a desired luminance, the response speed of the pixel varies according to an increase/decrease in a data voltage applied to the driving transistor, due to hysteresis, such that it is difficult to correctly display gray levels. For example, a delay in response speed may be generated when driving the OLED display to express a luminance from black to white, and this problem may cause sticking when scrolling text on a screen.

**[0008]** The above information disclosed in this Background section is only for enhancement of understanding of the background of the invention and therefore it may contain information that does not form the prior art that is already known in this country to a person of ordinary

skill in the art.

#### **SUMMARY**

**[0009]** The present invention sets out to provide a pixel, a display device including the same, and a driving method thereof to reduce (or remove) a delay in response speed and reduce sticking while driving a display.

**[0010]** The present invention also sets out to provide a pixel circuit that concurrently (e.g., simultaneously) compensates for a threshold voltage variation of a driving transistor while addressing (or solving) the problems of delayed response speed caused by hysteresis and reducing sticking on a screen.

**[0011]** Also, The present invention sets out to provide a high quality display device producing high image quality that is capable of compensating for a threshold voltage variation (or deviation) of a driving transistor; correctly expressing gray levels by reducing (or solving) a delay in a response speed, for example, in a case of displaying an image according to a data signal having a large luminance variation (or deviation); and a driving method thereof.

**[0012]** Technical aspects of the present invention are not limited to the above, and other aspects (e.g., nonmentioned aspects) will be clearly understood by a person of ordinary skill in the art by way of the following description.

[0013] A display device according to embodiments of the present invention includes: a display unit including a plurality of pixels respectively coupled to a plurality of scan lines for transmitting a plurality of scan signals, a plurality of data lines for transmitting a plurality of data signals, and a plurality of light emission control lines for transmitting a plurality of light emission control signals; a scan driver for transmitting the plurality of scan signals; a data driver for transmitting the plurality of data signals; and a light emission driver for transmitting the plurality of light emission control signals, wherein each pixel of the plurality of pixels includes: an organic light emitting diode (OLED); a driving transistor configured to transmit a driving current corresponding to a data signal from among the plurality of data signals to the OLED; a first transistor configured to transmit the data signal to the driving transistor according to a first scan signal from among the plurality of scan signals; a second transistor configured to apply a first power source voltage to a first electrode of the driving transistor according to a second scan signal from among the plurality of scan signals, during an initialization period for initializing a gate electrode voltage of the driving transistor; and a capacitor including a first electrode coupled to a gate electrode of the driving transistor and a second electrode coupled to a first power source supply.

**[0014]** A voltage difference between the gate electrode voltage and a first electrode voltage of the driving transistor during the initialization period may be a voltage for operating the driving transistor.

**[0015]** The first transistor may be switching-operated according to the first scan signal to transmit the data signal to the first electrode of the driving transistor.

**[0016]** The second scan signal may be transmitted to a previous scan line from among the plurality of scan lines, and the previous scan line may precede the scan line receiving the first scan signal.

**[0017]** The scan driver may be configured to transmit the first scan signal and the second scan signal to the plurality of pixels.

**[0018]** Each pixel of the plurality of pixels may further include: an initialization transistor configured to supply an initialization voltage to the gate electrode of the driving transistor during the initialization period and to initialize the gate electrode voltage of the driving transistor.

**[0019]** The initialization transistor may be switching-operated according to the second scan signal transmitted to a previous scan line from among the plurality of scan lines, and the previous scan line may precede the scan line receiving the first scan signal transmitted to the first transistor.

**[0020]** The initialization period may be a period in which the second scan signal is transmitted to the initialization transistor at a gate-on voltage level.

**[0021]** The initialization period may be before a period in which a threshold voltage of the driving transistor is compensated.

**[0022]** Each pixel of the plurality of pixels may further include: a threshold voltage compensation transistor configured to be switching-operated according to the first scan signal after the initialization period and to diodecouple the driving transistor and compensate a threshold voltage of the driving transistor.

**[0023]** Each pixel of the plurality of pixels may further include: at least one light emission control transistor configured to control light emission of the OLED receiving the driving current according to the data signal.

**[0024]** The at least one light emission control transistor may be configured to be switching-operated according to a light emission control signal from among the plurality of light emission control signals transmitted at a gate-on voltage level, after the first scan signal and the second scan signal are respectively transmitted at the gate-on voltage level to the first transistor and the second transistor.

**[0025]** A pixel according to another embodiment of the present invention includes: an organic light emitting diode (OLED); a driving transistor configured to transmit a driving current to the OLED according to a data signal; a first transistor configured to transmit the data signal to the driving transistor according to a first scan signal; a second transistor configured to apply a first power source voltage to a source electrode of the driving transistor according to a second scan signal during an initialization period for initializing a gate electrode voltage of the driving transistor; and a capacitor including a first electrode coupled to a gate electrode of the driving transistor and a second electrode coupled to a first power source supply.

**[0026]** A voltage difference between the gate electrode voltage and a source electrode voltage of the driving transistor during the initialization period may be a voltage for operating the driving transistor.

[0027] The first transistor may include a gate electrode for receiving the first scan signal, a source electrode for receiving the data signal, and a drain electrode coupled to the source electrode of the driving transistor, and the first transistor may be switching-operated according to the first scan signal and may be configured to transmit the data signal to the source electrode of the driving transistor.

**[0028]** The second scan signal may be transmitted to a second scan line preceding a first scan line receiving the first scan signal.

**[0029]** The pixel may further include: an initialization transistor configured to supply an initialization voltage to the gate electrode of the driving transistor during the initialization period and to initialize the gate electrode voltage of the driving transistor.

**[0030]** The initialization transistor may include: a gate electrode for receiving the second scan signal, a source electrode applied with the initialization voltage, and a drain electrode coupled to the gate electrode of the driving transistor, and the initialization transistor may be configured to be switching-operated according to the second scan signal.

**[0031]** The initialization period may be a period in which the second scan signal is transmitted to the initialization transistor at a gate-on voltage level.

**[0032]** The initialization period may be before a period in which a threshold voltage of the driving transistor is compensated.

**[0033]** The pixel may further include: a threshold voltage compensation transistor configured to be switching-operated according to the first scan signal after the initialization period and to diode-couple the driving transistor and compensate a threshold voltage of the driving transistor.

40 [0034] The pixel may further include: at least one light emission control transistor coupled between the first power source supply and the OLED and including a gate electrode for receiving a light emission control signal for controlling light emission of the OLED receiving the driving current according to the data signal.

**[0035]** The at least one light emission control signal may be transmitted at a gate-on voltage level after the first scan signal and the second scan signal are respectively transmitted at the gate-on voltage level to the first transistor and the second transistor in the pixel.

**[0036]** The at least one light emission control transistor may further include: a source electrode coupled to a drain electrode of the driving transistor, and a drain electrode coupled to an anode of the OLED.

**[0037]** The at least one light emission control transistor may further include: a source electrode coupled to the first power source supply, and a drain electrode coupled to the source electrode of the driving transistor.

25

30

40

[0038] According to another embodiment of the present invention, a method is provided for driving a display device including a plurality of pixels, wherein each pixel of the plurality of pixels includes: an organic light emitting diode (OLED); a driving transistor for transmitting a driving current to the OLED according to a data signal; a first transistor for transmitting the data signal to the driving transistor according to a first scan signal; a second transistor for applying a first power source voltage to the driving transistor according to a second scan signal; and a capacitor coupled between the driving transistor and a first power source supply, the method including: initializing a gate electrode voltage of the driving transistor; compensating for a threshold voltage of the driving transistor and transmitting the data signal to the driving transistor; and providing the driving current to the OLED according to the data signal to produce light emission, wherein the second scan signal is transmitted at a gateon voltage level during the initializing the gate electrode voltage of the driving transistor.

**[0039]** A voltage between a gate electrode and a source electrode of the driving transistor may be a voltage for operating the driving transistor during the initializing the gate electrode voltage of the driving transistor.

**[0040]** The second scan signal may be transmitted to a second scan line preceding a first scan line receiving the first scan signal.

**[0041]** The initializing the gate electrode voltage of the driving transistor may include applying an initialization voltage to a gate electrode of the driving transistor via an initialization transistor configured to be switching-operated according to the second scan signal.

**[0042]** The compensating for the threshold voltage of the driving transistor may include diode-coupling the driving transistor via a threshold voltage compensation transistor configured to be switching-operated according to the first scan signal.

The providing the driving current to the OLED according to the data signal to produce light emission may include controlling the light emission of the OLED via at least one light emission control transistor coupled between the first power source supply and the OLED, and the at least one light emission control transistor may be configured to be switching-operated by a light emission control signal.

**[0043]** The light emission control signal may be transmitted at the gate-on voltage level after the first scan signal and the second scan signal are respectively transmitted at the gate-on voltage level to the first transistor and the second transistor.

**[0044]** According to the pixel and the display device including the same of embodiments of the present invention, the problem of the delay in response speed caused by hysteresis may be reduced (or solved) and the sticking on the screen may be reduced such that a grayscale may be correctly expressed.

**[0045]** Also, according to embodiments of the present invention, a delay in response speed may be concurrently (e.g., simultaneously) reduced (or prevented) when dis-

playing an image according to a data signal having a large luminance variation (or deviation), while concurrently compensating for a threshold voltage variation (or deviation) of a driving transistor such that a high quality display producing high image quality may be realized.

[0046] At least some of the above and other features of the invention are set out in the claims.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

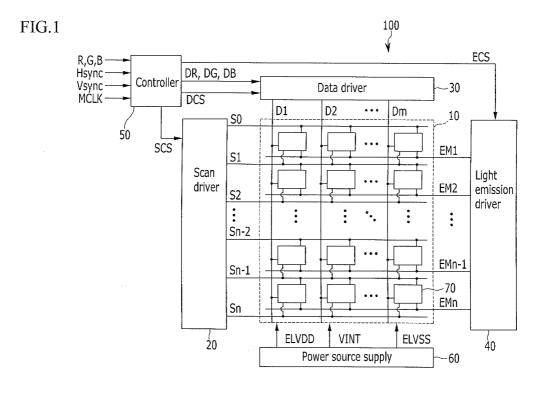

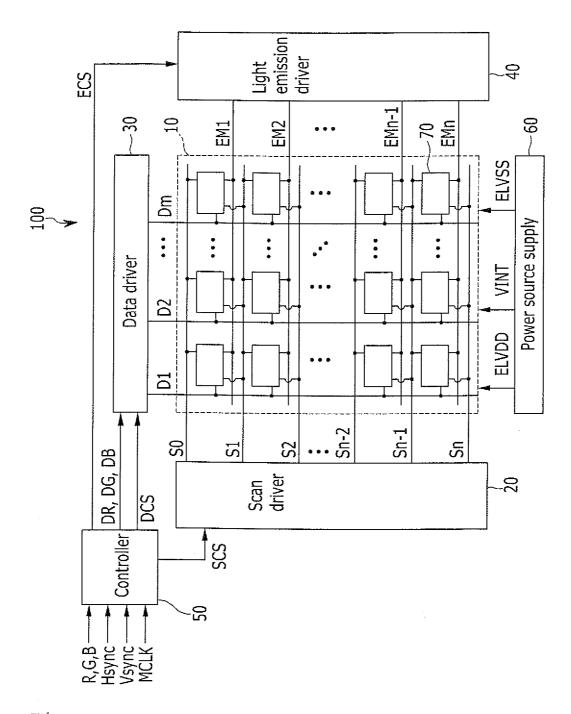

**[0047]** FIG. 1 is a block diagram of a display device according to an embodiment of the present invention.

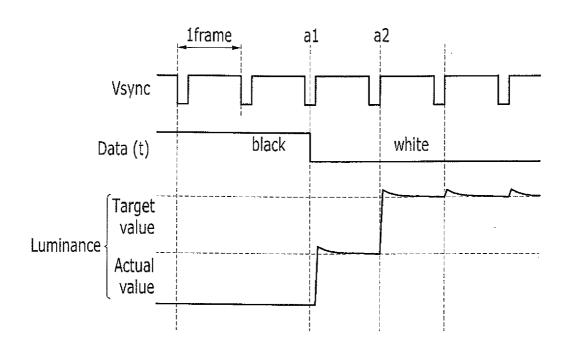

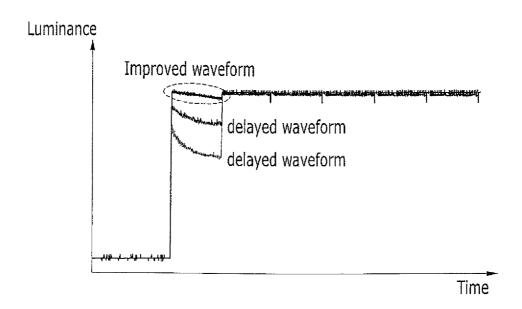

**[0048]** FIG. 2 is a waveform diagram of a delay in response speed due to hysteresis during expression of gray levels in a conventional pixel circuit.

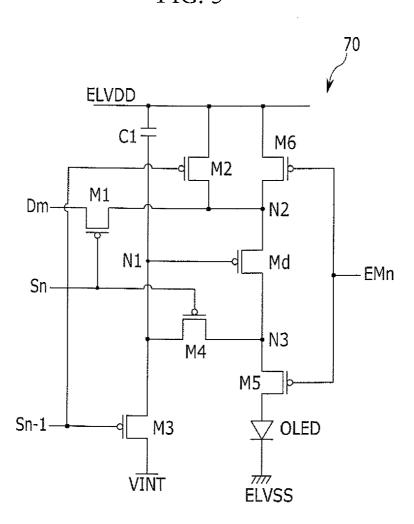

**[0049]** FIG. 3 is a circuit diagram of a pixel circuit of the display device shown in FIG. 1.

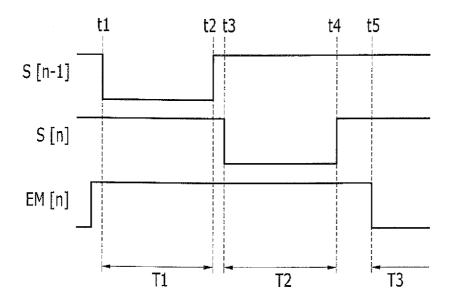

**[0050]** FIG. 4 is a timing diagram showing a driving operation of the pixel circuit shown in FIG. 3.

**[0051]** FIG. 5 is a waveform diagram showing an improved response speed in a display device according to an exemplary embodiment of the present invention.

#### **DETAILED DESCRIPTION OF THE EMBODIMENTS**

[0052] In the following detailed description, only certain embodiments of the present invention have been shown and described, simply by way of illustration. As those skilled in the art would realize, the described embodiments may be modified in various different ways, all without departing from the scope of the present invention. [0053] Further, constituent elements having the same configurations in the embodiments are described in a first embodiment using like reference numerals, and only configurations different from those in the first embodiment will be described in other embodiments.

**[0054]** In addition, some of the parts that are not essential to the description are omitted for clarity, and like reference numerals designate like elements and similar constituent elements throughout the application.

[0055] Throughout this specification and the claims that follow, when it is described that an element is "coupled" to another element, the element may be "directly coupled" to the other element or "electrically coupled" to the other element through a third element. In addition, unless explicitly described to the contrary, the word "comprise" and variations such as "comprises" or "comprising" will be understood to imply the inclusion of the stated elements but not the exclusion of any other elements.

[0056] FIG. 1 is a block diagram of a display device 100 according to an embodiment of the present invention. The display device 100 includes a display unit 10 including a plurality of pixels, a scan driver 20, a data driver 30, a light emission driver 40, a controller 50, and a power source supply unit 60 supplying an external voltage to the display device.

**[0057]** A plurality of pixels are respectively coupled to two scan lines among a plurality of scan lines S0 to Sn

for transmitting scan signals to the display unit 10. In FIG. 1, each pixel is coupled to a scan line that corresponds to a corresponding pixel row, and each pixel is also coupled to the scan line of the previous row thereof. However, embodiments of the present invention are not limited thereto.

**[0058]** Also, each pixel of a plurality of pixels is respectively coupled to one data line among a plurality of data lines D1 to Dm for transmitting data signals to the display unit 10, and one light emission control line among a plurality of light emission control lines EM1 to EMn for transmitting emission control signals to the display unit 10.

**[0059]** In this embodiment, the scan driver 20 generates and transmits two corresponding scan signals to the pixels through a plurality of scan lines S0 to Sn. That is, the scan driver 20 transmits the first scan signal through the scan line corresponding to the pixel row including the pixels, and the second scan signal through the scan line corresponding to the previous pixel row.

**[0060]** By way of example, one pixel 70 among a plurality of pixels included in the nth pixel row is respectively coupled to the scan line Sn corresponding to the corresponding nth pixel row and the scan line Sn-1 corresponding to the previous (n-1)th pixel row.

**[0061]** The pixel 70 receives the first scan signal through the scan line Sn, and concurrently (e.g., simultaneously) receives the second scan signal through the scan line Sn-1.

**[0062]** The data driver 30 transmits a data signal to each pixel through a plurality of data lines D1 to Dm.

**[0063]** The light emission driver 40 generates and transmits a light emission control signal to each pixel through a plurality of light emission control lines EM1 to EMn

[0064] The controller 50 converts (or changes) a plurality of video signals R, G, and B transmitted from an external source into a plurality of image data signals DR, DG, and DB, and transmits them to the data driver 30. Also, the controller 50 receives a vertical synchronization signal Vsync, a horizontal synchronization signal Hsync, and a clock signal MCLK to generate control signals to control the driving of the scan driver 20, the data driver 30, and the light emission driver 40. That is, the controller 50 generates and transmits the scan driving control signal SCS controlling the scan driver 20, the data driving control signal DCS controlling the data driver 30, and the light emitting driving control signal ECS controlling the light emission driver 40.

**[0065]** The display unit 10 includes a plurality of pixels positioned at crossing regions of a plurality of scan lines 50 to Sn, a plurality of data lines D1 to Dm, and a plurality of light emission control lines EM1 to EMn.

**[0066]** The plurality of pixels are supplied with external voltages such as a first power source voltage ELVDD, a second power source voltage ELVSS, and an initialization voltage VINT from the power source supply unit 60. The first power source voltage ELVDD may have a higher voltage level than the second power source voltage

FLVSS.

**[0067]** The display unit 10 includes a plurality of pixels arranged in an approximate matrix format. The plurality of scan lines 50 to Sn extend substantially in a row in a first direction so as to be parallel to each other, and the plurality of data lines extend substantially in a column, in a second direction crossing the first direction, so as to be parallel to each other in the arrangement of the pixels. However, embodiments of the present invention are not limited thereto.

**[0068]** A plurality of pixels respectively emit light having a luminance (e.g., a predetermined luminance), by way of a driving current supplied to an OLED in each pixel, according to a data signal transmitted through a plurality of data lines D1 to Dm.

**[0069]** FIG. 2 is a waveform diagram of a delay in a response speed due to hysteresis during expression of gray levels in a conventional pixel circuit.

**[0070]** In a general (or conventional) pixel circuit for compensating for a threshold voltage of a driving transistor, pixels of the display unit are scanned for one frame. The vertical synchronization signal Vsync is transmitted to the scanned pixels and the scanned pixels receive the data signal Data[t] to display the images.

**[0071]** When the plurality of pixels of the display unit that are displayed with a black image or a white image corresponding to the data signal are driven for a long time, the voltage level applied to the driving transistor in each pixel may be maintained such that hysteresis according thereto is generated. In this case, when displaying the image of a current frame, the gray level may be shifted to the left side or the right side of a TFT characteristic curve by an influence of the gray voltage of the previous frame.

**[0072]** For example, when the pixels are driven with the black image for a long time, the voltage level applied to the driving transistor is an off-bias voltage that is less than an operation reference voltage of the driving transistor. Accordingly, the gray level according to the video signal of the next frame is shifted to the right side of the TFT characteristic curve. In contrast, when the pixels are driven with the white image for a long time, the voltage level applied to the driving transistor is an on-bias voltage that is more than the operation reference voltage of the driving transistor, and thereby the gray level according to the video signal of the next frame is shifted to the left side of the TFT characteristic curve.

**[0073]** Accordingly, the response speeds may be different according to the change in the amount of the luminance between the previous frame and the current frame, due to the hysteresis of the driving transistor of the pixel when displaying the same luminance. These response speeds may vary (e.g., deteriorate) according to the application time of the off-bias voltage or the onbias voltage applied to the driving transistor.

**[0074]** Accordingly, improvement of the pixel circuit to concurrently (e.g., simultaneously) address (or solve) the response speed problem due to hysteresis while com-

40

pensating for a threshold voltage variation (or deviation) of a transistor in the pixel is needed.

[0075] In the waveform diagram of FIG. 2, a pixel that is displayed with a black luminance for a long time according to a black data signal Data[t] receives a white data signal emitting light with a white luminance, at the time a1. As shown in FIG. 2, the pixel does not immediately emit light having luminance target values corresponding to the white data signal at the time a1, when the white data signal is first transmitted, but emits light having the luminance target values at the time a2 after one frame has passed.

**[0076]** When driving the pixel to display images from black to white, in one frame the light may not reach (or may not be increased to) the target value of the white luminance, and may only arrive at a middle luminance. Therefore, the response speed may be delayed compared with the case where the pixel is driven to display the image from white to white. The delay in the response speed due to this hysteresis is manifest (or represented) as sticking during text scrolling of the display screen.

**[0077]** A pixel circuit structure and a driving method according to an embodiment of the present invention address (or solve) the problem of the delay in response speed caused by hysteresis.

**[0078]** FIG. 3 is a circuit diagram showing a circuit structure of a pixel 70 of the display device 100 shown in FIG. 1.

**[0079]** Each pixel in this embodiment of the present invention is coupled to a first scan line and a second scan line. The second scan line applies an initialization voltage VINT to a driving transistor Md in the pixel during an initialization period and transmits a second scan signal controlling the driving transistor Md to maintain it with the operation voltage (on-bias voltage). The first scan line transmits a first scan signal to activate the pixel to transmit the data signal.

**[0080]** The pixel 70 shown in FIG. 3 is respectively coupled to the nth scan line Sn and the (n-1)th scan line Sn-1 among a plurality of pixels included in the display unit 10 of the display device 100 of FIG. 1. Also, the pixel 70 is coupled to the mth data line Dm and the nth light emission control line EMn.

[0081] The pixel 70 shown in FIG. 3 includes an OLED; a driving transistor Md coupled to an anode of the OLED; a first transistor M1 coupled to the source electrode of the driving transistor Md; a second transistor M2, which has one electrode coupled to a node N2 that is coupled to the driving transistor Md and the first transistor M1, and another electrode that is coupled to the first power source voltage ELVDD; and a capacitor C1 between the driving transistor Md and the first power source voltage ELVDD.

**[0082]** The pixel 70 further includes an initialization transistor M3 for transmitting the initialization voltage VINT during the initialization period.

**[0083]** The pixel 70 further includes a threshold voltage compensation transistor M4 diode-coupling the driving

transistor Md to compensate for the threshold voltage of the driving transistor Md.

[0084] Also, the pixel 70 further includes light emission control transistor coupled to the anode of the OLED and controlling light emission according to the driving current of the OLED. The light emission control transistors included in the pixel 70 of FIG. 3 include a first light emission control transistor M5 coupled between the anode of the OLED and the driving transistor Md, and a second light emission control transistor M6 coupled between the driving transistor Md and the first power source voltage ELVDD.

**[0085]** The OLED of the pixel 70 has an anode and a cathode, and emits light as a result of the driving current corresponding to a corresponding data signal. The driving current corresponding to the data signal is compensated for, so as not to be affected by the variations in threshold voltage of the driving transistor included in each of the pixels of the display unit 10.

**[0086]** The driving transistor Md includes a source electrode coupled to the second node N2 to which the first power source voltage ELVDD is coupled, a drain electrode coupled to a third node N3, and a gate electrode coupled to the first node N1. The driving transistor Md receives the data signal through the first transistor M1 coupled to the second node N2.

**[0087]** The driving transistor Md transmits the driving current corresponding to the voltage difference between its source electrode and its gate electrode to the OLED for light emission.

[0088] The first transistor M1 includes a source electrode coupled to the data line Dm and transmitting the data signal, a drain electrode coupled to the second node N2, and a gate electrode coupled to the scan line Sn corresponding to the pixel row including the pixel 70 and transmitting the scan signal S[n]. Here, the pixel 70 is included in the nth pixel row such that the corresponding scan line is the nth scan line.

[0089] If the scan signal S[n] is transmitted through the nth scan line such that the first transistor M1 is turned on, the data signal is transmitted to the second node N2, and the data voltage Vdata corresponding to the data signal is transmitted to the source electrode of the driving transistor Md.

**[0090]** The scan signal S[n] is also concurrently (e.g., simultaneously) transmitted to the gate electrode of the threshold voltage compensation transistor M4.

[0091] The threshold voltage compensation transistor M4 is coupled between the gate electrode and the drain electrode of the driving transistor Md, and is turned on during the time that the scan signal S[n] is transmitted as the gate-on voltage level to diode-couple the driving transistor Md. Thus, a data voltage Vdata applied to the source electrode of the driving transistor Md is reduced by the threshold voltage of the driving transistor Md such that a voltage Vdata-Vth is applied to the gate electrode of the driving transistor Md. The gate electrode of the driving transistor Md is coupled to one terminal of the

20

40

capacitor C1 such that the voltage Vdata-Vth is maintained by the capacitor C1. The voltage Vdata-Vth reflecting the threshold voltage Vth of the driving transistor Md is applied to the gate electrode of the driving transistor Md and is maintained such that the driving current flowing in the driving transistor Md is not affected by variations in the threshold voltage of the driving transistor Md.

**[0092]** The second transistor M2 includes a gate electrode coupled to the (n-1)th scan line and receiving the scan signal S[n-1], a source electrode coupled to the first power source voltage ELVDD, and a drain electrode coupled to the second node N2.

[0093] The second transistor M2 is turned on by the scan signal S[n-1], which is transmitted at a gate-on voltage level through the (n-1)th scan line before the scan signal S[n] is transmitted to the pixel 70 through the nth scan line at the gate-on voltage level. Thus, the first power source voltage ELVDD is applied to the source electrode of the driving transistor Md during the period in which the driving transistor Md is switched on by the scan signal S[n-1].

**[0094]** The initialization transistor M3 transmitting the initialization voltage VINT to the gate electrode of the driving transistor Md is switching-operated by the scan signal S[n-1].

**[0095]** The initialization transistor M3 includes a gate electrode coupled to the (n-1)th scan line, a source electrode coupled to the voltage source transmitting the initialization voltage VINT, and a drain electrode coupled to the gate electrode of the driving transistor Md.

**[0096]** The initialization voltage VINT is applied to the gate electrode of the driving transistor Md during the time that the scan signal S[n-1] is transmitted to the initialization transistor M3 as the gate-on voltage level. The gate electrode of the driving transistor Md is initialized at the initialization voltage VINT during a period in which the scan signal S[n-1] is transmitted at the gate-on voltage level.

**[0097]** During the initialization period in which the scan signal S[n-1] is transmitted at the gate-on voltage level, the source electrode of the driving transistor Md is applied with the first power source voltage ELVDD, and concurrently (e.g., simultaneously) the gate electrode of the driving transistor Md is applied with the initialization voltage VINT, and thereby the voltage difference Vgs between the gate and the source of the driving transistor Md during the initialization period becomes ELVDD-VINT. This is a voltage value that is greater than the reference voltage at which the driving transistor Md is operated.

**[0098]** The voltage difference Vgs between the gate and the source of the driving transistor Md during the initialization period is more than the reference voltage such that the driving transistor Md is on-biased.

**[0099]** The data voltage is written to the driving transistor Md during the state in which the driving transistors Md of all of the pixels are on-biased, and thereby the hysteresis characteristic may be improved.

[0100] When a plurality of driving transistors are ap-

plied with the data voltage of the previous frame, the gatesource voltage of each driving transistor may be at a different level than the gate-source voltage of each driving transistor in the current frame, before the data voltage of the current frame is written.

**[0101]** If there is no initialization period, the hysteresis characteristic of the gate-source voltage of each driving transistor may be different depending on whether the data voltage of the current frame is a higher or lower voltage than the data voltage of the previous frame. In this embodiment of the present invention, the gate-source voltage of each driving transistor during the initialization period becomes ELVDD-VINT such that all of the driving transistors are on-biased with the same condition (e.g., all of the driving transistors have the same gate-source voltage).

**[0102]** Accordingly, the gate-source voltage of the driving transistors of all pixels is determined according to the data voltage of the current frame in the same conditions without the effect of the hysteresis characteristic.

**[0103]** In this embodiment of the present invention, the signal controlling the switching operation of the second transistor M2 and the initialization transistor M3 uses the scan signal transmitted through the previous scan line of the scan line coupled to the corresponding pixel row, however it is not limited thereto and an additional control signal may be transmitted.

**[0104]** On the other hand, in the case of the pixel included in the first pixel row, the scan signal transmitted to the second transistor M2 and the initialization transistor M3 may be a dummy scan signal that is generated and transmitted from the scan driver 20.

[0105] For example, the capacitor C1 includes a first electrode coupled to the first node N1 and a second electrode coupled to the first power source voltage ELVDD. [0106] The capacitor C1 is coupled to the first node N1 to which the gate electrode of the driving transistor Md is coupled, thereby storing the voltage value of the gate electrode of the driving transistor Md according to the driving process of the pixel.

**[0107]** Also, the first light emission control transistor M5 of the pixel 70 includes a gate electrode coupled to the nth light emission control line and receiving the light emission control signal EM[n], a source electrode coupled to the third node N3, and a drain electrode organic coupled to the anode of the light emitting diode OLED.

**[0108]** The pixel 70 includes the second light emission control transistor M6, and the second light emission control transistor M6 has a gate electrode coupled to the nth light emission control line and receiving the light emission control signal EM[n], a source electrode coupled to the first power source voltage ELVDD, and a drain electrode coupled to the second node N2.

[0109] The light emission control transistor of this embodiment of the present invention is only one example and the pixel circuit configuration is not limited thereto.

[0110] If the light emission control signal EM[n] is transmitted at the gate-on voltage level, the first light emission

control transistor M5 and the second light emission control transistor M6 are turned on. The driving current corresponding to the data voltage stored in the capacitor C1 is transmitted to the OLED according to the data signal and during the data writing period, such that light is emitted. As described above, the data voltage stored to the capacitor C1 is the voltage value Vdata-Vth reflecting the threshold voltage Vth such that the effect of variations in the threshold voltage is reduced when light emission occurs due to the corresponding driving current.

**[0111]** Although the transistors included in the driving circuit of the pixel shown in FIG. 3 are PMOS transistors, embodiments of the present invention are not limited thereto, and the transistors may be realized as NMOS transistors.

**[0112]** A driving timing diagram is shown in FIG. 4 for comprehension of the driving of the pixel 70 shown in FIG. 3.

**[0113]** The pixel 70 is coupled to two scan lines to receive the scan signals and be operated.

**[0114]** First, the scan signal S[n-1] is transmitted through the (n-1)th scan line and is transitioned (or changed) to a low level at the time t1 and maintains the low level during the period T1.

**[0115]** Accordingly, the second transistor M2 and the initialization transistor M3 receiving the scan signal S[n-1] in the pixel are concurrently (e.g., simultaneously) turned on.

**[0116]** The first power source voltage ELVDD having a high level voltage is applied to the source electrode of the driving transistor Md through the second transistor M2 during the period T1, and the initialization voltage VINT is applied to the gate electrode of the driving transistor Md through the initialization transistor M3.

[0117] The gate-source voltage difference Vgs of the driving transistor Md is maintained as ELVDD-VINT during the period T1. At this time, the initialization voltage VINT is at a low level such that the voltage difference Vgs may be more than a minimum reference voltage for operating the driving transistor Md. Accordingly, the driving transistors Md included in all of the pixels are onbiased before the period in which the threshold voltage of the driving transistor Md is compensated for and the data is written in each frame. Accordingly, an image that is displayed with the desired gray level may be realized regardless of the hysteresis characteristic of the driving transistor Md.

**[0118]** Next, the scan signal S[n-1] is transitioned to a high level at the time t2, and the scan signal S[n] transmitted through the nth scan line is transitioned (or changed) to a low level at the time t3 and maintains the low level during the period T2.

**[0119]** The scan signal S[n-1] is transmitted at the high level (or maintains the high state) during the period T2 such that the second transistor M2 and the initialization transistor M3 are turned off, and the first node N1 is floating.

[0120] Concurrently (e.g., simultaneously), the first

transistor M1 and the threshold voltage compensation transistor M4 receiving the scan signal S[n] in the pixel during period T2 are turned on. Thus, the data voltage Vdata according to the data signal DATA is transmitted to the source electrode of the driving transistor Md through the first transistor M1 during the period T2, and the driving transistor Md is diode-coupled with the threshold voltage compensation transistor M4.

**[0121]** Accordingly, the voltage maintained at the first node N1 coupled to one terminal of the capacitor C1 during the period T2 is the voltage Vgs. The voltage Vgs corresponds to the voltage difference between gate and source electrodes of the driving transistor Md, and is represented by the voltage value Vdata-Vth, which is the data voltage Vdata reduced by the threshold voltage Vth of the driving transistor Md.

**[0122]** The driving transistor Md is on-biased during the initialization period of the period T1 such that the hysteresis characteristic may be reduced (or improved), and thereby the delay problem of the response speed may be improved (or solved) during the expression of gray levels according to the data voltage Vdata.

**[0123]** When the scan signal S[n] is transitioned to a high level at the time t4, the first transistor M1 and the threshold voltage compensation transistor M4 are turned off. Thus, the first node N1 is again floating.

**[0124]** The light emission control signal EM[n] transmitted to the pixel 70 included in the nth pixel row is transitioned (or changed) to the low level at the time t5.

[0125] Thus, the first light emission control transistor M5 and the second light emission control transistor M6 receiving the light emission control signal EM[n] of the pixel 70 are turned on, and the driving current stored to the capacitor C1 and corresponding to the data voltage according to the data signal is transmitted to the OLED for light emission.

**[0126]** The voltage value for calculating the driving current is the corresponding voltage ELVDD-Vdata, excluding the effect of the threshold voltage Vth of the driving transistor Md.

[0127] The pixel and the display device including the same according to an embodiment of the present invention may concurrently (e.g., simultaneously) reduce (or solve the problem of) the delay in the response speed due to hysteresis while reducing (or excluding) the effect of variations in the threshold voltage of the driving transistor when displaying the image according to the data signal, such that the response speed is not delayed and light is emitted with the desired luminance in the corresponding frame as shown in the waveform diagram in FIG. 5. As a result, a clear and high quality image may be provided.

**[0128]** Referring to the waveform diagram of FIG. 5, if the display device is driven using a conventional pixel, the light is not emitted with the desired luminance due to hysteresis, but is displayed with a luminance of a middle degree, and then the light is emitted with a normal luminance in the next frame. However, if the display device

30

35

40

45

50

is driven through a pixel according to embodiments of the present invention, an improved waveform displaying an improved luminance (e.g., a desired luminance) in the corresponding frame may be obtained.

[0129] Although the present invention is described with reference to detailed embodiments of the present invention, this is by way of example only and the present invention is not limited thereto. A person of ordinary skill in the art may change or modify the described embodiments without departing from the scope of the present invention, and the changes or modifications are also included in the scope of the present invention. Further, materials of each of the components described in the present specification may be selected from or replaced by various materials known to a person of ordinary skill in the art. In addition, a person of ordinary skill in the art may omit some of the components described in the present application without deteriorating the performance, or may add components in order to improve the performance. Further, a person of ordinary skill in the art may change a sequence of processes described in the present application, according to the process environments or equipment. Therefore, while the present invention has been described in connection with certain exemplary embodiments, it is to be understood that the invention is not limited to the disclosed embodiments, but, on the contrary, is intended to cover various modifications and equivalent arrangements included within the scope of the appended claims, and equivalents thereof.

#### Claims

1. A pixel comprising:

an organic light emitting diode (OLED); a driving transistor configured to transmit a driving current to the OLED according to a data signal:

a first transistor configured to transmit the data signal to the driving transistor according to a first scan signal;

a second transistor configured to apply a first power source voltage to a source electrode of the driving transistor according to a second scan signal during an initialization period for initializing a gate electrode voltage of the driving transistor; and

a capacitor comprising a first electrode coupled to a gate electrode of the driving transistor and a second electrode coupled to a first power source supply.

2. A pixel according to claim 1, wherein

The driving transistor is adapted to be operated by

a voltage difference between the gate electrode voltage and a source electrode voltage of the driving

transistor during the initialization period.

3. The pixel according to claim 1 or 2, wherein the first transistor comprises a gate electrode for receiving the first scan signal, a source electrode for receiving the data signal, and a drain electrode coupled to the source electrode of the driving transistor, wherein the first transistor is switching-operated according to the first scan signal and is configured to transmit the data signal to the source electrode of the driving transistor.

**4.** A pixel according to any preceding claim, wherein the second scan signal is transmitted to a second scan line preceding a first scan line receiving the first scan signal.

**5.** A pixel according to any preceding claim, further comprising:

an initialization transistor configured to supply an initialization voltage to the gate electrode of the driving transistor during the initialization period and to initialize the gate electrode voltage of the driving transistor.

25 **6.** A pixel according to claim 5, wherein the initialization transistor comprises:

a gate electrode for receiving the second scan signal, a source electrode applied with the initialization voltage, and a drain electrode coupled to the gate electrode of the driving transistor, wherein the initialization transistor is configured to be switching-operated according to the second scan signal.

7. A pixel according to claim 5 or 6, wherein the initialization period is a period in which the second scan signal is transmitted to the initialization transistor at a gate-on voltage level.

A pixel according to any preceding claim, wherein the initialization period is before a period in which a threshold voltage of the driving transistor is compensated.

**9.** A pixel according to any preceding claim, further comprising:

a threshold voltage compensation transistor configured to be switching-operated according to the first scan signal after the initialization period and to diode-couple the driving transistor and compensate a threshold voltage of the driving transistor.

10. A pixel according to any preceding claim, further comprising:

15

20

25

40

45

50

at least one light emission control transistor coupled between the first power source supply and the OLED and comprising a gate electrode for receiving a light emission control signal for controlling light emission of the OLED receiving the driving current according to the data signal.

- 11. A pixel according to claim 10, wherein the at least one light emission control transistor is configured to be operated according to the light emission control signal transmitted at a gate-on voltage level after the first scan signal and the second scan signal are respectively transmitted at the gate-on voltage level to the first transistor and the second transistor in the pixel.

- **12.** A pixel according to claim 10 or 11, wherein the at least one light emission control transistor further comprises:

a source electrode coupled to a drain electrode of the driving transistor, and a drain electrode coupled to an anode of the OLED.

- **13.** A pixel according to claim 10, 11 or 12, wherein the at least one light emission control transistor further comprises:

- a source electrode coupled to the first power source supply, and a drain electrode coupled to the source electrode of the driving transistor.

- 14. A pixel according to any preceding claim, wherein the first transistor is adapted to be switching-operated according to the first scan signal to transmit the data signal to the first electrode of the driving transistor.

- 15. A display device comprising:

a display unit comprising a plurality of pixels respectively coupled to a plurality of scan lines for transmitting a plurality of scan signals, a plurality of data lines for transmitting a plurality of data signals, and a plurality of light emission control lines for transmitting a plurality of light emission control signals;

a scan driver for transmitting the plurality of scan signals;

a data driver for transmitting the plurality of data signals; and

a light emission driver for transmitting the plurality of light emission control signals,

wherein at least one of the pixels is as set out in one of Claims 1 to 14.

**16.** A display device according to claim 15, wherein the scan driver is configured to transmit the first scan

signal and the second scan signal to the plurality of pixels.

17. A method of driving a display device comprising a plurality of pixels, wherein each pixel of the plurality of pixels comprises: an organic light emitting diode (OLED); a driving transistor for transmitting a driving current to the OLED according to a data signal; a first transistor for transmitting the data signal to the driving transistor according to a first scan signal; a second transistor for applying a first power source voltage to the driving transistor according to a second scan signal; and a capacitor coupled between the driving transistor and a first power source supply, the method comprising:

initializing a gate electrode voltage of the driving transistor;

compensating for a threshold voltage of the driving transistor and transmitting the data signal to the driving transistor; and

providing the driving current to the OLED according to the data signal to produce light emission,

wherein the second scan signal is transmitted at a gate-on voltage level during the initializing the gate electrode voltage of the driving transistor

- 30 18. A method according to claim 17, wherein a voltage between a gate electrode and a source electrode of the driving transistor is a voltage for operating the driving transistor during the initializing the gate electrode voltage of the driving transistor.

- **19.** A method according to claim 17 or 18, wherein the second scan signal is transmitted to a second scan line preceding a first scan line receiving the first scan signal.

- 20. A method according to one of claims 17 to 19, wherein the initializing the gate electrode voltage of the driving transistor comprises applying an initialization voltage to a gate electrode of the driving transistor via an initialization transistor configured to be switching-operated according to the second scan signal.

- 21. A method according to one of claims 17 to 20, wherein the compensating for the threshold voltage of the driving transistor comprises diode-coupling the driving transistor via a threshold voltage compensation transistor configured to be switching-operated according to the first scan signal.

- 55 22. A method according to one of claims 17 to 21, wherein the providing the driving current to the OLED according to the data signal to produce light emission comprises

controlling the light emission of the OLED via at least one light emission control transistor coupled between the first power source supply and the OLED, wherein the at least one light emission control transistor is configured to be switching-operated by a light emission control signal.

23. A method according to claim 22, wherein the light emission control signal is transmitted at the gate-on voltage level after the first scan signal and the second scan signal are respectively transmitted at the gate-on voltage level to the first transistor and the second transistor.

FIG. 1

FIG. 3

FIG. 4

# FIG. 5

# **EUROPEAN SEARCH REPORT**

Application Number EP 11 17 8920

|                                                     | DOCUMENTS CONSID                                                                                                                                                                         |                                                                           |                                                                   |                                         |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------|

| Category                                            | Citation of document with in of relevant pass                                                                                                                                            | ndication, where appropriate,<br>ages                                     | Relevant<br>to claim                                              | CLASSIFICATION OF THE APPLICATION (IPC) |

| Х                                                   | 12 January 2005 (20                                                                                                                                                                      | MSUNG SDI CO LTD [KR])<br>05-01-12)<br>- [0043]; figures 4-7              | 1-23                                                              | INV.<br>G09G3/32                        |

| Х                                                   | JIN TAE [KR]) 16 Ma                                                                                                                                                                      | JEONG JIN T [KR] JEONG<br>arch 2006 (2006-03-16)<br>- [0068]; figures 6,7 | 1-23                                                              |                                         |

| Х                                                   | SAMSUNG MOBILE DISF<br>25 June 2008 (2008-                                                                                                                                               |                                                                           | 1-23                                                              |                                         |

| х                                                   | AL) 14 January 2010                                                                                                                                                                      | TANIKAME TAKAO [JP] ET<br>(2010-01-14)<br>- [0134]; figure 6 *            | 1-23                                                              |                                         |

|                                                     |                                                                                                                                                                                          |                                                                           |                                                                   | TECHNICAL FIELDS<br>SEARCHED (IPC)      |

|                                                     |                                                                                                                                                                                          |                                                                           |                                                                   | G09G                                    |

|                                                     |                                                                                                                                                                                          |                                                                           |                                                                   |                                         |

|                                                     | The present search report has                                                                                                                                                            | been drawn up for all claims                                              |                                                                   |                                         |

|                                                     | Place of search                                                                                                                                                                          | Date of completion of the search                                          | <u>'                                    </u>                      | Examiner                                |

|                                                     | The Hague                                                                                                                                                                                | 7 December 2011                                                           | Be1                                                               | latalla, Filippo                        |

| X : part<br>Y : part<br>docu<br>A : tech<br>O : non | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone icularly relevant if combined with anot iment of the same category inclogical background written disclosure mediate document | L : document cited fo                                                     | eument, but publise<br>e<br>n the application<br>or other reasons | shed on, or                             |

#### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 11 17 8920

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

07-12-2011

| EP 1496495 A2  US 2006055336 A1 | 12-01-2005 | CN 1577453<br>EP 1496495<br>JP 4391857                                                       |                    | 09-02-200                                                                  |

|---------------------------------|------------|----------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------|

| US 2006055336 A1                |            | JP 2005031630<br>KR 20050005646<br>US 2005017934                                             | B2<br>A<br>A       | 12-01-200<br>24-12-200<br>03-02-200<br>14-01-200<br>27-01-200              |

|                                 | 16-03-2006 | CN 1744774<br>JP 4188930<br>JP 2006065282<br>KR 20060019757<br>US 2006055336                 | B2<br>A<br>A       | 08-03-20<br>03-12-20<br>09-03-20<br>06-03-20<br>16-03-20                   |

| EP 1936596 A1                   | 25-06-2008 | CN 101231821<br>CN 102097054<br>EP 1936596<br>JP 2008158477<br>KR 100833753<br>US 2008150846 | A<br>A1<br>A<br>B1 | 30-07-20(<br>15-06-20)<br>25-06-20(<br>10-07-20(<br>30-05-20(<br>26-06-20( |

| US 2010007649 A1                | 14-01-2010 | CN 101630475<br>JP 2010020208<br>KR 20100007747<br>TW 201005706<br>US 2010007649             | A<br>A<br>A        | 20-01-20<br>28-01-20<br>22-01-20<br>01-02-20<br>14-01-20                   |

© For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

| 像素,包括其的显示装置及其驱动方法                                                                              |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| EP2463849A1                                                                                    | 公开(公告)日                                                                                                                                                                             | 2012-06-13                                                                                                                                                                                             |  |  |

| EP2011178920                                                                                   | 申请日                                                                                                                                                                                 | 2011-08-25                                                                                                                                                                                             |  |  |

| 三星显示有限公司                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

| 三星移动显示器有限公司.                                                                                   |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

| 三星移动显示器有限公司.                                                                                   |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

| JEONG JIN TAE                                                                                  |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

| JEONG, JIN-TAE                                                                                 |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

| G09G3/32                                                                                       |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

| G09G3/3233 G09G2300/0819 G09G2300/0842 G09G2300/0861 G09G2310/0251 G09G2320/0233 G09G2320/0252 |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

| 1020100126489 2010-12-10 KR                                                                    |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

| EP2463849B1                                                                                    |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

| Espacenet                                                                                      |                                                                                                                                                                                     |                                                                                                                                                                                                        |  |  |

|                                                                                                | EP2463849A1 EP2011178920 三星显示有限公司 三星移动显示器有限公司. 三星移动显示器有限公司. JEONG JIN TAE JEONG, JIN-TAE G09G3/32 G09G3/3233 G09G2300/0819 G09G09G2320/0252 1020100126489 2010-12-10 KR EP2463849B1 | EP2463849A1 EP2011178920 申请日 三星显示有限公司 三星移动显示器有限公司. 三星移动显示器有限公司. JEONG JIN TAE JEONG, JIN-TAE G09G3/323 G09G2300/0819 G09G2300/0842 G09G2300/0861 G09G2320/0252 1020100126489 2010-12-10 KR EP2463849B1 |  |  |

### 摘要(译)

一种显示装置,包括:显示单元,包括耦合到用于传输扫描信号的扫描 线的像素,用于传输数据信号的数据线,以及用于传输光发射控制信号 的光发射控制线;扫描驱动程序;数据驱动程序;和一个发光驱动器。每个 像素包括:OLED;驱动晶体管,用于将对应于数据信号的驱动电流传输 到OLED;第一晶体管,用于根据第一扫描信号将数据信号传输至驱动晶 体管;第二晶体管,用于在初始化时段期间根据第二扫描信号将第一电源 电压施加到驱动晶体管的第一电极,用于初始化驱动晶体管的栅电极电 压;电容器包括耦合到驱动晶体管的栅电极的第一电极和耦合到第一电源 的第二电极。