(11) EP 1 594 118 B1

(12)

## EUROPEAN PATENT SPECIFICATION

(45) Date of publication and mention

of the grant of the patent:

**27.08.2008 Bulletin 2008/35**

(51) Int Cl.:

**G09G 3/32 (2006.01)**

(21) Application number: **05103365.2**(22) Date of filing: **26.04.2005****(54) Pixel drive circuit for driving sub-pixels in OLED colour display in time multiplexing mode**

Pixelschaltung zur Zeitmultiplexansteuerung von Unterpixeln in einer OLED-Farbanzeige

Circuit d'attaque de pixel à multiplexage temporel de sous-pixels dans un affichage couleur à OLED

(84) Designated Contracting States:

**AT BE BG CH CY CZ DE DK EE ES FI FR GB GR

HU IE IS IT LI LT LU MC NL PL PT RO SE SI SK TR**

(30) Priority: **29.04.2004 KR 2004029944

29.04.2004 KR 2004029945**

(43) Date of publication of application:

**09.11.2005 Bulletin 2005/45**

(73) Proprietor: **Samsung SDI Co., Ltd.**

**Suwon-si,

Gyeonggi-do (KR)**

(72) Inventor: **Kwak, Won-Kyu,

c/o Samsung SDI Co., Ltd.

Suwon-si,

Gyeonggi-do (KR)**

(74) Representative: **Hengelhaupt, Jürgen et al

Anwaltskanzlei

Gulde Hengelhaupt Ziebig & Schneider

Wallstrasse 58/59

10179 Berlin (DE)**

(56) References cited:

**EP-A- 0 762 374 EP-A- 1 531 452

US-A1- 2004 070 557 US-B1- 6 618 031**

- N. KOMIYA ET AL.: "Comparison of V<sub>th</sub> compensation ability among voltage programming circuits for AMOLED panels" IDW INTERNATIONAL DISPLAY WORKSHOPS TECHNICAL DIGEST, 2003, pages 275-278, XP008051507**

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

**Description****(a) Field of the Invention**

5 [0001] The present invention relates to a display device. More particularly, the present invention relates to an organic electroluminescent display using electroluminescence (hereinafter, 'EL') of organic materials.

**(b) Description of the Related Art**

10 [0002] In general, an organic electroluminescent (EL) display electrically excites a phosphorous organic compound to emit light. The organic emitting elements (or organic emitting cells) are arranged in an nxm matrix format to configure an organic EL display panel which displays image data by voltage- or current-driving.

15 [0003] The organic emit element has diode properties, and thus is also referred to as an organic light emitting diode (OLED). The organic emit element includes an anode (ITO), an organic thin film, and a cathode layer (metal). The organic thin film has a multi-layer structure including an emitting layer (EML), an electron transport layer (ETL), and a hole transport layer (HTL) for maintaining balance between electrons and holes and improving emitting efficiencies. Further, the organic emitting element includes an electron injecting layer (EIL) and a hole injecting layer (HIL). The organic emitting elements are arranged in an nxm matrix format to configure an organic EL display panel.

20 [0004] Methods for driving the organic EL display panel include a passive matrix method, and an active matrix method which uses thin-film transistors (TFTs). The passive matrix method includes forming anodes and cathodes to cross (or cross over) with or to be substantially perpendicular to each other, selecting lines, and driving the organic EL display panel. The active matrix method includes orderly turning on of a plurality of TFTs which are respectively coupled to data lines and scan lines according to signals for selecting the scan lines and driving the organic EL display panel.

25 [0005] Hereinafter, a pixel circuit of a general active matrix organic EL display is described.

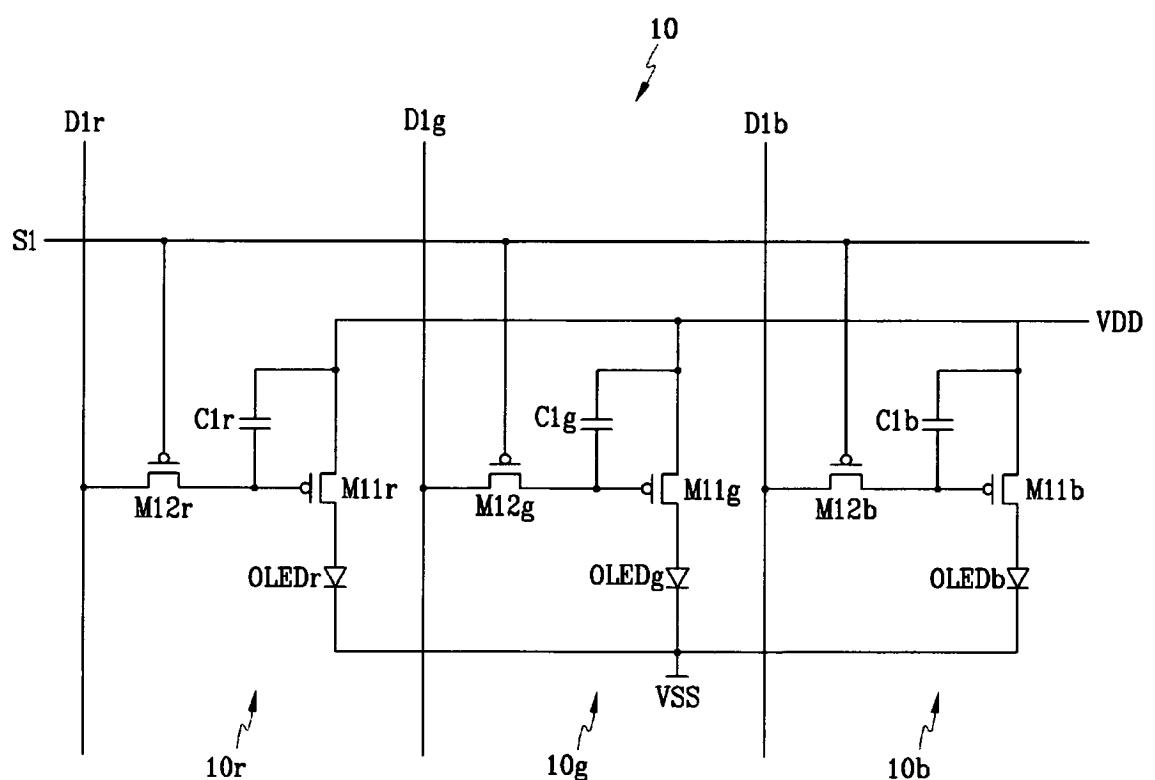

26 [0006] Fig. 1 shows a pixel circuit, one of nxm pixels, which is located at a first row and a first column.

30 [0007] As shown in Fig. 1, one pixel 10 includes three sub pixels 10r, 10g, and 10b, which respectively include organic EL elements OLED<sub>r</sub>, OLED<sub>g</sub>, and OLED<sub>b</sub> for respectively emitting a red light (R), a green light (G), and a blue light (B). Further, in the structure the sub pixels are arranged in a stripe format, and the sub pixels 10r, 10g, and 10b are coupled to separate data lines D1r, D1g, and D1b and to a common scan line S1.

35 [0008] The red color sub pixel 10r includes two transistors M11r and M12r and a capacitor C1r for driving the organic EL element OLED<sub>r</sub>. In the same manner, the green color sub pixel 10g includes two transistors M11g and M12g and a capacitor C1g for driving the organic EL element OLED<sub>g</sub>, and the blue color sub pixel 10b includes two transistors M11b and M12b and a capacitor C1b for driving the organic EL element OLED<sub>b</sub>. Since the connections and operations of the sub pixels 10r, 10g, and 10b are substantially the same, only the connection and operation of the sub pixel 10r will now be described as an example.

40 [0009] The driving transistor M11r is coupled between a power supply source voltage VDD and an anode of the organic EL element OLED<sub>r</sub>, and transmits a current for emitting light to the organic EL element OLED<sub>r</sub>. A cathode of the organic EL element OLED<sub>r</sub> is coupled to a voltage VSS which is lower than the power supply source voltage VDD. The amount of the current flowing in the driving transistor M11r is controlled by a data voltage applied through the switching transistor M12r. The capacitor C1r is coupled between a source and a gate of the transistor M11r and controls applied voltage during a predetermined period. A scan line S1 for transmitting an on/off selection signal is coupled to a gate of the transistor M12r, and a data line D1r for transmitting a data voltage corresponding to the red color sub pixel 10r is coupled to a source of the transistor M12r.

45 [0010] Here, the switching transistor M12r is turned on in response to a select signal which is applied to the gate. Then, the data voltage V<sub>DATA</sub> is applied to the gate of the transistor M11r from the data line D1r through the transistor M12r. Then, a current I<sub>OLED</sub> flows to (and/or through) the transistor M11r corresponding to a voltage V<sub>GS</sub> which is charged between the gate and source of the transistor M11r by the capacitor C1r. The organic EL element OLED<sub>r</sub> emits red light corresponding to the current I<sub>OLED</sub>. The current flowing to the organic EL element OLED<sub>r</sub> is calculated as given in the following Equation 1.

50

**[Equation 1]**

$$I_{OLED} = \frac{\beta}{2} (V_{GS} - V_{TH})^2 = \frac{\beta}{2} (V_{DD} - V_{DATA} - |V_{TH}|)^2$$

[0011] Here,  $V_{TH}$  is a threshold voltage of the transistor M11r, and  $\beta$  is a constant.

[0012] As represented by Equation 1, a current corresponding to a data voltage is supplied to an organic EL element OLEDr in the pixel circuit shown in Fig. 1, and the organic EL element OLEDr emits a red light to brightness corresponding to the supplied current. Here, the supplied data voltage has multistage voltage values in a predetermined range to display a certain gray scale.

[0013] As such, in the organic EL display, one pixel 10 includes three subpixels 10r, 10g, and 10b, and each sub pixel includes a driving transistor, M11r, M11g or M11b, a switching transistor, M12r, M12g or M12b, and a capacitor, C1r, C1g or C1b, for driving the organic EL element, OLEDr, OLEDg or OLEDb. Further, each sub pixel is coupled to a data line for transmitting a data signal and a power line for transmitting a power supply source voltage  $V_{DD}$ .

[0014] Therefore, many lines for transmitting voltages and signals to a transistor and a capacitor are required to be located in each pixel, and there is difficulty to arrange all the lines within one pixel.

[0015] EP0762374 A discloses a driving circuit for OLED pixels in active matrix display devices. The subpixels of one OLED pixel share the same data line and the same current driving transistor in order to improve aperture ratio. The cathodes of the subpixels' LEDs are connected to the current driving transistor, the anodes are connected to a power supply line which is controlled in a time multiplexing mode to switch on the respective subpixel during a corresponding subframe.

[0016] In US6618031 B1 red, green, and blue LEDs of a pixel share the same driver circuit. Each LED is series connected to a corresponding FET for enabling current flow through the LED. The FETs are controlled by means of enable signals.

[0017] N. Komiya et al. propose a pixel circuit for an OLED display device in "Comparison of Vth compensation ability among voltage programming circuits for AMOLED panels", IDW International Display Workshops Technical Digest, pages 275 through 278, 00-00-2003. There, a threshold voltage compensation capacitor is connected between the gate of the driver transistor and the address transistor. A data voltage storage capacitor is connected between the address transistor and Vdd. The pixel circuit further includes a reset transistor connected to the data storage transistor and a threshold compensation transistor coupled between the gate and the drain of the driver transistor. The gates of the reset and the threshold compensation transistors are connected to a previous gate line for initialisation of the threshold compensation.

## SUMMARY OF THE INVENTION

[0018] The present invention provides a light emitting display having components that are efficiently arranged in a pixel. The display device comprises a plurality of scan lines for transmitting select signals, a plurality of data lines for transmitting data signals, and a plurality of pixel circuits coupled to the scan lines and the data lines. Each of the pixel circuits comprises first and second capacitors, first, second, third, and fourth transistors, first, second, and third emit elements, and first, second, and third emit control transistors. The first capacitor is provided for charging a voltage which corresponds to one of the data signals transmitted from a corresponding one of the data lines. The first transistor is provided for outputting a current which corresponds to the voltage charged in the first capacitor and has one of the source and the drain connected to a first power supply source. The second transistor is coupled between a control electrode of the first transistor and the other one of the drain and the source of the first transistor. The control electrode of the second transistor is coupled to a first scan line. The third transistor has a first one of the source and the drain coupled to a first electrode of the first capacitor and to said first power supply source, a second one of the source and the drain coupled to a second electrode of the first capacitor, and the control electrode coupled to said first scan line (Sk-1). The second capacitor has a first electrode coupled to the second one of the source and the drain of the third transistor and a second electrode coupled to the control electrode of the first transistor. The fourth transistor has a first one of the source and the drain coupled to said one of the data lines, the other one of the source and the drain coupled to the first electrode of the second capacitor, and the control electrode coupled to a second scan line. The first, second, and third emit elements for emitting a light corresponding to the current outputted from the first transistor each have a first electrode coupled to a second power source. The first, second, and third emit control transistors are respectively coupled between said other one of the drain and the source of the first transistor and the second electrode of the corresponding one of the first, second, and third emit elements. The control electrodes of the first, second, and third emit transistors are coupled to emit control lines. According to the invention, the first semiconductor layer forming the first emit control transistor is arranged generally symmetrically with the second semiconductor layer forming the second emit control transistor with respect to the third semiconductor layer forming the third emit control transistor.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0019] The accompanying drawings, together with the specification, illustrate exemplary embodiments of the present invention, and, together with the description, serve to explain the principles of the present invention.

[0020] Fig. 1 shows a pixel circuit of a conventional light emitting display panel.

[0021] Fig. 2 is a schematic diagram of an organic EL display according to an exemplary embodiment of the present invention.

5 [0022] Fig. 3 shows an equivalent circuit of a pixel circuit according to an exemplary embodiment of the present invention.

[0023] Fig. 4 is an arrangement diagram of a pixel circuit according to a first exemplary embodiment of the present invention.

[0024] Fig. 5 is a cross-sectional view taken along I-I' in Fig. 4.

[0025] Fig. 6 is a cross-sectional view taken along II-II' in Fig. 4.

10 [0026] Fig. 7 is an arrangement diagram of a pixel circuit according to a second exemplary embodiment of the present invention.

## DETAILED DESCRIPTION

15 [0027] In the following detailed description, only certain exemplary embodiments of the present invention are shown and described, simply by way of illustration. As those skilled in the art would recognize, the described exemplary embodiments may be modified in various ways, all without departing from the spirit or scope of the present invention. Accordingly, the drawings and description are to be regarded as illustrative in nature, and not restrictive.

20 [0028] There may be parts shown in the drawings, or parts not shown in the drawings, that are not discussed in the specification as they are not essential to a complete understanding of the invention. Like reference numerals designate like elements. The thickness is magnified to more clearly show several layers and areas in the drawings. When a layer, a membrane, a board, etc., is described to be located 'on' another part, it is understood that a further part can be located therebetween.

25 [0029] In addition, several terms for scan lines are defined. "A present scan line" refers to a scan line transmitting a present selection signal, and "a previous scan line" refers to a scan line that transmitted a selection signal before the present selection signal.

30 [0030] Further, "a present pixel" refers to a pixel emitting light on the basis of a selection signal of the present scan line, "a previous pixel" refers to a pixel emitting light on the basis of a selection signal of the previous scan line, and "a next pixel" refers to a pixel emitting light on the basis of a selection signal of the next scan line.

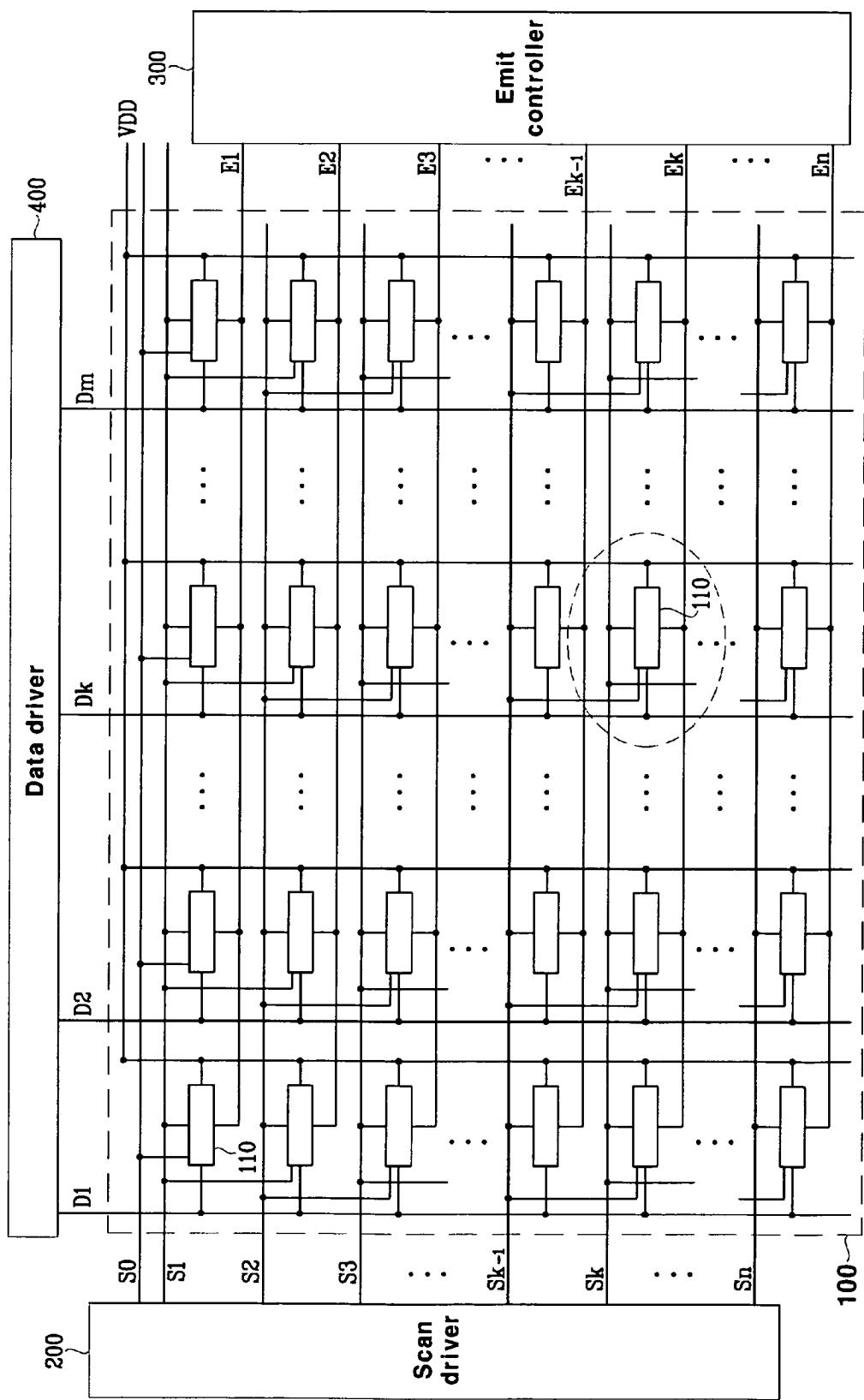

35 [0031] As shown in Fig. 2, the organic EL display according to an exemplary embodiment of the present invention includes a display panel 100, a scan driver 200, an emit controller 300, and a data driver 400. The display panel 100 includes a plurality of scan lines S0, S1, ... Sk... Sn and a plurality of emit control lines E1, ... Ek... En arranged in the row direction, a plurality of data lines D1 ... Dk... Dm and a plurality of power lines for applying power supply source voltage VDD arranged in the column direction and a plurality of pixels 110. Each of the pixels 110 is formed at a pixel area defined or surrounded by any two scan lines Sk-1 and Sk and any two neighboring data lines Dk-1 and Dk, and the pixels 110 are driven according to a signal transmitted from the present scan line Sk, the previous scan line Sk-1, the emit control line Ek, and the data line Dk. Further, each of the emit control lines E1 to En is composed of three emit control lines (e.g., E1 includes E1r, E1g and E1b, En includes Enr, Eng and Enb, and Ek includes Ekr, Ekg and Ekb as shown in FIG. 3).

40 [0032] The scan driver 200 sequentially applies the select signals for selecting corresponding lines to the scan lines S0 to Sn such that the data signals can be applied to the pixels of the corresponding lines. The emit controller 300 sequentially applies the emit control signals for controlling emission of the organic EL elements OLED<sub>r</sub>, OLED<sub>g</sub>, and OLED<sub>b</sub> shown in FIG. 3 to the emit control lines E1 to En. The data driver 400 applies the data signals corresponding to the pixels of the lines to which the selection signals are applied, to the data lines D1 to Dm, whenever the selection signals are sequentially applied.

45 [0033] The scan driver 200, the emit controller 300, and the data driver 400 can be coupled to the substrate on which the display panel 100 is formed. Alternatively, the scan driver 200, the emit controller 300, and/or the data driver 400 can be directly formed on the glass substrate of the display panel 100. Further, a driving circuit composed of the scan lines, the data lines, and transistors can be formed on the substrate of the display panel 100. Further, the scan driver 200, the emit controller 300, and/or the data driver 400 can be adhered and be coupled to the substrate of the display panel 100, as a tape carrier package (TCP), flexible printed circuit (FPC), or tape automatic bonding (TAB), etc.

50 [0034] In exemplary embodiments of the present invention, one field can be divided into three subfields which are then driven. Red, green, and blue color data are applied and red, green, and blue lights are emitted at the three subfields. Here, the scan driver 200 sequentially applies the select signals to the scan lines S0 to Sn at each subfield. The emit controller 300 sequentially applies the emit control signals to the emit control lines E1 to En such that each color organic EL element is emitted at each one subfield. The data driver 400 applies the data signals corresponding to red, green, and blue organic EL elements to the data lines D1 to Dm at three subfields.

55 [0035] Hereinafter, the detailed operation of the organic EL display according to an exemplary embodiment of the

present invention will be described in detail with reference to Fig. 3.

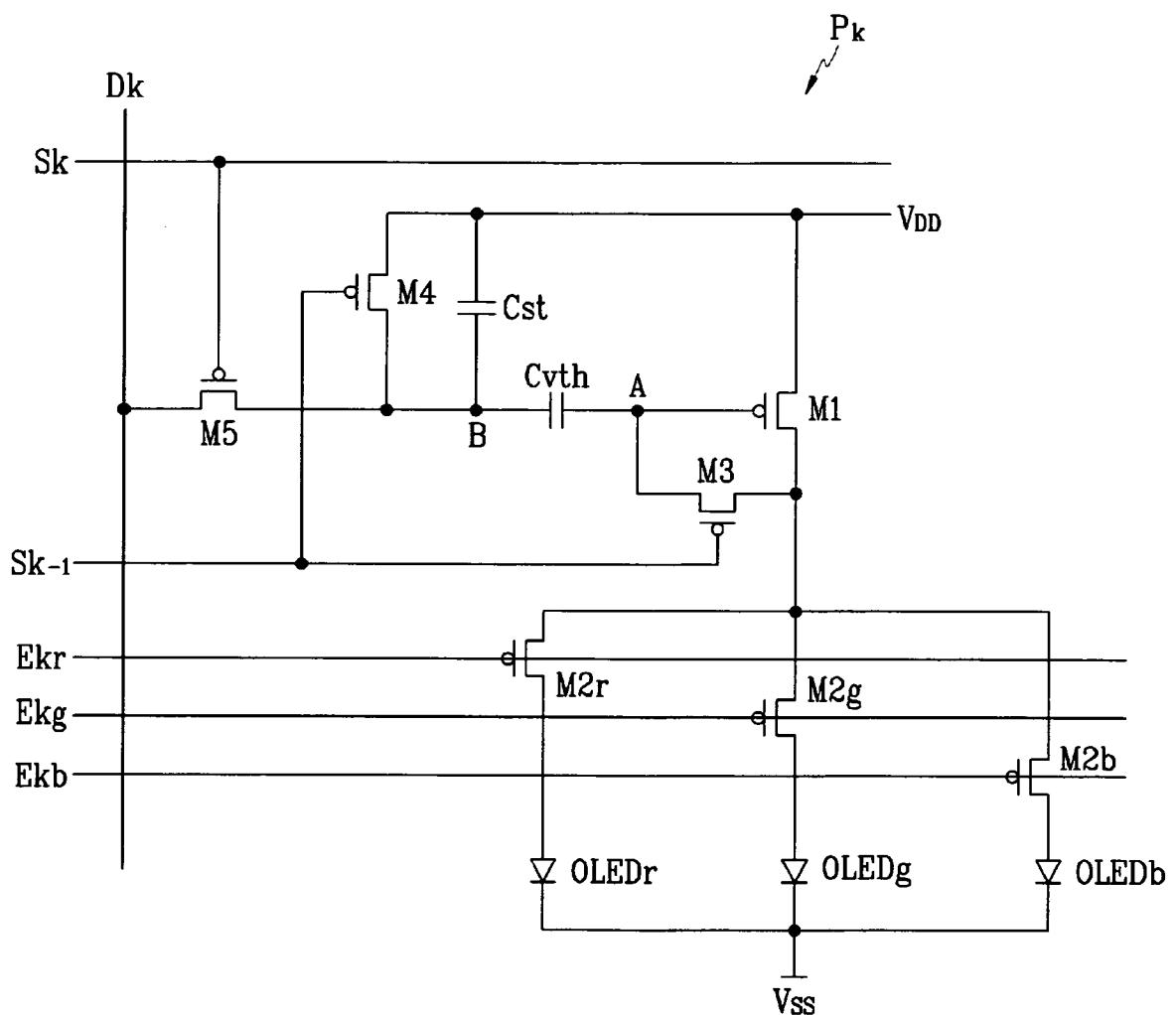

[0036] Fig. 3 shows an equivalent circuit of one pixel 110 in the organic EL display of Fig. 2. In Fig. 3, for example, a pixel  $P_k$  coupled to any  $k_{th}$  row of scan line  $S_k$ , and  $k_{th}$  column of data line  $D_k$  is described, and all transistors are p channel transistors.

[0037] As shown in Fig. 3, the pixel circuit according to the exemplary embodiment of the present invention includes a driving transistor M1, a diode transistor M3, a capacitor transistor M4, a switching transistor M5, three organic EL elements OLED<sub>r</sub>, OLED<sub>g</sub>, and OLED<sub>b</sub>, and three emit control transistors M2<sub>r</sub>, M2<sub>g</sub>, and M2<sub>b</sub> for controlling the emission of three organic EL elements OLED<sub>r</sub>, OLED<sub>g</sub>, and OLED<sub>b</sub>, and two capacitors C<sub>st</sub> and C<sub>vt</sub>. An emit control line E<sub>k</sub> is composed of three emit control lines E<sub>kr</sub>, E<sub>kg</sub>, and E<sub>kb</sub>. The emit control transistors M2<sub>r</sub>, M2<sub>g</sub>, and M2<sub>b</sub> respond to the emitting control signals transmitted through the emit control lines E<sub>kr</sub>, E<sub>kg</sub>, and E<sub>kb</sub>. The emit control transistors M2<sub>r</sub>, M2<sub>g</sub>, and M2<sub>b</sub> respond to the emitting control signals transmitted through the emit control lines E<sub>kr</sub>, E<sub>kg</sub>, and E<sub>kb</sub>, respectively, and selectively transmit the current transmitted from the driving transistor M1 to the organic EL elements OLED<sub>r</sub>, OLED<sub>g</sub>, and OLED<sub>b</sub>.

[0038] In detail, the transistor M5, of which the gate is coupled to the present scan line  $S_k$  and the source is coupled to the data line  $D_k$ , responds to the selection signal transmitted from the scan line  $S_k$  and transmits the data voltage applied from the data line  $D_k$  to a first electrode or node B of the capacitor C<sub>vt</sub>. The transistor M4 responds to the selection signal transmitted from the previous scan line  $S_{k-1}$  and couples the node B of the capacitor C<sub>vt</sub> to the power supply source V<sub>DD</sub>. The transistor M3 is coupled between a second electrode or a node A of the capacitor C<sub>vt</sub> and a drain of the transistor M1. The transistor M3 is turned on in response to the selection signal transmitted from the previous scan line  $S_{k-1}$  such that the transistor M1 is diode-connected. The driving transistor M1, for driving the organic EL element OLED (e.g., OLED<sub>r</sub>, OLED<sub>g</sub> and/or OLED<sub>b</sub>), has its gate coupled to the node A of the capacitor C<sub>vt</sub>, and its source coupled to the power supply source V<sub>DD</sub>. The driving transistor M1 controls the current that is applied to the organic EL element OLED according to the voltage that is applied to the gate.

[0039] Further, a first electrode of the capacitor C<sub>st</sub> is coupled to the power supply source V<sub>DD</sub>, and a second electrode of the capacitor C<sub>st</sub> is coupled to the drain of the transistor M4 at or about the node B, and the first electrode of the capacitor C<sub>vt</sub> is coupled to the second electrode of the capacitor C<sub>st</sub> such that the two capacitors are coupled in series, and the second electrode of the capacitor C<sub>vt</sub> is coupled to the gate of the driving transistor M1 at or about the node A.

[0040] The drain of the driving transistor M1 is coupled to the sources of the emit control transistors M2<sub>r</sub>, M2<sub>g</sub>, and M2<sub>b</sub>, and gates of the transistors M2<sub>r</sub>, M2<sub>g</sub>, and M2<sub>b</sub> are respectively coupled to the emit control lines E<sub>kr</sub>, E<sub>kg</sub> and E<sub>kb</sub>. Drains of the emit control transistors M2<sub>r</sub>, M2<sub>g</sub>, and M2<sub>b</sub> are respectively coupled to anodes of organic EL elements OLED<sub>r</sub>, OLED<sub>g</sub>, and OLED<sub>b</sub>. A power supply source V<sub>SS</sub> having a voltage level lower than that of the power supply source V<sub>DD</sub> is applied to the cathodes of the organic EL elements OLED<sub>r</sub>, OLED<sub>g</sub>, and OLED<sub>b</sub>. A negative voltage or ground voltage can be used for the power supply source V<sub>SS</sub>.

[0041] When a low level scan voltage is applied to the previous scan line  $S_{k-1}$ , the transistors M3 and M4 are turned on. When the transistor M3 is turned on, the transistor M1 comes to be in a diode-connected state. Thus, the voltage difference between the gate and source of the transistor M1 is changed until the voltage difference becomes a threshold voltage V<sub>th</sub> of the transistor M1. At this time, since the source of the transistor M1 is coupled to the power supply source V<sub>DD</sub>, a sum of the power supply source voltage V<sub>DD</sub> and the threshold voltage V<sub>th</sub> is applied to the gate of the transistor M1, that is, at or about the node A of the capacitor C<sub>vt</sub>. Further, when the transistor M4 is turned on and the power supply source voltage V<sub>DD</sub> is applied to the node B, the voltage V<sub>Cvt</sub> charged at the capacitor C<sub>vt</sub> can be calculated as given in the following Equation 2.

40

### [Equation 2]

$$V_{Cvt} = V_{CvtA} - V_{CvtB} = (VDD + Vth) - VDD = Vth$$

[0042] Here, C<sub>vt</sub> refers to a voltage that is charged at the capacitor C<sub>vt</sub>, V<sub>CvtA</sub> refers to a voltage that is applied to the node A of the capacitor C<sub>vt</sub>, and V<sub>CvtB</sub> refers to a voltage that is applied to the node B of the capacitor C<sub>vt</sub>.

[0043] When the low level scan voltage is applied to the present scan line  $S_k$ , the transistor M5 is turned on, and the data voltage V<sub>data</sub> is applied to the node B. Further, since the voltage corresponding to the threshold voltage V<sub>th</sub> of the transistor M1 is charged at the capacitor C<sub>vt</sub>, a voltage corresponding to the sum of the data voltage V<sub>data</sub> and the threshold voltage V<sub>th</sub> is applied to the gate of the transistor M1. That is, the voltage V<sub>gs</sub> between the gate and source of the transistor M1 can be calculated as given in the following Equation 3. Here, a high-level signal is applied to the emit control line E<sub>k</sub> (e.g., E<sub>kr</sub>, E<sub>kg</sub> and/or E<sub>kb</sub>), and the transistor M2 (e.g., M2<sub>r</sub>, M2<sub>g</sub> and/or M2<sub>b</sub>) is turned off to block a current flow.

## [Equation 3]

$$5 \quad V_{gs} = (V_{data} + V_{th}) - V_{DD}$$

10 [0044] Next, the transistor M2 is turned on in response to a low-level signal from the emit control line E<sub>k</sub>. Thus, the current I<sub>OLED</sub> corresponding to the gate-source voltage V<sub>gs</sub> of the transistor M1 is supplied to the organic EL element through the transistor M2, and the organic EL element OLED (e.g., OLED<sub>r</sub>, OLED<sub>g</sub>, and/or OLED<sub>b</sub>) is emitted. The current I<sub>OLED</sub> can be calculated as in the following Equation 4.

## 15 [Equation 4]

$$I_{OLED} = \frac{\beta}{2} (V_{gs} - V_{th})^2 = \frac{\beta}{2} ((V_{data} + V_{th} - V_{DD}) - V_{th})^2 = \frac{\beta}{2} (V_{DD} - V_{data})^2$$

20 [0045] Here, I<sub>OLED</sub> indicates a current flowing into the organic EL element OLED, V<sub>GS</sub> indicates a voltage between the source and the gate of the transistor M1, V<sub>th</sub> indicates a threshold voltage of the transistor M1, V<sub>data</sub> indicates a data voltage, and  $\beta$  indicates a constant.

25 [0046] When the data voltage V<sub>data</sub> is a red data signal, and the emit control transistor M2r is turned on in response to the low-level emit control signal transmitted from the emit control line E<sub>kr</sub>, the current I<sub>OLED</sub> is transmitted to the red organic EL element OLED<sub>r</sub> and the emission of red light occurs.

30 [0047] In the same manner, when the data voltage V<sub>data</sub> is a green data signal, and the emit control transistor M2g is turned on in response to the low-level emit control signal transmitted from the emit control line E<sub>kg</sub>, the current I<sub>OLED</sub> is transmitted to the green organic EL element OLED<sub>g</sub> and the emission of green light occurs. Further, when the data voltage V<sub>data</sub> is a blue data signal, and the emit control transistor M2b is turned on in response to the low-level emit control signal transmitted from the emit control line E<sub>kb</sub>, the current I<sub>OLED</sub> is transmitted to the blue organic EL element OLED<sub>b</sub> and the emission of blue light occurs. Three emit control signals that are applied to three emit control lines respectively have low level periods that are not overlapped with each other during one field, such that one pixel can display red, green, and blue colors.

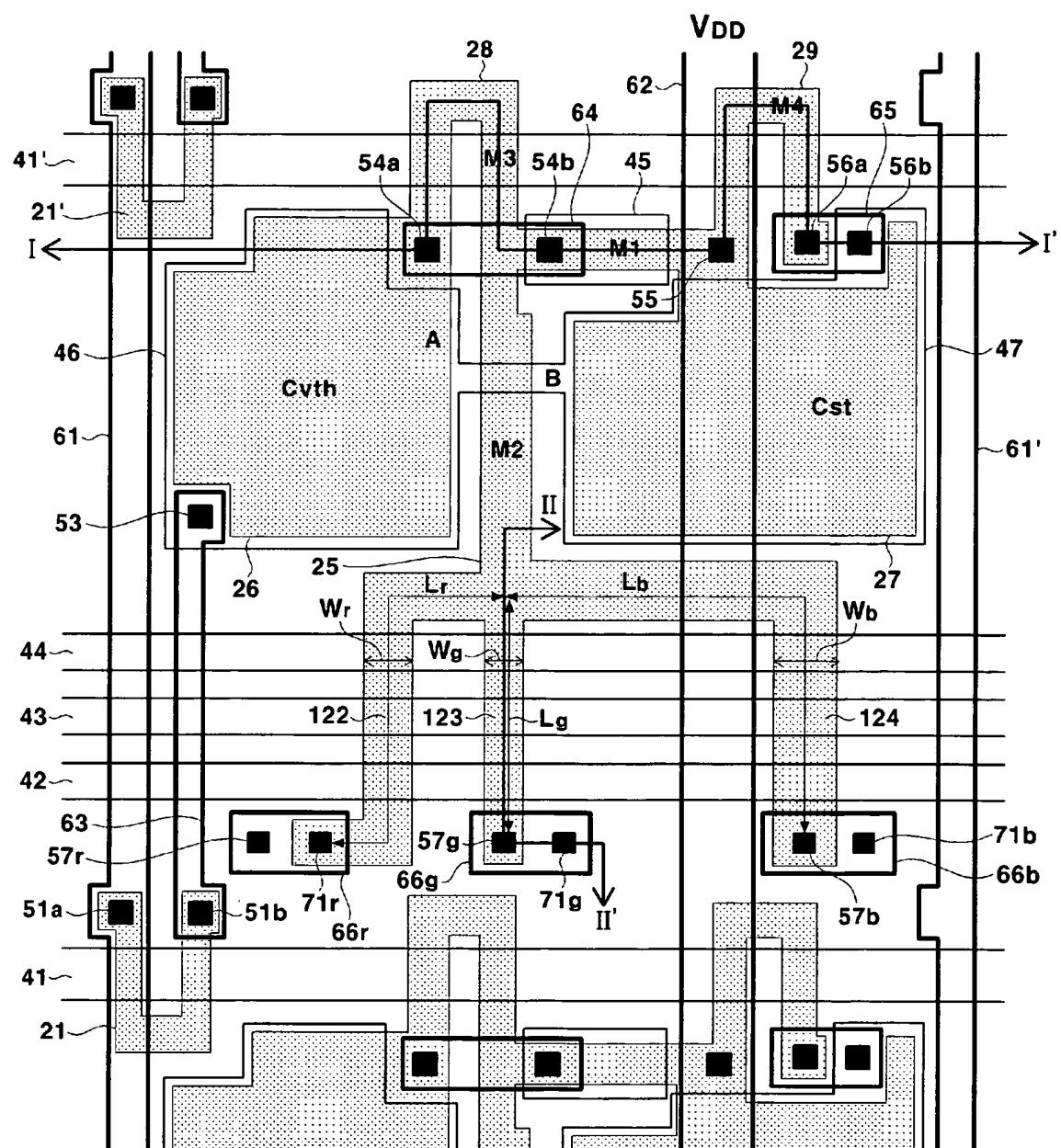

35 [0048] Next, in an organic EL display according to a first exemplary embodiment of the present invention, an arrangement structure in a pixel area where a pixel circuit is arranged is described in detail with reference to Fig. 4, Fig. 5, and Fig. 6. Here, reference numerals are provided to the components of the present pixel P<sub>k</sub>, and the same reference numerals are provided to the components of the previous pixel P<sub>k-1</sub>, except that an apostrophe symbol ("') is added to the reference numerals. The apostrophe symbol ("') is used to distinguish the components of the present pixel from the components of the previous pixel.

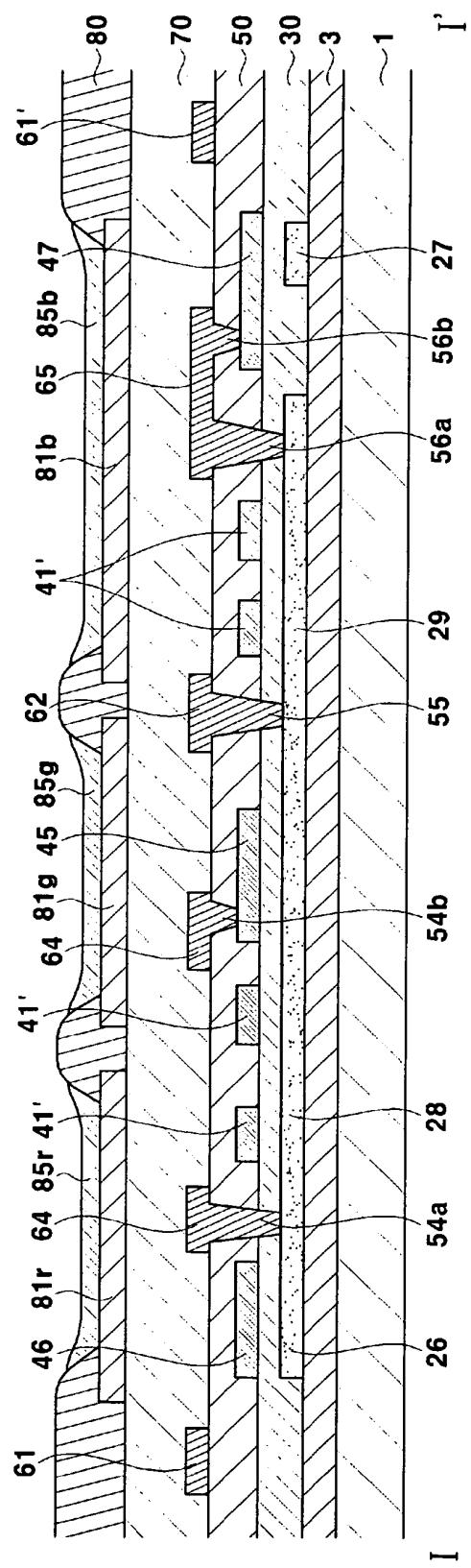

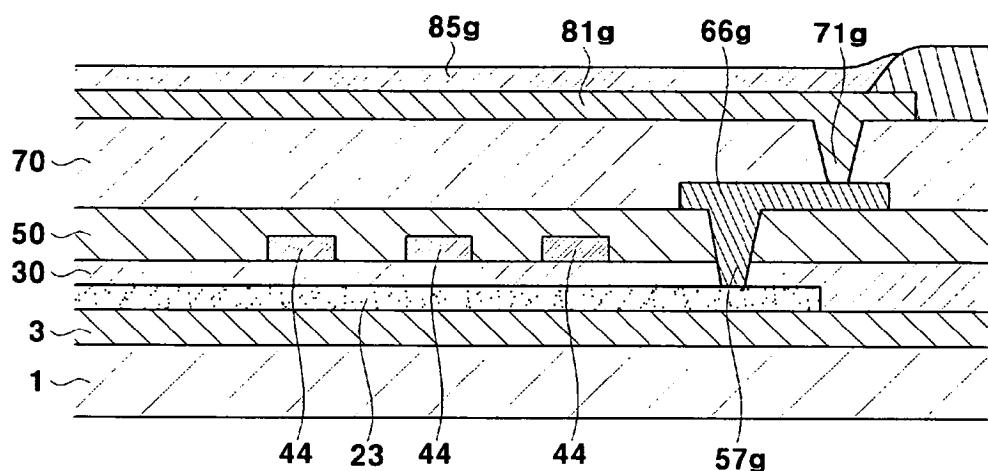

40 [0049] Fig. 4 is an arrangement diagram of a pixel area in which the pixel circuit shown in Fig. 3 is arranged, according to the first exemplary embodiment of the present invention. Fig. 5 is a cross-sectional view taken along I-I' in Fig. 4. Fig. 6 is a cross-sectional view taken along II-II' in Fig. 4.

45 [0050] First, as shown in Fig. 4, Fig. 5, and Fig. 6, a cut off layer 3 is formed on an insulated substrate 1. The cut off layer 3 is composed of material such as silicon oxide, or the like. Polysilicon layers 21, 22, 23, 24, 25, 26, 27, 28, and 29 that are semiconductor layers are formed on the cut off layer 3.

50 [0051] The polysilicon layer 21 forms a semiconductor layer including a source area, a drain area, and a channel area of the transistor M5 in the present pixel P<sub>k</sub>, of which shape resembles the letter 'U'. The polysilicon layer 22 forms a semiconductor layer including a source area, a drain area and a channel area of the transistor M2r in the present pixel

55 P<sub>k</sub>, of which shape resembles the shape . The polysilicon layer 23 forms a semiconductor layer including a source area, a drain area, and a channel area of the transistor M2g in the present pixel P<sub>k</sub>, which is arranged in the column direction. The polysilicon layer 24 forms a semiconductor layer including the source area, the drain area and the channel

55 area of the transistor M2b in the present pixel P<sub>k</sub>, of which shape resembles the shape . The polysilicon layers

22, 23, and 24 are coupled to form a shape of the letter 'm'. The polysilicon layer 22 is located at the left side of the polysilicon layer 23, and the polysilicon layer 24 is located at the right side of the polysilicon layer 23. The polysilicon layer 22 is generally symmetrical with the polysilicon layer 24 with respect to the polysilicon layer 23.

**[0052]** The polysilicon layer 25 is located at or about the middle of the pixel area and is arranged in the column direction, and the bottom end of the polysilicon layer 25 is coupled to the polysilicon layers 22, 23, and 24. The polysilicon layer 26 is located at the left side of the polysilicon layer 25, and the polysilicon layer 27 is located at the right side of the polysilicon layer 25. The polysilicon layer 26 is generally symmetrical with the polysilicon layer 27 with respect to the polysilicon layer 25. The polysilicon layer 26 generally has a shape of a square and forms a second electrode (node A) of the capacitor Cvth, and the polysilicon layer 27, which generally has a shape of a rectangle, forms a first electrode of the capacitor Cst. The polysilicon layer 28 has a shape of the letter 'n', and one end of the polysilicon layer 28 is coupled to the polysilicon layer 26 and other end of the polysilicon layer 28 is coupled to the polysilicon layer 25 and forms the source, drain, and channel area of the transistor M3. The polysilicon layer 29 has a shape of the letter 'n', and one end of the polysilicon layer 29 is coupled to the polysilicon layer 28 and forms the channel area and drain area of the transistor M1, and the source area, channel area, and drain area of the transistor M4.

**[0053]** A gate insulating film 30 is formed on the polysilicon layers 21 to 29.

**[0054]** The gates 41, 42, 43, 44, 45, 46, and 47 are formed on the gate insulating film 30. In detail, the gate line 41 is arranged in the row direction, and corresponds to the present scan line Sk of the present pixel Pk, and the gate line 41 is insulated and crosses the polysilicon layer 21 to form the gate of the transistor M5 in the present pixel Pk. The gate line 42 is arranged in the row direction, and corresponds to the emit control line Ekb in the present pixel Pk, to form the gate of the transistor M2b. The gate line 43 is arranged in the row direction, and corresponds to the emit control line Ekg of the present pixel Pk, to form the gate of the transistor M2g. The gate line 44 is arranged in the row direction, and corresponds to the emit control line Ekr of the present pixel Pk, to form the gate of the transistor M2r. The gate line 45 is insulated and crosses the polysilicon layer 26 to form the gate of the transistor M1. The gate 46, which generally has a shape of a square, is arranged on the polysilicon layer 26 to form the first electrode (node B) of the capacitor Cvth. The gate 47, which generally has a shape of a rectangle, is arranged on the polysilicon layer 27 to form the second electrode (node B) of the capacitor Cst.

**[0055]** The gate line 41' is arranged in the row direction; it corresponds to the previous scan line Sk-1 of the previous pixel Pk-1, and is insulated and crosses the polysilicon layer 21' to form the gate of the transistor M5 of the previous pixel Pk-1. Further, the gate line 41' is insulated and crosses the polysilicon layers 28 and 29 to form gates of the transistors M3 and M4 of the present pixel Pk.

**[0056]** The layer insulating film 50 is formed on the gates 41, 42, 43, 44, 45, 46, and 47. A data line 61, a power line 62, and electrodes 63, 64, 65, 66r, 66g, and 66b are formed on the layer insulating film 50, such that the data line 61, the power line 62, and the electrodes 63, 64, 65, 66r, 66g, and 66b are contacted to the corresponding electrodes through contact holes 51a, 51b, 53, 54a, 54b, 55, 56a, 56b, 57r, 57g, and 57b.

**[0057]** The data line 61 is arranged in the column direction between two pixel areas and is coupled to the polysilicon layer 21 through the contact hole 51a such that the data line 61 is coupled to the source of the transistor M5. The contact hole 51a passes through the layer insulating film 50 and the gate insulating film 30.

**[0058]** The power supply source line 62 is arranged in the column direction and is coupled to the polysilicon layers 27 and 29 through the contact hole 55 such that the power supply source line 62 supplies power to the first electrode of the capacitor Cst and the source of the transistor M1. The contact hole 55 passes through the layer insulating film 50 and the gate insulating film 30.

**[0059]** The electrode 63 is close to the data line 61, is substantially parallel with the data line 61, and couples the drain area of the polysilicon layer 21 to the gate 46 through the contact hole 51 b penetrating the layer insulating film 50 and the gate insulating film 30, and the contact hole 53 penetrating the layer insulating film 50. The electrode 63 becomes the node B.

**[0060]** The electrode 64 is close to the gate 41', is substantially parallel with the gate 41', and couples the drain area to the gate 45 of the transistor M3 in the polysilicon layer 28 through the contact hole 54a penetrating the layer insulating film 50 and the gate insulating film 30, and the contact hole 54b penetrating the layer insulating film 50. The electrode 64 becomes the node A.

**[0061]** The electrode 65, which substantially has a shape of a rectangle, is close to the gate 41' and couples the drain area to the gate 47 of the transistor M4 in the polysilicon layer 29 through the contact hole 56a penetrating the layer insulating film 50 and the gate insulating film 30, and the contact hole 56b penetrating the layer insulating film 50. The electrode 65 becomes the node B.

**[0062]** The electrodes 66r, 66g, and 66b respectively couple the pixel electrodes 81r, 81g, and 81b of each emit element to the drains of the transistors M2r, M2g, and M2b. In the electrodes 66r, 66g, and 66b, each of which substantially has a shape of a rectangle, their row directions are longer than their column directions. Here, the data line 62 is arranged in the column line, and the gates 42 to 44 are arranged in the row direction. The electrodes 66r, 66g, and 66b are respectively coupled to the polysilicon layers 22, 23, and 24 through the contact holes 57r, 57g, and 57b penetrating

the gate insulating film 30 and the layer insulating film 50, and are coupled to the drains of the transistors M2r, M2g, and M2b.

**[0063]** A flatting film 70 is formed on the electrodes 63, 64, 65, 66r, 66g, and 66b. The pixel electrodes 81r, 81g, and 81b are respectively coupled to the electrodes 66r, 66g, and 66b through the contact holes 71r, 71g, and 71b. In Fig. 5 and Fig. 6, the poly layer structure of red, green, and blue organic films 85r, 85g, and 85b including an emitting layer (EML), an electron transporting layer (ETL), and a hole transporting layer (HTL) are formed on the pixel electrodes 81r, 81g, and 81b.

**[0064]** As such, the polysilicon layers 22, 23, and 24 forming the emit control transistor are coupled to each other. The polysilicon layer 23 forms the emit control transistor M2g of the organic EL element located in the middle of the three organic EL elements. The polysilicon layer 22 forms the emit control transistor M2r of the organic EL element located in the left side of the three organic EL elements. The polysilicon layer 24 forms the emit control transistor M2b of the organic EL element located in the right side of the three organic EL elements. The polysilicon layer 22 is arranged generally symmetrically with the polysilicon layer 24 with respect to the polysilicon layer 23. Thus, the elements including the driving transistor M1 and n channel emit control transistors M2r, M2g, and M2b can be efficiently arranged at the pixel area, while the inner resistances of the polysilicon layers are substantially constantly maintained.

**[0065]** Next, the arrangement structure of the pixel area according to a second exemplary embodiment of the present invention is described in detail with reference to Fig. 7.

**[0066]** The second exemplary embodiment of the present invention is different from the first exemplary embodiment in that each of polysilicon layers 122, 123, and 124 for respectively forming emit control transistors M2r, M2g, and M2b, has a substantially constant ratio of length and width such that the emit control transistors M2r, M2g, and M2b have similar or substantially the same inner resistances. Hereinafter, the components of the second exemplary embodiment of FIG. 7 that are different from the corresponding components of the first exemplary embodiment of FIG. 4 will be described.

**[0067]** As shown in Fig. 7, the polysilicon layer 122 has length Lr and width Wr, the polysilicon layer 123 has length Lg and width Wg, and the polysilicon layer 124 has length Lb and width Wb.

**[0068]** Generally, the inner resistance of the polysilicon layer can be calculated as given in the following Equation 5.

### [Equation 5]

$$R = R_s \times \frac{L}{W}$$

**[0069]** Here, the R is the inner resistance of the polysilicon layer, L is the length of the polysilicon layer, that is, the sum of the lengths of the source area, the channel area, and the drain area, and W is the width of the polysilicon layer in a direction that is substantially perpendicular to the direction in which the length is measured. Further, Rs is a plane resistance, which is a resistance of the polysilicon layer having the unit width W and unit length L. By way of example, the plane resistance may have a value of  $5 \Omega/\text{plane}$ .

**[0070]** In this case, each inner resistance of each polysilicon layer 122, 123, and 124 depends on each of Lr/Wr, Lg/Wg, and Lb/Wb. Thus, the polysilicon layers 122, 123, and 124 have correlation such as given in the following Equation 6, such that the inner resistances R of each polysilicon layer 122, 123, and 124 have similar or substantially the same values.

### [Equation 6]

$$\frac{Lr}{Wr} = \frac{Lg}{Wg} = \frac{Lb}{Wb}$$

**[0071]** As such, the properties of the emit control transistors M2r, M2g, and M2b can be substantially constantly maintained by using the polysilicon layers 122, 123, and 124 having substantially the same ratio of (or between) the length and the width.

**[0072]** As such, the properties of the emit control transistors M2r, M2g and M2b can be established to be substantially the same as each other by using the polysilicon layers 122, 123, and 124 having substantially the same ratio of length

and width, such that the current  $I_{OLED}$  transmitted through the emit control transistors M2r, M2g, and M2b can be substantially constantly maintained.

[0073] According to exemplary embodiments of the present invention, when one pixel area includes three organic EL elements, and each emit control transistor is coupled between the drain of the driving transistor and the corresponding organic EL element, polysilicon layers forming the emit control transistors are coupled to be one body. Further, when the polysilicon layer forming the emit control transistor of the organic EL element which is located in the middle of the three organic EL elements, is located in the middle, the polysilicon layer which is located at the left side of the three organic EL elements is arranged generally symmetrically with the polysilicon layer which is located at the right side of the three organic EL elements with respect to the polysilicon layer which is located in the middle. Further, the emit control transistors can have substantially the same properties by using the polysilicon layers having substantially the same ratio of length and width.

[0074] As such, each element is more efficiently arranged at the small pixel area, while the inner resistances of the polysilicon layers forming the emit control transistors are substantially constantly maintained. Further, the emit control transistors have substantially the same current transmitting properties, and thus the current outputted from the driving transistor can be substantially stably transmitted to the corresponding emit elements.

[0075] While the present invention has been described in connection with certain exemplary embodiments, it is to be understood by those skilled in the art that the invention is not limited to the disclosed embodiments, but, on the contrary, is intended to cover various modifications and equivalent arrangements included within the scope of the appended claims.

## Claims

1. A display device comprising a plurality of scan lines for transmitting select signals, a plurality of data lines for transmitting data signals, and a plurality of pixel circuits coupled to the scan lines and the data lines, wherein each of the pixel circuits comprises:

a first capacitor (Cst) for charging a voltage which corresponds to one of the data signals transmitted from a corresponding one of the data lines (Dk);

a first transistor (M1) for outputting a current which corresponds to the voltage charged in the first capacitor (Cst), the first transistor having one of the source and the drain connected to a first power supply source (VDD); a second transistor (M3) coupled between a control electrode of the first transistor and the other one of the drain and the source of the first transistor, the control electrode of the second transistor being coupled to a first scan line (Sk-1);

a third transistor (M4) having a first one of the source and the drain coupled to a first electrode of the first capacitor (Cst) and to said first power supply source (VDD), a second one of the source and the drain coupled to a second electrode of the first capacitor (Cst), and the control electrode coupled to said first scan line (Sk-1); and a second capacitor (Cvth) having a first electrode coupled to the second one of the source and the drain of the third transistor (M4) and a second electrode coupled to the control electrode of the first transistor (M1);

a fourth transistor (M5) having a first one of the source and the drain coupled to said one of the data lines (Dk), the other one of the source and the drain coupled to the first electrode of the second capacitor (Cvth), and the control electrode coupled to a second scan line (Sk);

the pixel circuit being further **characterised by**:

first, second, and third emit elements (OLEDr, OLEDb, OLEDg) for emitting a light corresponding to the current outputted from the first transistor (M1), the first, second, and third emit elements each having a first electrode coupled to a second power source (Vss); and

first, second, and third emit control transistors (M2r, M2b, M2g) respectively coupled between said other one of the drain and the source of the first transistor and the second electrode of the corresponding one of the first, second, and third emit elements (OLEDr, OLEDb, OLEDg), the control electrodes of the first, second, and third emit transistors (M2r, M2b, M2g) being coupled to emit control lines (Ekr, Ekb, Ekg),

wherein the first semiconductor layer forming the first emit control transistor (M2r) is arranged generally symmetrically with the second semiconductor layer forming the second emit control transistor (M2b) with respect to the third semiconductor layer forming the third emit control transistor (M2g).

2. The display device of claim 1, wherein at least two semiconductor layers among the first, second, and third semiconductor layers are substantially parallel to each other.

3. The display device of claim 2, wherein the first, second, and third semiconductor layers forming the first, second, and third emit elements (OLED<sub>r</sub>, OLED<sub>g</sub>, OLED<sub>b</sub>) are doped with the same type of impurities.

5 **Patentansprüche**

1. Eine Anzeigevorrichtung, umfassend eine Vielzahl von Abtastleitungen zum Übertragen von Auswahlsignalen, eine Vielzahl von Datenleitungen zum Übertragen von Datensignalen sowie eine Vielzahl von mit den Abtastleitungen und den Datenleitungen verbundenen Pixelschaltungen, wobei

10 jede der Pixelschaltungen umfasst:

15 einen ersten Kondensator (Cst) zum Laden einer Spannung, die einem der von einer entsprechenden der Datenleitungen (Dk) übertragenen Datensignale entspricht;

20 einen ersten Transistor (M1) zum Ausgeben eines Stroms, der der in dem ersten Kondensator (Cst) geladenen Spannung entspricht, wobei bei dem ersten Transistor ein aus der Source und dem Drain Gewähltes mit einer ersten Stromversorgungsquelle (VDD) verbunden ist;

25 einen zwischen einer Steuerelektrode des ersten Transistors und dem Verbleibenden aus dem Drain und der Source des ersten Transistors geschalteten zweiten Transistor (M3), wobei die Steuerelektrode des zweiten Transistors mit einer ersten Abtastleitung (Sk-1) verbunden ist;

30 einen dritten Transistor (M4), bei dem ein erstes aus der Source und dem Drain Gewähltes mit einer ersten Elektrode des ersten Kondensators (Cst) und mit besagter erster Stromversorgungsquelle (VDD) verbunden ist, ein zweites aus der Source und dem Drain Gewähltes mit einer zweiten Elektrode des ersten Kondensators (Cst) verbunden ist und die Steuerelektrode mit besagter erster Abtastleitung (Sk-1) verbunden ist; und

35 einen zweiten Kondensator (Cvth), bei dem eine erste Elektrode mit dem zweiten aus der Source und dem Drain Gewählten des dritten Transistors (M4) verbunden ist und eine zweite Elektrode mit der Steuerelektrode des ersten Transistors (M1) verbunden ist;

40 einen vierten Transistor (M5), bei dem ein erstes aus der Source und dem Drain Gewähltes mit besagter einer der Datenleitungen (Dk) verbunden ist, das Verbleibende aus der Source und dem Drain mit der ersten Elektrode des zweiten Kondensators (Cvth) verbunden ist und die Steuerelektrode mit einer zweiten Abtastleitung (Sk) verbunden ist;

45 wobei die Pixelschaltung ferner **gekennzeichnet ist durch:**

50 erste, zweite und dritte Emissionselemente (OLED<sub>r</sub>, OLED<sub>b</sub>, OLED<sub>g</sub>) zum Emissieren eines dem von dem ersten Transistor (M1) ausgegebenen Strom entsprechenden Lichts, wobei bei jedem der ersten, zweiten und dritten Emissionselemente eine erste Elektrode mit einer zweiten Stromquelle (Vss) verbunden ist; und

55 jeweils zwischen besagtes Verbleibende aus dem Drain und der Source des ersten Transistors und die zweite Elektrode des entsprechenden der ersten, zweiten und dritten Emissionselemente (OLED<sub>r</sub>, OLED<sub>b</sub>, OLED<sub>g</sub>) geschaltete erste, zweite und dritte Emissionssteuertransistoren (M2r, M2b, M2g), wobei die Steuerelektroden der ersten, zweiten und dritten Emissionstransistoren (M2r, M2b, M2g) mit Emissionssteuerleitungen (Ekr, Ekb, Ekg) verbunden sind,

60 wobei die erste, den ersten Emissionssteuertransistor (M2r) bildende Halbleiterschicht mit der zweiten, den zweiten Emissionssteuertransistor (M2b) bildenden Halbleiterschicht bezüglich der dritten, den dritten Emissionssteuertransistor (M2g) bildenden Halbleiterschicht allgemein symmetrisch angeordnet ist.

65 2. Die Anzeigevorrichtung nach Anspruch 1, wobei mindestens zwei Halbleiterschichten von den ersten, zweiten und dritten Halbleiterschichten im Wesentlichen parallel zueinander liegen.

70 3. Die Anzeigevorrichtung nach Anspruch 2, wobei die die ersten, zweiten und dritten Emissionselemente (OLED<sub>r</sub>, OLED<sub>g</sub>, OLED<sub>b</sub>) bildenden ersten, zweiten und dritten Halbleiterschichten mit derselben Art von Fremdatomen dotiert sind.

75 **Revendications**

1. Dispositif d'affichage comportant de multiples lignes de balayage pour la transmission de signaux de sélection, de multiples lignes de données pour la transmission de signaux de données et de multiples circuits de pixels couplés

aux lignes de balayage et aux lignes de données, dans lequel :

chacun des circuits de pixels comporte :

- 5        un premier condensateur (Cst) destiné à charger une tension qui correspond à l'un des signaux de données transmis depuis une, correspondante, des lignes de données (Dk) ;

- 10      un premier transistor (M1) destiné à délivrer en sortie un courant qui correspond à la tension chargée dans le premier condensateur (Cst), le premier transistor ayant l'un de la source et du drain connecté à une première source d'alimentation en énergie (VDD) ;

- 15      un deuxième transistor (M3) couplé entre une électrode de commande du premier transistor et l'autre du drain et de la source du premier transistor, l'électrode de commande du second transistor étant couplée à une première ligne de balayage (Sk-1) ;

- 20      un troisième transistor (M4) ayant un premier de la source et du drain couplé à une première électrode du premier condensateur (Cst) et à ladite première source d'alimentation en énergie (VDD), un second de la source et du drain couplé à une seconde électrode du premier condensateur (Cst), et la seconde électrode couplée à ladite première ligne de balayage (Sk-1) ; et

- 25      un second condensateur (Cvth) ayant une première électrode couplée au second de la source et du drain du troisième transistor (M4) et une seconde électrode couplée à l'électrode de commande du premier transistor (M1) ;

- 30      un quatrième transistor (M5) ayant un premier de la source et du drain couplé à ladite une des lignes de données (Dk), l'autre de la source et du drain couplé à la première électrode du second condensateur (Cvth), et l'électrode de commande couplée à une deuxième ligne de balayage (Sk) ;

le circuit de pixel étant en outre **caractérisé par** :

- 25      des premier, deuxième et troisième éléments d'émission (OLEDr, OLED<sub>b</sub>, OLED<sub>g</sub>) pour l'émission d'une lumière correspondant au courant délivré en sortie du premier transistor (M1), les premier, deuxième et troisième éléments d'émission ayant chacun une première électrode couplée à une seconde source d'énergie (Vss) ; et

- 30      des premier, deuxième et troisième transistors de commande d'émission (M2r, M2b, M2g) couplés respectivement entre ledit autre du drain et de la source du premier transistor et la seconde électrode de l'un, correspondant, des premier, deuxième et troisième éléments d'émission (OLEDr, OLED<sub>b</sub>, OLED<sub>g</sub>), les électrodes de commande des premier, deuxième et troisième transistors d'émission (M2r, M2b, M2g) étant couplées à des lignes (Ekr, Ekb, Ekg) de commande d'émission,

35      dans lequel la première couche de semiconducteur formant le premier transistor de commande d'émission (M2r) est agencée globalement symétriquement avec la deuxième couche de semiconducteur formant le deuxième transistor (M2b) de commande d'émission par rapport à la troisième couche de semiconducteur formant le troisième transistor (M2g) de commande d'émission.

- 40      2. Dispositif d'affichage selon la revendication 1, dans lequel au moins deux couches de semiconducteurs parmi les première, deuxième et troisième couches de semiconducteurs sont sensiblement parallèles entre elles.

- 45      3. Dispositif d'affichage selon la revendication 2, dans lequel les première, deuxième et troisième couches de semiconducteurs formant les premier, deuxième et troisième éléments d'émission (OLEDr, OLED<sub>g</sub>, OLED<sub>b</sub>) sont dopées avec le même type d'impuretés.

50

55

FIG.1

(Prior Art)

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6

FIG. 7

**REFERENCES CITED IN THE DESCRIPTION**

*This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.*

**Patent documents cited in the description**

- EP 0762374 A [0015]

- US 6618031 B1 [0016]

**Non-patent literature cited in the description**

- **N. KOMIYA et al.** Comparison of Vth compensation ability among voltage programming circuits for AMOLED panels. *IDW International Display Workshops Technical Digest*, 2003, 275 [0017]

|                |                                                                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于在时间复用模式下驱动OLED彩色显示器中的子像素的像素驱动电路                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">EP1594118B1</a>                                                                                                                                              | 公开(公告)日 | 2008-08-27 |

| 申请号            | EP2005103365                                                                                                                                                             | 申请日     | 2005-04-26 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 三星SDI CO. , LTD.                                                                                                                                                         |         |            |

| 当前申请(专利权)人(译)  | 三星SDI CO. , LTD.                                                                                                                                                         |         |            |

| [标]发明人         | KWAK WON KYU C O SAMSUNG SDI CO LTD                                                                                                                                      |         |            |

| 发明人            | KWAK, WON-KYU, C/O SAMSUNG SDI CO., LTD.                                                                                                                                 |         |            |

| IPC分类号         | G09G3/32 H01L51/50 G09F9/30 H01L21/336 H01L27/32 H01L29/786                                                                                                              |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0804 G09G2300/0814 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2310/0235 G09G2310/0262 G09G2320/043 H01L27/3211 H01L27/326 H01L27/3262 H01L27/3265 |         |            |

| 代理机构(译)        | hengelhaupt , Jürgen                                                                                                                                                     |         |            |

| 优先权            | 1020040029944 2004-04-29 KR<br>1020040029945 2004-04-29 KR                                                                                                               |         |            |

| 其他公开文献         | EP1594118A1                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                |         |            |

### 摘要(译)

一种显示装置，具有有效排列在像素中的组件。像素电路包括用于对与从数据线传输的数据信号对应的电压充电的电容器。像素电路的第一晶体管输出对应于电容器中充电的电压的电流。多个发光元件发出与从驱动晶体管输出的电流对应的光。多个发射控制晶体管耦合在第一晶体管和多个发光元件之间。发射控制晶体管包括多个半导体层，所述多个半导体层具有彼此基本相同的内部电阻。

Equation 1

$$I_{OLED} = \frac{\beta}{2} (V_{GS} - V_{TH})^2 = \frac{\beta}{2} (V_{DD} - V_{DATA} - |V_{TH}|)^2$$