(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

19 February 2009 (19.02.2009)

PCT

(10) International Publication Number

WO 2009/022563 A1

## (51) International Patent Classification:

*G09G 3/30* (2006.01) *H01L 51/50* (2006.01)

*G09G 3/20* (2006.01)

30-2, Shimomaruko 3-chome, Ohta-ku, Tokyo, 1468501 (JP). **HAYASHI, Ryo** [JP/JP]; c/o CANON KABUSHIKI KAISHA, 30-2, Shimomaruko 3-chome, Ohta-ku, Tokyo, 1468501 (JP).

## (21) International Application Number:

PCT/JP2008/063932

(74) Agents: **OKABE, Masao** et al.; No. 602, Fuji Bldg., 2-3, Marunouchi 3-chome, Chiyoda-ku, Tokyo 1000005 (JP).

## (22) International Filing Date:

29 July 2008 (29.07.2008)

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

## (25) Filing Language:

English

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM,

## (26) Publication Language:

English

## (30) Priority Data:

2007-209984 10 August 2007 (10.08.2007) JP

*[Continued on next page]*

(71) Applicant (for all designated States except US): **CANON KABUSHIKI KAISHA** [JP/JP]; 30-2, Shimomaruko 3-chome, Ohta-ku, Tokyo, 1468501 (JP).

## (72) Inventors; and

(75) Inventors/Applicants (for US only): **SHIMIZU, Hisae** [JP/JP]; c/o CANON KABUSHIKI KAISHA, 30-2, Shimomaruko 3-chome, Ohta-ku, Tokyo, 1468501 (JP). **ABE, Katsumi** [JP/JP]; c/o CANON KABUSHIKI KAISHA,

(54) Title: THIN FILM TRANSISTOR CIRCUIT, LIGHT EMITTING DISPLAY APPARATUS, AND DRIVING METHOD THEREOF

FIG. 8

(57) Abstract: In order to suppress an influence of an electrical stress on a TFT characteristic in use of a TFT, a light emitting display apparatus according to the present invention comprises organic EL devices and driving circuits for driving the organic EL devices. The driving circuit includes plural pixels each having a thin film transistor of which a threshold voltage reversibly changes due to the electrical stress applied between a gate terminal and a source terminal, and a voltage applying unit which sets gate potential of the thin film transistor higher than source potential. The voltage applying unit applies the electrical stress between the gate terminal and the source terminal at a time when the thin film transistor is not driven, so as to drive the thin film transistor in a region that the threshold voltage is saturated to the electrical stress.

ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

— *with international search report*

## DESCRIPTION

THIN FILM TRANSISTOR CIRCUIT, LIGHT EMITTING DISPLAY

APPARATUS, AND DRIVING METHOD THEREOF

5

## TECHNICAL FIELD

The present invention relates to a thin film transistor circuit, a light emitting display apparatus, and the driving methods thereof. In particular, the 10 light emitting display apparatus and the driving method thereof according to the present invention are suitably used respectively for a light emitting display apparatus which includes, like a matrix, pixels each composed of a light emitting device and a driving 15 circuit for supplying current to the light emitting device, and for the driving method thereof. Here, it should be noted that, for example, an organic electroluminescence (EL) device can be used as the 20 light emitting device.

20

## BACKGROUND ART

Recently, an organic EL display using an organic EL device as a light emitting device has been studied and developed. In the organic EL display like this, an 25 active-matrix (AM) organic EL display in which a driving circuit is provided in each pixel is generally used to extend the life span of the organic EL device

and achieve high-quality image.. The relevant driving circuit is constituted by a thin film transistor (TFT) formed on a substrate such as glass, plastic or the like. In the organic EL display, the substrate and the 5 driving circuit portion are together called a back plane.

As the TFT of the back plane for the organic EL display, amorphous silicon (called a-Si hereinafter), polycrystal silicon (called p-Si hereinafter), or the 10 like have been studied. In addition, a TFT in which an amorphous oxide semiconductor (called an AOS hereinafter) is used as its channel layer has newly been proposed recently. Here, for example, amorphous In(indium)-Ga(gallium)-Zn(zinc)-O(oxide) (called a-IGZO 15 hereinafter) is used as the material of the AOS. Besides, for example, amorphous Zn(zinc)-In(indium)-O(oxide) (called a-ZIO hereinafter) is used as the material of the AOS. It is conceivable that the TFT in which the AOS is used as its channel layer has mobility 20 which is ten times or more as much as that of an a-Si TFT and also has high uniformity which is caused by amorphousness. Therefore, the TFT in which the AOS is used as its channel layer is promising as the TFT of the back plane for the display. The TFT in which the 25 AOS is used as its channel layer is disclosed in, for example, "Nomura, et al., Room-Temperature Fabrication of Transparent Flexible Thin Film Transistors using

Amorphous Oxide Semiconductors, *Nature*, vol. 432, pp. 488-492 (2004)" and "Yabuta, et al., High-Mobility Thin-Film Transistor with Amorphous InGaZnO<sub>4</sub> Channel Fabricated by Room Temperature RF-magnetron Sputtering, 5 *Appl. Phys. Lett. (APL)*, 89, 112123 (2006)".

In any case, there are several problems in case of achieving high-quality display by an active matrix (AM) organic EL display. More specifically, (1) a voltage-luminance characteristic of an organic EL 10 device changes over time, (2) a characteristic of a TFT being the constituent element of a driving circuit varies from others, and (3) the characteristic of the TFT changes due to an electrical stress.

Here, in a case where an AOS-TFT is used for the 15 driving circuit, the above problems (1) and (2) can be improved because uniformity of the AOS-TFTs is high and a driving circuit for controlling the currents supplied from the AOS-TFT to the organic EL device is employed.

On the other hand, since the characteristic of 20 the AOS-TFT changes due to the electrical stress, the above problem (3) still remains.

#### DISCLOSURE OF THE INVENTION

The present invention aims to suppress 25 deterioration of display quality according to a characteristic change of a TFT due to an electrical stress.

A driving method of the present invention, of a thin film transistor circuit which includes a thin film transistor of which a threshold voltage changes due to an electrical stress applied between a gate terminal and a source terminal, is characterized by comprising: applying the electrical stress between the gate terminal and the source terminal at a time when the thin film transistor is not driven, so as to drive the thin film transistor in a region that the threshold voltage is saturated to the electrical stress.

Further, a driving method of the present invention, of a light emitting display apparatus which includes plural pixels each having a light emitting device and a driving circuit for driving the light emitting device, is characterized in that the driving circuit includes at least one thin film transistor of which a threshold voltage reversibly changes due to an electrical stress applied between a gate terminal and a source terminal, and the driving method comprises applying the electrical stress between the gate terminal and the source terminal of the thin film transistor in a non-displaying period of the light emitting display apparatus, so as to drive the thin film transistor in a region that the threshold voltage is saturated to the electrical stress.

Furthermore, a thin film transistor circuit, of the present invention, which includes a thin film

transistor of which a threshold voltage reversibly changes due to an electrical stress applied between a gate terminal and a source terminal, and a voltage applying unit to apply voltage between the gate 5 terminal and the source terminal of the thin film transistor as the electrical stress, is characterized in that the voltage applying unit applies the electrical stress between the gate terminal and the source terminal at a time when the thin film transistor 10 is not driven, so as to drive the thin film transistor in a region that the threshold voltage is saturated to the electrical stress.

Furthermore, a light emitting display apparatus, of the present invention, which includes plural pixels 15 each having a light emitting device and a driving circuit for driving the light emitting device, is characterized in that: the driving circuit includes a thin film transistor of which a threshold voltage reversibly changes due to an electrical stress applied 20 between a gate terminal and a source terminal, and a voltage applying unit to apply voltage between the gate terminal and the source terminal of the thin film transistor as the electrical stress; and the voltage applying unit applies the electrical stress between the 25 gate terminal and the source terminal of the thin film transistor in a non-displaying period of the light emitting display apparatus, so as to drive the thin

film transistor in a region that the threshold voltage is saturated to the electrical stress.

According to the present invention, since it is possible to use the thin film transistor (TFT) in the 5 region that the threshold voltage is saturated to the electrical stress, it is possible to suppress an influence of a characteristic change of the TFT due to the electrical stress.

Further features of the present invention will 10 become apparent from the following description of exemplary embodiments with reference to the attached drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

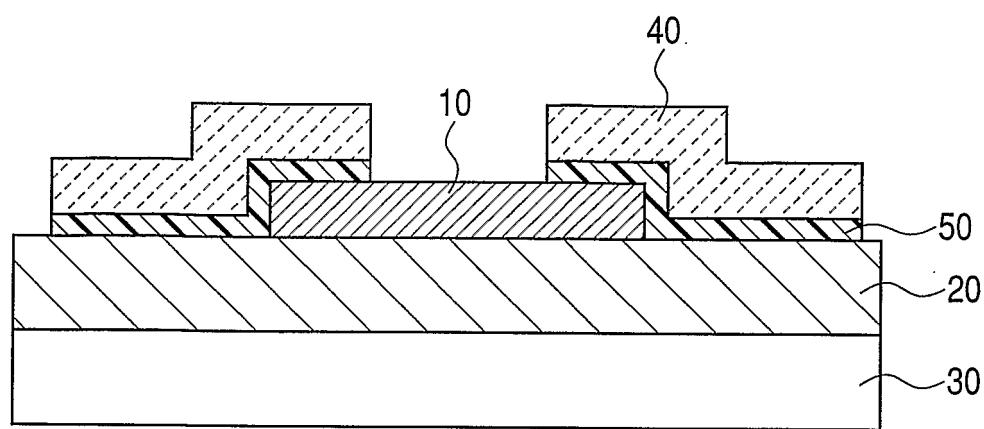

15 FIG. 1 is a view indicating the constitution 1 (on Si substrate) of an a-IGZO TFT in the Embodiment 1 of the present invention.

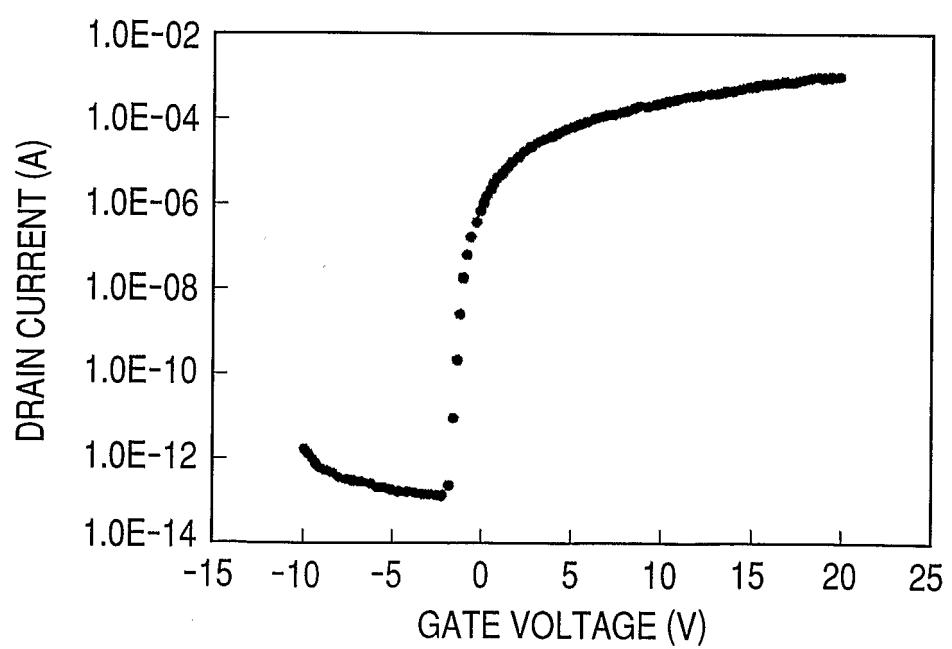

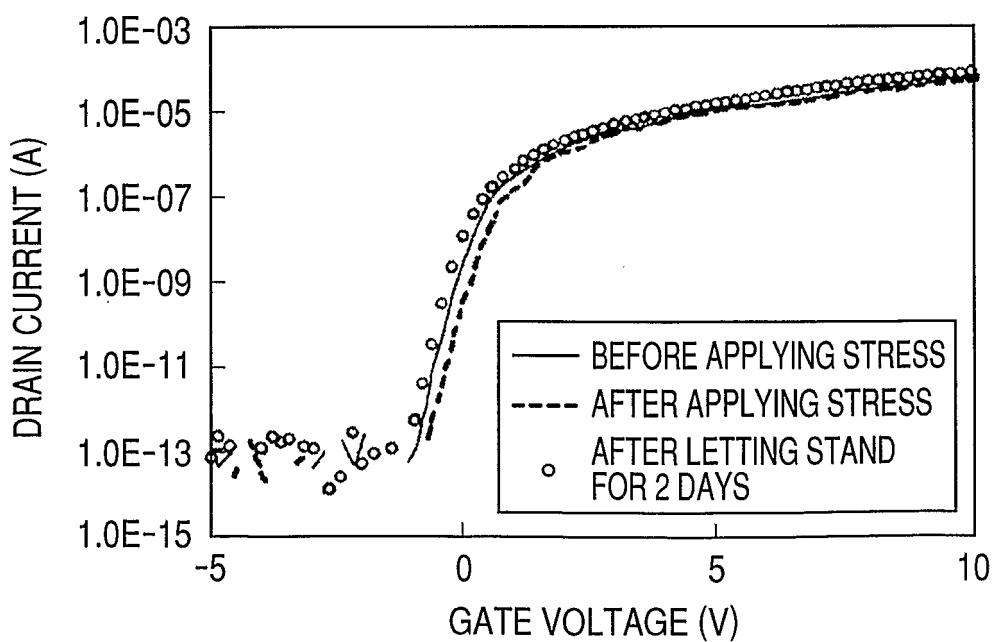

20 FIG. 2 is a view indicating an Id-Vg (drain current versus gate voltage) characteristic of the constitution 1 of the a-IGZO TFT in the Embodiment 1 of the present invention.

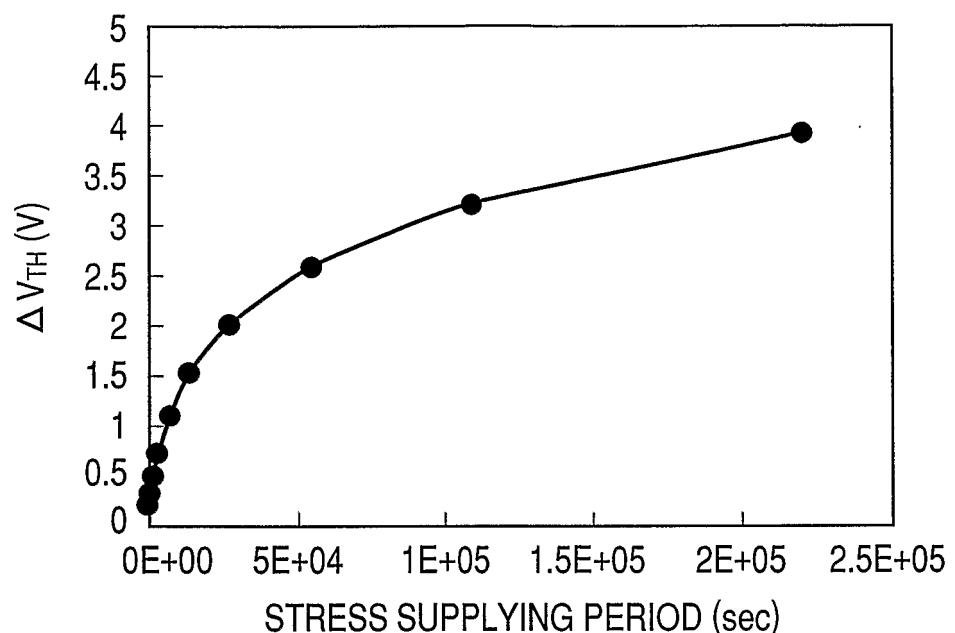

FIG. 3 is a view indicating the threshold change by the electric stress of the constitution 1 of the a-IGZO TFT in the Embodiment 1 of the present invention.

25 FIG. 4 is a view indicating the recovery characteristic of the recovery from the changed situation of the constitution 1 of the a-IGZO TFT in

the Embodiment 1 of the present invention.

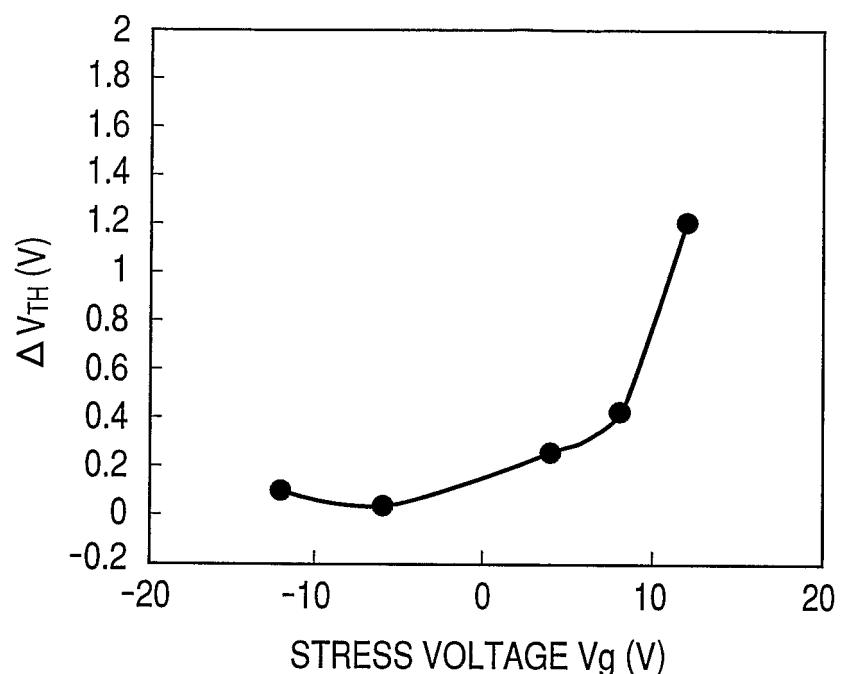

FIG. 5 is a view indicating the gate voltage dependency of the stress change of the constitution 1 of the a-IGZO TFT in the Embodiment 1 of the present invention.

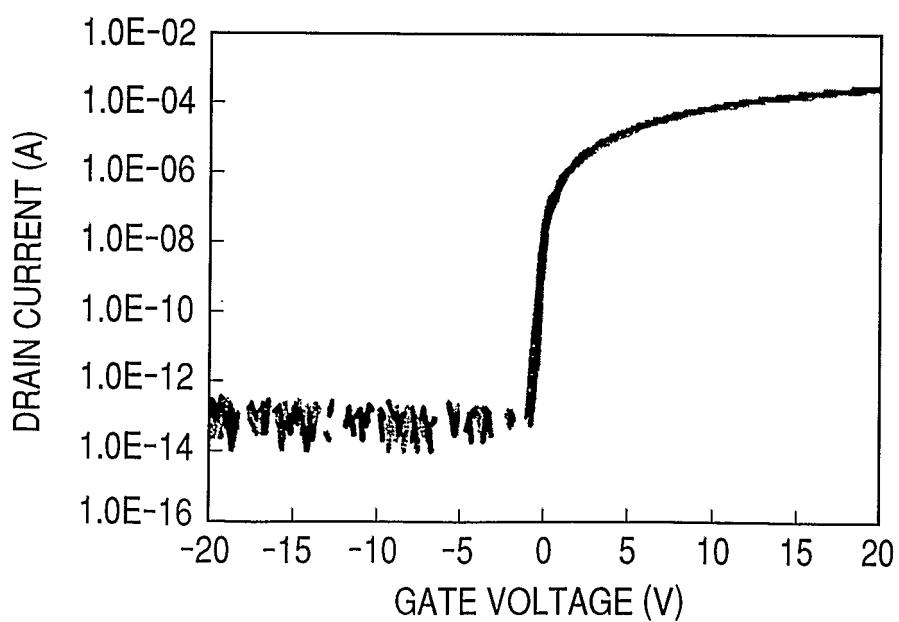

FIG. 6 is a view indicating the plural  $Id$ - $Vg$  characteristics of the constitution 1 of the a-IGZO TFT in the Embodiment 1 of the present invention.

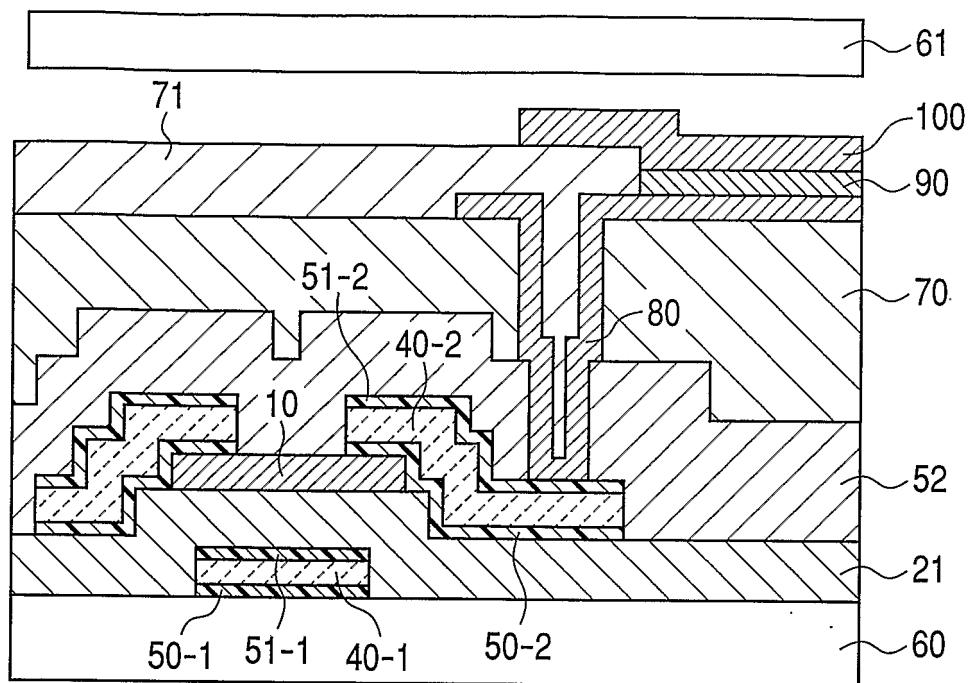

FIG. 7 is a view indicating the constitution 2 (on glass substrate) of the a-IGZO TFT in the Embodiment 1 of the present invention.

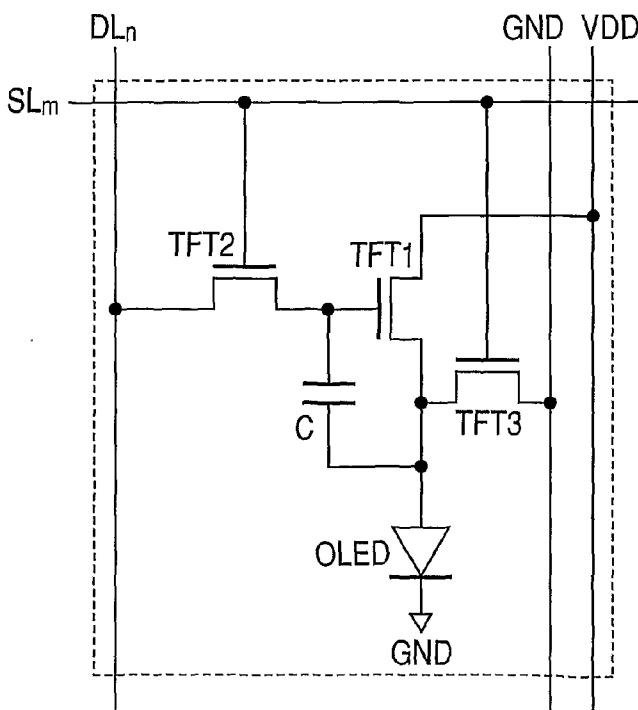

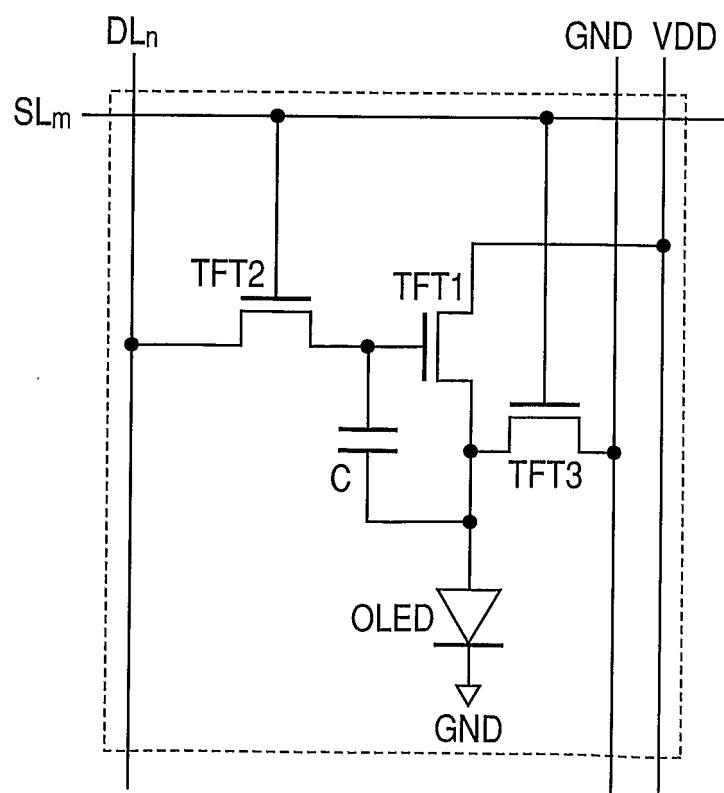

FIG. 8 is a view indicating a pixel circuit in the Embodiment 1 of the present invention.

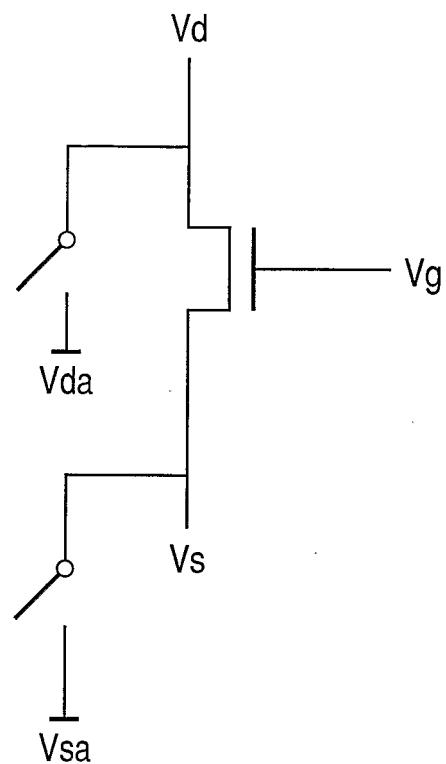

FIG. 9 is a circuit diagram indicating a case that the voltage is applied so as to lower drain and source potentials to a gate potential in a thin film transistor.

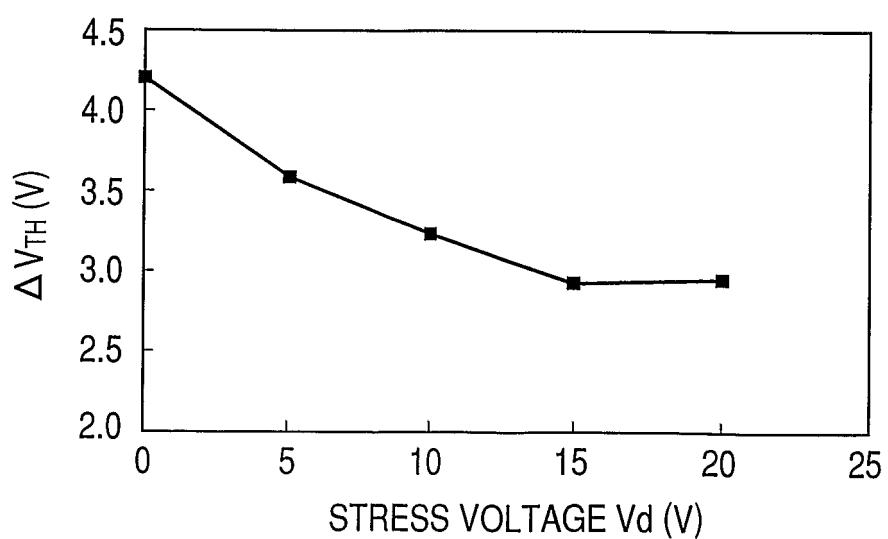

FIG. 10 is a view indicating the change of threshold voltage in case of changing the drain voltage.

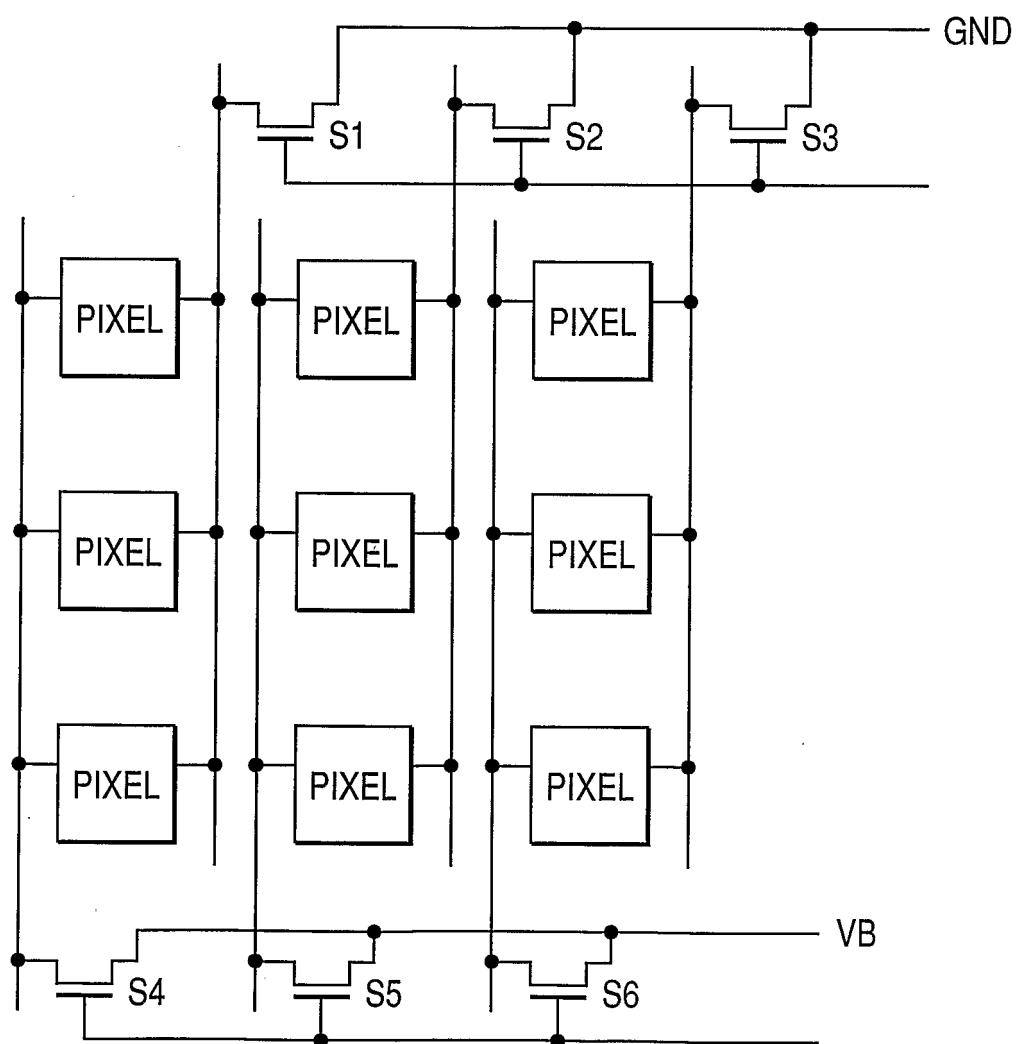

FIG. 11 is a view indicating a pixel region of an organic EL display apparatus of the present embodiment.

#### BEST MODE FOR CARRYING OUT THE INVENTION

The present inventors obtained the following knowledge by advancing an evaluation of an AOS-TFT (amorphous oxide semiconductor - thin film transistor).

That is, although the AOS-TFT has such a property

of shifting threshold voltage by the electrical stress, the shift of this threshold voltage tends to be temporally saturated. The shift of the threshold voltage appears in a case that a gate potential is 5 higher than a source potential. With respect to the shift of the threshold voltage of the AOS-TFT, there is such a property of returning to a condition before applying the electrical stress by eliminating the electrical stress and leaving the AOS-TFT for a certain 10 period. That is, the AOS-TFT according to the present invention has been proposed on the basis of a property that the threshold voltage of the AOS-TFT reversibly changes by applying and eliminating the electrical stress. Note that the present invention can be applied 15 to a TFT, of which the threshold voltage is changed by the electrical stress to be applied between a gate terminal and a source terminal, and is not limited to the AOS-TFT.

Hereinafter, as the embodiments of the present 20 invention, a description will be given about an organic EL display apparatus (serving as a light emitting display apparatus), where a driver circuit has the AOS-TFT in which an a-IGZO is treated as a channel layer and organic EL devices serve as light emitting devices.

25 However, the present invention can be also applied to a light emitting display apparatus, where the AOS other than the a-IGZO is treated as a

semiconductor, or a light emitting display apparatus, where light emitting devices other than the organic EL devices, for example, inorganic EL devices are used. In addition, the present invention can be widely used 5 to thin film transistor circuits having TFTs of using amorphous oxide semiconductors as channel layers.

A thin film transistor circuit of the present invention has a thin film transistor, of which the threshold voltage is changed by the electrical stress 10 to be applied between the gate terminal and the source terminal, and a voltage applying unit, which applies the voltage between the gate terminal and the source terminal of the thin film transistor as the electrical stress. The voltage applying unit applies the 15 electrical stress between the gate terminal and the source terminal when the thin film transistor is not driven so as to drive the thin film transistor in a region that the threshold voltage is saturated to the electrical stress. Specifically, the voltage is 20 applied between the gate terminal and the source terminal such that the gate potential becomes higher than the source potential in the thin film transistor. When the electrical stress is applied, the gate potential may be set to become equal to or higher than 25 a drain potential in the thin film transistor.

The voltage may be applied to the source terminal of the thin film transistor so as to lower to the gate

potential. FIG. 9 is a circuit diagram indicating a case that the voltage is applied so as to lower the drain and source potentials to the gate potential in the thin film transistor. The voltage applying unit is 5 constituted from two switches and two power sources  $V_{sa}$  and  $V_{da}$ . At a time point of ordinarily using the thin film transistor, a voltage  $V_g$  is applied to the gate terminal, a voltage  $V_d$  is applied to the drain terminal and a voltage  $V_s$  is applied to the source terminal. At 10 a time point before using the thin film transistor, the gate potential  $V_g$  can be kept higher than the source potential  $V_s$  by switching on the power source  $V_{sa}$  at a source terminal side and applying the voltage  $V_s$  ( $V_g > V_s$ ) to the source terminal with a state of applying the 15 voltage  $V_g$  to the gate terminal. In this case, the voltage  $V_d$  may be applied to the drain terminal (it assumed that  $V_g > V_d$  or  $V_g = V_d$ ) upon switching on the power source  $V_{da}$  at a drain terminal side.

As an AM device of using the AOS-TFT other than 20 the light emitting display apparatus, it can be applied to, for example, a pressure sensor of using a pressure-sensitive device or an optical sensor of using a photosensitive device, and the similar effect can be obtained.

25 An amorphous described in the present invention is defined in that an obvious peak is not observed in an X-ray diffraction.

The organic EL display apparatus of the present invention has plural pixels having organic EL devices and driver circuits for driving the organic EL devices. A driver a-IGZO TFT for controlling a current to be supplied to the organic EL device and one or plural switches of changing the connection of the driver TFT are at least provided in the driver circuit. In addition, in a displaying period, the driver TFT operates in a region that the threshold voltage is saturated to the electrical stress. In the present embodiment, the region that the threshold voltage is saturated means a region that a change rate of the threshold voltage of a thin film transistor to the electrical stress is in a small level. Here, the region that a change rate of the threshold voltage is in a small level means a region that the change of the threshold voltage to the electrical stress does not influence the driving of the thin film transistor.

In the organic EL display apparatus of the present embodiment, a high level voltage is applied to the gate terminal and a low level voltage is applied to the source and drain terminals in the driver TFT by turning on and off a switch during a non-light emitting period, for example, in a case that a switch of the display is turned off. According to this operation, since the electrical stress is continuously applied to the driver TFT, the driver TFT can maintain a saturated

region without recovering the shift of the threshold voltage. With respect to application of the electrical stress, the voltage may be continuously or intermittently (for example, plural-time pulses) applied.

Thereafter, if a displaying operation is performed again, the driver TFT is to operate in a region that the threshold voltage is saturated. Therefore, in the organic EL display apparatus of the present embodiment, the shift of the threshold voltage to the electrical stress in the TFT can be reduced to a small level, and the deterioration of display quality can be suppressed.

In addition, it is preferable that the organic EL display apparatus of the present invention performs an operation of applying the voltage to the driver TFT by the time at least 48 hours before starting to use the display apparatus and more preferably by the time 24 hours before starting to use the display apparatus after the display apparatus was fabricated. By performing the present operation, the driver TFT can be operated in a region that the threshold voltage is saturated to the electrical stress from the time of starting to use the display apparatus.

In addition, it is more preferable that the organic EL display apparatus of the present embodiment equips an accessory battery. By equipping the

accessory battery, even if in a case that the display apparatus is not connected to an external power source in moving, an operation of applying the electrical stress can be performed. Since an operation of 5 applying the voltage to the driver TFT does not almost require the current supply, the power consumption in operating results in a little consumption.

(Embodiment 1)

First, the characteristic of a TFT, in which the 10 a-IGZO to be used in the present embodiment is treated as a channel layer, will be described.

A fabricating method of the a-IGZO TFT will be indicated as below.

As indicated in FIG. 1, a thermally-oxidized  $\text{SiO}_2$  15 insulation film 20, of which thickness is 100nm, is formed on an Si substrate 30, to which impurity such as P (phosphorus) or As (arsenic) is densely injected. Here, a part of the Si substrate 30 constitutes a gate electrode.

20 Thereafter, an a-IGZO film 10, of which thickness is 50nm, is deposited in the room temperature by a sputter deposition method by treating a polycrystalline IGZO as a target. Next, a channel layer is formed by patterning the a-IGZO film 10 by a wet etching process 25 depending on a photolithography method and the dilute hydrochloric acid.

Subsequently, after depositing a Ti layer (5nm)

50 and an Au layer (40nm) 40 by an EB (electron beam) vapor deposition method upon patterning the resist by the photolithography method, source and drain electrodes of Au/Ti are formed by a lift-off method.

5 Then, an annealing process is further executed for an hour at the temperature of 300°C.

According to the above process, the a-IGZO TFT as indicated in FIG. 1 can be formed.

10 An electric characteristic of the a-IGZO TFT which can be obtained by the above-described fabricating method will be indicated.

15 FIG. 2 indicates the  $I_d$ - $V_g$  characteristic of the present TFT. The present TFT, of which the channel width is 80 $\mu$ m, the channel length is 10 $\mu$ m, the threshold voltage is -0.1V and the mobility is 18cm $^2$ /Vs, has such the mobility which is ten times larger than that of an ordinary a-Si TFT.

20 The threshold voltage change ( $\Delta V_{TH}$ ) in a case that a portion between the gate terminal and the drain terminal is short-circuited to the present TFT and a constant current of 27 $\mu$ A is applied between the drain terminal and the source terminal is indicated in FIG. 3. A lateral axis in FIG. 3 denotes a time of applying the electrical stress. At this time, the gate potential is 25 made higher than the source potential. And, the gate potential is made equal to the drain potential. For example, a notation of 5E+04 marked on the lateral axis

in FIG. 3 denotes  $5 \times 10^4$ .

In this case, a constant voltage is applied to the gate terminal and the drain terminal. In addition, a variable power source is provided on the source 5 terminal such that a constant current flows between the drain terminal and the source terminal. That is, since the current flows between the drain terminal and the source terminal is determined by the potential difference between the gate terminal and the source 10 terminal, the voltage of the power source provided on the source terminal is adjusted such that the current flows between the drain terminal and the source terminal becomes a constant current.

And, from a fact that a voltage of the gate 15 terminal is larger than a voltage of the source terminal, the electrical stress is applied to the TFT. In this case, the threshold voltage of the TFT gradually increases. Therefore, in order to set the current, which flows between the drain terminal and the 20 source terminal, to a constant current, it is required to increase the potential difference between the gate terminal and the source terminal. For this reason, it is adjusted such that a voltage of the power source provided on the source terminal becomes small voltage 25 as the stress applying time is increased.

As compared with a fact that threshold voltage variation is about 1V during a period from a time of

elapsing twenty hours (about 70000 seconds) to a time of elapsing sixty hours, the threshold voltage varies about 3V during a period from a time of starting the measurement to the time of elapsing about 70000 seconds.

5 Therefore, it is considered that when the stress applying time reaches a certain level, the change rate of the threshold voltage by the electrical stress approaches a constant level. In a case indicated in FIG. 3, for example, a region that the threshold 10 voltage variation is about 1V (after elapsing about 70000 seconds) is a saturation region of the threshold voltage, and the TFT is driven in this region.

Incidentally, FIG. 3 indicates an example of the relationship between the stress applying time and the 15 threshold voltage in a case that the electrical stress was applied to a thin film transistor of using an amorphous oxide semiconductor. The relationship between the stress applying time and the threshold voltage varies depending on the property of the 20 amorphous oxide semiconductor to be used and the stress applying condition (voltage, temperature or the like).

A waveform of the  $I_d$ - $V_g$  characteristic before and after applying the electrical stress of the gate voltage 12V, the drain voltage 6V and the source 25 voltage 0V to another a-IGZO TFT (channel width is 180 $\mu$ m and channel length is 30 $\mu$ m) obtained by the above-described method for 800 seconds is indicated in

FIG. 4. A waveform of the  $I_d$ - $V_g$  characteristic of the same TFT after storing it in a dark place for two days after that is similarly indicated in FIG. 4. According to this FIG. 4, in case of storing it in a dark place for two days (48 hours), the change of the threshold voltage by the electrical stress is recovered. That is, it is indicated that the influence by the electrical stress remains during a period equal to or less than 48 hours. Consequently, it is understood that the threshold voltage is reversibly changed by the electrical stress to be applied between the gate terminal and the source terminal.

In addition, the electrical stress is applied to another a-IGZO TFT (channel width is  $180\mu\text{m}$  and channel length is  $30\mu\text{m}$ ) obtained by the above-described method for 400 seconds in some gate voltages upon fixing the drain voltage to 6V and the source voltage to the GND. Kinds of gate voltages are five ways of -12V, -6V, 4V, 8V and 12V. FIG. 5 indicates the threshold voltage variation by the electrical stress. According to this FIG. 5, the threshold change is almost never observed in a case that the gate voltage is lower than the source voltage (equal to or less than 0V). Further, in a case that the gate voltage is higher than the source voltage and the drain voltage (12V), the threshold change is resulted to become the largest change.

In addition, the electrical stress is applied to

the a-IGZO TFT (channel width is 180 $\mu$ m and channel length is 30 $\mu$ m) for 400 seconds in some drain voltages upon fixing the gate voltage to 20V and the source voltage to the GND. FIG. 10 indicates the threshold voltage variation in case of changing the drain voltage. According to this FIG. 10, it is understood that the threshold change becomes small as the drain voltage approaches the gate voltage (20V).

Additionally, the Id-Vg characteristic of the a-IGZO TFT, of which the channel width is 180 $\mu$ m and the channel length is 30 $\mu$ m, obtained by the above-described method is indicated in FIG. 6. FIG. 6 is a view of overwriting Id-Vg characteristics of eight TFTs, and uniformity of the characteristics becomes more high level when the overwritten characteristics can be more seen almost in one characteristic.

By using the a-IGZO TFT exhibiting the above characteristic, an organic EL display apparatus indicated in FIG. 7 will be fabricated by the following method.

First, a Ti/Au/Ti stack film consisted of a Ti layer 50-1, an Au layer 40-1 and a Ti layer 51-1 is deposited by a vapor deposition method on a glass substrate 60 as a gate line and a gate electrode. The pattern forming for the Ti/Au/Ti stack film is performed by using a photolithography method and a lift-off method.

Next, an  $\text{SiO}_2$  film is deposited by a sputtering method as an insulation layer 21. The pattern forming for the  $\text{SiO}_2$  film is performed by the photolithography method and a wet etching method of using the buffered hydrofluoric acid.

Subsequently, the a-IGZO film 10 is formed by the sputtering method as a channel layer. The pattern forming for the a-IGZO film 10 is performed by the photolithography method and the wet etching method of using the dilute hydrochloric acid.

Subsequently, a Ti/Au/Ti stack film consisted of a Ti layer 50-2, an Au layer 40-2 and a Ti layer 51-2 is deposited by the vapor deposition method as data wirings and source-drain electrodes. The pattern forming for the Ti/Au/Ti stack film is performed by using the photolithography method and the lift-off method.

Subsequently, an  $\text{SiO}_2$  film 52 is deposited as an interlayer insulation film. The pattern forming for the  $\text{SiO}_2$  film 52 is performed by the photolithography method and the wet etching method of using the buffered hydrofluoric acid.

Subsequently, a photosensitive polyimide film 70 is deposited by a spin coat method as a planarization film. The patterning for the photosensitive polyimide film 70 can be performed by executing an exposure process by the photolithography method and executing a

separating process, because the photosensitive polyimide is used.

Subsequently, an organic EL device is formed.

First, an ITO (indium tin oxide) film 80 is 5 deposited by the sputtering method as an anode electrode. The pattern forming for the ITO film 80 is performed by the photolithography method and the wet etching method of using an ITO stripping solution or a dry etching method.

10 Subsequently, a photosensitive polyimide film 71 is deposited by the spin coat method as a device separation film. The patterning for the photosensitive polyimide film 71 can be performed by executing the exposure process by the photolithography method and 15 executing the separating process, because the photosensitive polyimide is used.

Subsequently, an organic film 90 is deposited by 20 the vapor deposition method as a light emitting layer. The pattern forming for the organic film 90 is performed by a metal mask method.

Subsequently, an Al film is deposited by the vapor deposition method as a cathode electrode 100. The pattern forming for the Al film is performed by the metal mask method.

25 At last, an organic EL display apparatus can be fabricated (FIG. 7) by performing the glass sealing by using a glass substrate 61.

FIG. 8 indicates a pixel circuit in the organic EL display apparatus of the present embodiment. The pixel circuit corresponds to a circuit constituting part surrounded by a broken line excepting an organic 5 EL device (OLED (organic light emitting diode)). FIG. 11 indicates a pixel region of the organic EL display apparatus of the present embodiment. In Fig. 11, reference symbols S1 to S6 denote switches which serve to operate the voltage applying means, and a pixel is 10 composed of the organic EL device (OLED) and the pixel circuit. In the present embodiment, the pixel circuit serving as a driver circuit is constituted by three a-IGZO TFTs (TFT1, TFT2 and TFT3) and a capacitor C exists between the gate terminal and the source 15 terminal of the TFT1. The TFT1 is a driver TFT for controlling a current to be supplied to the organic EL device (OLED) and the TFT2 and the TFT3 operate as switches.

Initially, an operation in an ordinary display 20 period in the present embodiment will be described. Here, although an operation of a pixel positioned on a place defined by the m-row and the n-column will be described, an operation of another pixel is same as that of the above-described pixel. In the ordinary 25 display period, the switches S1 to S6 are in an OFF state.

In a period that a scanning line  $SL_m$  is selected,

a high level voltage is applied to the scanning line  $SL_m$ , and the TFT2 and the TFT3 are switched ON. During that selection period, the gray-scale voltage is applied to the gate terminal of the TFT1 from a data line  $DL_n$  via the TFT2. And, the GND voltage is applied to the source terminal of the TFT1 from a GND line via the TFT3. Thereafter, when a scanning line of a next stage is selected, a low level voltage is applied to the scanning line  $SL_m$ , and the TFT2 and the TFT3 are switched OFF. At this time, with respect to the voltage between the gate terminal and the source terminal of the TFT1, the gray-scale voltage in a selection period is held by the capacitor C. As long as the TFT1 operates in a saturation region, a current to be flown in the TFT1 is determined by the gray-scale voltage. Therefore, a current to be supplied to the OLED, that is, the luminance of the OLED can be controlled by the magnitude of the present gray-scale voltage.

The selection of the above-described scanning line is performed sixty times per second for all the scanning lines on the display. That is, one frame period corresponds to a ratio of 1/60 seconds.

Next, an operation in a non-displaying period in the present embodiment will be described. Although an operation of a pixel positioned on a place defined by the m-row and the n-column will be described, an

operation of another pixel is same as that of the above-described pixel.

In the organic EL display apparatus of the present embodiment, all the scanning lines of  $SL_m$  and the data lines of  $DL_n$  are selected in at least a part of the non-displaying period, and the TFT2 and the TFT3 are switched ON. And, a constant voltage  $VB$  higher than the GND voltage is applied to the data line  $DL_n$  upon turning ON the switches S4 to S6. Further, the drain voltage of the TFT1, that is, the voltage  $Vdd$  is set to the GND voltage upon turning ON the switches S1 to S3.

At this time, a current does not flow in the OLED, meanwhile the electrical stress is continuously applied to the TFT1. Consequently, the TFT1 is held with a state that a value of the threshold voltage for the electrical stress is saturated.

By performing the above operation, the organic EL display apparatus of the present invention can operate the a-IGZO TFT in a saturated region of the threshold voltage for the electrical stress. As a result, the deterioration of image quality due to the electrical stress can be suppressed.

Note that since the TFT2 and the TFT3 operate as switches, even if the threshold voltage is shifted, the TFT can be driven if the driving voltage of the TFT is previously set to a predetermined value. Therefore,

although it is not always required to apply the electrical stress to the TFT2 and the TFT3, when the driving voltage of the TFT is desired to be set to a constant voltage, that is, when the influence by the 5 variation of the threshold voltage is desired to be suppressed, the electrical stress may be applied similar to a case of the TFT1.

(Embodiment 2)

An organic EL display apparatus of the present 10 embodiment further includes a battery in the organic EL display apparatus of the Embodiment 1, and an operation of applying the electrical stress is enabled to be performed in at least a part of the non-displaying period indicated in the Embodiment 1 without supplying 15 the power from an external.

After completing to fabricate the product, the TFT1 can be realized to operate in the saturated region of the threshold voltage for the electrical stress by applying the electrical stress. Additionally, the TFT1 20 can be kept in a state of operating in a region that the change for the electrical stress is saturated until a time before starting to use by performing an operation in the above-described non-display state by using the battery.

25 Furthermore, by providing the battery, the TFT1 can be kept in a state of operating in the region that the change for the electrical stress is saturated even

if in a case that the organic EL display apparatus is separated from the power source and is moved.

However, since the recovery of the above-described characteristic comes about after elapsing a time equal to or longer than 48 hours, it is desirable to avoid to space the time equal to or longer than 48 hours concerning the above-described operation from a time of starting to use. More preferably, it has to be avoided to space a time to be fixed within 24 hours.

10        In an operation of the above-described non-display state, since there is not a route of flowing a current excepting a leak current, the power supplied from the battery to be used to perform the operation in the above-described non-display state is a small power.

15        Therefore, in case of mounting the organic EL display apparatus of the present embodiment on an apparatus having a battery such as a notebook PC or a mobile phone, the influence for a period available to supply the power of the battery caused by performing the

20        operation in the above-described non-display state is very few.

25        In case of applying the electrical stress after completing to fabricate the product, a time taken for the TFT1 to reach a region that the threshold voltage is saturated to the electrical stress can be shortened by applying the temperature together with the electrical stress.

As above described, in the present embodiment, the deterioration of display quality by the electrical stress can be suppressed in the organic EL display apparatus having driver circuits in which the a-IGZO TFTs serve as the constituent.

Although the description only concerning the TFT, in which the a-IGZO film is treated as a channel layer, was given in the Embodiments 1 and 2, the present invention can be also applied to the AOS-TFT having the similar characteristic to the electrical stress.

In addition, in case of realizing a display apparatus more excellent in the multi gray-scale, even if a driver circuit having a threshold correction function or a driver circuit having the current mirror constitution is adopted, the same effect can be obtained by applying the voltage to the driver TFT in the non-displaying period as described above.

In addition, in the Embodiment 2, the power necessary for applying the voltage is supplied from a battery equipped with the light emitting display apparatus or equipped with a system including the display apparatus, and the voltage is applied in a non-light emitting period without supplying the power from an external power source of the light emitting display apparatus. Herewith, the voltage can be applied even if the external power source is not provided.

The present invention can be applied to a light

emitting apparatus having an AOS-TFT in which a driver circuit of a light emitting device functions to treat the AOS as a channel layer. The present invention can be also applied to an AM device of using the AOS-TFT 5 other than the light emitting display apparatus, for example, a pressure sensor of using a pressure-sensitive device or an optical sensor of using a photosensitive device.

While the present invention has been described 10 with reference to the exemplary embodiments, it is to be understood that the invention is not limited to the disclosed exemplary embodiments. The scope of the following claims is to be accorded the broadest interpretation so as to encompass all such 15 modifications and equivalent structures and function.

This application claims the benefit of Japanese Patent Application No. 2007-209984, filed August 10, 2007, which is hereby incorporated by reference herein in its entirety.

## CLAIMS

1. A driving method of a thin film transistor circuit which includes a thin film transistor of which

5 a threshold voltage changes due to an electrical stress applied between a gate terminal and a source terminal, the driving method comprising:

10 applying the electrical stress between the gate terminal and the source terminal at a time when the thin film transistor is not driven, so as to drive the thin film transistor in a region that the threshold voltage is saturated to the electrical stress.

15 2. A driving method of the thin film transistor circuit according to Claim 1, wherein the electrical stress is applied by making gate potential of the thin film transistor higher than source potential of the thin film transistor.

20 3. A driving method of the thin film transistor circuit according to Claim 2, wherein the gate potential of the thin film transistor is made equal to or higher than drain voltage when the electrical stress is applied.

25 4. A driving method of a light emitting display apparatus which includes plural pixels each having a light emitting device and a driving circuit for driving the light emitting device, wherein

the driving circuit includes at least one thin

film transistor of which a threshold voltage changes due to an electrical stress applied between a gate terminal and a source terminal, and

the driving method comprises applying the

5 electrical stress between the gate terminal and the source terminal of the thin film transistor in a non-displaying period of the light emitting display apparatus, so as to drive the thin film transistor in a region that the threshold voltage is saturated to the

10 electrical stress.

5. A driving method of the light emitting display apparatus according to Claim 4, wherein the electrical stress is applied by making gate potential of the thin film transistor higher than source potential of the

15 thin film transistor.

6. A thin film transistor circuit which includes a thin film transistor of which a threshold voltage changes due to an electrical stress applied between a gate terminal and a source terminal, and a voltage

20 applying unit adapted to apply voltage between the gate terminal and the source terminal of the thin film transistor as the electrical stress, wherein

the voltage applying unit applies the electrical stress between the gate terminal and the source

25 terminal at a time when the thin film transistor is not driven, so as to drive the thin film transistor in a region that the threshold voltage is saturated to the

electrical stress.

7. A thin film transistor circuit according to

Claim 6, wherein the voltage applying unit makes gate

potential of the thin film transistor higher than

5 source potential of the thin film transistor.

8. A thin film transistor circuit according to

Claim 6, wherein the thin film transistor uses an

amorphous oxide semiconductor as a channel layer.

9. A light emitting display apparatus which

10 includes plural pixels each having a light emitting

device and a driving circuit for driving the light

emitting device, wherein

the driving circuit includes a thin film

transistor of which a threshold voltage changes due to

15 an electrical stress applied between a gate terminal

and a source terminal, and a voltage applying unit

adapted to apply voltage between the gate terminal and

the source terminal of the thin film transistor as the

electrical stress, and

20 the voltage applying unit applies the electrical

stress between the gate terminal and the source

terminal of the thin film transistor in a non-

displaying period of the light emitting display

apparatus, so as to drive the thin film transistor in a

25 region that the threshold voltage is saturated to the

electrical stress.

10. A light emitting display apparatus according

to Claim 9, wherein the voltage applying unit makes gate potential of the thin film transistor higher than source potential of the thin film transistor.

11. A light emitting display apparatus according

5 to Claim 9, wherein power necessary for the voltage to be applied is provided by the light emitting display apparatus or supplied from a battery provided in a system including the light emitting display apparatus.

12. A light emitting display apparatus according

10 to Claim 9, wherein the thin film transistor of the light emitting display apparatus uses an amorphous oxide semiconductor as a channel layer.

FIG. 1

FIG. 2

2 / 6

FIG. 3

FIG. 4

3 / 6

FIG. 5

FIG. 6

4 / 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/JP2008/063932

**A. CLASSIFICATION OF SUBJECT MATTER**

Int.Cl. G09G3/30 (2006.01) i, G09G3/20 (2006.01) i, H01L51/50 (2006.01) i

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

Int.Cl. G09G3/30, G09G3/20, H01L51/50

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Published examined utility model applications of Japan 1922-1996

Published unexamined utility model applications of Japan 1971-2008

Registered utility model specifications of Japan 1996-2008

Published registered utility model applications of Japan 1994-2008

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                            | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | JP 2006-525539 A (Koninklijke Philips Electronics N.V.) 2006.11.09, [0013]-[0045], [0075], Fig.3,5<br>& US 2006/0208971 A1<br>& EP 1627372 A<br>& WO 2004/097782 A1<br>& KR 10-2006-0015571 A | 1-12                  |

| A         | JP 2005-512297 A (INTERNATIONAL BUSINESS MACHINES CORPORATION) 2005.04.28, whole document<br>& US 2003/0094616 A1<br>& WO 2003/050892 A1<br>& CN 1589506 A                                    | 1-12                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents:

“A” document defining the general state of the art which is not considered to be of particular relevance

“E” earlier application or patent but published on or after the international filing date

“L” document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

“O” document referring to an oral disclosure, use, exhibition or other means

“P” document published prior to the international filing date but later than the priority date claimed

“T” later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

“X” document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

“Y” document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

“&” document member of the same patent family

|                                                                                                                                    |                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Date of the actual completion of the international search<br><br>10.09.2008                                                        | Date of mailing of the international search report<br><br>22.09.2008                      |

| Name and mailing address of the ISA/JP<br><br><b>Japan Patent Office</b><br>3-4-3, Kasumigaseki, Chiyoda-ku, Tokyo 100-8915, Japan | Authorized officer<br><br><b>Taku FUKUMURA</b><br>Telephone No. +81-3-3581-1101 Ext. 3226 |

**INTERNATIONAL SEARCH REPORT**

|                                                    |

|----------------------------------------------------|

| International application No.<br>PCT/JP2008/063932 |

|----------------------------------------------------|

**C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                 | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------|-----------------------|

| A         | JP 2006-208966 A (Pioneer Corporation)<br>2006.08.10, [0029]-[0031], Fig.7<br>& US 2006/0187154 A1 | 1-12                  |

|                |                                                                              |         |            |

|----------------|------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管电路，发光显示装置及其驱动方法                                                         |         |            |

| 公开(公告)号        | <a href="#">EP2165325A1</a>                                                  | 公开(公告)日 | 2010-03-24 |

| 申请号            | EP2008792138                                                                 | 申请日     | 2008-07-29 |

| [标]申请(专利权)人(译) | 佳能株式会社                                                                       |         |            |

| 申请(专利权)人(译)    | 佳能株式会社                                                                       |         |            |

| 当前申请(专利权)人(译)  | 佳能株式会社                                                                       |         |            |

| [标]发明人         | SHIMIZU HISAE<br>ABE KATSUMI<br>HAYASHI RYO                                  |         |            |

| 发明人            | SHIMIZU, HISAE<br>ABE, KATSUMI<br>HAYASHI, RYO                               |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                  |         |            |

| CPC分类号         | G09G3/3258 G09G3/3233 G09G2300/0417 G09G2300/0842 G09G2320/0233 G09G2320/043 |         |            |

| 优先权            | 2007209984 2007-08-10 JP                                                     |         |            |

| 其他公开文献         | <a href="#">EP2165325A4</a>                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                    |         |            |

**摘要(译)**

为了抑制电应力对使用TFT的TFT特性的影响，根据本发明的发光显示装置包括有机EL器件和用于驱动有机EL器件的驱动电路。驱动电路包括多个像素，每个像素具有薄膜晶体管和阈值电压，薄膜晶体管的阈值电压由于施加在栅极端子和源极端子之间的电应力而可逆地改变，并且电压施加单元将薄膜晶体管的栅极电位设置为高于来源潜力。电压施加单元在未驱动薄膜晶体管时在栅极端子和源极端子之间施加电应力，以便在阈值电压饱和到电应力的区域中驱动薄膜晶体管。