# (11) EP 2 261 884 A1

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

15.12.2010 Bulletin 2010/50

(51) Int Cl.: **G09G** 3/32 (2006.01)

(21) Application number: 10158802.8

(22) Date of filing: 31.03.2010

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO SE SI SK SM TR

**Designated Extension States:**

AL BA ME RS

(30) Priority: 05.06.2009 KR 20090049848

(71) Applicant: Samsung Mobile Display Co., Ltd. Yongin-City

Gyunggi-do (KR)

(72) Inventors:

- Kang, Chul-Kyu Gyunggi-Do 446-711 (KR)

- Choi, Sang-Moo Gyunggi-Do 446-711 (KR)

- Kim, Keum-Nam Gyunggi-Do 446-711 (KR)

- (74) Representative: Gulde Hengelhaupt Ziebig & Schneider Patentanwälte - Rechtsanwälte Wallstrasse 58/59 10179 Berlin (DE)

## (54) Pixel and organic light emitting display using the same

(57) A pixel includes an organic light emitting diode (OLED) having a cathode electrode coupled to a second power source (ELVSS), a first transistor (M1) for controlling an amount of current that flows from a first power source (ELVDD) to the second power source (ELVSS) via the OLED corresponding to a data signal, a second transistor (M2) coupled between a data line and a gate electrode of the first transistor, a third transistor (M3) coupled between the gate electrode of the first transistor and

a reference power source (Vref), a fourth transistor (M4) coupled between the third transistor and the reference power source, a fifth transistor (M5) coupled between an anode electrode of the OLED and an initial power source (Vinit), a first capacitor (C1) coupled between the anode electrode of the OLED and a node between the third transistor and the fourth transistor, and a second capacitor (C2) coupled between the node and the gate electrode of the first transistor.

FIG. 3

140

Dm ELVDD -142 N1 M1 En М3 : C2 N2 C1 CLn M4 N3Sn M5 V OLED **ELVSS** Vref Vint

EP 2 261 884 A1

#### **Description**

### **BACKGROUND**

#### 1. Field

5

10

20

30

35

40

45

50

55

[0001] The following description relates to a pixel and an organic light emitting display using the same.

### 2. Description of the Related Art

**[0002]** Recently, various flat panel displays (FPDs) having reduced weight and volume as compared to cathode ray tubes (CRTs) have been developed. The FPDs include liquid crystal displays (LCDs), field emission displays (FEDs), plasma display panels (PDPs), and organic light emitting displays.

**[0003]** Among the FPDs, the organic light emitting displays display images using organic light emitting diodes (OLEDs) that generate light through the re-combination of electrons and holes. The organic light emitting display has fast response times and is driven with low power consumption.

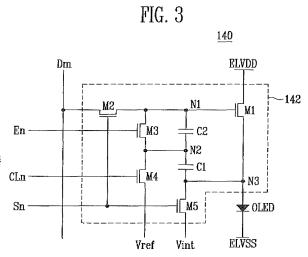

**[0004]** FIG. 1 is a circuit diagram illustrating a pixel of a conventional organic light emitting display. In FIG. 1, transistors included in the pixel are NMOS transistors.

**[0005]** Referring to FIG. 1, a pixel 4 of the conventional organic light emitting display includes an organic light emitting diode (OLED), and a pixel circuit 2 coupled to a data line Dm and a scan line Sn to control the OLED.

**[0006]** The anode electrode of the OLED is coupled to the pixel circuit 2 and the cathode electrode of the OLED is coupled to a second power source ELVSS. The OLED generates light with a predetermined brightness corresponding to current supplied from the pixel circuit 2.

[0007] The pixel circuit 2 controls an amount of current supplied to the OLED corresponding to a data signal supplied to the data line Dm when a scan signal is supplied to the scan line Sn. Therefore, the pixel circuit 2 includes a second transistor M2 (that is, a driving transistor) coupled between a first power source ELVDD and the OLED, a first transistor M1 coupled between the second transistor M2 and the data line Dm, and having a gate electrode coupled to the scan line Sn, and a storage capacitor Cst coupled between a gate electrode and a second electrode of the second transistor M2.

**[0008]** The gate electrode of the first transistor M1 is coupled to the scan line Sn, and the first electrode thereof is coupled to the data line Dm. The second electrode of the first transistor M1 is coupled to one terminal of the storage capacitor Cst. Here, the first electrode of the first transistor M1 is one of a source electrode or a drain electrode, and the second electrode thereof is the other one of the source electrode or the drain electrode. For example, when the first electrode is a source electrode, the second electrode is a drain electrode. The first transistor M1 is turned on when a scan signal is supplied from the scan line Sn to supply a data signal supplied from the data line Dm to the storage capacitor Cst. At this time, the storage capacitor Cst charges a voltage corresponding to the data signal.

**[0009]** The gate electrode of the second transistor M2 is coupled to one terminal of the storage capacitor Cst, and the first electrode thereof is coupled to the first power source ELVDD. The second electrode of the second transistor M2 is coupled to the other terminal of the storage capacitor Cst and the anode electrode of the OLED. The second transistor M2 controls the amount of current supplied from the first power source ELVDD to the second power source ELVSS via the OLED corresponding to the voltage value stored in the storage capacitor Cst.

**[0010]** One terminal of the storage capacitor Cst is coupled to the gate electrode of the second transistor M2 and the other terminal of the storage capacitor Cst is coupled to the anode electrode of the OLED. The storage capacitor Cst charges the voltage corresponding to the data signal.

**[0011]** The conventional pixel 4 supplies a current corresponding to the voltage charged in the storage capacitor Cst to the OLED to display an image with a predetermined brightness. However, a conventional organic light emitting display using the above-described pixel cannot display an image having uniform brightness throughout the display due to deviations in the threshold voltages of the second transistors M2 in different pixels.

**[0012]** Specifically, when the threshold voltages of the second transistors M2 vary between different pixels 4, the pixels 4 generate light with different brightnesses corresponding to the same data signal, and an image with uniform brightness cannot be displayed or is very difficult to display.

### SUMMARY OF THE INVENTION

**[0013]** Accordingly, exemplary embodiments of the present invention provide pixels and an organic light emitting display capable of displaying an image with uniform brightness, independent of the threshold voltages of driving transistors in the pixels. More specifically, a first aspect of the invention provides the pixel as set forth in claim 1. Preferred embodiments of the pixel are subject of the dependent claims 2 through 5. A second aspect of the invention provides the organic light emitting display of claim 6. Preferred embodiments of the organic light emitting display are subject of the dependent

claims 7 through 10.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

- 5 **[0014]** The accompanying drawings, together with the specification, illustrate exemplary embodiments of the present invention, and, together with the description, serve to explain the principles of the present invention.

- [0015] FIG. 1 is a circuit diagram illustrating a pixel of a conventional organic light emitting display;

- [0016] FIG. 2 is a schematic view illustrating an organic light emitting display according to an embodiment of the present invention;

- [0017] FIG. 3 is a circuit diagram illustrating an embodiment of a pixel of FIG. 2; and

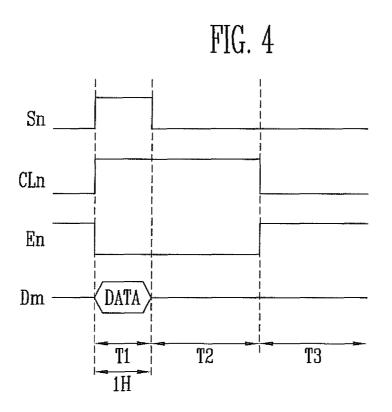

- [0018] FIG. 4 illustrates waveforms describing a method of driving the pixel of FIG. 3.

#### **DETAILED DESCRIPTION**

30

35

40

55

- [0019] Hereinafter, certain exemplary embodiments according to the present invention will be described with reference to the accompanying drawings. Here, when a first element is described as being coupled to a second element, the first element may be directly coupled to the second element, or may be indirectly coupled to the second element via one or more additional elements. Further, some of the elements that are not essential to the complete understanding of the invention are omitted for clarity. Also, like reference numerals refer to like elements throughout.

- [0020] Hereinafter, exemplary embodiments by which those skilled in the art can easily perform the present invention will be described in detail with reference to the accompanying drawings, specifically, FIGS. 2 to 4.

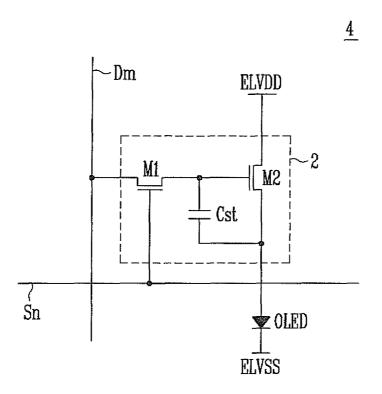

- **[0021]** FIG. 2 is a schematic view illustrating an organic light emitting display according to an embodiment of the present invention.

- **[0022]** Referring to FIG. 2, an organic light emitting display according to an embodiment of the present invention includes pixels 140 coupled to scan lines S1 to Sn, control lines CL1 to CLn, emission control lines E1 to En, and data lines D1 to Dm, a scan driver 110 for driving the scan lines S1 to Sn, the emission control lines E1 to En, and the control lines CL1 to CLn, a data driver 120 for driving the data lines D1 to Dm, and a timing controller 150 for controlling the scan driver 110 and the data driver 120.

- [0023] The scan driver 110 receives a scan driving control signal SCS from the timing controller 150. The scan driver 110 generates scan signals and sequentially supplies the generated scan signals to the scan lines S1 to Sn. In addition, the scan driver 110 generates control signals and sequentially supplies the generated control signals to the control lines CL1 to CLn. Here, the control signal supplied to an ith (i is a natural number) control line CLi is concurrently supplied with the scan signal supplied to the ith scan line Si, and is supplied for a longer duration than the scan signal. For example, the control signal supplied to the ith control line CLi can be supplied to overlap with the scan signals supplied to at least two scan lines (e.g., Si, Si+1, ....).

- **[0024]** The scan driver 110 generates the emission control signals and sequentially supplies the generated emission control signals to the emission control lines E1 to En. Here, the emission control signal supplied to the ith emission control line Ei is supplied to overlap with the control signal supplied to the ith control line CLi.

- [0025] According to the embodiment of the present invention, the scan signals and the control signals are set to have a voltage by which the transistors included in the pixels 140 can be turned on, and the emission control signals are set to have a voltage by which the transistors included in the pixels 140 can be turned off. For example, the scan signals and the control signals can be set to have a high voltage, while the emission control signals can be set to have a low voltage.

[0026] The data driver 120 receives a data driving control signal DCS from the timing controller 150. The data driver 120 supplies data signals to the data lines D1 to Dm synchronously with the scan signals.

- [0027] The timing controller 150 generates the data driving control signal DCS and the scan driving control signal SCS corresponding to synchronization signals supplied from the outside. The data driving control signal DCS is supplied to the data driver 120 and the scan driving control signal SCS is supplied to the scan driver 110. The timing controller 150 supplies the data Data from the outside to the data driver 120.

- [0028] A display region 130 receives a first power source ELVDD, a second power source ELVSS, a reference power source Vref, and an initial power source Vint from the outside, and supplies the first power source ELVDD, the second power source ELVSS, the reference power source Vref, and the initial power source Vint to the pixels 140. The pixels 140 generate light corresponding to the data signals.

- **[0029]** Here, the voltage Vdata corresponding to the data signals, the voltage of the first power source ELVDD, the voltage of the reference power source Vref, and the voltage of the initial power source Vint are set corresponding to Equation 1.

## Equation 1

5

20

30

35

45

50

### ELVDD>Vref≥Vdata>Vint

**[0030]** Referring to Equation 1, the reference power source Vref is set to have a voltage equal to or higher than the voltage Vdata of the data signals. The initial power source Vint is set to have a voltage lower than the voltage Vdata of the data signals. More specifically, the initial power source Vint is set to have a voltage lower than a voltage obtained by subtracting the threshold voltage of the driving transistor from the voltage Vdata of the data signals. The first power source ELVDD is set to have a voltage higher than the voltage of the reference power source Vref.

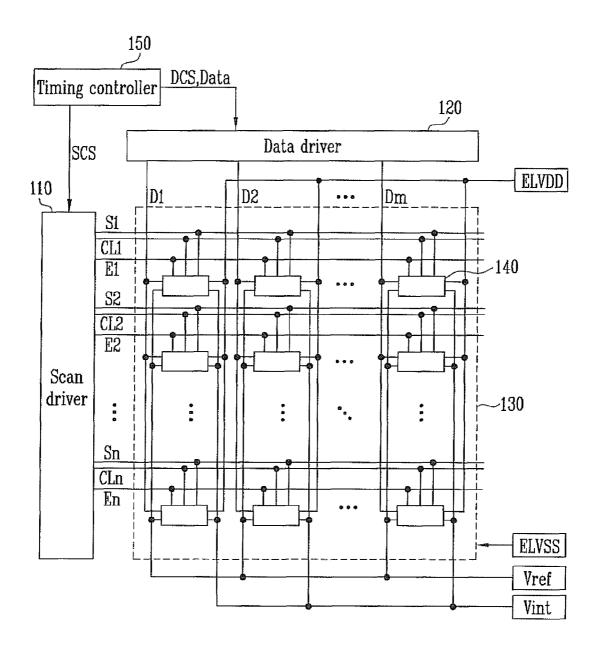

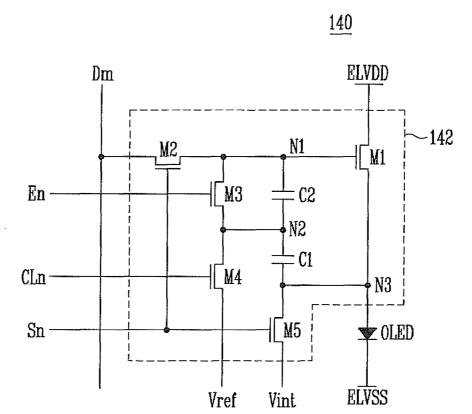

**[0031]** FIG. 3 is a circuit diagram illustrating a pixel according to an embodiment of the present invention. For convenience, in FIG. 3, a pixel coupled to an nth scan line Sn and an mth data line Dm is illustrated.

**[0032]** Referring to FIG. 3, the pixel 140 according to the embodiment of the present invention includes an OLED, and a pixel circuit 142 coupled to a data line Dm, a scan line Sn, an emission control line En, and a control line CLn, to control the OLED.

**[0033]** The anode electrode of the OLED is coupled to the pixel circuit 142 and the cathode electrode of the OLED is coupled to a second power source ELVSS. The OLED generates light with a brightness (e.g., a predetermined brightness) corresponding to a current supplied from the pixel circuit 142.

**[0034]** The pixel circuit 142 charges the voltage corresponding to a data signal during a period where a scan signal (e.g., a high scan signal) is supplied to the scan line Sn. Then, the pixel circuit 142 charges the voltage corresponding to the threshold voltage of a first transistor M1 during a period where the supply of the scan signal to the scan line Sn is stopped, and the supply of a control signal to the control line CLn is continued or maintained. Then, the pixel circuit 142 supplies the current corresponding to the charged voltages to the OLED. The pixel circuit 142 includes first to fifth transistors M1 to M5, a first capacitor C1, and a second capacitor C2.

**[0035]** A gate electrode of the first transistor M1 (a driving transistor) is coupled to a first node N1, and a first electrode of the first transistor M1 is coupled to the first power source ELVDD. A second electrode of the first transistor M1 is coupled to the anode electrode of the OLED at a third node N3. The first transistor M1 controls an amount of current supplied to the OLED in response to a voltage applied to the first node N1.

[0036] A gate electrode of the second transistor M2 is coupled to the scan line Sn, and a first electrode of the second transistor M2 is coupled to the data line Dm. A second electrode of the second transistor M2 is coupled to the first node N1. The second transistor M2 is turned on when a scan signal (e.g., a high scan signal) is supplied to the scan line Sn to electrically couple the data line Dm to the first node N1.

**[0037]** A gate electrode of the third transistor M3 is coupled to the emission control line En, and a second electrode of the third transistor M3 is coupled to the first node N1 (i.e., the gate electrode of the first transistor M1). A first electrode of the third transistor M3 is coupled to a second node N2. The third transistor M3 is turned off when an emission control signal (e.g., a low emission control signal) is supplied to the emission control line En, and is turned on when the emission control signal is not supplied, to electrically couple the first node N1 and the second node N2.

**[0038]** A gate electrode of the fourth transistor M4 is coupled to the control line CLn, and a second electrode of the fourth transistor M4 is coupled to the second node N2. A first electrode of the fourth transistor M4 is coupled to the reference power source Vref. The fourth transistor M4 is turned on when a control signal (e.g., a high control signal) is supplied to the control line CLn, to supply the voltage of the reference power source Vref to the second node N2.

**[0039]** A gate electrode of the fifth transistor M5 is coupled to the scan line Sn and a first electrode of the fifth transistor M5 is coupled to the third node N3. A second electrode of the fifth transistor M5 is coupled to the initial power source Vint. The fifth transistor M5 is turned on when the scan signal is supplied to the scan line Sn, to supply the initial power source Vint to the third node N3.

**[0040]** The first capacitor C1 and the second capacitor C2 are coupled in series between the third node N3 and the first node N1. The common node between the first capacitor C1 and the second capacitor C2 is coupled to the second node N2, which is also the common node between the third transistor M3 and the fourth transistor M4. Here, the second capacitor C2 and the third transistor M3 are coupled between the first node N1 and the second node N2 in parallel.

**[0041]** FIG. 4 illustrates waveforms for driving the pixel of FIG. 3.

[0042] Processes for operating a pixel according to an embodiment of the present invention will be described in detail with reference to FIGS. 3 and 4.

**[0043]** First, a high scan signal, a high control signal, and a low emission control signal are respectively supplied to the scan line Sn, the control line CLn, and the emission control line En in a first period T1.

**[0044]** When the scan signal is supplied to the scan line Sn, the second transistor M2 and the fifth transistor M5 are turned on. When the control signal is supplied to the control line CLn, the fourth transistor M4 is turned on. When the emission control signal is supplied to the emission control line En, the third transistor M3 is turned off.

4

**[0045]** When the second transistor M2 is turned on, the data signal from the data line Dm is supplied to the first node N1. When the fifth transistor M5 is turned on, the initial power source Vint is supplied to the third node N3. Here, the initial power source Vint is set to have a voltage for the OLED to be turned off. Therefore, light is not generated by the OLED during this time. When the fourth transistor M4 is turned on, the reference power source Vref is supplied to the second node N2.

[0046] That is, in the first period T1, the first node N1 is at the voltage Vdata of the data signal, the second node N2 is at the voltage of the reference power source Vref, and the third node N3 is at the voltage of the initial power source Vint. In this case, the second capacitor C2 is charged with a voltage corresponding to a difference between the voltage Vdata of the data signal and the reference power source Vref, and the first capacitor C1 is charged with a voltage corresponding to a difference between the reference power source Vref and the initial power source Vint. In addition, since the current path flowing through the first transistor M1 in the first period T1 flows to the initial power source Vint, the OLED does not emit light.

**[0047]** Then, in a second period T2, the supply of the scan signal to the scan line Sn is stopped (i.e., the scan signal becomes low). When the supply of the scan signal to the scan line Sn is stopped, the second transistor M2 and the fifth transistor M5 are turned off.

**[0048]** When the second transistor M2 is turned off, the first node N1 maintains the voltage supplied during the first period T1 due to the voltage charged in the second capacitor C2. When the fifth transistor M5 is turned off, the voltage of the third node N3 increases to the voltage obtained by subtracting the threshold voltage of the first transistor M1 from the voltage Vdata of the data signal.

**[0049]** To be more specific, in the first period T1, the voltage of the first node N1 is set at the voltage Vdata of the data signal and the voltage of the third node N3 is set at the voltage of the initial power source Vint. Here, the voltage of the initial power source Vint is set at a voltage lower than the voltage obtained by subtracting the threshold voltage of the first transistor M1 from the voltage Vdata of the data signal. Therefore, when the fifth transistor M5 is turned off, the voltage of the third node N3 increases to a voltage obtained by subtracting the threshold voltage of the first transistor M1 from the voltage Vdata of the data signal.

**[0050]** In this case, the voltage of Vref - Vdata is charged in the second capacitor C2 and the voltage of Vref - Vdata + Vth (M1) is charged in the first capacitor C1.

**[0051]** Then, in a third period T3, the supply of the control signal to the control line CLn is stopped (i.e., the control signal becomes low), and the supply of the emission control signal to the emission control line En is stopped (i.e., the emission control signal becomes high). When the supply of the control signal to the control line CLn is stopped, the fourth transistor M4 is turned off. When the supply of the emission control signal to the emission control line En is stopped, the third transistor M3 is turned on.

[0052] When the third transistor M3 is turned on, the first node N1 and the second node N2 are electrically coupled to each other. In this case, a voltage difference between the ends of the second capacitor C2 becomes 0, and the voltage charged in the first capacitor C1 becomes the voltage Vgs (M1) between the gate electrode and the source electrode of the first transistor M1. That is, the voltage between the gate electrode and the source electrode of the first transistor M1 is set corresponding to Equation 2.

## **Equation 2**

$$Vgs(M1) = Vref - Vdata + Vth(M1)$$

[0053] The amount of current that flows to the OLED corresponding to the voltage of Vgs of the first transistor M1 is therefore set corresponding to Equation 3.

## **Equation 3**

20

30

35

40

50

55

$$Ioled = \beta(Vgs(M1) - Vth(M1))^2 = \beta\{(Vref - Vdata + Vth(M1)) - Vth(M1)\}^2 = \beta(Vref - Vdata)^2$$

**[0054]** Referring to Equation 3, the current that flows to the OLED is determined by a voltage difference between the voltage of the reference power source Vref and the voltage Vdata of the data signal. Here, since the reference power source Vref has a fixed voltage, the current that flows to the OLED is determined by the voltage Vdata of the data signal.

### EP 2 261 884 A1

Therefore, according to an embodiment of the present invention, corresponding to Equation 3, an image with uniform brightness can be displayed independent of deviations in the threshold voltages of the first transistors M1 in different pixels of a display.

**[0055]** Furthermore, in FIG. 3, the transistors are NMOS transistors. However, the present invention is not limited to the above described embodiment. For example, the transistors can be PMOS transistors. In this case, the polarities of the supplied waveforms illustrated in FIG. 4 would be inverted. However, the processes for operating the pixel would be substantially similar.

#### 10 Claims

15

20

25

30

45

55

#### 1. A pixel, comprising:

- a first transistor (M1) having a first electrode connected to a first power source (ELVDD) and a gate electrode connected to a first node (N1);

- an organic light emitting diode (OLED) having an anode electrode coupled to a second electrode of the first transistor (M1) and a cathode electrode coupled to a second power source (ELVSS);

- a second transistor (M2) having a first electrode connected to a data line, a second electrode connected to the first node (N1), and a gate electrodeconnected to a scan line (Sn);

- a third transistor (M3) having a first electrode connected to a second node (N2), a second electrode connected to the first node (N1), and a gate electrode connected to an emission control line (En);

- a fourth transistor (M4) having a first electrode connected to a reference power source (Vref), a second electrode connected to the second node (N2), and a gate electrode connected to a control line (CLn);

- a fifth transistor (M5) having a first electrode connected to the anode electrode of the organic light emitting diode (OLED), a second electrode connected to an initial power source (Vint), and a gate electrode connected to the scan line (Sn);

- a first capacitor (C1) connected between the anode electrode of the organic light emitting diode (OLED) and the second node (N2); and

- a second capacitor (C2) connected between the first node (N1) and the second node (N2).

- 2. The pixel as claimed in claim 1, wherein the reference power source (Vref) has a voltage equal to or higher than a voltage of the data signal.

- 3. The pixel as claimed in one of the claims 1 or 2, wherein the initial power source (Vint) has a voltage lower than the voltage of the data signal.

- **4.** The pixel as claimed in claim 3, wherein the voltage of the initial power source (Vint) is lower than a voltage obtained by subtracting a threshold voltage of the first transistor (M1) from the voltage of the data signal.

- 5. The pixel as claimed in one of the preceding claims, wherein the first power source (ELVDD) has a voltage higher than the voltage of the reference power source (Vref).

- **6.** The pixel as claimed in one of the preceding claims, wherein all of the first transistor (M1), the second transistor (M2), the third transistor (M3), the fourth transistor (M4), and the fifth transistor (M5) are transistors of the same polarity type.

- 7. The pixel of claim 6, wherein all of the first transistor (M1), the second transistor (M2), the third transistor (M3), the fourth transistor (M4), and the fifth transistor (M5) are NMOS transistors.

- 50 **8.** An organic light emitting display, comprising:

- a scan driver (110) adapted to sequentially supply a scan signal to a plurality of scan lines (S1...Sn), to sequentially supply an emission control signal to a plurality of emission control lines (E1...En), and to sequentially supply a control signal to a plurality of control lines (CL1...CLn), the scan lines (S1...Sn), emission control lines (E1...En), and control lines (CL1...CLn) extending in a first direction;

- a data driver (120) adapted to supply a data signal to a plurality of data lines (D1...Dm) extending in a second direction crossing the first direction; and

- a plurality of pixels (140) arranged at crossing regions of the scan lines (S1...Sn), the emission control lines

### EP 2 261 884 A1

(E1...En), and the control lines (CL1...CLn) with the data lines (D1...Dm), wherein each pixel (140) is a pixel according to one of the preceding claims.

**9.** The organic light emitting display as claimed in claim 8, wherein the scan driver (110) is configured to supply the scan signal to an ith scan line (Si) when supplying the control signal to an ith control line (CLi).

- **10.** The organic light emitting display as claimed in one of the claims 8 or 9, wherein the scan driver (110) is adapted to provide the control signal for a longer time period than the scan signal.

- **11.** The organic light emitting display as claimed in one of the claims 8 through 10, wherein the scan driver (110) is configured to supply the emission control signal to an ith emission control line when supplying the control signal to an ith control line.

- 12. The organic light emitting display as claimed in one of the claims 8 through 11, wherein the data driver (120) is configured to provide the data signal for a row of pixels corresponding to an ith scan line (Si) concurrently with the scan driver (110) supplying the scan signal to the ith scan line (Si).

FIG. 2

FIG. 3

## **EUROPEAN SEARCH REPORT**

Application Number EP 10 15 8802

|                              | DOCUMENTS CONSID  Citation of document with ir                                                                                                    | dication, where appropriate,                                      |                                    | elevant                                  | CLASSIFICATION OF THE |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------|------------------------------------------|-----------------------|

| Category                     | of relevant passa                                                                                                                                 |                                                                   |                                    | claim                                    | APPLICATION (IPC)     |

| A                            | WO 2006/103797 A1 (TAKAJI) 5 October 2 * figures 8,9 *                                                                                            | SHARP KK [JP]; NUMA<br>006 (2006-10-05)                           | 0 1-:                              | 12                                       | INV.<br>G09G3/32      |

| A,P                          | -& US 2009/231308 A<br>17 September 2009 (                                                                                                        | - [0121], [0157]                                                  | ·                                  | 12                                       |                       |

| А                            | ET AL) 14 June 2007                                                                                                                               | UCHINO KATSUHIDE [J<br>(2007-06-14)<br>- [0088]; figures          | -                                  | 12                                       |                       |

| A,P                          | LTD [KR]) 2 December                                                                                                                              | MSUNG MOBILE DISPLA<br>r 2009 (2009-12-02)<br>- [0045]; figures   |                                    | 12                                       |                       |

| A                            | AL) 23 December 200                                                                                                                               | IMAMURA YOICHI [JP]<br>4 (2004-12-23)<br>- [0069]; figures        |                                    | 12                                       | TECHNICAL FIELDS      |

|                              | *                                                                                                                                                 | [0005], Tiguies                                                   | -,-                                |                                          | SEARCHED (IPC)        |

|                              |                                                                                                                                                   |                                                                   |                                    |                                          | G09G                  |

|                              |                                                                                                                                                   |                                                                   |                                    |                                          |                       |

|                              | The present search report has I                                                                                                                   | ·                                                                 |                                    |                                          |                       |

|                              | Place of search                                                                                                                                   | Date of completion of the se                                      | arch                               |                                          | Examiner              |

|                              | Munich                                                                                                                                            | 17 May 2010                                                       |                                    | Ley                                      |                       |

| X : part<br>Y : part<br>docu | ATEGORY OF CITED DOCUMENTS icularly relevant if taken alone icularly relevant if combined with another of the same category nolociacal background | E : earlier pa<br>after the fi<br>ner D : documen<br>L : document | t cited in the a<br>cited for othe | t, but publis<br>pplication<br>r reasons |                       |

EPO FORM 1503 03.82 (P04C01)

## ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 10 15 8802

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

17-05-2010

| US 200<br>US 200<br>US 200 | 006103797 | A1<br>A1 | 05-10-2006<br>17-09-2009 | US<br>WO                   | 2009231308                                                | A1           | 17-09-2009                                                         |

|----------------------------|-----------|----------|--------------------------|----------------------------|-----------------------------------------------------------|--------------|--------------------------------------------------------------------|

| US 200                     |           |          | 17-09-2009               | <br>WO                     |                                                           |              |                                                                    |

|                            | 07132694  |          |                          |                            | 2006103797                                                | A1           | 05-10-2000                                                         |

| EP 212                     |           | A1       | 14-06-2007               | US                         | 2007164962                                                | A1           | 19-07-200                                                          |

|                            | .28848    | A1       | 02-12-2009               | CN<br>JP<br>KR<br>US       | 101593767<br>2009288761<br>20090123562<br>2009295772      | A<br>A       | 02-12-2009<br>10-12-2009<br>02-12-2009<br>03-12-2009               |

| US 200                     | 004257353 | A1       | 23-12-2004               | CN<br>JP<br>JP<br>KR<br>TW | 1551059<br>3772889<br>2005004173<br>20040100887<br>269251 | B2<br>A<br>A | 01-12-2004<br>10-05-2006<br>06-01-2009<br>02-12-2004<br>21-12-2006 |

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

| 专利名称(译)        | 使用其的像素和有机发光显示器                                                                 |         |                           |  |

|----------------|--------------------------------------------------------------------------------|---------|---------------------------|--|

| 公开(公告)号        | EP2261884A1                                                                    | 公开(公告)日 | 2010-12-15                |  |

| 申请号            | EP2010158802                                                                   | 申请日     | 2010-03-31                |  |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                       |         |                           |  |

| 申请(专利权)人(译)    | 三星移动显示器有限公司.                                                                   |         |                           |  |

| 当前申请(专利权)人(译)  | 三星移动显示器有限公司.                                                                   |         |                           |  |

| [标]发明人         | KANG CHUL KYU<br>CHOI SANG MOO<br>KIM KEUM NAM                                 |         |                           |  |

| 发明人            | KANG, CHUL-KYU<br>CHOI, SANG-MOO<br>KIM, KEUM-NAM                              |         |                           |  |

| IPC分类号         | G09G3/32                                                                       |         |                           |  |

| CPC分类号         | G09G3/3233 G09G2300/043 G09G2300/0819 G09G2300/0852 G09G2320/0233 G09G2320/043 |         | 09G2320/0233 G09G2320/043 |  |

| 优先权            | 1020090049848 2009-06-05 KR                                                    |         |                           |  |

| 其他公开文献         | EP2261884B1                                                                    |         |                           |  |

| 外部链接           | Espacenet                                                                      |         |                           |  |

|                |                                                                                |         |                           |  |

## 摘要(译)

像素包括具有耦合到第二电源(ELVSS)的阴极电极的有机发光二极管(OLED),用于控制从第一电源(ELVDD)流到第二电源的电流量的第一晶体管(M1)电源(ELVSS)通过OLED对应于数据信号,第二晶体管(M2)耦合在第一晶体管的数据线和栅电极之间,第三晶体管(M3)耦合在第一晶体管的栅电极和参考电源(Vref),耦合在第三晶体管和参考电源之间的第四晶体管(M4),耦合在OLED的阳极和初始电源(Vinit)之间的第五晶体管(M5),第一晶体管电容器(C1)耦合在OLED的阳极和第三晶体管和第四晶体管之间的节点之间,第二电容器(C2)耦合在第一晶体管的节点和栅极之间。