# (11) **EP 1 981 018 A1**

(12)

## **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

15.10.2008 Bulletin 2008/42

(51) Int Cl.:

G09G 3/32 (2006.01)

(21) Application number: 08154330.8

(22) Date of filing: 10.04.2008

(84) Designated Contracting States:

AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MT NL NO PL PT RO SE SI SK TR

**Designated Extension States:**

AL BA MK RS

(30) Priority: 10.04.2007 KR 20070035007

(71) Applicant: Samsung SDI Co., Ltd.

Suwon-si Gyeonggi-do (KR) (72) Inventor: Kim, Yang-Wan Suwon-si, Gyeonggi-do (KR)

(74) Representative: Hengelhaupt, Jürgen et al

Anwaltskanzlei

Gulde Hengelhaupt Ziebig & Schneider

Wallstrasse 58/59 10179 Berlin (DE)

## (54) Plixel, organic light emitting display usig the same, and associated methods

(57) A pixel, including an organic light emitting diode, a first transistor between a data line and a first node, a second transistor between the first node and a third node, a third transistor between the second node and the third node, a fourth transistor between a first power source and the first node, a fifth transistor between the third node and the organic light emitting diode, a sixth transistor between an initialization power source and the second node, a storage capacitor between the second node and

the first power source, first and second feedback capacitors in series between a fourth node and the second node, a seventh transistor between the fourth node and the organic light emitting diode, an eighth transistor between the first power source and the fourth node, and a ninth transistor between a fifth node and a predetermined voltage source.

EP 1 981 018 A1

#### Description

#### BACKGROUND OF THE INVENTION

## 1. Field of the Invention

**[0001]** Embodiments relate to a pixel, an organic light emitting display using the same, and associated methods, in which degradation of an organic light emitting diode is automatically compensated.

## 2. Description of the Related Art

**[0002]** In the manufacture and operation of a display, e.g., a display used to reproduce text, images, video, etc., uniform operation of pixel elements of the display is highly desirable. However, providing such uniform operation may be difficult. For example, in some display technologies, e.g., those utilizing electroluminescent elements such as organic light emitting diodes (OLEDs), operational characteristics, e.g., luminance, of the pixel elements may change over time. Accordingly, there is a need for a display adapted to compensate for changes in the operational characteristics of pixel elements.

#### **SUMMARY OF THE INVENTION**

**[0003]** Therefore, it is an object of the present invention to provide a pixel, an organic light emitting display device and a driving method thereof capable of compensating for a deterioration of an organic light emitting diode.

[0004] In order to accomplish the above object, there is provided a pixel according to an embodiment of the present invention including: an organic light emitting diode; a second transistor for supplying current to the organic light emitting diode; a pixel circuit for compensating for the threshold voltage of the second transistor; and a compensating unit for controlling the voltage of a gate electrode of the second transistor in order to compensate for a deterioration of the organic light emitting diode, wherein the compensating unit includes: seventh and eighth transistors coupled between the organic light emitting diode and a first power supply; first and second feedback capacitors positioned between a second node, which is a common node of the seventh and eighth transistors, and a first node electrically coupled to the gate electrode of the second transistor; and a ninth transistor coupled between a third node, which is a common node of the first and second feedback capacitors, and a predetermined voltage supply.

**[0005]** Preferably, the pixel circuit includes: a first transistor coupled to an ith (i is a natural number) scan line and data line and turned-on when a scan signal is supplied to the ith scan line to supply a data signal supplied to the data line to the first electrode of the second transistor; a third transistor coupled between the second electrode of the second transistor and the first node and turned-on when the scan signal is supplied to the ith scan

line; a fourth transistor coupled between an initialization power supply and the first node, and turned-on when the scan signal is supplied to an i-1th scan line; a fifth transistor coupled between the first electrode of the second transistor and the first power supply and turned-on when a light emitting control signal is not supplied to a ith light emitting control line; a sixth transistor coupled between the second electrode of the second transistor and the organic light emitting diode and turned-on when the light emitting control signal is not supplied to the ith light emitting control line; and a storage capacitor coupled between the first node and the first power supply. The initialization power supply is set to a voltage value lower than the data signal. The seventh and eighth transistors are alternatively turned-on and turned-off.

[0006] There is provided an organic light emitting display device according to an embodiment of the present invention including: a scan driver for sequentially supplying scan signals to scan lines and sequentially supplying light emitting control signals to light emitting control lines; a data driver for supplying data signals to data lines; and pixels positioned in regions partitioned by the scan lines and the data lines, wherein each of the pixels includes: an organic light emitting diode; a second transistor for supplying current to the organic light emitting diode; a pixel circuit for compensating for the threshold voltage of the second transistor; and a compensating unit for controlling the voltage of a gate electrode of the second transistor in order to compensate for a deterioration of the organic light emitting diode, wherein the compensating unit includes: seventh and eighth transistors coupled between the organic light emitting diode and a first power supply; first and second feedback capacitors positioned between a second node, which is a common node of the seventh and eighth transistors, and a first node electrically coupled to the gate electrode of the second transistor; and a ninth transistor coupled between a third node, which is a common node of the first and second feedback capacitors, and a predetermined voltage supply.

[0007] Preferably, the scan driver supplies the light emitting control signals to an ith light emitting control line to be overlapped with the scan signals supplied to an i-1th (i is a natural number) scan line and an i th scan line. The pixel circuit includes: a first transistor coupled to the ith scan line and data line and turned-on when a scan signal is supplied to the ith scan line to supply a data signal supplied to the data line to the first electrode of the second transistor; a third transistor coupled between the second electrode of the second transistor and the first node and turned-on when the scan signal is supplied to the ith scan line; a fourth transistor coupled between an initialization power supply and the first node, and turned-on when the scan signal is supplied to an i-1th scan line; a fifth transistor coupled between the first electrode of the second transistor and the first power supply and turned-on when a light emitting control signal is not supplied to the ith light emitting control line; a sixth transistor coupled between the second electrode of the sec-

40

50

20

40

45

ond transistor and the organic light emitting diode and turned-on when the light emitting control signal is not supplied to the ith light emitting control line; and a storage capacitor coupled between the first node and the first power supply. The initialization power supply is set to a voltage value lower than the data signal. The seventh and eighth transistors are alternatively turned-on and turned-off.

[0008] There is provided a driving method of an organic light emitting display device according to an embodiment of the present invention, the organic light emitting display device including first and second transistors positioned between an anode electrode of an organic light emitting diode and a first power supply; and first feedback and second feedback capacitors positioned between a first node, which is a common node of the first and second transistors; and a gate electrode of a driving transistor, the driving method including the steps of: initializing the voltage of the gate electrode of the driving transistor with the voltage of an initialization power supply; charging the voltage corresponding to the threshold voltage of the driving transistor and a data signal in a storage capacitor by connecting the driving transistor in the form of a diode; supplying the current corresponding to the voltage charged in the storage capacitor to the organic light emitting diode; applying the voltage applied to the organic light emitting diode to the first node; maintaining a second node, which is a common terminal of the first and second feedback capacitors at a constant voltage during the steps of charging the voltage in the storage capacitor and the supplying the voltage applied to the organic light emitting diode to the first node; and controlling the voltage of the gate electrode of the driving transistor by setting the second node to the state of floating and at the same time, raising the voltage of the first node to the voltage of the first power supply.

[0009] A preferred embodiment of the invention provides a pixel comprising a pixel driving circuit and an organic light emitting diode, wherein the pixel driving circuit has a power input connected to a first power supply, a data input connected to a data line, a first scan input connected to a current scan line, a first emission control input connected to a current emission control line, and an output connected to a first electrode of the organic light emitting diode. The organic light emitting diode comprises a second electrode connected to a second power supply. The pixel driving circuit further comprises a storage capacitor having a first electrode connected to the first power supply and a second electrode connected to a storage node, a pass transistor having a first electrode connected to the data input and a control electrode connected to the first scan input, and a driving transistor having a control electrode connected to the storage node, a first electrode, and a second electrode. The driving transistor is adapted to supply a driving current through the first electrode to the organic light emitting diode corresponding to a data voltage stored in the storage node. The pixel driving circuit further comprises a first emission

control transistor having a control input connected to the first emission control input and adapted to interrupt the driving current from flowing to the organic light emitting diode in response to an emission control signal. According to the invention, the pixel may comprise a compensating unit having a sense input connected to the first electrode of the organic light emitting diode and a feedback output connected to the storage node of the pixel driving circuit. The compensating unit includes a first compensation transistor having a first electrode connected to the first electrode of the organic light emitting diode and a second electrode connected to a first electrode of a second compensation transistor, the second compensation transistor further comprising a second electrode connected to the first power supply, a first feedback capacitor having a first electrode connected to the second electrode of the first compensation transistor and a second electrode connected to a first electrode of a third compensation transistor, a second feedback capacitor having a first electrode connected to the second electrode of the first feedback capacitor and a second electrode connected to the feedback output.

**[0010]** In the preferred embodiment of the pixel, the pixel driving circuit may further include a threshold compensation transistor having a first electrode connected to the storage node and a second electrode connected to the first electrode of the driving transistor.

**[0011]** The first emission control transistor may have a first electrode connected to the first electrode of the driving transistor and a second electrode connected to the first electrode of the organic light emitting diode. In addition to this, the pixel driving circuit may further comprise a second emission control transistor having a control electrode connected to the first emission control input, a first electrode connected to the second electrode of the driving transistor and a second electrode connected to the first power supply.

**[0012]** A second electrode of the pass transistor may be connected to the second electrode of the driving transistor.

**[0013]** The pixel driving circuit may further comprise an initialisation transistor having a first electrode connected to the storage node, a second electrode connected to an initialisation voltage supply, and a control electrode connected to a second scan input of the pixel driving circuit, the second scan input being connected to a previous scan line. In addition, a second electrode of the third compensation transistor may be connected to the initialisation voltage supply. Alternatively, the second electrode of the third compensation transistor may be connected to the first power supply.

**[0014]** The initialisation power supply may be set to a voltage value lower than the data signal.

**[0015]** The second compensation transistor may be a PMOS transistor and wherein the third compensation transistor may be an NMOS transistor having a control electrode connected to a subsequent emission control line.

25

**[0016]** The first compensation transistor may be a PMOS transistor having a control electrode connected to a subsequent scan line and a control electrode of the second compensation transistor may be connected to the subsequent emission control line.

[0017] Alternatively, the first compensation transistor may be an NMOS transistor having a control input connected to a next-but-one emission control line and a control electrode of the second compensation transistor may be connected to the next-but-one emission control line. [0018] As a further preferred embodiment the invention provides an organic light emitting display device including a scan driver for sequentially supplying scan signals to scan lines and sequentially supplying light emitting control signals to light emitting control lines, a data driver for supplying data signals to data lines, and pixels positioned in regions partitioned by the scan lines and the data lines, each of the pixels being of the preferred embodiment of the pixel.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

[0019] The above and other features and advantages will become more apparent to those of ordinary skill in the art by describing in detail exemplary embodiments thereof with reference to the attached drawings, in which:

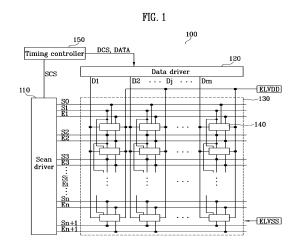

[0020] FIG. 1 illustrates a schematic view of an organic light emitting display according to a first embodiment;

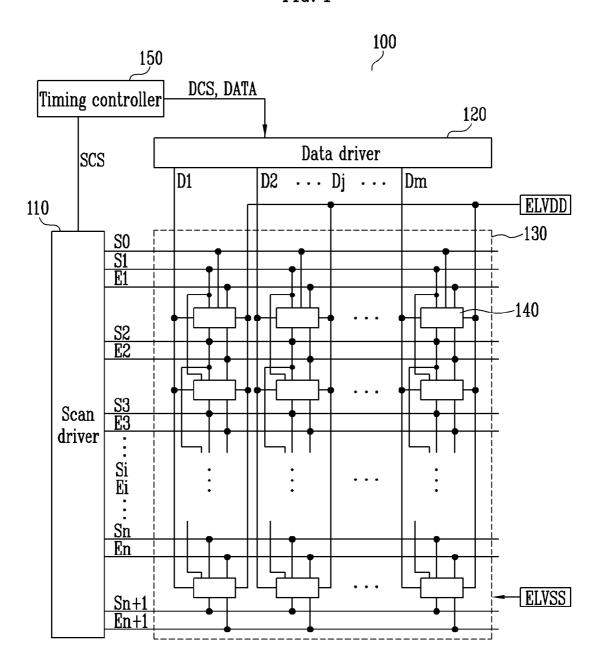

[0021] FIG. 2 illustrates a schematic view of a pixel

according to the first embodiment;

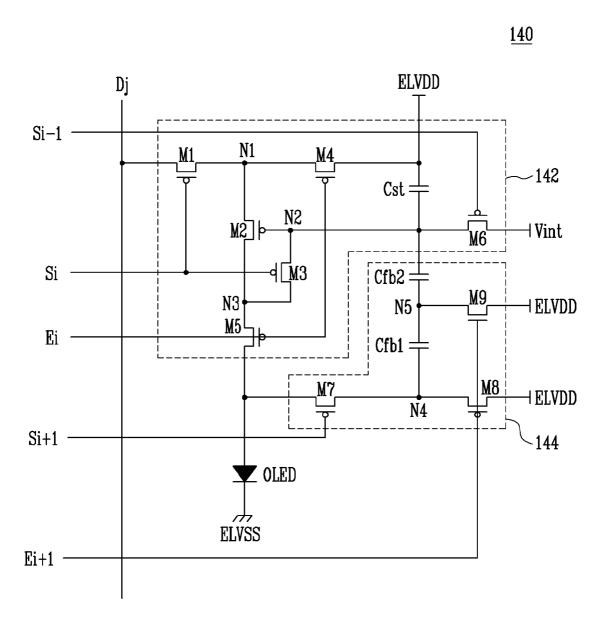

[0022] FIG. 3 illustrates waveforms for driving the pixel

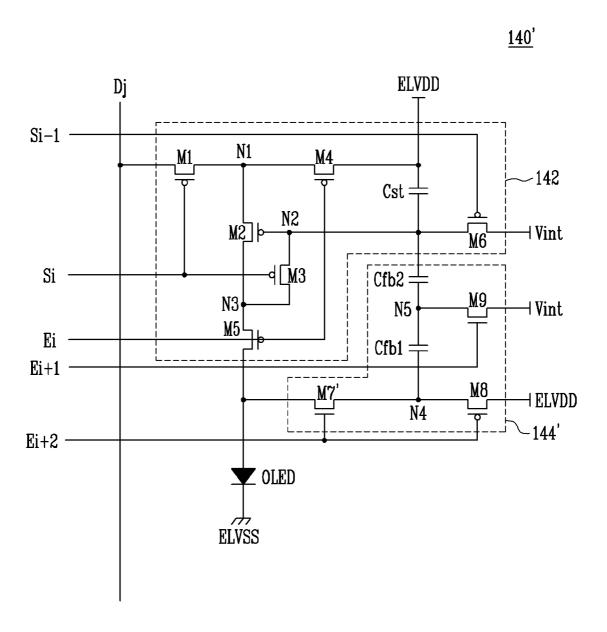

[0023] FIG. 4 illustrates a schematic view of a pixel according to a second embodiment; and

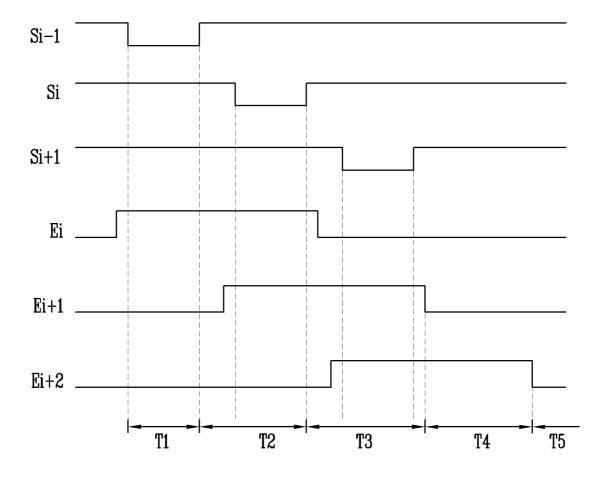

**[0024]** FIG. 5 illustrates waveforms for driving the pixel illustrated in FIG. 4.

#### **DETAILED DESCRIPTION OF THE INVENTION**

illustrated in FIG. 2;

**[0025]** Example embodiments will now be described more fully hereinafter with reference to the accompanying drawings; however, they may be embodied in different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the invention to those skilled in the art.

[0026] In the figures, the dimensions of layers and regions may be exaggerated, or elements may be omitted, for clarity of illustration. It will also be understood that when a layer or element is referred to as being "on" another layer or substrate, it can be directly on the other layer or substrate, or intervening layers may also be present. Further, it will be understood that when a layer is referred to as being "under" another layer, it can be directly under, and one or more intervening layers may also be present. In addition, it will also be understood that when a layer is referred to as being "between" two

layers, it can be the only layer between the two layers, or one or more intervening layers may also be present. [0027] Similarly, where an element is described as being coupled to a second element, the element may be directly coupled to the second element, or may be indirectly coupled to the second element via one or more other elements. Further, where an element is described as being coupled to a second element, it will be understood that the elements may be electrically coupled, e.g., in the case of transistors, capacitors, power sources, nodes, etc. Where two or more elements are described as being coupled to a node, the elements may be directly coupled to the node, or may be coupled via conductive features to which the node is common. Thus, where embodiments are described or illustrated as having two or more elements that are coupled at a common point, it will be appreciated that the elements may be coupled at respective points on a conductive feature that extends between the respective points. Like reference numerals refer to like elements throughout.

**[0028]** As used herein, in the context of PMOS transistors, when a scan signal is described as being supplied, the scan signal has a LOW polarity, and when the scan signal is described as being stopped, the scan signal has a HIGH polarity. Further, when a light emitting control signal is described as being supplied, the light emitting control signal has a HIGH polarity, and when the light emitting control signal is described as being stopped, the light emitting control signal has a LOW polarity. When signals are described as overlapping, the signals are concurrently supplied.

[0029] FIG. 1 illustrates a schematic view of an organic light emitting display 100 according to a first embodiment, and FIG. 2 illustrates a schematic view of a pixel 140 according to the first embodiment. Referring to FIG. 1, the organic light emitting display 100 may include a pixel unit 130 including pixels 140 coupled to scan lines SO to Sn+1, light emitting control lines E1 to En+1, and data lines D 1 to Dm. The organic light emitting display 100 may further include a scan driver 110 for driving the scan lines SO to Sn+1 and the light emitting control lines E1 to En+1, a data driver for driving the data lines D1 to Dm, and a timing controller 150 for controlling the scan driver 110 and the data driver 120.

[0030] The scan driver 110 may be supplied with a scan driving control signal SCS from the timing controller 150. The scan driver 110 may generate scan signals in response to the scan driving control signal SCS and sequentially supply the generated scan signals to the scan lines SO to Sn+1. The scan driver 110 may also generate light emitting control signals in response to the scan driving control signal SCS and sequentially supply the generated light emitting control signals to the light emitting control lines E1 to En+1.

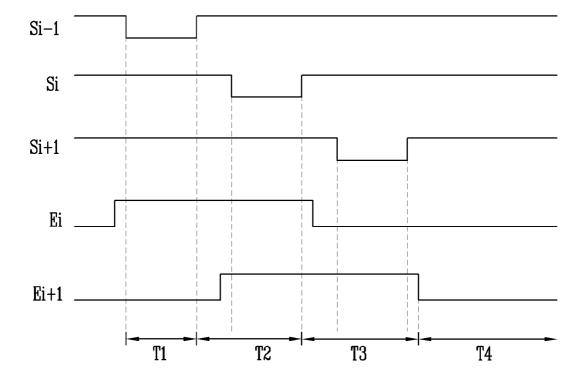

**[0031]** FIG. 3 illustrates waveforms for driving the pixel illustrated in FIG. 2 Referring to FIG. 3, a pulse width of the light emitting control signal may be greater than a pulse width of the scan signal. The light emitting control

45

40

signal supplied to an i<sup>th</sup> light emitting control line Ei (i is a natural number from 1 to n, inclusive) may overlap with the scan signals supplied to an i-1<sup>th</sup> scan line Si-1 and an i<sup>th</sup> scan line Si. The polarity of the pulse of the light emitting control signal may be different, e.g., opposite, from the polarity of the pulse of the scan signal. For example, if the scan line is set to a low polarity, the light emitting control signal may be set to a high polarity.

[0032] The data driver 120 may be supplied with the data driving control signal DSC from the timing controller 150. The data driver 120 may generate data signals in response to the data driving control signal DCS, and may sequentially supply the generated data signals to the data lines D1 to Dm in synchronization with the scan signals. [0033] The timing controller 150 may generate the data driving control signal DCS and the scan driving control signal SCS corresponding to externally supplied synchronizing signals. The data driving control signal DCS generated from the timing controller 150 may be supplied to the data driver 120, and the scan driving control signal SCS may be supplied to the scan driver 110. The timing controller 150 may also supply externally-provided data DATA to the data driver 120.

**[0034]** The pixel unit 130 may be supplied with voltages of a first power source ELVDD and a second power source ELVSS, and may distribute the voltages to each pixel 140. The first and second power sources ELVDD and ELVSS may be external to the pixel unit 130.

[0035] Each pixel 140 may generate light, e.g., one of red (R), green (G), or blue (B), corresponding to the data signals. The pixel 140 may generate light having a desired brightness by compensating for deterioration of an organic light emitting diode (OLED) included in the pixel 140, such as deterioration that results in an increase in resistance of the organic light emitting diode (OLED). Further, the pixel 140 may compensate for changes in the threshold voltage of a driving transistor included in the pixel 140. The pixel 140 may be provided with a compensating unit 144 for compensating the deterioration of the organic light emitting diode (OLED) and a pixel circuit 142 that compensates for the threshold voltage of the driving transistor.

**[0036]** For convenience of explanation, FIG. 2 illustrates only a pixel 140 positioned at i<sup>th</sup> horizontal line and coupled to a i<sup>th</sup> data line Dj (j is a natural number from 1 to m, inclusive). Referring to FIGS. 1 and 2, in order to drive the compensating unit 144 and the pixel circuit 142 included in the pixel 140, the pixel 140 positioned at the i<sup>th</sup> horizontal line may be coupled to the i-1<sup>th</sup> scan line Si-1, the i<sup>th</sup> scan line Si, the i+1<sup>th</sup> scan line Si+1, the i<sup>th</sup> light emitting control line Ei, and the i+1<sup>th</sup> light emitting control line.

[0037] Referring to FIG. 2, the pixels 140 according to the first embodiment may include an organic light emitting diode (OLED), the pixel circuit 142 that compensates for the threshold voltage of a second transistor M2 (driving transistor) supplying current to the organic light emitting diode (OLED), and the compensating unit 144 that com-

pensates for the deterioration of the organic light emitting diode (OLED). The compensating unit 144 may control the voltage of a second node N2 coupled to a gate electrode of the second transistor M2 by lowering the voltage as the organic light emitting diode (OLED) deteriorates, in order to compensate for the deterioration of the organic light emitting diode (OLED).

[0038] An anode electrode of the organic light emitting diode (OLED) may be coupled to the pixel circuit 142, and a cathode electrode of the organic light emitting diode (OLED) may be coupled to the second power source ELVSS. The organic light emitting diode (OLED) may generate a predetermined brightness of light corresponding to an amount of current supplied from the second transistor M2. The first power source ELVDD may be set to a voltage higher than that of the second power source ELVSS. The pixel circuit 142 may supply current to the organic light emitting diode (OLED) and compensate for the threshold voltage of the second transistor M2, and may include first to sixth transistors M1 to M6, and a storage capacitor Cst.

**[0039]** A gate electrode of the first transistor M1 may be coupled to the i<sup>th</sup> scan line Si, and a first electrode of the first transistor M1 may be coupled to the data line Dj. A second electrode of the first transistor M1 may be coupled to a first electrode of the second transistor M2 via a first node N1. The first transistor M1 may be turned-on when the scan signal is supplied to the i<sup>th</sup> scan line Si, and may thus supply a data signal from the data line Dj to the first electrode of the second transistor M2.

[0040] The gate electrode of the second transistor M2 may be coupled to the second node N2, and a first electrode of the second transistor M2 may be coupled to the second electrode of the first transistor M1 via the first node N1. A second electrode of the second transistor M2 may be coupled to a first electrode of the fifth transistor M5 via a third node N3. The second transistor M2 may supply current, in correspondence with a voltage applied to the second node N2, to the organic light emitting diode (OLED).

**[0041]** A first electrode of the third transistor M3 may be coupled to the second electrode of the second transistor M2 via the third node N3, and a second electrode of the third transistor M3 may be coupled to the second node N2. A gate electrode of the third transistor M3 may be coupled to the i<sup>th</sup> scan line Si. The third transistor M3 may be turned-on when the scan signal is supplied to the i<sup>th</sup> scan line Si, and may thus diode-connect the second transistor M2.

[0042] A first electrode of the fourth transistor M4 may be coupled to the first power source ELVDD, and a second electrode of the fourth transistor M4 may be coupled to the first electrode of the second transistor M2 via the first node N1. A gate electrode of the fourth transistor M4 may be coupled to the i<sup>th</sup> light emitting control line Ei. The fourth transistor M4 may be turned-on when the light emitting control signal is not supplied to the i<sup>th</sup> light emitting control line Ei, and may thus electrically connect the

40

50

first power source ELVDD to the first electrode of the second transistor **M2** via the first node N1.

**[0043]** A first electrode of the fifth transistor M5 may be coupled to the second electrode of the second transistor M2 via the third node N3, and a second electrode of the fifth transistor M5 may be coupled to the organic light emitting diode (OLED). A gate electrode of the sixth transistor may be coupled to the i<sup>th</sup> light emitting control line Ei. The fifth transistor M5 may be turned-on when the light emitting control line is not supplied to the i<sup>th</sup> light control line En, and may thus electrically connect the second transistor M2 to the organic light emitting diode (OLED).

**[0044]** A first electrode of the sixth transistor M6 may be coupled to the second node N2, and a second electrode of the sixth transistor M6 may be coupled to an initialization power source Vint. A gate electrode of the sixth transistor M6 may be coupled to the i-1<sup>th</sup> scan line Si-1. The sixth transistor M6 may be turned-on when the scan signal is supplied to the i-1<sup>th</sup> scan line Si-1, and may thus initialize the voltage of the second node N2 with the initialization power source Vint.

**[0045]** The storage capacitor Cst may be coupled between the second node N2 and the first power source ELVDD. The storage capacitor Cst may be charged with a predetermined voltage corresponding to the voltage applied to the second node N2.

[0046] The compensating unit 144 may control, via the second node N2, the voltage of the gate electrode of the second transistor M2 in correspondence with deterioration of the organic light emitting diode (OLED). For example, the compensating unit 144 may control the voltage of the second node N2 to be lowered as the organic light emitting diode (OLED) is deteriorated, thereby compensating for the deterioration of the organic light emitting diode (OLED). The compensating unit 144 may include seventh to ninth transistors M7 to M9, a first feedback capacitor Cfb1, and a second feedback capacitor Cfb2. [0047] A first electrode of the seventh transistor M7 may be coupled to a fourth node N4 and a second electrode of the seventh transistor M7 may be coupled to an anode electrode of the organic light emitting diode (OLED). A gate electrode of the seventh transistor M7 may be coupled to the i+1<sup>th</sup> scan line Si+1. The seventh transistor M7 may be turned-on when the scan signal is supplied to the i+1th scan line Si+1, and may thus electrically connect the fourth node N4 to the organic light emitting diode (OLED).

**[0048]** A first electrode of the eighth transistor M8 may be coupled to the first power source ELVDD, and a second electrode of the eighth transistor M8 may be coupled to the fourth node N4. A gate electrode of the eighth transistor M8 may be coupled to the i+1<sup>th</sup> light emitting control line Ei+1. The eighth transistor M8 may be turned-on when the light emitting control signal is not supplied to the i+1<sup>th</sup> light emitting control line Ei+1, and may thus electrically connect the first power source ELVDD to the fourth node N4.

**[0049]** A first terminal of the first feedback capacitor Cfb 1 may be coupled to the fourth node N4, and a second terminal of the first feedback capacitor Cfb1 may be coupled to a fifth node N5, which may be common to the first and second feedback capacitors Cfb1 and Cfb2. The first feedback capacitor Cfb1 may change the voltage of the fifth node N5 corresponding to an amount of change in voltage of the fourth node N4.

**[0050]** A first terminal of the second feedback capacitor Cfb2 may be coupled to the fifth node N5, and a second terminal of the second feedback capacitor Cfb2 may be coupled to the second node N2. The feedback capacitor Cfb2 may change the voltage of the second node N2 corresponding to an amount of change in voltage of the fifth node N5.

**[0051]** As described above, the first feedback capacitor Cfb1 and the second feedback capacitor Cfb2 may be coupled between the fourth node N4 and the second node N2, and may change the voltage of the second node N2 corresponding to the amount of change in voltage of the fourth node N4.

[0052] A first electrode of the ninth electrode N9 may be coupled to the first power source ELVDD, and a second electrode of the ninth electrode N9 may be coupled to the fifth node N5. A gate electrode of the ninth transistor M9 may be coupled to the i+1<sup>th</sup> light emitting control line Ei+1. The ninth transistor M9 may be turned-on when the light emitting control signal is supplied to the i+1<sup>th</sup> light emitting control line Ei+1, and may thus electrically connect the fifth node N5 to the first power source ELVDD. The ninth transistor M9 may have a conductivity type that is different from the other transistors M1 to M8. For example, if the transistors M1 to M8 are PMOS transistors, the ninth transistor M9 may be an NMOS transistor.

**[0053]** Operation of the above-described pixel 140 will now be described in connection with the waveforms illustrated in FIG. 3. Referring to FIGS. 2 and 3, during a first period T1 illustrated in FIG. 3, the scan signal may be supplied to the scan line Si-1, and the light emitting control signal may be supplied to the i<sup>th</sup> light emitting control signal Ei.

[0054] When the light emitting control signal is supplied to the light emitting control line Ei, the fourth transistor M4 and the fifth transistor M5 may be turned-off, and when the scan signal is supplied to the scan line Si-1, the sixth transistor M6 may be turned-on. Accordingly, when the sixth transistor M6 is turned-on, the second node N2 may be initialized with the voltage of the initialization power source Vint. The initialization power source Vint may be set to a voltage that is lower than that of the data signal.

**[0055]** During a second period T2, the supply of the scan signal to the scan line Si-1 may stop, while the supply of the light emitting control signal to the light emitting control line Ei+1 may be maintained. When the supply of the scan signal to the scan line Si-1 stops, the sixth transistor M6 may be turned-off. Further, during the second period T2, the scan signal supplied to the subsequent

40

45

scan line Si may turn on the first transistor M1 and the third transistor M3. When the third transistor M3 is turned-on, the second transistor M2 may be diode-connected. Further, when the first transistor M1 is turned-on, the data signal from the data line Dj may be supplied to the first electrode of the second transistor M2.

[0056] As described above, the voltage of the second node N2 may be initialized with the voltage of the initialization power source Vint during the first period T1, and the second transistor M2 may be turned-on. Accordingly, the data signal supplied via the first transistor M1 may be supplied to the second node N2 via the second transistor M2 and the third transistor M3. Thus, the second node N2 may be supplied with a signal, the voltage of which corresponds to the data signal and the threshold voltage of the second transistor M2. The storage capacitor Cst may be charged with a voltage corresponding to the voltage supplied to the second node N2.

[0057] Also during the second period T2, when the light emitting control signal is supplied to the i+1<sup>th</sup> light emitting control line Ei+1, the ninth transistor M9 may be turned-on and the eighth transistor M8 may be turned-off. When the ninth transistor M9 is turned-on, the voltage of the first power source ELVDD may be supplied to the fifth node N5. Thus, the fifth node N5 may maintain the voltage of the first power source ELVDD during the period when the voltage corresponding to the data signal is applied.

[0058] During a third period T3, the light emitting control signal supplied to the light emitting control line Ei and the scan signal supplied to the scan line Si may stop. When the supply of the scan signal to the scan line Si stops, the first transistor M1 and the third transistor M3 may be turned-off. When the supply of the light emitting control signal to the light emitting control line Ei stops, the fourth transistor M4 and the fifth transistor M5 may be turned-on. When the fourth transistor M4 and the fifth transistor M5 are turned-on, the first power source ELVDD, the fourth transistor M4, the second transistor M2, the fifth transistor M5, and the organic light emitting diode (OLED) may be electrically coupled. Thus, the second transistor M2 may supply a current, corresponding to the voltage applied to the second node N2, to the organic light emitting diode (OLED), so as to illuminate the organic light emitting diode (OLED).

**[0059]** Also during the third period T3, the seventh transistor M7 may be maintained in the turned-on state by a scan signal supplied to the next scan line Si+1. Accordingly, the fourth node N4 may be supplied with a voltage Voled applied to the organic light emitting diode (OLED) during the third period T3.

**[0060]** Thereafter, during a fourth period T4, the scan signal supplied to the scan line Si+1 and the light emitting control signal supplied to the light emitting control line Ei+1 may stop. When the supply of the scan signal to the scan line Si+1 stops, the seventh transistor M7 may be turned-off. When the supply of the light emitting control line to the light emitting control signal Ei+1 stops, the

ninth transistor M9 may be turned off and the eighth transistor M8 may be turned-on.

[0061] When the eighth transistor M8 is turned-on, the voltage of the fourth node N4 may rise from the voltage Voled of the organic light emitting diode (OLED) to the voltage of the first power source ELVDD. Further, since the ninth transistor M9 may be turned-off during the fourth period T4, the fifth node N5 may be set to a floating state. Accordingly, the voltage of the fifth node N5 may rise by an amount corresponding to the increase in voltage of the fourth node N4. Likewise, the voltage of the second node N2, which may also be in a floating state, may rise by an amount corresponding to the rise in the voltage of the fifth node N5. Thus, the voltage of the second node N2 may be controlled corresponding to the amount of voltage rise of the fourth node N4 in the fourth period T4, and, subsequently, the second transistor M2 may supply the current corresponding to the voltage applied to the second node N2 to the organic light emitting diode (OLED).

[0062] The organic light emitting diode (OLED) may deteriorate over time, e.g., due to exposure to air and/or moisture, or due to operation of the organic light emitting diode (OLED). If the organic light emitting diode (OLED) is deteriorated, the voltage Voled applied to the organic light emitting diode (OLED) may rise, i.e., when the current is supplied to the organic light emitting diode (OLED), the voltage applied to the organic light emitting diode (OLED) may rise as the organic light emitting diode (OLED) is deteriorated.

[0063] As the organic light emitting diode (OLED) is deteriorated, the amount of the voltage rise at the fourth node N4 may become smaller due to a rise in the voltage Voled of the organic light emitting diode (OLED) supplied to the fourth node N4. When the voltage Voled applied to the organic light emitting diode (OLED) rises, the amount of voltage rise may be reduced when the voltage of the first power source ELVDD is supplied to the fourth node N4. Moreover, as the amount of the voltage rise of the fourth node N4 is reduced, the amount of the voltage rise of the fifth node N5 and the second node N2 may be correspondingly reduced. Accordingly, the amount of current supplied from the second transistor M2 to the organic light emitting diode (OLED) may increase for a given data signal. Thus, according to the first embodiment, as the organic light emitting diode (OLED) deteriorates, the amount of current supplied from the second transistor M2 may increase so that degradation in brightness due to the deterioration of the organic light emitting diode (OLED) may be compensated.

**[0064]** FIG. 4 illustrates a schematic view of a pixel 140' according to a second embodiment. For convenience of explanation, FIG. 4 illustrates a pixel 140' positioned at the i<sup>th</sup> horizontal line and coupled to the i<sup>th</sup> data line (Dj).

**[0065]** The pixel 140' may be similar to the pixel 140 described above. In particular, the pixel 140' may include the pixel circuit 142, which may be coupled to light emit-

40

45

ting control line Ei, scan lines Si-1 and Si, and data line Dj, in the same manner as the pixel circuit 142 described above in connection with the first embodiment. The pixel 140' may also include a compensating unit 144', which may be similar to the compensation unit 144 described above in connection with the first embodiment, except for the construction of a seventh transistor M7' and the configuration of the signal lines coupled to the compensation unit 144'. In particular, the compensating unit 144' may have an NMOS transistor as the seventh transistor M7', whereas the compensating unit 144 may have a PMOS transistor as the seventh transistor M7. Further, in the compensating unit 144', the seventh transistor M7' and the eighth transistor M8 may both be coupled to an i+2th light emitting control line Ei+2. Additionally, in the compensating unit 144', the ninth transistor M9 may be coupled to the initialization power source Vint, whereas, in the compensating unit 144, the ninth transistor M9 may be coupled to the first power source ELVDD. In an organic light emitting display including pixels 140', scan lines SO to Sn and light emitting control lines E1 to En+2 may be provided (not shown), which may be coupled to a suitably configured scan driver. In the following description of the second embodiment, the description of features that are the same as those in the first embodiment may be omitted in order to avoid repetition.

**[0066]** Referring to FIG. 4, the pixel 140' at the i<sup>th</sup> horizontal line may be coupled to the i-1<sup>th</sup> scan line Si-1, the i<sup>th</sup> scan line Si, the i<sup>th</sup> light emitting control line Ei, the i+1<sup>th</sup> light emitting control line Ei+1, and the i+2 light emitting control line Ei+2.

**[0067]** In the pixel 140' according to the second embodiment, the ninth transistor M9 may be coupled between the fifth node N5 and the initialization power source Vint. The ninth transistor M9 may be turned-on when the light emitting control signal is supplied to the i+1<sup>th</sup> light emitting control line Ei+1, and may thus supply the initialization power source Vint to the fifth node N5.

**[0068]** The initialization power source Vint supplied to the fifth node N5 may maintain the voltage of the fifth node N5 constant, irrespective of a voltage change of the second node N2. The ninth transistor M9 may be coupled to the initialization power source Vint or the first power source ELVDD to allow the voltage of the fifth node N5 to be maintained constant.

**[0069]** Also, in the pixel 140' according to the second embodiment, the gate electrodes of the seventh transistor M7' and the eighth transistor M8 may be coupled to the i+2 light emitting control line Ei+2. The seventh transistor M7' and the eighth transistor M8 may thus be alternately turned-on and turned-off, i.e., they may operate in opposition such that one is turned-off while the other is turned-on. In an implementation, the seventh transistor M7' may be an NMOS transistor and the eighth transistor M8 may be a PMOS transistor.

**[0070]** FIG. 5 illustrates waveforms for driving the pixel 140' illustrated in FIG. 4. In particular, FIG. 5 illustrates the waveforms shown in FIG. 3, in addition to a waveform

applied to the i+2th light emitting control line Ei+2.

[0071] Referring to FIGS. 4 and 5, during the first period T1, the scan signal may be supplied to the i-1<sup>th</sup> scan line Si-1 and the light emitting control signal may be supplied to the i<sup>th</sup> light emitting control line Ei. When the light emitting control signal is supplied to the i<sup>th</sup> light emitting control line Ei, the fourth transistor M4 and the fifth transistor M5 may be turned-off. When the scan signal is supplied to the i-1<sup>th</sup> scan line Si-1, the sixth transistor M6 may be turned-on. When the sixth transistor M6 is turned-on, the voltage of the second node N2 may be initialized with the initialization power source Vint. The initialization power source Vint may be set to a voltage that is lower than that of the data signal.

**[0072]** During the second period T2, the supply of the scan signal to the i-1<sup>th</sup> scan line Si-1 may stop. A light emitting control signal may be supplied to the i+1<sup>th</sup> light emitting control line Ei+1 during the second period T2. When the supply of the scan signal to the scan line Si-1 stops, the sixth transistor M6 may be turned-off. The scan signal may be supplied to the subsequent scan line Si during the second period T2, such that the first transistor M1 and the third transistor M3 may be turned-on.

[0073] When the third transistor M3 is turned-on, the second transistor M2 may be diode-connected. When the first transistor M1 is turned-on, the data signal supplied to the data line Dj may be supplied to the first electrode of the second transistor M2 via the first node N1. As described above, the voltage of the second node N2 may be initialized with the voltage of the initialization power source Vint during the first period T1, and the second transistor M2 may be turned-on. Accordingly, during the second period T2, the data signal supplied by the first transistor M1 may be supplied to the second node N2 via the second transistor M2, the third node N3, and the third transistor M3. Accordingly, the second node N2 may be supplied with a voltage corresponding to the data signal and the threshold voltage of the second transistor M2. The storage capacitor Cst may be charged with a voltage corresponding to the voltage supplied to the second node N2.

[0074] Also during the second period T2, when the light emitting control signal is supplied to the i+1<sup>th</sup> light emitting control line Ei+1, the ninth transistor M9 may be turned-on. When the ninth transistor M9 is turned-on, the voltage of the initialization power source Vint may be supplied to the fifth node N5. Thus, the fifth node N5 may maintain the voltage of the initialization power source Vint during the period where the voltage corresponding to the data signal is applied.

**[0075]** The light emitting control signal supplied to the i<sup>th</sup> light emitting control line Ei and the scan signal supplied to the i<sup>th</sup> scan line Si may stop during a third period T3. When the supply of the scan signal to the i<sup>th</sup> scan line Si stops, the first transistor M1 and the third transistor M3 may be turned-off. When the supply of the light emitting control signal to the light emitting control line Ei stops, the fourth transistor M4 and the fifth transistor M5 may

be turned-on. When the fourth transistor M4 and the fifth transistor M5 are turned-on, the first power source ELVDD, the fourth transistor M4, the second transistor M2, the fifth transistor M5, and the organic light emitting diode (OLED) may be electrically coupled. Thus, the second transistor M2 may supply a current, corresponding to the voltage applied to the second node N2, to the organic light emitting diode (OLED), so as to illuminate the organic light emitting diode (OLED).

**[0076]** Meanwhile, when the light emitting control signal is supplied to the i+2<sup>th</sup> light emitting control line Ei+2, the seventh transistor M7' may be turned-on, and the voltage Voled applied to the organic light emitting diode OLED may be supplied to the fourth node N4.

[0077] During the fourth period T4, the supply of the light emitting control signal to the i+1<sup>th</sup> light emitting control line Ei+1 may stop. When the supply of the light emitting control signal to the light emitting control line Ei+1 stops, the ninth transistor M9 may be turned-off, and the fifth node N5 may thus be placed in a floating state.

[0078] During a fifth period T5, the supply of the light emitting control signal to the i+2th light emitting control line Ei+2 may stop. Accordingly, during the fifth period T5, the seventh transistor M7' may be turned-off, and the eighth transistor M8 may be turned-on. When the eighth transistor M8 is turned-on, the voltage of the fourth node N4 may rise from the voltage Voled of the organic light emitting diode (OLED) to the voltage of the first power source ELVDD. At this time, since the fifth node N5 may be in a floating state, the voltage of the fifth node N5 may rise by an amount corresponding to the amount of voltage rise of the fourth node N4. Further, the voltage of the second node N2 set to the floating state may rise by a voltage amount corresponding to the amount of voltage rise of the fifth node N5. Thus, the voltage of the second node N2 may be controlled corresponding to the amount of voltage rise of the fourth node N4 in the fifth period T5. Subsequently, the second transistor M2 may supply current, in an amount corresponding to the voltage applied to the second node N2, to the organic light emitting diode (OLED).

[0079] As in the first embodiment, the organic light emitting diode (OLED) may deteriorate over time. As the organic light emitting diode (OLED) deteriorates, the voltage applied to the organic light emitting diode (OLED) may rise, i.e., when the current is supplied to the organic light emitting diode (OLED), the voltage Voled applied to the organic light emitting diode (OLED) may rise as the organic light emitting diode (OLED) may rise as the organic light emitting diode (OLED) deteriorates. Then, the current amount supplied from the second transistor M2 to the organic light emitting diode (OLED) may increase for a given data signal. Thus, as the organic light emitting diode (OLED) deteriorates, the amount of current supplied from the second transistor M2 may increase so that a degradation in brightness due to the deterioration of the organic light emitting diode (OLED) may be compensated.

[0080] As described above, embodiments may com-

pensate for a deterioration in characteristics of an organic light emitting diode by controlling a voltage of a gate electrode of a driving transistor in correspondence with the deterioration of the organic light emitting diode. Further, the threshold voltage of the driving transistor may be compensated, such that images with uniform brightness may be displayed despite deviation in the threshold voltage.

## **Claims**

15

20

25

35

40

45

**1.** A pixel (140, 140') comprising:

an organic light emitting diode (OLED); a second transistor (M2) for supplying current to the organic light emitting diode (OLED); a pixel circuit (142, 142') for compensating for the threshold voltage of the second transistor (M2); and

a compensating unit (144, 144') for controlling the voltage of a gate electrode of the second transistor (M2) in order to compensate for a deterioration of the organic light emitting diode (OLED),

wherein the compensating unit (144, 144') includes:

seventh and eighth transistors (M7, M8) coupled between the organic light emitting diode (OLED) and a first power supply (ELVDD);

first and second feedback capacitors (Cfb1, Cfb2) positioned between a second node (N4), which is a common node of the seventh and eighth transistors (M7, M8), and a first node (N2) electrically coupled to the gate electrode of the second transistor (M2); and

a ninth transistor (M9) coupled between a third node (N5), which is a common node of the first and second feedback capacitors (Cfb1, Cfb2), and a predetermined voltage supply (ELVDD, Vint).

2. The pixel (140, 140') as claimed in claim 1, wherein the pixel circuit (142, 142') includes:

a first transistor (M1) coupled to an i<sup>th</sup> scan line (Si) and data line (Dj) and turned-on when a scan signal is supplied to the i<sup>th</sup> scan line (Si) to supply a data signal supplied to the data line (Dj) to the first electrode of the second transistor (M2); a third transistor (M3) coupled between the second electrode of the second transistor (M2) and the first node (N2) and turned-on when the scan signal is supplied to the i<sup>th</sup> scan line (Si); a fourth transistor (M4) coupled between an initialization power supply (Vint) and the first node (N2), and turned-on when the scan signal is supplied to an i-1<sup>th</sup> scan line (Si-1);

20

30

40

45

a fifth transistor (M5) coupled between the first electrode of the second transistor (M2) and the first power supply (ELVDD) and turned-on when a light emitting control signal is not supplied to an i<sup>th</sup> light emitting control line (Ei);

a sixth transistor (M6) coupled between the second electrode of the second transistor (M2) and the organic light emitting diode (OLED) and turned-on when the light emitting control signal is not supplied to the i<sup>th</sup> light emitting control line (Ei); and

a storage capacitor (Cst) coupled between the first node (N2) and the first power supply (ELVDD).

- 3. The pixel (140, 140') as claimed in claim 2, wherein the initialization power supply (Vint) is set to a voltage value lower than the data signal.

- **4.** The pixel (140, 140') as claimed in one of claims 2 or 3, wherein the seventh and eighth transistors (M7, M8) are alternatively turned-on and turned-off.

- 5. The pixel (140, 140') as clamed in claim 4, wherein the light emitting control signal supplied to the i<sup>th</sup> light emitting control line (Ei) is supplied to be overlapped with the scan signals supplied to the i-1<sup>th</sup> scan line (Si-1) and the i<sup>th</sup> scan line (Si).

- 6. The pixel (140, 140') as claimed in claim 5, wherein the seventh transistor (M7) is turned on when the scan signal is supplied to i+1<sup>th</sup> scan line (Si+1) to supply the voltage applied to the organic light emitting diode (OLED) to the second node (N4); and the eighth transistor (M8) is turned on when the light emitting control signal is not supplied to i+1<sup>th</sup> light emitting control line (Ei+1) to supply the voltage of the first power supply (ELVDD) to the second node (N4).

- 7. The pixel (140, 140') as claimed in claim 5, wherein the seventh transistor (M7) is turned on when the light emitting control signal is supplied to an i+2<sup>th</sup> light emitting control line (Ei+2) to supply the voltage applied to the organic light emitting diode (OLED) to the second node (N4); and the eighth transistor (M8) is turned on when the light emitting control signal is not supplied to an i+2<sup>th</sup> light emitting control line (Ei+2) to supply the voltage of the first power (ELVDD) supply to the second node (N4).

- 8. The pixel (140, 140') as claimed in claim 7, wherein the seventh transistor (M7) is formed in an NMOS, and the eighth transistor (M8) is formed in a PMOS.

- **9.** The pixel (140, 140') as claimed in claim 5, wherein the ninth transistor (M9) is turned on when the light

emitting control signal is supplied to i+1<sup>th</sup> light emitting control line (Ei+1) to maintain the voltage of the third node (N5) with the predetermined voltage supply (ELVDD, Vint).

- **10.** The pixel (140, 140') as claimed in claim 9, wherein the ninth transistor (M9) is formed in an NMOS.

- **11.** The pixel (140, 140') as claimed in claim 9, wherein the predetermined voltage supply (ELVDD, Vint) is any one of the first power supply (ELVDD) and the initialization power supply (Vint).

- **12.** An organic light emitting display device (100) including:

a scan driver (110) for sequentially supplying scan signals to scan lines (SO...Sn+1) and sequentially supplying light emitting control signals to light emitting control lines (E0...En+1); a data driver (120) for supplying data signals to data lines (D1...Dm); and pixels (140, 140') positioned in regions partitioned by the scan lines (SO...Sn+1) and the data lines (D1...Dm), characterised in that each of the pixels is a pixel according to one of the preceding claims.

- **13.** The organic light emitting display device (100) as claimed in claim 12, wherein the scan driver (110) supplies the light emitting control signals to an i<sup>th</sup> light emitting control line (Ei) to be overlapped with the scan signals supplied to an i-1<sup>th</sup> (i is a natural number) scan line (Si-1) and an i<sup>th</sup> scan line (Si).

- 14. An driving method of an organic light emitting display device (100), which includes first and second transistors (M7, M8) positioned between an anode electrode of an organic light emitting diode (OLED) and a first power supply (ELVDD); and first feedback and second feedback capacitors (Cfb1, Cfb2) positioned between a first node (N4), which is a common node of the first and second transistors (M7, M8); and a gate electrode of a driving transistor (M2), the driving method including the steps of:

initializing the voltage of the gate electrode of the driving transistor (M2) with the voltage of an initialization power supply (Vint);

charging the voltage corresponding to the threshold voltage of the driving transistor (M2) and a data signal in a storage capacitor (Cst) by connecting the driving transistor (M2) in the form of a diode;

supplying the current corresponding to the voltage charged in the storage capacitor (Cst) to the organic light emitting diode (OLED);

applying the voltage applied to the organic light emitting diode (OLED) to the first node (N4);

maintaining a second node (N5), which is a common terminal of the first and second feedback capacitors (Cfb1, Cfb2) at a constant voltage during the steps of charging the voltage in the storage capacitor (Cst) and the supplying the voltage applied to the organic light emitting diode (OLED) to the first node (N4); and controlling the voltage of the gate electrode of the driving transistor (M2) by setting the second node (N5) to the state of floating and at the same time, raising the voltage of the first node (N4) to the voltage of the first power supply (ELVDD).

- the voltage of the first power supply (ELVDD). **15.** The driving method of an organic light emitting display device (100) as claimed in claim 14, wherein the constant voltage is the voltage supplied from any

- **16.** The driving method of an organic light emitting display device (100) as claimed in one of claims 14 or 15, wherein the initialization power supply (Vint) is set to a voltage value lower than the data signal.

one of the initialization power supply (Vint) and the

first power supply (ELVDD).

17. The driving method of an organic light emitting display device (100) as claimed in one of the claims 14 through 16, wherein the first and second transistors (M7, M8) are alternatively turned-on and turned-off.

55

30

35

40

45

50

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

# **EUROPEAN SEARCH REPORT**

**Application Number** EP 08 15 4330

|                                                     | DOCUMENTS CONSIDERED                                                                                                                                                                                      | TO BE RELEVANT                                                                                                             |                                                                                    |                                            |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------|--|

| ategory                                             | Citation of document with indication of relevant passages                                                                                                                                                 | n, where appropriate,                                                                                                      | Relevant<br>to claim                                                               | CLASSIFICATION OF THE APPLICATION (IPC)    |  |

| 1                                                   | US 2006/022305 A1 (YAMA: [JP]) 2 February 2006 (2 * paragraphs [0016], [0 * paragraphs [0483] - [0483] + figures 2,3,38,39 *                                                                              | 2006-02-02)<br>9166] - [0194] *                                                                                            | 1,14                                                                               | INV.<br>G09G3/32                           |  |

| •                                                   | US 2004/174354 A1 (ONO 9<br>9 September 2004 (2004-1<br>* paragraphs [0051] - [0<br>* figures 1-3D *                                                                                                      | 9-09)                                                                                                                      | 1,14                                                                               |                                            |  |

|                                                     |                                                                                                                                                                                                           |                                                                                                                            |                                                                                    | TECHNICAL FIELDS<br>SEARCHED (IPC)<br>G09G |  |

|                                                     |                                                                                                                                                                                                           |                                                                                                                            |                                                                                    |                                            |  |

|                                                     | The present search report has been dra                                                                                                                                                                    | •                                                                                                                          |                                                                                    |                                            |  |

| Place of search                                     |                                                                                                                                                                                                           | Date of completion of the search                                                                                           |                                                                                    | Examiner                                   |  |

| X : part<br>Y : part<br>docu<br>A : tech<br>O : non | The Hague  ATEGORY OF CITED DOCUMENTS  icularly relevant if taken alone icularly relevant if combined with another iment of the same category inological background -written disclosure rmediate document | 5 June 2008  T: theory or principle E: earlier patent doc after the filing date D: document cited in L: document cited for | e underlying the i<br>sument, but publise<br>n the application<br>or other reasons | shed on, or                                |  |

## ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 08 15 4330

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

05-06-2008

| Patent document cited in search report     | Publication<br>date                                                                                |            | Patent family<br>member(s) |        | Publication<br>date      |  |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------|------------|----------------------------|--------|--------------------------|--|--|

| US 2006022305 A1                           | 02-02-2006                                                                                         | JP 2       | 2006309104                 | Α      | 09-11-2006               |  |  |

| US 2004174354 A1                           | 09-09-2004                                                                                         | JP 2<br>TW | 2004280059<br>239500       | A<br>B | 07-10-2004<br>11-09-2005 |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

|                                            |                                                                                                    |            |                            |        |                          |  |  |

| RM P0459                                   |                                                                                                    |            |                            |        |                          |  |  |

| Enr more details about this appear : coo   | For more details about this annex : see Official Journal of the European Patent Office, No. 12/82  |            |                            |        |                          |  |  |

| m i oi more details about this annex . see | more details about this differ . See Official countries of the European Faterit Office, 110. 12/02 |            |                            |        |                          |  |  |

| 专利名称(译)        | Plxel,使用其的有机发光显示器以及相关方法                                          |         |            |  |  |  |

|----------------|------------------------------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号        | EP1981018A1                                                      | 公开(公告)日 | 2008-10-15 |  |  |  |

| 申请号            | EP2008154330                                                     | 申请日     | 2008-04-10 |  |  |  |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                      |         |            |  |  |  |

| 申请(专利权)人(译)    | 三星SDI CO., LTD.                                                  |         |            |  |  |  |

| 当前申请(专利权)人(译)  | 三星移动显示器有限公司.                                                     |         |            |  |  |  |

| [标]发明人         | KIM YANG WAN                                                     |         |            |  |  |  |

| 发明人            | KIM, YANG-WAN                                                    |         |            |  |  |  |

| IPC分类号         | G09G3/32                                                         |         |            |  |  |  |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0852 G09G2320/043 G09G2320/045 |         |            |  |  |  |

| 代理机构(译)        | hengelhaupt , Jürgen                                             |         |            |  |  |  |

| 优先权            | 1020070035007 2007-04-10 KR                                      |         |            |  |  |  |

| 其他公开文献         | EP1981018B1                                                      |         |            |  |  |  |

| 外部链接           | Espacenet                                                        |         |            |  |  |  |

# 摘要(译)

像素,包括有机发光二极管,数据线和第一节点之间的第一晶体管,第一节点和第三节点之间的第二晶体管,第二节点和第三节点之间的第三晶体管,第四晶体管之间的第四晶体管第一电源和第一节点,第三节点和有机发光二极管之间的第五晶体管,初始化电源和第二节点之间的第六晶体管,第二节点和第一电源之间的存储电容器,第一第四节点和第二节点之间串联的第二反馈电容器,第四节点和有机发光二极管之间的第七晶体管,第一电源和第四节点之间的第八晶体管,以及第五节点之间的第九晶体管和预定的电压源。