(19)

(11)

**EP 1 923 857 B1**

(12)

## **EUROPEAN PATENT SPECIFICATION**

(45) Date of publication and mention

of the grant of the patent:

**08.01.2014 Bulletin 2014/02**

(51) Int Cl.:

**G09G 3/32 (2006.01)**

(21) Application number: **07120624.7**

(22) Date of filing: **14.11.2007**

---

### **(54) Pixel and organic light emitting diode display device**

Pixel und organische Leuchtdioden Anzeigevorrichtung

Pixel et dispositif d'affichage électroluminescent à diodes organiques

(84) Designated Contracting States:

**DE FR GB HU IT PL**

(30) Priority: **14.11.2006 KR 20060112223**

**19.12.2006 KR 20060130109**

(43) Date of publication of application:

**21.05.2008 Bulletin 2008/21**

(73) Proprietor: **Samsung Display Co., Ltd.**

**Yongin-City, Gyeonggi-Do, 446-711 (KR)**

Designated Contracting States:

**DE FR GB HU IT PL**

(72) Inventors:

- **Choi, Sang-moo**

**Gyeonggi-do (KR)**

- **Lee, Wang-jo**

**Gyeonggi-do (KR)**

(74) Representative: **Hengelhaupt, Jürgen et al**

**Gulde Hengelhaupt Ziebig & Schneider**

**Patentanwälte - Rechtsanwälte**

**Wallstrasse 58/59**

**10179 Berlin (DE)**

(56) References cited:

**EP-A- 1 130 565 EP-A- 1 496 495**

**WO-A-98/48403**

**EP 1 923 857 B1**

---

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

**Description**

## BACKGROUND OF THE INVENTION

5 1. Field of the Invention

**[0001]** Embodiments of the present invention relate to a pixel and an organic light emitting display device including the same. More specifically, embodiments of the present invention relate to a pixel capable of compensating for reduced luminance of a light emitting diode thereof, and an organic light emitting display device including the same.

10 2. Description of the Related Art

**[0002]** In general, flat panel displays, e.g., a liquid crystal display (LCD), a field emission display (FED), a plasma display panel (PDP), an electroluminescent (EL) display, and so forth, may have reduced weight and volume as compared to a cathode ray tube (CRT) display. For example, the EL display, e.g., an organic light emitting display device, may include a plurality of pixels, and each pixel may have a light emitting diode (LED). Each LED may include a light emitting layer emitting red (R), green (G), or blue (B) light triggered by combination of electrons and holes therein, so the pixel may emit a corresponding light to form images. Such an EL display may have rapid response time and low power consumption.

20 **[0003]** The conventional pixel of the EL display may be driven by a driving circuit configured to receive data and scan signals, and to control light emission from its LED with respect to the data signals. More specifically, an anode of the LED may be coupled to the driving circuit and a first power source, and a cathode of the LED may be coupled to a second power source. Accordingly, the LED may generate light having a predetermined luminance with respect to current flowing therethrough, while the current may be controlled by the driving circuit according to the data signal.

25 **[0004]** However, the material of the light emitting layer of the conventional LED, e.g., organic material, may deteriorate over time as a result of, e.g., contact with moisture, oxygen, and so forth, thereby reducing current/voltage characteristics of the LED and, consequently, deteriorating luminance of the LED. Further, each conventional LED may deteriorate at a different rate with respect to a composition of its light emitting layer, i.e., type of material used to emit different colors of light, thereby causing non-uniform luminance. Inadequate luminance, i.e., deteriorated and/or non-uniform, of the 30 LEDs may decrease display characteristics of the EL display device, and may reduce its lifespan and efficiency. A deterioration of an LED may result in an increased threshold voltage, i.e. the voltage across the LED at which a predetermined current may flow through the LED may increase when the LED deteriorates.

**[0005]** The international patent application WO 98/48403 A discloses a pixel circuit including compensation of threshold variation of the driving transistor. European patent application EP 1 496 495 A2 concerns a pixel circuit for an organic 35 light emitting device with self-compensation of threshold voltage of the driving transistor.

**[0006]** Furthermore, European patent application EP 1 130 565 A1 discloses a pixel circuit and a current drive circuit for driving the light emitting element comprised in the pixel circuit, wherein the current supplied to the light emitting element is controlled by a field effect transistor.

**[0007]** US patent application US 2006/0253755 A1 deals with a display unit comprising an organic light emitting diode 40 and a control circuit for adjusting the threshold voltage of the driving transistor.

## SUMMARY OF THE INVENTION

**[0008]** Embodiments of the present invention are therefore directed to a pixel and an organic light emitting display 45 device including the same, which substantially overcome one or more of the problems due to the limitations and disadvantages of the related art. It is therefore a feature of an embodiment of the present invention to provide a pixel with a compensation unit capable of compensating for inadequate luminance of its light emitting diode (LED).

**[0009]** It is another feature of an embodiment of the present invention to provide an organic light emitting display 50 device with pixels having compensation units capable of compensating for inadequate luminance of their LEDs. Accordingly, a first aspect of the invention provides a pixel comprising a storage capacitor, an organic light emitting diode, first and second transistors, and a compensation unit. The storage capacitor has a first electrode coupled to a first power source. The organic light emitting diode has a cathode coupled to a second power source. The first transistor has a first electrode coupled to a data line, a second electrode coupled to a second electrode of the storage capacitor, and a gate electrode coupled to a scan line. The second transistor has a first electrode coupled to the first power source, a gate electrode coupled to the second electrode of the first transistor, and a second electrode directly or indirectly coupled to an anode of the organic light emitting diode. The compensation unit is configured to sense a voltage at the anode of the organic light emitting diode and to provide a compensation voltage to the gate electrode of the second transistor. The compensation voltage is proportional to a voltage difference between a supplementary voltage and the voltage at the

anode of the organic light emitting diode. The compensation unit includes third and fourth transistors and a feedback capacitor. The third transistor has a first electrode coupled to the anode of the organic light emitting diode. The fourth transistor has a first electrode coupled to a supplementary voltage source and a second electrode coupled to a second electrode of the third transistor. The supplementary voltage source is adapted to provide the supplementary voltage.

5 The feedback capacitor has a first electrode coupled to the second electrode of the third transistor and a second electrode coupled to the gate electrode of the second transistor. The supplementary voltage source is either the scan line or a previous scan line.

[0010] One of the third and the fourth transistors may be an NMOS transistor and the remaining one of the third and the fourth transistors may be a PMOS transistor.

10 [0011] The pixel may further comprise a fifth transistor having a first electrode coupled to the second electrode of the second transistor and a second electrode coupled to the anode of the organic light emitting diode.

[0012] A second aspect of the present invention provides an organic light emitting diode display device, comprising a plurality of scan lines, a plurality of data lines, a plurality of pixels, each of the pixels being coupled to a corresponding one of the scan lines and of the data lines, a scan driver configured to supply scan signals via the scan lines, and a data driver configured to drive the data lines. Each pixel is a pixel according to the first aspect of the invention.

15 [0013] The scan driver may be further adapted to turn on the third transistor while turning off the fourth transistor during a first period and to turn off the third transistor while turning on the fourth transistor during a second period.

[0014] The plurality of pixels may comprise a plurality of first sub-pixels adapted to emit light of a first colour at a first emission efficiency and a plurality of second sub-pixels adapted to emit light of a second colour at a second emission efficiency. The second colour and the second emission efficiency are different from the first colour and the first emission efficiency, respectively. Then, each of the first sub-pixels may comprise a feedback capacitor having a first capacitance and each of the second sub-pixels may comprise a feedback capacitor having a second capacitance different from the first capacitance.

20 [0015] The first colour may be blue and the second colour may be either red or green. Alternatively, the first colour may be red and the second colour may be green. In both cases, the second capacitance may be larger than the first capacitance.

25 [0016] If the pixels comprise a fifth transistor as mentioned above, the fifth transistor may have a gate electrode coupled to a corresponding one of a plurality of light emitting control lines. Then, the scan driver may be further configured to provide emission control signals to the plurality of emission control lines.

30

## BRIEF DESCRIPTION OF THE DRAWINGS

[0017] The above and other features and advantages of the present invention will become more apparent to those of ordinary skill in the art by describing in detail exemplary embodiments thereof with reference to the attached drawings, 35 in which:

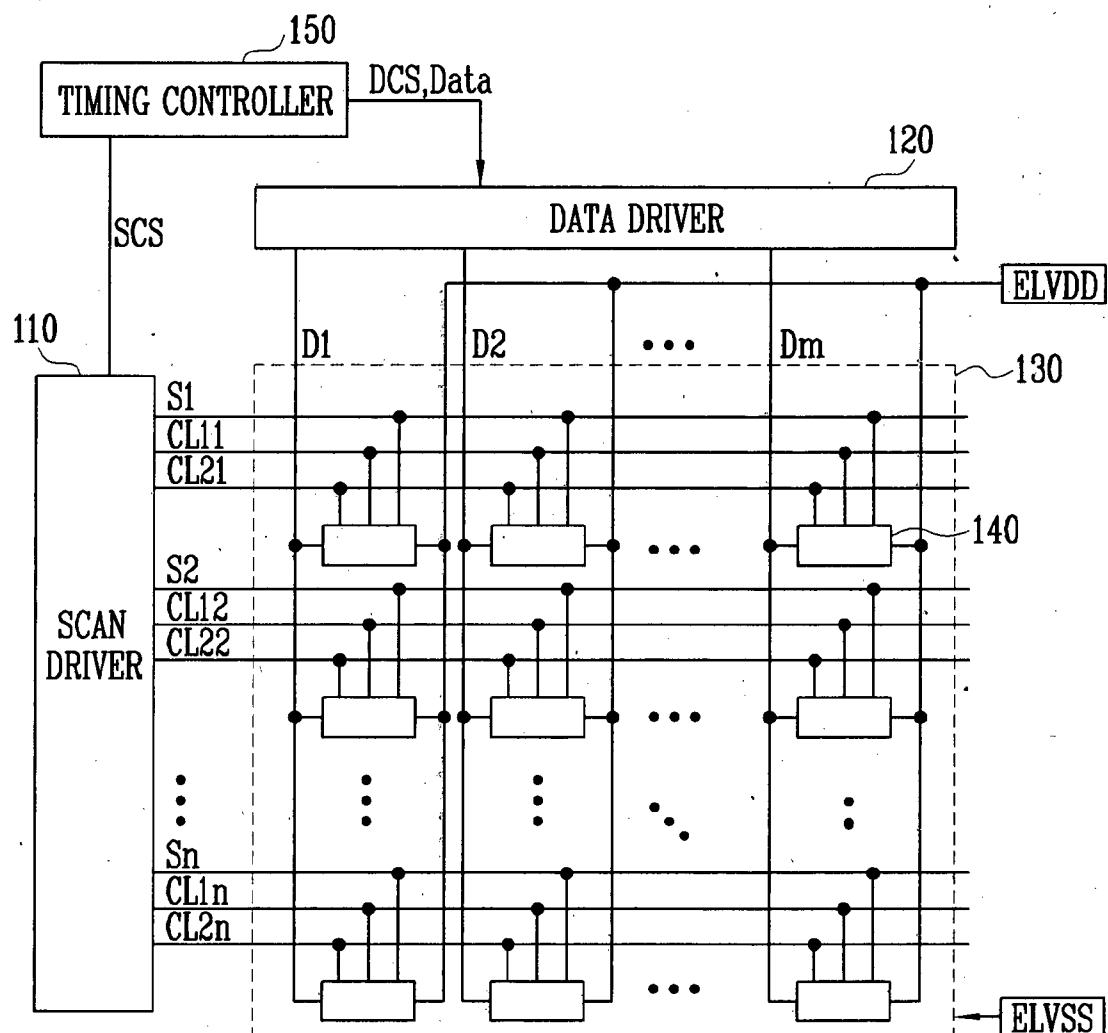

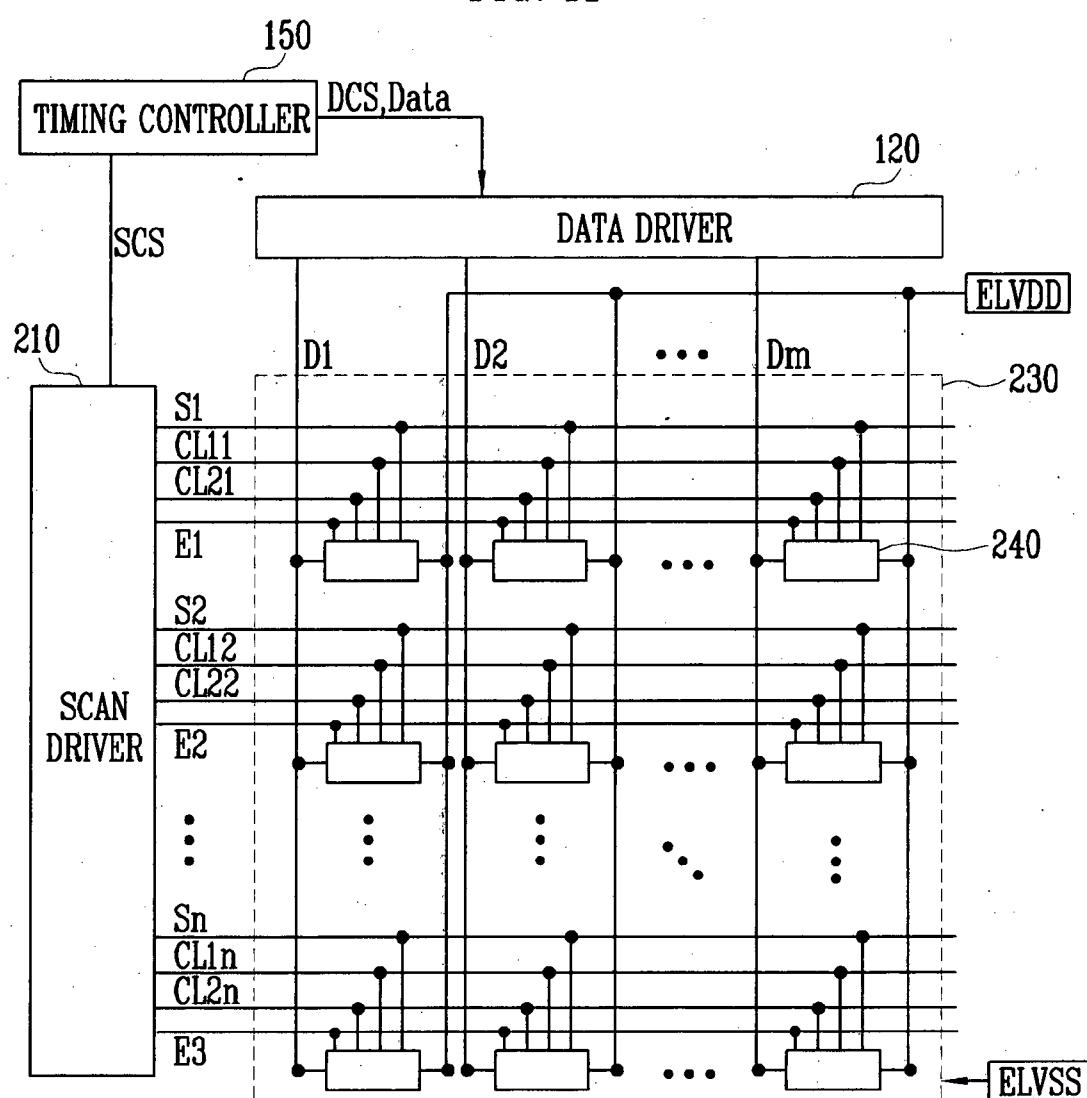

- FIG. 1 illustrates a schematic diagram of an organic light emitting display device according to an embodiment of the present invention;

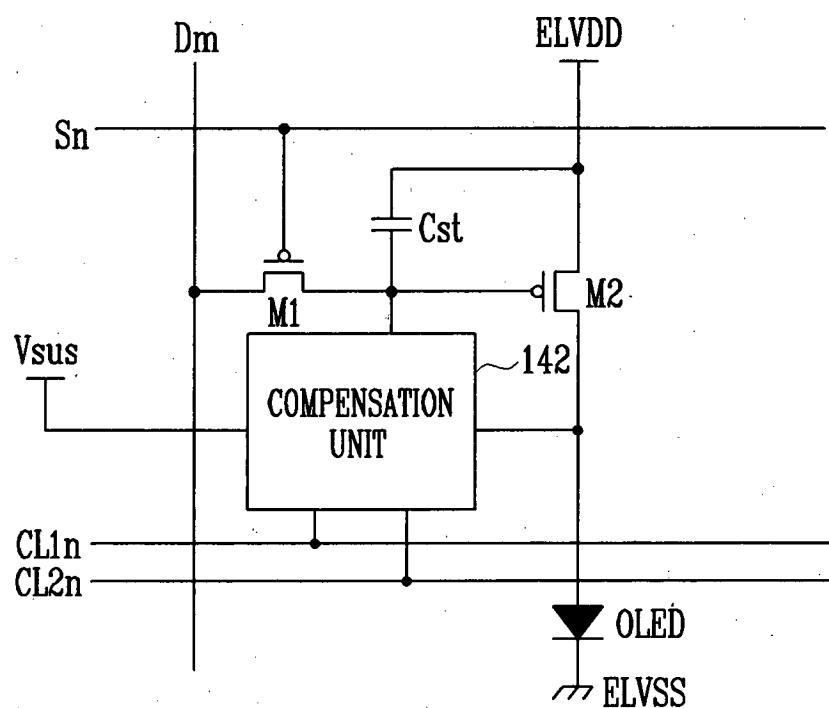

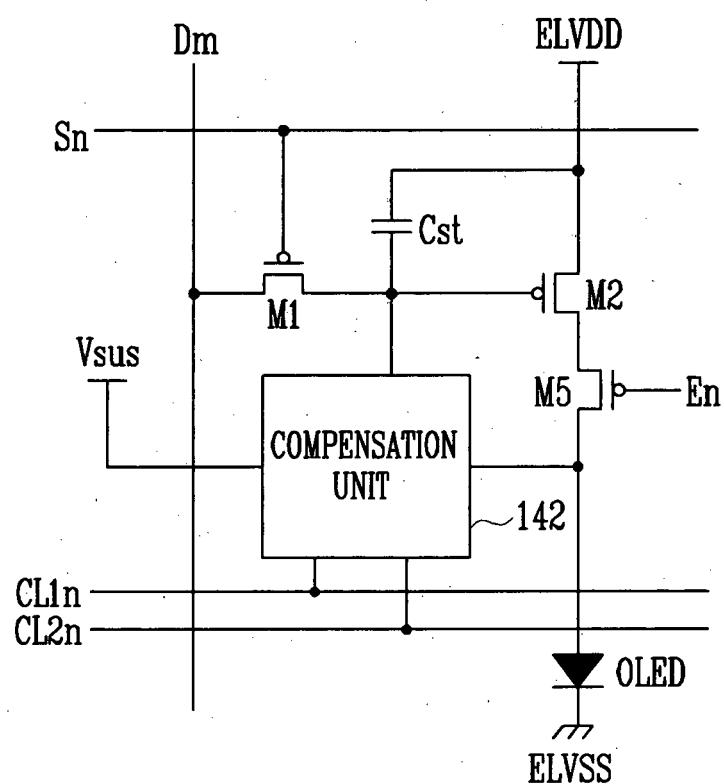

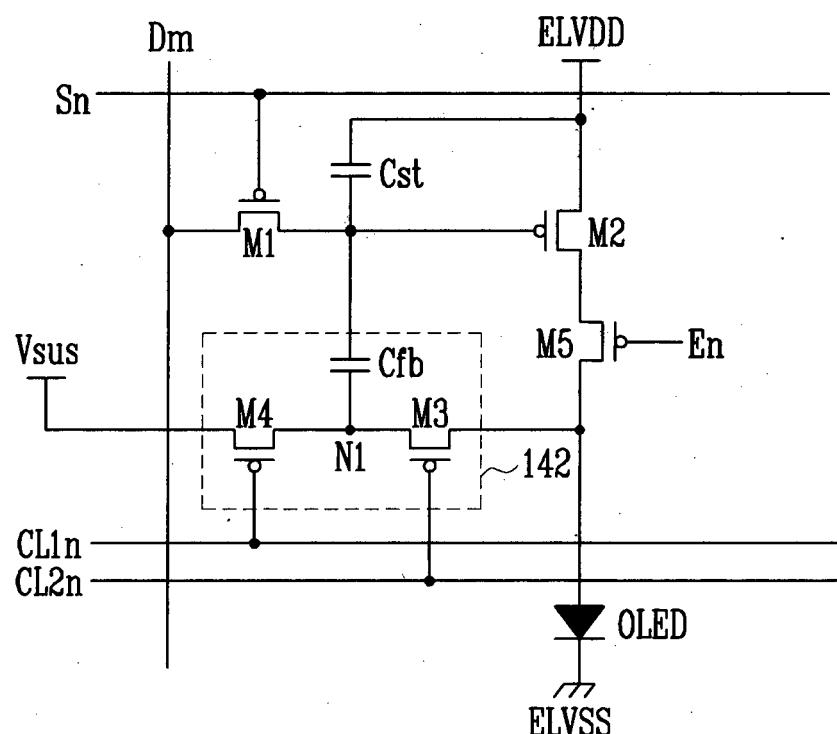

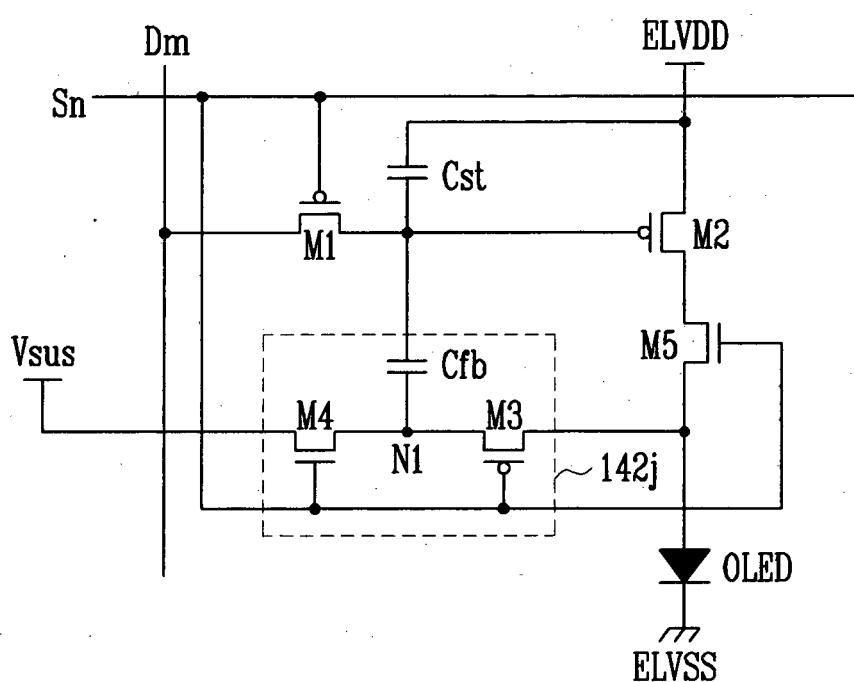

- 40 FIG. 2 illustrates a circuit diagram of a pixel in the organic light emitting display device of FIG. 1 according to an embodiment of the present invention;

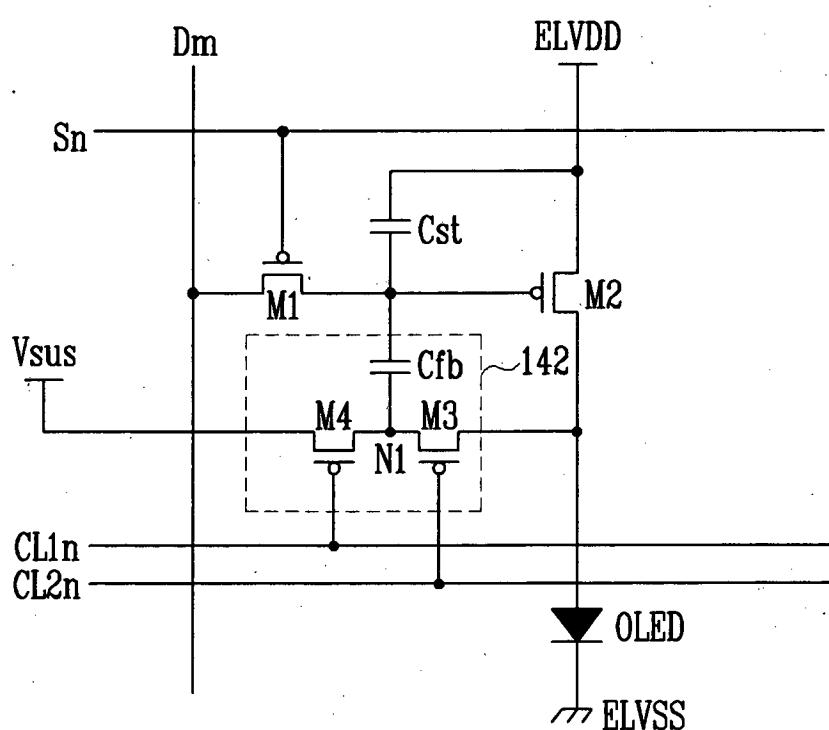

- FIG. 3 illustrates a detailed circuit diagram of a compensation unit in the pixel of FIG. 2 according to an embodiment of the present invention;

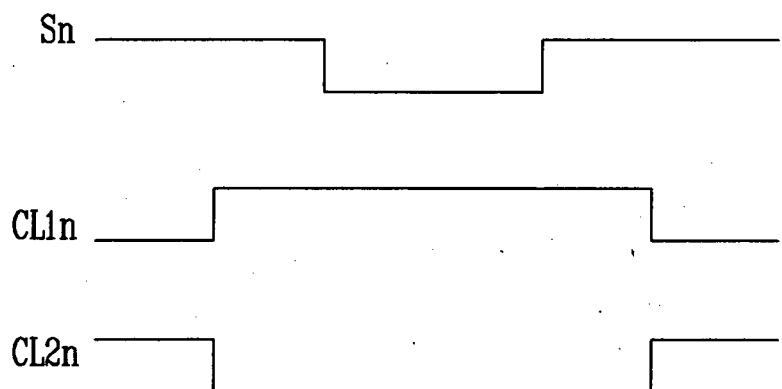

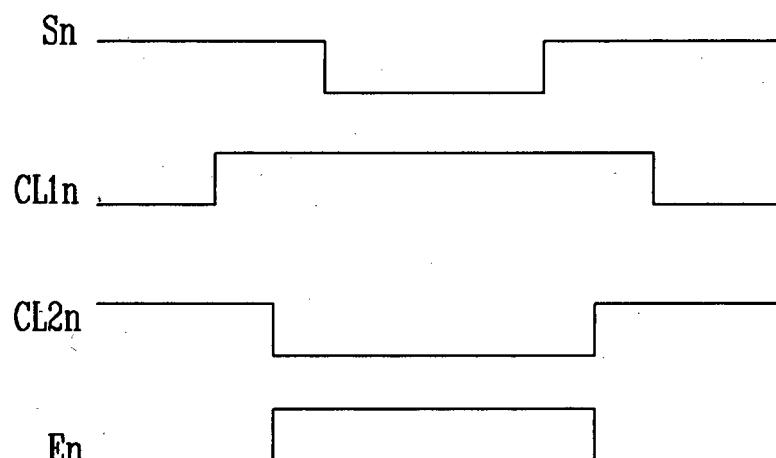

- 45 FIG. 4 illustrates a waveform diagram of signals in the circuit diagram of FIG. 2.

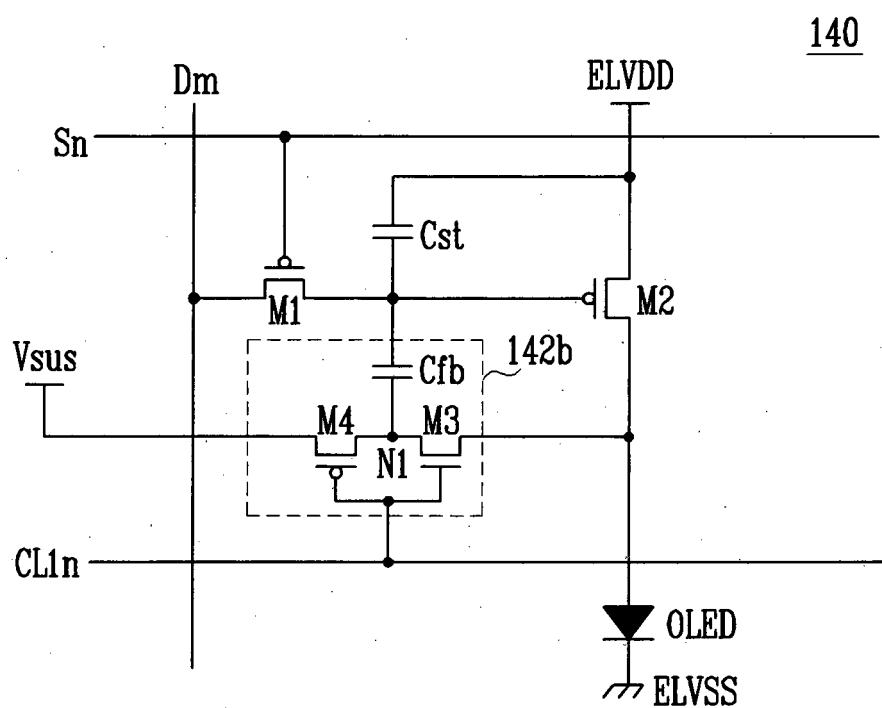

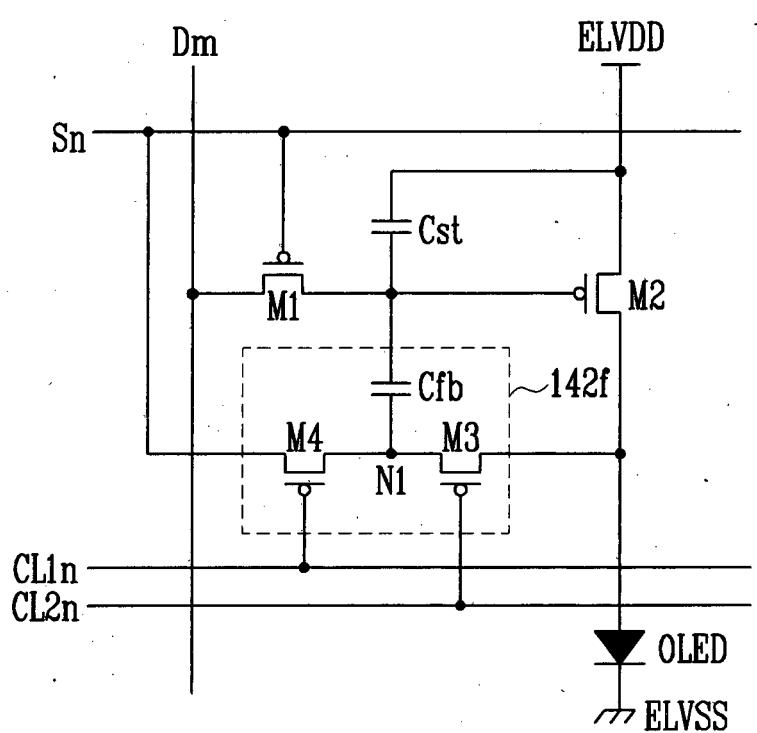

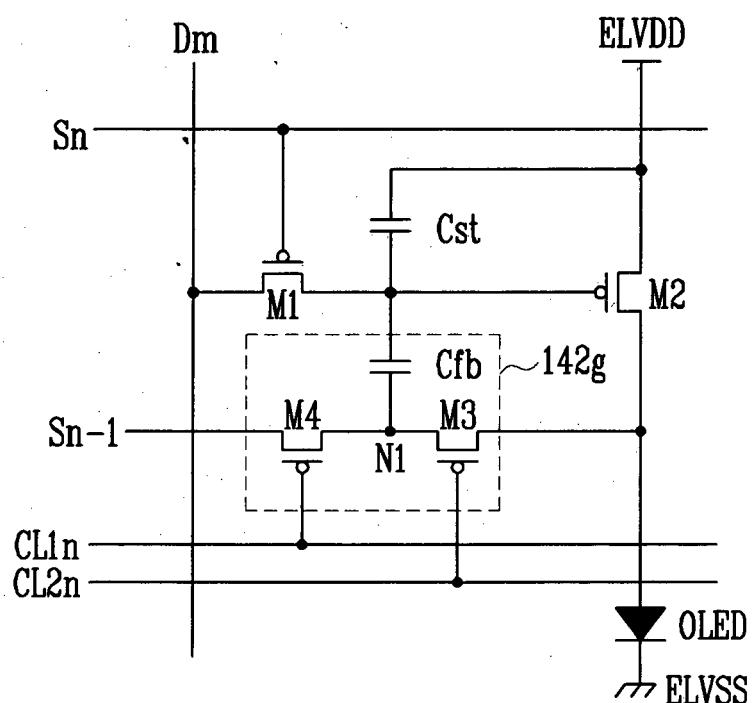

- FIG. 5 illustrates a detailed circuit diagram of a compensation unit in the pixel in FIG. 2 according to another embodiment of the present invention;

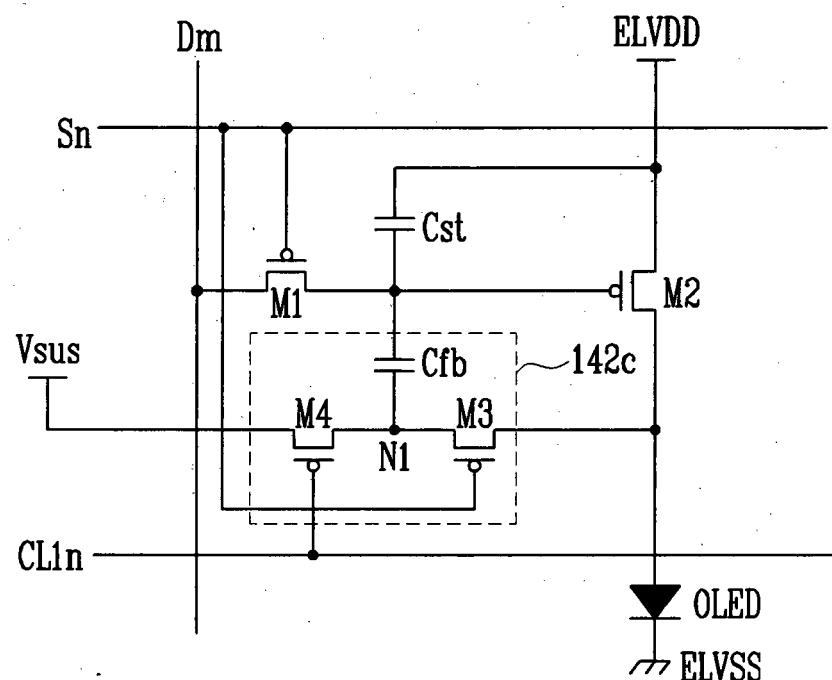

- FIG. 6 illustrates a detailed circuit diagram of a compensation unit in the pixel in FIG. 2 according to another embodiment of the present invention;

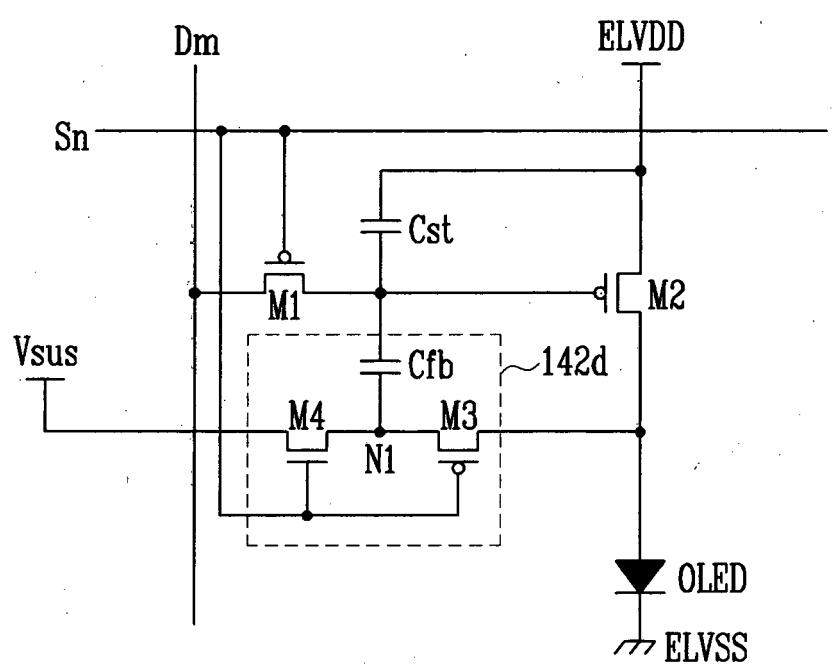

- 50 FIG. 7 a detailed circuit diagram of a compensation unit in the pixel in FIG. 2 according to another embodiment of the present invention;

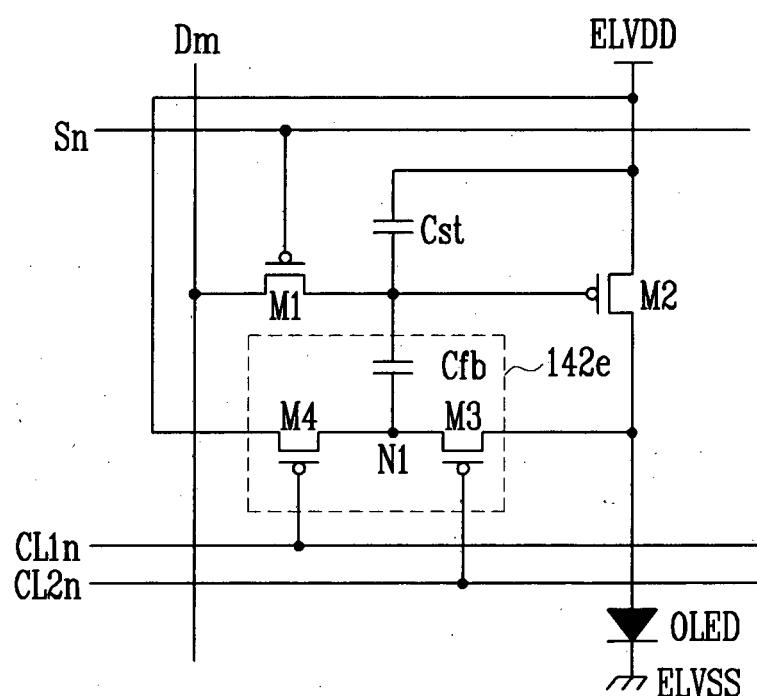

- FIG. 8 illustrates a detailed circuit diagram of a compensation unit in the pixel in FIG. 2 according to a comparative example which is not part of the present invention;

- FIG. 9 illustrates a detailed circuit diagram of a compensation unit in the pixel in FIG. 2 according to another embodiment of the present invention;

- 55 FIG. 10 illustrates a detailed circuit diagram of a compensation unit in the pixel in FIG. 2 according to another embodiment of the present invention;

- FIG. 11 illustrates a schematic diagram of an organic light emitting display device according to another embodiment of the present invention;

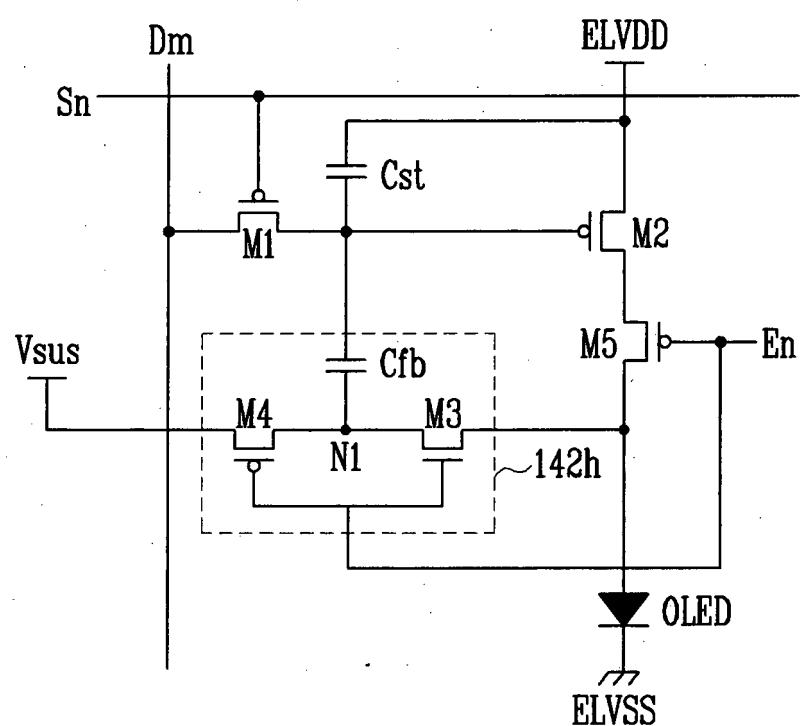

- FIG. 12 illustrates a circuit diagram of a pixel in the organic light emitting display device of FIG. 11 according to an

embodiment of the present invention;

FIG. 13 illustrates a detailed circuit diagram of a compensation unit in the pixel of FIG. 12 according to an embodiment of the present invention;

FIG. 14 illustrates a waveform diagram of signals in the circuit diagram of FIG. 12;

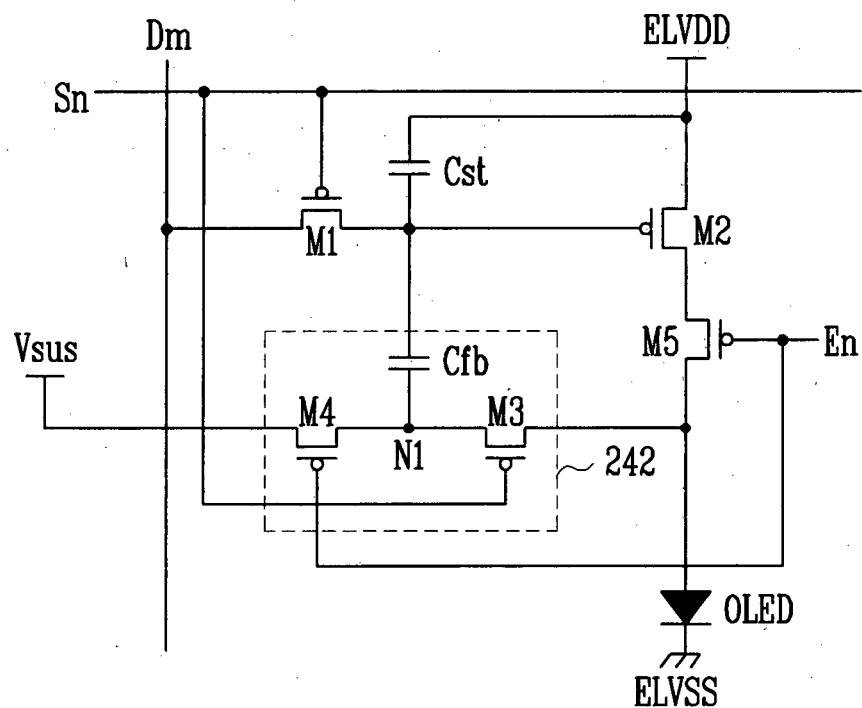

5 FIG. 15 illustrates a detailed circuit diagram of a compensation unit in the pixel in FIG. 12 according to another embodiment of the present invention;

FIG. 16 illustrates a detailed circuit diagram of a compensation unit in the pixel in FIG. 12 according to another embodiment of the present invention; and

10 FIG. 17 illustrates a detailed circuit diagram of a compensation unit in the pixel in FIG. 12 according to another embodiment of the present invention.

## DETAILED DESCRIPTION OF THE INVENTION

15 [0018] Embodiments of the present invention will now be described more fully hereinafter with reference to the accompanying drawings, in which exemplary embodiments of the invention are illustrated. Aspects of the invention may, however, be embodied in different forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the invention to those skilled in the art.

20 [0019] In the figures, the dimensions of elements and regions may be exaggerated for clarity of illustration. It will also be understood that when an element is referred to as being "on" another element, it can be directly on the other layer or substrate, or intervening layers may also be present. Further, it will also be understood that when an element is referred to as being "between" two elements, it can be the only element between the two elements, or one or more intervening elements may also be present. In addition, when an element is referred to as being "coupled to" another element, it can be directly connected to another element or be indirectly connected to another element with one or more intervening elements interposed therebetween. Like reference numerals refer to like elements throughout.

25 [0020] Referring to FIG. 1, an organic light emitting display device according to an embodiment of the present invention may include a pixel unit 130 having a plurality of pixels 140, a scan driver 110 to drive scan lines S1 to Sn, first control lines CL11 to CL1n, and second control lines CL21 to C2n, a data driver 120 to drive data lines D1 to Dm, and a timing controller 150 for controlling the scan driver 110 and the data driver 120. The pixels 140 of the pixel unit 130 may be arranged in any suitable pattern, so each pixel 140 may be coupled to a scan line S1 to Sn, a first control line CL11 to CL1n, a second control line CL21 to C2n, and/or a data line D1 to Dm, as illustrated in FIG. 1.

30 [0021] The scan driver 110 of the organic light emitting display device may receive a scan drive control signal SCS from the timing controller 150, and may generate a corresponding scan signal to be supplied to the scan lines S1 to Sn. Also, the scan driver 110 may generate first and second control signals in response to the received SCS, and may supply 35 the generated first and second control signals to the first and second control lines CL11 to CL1n and CL21 to CL2n, respectively. The first and second control signals may have substantially same lengths, and may be opposite to one another. The scan signal may be shorter than and completely overlap with each of its corresponding first and second control signals, as will be described in more detail below with respect to FIG. 4. In this respect, it is noted that a length 40 of a signal hereinafter may refer to a width of a single pulse along a horizontal axis, as illustrated in FIGS. 4 and 14. It is further noted an "overlap" as related to signals refers hereinafter to an overlap with respect to time.

[0022] The data driver 120 of the organic light emitting display device may receive a data drive control signal DCS from the timing controller 150, and may generate a corresponding data signal to be supplied to the data lines D1 to Dm.

[0023] The timing controller 150 of the organic light emitting display device may generate synchronized DCS and SCS signals to be supplied to the data driver 120 and the scan driver 110, respectively. Additionally, the timing controller 150 45 may transmit data information from an external source to the data driver 120.

[0024] The pixel unit 130 may be coupled to a first power source ELVDD and to a second power source ELVSS, so voltage of each of the first and second power sources ELVDD and ELVSS may be supplied to each of the pixels 140. Accordingly, each of the pixels 140 receiving voltage from the first and second power sources ELVDD and ELVSS may generate light in accordance with the data signal supplied thereto. A compensation unit 142 may be installed in each of the pixels 140 to compensate for a deterioration degree of the organic light emitting diode, as will be described in more detail below with respect to FIGS. 2-3. In this respect it is noted that "deterioration degree" refers to a measure of a reduced amount of voltage at the anode of the organic light emitting diode in which a substantially high level of total current has passed, as compared to an amount of voltage at an anode of an organic light emitting diode in which a substantially low level of total current has passed.

55 [0025] Referring to FIG. 2, each pixel 140 may include an organic light emitting diode OLED and a driving circuit capable of controlling current supplied to the OLED, so light emitted by the OLED may correspond to a data signal supplied to the pixel 140. The driving circuit may include a first transistor M1, a second transistor M2, a storage capacitor Cst, and a compensation unit 142. An anode electrode of the OLED may be coupled to the second transistor M2, and

a cathode electrode of the OLED may be coupled to the second power source ELVSS, so the OLED may generate a predetermined luminance with respect to the electric current supplied by the second transistor M2. The second transistor M2 may be referred to as a driving transistor.

**[0026]** The first transistor M1 may have its gate electrode coupled to the scan line Sn, and may have its first and second electrodes coupled to the data line Dm and gate electrode of the second transistor M2, respectively. The first transistor M1 may be turned on when a scan signal is supplied to its gate electrode, so a data signal may be supplied through the data line Dm to the second electrode of the first transistor M1 to be transmitted through the first electrode of the first transistor M1 to the gate electrode of the second transistor M2. In this respect, it is noted that a first electrode of a transistor refers to either one of the source and/or drain thereof, so a second electrode of a transistor refers to a corresponding drain and/or source thereof. In other words, if a first electrode is a source, the second electrode is a drain, and vice versa.

**[0027]** The second transistor M2 may have its gate electrode coupled to a second electrode of the first transistor M1, and may have its first and second electrodes coupled to the first power source ELVDD and the anode electrode of the OLED, respectively. The second transistor M2 may receive the data signal from the first transistor M1, and may control current flowing from the first power source ELVDD to the second power source ELVSS via the OLED to correspond to the data signal received from the first transistor M1. In other words, the OLED may generate light in accordance with a voltage at the gate electrode of the second transistor M2. Voltage of the first power source ELVDD may be set to be higher than voltage of the second power source ELVSS.

**[0028]** The storage capacitor Cst may be coupled between the gate electrode of the second transistor M2 and the first power source ELVDD, so the storage capacitor Cst may store voltage corresponding to the data signal transmitted from the first transistor M1 to the second transistor M2.

**[0029]** The compensation unit 142 may be coupled to the gate electrode of the second transistor M2 to adjust voltage thereof upon deterioration of the OLED. More specifically, the compensation unit 142 may be coupled to a voltage source Vsus, a first control line CL1n, and a second control line CL2n, so the voltage source Vsus may be used to adjust the voltage at the gate electrode of the second transistor M2 with respect to signals received from the first and second control lines CL1n and CL2n, as will be discussed in more detail below with respect to FIG. 3. Accordingly, a voltage of the voltage source Vsus may be higher than a voltage Voled at the anode electrode of the OLED and corresponding to an electric current flowing through the OLED, but may be lower than the first power source ELVDD in order to generate sufficient luminance in the pixel 140.

**[0030]** Referring to FIG. 3, the compensation unit 142 may include a third transistor M3 and a fourth transistor M4 arranged between the voltage source Vsus and an anode electrode of the OLED, and a feedback capacitor Cfb between a first node N1 and the gate electrode of the second transistor M2. The first node N1 may be a common node of the third and fourth transistors M3 and M4, so the feedback capacitor Cfb may account for a change in voltage between the first node N1 and the second transistor M2.

**[0031]** As illustrated in FIGS. 3-4, the third transistor M3 may be coupled between the first node N1 and the anode electrode of the OLED, and may be controlled by a second control signal supplied by the second control line CL2n. The fourth transistor M4 may be coupled between the first node N1 and the voltage source Vsus, and may be controlled by a first control signal supplied by the first control line CL1n. The first and second control signals may be supplied to the gate electrodes of the fourth and third transistors M4 and M3, respectively, before a scan signal is supplied to the scan line Sn, so the fourth transistor M4 may be turned off and the third transistor M3 may be turned on. When the fourth transistor M4 is turned off and the third transistor M3 is turned on, the voltage Voled may be supplied to the first node N1.

**[0032]** Once the voltage Voled is supplied to the first node N1, the scan signal may be supplied via the scan line Sn to the first transistor M1 to turn on the first transistor M1. Once the first transistor M1 is turned on, voltage corresponding to the data signal supplied via the data line Dm may be stored in the storage capacitor Cst, followed by suspension of the scan signal. In other words, once voltage is stored in the storage capacitor Cst, the first transistor M1 may be turned off.

**[0033]** After the first transistor M1 is turned off, the first and second control signals may be inverted, as further illustrated in FIG. 4, so the fourth transistor M4 may be turned on and the third transistor M3 may be turned off. If the fourth transistor M4 is turned on, the voltage at the first node N1 may increase from Voled to the voltage of the voltage source Vsus. Once the voltage at the first node N1 is increased, voltage at the gate electrode of the second transistor M2 may also increase. In particular, the increased voltage value at the gate electrode of the second transistor M2 may be determined according to the relationship illustrated in Equation 1 below,

$$\Delta V_{M2\_gate} = \Delta V_{N1} \times (Cfb / (Cst + Cfb)) \quad \text{Equation 1}$$

where  $\Delta V_{M2\_gate}$  represents the change in the voltage of the gate electrode of the second transistor M2, and  $\Delta V_{N1}$

represents the change in the voltage of the first node N1.

**[0034]** As can be seen in Equation 1, voltage at the gate electrode of the second transistor M2 may vary with respect to the change in the voltage at the first node N1. The compensation unit 142 thus acts as a negative feedback loop for variations of the voltage  $V_{oled}$  of the OLED which may change due to deterioration. When  $V_{oled}$  increases, the voltage change at the first node N1 decreases if  $V_{sus}$  is set to a higher voltage than  $V_{oled}$ . Thus, the voltage at the gate electrode of the second transistor M2 is increased less with an increasing  $V_{oled}$ . Hence, the current provided by the second transistor M2 is decreased less for a higher threshold voltage  $V_{oled}$  (aging OLED) than for a lower  $V_{oled}$  (fresh OLED) thereby compensating for the decreased luminance efficiency of the aging OLED. Accordingly, when voltage at the first node N1 is increased to correspond to the voltage of the voltage source  $V_{sus}$ , voltage at the gate electrode of the second transistor M2 may also increase according to Equation 1 above. The increased voltage at the gate electrode of the second transistor M2 may decrease the electric current, i.e., from the first power source ELVDD to the second power source ELVSS, via the OLED in order to maintain a predetermined luminance thereof. In other words, the OLED may be configured to generate light having a predetermined luminance corresponding to the voltage at the gate electrode of the second transistor M2. Accordingly, the current capacity of the second transistor M2 may correspond to the data signal, i.e., voltage stored in the storage capacitor  $C_{st}$ , and may be adjusted to a higher value when the OLED is deteriorated, so the luminance generated by the OLED may be constant regardless of its deterioration degree.

**[0035]** Additionally, each pixel 140 may be set to have a feedback capacitor  $C_{fb}$  having a capacity corresponding to a color emitted by its respective OLED. In other words, each OLED of a pixel 140 may include a different light emitting material with a different relative lifespan length corresponding to a specific composition of its light emitting layer, i.e., material emitting green G, red R, or blue B lights. Since pixels emitting G, R, and B light, as illustrated in Equation 2 below, may have different lifespans, adjusting capacity of the feedback capacitors  $C_{fb}$  with respect to specific materials to impart a substantially uniform deterioration rate to all the pixels 140 may provide substantially uniform lifespan characteristics to all the pixels 140.

25

$$(B \text{ Pixels})_{\text{LifeSpan}} < (R \text{ Pixels})_{\text{LifeSpan}} < (G \text{ Pixels})_{\text{LifeSpan}} \quad \text{Equation 2}$$

**[0036]** For example, since B Pixels may have a shorter lifespan, as compared to the R and/or G Pixels, the capacity of the feedback capacitor  $C_{fb}$  in each B Pixel may be set to have a higher capacity value, as compared to the feedback capacitors  $C_{fb}$  of the R and/or G Pixels. The capacity of the feedback capacitor  $C_{fb}$  in each pixel 140 may be determined according to a material used in the corresponding light emitting layer of the OLED, so non-uniform deterioration of multiple OLEDs of pixels 140 emitting different light colors may be compensated for.

**[0037]** According to another embodiment illustrated FIG. 5, a compensation unit 142b may be substantially similar to the compensation unit 142 described previously with respect to FIG. 3 with the exception of being coupled to a single control line. More specifically, the compensation unit 142b may include the feedback capacitor  $C_{fb}$  and the third and fourth transistors M3 and M4 in a substantially same configuration described previously with respect to FIG. 3, with the exception of having the first control line CL1n coupled to both the third and fourth transistors M3 and M4. Accordingly, the first control line CL1n may control both the third and fourth transistors M3 and M4.

**[0038]** More specifically, the third transistor M3 may have an opposite conductivity as compared to the first, second, and fourth transistors M1, M2, and M4. For example, as illustrated in FIG. 5, the third and fourth transistors M3 and M4 may be NMOS-type and PMOS-type transistors, respectively. Accordingly, a first control signal supplied to the first control line CL1n may turn on the third transistor M3 and turn off the fourth transistor M4. Similarly, when supply of the first control signal to the first control line CL1n is suspended, operational states of the third and fourth transistors M3 and M4 may be reversed, i.e., the third transistor M3 may be turned off and the fourth transistor M4 may be turned on. The compensation unit 142b illustrated in FIG. 5 may be advantageous in providing a circuit driven by a single control line, i.e., the second control line CL2n illustrated in FIG. 3, may be removed. Operation of the compensation unit 142b may be substantially similar to operation of the compensation unit 142 described previously with respect to FIG. 4, and may be illustrated with reference to FIG. 4. More specifically, a first control signal may be supplied to the first control line CL1n before a scan signal is supplied to the scan line  $S_n$ , thereby turning off the fourth transistor M4 and turning on the third transistor M3. When the third transistor M3 is turned on, the voltage  $V_{oled}$  of the OLED may be supplied to the first node N1.

**[0039]** Then, the scan signal may be supplied to the scan line  $S_n$ , thereby turning on the first transistor M1. When the first transistor M1 is turned on, the voltage corresponding to the data signal supplied to the data line  $D_m$  may be stored in the storage capacitor  $C_{st}$ , followed by suspension of the scan signal, thereby turning off the first transistor M1. Once the first transistor M1 is turned off, the first control signal to the first control line CL1n may be suspended, thereby turning off the third transistor M3 and turning on the fourth transistor M4. When the fourth transistor M4 is turned on, the voltage

at the first node N1 may increase to the voltage of the voltage source Vsus, so the voltage of the gate electrode of the second transistor M2 may also increase. The increase of voltage at the first node N1 and the second transistor M2 may be adjusted to compensate for deterioration of the OLED, thereby minimizing decrease of luminance thereof.

**[0040]** According to another embodiment illustrated FIG. 6, a compensation unit 142c may be substantially similar to the compensation unit 142 described previously with respect to FIG. 3, with the exception of being coupled to a single control line and the scan line Sn. More specifically, the compensation unit 142c may include the feedback capacitor Cfb and the third and fourth transistors M3 and M4 in a substantially same configuration described previously with respect to FIG. 3, with the exception of having the third transistor M3 coupled to the scan line Sn, as opposed to being coupled to the second control line CL2n. Accordingly, the third transistor M3 may be controlled by a scan signal supplied from the scan line Sn, and the fourth transistor M4 may be controlled by the first control signal supplied from the first control line CL1n. The compensation unit 142c illustrated in FIG. 6 may be advantageous in providing a circuit driven by a single control line, i.e., the second control line CL2n illustrated in FIG. 3 may be removed. Operation of the compensation unit 142c may be substantially similar to operation of the compensation unit 142 described previously with respect to FIG. 3, and may be illustrated with reference to FIG. 4. More specifically, a first control signal, i.e., a high signal, may be supplied to the first control line CL1n to turn the fourth transistor M4 off. The first control signal may be supplied before a scan signal is supplied to the scan line Sn.

**[0041]** While the first control signal is supplied to the first control line CL1n, a scan signal to the scan line Sn may be initiated, so the first and third transistors M1 and M3 may be turned on. When the first transistor M1 is turned on, the data signal Dm may be transmitted through the first transistor M1, and may be stored in the storage capacitor Cst. Simultaneously, since the third transistor M3 is turned on, the voltage Voled of the OLED may be supplied to the first node N1. Once voltage corresponding to the data signal is stored in the storage capacitor Cst, and voltage Voled is supplied to the first node N1, the scan signal may be suspended, so the first and third transistors M1 and M3 may be turned off.

**[0042]** After the first transistor M1 and the third transistor M3 are turned off, the fourth transistor M4 may be turned on by the first control signal. Once the fourth transistor M4 is turned on, voltage at the first node N1 may increase to a voltage of the voltage source Vsus, thereby triggering voltage increase at the gate electrode of the second transistor M2 according to Equation 1. Accordingly, it is possible to compensate for deterioration of the OLED by adjusting the voltage increase at the gate electrode of the second transistor M2.

**[0043]** According to another embodiment illustrated in FIG. 7, a compensation unit 142d may be substantially similar to the compensation unit 142 described previously with respect to FIG. 3, with the exception of being coupled to the scan line Sn, as opposed to being coupled to first and second control lines CL1n and CL2n. More specifically, the compensation unit 142d may include the feedback capacitor Cfb and the third and fourth transistors M3 and M4 in a substantially same configuration described previously with respect to FIG. 3, with the exception that both the third and fourth transistors M3 and M4 may be coupled to and controlled by the scan line Sn.

**[0044]** More specifically, the fourth transistor M4 may have an opposite conductivity as compared to the first transistor M1. For example, as illustrated in FIG. 7, the third and fourth transistors M3 and M4 may be PMOS-type and NMOS-type transistors, respectively. Accordingly, the fourth transistor M4 may be turned off when a (low-level) scan signal is supplied to the scan line Sn, and may be turned on when the scan signal is not supplied to the scan line Sn. Operation of the third transistor M3 may be opposite to operation of the fourth transistor with respect to the scan signal. The compensation unit 142d illustrated in FIG. 7 may be advantageous in providing a circuit driven by the scan line Sn, so the first control line CL1n and the second control line CL2n may be removed.

**[0045]** Operation of the compensation unit 142d will be described in detail below. First, a scan signal may be supplied to the scan line Sn, so the first and third transistors M1 and M3 may be turned on, while the fourth transistor M4 may be turned off. Accordingly, voltage corresponding to the data signal supplied to the data line Dm may be stored in the storage capacitor Cst, and voltage Voled may be supplied to the first node N1. Next, the scan signal may be suspended.

**[0046]** Once supply of the scan signal is suspended, the first and third transistors M1 and M3 may be turned off, and the fourth transistor M4 may be turned on. Subsequently, voltage at the first node N1 may increase to voltage of the voltage source Vsus, thereby triggering voltage increase at the gate electrode of the second transistor M2 according to Equation 1. Accordingly, it is possible to compensate for deterioration of the OLED by adjusting the voltage increase at the gate electrode of the second transistor M2.

**[0047]** It is noted that even though embodiments illustrated in FIGS. 3-7 included the voltage source Vsus as a voltage source coupled to the fourth transistor M4, other voltage sources for the fourth transistor M4, e.g., embodiments described with respect to FIGS. 8-10 below, are within the scope of the present invention. Accordingly, each of the embodiments illustrated in FIGS. 3-7 may be configured to include coupling of the fourth transistor M4 to a voltage source other than the voltage source Vsus.

**[0048]** For example, according to a comparative example illustrated in FIG. 8, a compensation unit 142e may be substantially similar to the compensation unit 142 described previously with respect to FIG. 3, with the exception of having the fourth transistor M4 coupled to the first power source ELVDD, as opposed to being coupled to the voltage

source  $V_{sus}$ . Accordingly, voltage at the first node N1 may be increased from the voltage  $V_{oled}$  to voltage of the first power source ELVDD, so voltage at the gate electrode of the second transistor M2 may be increased with respect to Equation 1 to compensate for deterioration of the OLED even when the fourth transistor M4 is not coupled to the voltage source  $V_{sus}$ . According to another embodiment illustrated FIG. 9, a compensation unit 142f may be substantially similar to the compensation unit 142 described previously with respect to FIG. 3, with the exception of having the fourth transistor M4 coupled to the scan line  $S_n$ , as opposed to being coupled to the voltage source  $V_{sus}$ . More specifically, the compensation unit 142f may include the feedback capacitor  $C_{fb}$  and the third and fourth transistors M3 and M4 in a substantially same configuration described previously with respect to FIG. 3, with the exception of using voltage corresponding to the scan signal, i.e., an inverted voltage signal, in the scan line  $S_n$  when the fourth transistor M4 is turned on, as illustrated in FIGS. 4 and 9. Accordingly, voltage at the first node N1 may be increased from the voltage  $V_{oled}$  to voltage of the scan line  $S_n$ , so deterioration of the OLED may be stably compensated for. In this respect, it is noted that voltage of the scan lines in the organic light emitting display device  $S_n$  may be set to be higher than voltage  $V_{oled}$ . According to another embodiment illustrated in FIG. 10, a compensation unit 142g may be substantially similar to the compensation unit 142 described previously with respect to FIG. 3 with the exception of having the fourth transistor M4 coupled to a previous scan line  $S_{n-1}$ , i.e., a scan line of an adjacent pixel, as opposed to being coupled to the voltage source  $V_{sus}$ . More specifically, the compensation unit 142g may include the feedback capacitor  $C_{fb}$  and the third and fourth transistors M3 and M4 in a substantially same configuration described previously with respect to FIG. 3, with the exception of using voltage corresponding to the scan signal, i.e., an inverted voltage signal, in the previous scan line  $S_{n-1}$  when the fourth transistor M4 is turned on, as illustrated in FIGS. 4 and 10. Accordingly, voltage at the first node N1 may be increased from the voltage  $V_{oled}$  to voltage of the previous scan line  $S_{n-1}$ , so deterioration of the OLED may be stably compensated for.

**[0049]** According to another embodiment illustrated FIG. 11, an organic light emitting display device may be substantially similar to the organic light emitting display device described previously with reference to FIG. 1, with the exception of including a plurality of pixels 240 in a pixel unit 230, and light emitting control lines E1 to En in addition to the scan lines S1 to  $S_n$ , the first control lines CL11 to CL1n, the second control lines CL21 to C2n, and the data lines D1 to Dm, as illustrated in FIG. 11. Accordingly, a scan driver 210 of the organic light emitting display device may generate a light emitting control signal to supply to the light emitting control lines E1 to En.

**[0050]** The light emitting control signal may have a substantially same length as the second control signal, and may be opposite thereto, as illustrated in FIG. 14. The light emitting control signal may be longer than the scan signal, and may be shorter than the first control signal, as further illustrated in FIG. 14. The light emitting control signal, the scan signal, the first control signal, and the second control signal may overlap with one another.

**[0051]** Referring to FIG. 12, each pixel 240 may include an organic light emitting diode OLED and a driving circuit capable of controlling current supplied to the OLED, so light emitted by the OLED may correspond to a data signal supplied to the pixel 140. The driving circuit may be substantially similar to the driving circuit of the pixel 140 described previously with respect to FIG. 2, with the exception of including a fifth transistor M5 between the OLED and the second transistor M2, so the light emitting control signal may be input into the gate electrode of the fifth transistor M5. The fifth transistor M5 may be turned off when a light emitting control signal is supplied thereto, and may be turned on when the light emitting control signal is not supplied.

**[0052]** More specifically, an anode electrode of the OLED may be coupled to the fifth transistor M5, and a cathode electrode of the OLED may be coupled to the second power source ELVSS, so the OLED may generate light with the predetermined luminance with respect to the electric current supplied by the second transistor M2 via the fifth transistor M5. The first transistor M1, storage capacitor Cst, and compensation unit 142 may be arranged in a substantially similar configuration as described previously with respect to FIG. 2, and therefore, their detailed description will not be repeated herein. The second transistor M2 may be configured in a substantially similar way as described previously with respect to FIG. 2, with the exception of having its second electrode coupled to a first electrode of the fifth transistor M5.

**[0053]** Referring to FIG. 13, the pixel 240 may be substantially similar to the pixel 140 described previously with reference to FIG. 3, with the exception of including the fifth transistor M5 to substantially minimize and/or prevent unnecessary electric current flow into the OLED. Referring to FIGS. 13-14, operation of the pixel 240 may be as follows. First, a first control signal, i.e., a high voltage pulse, may be supplied to the first control line CL1n, so the fourth transistor M4 may be turned off. Accordingly, the first node N1 and the voltage source  $V_{sus}$  may be electrically disconnected, i.e., when the fourth transistor M4 is turned off. Once the fourth transistor M4 is turned off, a second control signal, i.e., a low voltage pulse, may be supplied to the second control line CL2n, so the third transistor M3 may be turned on. Simultaneously, a light emitting control signal, i.e., a high voltage pulse, may be supplied to the light emitting control line En, so the fifth transistor M5 may be turned off. Once the third transistor M3 is turned on, the voltage  $V_{oled}$  of the OLED may be supplied to the first node N1. In this respect, it is noted that since the fifth transistor M5 is turned off, the voltage  $V_{oled}$  may be set to a threshold voltage of the OLED.

**[0054]** Next, the scan signal may be supplied to the scan line  $S_n$ , so the first transistor M1 may be turned on. When the first transistor M1 is turned on, voltage corresponding to the data signal supplied to the data line Dm may be transmitted

through the first transistor M1, and may be stored in the storage capacitor Cst. Once the data signal is stored, the first transistor M1 may be turned off by suspending the scan signal.

[0055] Next, supplies of the second control signal and the light emitting control signal may be suspended, so the third transistor may be turned off and the fifth transistor M5 may be turned on, respectively. Then, the first control signal may be suspended to turn on the fourth transistor M4. When the fourth transistor M4 is turned on, the voltage at the first node N1 may be increased to a voltage of the voltage source Vsus, thereby triggering an increase in a voltage of the gate electrode of the second transistor M2. The voltage at the gate electrode of the second transistor M2 may be calculated according to Equation 1. In this respect, it is noted that the compensation unit 142 may be configured according to any configurations described previously with respect to FIGS. 5-10.

[0056] According to another embodiment illustrated in FIG. 15, a compensation unit 142h may be substantially similar to the compensation unit 142 described previously with respect to FIG. 13, with the exception of being coupled to the light emitting control line En, as opposed to being coupled to the first and second control lines CL1 and CL2. More specifically, the compensation unit 142h may include the feedback capacitor Cfb and the third and fourth transistors M3 and M4 in a substantially same configuration described previously with respect to FIG. 13, with the exception of having both the third and fourth transistors M3 and M4 coupled to and controlled by a light emitting control signal supplied from the light emitting control line En.

[0057] More specifically, the third transistor M3 may have an opposite conductivity as compared to the first, second, fourth, and fifth transistors M1, M2, M4, and M5. For example, as illustrated in FIG. 15, the third and fourth transistors M3 and M4 may be NMOS-type and PMOS-type transistors, respectively. Accordingly, a light emitting control signal supplied to the light emitting control line En may turn on the third transistor M3, and may turn off the fourth transistor M4. Similarly, when supply of light emitting control signal supplied from the light emitting control line En is suspended, operational states of the third and fourth transistors M3 and M4 may be reversed, i.e., the third transistor M3 may be turned off, and the fourth transistor M4 may be turned on. The compensation unit 142h illustrated in FIG. 15 may be advantageous in removing the first and second control lines CL1n and CL2n.

[0058] Operation of the compensation unit 142h may be substantially similar to operation of the compensation unit 142 described previously with respect to FIGS. 13-14, and may be illustrated with reference to FIG. 14. First, a light emitting control signal may be supplied to the light emitting control line En before a scan signal is supplied to the scan line Sn. Accordingly, the fourth and fifth transistors M4 and M5 may be turned off, and the third transistor M3 may be turned on. When the third transistor M3 is turned on, voltage Voled of the OLED may be supplied to the first node N1.

[0059] Then, a scan signal may be supplied to the scan line Sn to turn on the first transistor M1. When the first transistor M1 is turned on, the voltage corresponding to the data signal supplied to the data line Dm may be stored in the storage capacitor Cst, followed by suspension of the scan signal, so the first transistor M1 may be turned off. Once the first transistor M1 is turned off, the supply of the light emitting control signal may be suspended, thereby turning on the fourth and fifth transistors M4 and M5. When the fourth transistor M4 is turned on, the voltage at the first node N1 may increase to a voltage of the voltage source Vsus, so the voltage of the gate electrode of the second transistor M2 may be increased. Accordingly, deterioration of the OLED may be compensated by adjusting an increase in voltage at the gate electrode of the second transistor M2 to correspond to the deterioration of the OLED.

[0060] According to another embodiment illustrated in FIG. 16, a compensation unit 142i may be substantially similar to the compensation unit 142 described previously with respect to FIG. 13, with the exception of being coupled to the light emitting control line En and scan line Sn, as opposed to being coupled to the first and second control lines CL1 and CL2. More specifically, the compensation unit 142i may include the feedback capacitor Cfb and the third and fourth transistors M3 and M4 in a substantially same configuration described previously with respect to FIG. 13, with the exception of having the third and fourth transistors M3 and M4 coupled to and controlled by the scan line Sn and the light emitting control line En, respectively. The compensation unit 142i illustrated in FIG. 16 may be advantageous in removing the first and second control lines CL1n and CL2n.

[0061] Operation of the compensation unit 142i may be substantially similar to operation of the compensation unit 142 described previously with respect to FIGS. 13-14, and may be illustrated with reference to FIG. 14. First, a light emitting control signal may be supplied to the light emitting control line En before a scan signal is supplied to the scan line Sn. Accordingly, the fourth and fifth transistors M4 and M5 may be turned off.

[0062] Then, a scan signal may be supplied to the scan line Sn to turn on the first and third transistors M1 and M3. When the first transistor M1 is turned on, the voltage corresponding to the data signal supplied to the data line Dm may be stored in the storage capacitor Cst, and when the third transistor M3 is turned on, voltage Voled of the OLED may be supplied to the first node N1. After voltage corresponding to the data signal is stored in the storage capacitor Cst, the first transistor M1 and the third transistor M3 may be turned off by suspension of the scan signal. Once the first and third transistors M1 and M3 are turned off, the supply of the light emitting control signal may be suspended, thereby turning on the fourth and fifth transistors M4 and M5. When the fourth transistor M4 is turned on, the voltage at the first node N1 may increase to a voltage of the voltage source Vsus, so the voltage of the gate electrode of the second transistor M2 may be increased. Accordingly, deterioration of the OLED may be compensated by adjusting an increase

in voltage at gate electrode of the second transistor M2 to correspond to the deterioration of the OLED.

[0063] According to another embodiment illustrated in FIG. 17, a compensation unit 142j may be substantially similar to the compensation unit 142 described previously with respect to FIG. 13, with the exception of being coupled to the scan line Sn, as opposed to being coupled to the first and second control lines CL1 and CL2. More specifically, the compensation unit 142j may include the feedback capacitor Cfb and the third and fourth transistors M3 and M4 in a substantially same configuration described previously with respect to FIG. 13, with the exception of having the third, fourth, and fifth transistors M3, M4, and M5 coupled to and controlled by a scan signal supplied by the scan line Sn.

[0064] More specifically, the fourth and fifth transistors M4 and M5 may have opposite conductivities as compared to the first and third transistors M1 and M3. For example, as illustrated in FIG. 17, the fourth and fifth transistors M4 and M5 may be NMOS-type transistors. Accordingly, a scan signal supplied to the scan line Sn may turn off the fourth and fifth transistors M4 and M5, and may turn on the third transistor M3, and vice versa. The compensation unit 142j illustrated in FIG. 17 may be advantageous in removing the first and second control lines CL1n and CL2n, and the light emitting control line En.

[0065] Operation of the compensation unit 142j may be substantially similar to operation of the compensation unit 142 described previously with respect to FIGS. 13-14, and may be illustrated with reference to FIG. 14. First, a scan signal may be supplied to the scan line Sn to turn on the first and third transistors M1 and M3, and to turn off the fourth and fifth transistors M4 and M5. When the first transistor M1 is turned on, the voltage corresponding to the data signal supplied to the data line Dm may be stored in the storage capacitor Cst. When the third transistor M3 is turned on, the voltage Voled of the OLED may be supplied to the first node N1. After voltage corresponding to the data signal is stored in the storage capacitor Cst and, simultaneously, the voltage Voled of the OLED is supplied to the first node N1, the supply of the scan signal may be suspended to turn off the first and third transistors M1 and M3, and to turn on the fourth and fifth transistors M4 and M5. When the fourth transistor M4 is turned on, the voltage at the first node N1 may increase to a voltage of the voltage source Vsus, so the voltage of the gate electrode of the second transistor M2 may be increased. Accordingly, deterioration of the OLED may be compensated by adjusting an increase in voltage at gate electrode of the second transistor M2 to correspond to the deterioration of the OLED.

## Claims

30 1. A pixel, comprising:

a storage capacitor ( $C_{st}$ ) having a first electrode coupled to a first power source ( $ELV_{DD}$ );

an organic light emitting diode having a cathode coupled to a second power source ( $ELV_{SS}$ );

a first transistor (M1) having a first electrode coupled to a data line ( $D_m$ ), a second electrode coupled to a second electrode of the storage capacitor ( $C_{st}$ ), and a gate electrode coupled to a scan line ( $S_n$ );

a second, transistor (M2) having a first electrode coupled to the first power source ( $ELV_{DD}$ ), a gate electrode coupled to the second electrode of the first transistor (M1), and a second electrode directly or indirectly coupled to an anode of the organic light emitting diode (OLED); and

a compensation unit (142) configured to sense a voltage at the anode of the organic light emitting diode (OLED) and to provide a compensation voltage to the gate electrode of the second transistor (M2), the compensation voltage being proportional to a voltage difference between a supplementary voltage and the voltage at the anode of the organic light emitting diode (OLED),

wherein the compensation unit includes:

45 a third transistor (M3) having a first electrode coupled to the anode of the organic light emitting diode (OLED);

a fourth transistor (M4) having a first electrode coupled to a supplementary voltage source ( $V_{sus}$ ), the supplementary voltage source being adapted to provide the supplementary voltage, and a second electrode coupled to a second electrode of the third transistor (M3); and

50 a feedback capacitor ( $C_{fb}$ ) having a first electrode coupled to the second electrode of the third transistor (M3) and a second electrode coupled to the gate electrode of the second transistor (M2); and

**characterized in that**

the supplementary voltage source ( $V_{sus}$ ) is the scan line ( $S_n$ ) or a previous scan line ( $S_{n-1}$ ).

55 2. The pixel as claimed in claim 1, wherein one of the third and the fourth transistors is an NMOS transistor and the remaining one of the third and the fourth transistors is a PMOS transistor.

3. The pixel as claimed in one of the preceding claims, further comprising a fifth transistor having a first electrode coupled to the second electrode of the second transistor and a second electrode coupled to the anode of the organic

light emitting diode.

4. An organic light emitting diode display device, comprising:

5 a plurality of scan lines;

a plurality of data lines;

a plurality of pixels, each of the pixels being coupled to a corresponding one of the scan lines and of the data lines;

a scan driver configured to supply scan signals via the scan lines; and

a data driver configured to drive the data lines,

10 **characterized in that**

each pixel is a pixel according to one of the preceding claims.

15 5. The organic light emitting diode display device of claim 4, wherein the scan driver is further adapted to turn on the third transistor while turning off the fourth transistor during a first period and to turn off the third transistor while turning on the fourth transistor during a second period.

20 6. The organic light emitting diode display of one of the claims 4 or 5, wherein the plurality of pixels comprise a plurality of first sub-pixels adapted to emit light of a first colour at a first emission efficiency and a plurality of second sub-pixels adapted to emit light of a second colour at a second emission efficiency, the second colour and the second emission efficiency being different from the first colour and the first emission efficiency, respectively, **characterized in that** each of the first sub-pixels comprises a feedback capacitor having a first capacitance and **in that** each of the second sub-pixels comprises a feedback capacitor having a second capacitance different from the first capacitance.

25 7. The organic light emitting diode display of claim 6, wherein the first colour is blue and the second colour is either red or green, or wherein the first colour is red and the second colour is green, and wherein the second capacitance is larger than the first capacitance.

30 8. The organic light emitting diode display of one of the claims 4 through 7, wherein each pixel is a pixel according to claim 3, wherein the fifth transistor has a gate electrode coupled to a corresponding one of a plurality of light emitting control lines, and wherein the scan driver is further configured to provide emission control signals to the plurality of emission control lines.

35 **Patentansprüche**

1. Pixel, aufweisend:

40 einen Speicherkondensator (Cst), der eine erste Elektrode aufweist, die mit einer ersten Energiequelle (ELVDD) gekoppelt ist;

eine organische Leuchtdiode, die eine Kathode aufweist, die mit einer zweiten Energiequelle (ELVSS) gekoppelt ist;

einen ersten Transistor (M1), der eine erste Elektrode, die mit einer Datenleitung (Dm) gekoppelt ist, eine zweite Elektrode, die mit einer zweiten Elektrode des Speicherkondensators (Cst) gekoppelt ist, und eine Gate-Elektrode, die mit einer Ansteuerleitung (Sn) gekoppelt ist, aufweist,

einen zweiten Transistor (M2), der eine erste Elektrode, die mit der ersten Energiequelle (ELVDD) gekoppelt ist, eine Gate-Elektrode, die mit der zweiten Elektrode des ersten Transistors (M1) gekoppelt ist, und eine zweite Elektrode,

50 die direkt oder indirekt mit einer Anode der organischen Leuchtdiode (OLED) gekoppelt ist, aufweist; und eine Kompensationseinheit (142), die konfiguriert ist, eine Spannung an der Anode der organischen Leuchtdiode (OLED) zu erfassen und eine Kompensationsspannung zur Gate-Elektrode des zweiten Transistors (M2) zu liefern, wobei die Kompensationsspannung proportional zu einer Spannungsdifferenz zwischen einer Zusatzspannung und der Spannung an der Anode der organischen Leuchtdiode (OLED) ist,

wobei die Kompensationseinheit aufweist:

55 einen dritten Transistor (M3), der eine erste Elektrode aufweist, die mit der Anode der organischen Leuchtdiode (OLED) gekoppelt ist;

einen vierten Transistor (M4), der eine erste Elektrode aufweist, die mit einer Zusatzspannungsquelle (Vsus)

gekoppelt ist, wobei die Zusatzspannungsquelle ausgebildet ist, die Zusatzspannung bereitzustellen, und der eine zweite Elektrode aufweist, die mit einer zweiten Elektrode des dritten Transistors (M3) gekoppelt ist; und

5 einen Rückkopplungskondensator (Cfb), der eine erste Elektrode, die mit der zweiten Elektrode des dritten Transistors (M3) gekoppelt ist, und eine zweite Elektrode, die mit der Gate-Elektrode des zweiten Transistors (M2) gekoppelt ist, aufweist, und

**dadurch gekennzeichnet, dass**

10 die Zusatzspannungsquelle (Vsus) die Ansteuerleitung (Sn) oder eine vorhergehende Ansteuerleitung (Sn-1) ist.

10 2. Pixel nach Anspruch 1, wobei einer des dritten und des vierten Transistors ein NMOS-Transistor ist und der verbleibende des dritten und des vierten Transistors ein PMOS-Transistor ist.

15 3. Pixel nach einem der vorhergehenden Ansprüche, weiterhin aufweisend einen fünften Transistor, der eine erste Elektrode, die mit der zweiten Elektrode des zweiten Transistors gekoppelt ist, und eine zweite Elektrode, die mit der Anode der organischen Leuchtdiode gekoppelt ist, aufweist.

20 4. Organische Leuchtdioden-Anzeigevorrichtung, aufweisend:

20 eine Vielzahl von Ansteuerleitungen;

eine Vielzahl von Datenleitungen;

eine Vielzahl von Pixeln, wobei jeder der Pixel mit einer entsprechenden der Ansteuerleitungen und der Datenleitungen gekoppelt ist;

25 einen Ansteuertreiber, der zum Anlegen von Ansteuersignalen über die Ansteuerleitungen konfiguriert ist; und einen Datentreiber, der zum Treiben der Datenleitungen konfiguriert ist,

**dadurch gekennzeichnet, dass**

jeder Pixel ein Pixel nach einem der vorhergehenden Ansprüche ist.

30 5. Organische Leuchtdioden-Anzeigevorrichtung nach Anspruch 4, wobei der Ansteuertreiber weiterhin ausgebildet ist, während einer ersten Periode den dritten Transistor einzuschalten, während der vierte Transistor ausgeschaltet wird, und während einer zweiten Periode den dritten Transistor auszuschalten, während der vierte Transistor eingeschaltet wird.

35 6. Organische Leuchtdioden-Anzeige nach einem der Ansprüche 4 oder 5, wobei die Vielzahl der Pixel eine Vielzahl erster Subpixel, die zur Emission von Licht einer ersten Farbe mit einer ersten Emissionseffizienz ausgebildet sind, und eine Vielzahl zweiter Subpixel aufweist, die zur Emission von Licht einer zweiten Farbe mit einer zweiten Emissionseffizienz ausgebildet sind, wobei sich die zweite Farbe und die zweite Emissionseffizienz jeweils von der ersten Farbe und der ersten Emissionseffizienz unterscheiden, **dadurch gekennzeichnet, dass** jeder der ersten Subpixel einen Rückkopplungskondensator aufweist, der eine erste Kapazität aufweist, und dadurch, dass jeder der zweiten Subpixel einen Rückkopplungskondensator aufweist, der eine zweite Kapazität aufweist, die sich von der ersten Kapazität unterscheidet.

40 7. Organische Leuchtdioden-Anzeige nach Anspruch 6, wobei die erste Farbe blau ist und die zweite Farbe entweder rot oder grün ist, oder wobei die erste Farbe rot ist und die zweite Farbe grün ist, und wobei die zweite Kapazität größer als die erste Kapazität ist.

45 8. Organische Leuchtdioden-Anzeige nach einem der Ansprüche 4 bis 7, wobei jeder Pixel ein Pixel nach Anspruch 3 ist, wobei der fünfte Transistor eine Gate-Elektrode aufweist, die mit einer entsprechenden Lichtemissionskontrollleitung aus einer Vielzahl von Lichtemissionskontrollleitungen gekoppelt ist, und wobei der Ansteuertreiber weiterhin konfiguriert ist, Emissionskontrollsignale zu der Vielzahl der Emissionskontrollleitungen zu liefern.

## Revendications

55 1. Pixel, comprenant :

un condensateur de stockage ( $C_{st}$ ) ayant une première électrode reliée à une première source d'alimentation ( $ELV_{DD}$ ),

une diode électroluminescente organique ayant une cathode reliée à une deuxième source d'alimentation (ELV<sub>ss</sub>);

5 un premier transistor (M1) ayant une première électrode reliée à une ligne de données (D<sub>m</sub>), une deuxième électrode reliée à une deuxième électrode du condensateur de stockage (C<sub>st</sub>), et une électrode de grille reliée à une ligne de balayage (S<sub>n</sub>);

10 un deuxième transistor (M2) ayant une première électrode reliée à la première source d'alimentation (ELV<sub>DD</sub>), une électrode de grille reliée à la deuxième électrode du premier transistor (M1), et une deuxième électrode directement ou indirectement reliée à une anode de la diode électroluminescente organique (OLED) ; et une unité de compensation (142) configurée pour détecter une tension au niveau de l'anode de la diode électroluminescente organique (OLED) et pour fournir une tension de compensation à l'électrode de grille du deuxième transistor (M2), la tension de compensation étant proportionnelle à une différence de tension entre la tension supplémentaire et la tension au niveau de l'anode de la diode électroluminescente organique (OLED), dans lequel l'unité de compensation comporte :

15 un troisième transistor (M3) ayant une première électrode reliée à l'anode de la diode électroluminescente organique (OLED) ;

un quatrième transistor (M4) ayant une première électrode reliée à une source de tension supplémentaire (V<sub>SUS</sub>), la source de tension supplémentaire étant apte à fournir la tension supplémentaire, et une deuxième électrode reliée à une deuxième électrode du troisième transistor (M3) ; et

20 un condensateur de rétroaction (C<sub>fb</sub>) ayant une première électrode reliée à la deuxième électrode du troisième transistor (M3) et une deuxième électrode reliée à l'électrode de grille du deuxième transistor (M2), et

**caractérisé en ce que**

25 la source de tension supplémentaire (V<sub>SUS</sub>) est la ligne de balayage (S<sub>n</sub>) ou une ligne de balayage précédente (S<sub>n-1</sub>).

2. Pixel selon la revendication 1, dans lequel l'un des troisième et quatrième transistors est un transistor NMOS et le transistor restant des troisième et quatrième transistors est un transistor PMOS.

30 3. Pixel selon l'une des revendications précédentes, comprenant en outre un cinquième transistor ayant une première électrode reliée à la deuxième électrode du deuxième transistor et une deuxième électrode reliée à l'anode de la diode électroluminescente organique.

4. Dispositif d'affichage à diodes électroluminescentes organiques, comprenant :

35 une pluralité de lignes de balayage ;

une pluralité de lignes de données ;

une pluralité de pixels, chacun des pixels étant relié à l'une, correspondante, des lignes de balayage et des lignes de données ;

40 un circuit d'attaque de balayage, configuré pour délivrer des signaux de balayage par l'intermédiaire des lignes de balayage ; et

un circuit d'attaque de données configuré pour attaquer les lignes de données,

**caractérisé en ce que**

45 chaque pixel est un pixel selon l'une des revendications précédentes.

5. Dispositif d'affichage à diodes électroluminescentes organiques selon la revendication 4, dans lequel le circuit d'attaque est en outre apte à rendre passant le troisième transistor tout en rendant non passant le quatrième transistor pendant une première période et à rendre non passant le troisième transistor tout en rendant passant le quatrième transistor pendant une deuxième période.

50 6. Afficheur à diodes électroluminescentes organiques selon l'une des revendications 4 ou 5, dans lequel la pluralité de pixels comprend une pluralité de premiers sous-pixels aptes à émettre une lumière d'une première couleur avec un premier rendement d'émission et une pluralité de deuxièmes sous-pixels aptes à émettre de la lumière d'une deuxième couleur avec un deuxième rendement d'émission, la deuxième couleur et le deuxième rendement d'émission étant respectivement différents de la première couleur et du premier rendement d'émission, **caractérisé en ce que** chacun des premiers sous-pixels comprend un condensateur de rétroaction ayant une première capacité et **en ce que** chacun des deuxièmes sous-pixels comprend un condensateur de rétroaction ayant une deuxième capacité différente de la première capacité.

7. Afficheur à diodes électroluminescentes organiques selon la revendication 6, dans lequel la première couleur est le bleu et la deuxième couleur est soit le rouge, soit le vert, ou dans lequel la première couleur est le rouge et la deuxième couleur est le vert, et dans lequel la deuxième capacité est supérieure à la première capacité.

- 5 8. Afficheur à diodes électroluminescentes organiques selon l'une des revendications 4 à 7, dans lequel chaque pixel est un pixel selon la revendication 3, dans lequel le cinquième transistor a une électrode de grille reliée à l'une, correspondante, d'une pluralité de lignes de commande d'émission lumineuse, et dans lequel le circuit d'attaque de balayage est en outre configuré pour fournir des signaux de commande d'émission à la pluralité de lignes de commande d'émission.

10

15

20

25

30

35

40

45

50

55

FIG. 1

FIG. 2

140

FIG. 3

140

FIG. 4

FIG. 5

FIG. 6

140

FIG. 7

140

FIG. 8

140

FIG. 9

140

FIG. 10

140

FIG. 11

FIG. 12

240

FIG. 13

240

FIG. 14

FIG. 15

240

FIG. 16

240

FIG. 17

240

**REFERENCES CITED IN THE DESCRIPTION**

*This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.*

**Patent documents cited in the description**

- WO 9848403 A [0005]

- EP 1496495 A2 [0005]

- EP 1130565 A1 [0006]

- US 20060253755 A1 [0007]

|                |                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素和有机发光二极管显示装置                                                                                 |         |            |

| 公开(公告)号        | <a href="#">EP1923857B1</a>                                                                    | 公开(公告)日 | 2014-01-08 |

| 申请号            | EP2007120624                                                                                   | 申请日     | 2007-11-14 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                    |         |            |

| 申请(专利权)人(译)    | 三星SDI CO. , LTD.                                                                               |         |            |

| 当前申请(专利权)人(译)  | 三星DISPLAY CO. , LTD.                                                                           |         |            |

| [标]发明人         | CHOI SANG MOO<br>LEE WANG JO                                                                   |         |            |

| 发明人            | CHOI, SANG-MOO<br>LEE, WANG-JO                                                                 |         |            |

| IPC分类号         | G09G3/32                                                                                       |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2320/029 G09G2320/043<br>G09G2320/045 |         |            |

| 代理机构(译)        | hengelhaupt , Jürgen                                                                           |         |            |

| 优先权            | 1020060112223 2006-11-14 KR<br>1020060130109 2006-12-19 KR                                     |         |            |

| 其他公开文献         | EP1923857A2<br>EP1923857A3                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                      |         |            |

### 摘要(译)

像素包括有机发光二极管，耦合到扫描线和数据线的第一晶体管，第一晶体管被配置为当扫描信号被提供给扫描线时经由数据线接收数据信号，存储电容器被配置为存储与由第一晶体管接收的数据信号对应的电压，第二晶体管被配置为相对于存储电容器中存储的电压经由有机发光二极管控制从第一电源到第二电源的电流。补偿单元，用于调整第二晶体管的栅极电压，该电压调整足以补偿有机发光二极管的劣化程度。

$$\Delta V_{M2\_gate} = \Delta V_N \times (C_{fb} / (C_{st} + C_{fb})) \quad \text{Equation 1}$$