(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-176165

(P2008-176165A)

(43) 公開日 平成20年7月31日(2008.7.31)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | J 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 680G 5C006  |

| <b>G09G 3/36</b> (2006.01)  | G09G 3/20 | 621B 5C080  |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 623B        |

|                             | G09G 3/20 | 611J        |

審査請求 未請求 請求項の数 4 O L (全 12 頁) 最終頁に続く

|           |                            |            |                                             |

|-----------|----------------------------|------------|---------------------------------------------|

| (21) 出願番号 | 特願2007-11068 (P2007-11068) | (71) 出願人   | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号      |

| (22) 出願日  | 平成19年1月22日 (2007.1.22)     | (74) 代理人   | 100102185<br>弁理士 多田 繁範                      |

|           |                            | (72) 発明者   | 山本 哲郎<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内     |

|           |                            | (72) 発明者   | 甚田 誠一郎<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内    |

|           |                            | F ターム (参考) | 3K107 AA01 BB01 CC31 DD39 EE03<br>HH02 HH04 |

最終頁に続く

(54) 【発明の名称】ディスプレイ装置及び駆動回路

## (57) 【要約】

【課題】本発明は、ディスプレイ装置及び駆動回路に関し、例えば有機EL素子によるディスプレイ装置に適用して、従来に比して十分な位相マージンを入力信号に確保することができるようとする。

【解決手段】本発明は、入力信号S1の配線パターンP2と平行に逆相信号用の配線パターンP3を形成し、この逆相信号用の配線パターンP3に入力信号S1の逆相の信号を供給する。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

画素をマトリックス状に配置した画素部と、

前記画素部の信号線を順次入力信号の信号レベルに設定して前記画素部を駆動する駆動回路とを有するディスプレイ装置において、

少なくとも前記駆動回路において、前記入力信号の配線パターンと平行に逆相信号用の配線パターンが形成され、

前記逆相信号用の配線パターンに前記入力信号の逆相の信号が供給される

ことを特徴とするディスプレイ装置。

## 【請求項 2】

前記逆相の信号が、前記入力信号をほぼ利得 - 1 の反転増幅回路で反転増幅して生成される

ことを特徴とする請求項 1 に記載のディスプレイ装置。

## 【請求項 3】

前記逆相の信号が、前記入力信号をインバーターに入力して生成される

ことを特徴とする請求項 1 に記載のディスプレイ装置。

## 【請求項 4】

画素をマトリックス状に配置した画素部を駆動する駆動回路であって、

前記画素部の信号線を順次入力信号の信号レベルに設定して前記画素部を駆動し、

前記入力信号の配線パターンと平行に逆相信号用の配線パターンが形成され、

前記逆相信号用の配線パターンに前記入力信号の逆相の信号を供給する

ことを特徴とする駆動回路。

10

20

30

40

50

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、ディスプレイ装置及び駆動回路に関し、例えば有機 E L (Electro Luminescence) 素子によるディスプレイ装置に適用することができる。本発明は、入力信号の配線パターンと平行に逆相信号用の配線パターンを形成し、この逆相信号用の配線パターンに入力信号の逆相の信号を供給することにより、従来に比して十分な位相マージンを入力信号に確保することができるようとする。

## 【背景技術】

## 【0002】

従来、有機 E L 素子を用いたディスプレイ装置に関して、例えば U S P 5 , 6 8 4 , 3 6 5 、特開平 8 - 2 3 4 6 8 3 号公報等に種々の工夫が提案されている。

## 【0003】

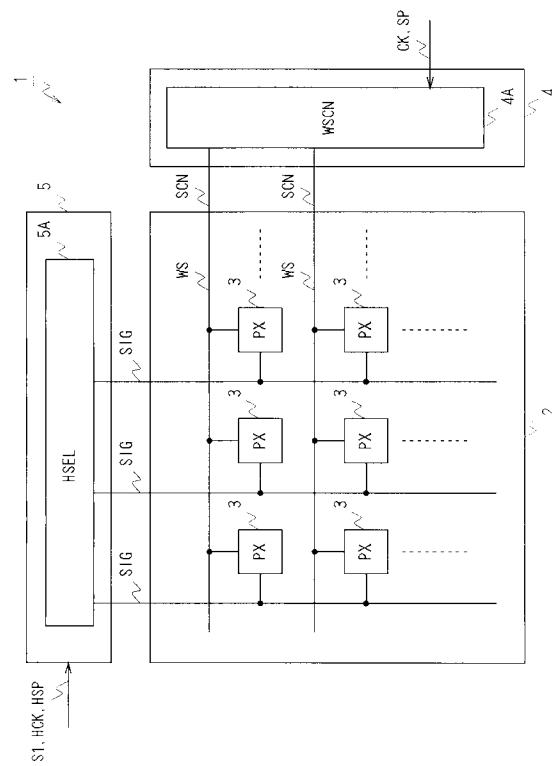

ここで図 4 は、従来の有機 E L 素子を用いたいわゆるアクティブマトリックス型のディスプレイ装置を示すブロック図である。ディスプレイ装置 1 において、画素部 2 は、マトリックス状に画素 (P X) 3 が配置されて形成される。また画素部 2 は、このマトリックス状に配置した画素 3 に対して、走査線 S C N がライン単位で水平方向に設けられ、また走査線 S C N と直交するように信号線 S I G が列毎に設けられる。

## 【0004】

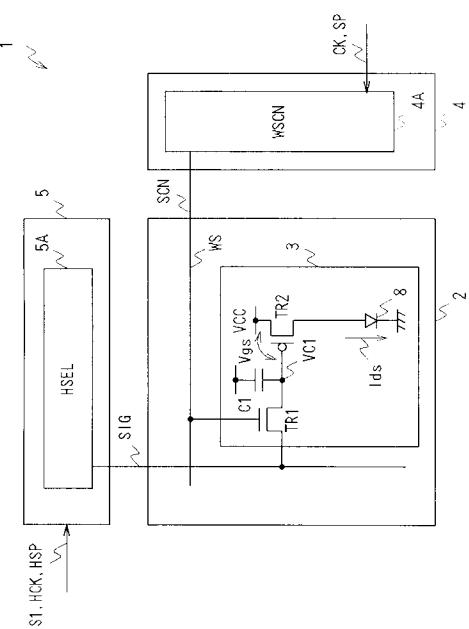

ここで図 5 に示すように、各画素 3 は、電流駆動による自発光型の発光素子である有機 E L 素子 8 と、この有機 E L 素子 8 を駆動する各画素 3 の駆動回路（以下、画素回路と呼ぶ）とで形成される。

## 【0005】

画素回路は、信号レベル保持用コンデンサ C 1 の一端が一定電位に保持され、書き込み信号 W S によりオンオフ動作するトランジスタ T R 1 を介して、この信号レベル保持用コンデンサ C 1 の他端が信号線 S I G に接続される。これにより画素回路は、書き込み信号

WSの立ち上がりによってトランジスタTR1がオン動作し、信号レベル保持用コンデンサC1の他端電圧VC1が信号線SIGの信号レベルに設定され、トランジスタTR1がオン状態からオフ状態に切り換わるタイミングで、信号線SIGの信号レベルが信号レベル保持用コンデンサC1の他端にサンプルホールドされる。

#### 【0006】

画素回路は、ソースを電源VCCに接続したPチャンネルトランジスタTR2のゲートに、この信号レベル保持用コンデンサC1の他端が接続され、このトランジスタTR2のドレインが有機EL素子8のアノードに接続される。ここで画素回路は、このトランジスタTR2が常に飽和領域で動作するように設定され、その結果、トランジスタTR2は、 $(1/2) \times \mu \times (W/L) \times C_o \times (V_{gs} - V_{th})^2$ で表されるドレイン電流Idsによる定電流回路を構成する。なおここでVgsは、トランジスタTR2のゲートソース間電圧であり、μは移動度である。またWはチャンネル幅、Lはチャンネル長、Co×はゲート容量、VthはトランジスタTR2のしきい値電圧である。これにより各画素回路は、信号レベル保持用コンデンサC1にサンプルホールドされた信号線SIGの信号レベルに応じた駆動電流Idsにより有機EL素子8を駆動する。

10

#### 【0007】

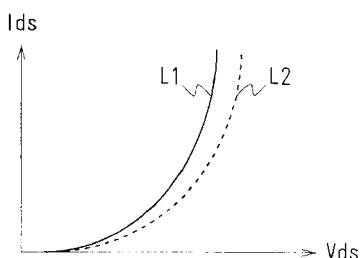

ここで有機EL素子8は、図6に示すように、使用により電流が流れ難くなる方向に電流電圧特性が経時変化する。なおこの図6において、符号L1が初期の特性を示し、符号L2が経時変化による特性を示すものである。従ってトランジスタTR2にNチャンネル型を適用した場合、この図6に示す電流電圧特性の変化によって、有機EL素子8に流れる電流が徐々に減少し、各画素の輝度が徐々に低下することになる。しかしながら図5に示す回路構成によりPチャンネルトランジスタTR2で有機EL素子8を駆動する場合には、電流電圧特性の経時変化による各画素の輝度変化を防止することができる。

20

#### 【0008】

ディスプレイ装置1は、垂直駆動回路4及び水平駆動回路5により、点順次又は線順次で、各画素部2に設けられた信号レベル保持用コンデンサC1の端子電圧VC1を設定し、これにより所望する画像を表示する。

#### 【0009】

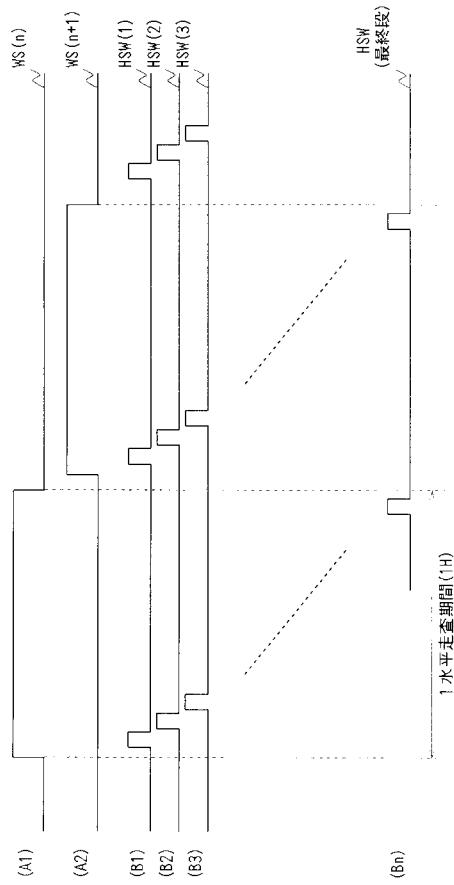

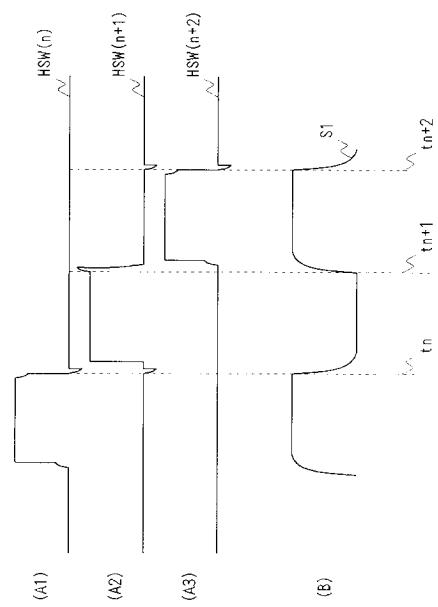

すなわち垂直駆動回路4において、ライトスキャン回路(WSCN)4Aは、所定のサンプリングパルスSPをクロックCKで順次転送して、図7に示すように、各画素3への書き込みをライン単位で順次指示するタイミング信号である書き込み信号WS(WS(n)、WS(n+1)……)(図7(A1)及び(A2))を生成し、この書き込み信号WS(WS(n)、WS(n+1)……)を各走査線SCNに出力する。なおこの図7の例では、1水平走査期間毎に、順次、ラインを選択するように、書き込み信号WS(WS(n)、WS(n+1)……)が出力される。

30

#### 【0010】

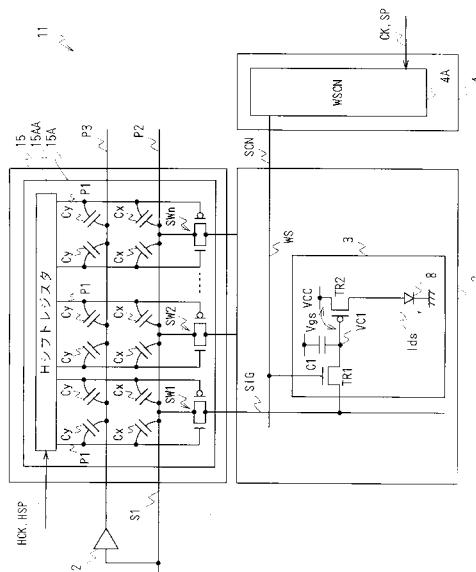

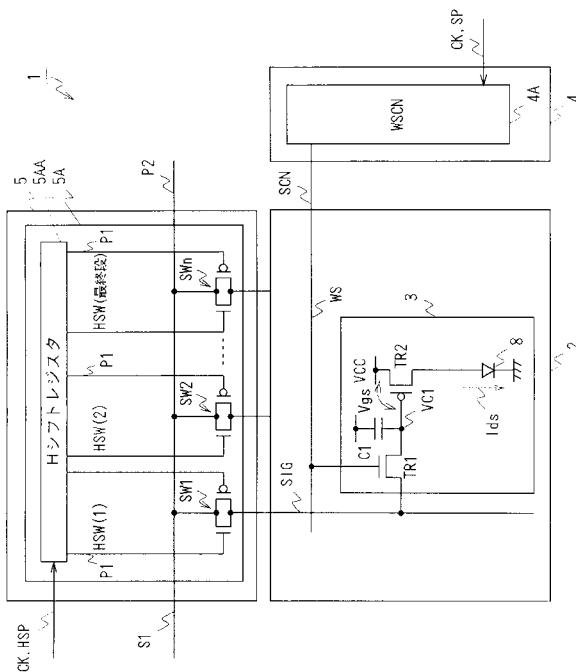

図8に示すように、水平駆動回路5は、水平セレクタ(HSEL)5Aの水平シフトレジスタ部(Hシフトレジスタ部)5AAにおいて、所定のサンプリングパルスHSPをクロックHCKで順次転送し、1水平走査期間の間で、各信号線SIGを順次選択するタイミング信号である信号線の書き込み信号HSW(HSW(1)、HSW(2)、HSW(3)、……、HSW(最終段))(図7(B1)及び(Bn))、この信号線の書き込み信号HSW(HSW(1)、HSW(2)、HSW(3)……)の反転信号を出力する。

40

#### 【0011】

水平駆動回路5は、水平セレクタ5Aにおいて、1対のトランジスタにより構成されるスイッチ回路SW1、SW2、……SWnに、これら信号線の書き込み信号HSW(HSW(1)、HSW(2)、HSW(3)、……)、対応する信号線の書き込み信号HSW(HSW(1)、HSW(2)、HSW(3)、……)の反転信号を入力し、1水平走査期間の間で、これらスイッチ回路SW1、SW2、……SWnを順次オン状態に設定する。ここでこれらスイッチ回路SW1、SW2、……SWnは、オン状態に設定されると、各画素の階調を示す入力信号S1を対応する信号線SIGに出力する。

50

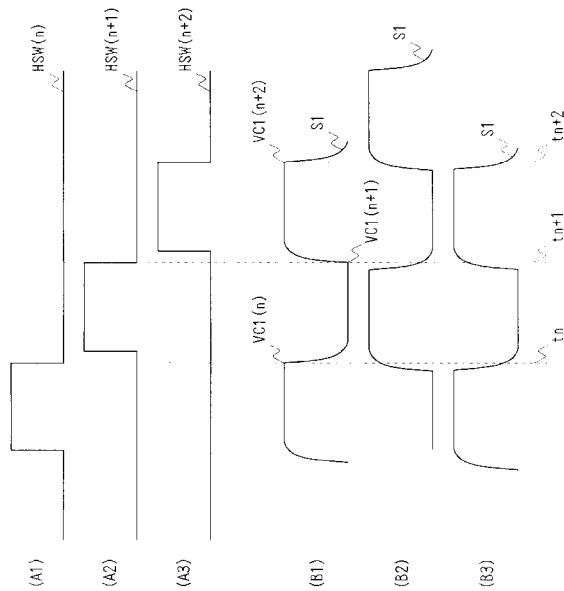

## 【0012】

これにより図9に示すように、画素部2に設けられた各画素3は、垂直駆動回路4により書き込み信号HSWが立ち上げられている期間の間であって、信号線の書き込み信号HSW(HSW(1)、HSW(2)、HSW(3)、……、HSW(n))が立ち上がっている期間の間、信号レベル保持用コンデンサC1の端子電圧VC1が入力信号S1の信号レベルに保持され(図9(A1)～(A3)、(B1))、対応する書き込み信号HSW(HSW(1)、HSW(2)、HSW(3)、……)の立ち下がりのタイミングで、信号レベル保持用コンデンサC1の端子電圧VC1が設定される。すなわちこの場合、時点tn、tn+1、tn+2でそれぞれ信号線SIGの信号レベルが対応する信号レベル保持用コンデンサC1にサンプルホールドされ、これによりこの図8の例では、線順次で、各画素3の階調が設定される。なお図9(B1)との対比により、図9(B2)及び(B3)で示すように、ディスプレイ装置1では、信号線の書き込み信号HSW(HSW(1)、HSW(2)、HSW(3)、……)に対して、入力信号S1の位相が変化すると、入力信号S1により正しく各画素3の階調を設定することが困難になる。従って入力信号S1には、十分な位相マージンを設けることが必要であり、画素数が多くなる程、位相マージンは小さくなる。

10

## 【0013】

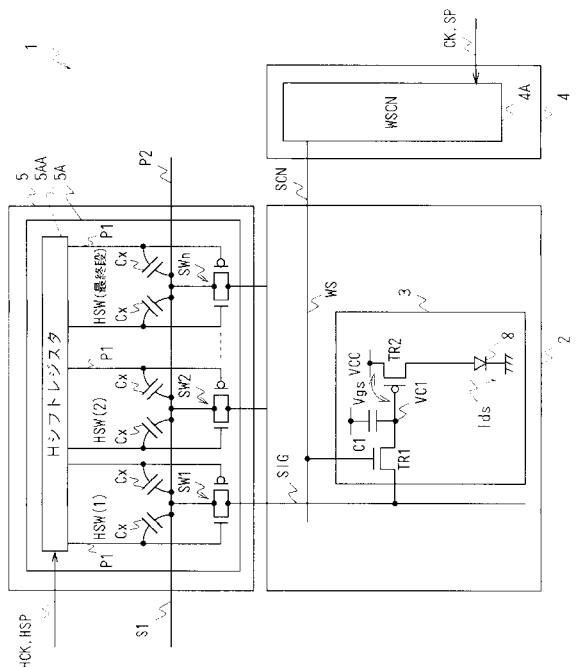

ところで水平セレクタ5Aにおいて、これら信号線の書き込み信号HSW、反転信号の配線パターンP1は、入力信号S1の配線パターンP2と交差することになる。従って図8との対比により図10に示すように、これら書き込み信号HSW、反転信号の配線パターンP1は、入力信号S1の配線パターンP2との間で寄生容量Cxの発生を避け得ず、この寄生容量Cxにより、図11に示すように、信号線の書き込み信号HSW、信号線の書き込み信号の反転信号が、入力信号S1の信号レベルの影響を受け、これら信号線の書き込み信号HSW、信号線の書き込み信号の反転信号におけるエッジのタイミングが入力信号S1の信号レベルによって変化することになる。

20

## 【0014】

その結果、従来のディスプレイ装置では、本来の正しい時点tn、tn+1、tn+2で入力信号S1をサンプルホールドすることが困難になり入力信号の位相マージンが少なくなる問題があった。

30

【特許文献1】U.S.P.5,684,365

【特許文献2】特開平8-234683号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0015】

本発明は以上の点を考慮してなされたもので、従来に比して十分な位相マージンを入力信号に確保することができるディスプレイ装置、駆動回路を提案しようとするものである。

## 【課題を解決するための手段】

## 【0016】

上記の課題を解決するため請求項1の発明は、画素をマトリックス状に配置した画素部と、前記画素部の信号線を順次入力信号の信号レベルに設定して前記画素部を駆動する駆動回路とを有するディスプレイ装置において、少なくとも前記駆動回路において、前記入力信号の配線パターンと平行に逆相信号用の配線パターンが形成され、前記逆相信号用の配線パターンに前記入力信号の逆相の信号が供給されるようにする。

40

## 【0017】

また請求項4の発明は、画素をマトリックス状に配置した画素部を駆動する駆動回路であって、前記画素部の信号線を順次入力信号の信号レベルに設定して前記画素部を駆動し、前記入力信号の配線パターンと平行に逆相信号用の配線パターンが形成され、前記逆相信号用の配線パターンに前記入力信号の逆相の信号を供給する。

## 【0018】

50

請求項 1 又は請求項 4 の構成によれば、入力信号の配線パターンと交差する配線パターンに対して、入力信号の配線パターンから混入する入力信号成分を打ち消すように、逆信号用の配線パターンから逆相の信号を混入させることができる。従ってこの交差する配線パターンに割り当てられる、画素部の信号線を順次入力信号の信号レベルに設定するタイミング信号にあっては、タイミングの変動を防止することができ、従来に比して十分な位相マージンを入力信号に確保することができる。

**【発明の効果】**

**【0019】**

本発明によれば、従来に比して十分な位相マージンを入力信号に確保することができる。

10

**【発明を実施するための最良の形態】**

**【0020】**

以下、適宜図面を参照しながら本発明の実施例を詳述する。

**【実施例 1】**

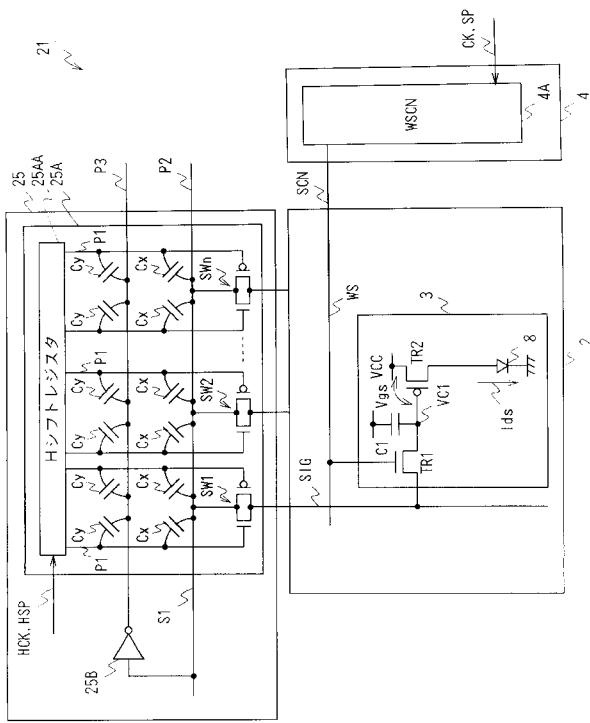

**【0021】**

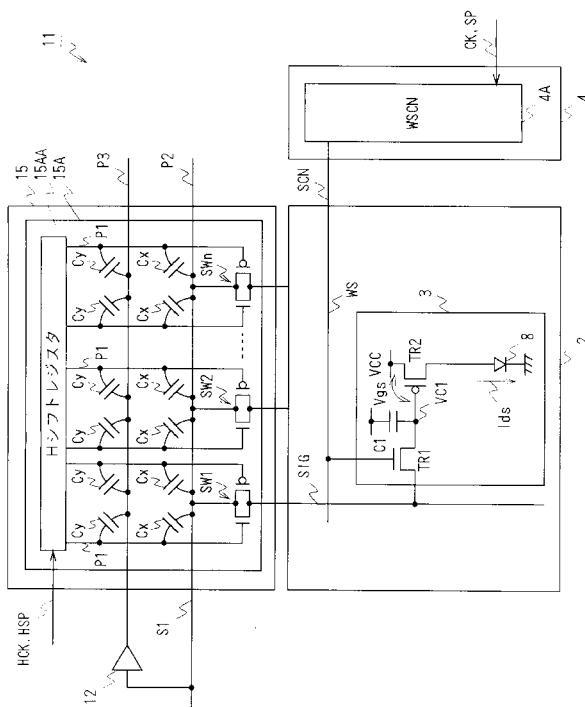

(1) 実施例の構成

図 2 は、図 8 との対比により、本発明の実施例 1 のディスプレイ装置を示すブロック図である。このディスプレイ装置 11 は、画素部 2、垂直駆動回路 4、水平駆動回路 15 がガラス基板上に一体に形成される。このディスプレイ装置 11 は、水平駆動回路 15 において、信号線の書き込み信号 HSW、信号線の書き込み信号 HSW の反転信号の配線パターン P1 と交差するように、入力信号 S1 の配線パターン P2 と平行に、入力信号 S1 の配線パターン P2 の形成層に、逆相信号用の配線パターン P3 が設けられる。これにより図 1 に示すように、ディスプレイ装置 11 は、信号線の書き込み信号 HSW、信号線の書き込み信号の反転信号の配線パターン P1 にそれぞれ寄生容量 Cx を有している入力信号 S1 の配線パターン P2 に対して、この寄生容量 Cx とほぼ同一容量の寄生容量 Cy を配線パターン P1 にそれぞれ有している配線パターン P3 が形成される。

20

**【0022】**

このディスプレイ装置 11 は、水平駆動回路 15 の前段に、利得 -1 の反転増幅回路 12 が設けられる。このディスプレイ装置 11 は、入力信号 S1 をこの反転増幅回路 12 に入力し、入力信号 S1 に対して逆相の信号が生成される。ディスプレイ装置 11 は、この逆相の信号が逆相信号用の配線パターン P3 に供給される。このディスプレイ装置 11 は、この逆相信号用の配線パターン P3 に関する構成が異なる点を除いて、図 4 等について上述した従来構成のディスプレイ装置 1 と同一に構成される。

30

**【0023】**

(2) 実施例の動作

以上の構成において、このディスプレイ装置 11 では、垂直駆動回路 4 による走査線 SCN の駆動により順次ライン単位で画素部 2 の画素 3 が選択される。また水平駆動回路 15 により、画素部 2 に設けられた信号線 SIG が、順次、入力信号 S1 の信号レベルに設定され、これにより点順次で、各画素 3 に設けられた信号レベル保持用コンデンサ C1 の端子電圧 Vc1 が、入力信号 S1 の信号レベルに設定される。このディスプレイ装置 11 では、この信号レベル保持用コンデンサ C1 の端子電圧 Vc1 に応じて各画素 3 の有機 E-L 素子 8 が発光し、これにより入力信号 S1 に応じた所望の画像を表示することができる。

40

**【0024】**

このようにして線順次で各画素 3 の階調を設定するにつき、水平駆動回路 15 では、水平セレクタ 15A の水平レジスタ部 15AA において、所定のサンプリングパルス HSP をクロック HCK で順次転送して、各信号線 SIG を順次選択する信号線の書き込み信号 HSW (HSW(1)、HSW(2)、HSW(3)、……、HSW(n)) と、各書き込み信号 HSW (HSW(1)、HSW(2)、HSW(3)、……、HSW(n)) の反転信号が生成され、これらの書き込み信号 HSW、反転信号によりそれぞれスイッチ回

50

路 S W 1、S W 2、……を順次循環的にオン状態に設定して、画素部 2 に設けられた信号線 S I G が、順次、入力信号 S 1 の信号レベルに設定される。

【0025】

これによりディスプレイ装置 1 1 では、垂直駆動回路 4 による書き込み信号 W S により選択されたラインの画素 3 において、対応するスイッチ回路 S W 1、S W 2、……がオン状態からオフ状態に切り換わるタイミングで、入力信号 S 1 の信号レベルが信号レベル保持用コンデンサ C 1 の端子電圧 V C 1 にサンプルホールドされ、各画素 3 の階調が設定される。

【0026】

しかしながら書き込み信号 H S W、反転信号の配線パターン P 1 と、入力信号 S 1 の配線パターン P 2との間で寄生容量 C x の発生を避け得ないことにより、何ら工夫を施さない場合、これら書き込み信号 H S W、反転信号の信号レベルは、この寄生容量 C x により入力信号 S 1 の信号レベルに応じて変化し、その結果、ディスプレイ装置 1 1 では、スイッチ回路 S W 1、S W 2、……がオン状態からオフ状態に切り換わるタイミングが入力信号 S 1 の信号レベルに応じて変化することになる。

10

【0027】

これによりディスプレイ装置 1 1 では、入力信号 S 1 における位相マージンが小さくなり、著しい場合には入力信号 S 1 の信号レベルを正しく対応する信号レベル保持用コンデンサ C 1 でサンプルホールドすることが困難になり、表示画像が乱れることになる。

20

【0028】

そこでこのディスプレイ装置 1 1 では、信号線の書き込み信号 H S W、反転信号の配線パターン P 1 と交差するように、入力信号 S 1 の配線パターン P 2 と平行に、入力信号 S 1 の配線パターン P 2 の形成層に、逆相信号用の配線パターン P 3 が設けられ、入力信号 S 1 の配線パターン P 2 による寄生容量 C x とほぼ同一容量の寄生容量 C y を、各信号線の書き込み信号 H S W、反転信号の配線パターン P 1 との間でそれぞれ有している配線パターン P 3 が形成される。

20

【0029】

また利得が - 1 の反転增幅回路 1 2 で入力信号 S 1 を増幅して、入力信号 S 1 の逆相の信号が生成され、この逆相の信号が逆相信号用の配線パターン P 3 に供給される。

30

【0030】

これによりこのディスプレイ装置 1 1 では、入力信号 S 1 の配線パターン P 2 による寄生容量 C x によって信号線の書き込み信号 H S W、反転信号に混入する入力信号 S 1 成分を打ち消すように、配線パターン P 3 による寄生容量 C y によって入力信号 S 1 の逆相の信号が配線パターン P 1 に混入し、入力信号 S 1 の信号レベルによる書き込み信号 H S W、反転信号の変化が防止される。

30

【0031】

その結果、このディスプレイ装置 1 1 では、入力信号 S 1 の混入による位相マージンの低下を防止して、従来に比して入力信号 S 1 に十分な位相マージンを確保することができ、画素 3 を高密度で配置して高精細化する場合等にあっても、高品位の画像を表示することができる。

40

【0032】

(3) 実施例の効果

以上の構成によれば、入力信号の配線パターンと平行に逆相信号用の配線パターンを形成し、この逆相信号用の配線パターンに入力信号の逆相の信号を供給することにより、信号線を順次選択するタイミング信号への入力信号の混入を低減することができ、その分、従来に比して十分な位相マージンを入力信号に確保することができる。

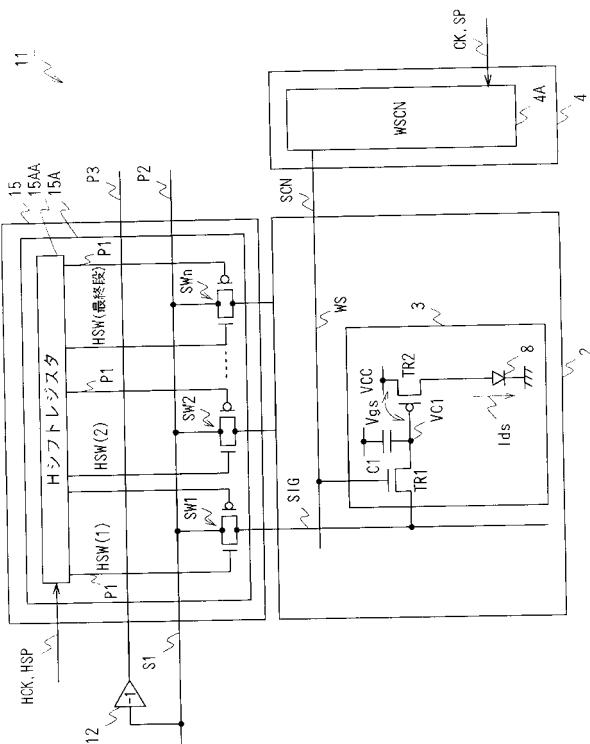

【実施例 2】

【0033】

図 3 は、図 2 との対比により本発明の実施例 2 のディスプレイ装置を示すブロック図である。このディスプレイ装置 2 1 は、水平駆動回路 2 5 に設けたインバータ 2 5 B で、入

50

力信号 S 1 の逆相の信号を生成する。このディスプレイ装置 2 1 は、このインバータ 2 5 B に関する構成が異なる点を除いて、実施例 1 のディスプレイ装置 1 1 と同一に構成される。

#### 【0034】

ここでインバータ 2 5 B は、入力信号 S 1 の信号レベルが所定の基準レベル以下の場合には、出力信号の信号レベルを白レベルの信号レベルに立ち上げ、入力信号 S 1 の信号レベルが所定の基準レベルより大きい場合には、出力信号の信号レベルを黒レベルの信号レベルに立ち下げる。これによりこのディスプレイ装置 2 1 では、白レベル側及び黒レベル側に信号レベルが飽和した状態で、逆相の信号を生成する。

#### 【0035】

すなわち上述のディスプレイ装置 1 1 では、水平駆動回路の前段のアナログ信号処理回路で入力信号 S 1 の逆相の信号を生成することが必要になり、このようなアナログ信号処理回路は、一般に、画素部 2 、垂直駆動回路 4 、水平駆動回路 1 5 とは別体に構成される。従ってディスプレイ装置 1 1 では、アナログ信号処理回路からの出力数が増大することになり、その分、構成が煩雑になる。

10

#### 【0036】

しかしながらこの実施例のように、インバータで逆相の信号を生成すれば、デジタル信号処理回路により逆相の信号を生成することができ、水平駆動回路 2 5 と一体化することができる。従ってその分、実施例 1 に比して簡易な構成で十分な位相マージンを確保することができる。

20

#### 【0037】

なおここでインバータ 2 5 B に、入出力特性にヒステリシス特性を有するインバータを適用して、頻繁な出力信号の信号レベルの切り換わりを防止するようにしてもよい。またトライステートのインバータを適用するようにして、頻繁な出力信号の信号レベルの切り換わりを防止するようにしてもよい。

#### 【0038】

すなわち書き込み信号への影響が最も大きく、位相マージンが最も低下する場合は、入力信号 S 1 の信号レベルが最も大きく変化した場合であり、このような場合についてだけ書き込み信号への入力信号 S 1 の混入を防止するようにしても、実用上十分に位相マージンを確保することができる。

30

#### 【0039】

この実施例によれば、インバータにより逆相の信号を生成することにより、実施例 1 に比して簡易な構成により十分な位相マージンを確保することができる。

#### 【実施例 3】

#### 【0040】

なお上述の実施例においては、入力信号の配線パターンと平行に、入力信号の配線パターンの形成層に、逆相信号用の配線パターンを設けることにより、入力信号の配線パターンと逆相の信号の配線パターンとがほぼ同一の寄生容量を有するように配線パターンを形成する場合について述べたが、本発明はこれに限らず、例えばレイアウトの都合等によって、入力信号の配線パターンに対して寄生容量が異なるように逆相の信号の配線パターンを形成するようにしてもよい。なおこの場合には、必要に応じて、寄生容量が異なる分、逆相の信号の信号レベルを補正することが必要になる。

40

#### 【0041】

また上述の実施例においては、有機 E L 素子によるディスプレイ装置に本発明を適用する場合について述べたが、本発明はこれに限らず、例えば液晶素子によるディスプレイ装置等、種々のディスプレイ装置に広く適用することができる。

#### 【産業上の利用可能性】

#### 【0042】

本発明は、ディスプレイ装置及び駆動回路に関し、例えば有機 E L 素子のディスプレイ装置に適用することができる。

50

## 【図面の簡単な説明】

## 【0043】

【図1】本発明の実施例1のディスプレイ装置の動作の説明に供するブロック図である。

【図2】本発明の実施例1のディスプレイ装置を示すブロック図である。

【図3】本発明の実施例2のディスプレイ装置を示すブロック図である。

【図4】従来の有機EL素子を用いたアクティブマトリックス型のディスプレイ装置を示すブロック図である。

【図5】図4のディスプレイ装置における画素の構成を示す接続図である。

【図6】有機EL素子の経時変化を示す特性曲線図である。

【図7】図4のディスプレイ装置の動作の説明に供する信号波形図である。 10

【図8】図4のディスプレイ装置における水平駆動回路の詳細構成を示すブロック図である。

【図9】図8の水平駆動回路の動作の説明に供する信号波形図である。

【図10】寄生容量の説明に供するブロック図である。

【図11】寄生容量による影響の説明に供する信号波形図である。

## 【符号の説明】

## 【0044】

1、11、21……ディスプレイ装置、2……画素部2……画素、4……垂直駆動回路

4、15、25……水平駆動回路、12……反転増幅回路、25B……インバータ

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 2 3 M

G 0 9 G 3/20 6 2 3 R

G 0 9 G 3/36

H 0 5 B 33/14 A

F ターム(参考) 5C006 AA16 AC09 AF46 AF50 AF71 BB16 BC02 BC06 BC13 BF03

BF11 BF25 BF27 BF33 BF34 FA12 FA16 FA18 FA22 FA33

FA37 FA43 FA54

5C080 AA06 BB05 DD05 DD07 DD08 DD09 DD29 EE28 EE29 FF11

HH09 JJ02 JJ03 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和驱动电路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2008176165A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2008-07-31 |

| 申请号            | JP2007011068                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 申请日     | 2007-01-22 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 山本哲郎<br>甚田誠一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 山本 哲郎<br>甚田 誠一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/30 G09G3/20 G09G3/36 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09G3/30.J G09G3/20.680.G G09G3/20.621.B G09G3/20.623.B G09G3/20.611.J G09G3/20.623.M G09G3/20.623.R G09G3/36 H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC31 3K107/DD39 3K107/EE03 3K107/HH02 3K107/HH04 5C006 /AA16 5C006/AC09 5C006/AF46 5C006/AF50 5C006/AF71 5C006/BB16 5C006/BC02 5C006/BC06 5C006/BC13 5C006/BF03 5C006/BF11 5C006/BF25 5C006/BF27 5C006/BF33 5C006/BF34 5C006 /FA12 5C006/FA16 5C006/FA18 5C006/FA22 5C006/FA33 5C006/FA37 5C006/FA43 5C006/FA54 5C080/AA06 5C080/BB05 5C080/DD05 5C080/DD07 5C080/DD08 5C080/DD09 5C080/DD29 5C080 /EE28 5C080/EE29 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ05 5C380/AA01 5C380/AB06 5C380/AB18 5C380/AB45 5C380/BA08 5C380/BA11 5C380/BA19 5C380/BA20 5C380 /BA31 5C380/BA33 5C380/BA34 5C380/BB22 5C380/BD05 5C380/BD09 5C380/CA08 5C380/CA09 5C380/CA12 5C380/CA21 5C380/CA24 5C380/CA57 5C380/CB01 5C380/CC02 5C380/CC26 5C380 /CC30 5C380/CC33 5C380/CC62 5C380/CD012 5C380/CE19 5C380/CF07 5C380/CF23 5C380/DA02 5C380/DA06 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

### 摘要(译)

显示装置和驱动电路技术领域本发明涉及显示装置和驱动电路，例如，应用于使用有机EL元件的显示装置，与以往相比，能够确保输入信号的足够的相位裕度。根据本发明，用于反相信号的布线图案P3与用于输入信号S1的布线图案P2平行地形成，并且将输入信号S1的相反相位的信号提供给用于反相信号的布线图案P3。要做。[选型图]图1