(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-107166

(P2005-107166A)

(43) 公開日 平成17年4月21日(2005.4.21)

(51) Int.Cl.<sup>7</sup>**G09G 3/30**

**G09G 3/20**

F 1

G09G 3/30 H

G09G 3/20 621A

G09G 3/20 631B

G09G 3/20 631R

テーマコード(参考)

5C080

審査請求 未請求 請求項の数 11 O L (全 8 頁)

(21) 出願番号

特願2003-340647 (P2003-340647)

(22) 出願日

平成15年9月30日 (2003. 9. 30)

(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100107906

弁理士 須藤 克彦

(72) 発明者 安田 仁志

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内F ターム(参考) 5C080 AA06 BB05 DD22 FF11 GG15

GG17 JJ02 JJ03 JJ04

(54) 【発明の名称】画像表示システム及びその制御方法

## (57) 【要約】

【課題】パネル書き込み制御信号を用いた書き込み制御により、表示不良の発生を抑止すると共に、バッファメモリのメモリ容量を小さくできる画像表示システム及びその制御方法を提供する。

【解決手段】有機EL表示パネル300の駆動を停止している1垂直期間中に、CPU100からフレームメモリ211へ表示データの書き込みを、一括して行うことで表示不良を防止している。CPU100から書き込み許可命令がCPUバス101を介して駆動LSI200に出力されると、駆動LSI200はこれを解読して、パネル書き込み制御信号をCPU100に出力する。すると、CPU100は表示データの出力を待機する。その待機中に、フレームメモリ211上にある表示データを読み出し、DA変換器212を介して、有機EL表示パネル300に出力する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数の画素を含む表示パネルと、

CPUバスを介して表示データを出力するCPUと、

前記CPUから出力される前記表示データがバッファメモリを介して書き込まれるフレームメモリを有し、前記CPUから出力される書き込み許可命令に応じて、前記表示データの出力を待機させるための書き込み待機信号を前記CPUに出力すると共に、その内部で発生される駆動信号に応じて、前記フレームメモリに書き込まれた前記表示データを前記表示パネルに出力する駆動回路と、

書き込み待機命令の解除に応じて、前記駆動信号の出力を所定期間、停止する制御回路とを具備し、

前記所定期間中に、前記CPUから表示データを前記フレームメモリに一括して書き込むようにしたことを特徴とする画像表示システム。

**【請求項 2】**

前記駆動信号は、水平スタート信号及び垂直スタート信号であることを特徴とする請求項1に記載の画像表示システム。

**【請求項 3】**

前記複数の画素は、前記フレームメモリから出力された表示データを前記所定期間中、保持する保持回路を有することを特徴とする請求項1又は請求項2に記載の画像表示システム。

**【請求項 4】**

前記所定期間は、1垂直期間以上の期間であることを特徴とする請求項1、2、3のいずれかに記載の画像表示システム。

**【請求項 5】**

前記制御回路が、前記駆動回路に内蔵されたことを特徴とする請求項1、2、3、4のいずれかに記載の画像表示システム。

**【請求項 6】**

前記表示パネルは有機EL表示パネルであることを特徴とする請求項1、2、3、4、5のいずれかに記載の画像表示システム。

**【請求項 7】**

複数の画素を含む表示パネルと、

CPUバスを介して表示データを出力するCPUと、

前記CPUから出力される前記表示データがバッファメモリを介して書き込まれるフレームメモリを有し、前記CPUから出力される書き込み許可命令に応じて、前記表示データの出力を待機させるための書き込み待機信号を前記CPUに出力すると共に、その内部で発生される駆動信号に応じて、前記フレームメモリに書き込まれた前記表示データを前記表示パネルに出力する駆動回路と、

前記書き込み待機命令の解除に応じて、前記駆動信号の出力を停止する制御回路と、を具備する画像表示システムの制御方法であって、

前記書き込み許可命令に応じて、前記表示データの出力を待機させるための書き込み待機信号を前記CPUに出力し、

前記フレームメモリに書き込まれた前記表示データを前記表示パネルに出力し表示を行い、

前記表示の完了後、前記書き込み待機信号を解除し、

前記駆動信号の出力を停止すると共に、この駆動信号の出力が停止されている所定期間に中に、前記CPUから新たな表示データを前記フレームメモリに一括して書き込み、

前記所定期間の経過後に、前記駆動信号の出力を再開し、前記フレームメモリに書き込まれた新たな表示データを前記表示パネルに表示することを特徴とする画像表示システムの表示制御方法。

**【請求項 8】**

10

20

30

40

50

前記駆動信号は、水平スタート信号及び垂直スタート信号であることを特徴とする請求項7に記載の画像表示システムの制御方法。

【請求項9】

前記複数の画素は、前記フレームメモリから出力された表示データを前記所定期間中、保持する保持回路を有することを特徴とする請求項7又は請求項8に記載の画像表示システムの制御方法。

【請求項10】

前記所定期間は、1垂直期間以上の期間であることを特徴とする請求項7、8、9のいずれかに記載の画像表示システムの制御方法。

【請求項11】

前記表示パネルは有機EL表示パネルであることを特徴とする請求項7、8、9、10のいずれかに記載の画像表示システムの制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像表示システム及びその制御方法に関し、特にCPUから出力される表示データをフレームメモリに書き込み、フレームメモリから表示データを読み出して表示パネルに出力する画像表示システム及びその制御方法に関する。

【背景技術】

【0002】

従来より、CPUから表示データを、CPUバスを介して駆動LSIへ出力し、この駆動用LSIに内蔵されたフレームメモリに、バッファメモリを介して一旦書き込み、その後、このフレームメモリに書き込まれた表示データを読み出して、これを表示パネルに出力することで画像表示を行う画像表示システムが知られている。

【0003】

このような画像表示システムでは、表示データのフレームメモリへの書き込みが、フレームメモリからの表示データの読み出しを追い越し、書き込み途中の表示データが表示パネルに出力されてしまい、これにより表示不良が生じるおそれがある。

【0004】

ここで、フレームメモリが2フレーム(2画面)分の表示データを記憶するメモリ容量を有していれば、一方のフレームのメモリ領域に表示データを書き込み中に、他方のフレームのメモリ領域に既に書き込まれた表示データを読み出し、表示パネルに出力するよう制御することで、フレームメモリの書き込みと読み出しどと別個に制御できるので、そのような表示不良を回避することができる。しかし、フレームメモリが1フレーム(1画面)分のメモリ容量しか有していない場合には、そのような表示不良を回避するのは困難である。

【0005】

そこで、駆動用LSIからCPUに対して、フレームメモリへの表示データの出力を一時的に待機させるパネル書き込み制御信号を出力し、表示データのフレームメモリへの書き込みが、フレームメモリからの表示データの読み出しを追い越さないように、フレームメモリへの表示データの書き込みを制御していた。

【0006】

なお、CPUから出力される表示データをフレームメモリに書き込み、フレームメモリから表示データを読み出して表示パネルに出力する画像表示システムについては、以下の特許文献1に記載されている。

【特許文献1】特開平9-244594号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、パネル書き込み制御信号を用いてフレームメモリへの表示データの書き

10

20

30

40

50

込みを制御するに際して、フレームメモリの前段のバッファメモリのメモリ容量が小さいと、パネル書き込み制御信号を用いた書き込み制御を頻繁に行わなければならず、書き込み制御が複雑になるという欠点があった。一方、書き込み制御を容易にするために、表示データをまとめてバッファメモリを介してフレームメモリに書き込むことが考えられるが、バッファメモリのメモリ容量を相当大きくする必要がある。

#### 【0008】

そこで、本発明は、バッファメモリのメモリ容量が小さくても、パネル書き込み制御信号を用いた書き込み制御により、表示不良の発生を抑止した画像表示システム及びその制御方法を提供するものである。

#### 【課題を解決するための手段】

#### 【0009】

本発明の画像表示システムは、複数の画素を含む表示パネルと、CPUバスを介して表示データを出力するCPUと、CPUから出力される前記表示データが書き込まれるフレームメモリを有し、CPUから出力される書き込み許可命令に応じて、表示データの出力を待機させるための書き込み待機信号を前記CPUに出力すると共に、その内部で発生される駆動信号に応じて、フレームメモリに書き込まれた前記表示データを前記表示パネルに出力する駆動回路と、書き込み待機命令の解除に応じて、駆動信号の出力を所定期間、停止する制御回路と、を備えている。そして、所定期間中に、CPUから表示データをフレームメモリに一括して書き込むようにしたことを特徴とするものである。

#### 【0010】

また、画像表示システムの制御方法は、CPUからの書き込み許可命令に応じて、表示データの出力を待機させるための書き込み待機信号をCPUに出力し、フレームメモリに書き込まれた表示データを表示パネルに出力し表示を行い、その表示の完了後、書き込み待機信号を解除し、表示パネルへの駆動信号の出力を停止すると共に、この駆動信号の出力が停止されている所定期間中に、CPUから新たな表示データをフレームメモリに一括して書き込み、所定期間の経過後に、駆動信号の出力を再開し、フレームメモリに書き込まれた新たな表示データを表示パネルに表示することを特徴とするものである。

#### 【発明の効果】

#### 【0011】

本発明によれば、CPUから出力される表示データを、パネル書き込み制御信号を用いた制御により、バッファメモリを介してフレームメモリに書き込み、フレームメモリから表示データを読み出して表示パネルに出力する画像表示システムにおいて、表示不良の発生を防止すると共に、バッファメモリのメモリ容量が小さくすることが可能になる。

#### 【実施例】

#### 【0012】

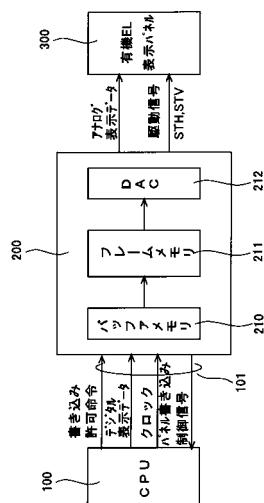

次に、本発明の実施例について図面を参照しながら説明する。図1は、本発明の実施例による画像表示システムのシステム構成を示す図である。

#### 【0013】

CPU100は、CPUバス101を介して、表示データをクロックに同期して駆動LSI200へ出力する。駆動用LSI200には、バッファメモリ210、フレームメモリ211、DA変換器212、垂直スタート信号、水平スタート信号、垂直クロック、水平クロック、垂直同期信号等の各種の駆動信号を発生するタイミングジェネレータ(不図示)が内蔵されている。

#### 【0014】

CPU100からCPUバス101を介して出力された表示データは、バッファメモリ210を介してフレームメモリ211に書き込まれ、その後、このフレームメモリ211に書き込まれた表示データを読み出し、そのデジタルの表示データを、DA変換器212を通してアナログの表示データに変換した後に、有機EL表示パネル300に出力することで画像表示を行う。

#### 【0015】

10

20

30

40

50

ここで、フレームメモリ 211への表示データの書き込みは、有機EL表示パネル300の駆動を停止し、有機EL表示パネル300がその表示を保持している期間中に、一括して行うことで表示不良を防止している。

#### 【0016】

具体的には、CPU100から書き込み許可命令がCPUバス101を介して駆動LSI200に出力されると、駆動LSI200はこれを解読して、パネル書き込み制御信号をCPU100に出力する。すると、CPU100は表示データの出力を待機する。その待機中に、フレームメモリ211上にある表示データを読み出し、DA変換器212を通して、有機EL表示パネル300に出力する。

#### 【0017】

そして、表示データの出力後、次の1垂直期間の間、水平スタート信号STH及び垂直スタート信号STVの出力を停止することで有機EL表示パネル300の駆動を停止すると共に、パネル書き込み制御信号を解除して、CPU100に対して表示データの出力を許可する。そして、有機EL表示パネル300の駆動が停止している間に、CPU100から1フレーム分の表示データが出力され、バッファメモリ210を介してフレームメモリ211に一括して書き込まれる。

#### 【0018】

この有機EL表示パネル300の駆動が停止している1垂直期間の間は、有機EL表示パネル300が表示データの保持機能により、静止画像として表示が保持されるので、表示不良は発生しない。

#### 【0019】

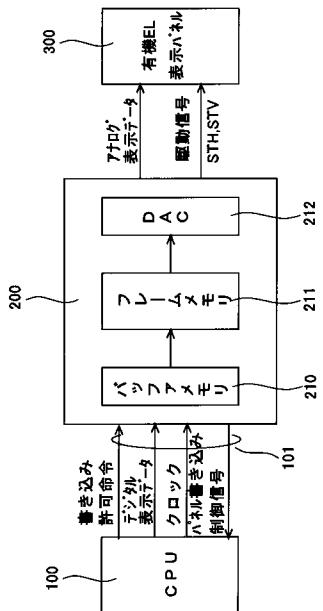

次に、フレームメモリ211への表示データの書き込みを制御する制御回路40及び有機EL表示パネル300の構成について、図2及び図3を参照しながら説明する。図2は、制御回路40、有機EL表示パネル300を示す回路図である。図3は制御回路40の具体的な構成例を示す回路図である。

#### 【0020】

有機EL表示パネル300において、複数の画素は行及び列に配列され、画素領域10を構成している。各画素は、ゲート信号線11とドレイン信号線12の各交差点付近に配置されている。なお、図2において、簡単のために、2行2列分の画素だけが図示されている。

#### 【0021】

ゲート信号線11には、垂直駆動回路30から画素選択信号が出力され、ドレイン信号線12には垂直駆動回路20が表示信号が出力される。そして、各画素は、ゲートがゲート信号線11に接続され、ドレインがドレイン信号線12に接続された画素選択TFT13と、ゲートに画素選択TFT13のソースが接続され、ソースに正駆動電圧PVDdが供給された有機EL駆動TFT14と、アノードが有機EL駆動TFT14のドレインに接続され、カソードに負駆動電圧CVが印加された有機EL素子15と、一端が画素選択TFT13のソースに接続され、その他端に固定電圧が印加された容量素子16と、から構成されている。

#### 【0022】

ここで、TFTは薄膜トランジスタ(thin film transistor)を表す。画素選抲TFT13はNチャネル型、有機EL駆動TFT14はPチャネル型であるが、これに限られない。

#### 【0023】

いま、ゲート信号線11に出力される画素選択信号がハイレベルになると、画素選択TFT13がオンし、ドレイン信号線12から表示信号Vsig(アナログ信号)が画素に書き込まれる。画素に書き込まれた表示信号は、容量素子16に保持される。有機EL駆動TFT14はその表示信号に応じた電流を有機EL素子15に流す。これにより、有機EL素子15は、その電流に応じて発光する。

#### 【0024】

10

20

30

40

50

水平駆動回路 20 には、駆動 L S I 2 0 0 より表示信号 V s i g 、水平クロック信号 C K H 1 , C K H 2 が入力され、制御回路 40 から水平スタート信号 S T H a が入力される。水平駆動回路 20 は、水平スタート信号 S T H a を水平クロック信号 C K H 1 , C K H 2 に同期してシフトし、複数のサンプリングパルスを順次発生するシフトレジスタ（不図示）を有している。表示信号 V s i g は、これらのサンプリングパルスに同期してサンプリングされ、各ドレイン信号線 12 に出力される。表示信号 V s i g を各ドレイン信号線 12 に出力する方式には、いわゆる点順次方式と線順次方式があるが、それらのどちらの方式を用いてもよい。

#### 【 0 0 2 5 】

垂直駆動回路 30 には、駆動 L S I 2 0 0 より垂直クロック信号 C K V 1 , C K V 2 が入力され、制御回路 40 からの水平スタート信号 S T V a が入力されている。そして、垂直駆動回路 30 は、垂直スタート信号 S T V a を水平クロック信号 C K H 1 , C K H 2 に同期してシフトして画素選択信号を作成するシフトレジスタを有しており、それらの画素選択信号を各ゲート信号線 11 に順次出力する。

#### 【 0 0 2 6 】

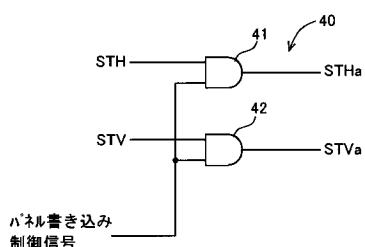

制御回路 40 は、図 3 に示すように、水平スタート信号 S T H 及びパネル書き込み制御信号が入力された第 1 のアンド回路 41 と、垂直スタート信号 S T V 及びパネル書き込み制御信号が入力された第 2 のアンド回路 42 から構成されている。パネル書き込み制御信号が H レベルの時、第 1 のアンド回路 41 の出力信号 S T H a は、水平スタート信号 S T H と同じ信号であり、第 2 のアンド回路 42 の出力信号 S T V a は、垂直スタート信号 S T V と同じ信号である。パネル書き込み制御信号が L レベルの時、出力信号 S T H a 、 S T V a とも L レベルに固定される。制御回路 40 は、駆動 L S I 2 0 0 に内蔵されていてもよいし、その外部に設けられていてもよい。

#### 【 0 0 2 7 】

制御回路 40 の出力信号 S T H a 、 S T V a が L レベルに固定されると、水平駆動回路 20 からサンプリングパルスは出力されず、垂直駆動回路 30 から画素選択信号は出力されないので、有機 E L 表示パネル 300 の駆動は 1 垂直期間停止される。そして、その駆動が停止されている 1 垂直期間中は、それ以前の 1 垂直期間に既に各画素に書き込まれた表示信号 V s i g が各画素の容量素子 16 に保持され、静止画像として表示が保持される。

30

#### 【 0 0 2 8 】

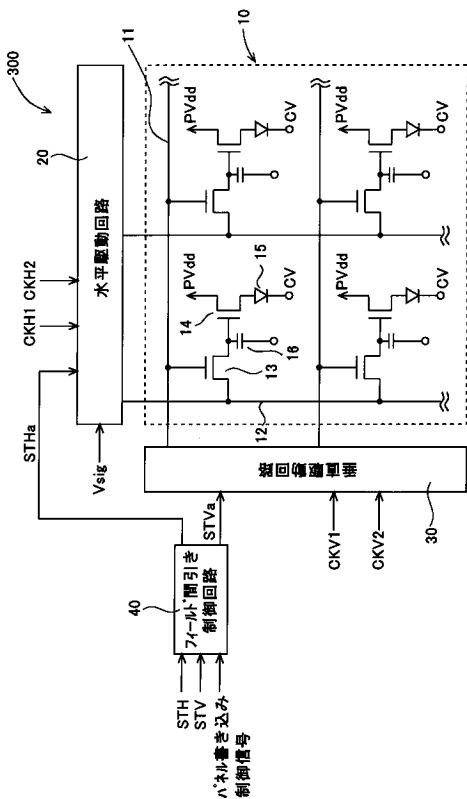

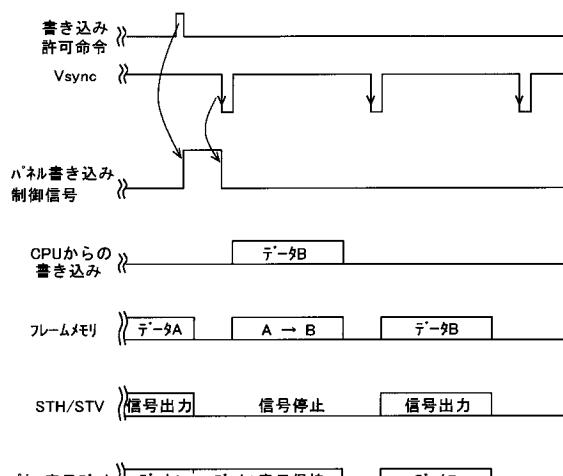

次に、本実施例の画像表示システムの動作例について、図 4 のタイミング図を参照しながらさらに詳しく説明する。

#### 【 0 0 2 9 】

いま、フレームメモリ 211 には、既に表示データ A ( 1 フレーム分の表示データ ) が書き込まれてあり、フレームメモリ 211 からは表示データ A が順次読み出され、有機 E L 表示パネル 300 に出力されているものとする。

#### 【 0 0 3 0 】

そして、この 1 垂直期間中の途中で、 C P U 1 0 0 から書き込み許可命令が C P U バス 101 を介して駆動 L S I 2 0 0 に出力されるとする。駆動 L S I 2 0 0 は、この命令を解読して、パネル書き込み制御信号 ( H レベル ) を C P U 1 0 0 に出力する。

40

#### 【 0 0 3 1 】

すると、 C P U 1 0 0 は表示データの出力を待機する。フレームメモリ 211 上にある表示データ A は引き続き、読み出され、 D A 変換器 212 を介して、有機 E L 表示パネル 300 に出力され続ける。そして、その 1 垂直期間の間にすべての表示データ A が出力され、有機 E L 表示パネル 300 に書き込まれる。

#### 【 0 0 3 2 】

そして、表示データ A の出力の完了は垂直同期信号 V inc によって検知され、これに応じて、パネル書き込み制御信号は H レベルからは L レベルに変化し、 C P U 1 0 0 のウエイト状態が解除される。すると、制御回路 40 により、水平スタート信号 S T H 及び垂直

50

スタート信号 S T V の出力が次の 1 垂直期間中、停止され、有機 E L 表示パネル 3 0 0 の駆動が停止される。

【 0 0 3 3 】

そして、有機 E L 表示パネル 3 0 0 の駆動が停止している間に、C P U 1 0 0 から 1 フレーム分の新たな表示データ B が出力され、バッファメモリ 2 1 0 を介してフレームメモリ 2 1 1 に一括して書き込まれる。

【 0 0 3 4 】

この有機 E L 表示パネル 3 0 0 の駆動が停止している 1 垂直期間の中は、書き込み途中の表示データ B が表示されることはない。また、有機 E L 表示パネル 3 0 0 は表示データ A の保持機能を有しているので、表示データ A の表示が保持され、表示不良は発生しない。

10

【 0 0 3 5 】

そして、次の 1 垂直期間には、水平スタート信号 S T H 及び垂直スタート信号 S T V の出力が再び出力されるようになり、有機 E L 表示パネル 3 0 0 の駆動が再開され、フレームメモリ 2 1 1 に書き込まれた表示データ B が読み出され、この表示データ B が有機 E L 表示パネル 3 0 0 に出力され、表示される。

【 0 0 3 6 】

このように、本実施例によれば、有機 E L 表示パネル 3 0 0 の駆動が停止している 1 垂直期間中に、C P U 1 0 0 からフレームメモリ 2 1 1 へ表示データの一括書き込みを行うようにしたので、フレームメモリ 2 1 1 の前段のバッファメモリ 2 1 0 のメモリ容量が小さくても、表示不良を防止でき、しかもパネル書き込み制御信号による書き込み制御を頻繁に行う必要がなくなる。なお、水平スタート信号 S T H 及び垂直スタート信号 S T V の出力を停止させることで、有機 E L 表示パネル 3 0 0 の駆動を停止させる期間は、1 垂直期間以上の期間であってもよい。

20

【 0 0 3 7 】

また、本実施例では、有機 E L 表示パネル 3 0 0 の各画素に有機 E L 素子 1 5 を用いているが、これに限らず、無機 E L 素子や、その他の E L 素子、L E D 素子を用いてもよい。また、各画素の容量素子 1 6 は、各画素に書き込まれた表示信号を保持する保持回路の一例であり、これに限らず、S R A M 等の他の保持回路を用いてもよい。

【 図面の簡単な説明 】

30

【 0 0 3 8 】

【 図 1 】本発明の実施例による画像表示システムを示すシステム図である。

【 図 2 】制御回路 4 0 、有機 E L 表示パネル 3 0 0 を示す回路図である。

【 図 3 】制御回路 4 0 の具体的な構成例を示す回路図である。

【 図 4 】本発明の実施例による画像表示システムの動作を説明するタイミング図である。

【 符号の説明 】

【 0 0 3 9 】

|       |         |       |                 |       |              |

|-------|---------|-------|-----------------|-------|--------------|

| 1 0   | 画素領域    | 1 1   | ゲート信号線          | 1 2   | ドレイン信号線      |

| 1 3   | 画素選択信号  | 1 4   | 有機 E L 駆動 T F T | 1 5   | 有機 E L 素子    |

| 1 6   | 容量素子    | 2 0   | 水平駆動回路          | 3 0   | 垂直駆動回路       |

| 4 0   | 制御回路    | 4 1   | 第 1 のアンド回路      | 4 2   | 第 2 のアンド回路   |

| 1 0 0 | C P U   | 2 0 0 | 駆動 L S I        | 2 1 0 | バッファメモリ      |

| 2 1 1 | フレームメモリ | 2 1 2 | D A 変換器         | 3 0 0 | 有機 E L 表示パネル |

【図1】

【図2】

【図3】

【図4】

|                |                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 图像显示系统及其控制方法                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2005107166A</a>                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2005-04-21 |

| 申请号            | JP2003340647                                                                                                                                                                                                                                                                                                                               | 申请日     | 2003-09-30 |

| [标]申请(专利权)人(译) | 三洋电机株式会社                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 安田仁志                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 安田 仁志                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/30.H G09G3/20.621.A G09G3/20.631.B G09G3/20.631.R G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD22 5C080/FF11 5C080/GG15 5C080/GG17 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/BA15 5C380/CA08 5C380/CA09 5C380/CA12 5C380/CB01 5C380/CC02 5C380/CC26 5C380/CC33 5C380/CC62 5C380/CD012 5C380/CE19 5C380/CF02 5C380/CF07 5C380/CF48 5C380/CF62 5C380/DA06 5C380/DA35 5C380/DA41 5C380/DA56 |         |            |

| 代理人(译)         | 须藤克彦                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

解决的问题：提供一种图像显示系统及其控制方法，该图像显示系统能够通过使用面板写入控制信号的写入控制来抑制显示故障的发生并减小缓冲存储器的存储容量。通过在停止有机EL显示面板300的驱动的一个垂直周期内将来自CPU 100的显示数据集中地写入帧存储器211，来防止显示不良。当经由CPU总线101从CPU 100向驱动器LSI 200输出写使能命令时，驱动器LSI 200对其进行解码并将面板写控制信号输出至CPU 100。然后，CPU 100等待显示数据的输出。在待机期间，帧存储器211上的显示数据被读取并经由DA转换器212输出到有机EL显示面板300。[选型图]图1