(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5400614号

(P5400614)

(45) 発行日 平成26年1月29日(2014.1.29)

(24) 登録日 平成25年11月1日(2013.11.1)

|                      |               |

|----------------------|---------------|

| (51) Int.Cl.         | F 1           |

| H05B 33/10 (2006.01) | H05B 33/10    |

| H05B 33/12 (2006.01) | H05B 33/12 E  |

| H01L 51/50 (2006.01) | H05B 33/14 A  |

| G02B 5/20 (2006.01)  | H05B 33/12 Z  |

| G09F 9/30 (2006.01)  | G02B 5/20 101 |

請求項の数 18 (全 23 頁) 最終頁に続く

|               |                               |           |                                                            |

|---------------|-------------------------------|-----------|------------------------------------------------------------|

| (21) 出願番号     | 特願2009-532358 (P2009-532358)  | (73) 特許権者 | 510059907<br>グローバル オーエルイーディー テクノロジー リミティド ライアビリティ カンパニー    |

| (86) (22) 出願日 | 平成19年10月2日 (2007.10.2)        |           | アメリカ合衆国, バージニア 20171, ハーフォード, パーク センター ロード 13873, スイート 330 |

| (65) 公表番号     | 特表2010-506375 (P2010-506375A) | (74) 代理人  | 100099759<br>弁理士 青木 篤                                      |

| (43) 公表日      | 平成22年2月25日 (2010.2.25)        | (74) 代理人  | 100077517<br>弁理士 石田 敏                                      |

| (86) 国際出願番号   | PCT/US2007/021128             | (74) 代理人  | 100087413<br>弁理士 古賀 哲次                                     |

| (87) 国際公開番号   | WO2008/045232                 | (74) 代理人  | 100128495<br>弁理士 出野 知                                      |

| (87) 国際公開日    | 平成20年4月17日 (2008.4.17)        |           |                                                            |

| 審査請求日         | 平成22年9月14日 (2010.9.14)        |           |                                                            |

| (31) 優先権主張番号  | 11/548,040                    |           |                                                            |

| (32) 優先日      | 平成18年10月10日 (2006.10.10)      |           |                                                            |

| (33) 優先権主張国   | 米国(US)                        |           |                                                            |

最終頁に続く

(54) 【発明の名称】調節されたフィルタ・アレイを有するOLEDディスプレイ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

- 画像を生成させるOLEDディスプレイ装置を製造する方法であって、

- a) 光発生素子アレイを形成するステップと、

- b) その光発生素子アレイをテストして欠陥のある光発生素子の位置を記録するステップと、

- c) カラー・フィルタ素子が形成されていないスペースにより発生させる白色を含め異なる少なくとも2色を生成するカラー・フィルタ素子を有するアレイのデフォルト・パターンを用意するステップと、

- d) 記録されている前記欠陥のある光発生素子の位置に対応する前記アレイ上の位置にカラー・フィルタ素子が形成されている場合には、前記欠陥のある光発生素子の位置に対応するカラー・フィルタ素子の位置と前記スペースの位置とが入れ替わるように、少なくとも1つのカラー・フィルタ素子の位置が前記デフォルト・パターンから変化しているカラー・フィルタ素子アレイを形成するステップと、を含み、

前記カラー・フィルタ素子アレイのデフォルト・パターンは、異なる色のカラー・フィルタ素子があらかじめ決められたランダムな配置にされている、

ことを特徴とする方法。

## 【請求項 2】

- e) メモリ・ユニットを用意するステップと、

- f) 欠陥のある上記光発生素子の位置とカラー・フィルタ素子の調節された位置の一方

10

20

または両方を上記メモリ・ユニットに記憶させるステップと、

g) ビデオ信号と、上記メモリ・ユニットに記憶された位置とに応じて上記光発生素子アレイを駆動する電子的駆動ユニットを用意するステップをさらに含む、請求項 1 に記載の方法。

【請求項 3】

アクティブ・マトリックス回路を形成するステップをさらに含む、請求項 1 に記載の方法。

【請求項 4】

上記光発生素子が広帯域光を発生させる、請求項 1 に記載の方法。

【請求項 5】

上記カラー・フィルタ素子アレイが、赤色、緑色、青色の複数のカラー・フィルタ素子を含む、請求項 4 に記載の方法。

【請求項 6】

上記カラー・フィルタ素子アレイのカラー・フィルタ素子の間に複数のフィルタなしのスペースが形成されていて、上記光発生素子アレイが、赤色画素を形成する赤色カラー・フィルタ素子と揃った複数の光発生素子と、緑色画素を形成する緑色カラー・フィルタ素子と揃った複数の光発生素子と、青色画素を形成する青色カラー・フィルタ素子と揃った複数の光発生素子と、広帯域画素を形成するフィルタなしの上記スペースと揃った複数の光発生素子とを含んでいる、請求項 5 に記載の方法。

【請求項 7】

欠陥のある上記光発生素子に関して記録されている位置に応じ、欠陥のあるその光発生素子がフィルタなしの上記スペースと揃うように上記デフォルト・パターンから 1 つ以上のカラー・フィルタ素子の位置を変化させる、請求項 6 に記載の方法。

【請求項 8】

上記カラー・フィルタ素子アレイのカラー・フィルタ素子の間に複数のフィルタなしのスペースが形成されていて、上記光発生素子アレイが、広帯域画素を形成するフィルタなしの上記スペースと揃った複数の光発生素子を含んでいる、請求項 1 に記載の方法。

【請求項 9】

欠陥のある上記光発生素子に関して記録されている位置に応じて 1 つ以上のカラー・フィルタ素子の位置を調節し、欠陥のあるその光発生素子をフィルタなしの上記スペースと揃える、請求項 8 に記載の方法。

【請求項 10】

欠陥のある上記光発生素子に関して記録されている位置に応じて 1 つ以上の光阻止素子の位置を調節した光阻止素子アレイを形成するステップをさらに含む、請求項 1 に記載の方法。

【請求項 11】

欠陥のある上記光発生素子に関して記録されている位置に応じて 1 つ以上の光阻止素子の位置を調節し、欠陥のあるその光発生素子をその光阻止素子と揃える、請求項 10 に記載の方法。

【請求項 12】

インクジェットの堆積を利用して上記カラー・フィルタ素子を形成する、請求項 1 に記載の方法。

【請求項 13】

ドナー・シートからカラー・フィルタ材料を転写することによって上記カラー・フィルタ素子を形成する、請求項 1 に記載の方法。

【請求項 14】

マスクなしパターニング法を利用して上記カラー・フィルタ素子を形成する、請求項 1 に記載の方法。

【請求項 15】

上記光発生素子アレイのテストを不活性な環境または減圧環境の中で実施する、請求項 1 に記載の方法。

10

20

30

40

50

1に記載の方法。

**【請求項 1 6】**

上記光発生素子アレイのテストに、その光発生素子アレイに電力を供給して各光発生素子の光出力を測定する操作が含まれる、請求項 1 に記載の方法。

**【請求項 1 7】**

ビデオ画像を生成させるOLEDディスプレイ装置を製造する方法であって、

- a) 第1の基板と第2の基板を用意するステップと、

- b) その第1の基板上に光発生素子アレイを形成するステップと、

- c) その第1の基板をテストして欠陥のある光発生素子の位置を記録するステップと、

- d) カラー・フィルタ素子が形成されていないスペースにより発生させる白色を含め異なる少なくとも2色を生成するカラー・フィルタ素子を有するアレイのデフォルト・パターンを用意するステップと、

- e) 記録されている前記欠陥のある光発生素子の位置に対応する前記アレイ上の位置にカラー・フィルタ素子が形成されている場合には、前記欠陥のある光発生素子の位置に対応するカラー・フィルタ素子の位置と前記スペースの位置とが入れ替わるように、前記第2の基板上に、少なくとも1つのカラー・フィルタ素子の位置が前記デフォルト・パターンから変化しているカラー・フィルタ素子アレイを形成するステップと、

- f) 前記カラー・フィルタ素子アレイを前記光発生素子アレイの少なくとも一部と揃えて前記第1の基板を前記第2の基板に接着するステップと、を含み、

前記カラー・フィルタ素子アレイのデフォルト・パターンは、異なる色のカラー・フィルタ素子があらかじめ決められたランダムな配置にされている、

ことを特徴とする方法。

**【請求項 1 8】**

上記光発生素子と上記カラー・フィルタ素子を上記第1の基板と上記第2の基板の間に配置する、請求項 1 7 に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、欠陥のある光発生素子に応じて変化するカラー・フィルタ素子アレイを有するOLEDディスプレイ装置の製造に関する。

**【背景技術】**

**【0002】**

最も単純な形態の有機エレクトロルミネッセンス(EL)デバイスは、正孔を注入するためのアノードとして機能する第1の電極と、電子を注入するためのカソードとして機能する第2の電極の間に配置された有機エレクトロルミネッセンス媒体で構成されている。有機エレクトロルミネッセンス媒体は、正孔と電子の再結合をサポートして光を発生させる。このデバイスは、一般に、有機発光ダイオードまたはOLEDとも呼ばれている。基本的な有機EL素子がアメリカ合衆国特許第4,356,429号に記載されている。ディスプレイとして有用な画素化されたOLEDディスプレイ装置(例えばテレビ、コンピュータのモニタ、携帯電話のディスプレイ、デジタル・カメラのディスプレイ)を構成するには、個々の有機EL素子を画素としてマトリックスのパターンに配置することができる。これらの画素は、すべて同じ色を発生するように製造してモノクロ・ディスプレイを作り出すこと、または複数の色を発生するように製造すること(例えば3画素式(赤、緑、青(RGB))ディスプレイ)ができる。

**【0003】**

高性能のディスプレイを製造するため、OLEDディスプレイ装置はアクティブ・マトリックス(AM)駆動回路を用いて製造してきた。そのようなAM OLEDディスプレイ装置の一例が、アメリカ合衆国特許第5,550,066号に開示されている。しかしこのタイプのディスプレイ装置では、光が基板を通過して下方に出るとき、光を発生させることのできる全面積は、不透明な薄膜トランジスタ(TFT)と他の回路の存在によって制限される。ディス

10

20

30

40

50

プレイの画素の全面積に対する発光画素の面積はアパー・チャ比(AR)として知られており、このようなディスプレイでは一般に50%未満である。小さなARを補償するため、このディスプレイ装置は、大きなARを持つディスプレイ装置よりも大きな電流密度で駆動せねばならない。その結果、ARがより小さなディスプレイ装置は、ARがより大きなディスプレイ装置よりも多くの電力を消費するため、使用可能な寿命がより短い。

#### 【0004】

したがって、トップ-エミッション型(または表面発光型)のAM OLEDディスプレイ装置、すなわち光が基板とアクティブ・マトリックス回路から上面を通過して出ていくAM OLE Dディスプレイ装置を製造するために多くの研究がこれまでになされてきた。このようなディスプレイ装置がアメリカ合衆国特許第6,737,800号に記載されている。このトップ-エミッション型の構成によってARを大きくし、したがってディスプレイの性能を向上させることができる。10

#### 【0005】

マルチ-カラー・ディスプレイを形成する1つの方法には、カラー・フィルタ素子からなる多色アレイ(CFA)とカップルした広帯域発光EL構造(例えば白色発光EL構造)を使用することが含まれる。この構成では、単一の有機EL層をすべての画素に適用することができ、見る人が認識する色は、画素の対応するカラー・フィルタ素子によって決まる。したがってマルチカラー装置またはRGB装置は、有機EL層をまったくパターニングせずに製造することができる。CFAを有するこのようなトップ-エミッション型白色光AMディスプレイ装置は、マルチカラー・パターニングがなされたトップ-エミッション型AMディスプレイ装置と比べて優れたAR、優れた製造の歩留まり、優れた製造スループットを提供することができる。白色CFAトップ-エミッション型ディスプレイ装置の一例が、アメリカ合衆国特許第6,392,340号に示されている。20

#### 【0006】

4つの異なるカラー画素を備える構成のカラー有機ELディスプレイも最近報告されている。4画素ディスプレイの一例は、赤色、緑色、青色、白色の画素を含んでいる。この構成は、RGBWタイプのディスプレイとして知られている。このような4画素ディスプレイの例が、アメリカ合衆国特許第6,771,028号、第7,012,588号、アメリカ合衆国特許出願公開2004/0113875 A1、2004/0201558 A1に示されている。このようなRGBWディスプレイは、赤色フィルタ、緑色フィルタ、青色フィルタをそれぞれ赤色画素、緑色画素、青色画素のために備えた白色有機EL発光層を用いて構成することができる。白色画素の領域は、フィルタなしにされる。フィルタなしの白色画素が含まれていることで、RGBだけを備えるフィルタ付きの同様の広帯域OLEDディスプレイと比べて少ない消費電力で完全には飽和しない色の表示が可能になる。30

#### 【0007】

有機ELディスプレイを製造するとき、有機EL材料に粒子の汚染や引っかき傷という問題があると、ディスプレイに欠陥が生じる可能性がある。粒子の汚染や引っかき傷によって起こる欠陥の1つのタイプは、薄い有機材料を貫通する短絡が発生してアノードとカソードが接続されるというものである。アノードとカソードが短絡すると、発光しない画素(死んだ画素)、または明るさが低下した画素(暗い画素)になる。40

#### 【0008】

同様に、粒子、引っかき傷、マスク-エラー、静電放電(ESD)や、同様の製造上の問題が、アクティブ・マトリックス式OLEDディスプレイ装置のアクティブ・マトリックス回路を製造する際に起こる可能性があり、その結果として機能しない画素や、正しくない輝度レベルの(暗い、または明るい)画素になる。あるいはアクティブ・マトリックス回路に欠陥があると、画素が動作中を通じて連続的に発光し、選択的にオフにできない状態になる可能性がある。これは、スタック-オン画素と呼ばれるタイプの欠陥画素である。

#### 【0009】

製造上のこれら欠陥の多くは、一般に、製造プロセスの性能、装置、環境に依存した面積密度で発生する。しかし非発光画素に関する全歩留まりは、欠陥の面積密度と、個々の50

ディスプレイの面積とに依存する。欠陥の密度が同じだとすると、より大きなディスプレイ装置（例えばテレビ、コンピュータ、ラップトップコンピュータのためのディスプレイ装置）では、より小さな基板よりも歩留まりが低下するであろう。

#### 【0010】

マルチカラー装置では、1つの色で死んだ画素になったり、暗い画素になったり、明るい画素になったり、スタック-オン画素になったりすると、画像の色が歪む可能性がある。すなわち、異なる色の複数の画素（例えば赤色画素と緑色画素）を所定の輝度比で同時に光らせることができるため、見る人は望ましい色（例えば黄色）を認識する。この例では、1つの画素（例えば緑色画素）が死んだり暗くなったりすると、得られる画像は、欠陥のある画素の領域で望む黄色には見えず、より赤色に見えるであろう。

10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0011】

そこで本発明の1つの目的は、カラー・フィルタ素子アレイをえていて、1つ以上の光発生素子が欠陥のある画素の場合でさえ高品質の画像を表示できるOLEDディスプレイ装置の製造方法を提供することである。

#### 【課題を解決するための手段】

#### 【0012】

この目的は、画像を生成させるOLEDディスプレイ装置を製造する方法であって、

- a) 光発生素子アレイを形成するステップと；

- b) その光発生素子アレイをテストして欠陥のある光発生素子の位置を記録するステップと；

- c) 異なる少なくとも2色のカラー・フィルタ素子からなるアレイのデフォルト・パターンを用意するステップと；

- d) 欠陥のある上記光発生素子に関して記録されている位置に応じ、少なくとも1つのカラー・フィルタ素子の位置が上記デフォルト・パターンから変化しているカラー・フィルタ素子アレイを形成するステップを含む方法によって達成される。

20

#### 【発明の効果】

#### 【0013】

本発明により、カラー・フィルタ素子を有するOLEDディスプレイ中の欠陥のある光発生素子を補償する有効な方法が提供される。高品質の画像を色の歪みなしに生成させることができる。本発明により、不合格になるOLEDディスプレイ装置を減らす方法が提供されるため、全体的な製造コストが低下する。

30

#### 【図面の簡単な説明】

#### 【0014】

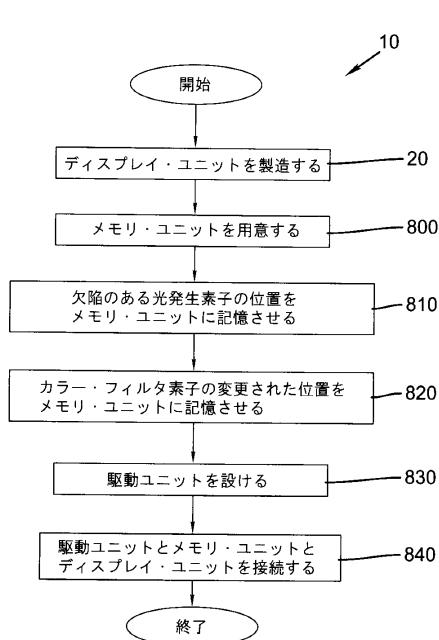

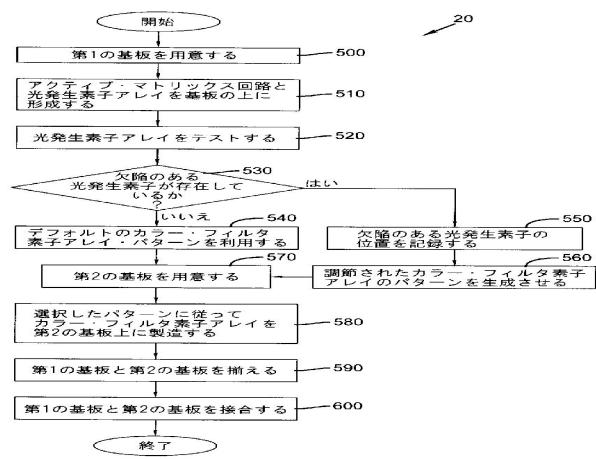

【図1】本発明によるOLEDディスプレイ装置を製造する方法の一実施態様を示すブロック・ダイヤグラムである。

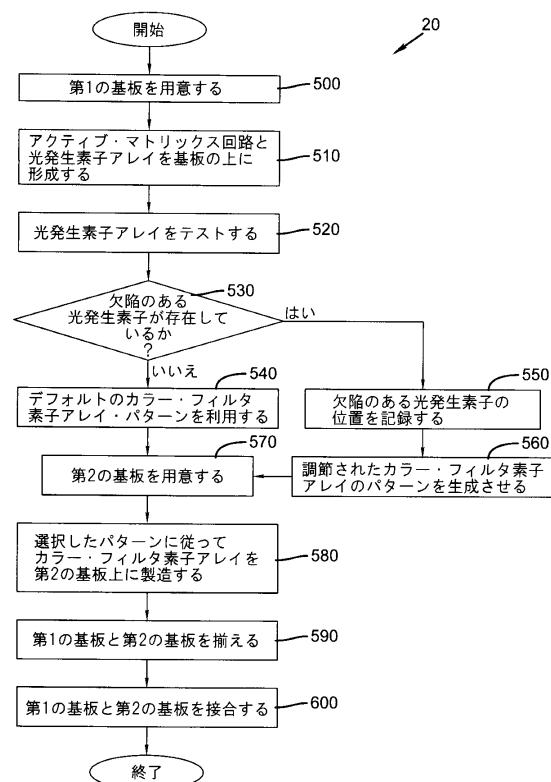

【図2】OLEDディスプレイ装置のOLEDディスプレイ・ユニットを製造する図1の方法をより詳細に示すブロック・ダイヤグラムである。

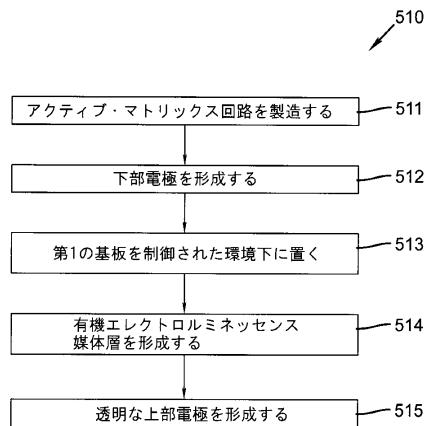

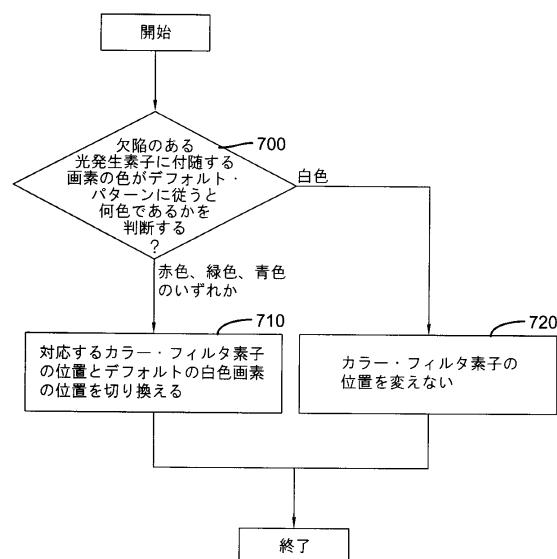

【図3】図2の実施態様の一部をより詳細に示すブロック・ダイヤグラムである。

40

【図4A】従来のOLEDディスプレイ装置のための、アクティブ・マトリックス回路を有する光発生素子アレイの概略レイアウト図である。

【図4B】従来のOLEDディスプレイ装置のためのカラー・フィルタ素子アレイを示している。

【図5A】アクティブ・マトリックス回路を有する光発生素子アレイに関する本発明の第1の実施態様の概略レイアウト図であり、ここでは1つの光発生素子に欠陥がある。

【図5B】本発明の第1の実施態様に従ってカラー・フィルタ素子の位置が調節されたカラー・フィルタ素子アレイを示している。

【図6】本発明の第1の実施態様によるOLEDディスプレイ装置の断面図である。

【図7】本発明の第1の実施態様に従ってカラー・フィルタ素子の位置を調節するための

50

論理アルゴリズムを示すブロック・ダイヤグラムである。

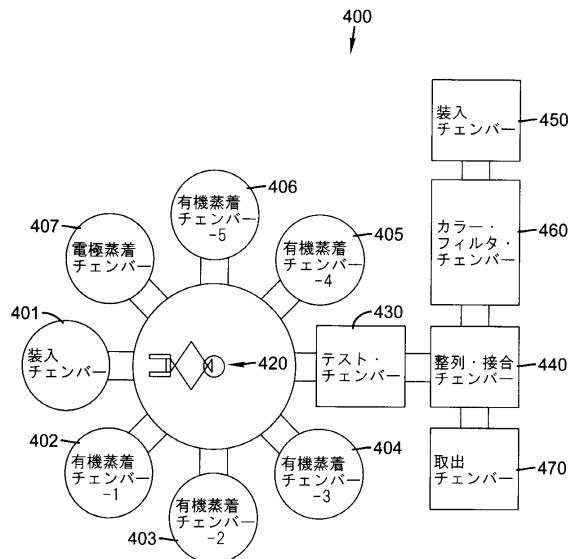

【図8】本発明によるOLEDディスプレイ装置を製造するため一連のチェンバーを有する製造ツールの一例を示している。

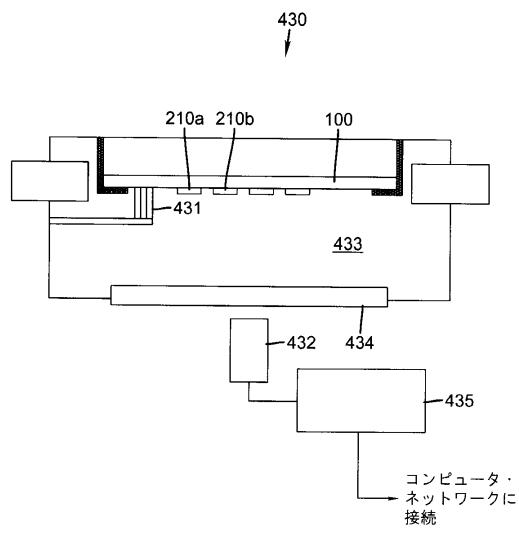

【図9】図8の製造ツールのテスト・チェンバーの詳細図である。

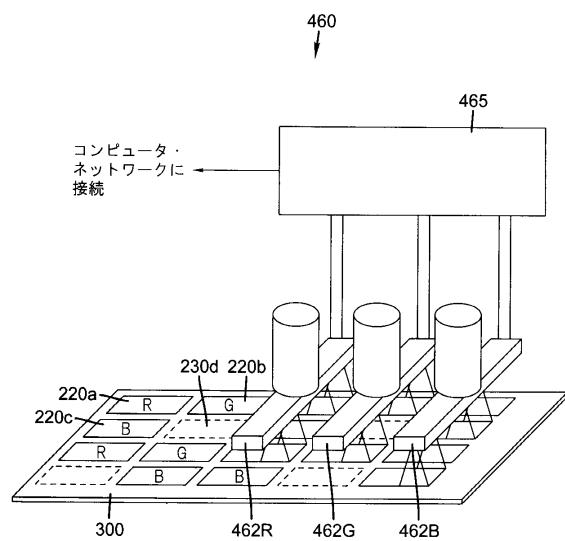

【図10】図8の製造ツールのカラー・フィルタ・チェンバーの詳細図である。

【図11】本発明の第2の実施態様によるOLEDディスプレイ装置の断面図である。

【図12】本発明の第3の実施態様に従ってカラー・フィルタ素子の位置が調節された、光阻止素子を含むカラー・フィルタ素子アレイを示している。

【発明を実施するための形態】

【0015】

10

デバイスの特徴的なサイズ（例えば層の厚さ）はミクロン未満の範囲であることがしばしばあるため、図面は、サイズを正確にするのではなく、見やすくなる縮尺にしてある。

【0016】

20

“マルチカラー”という用語は、異なる領域では色相が異なる光を出すことのできるディスプレイ装置を記述するのに用いる。この用語は、特に、いろいろな色からなる画像を表示することのできるディスプレイ・パネルを記述するのに用いる。“フル・カラー”という用語は、一般に、可視スペクトルの少なくとも赤色領域、緑色領域、青色領域で光を出すことが可能であらゆる組み合わせの色相の画像を表示することのできるマルチカラー・ディスプレイ・パネルを記述するのに用いる。赤色、緑色、青色が三原色を構成し、その三原色を適切に混合することによって他のすべての色を作り出すことができる。しかしデバイスの色域を広げるために追加の色を用いることも可能である。“画素”という用語は、この分野で知られている意味で用いられ、ディスプレイ・パネル内で刺激を与えることによって他の領域とは独立に光を出させることのできる領域を指す。フル-カラー・システムでは、色が異なるいくつかの画素を合わせて使用して広い範囲の色を作り出すことが知られている。この明細書では、そのようなグループを色の異なるいくつかの画素と見なす。

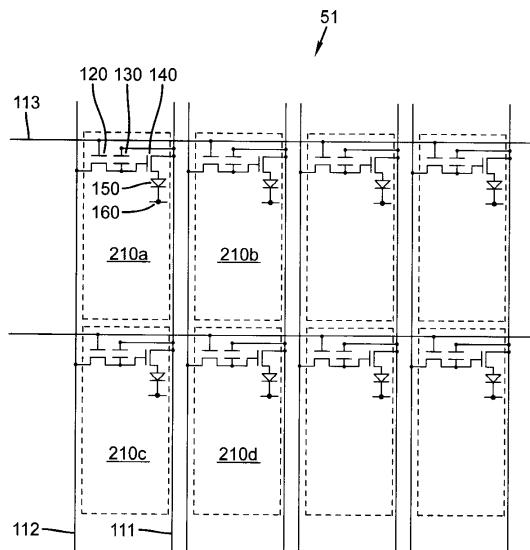

【0017】

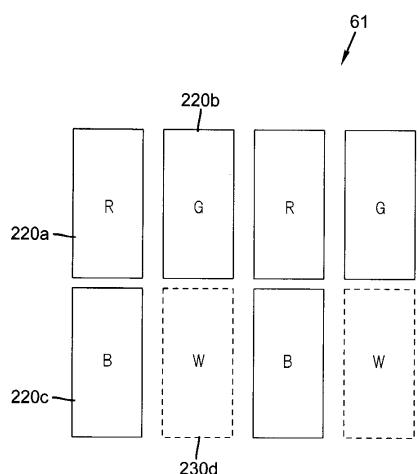

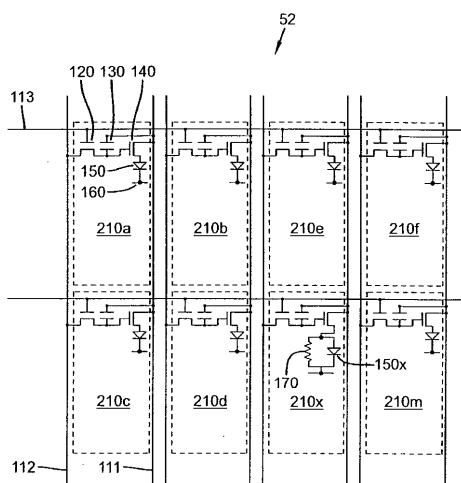

本発明をより十分に理解するため、従来のOLEDディスプレイ装置の特徴を図4Aと図4Bを参照して説明する。従来のディスプレイ装置のアクティブ・マトリックス回路を有する光発生素子アレイ51の概略レイアウト図を図4Aに示してある。この図には、光発生素子210a、210b、210c、210dが含まれている。説明を目的として2行4列に配置された合計で8つの光発生素子を示してあるが、典型的なディスプレイは一般にはるかに多くの行と列を有する。対応するカラー・フィルタ素子アレイ61を図4Bに示してある。この図には、カラー・フィルタ素子220a、220b、220cが含まれている。カラー・フィルタ素子の間には、フィルタのないスペース（例えばフィルタのないスペース230d）が残されている。この従来のディスプレイ装置は、光発生素子アレイ51をカラー・フィルタ素子アレイ61に揃えて取り付けることによって形成される。この場合には、カラー・フィルタ素子220aは光発生素子アレイ210aに揃え、カラー・フィルタ素子220bは光発生素子アレイ210bに揃え、カラー・フィルタ素子220cは光発生素子アレイ210cに揃えることで、それぞれが赤(R)、緑(G)、青(B)のカラー画素を形成する。同様に、フィルタのないスペース230dは光発生素子アレイ210dに揃えることで、白色(W)画素を形成する。画素は4つ組パターンとして知られる $2 \times 2$ のパターンに配置される。このパターンを表示領域全体で繰り返す。他のさまざまな画素パターンも従来技術で知られている。別のパターンのいくつかの例が、アメリカ合衆国特許第6,919,681号に示されている。

【0018】

例として示したこの従来のディスプレイは、図4Aに示したアクティブ・マトリックス回路によって電気的に駆動される。このアクティブ・マトリックス回路はいくつかの信号線（例えば選択線113、電力線111、データ線112）を含んでいる。各光発生素子（例えば光発生素子210a）は、いくつかの素子を含んでいる。それは、有機発光ダイオード150や、アクティブ・マトリックス素子（例えば選択用トランジスタ120、記憶用キャパシタ130、

40

50

駆動用トランジスタ140)などである。共通上部電極160がすべての有機発光ダイオードに取り付けられて回路が完成する。

#### 【0019】

アクティブ・マトリックス駆動回路は、従来技術でよく知られているようにして動作する。各光発生素子行は、その行に付随する選択線(例えば選択線113)に電圧信号を印加することによって選択される。すると、その行の各光発生素子に付隨する選択用トランジスタ(例えば選択用トランジスタ120)がオンになる。各光発生素子の明るさのレベルまたはグレー・スケールの情報は、データ線(例えばデータ線112)上に設定される電圧信号によって制御される。その後、各光発生素子の記憶用キャパシタ(例えば記憶用キャパシタ130)が、その画素に付隨するデータ線の電圧レベルまで充電され、次の画像フレームの間にその行が再び選択されるまでデータ電圧を維持する。記憶用キャパシタ130は、駆動用トランジスタ140のゲート端子に接続される。<sup>10</sup> 駆動用トランジスタ140は、記憶用キャパシタ130によってそのトランジスタのゲート端子に保持されている電圧に応答し、電力線111からそのトランジスタのソース端子とドレイン端子を通って有機発光ダイオード150へと流れる電流を調節することで、画素の明るさを調節する。有機発光ダイオードには第1の電圧源に接続された電力線111から駆動用トランジスタ140を通って電流が供給され、第2の電圧源に接続された共通上部電極160へと出していく。次に、選択線に電圧信号を印加することによって各行が非選択状態になる。すると選択用トランジスタがオフになる。<sup>20</sup> 次に、データ線の信号値が次の行にとって望ましいレベルに設定され、次の行の選択線がオンになる。これがすべての画素行について繰り返される。その間、記憶用キャパシタ130は駆動用トランジスタ140のゲート上にデータ信号を維持しているため、有機発光ダイオード150は光を出し続けるのに対し、他の行はデータを受信している。

#### 【0020】

2つのトランジスタと1つのキャパシタ(2T1C)からなるこの回路構成は従来技術で一般に利用されており、本発明を実施するのに利用できる。異なる別のタイプの回路構成も従来技術で多く知られている。本発明は、こうした別のタイプの回路構成を利用して実施することもできる。そのような別の構成として、例えばアメリカ合衆国特許第6,091,203号、第6,501,466号、第6,535,185号、第6,774,877号に示されている電流ミラー・タイプの回路のほか、アメリカ合衆国特許第6,229,506号に示されている画素回路やアメリカ合衆国特許出願公開2004/0222746 A1に記載されている画素回路が挙げられる。<sup>30</sup> 図4Aの回路に示してあるのは、カソードが共通電極に接続され、アノードが駆動用トランジスタに接続されるという特別なバイアスの構成にされた有機発光ダイオードである。有機発光ダイオードが逆の極性を持つ他の回路構成も利用できる。また、キャパシタは電力線に接続された状態が示してあるが、独立したキャパシタ信号線を有する他の回路構成も利用できる。

#### 【0021】

ここで図5Aを参照すると、本発明の第1の実施態様によるOLEDディスプレイ装置が示してある。このOLEDディスプレイ装置は、欠陥のある光発生素子210xを含む光発生素子アレイ52を有する。この場合には、有機発光ダイオード150xのアノードとカソードを接続する短絡回路という欠陥170が存在する。短絡回路という欠陥170は、約100k ~ ほぼ0 の範囲の抵抗値を持つ抵抗器として表わす。短絡回路というこの欠陥170は、例えば有機発光ダイオード150xに含まれる有機エレクトロルミネッセンス媒体の引っ掻き傷の粒子欠陥によって起こる可能性がある。短絡回路という欠陥170は、本発明を適用できる可能性のある欠陥の一例である。<sup>40</sup> 本発明は、他のタイプの欠陥(例えば欠陥のあるトランジスタ、トランジスタにおける開放と短絡、トランジスタを接続するワイヤに欠陥)にも適用することができる。欠陥のあるトランジスタには、製造プロセスの問題や変動が原因で閾値電圧や移動度といった特性が異常になったトランジスタが含まれる。

#### 【0022】

図5Bは、本発明の第1の実施態様によるカラー・フィルタ素子アレイ62を示しており、これは図5Aに示した光発生素子アレイに対応している。カラー・フィルタ素子アレイは、赤色(R)、緑色(G)、青色(B)のカラー・フィルタ素子(それぞれ図示したカラー・<sup>50</sup>

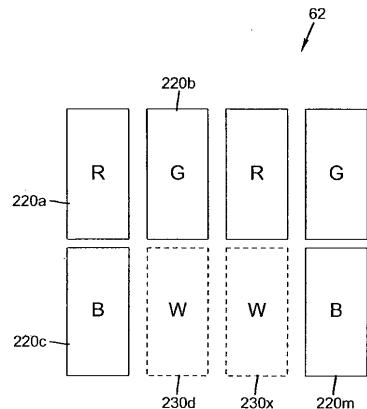

フィルタ素子220a、220b、220c)からなるデフォルト・パターンを含んでいる。フィルタなしのスペース230dが設けられて白色(W)画素にされている。このデフォルト・パターンは、図4Bに示した従来のデバイスと同じである。しかしこのカラー・フィルタ素子のパターンは、欠陥のある光発生素子210xの存在を補償するため本発明に従って調節されている。この場合、欠陥のある光発生素子210xは、デフォルト・パターンによれば本来なら青色画素となるはずのものである。欠陥のある光発生素子210xの存在を補償するため、青色(B)であるカラー・フィルタ素子220mの位置が調節されて光発生素子210mに対応するようにされている。この場合、フィルタなしのスペース230xの位置も調節されて光発生素子210xに対応するようにされている。その結果得られるOLEDディスプレイ装置は、欠陥のある光発生素子210xは利用せずに光発生素子210e、210f、210mを利用して赤色、緑色、青色の光でフル・カラー画像を生成させるようにプログラムされる(これについてはあとでより詳しく説明する)。したがって欠陥のある光発生素子210xの効果が小さくなるため、優れた画像品質が実現される。

#### 【0023】

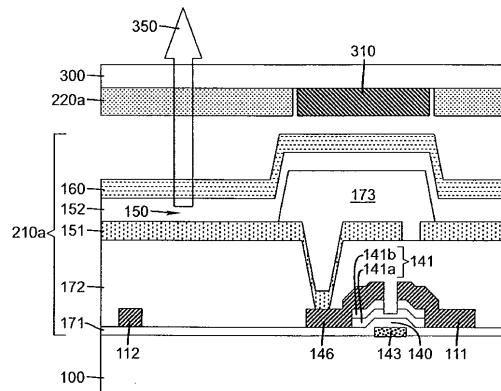

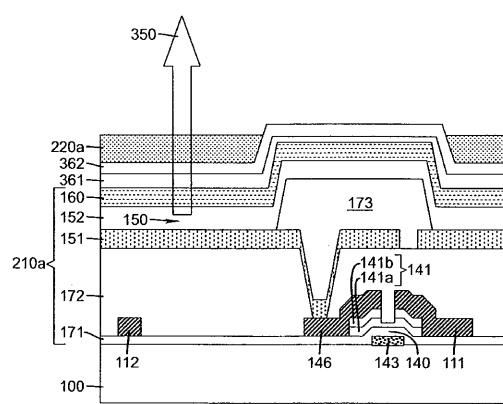

図6は、本発明の第1の実施態様による組み立てられたOLEDディスプレイ装置の断面図である。図6では光発生素子210aの構成を見ることができる。光発生素子は、第1の基板100上に形成される。第1の基板100は、従来技術で一般に使用されている既知のさまざまなタイプの基板から選択することができ、例えばガラス、プラスチック、金属ホイル、シリコン・ウエハなどが挙げられる。駆動用トランジスタ140の構成を見ることができ、半導体層141、ゲート端子143、端子146が含まれていることがわかる。端子146は駆動用トランジスタ140のソース端子またはドレイン端子として機能する。電力線111はこのトランジスタの第3の端子として機能する。半導体層141は、ドープされていないサブ層141aとドープされたサブ層141bを有するアモルファス・シリコンからなることが示されている。当業者であれば、従来技術で知られている他の半導体材料(例えばポリシリコン)も本発明に適用することができよう。駆動用トランジスタ140は底部にゲートがある構成を示してあるが、当業者であれば、他の公知の構成(従来技術で知られている例えば頂部のゲートや二重ゲートの構成)を本発明に適用することができよう。これら薄膜トランジスタの形成法は従来技術でよく知られており、一般的な堆積法、パターニング法、エッチング法が利用される。

#### 【0024】

ゲート絶縁層171と層間絶縁層172は、さまざまな信号線の間が電気的に絶縁されるように形成される。絶縁層にとって好ましい材料は窒化ケイ素である。下部電極151が設けられていて、駆動用トランジスタ140に電気的に接続されている。下部電極151は有機発光ダイオード150のための第1の電極として機能する。共通上部電極160は有機発光ダイオード150のための第2の電極として機能する。下部電極151は反射性にすることができ、アルミニウム、銀、モリブデンなどの材料を約100~400nmの厚さで含むことができる。下部電極151は、いくつかのサブ層で構成することもできる。その場合、上記の反射性材料を含む1つのサブ層と、透明な材料(例えばインジウム・スズ酸化物(ITO)、インジウム亜鉛酸化物(OZO)など)からなるサブ層とで構成する。これらの材料は従来技術で知られているいくつかの方法(例えばスパッタリング)で堆積させることができ、公知のリソグラフィ法やエッチング法によるパターニングが可能である。下部電極151の有用な構造のいくつかの例が、アメリカ合衆国特許第6,737,800号に提示されている。下部電極151の上方のスペースでは、例えばアメリカ合衆国特許第6,246,179号に記載されている画素間絶縁層173を用いて下部電極151の縁部を覆い、この領域の短絡または強い電場を防止することが好ましい。画素間絶縁層173を用いることが好ましいが、本発明をうまく実現するのに必要というわけではない。

#### 【0025】

有機エレクトロルミネッセンス媒体152が下部電極151と共に上部電極160の間に形成されている。有機エレクトロルミネッセンス媒体152は単一の層として図示してあるが、当業者であれば、この層は一般に複数のサブ層(例えば正孔注入サブ層、正孔輸送サブ層、

10

20

30

40

50

発光サブ層、電子輸送サブ層)からなることが理解できよう。本発明をうまく実施できる有機エレクトロルミネッセンス媒体152の構成は多数ある。有機エレクトロルミネッセンス媒体152では、色の異なるすべての画素が利用するさまざまな波長のすべてで光を出す共通の1つの広帯域(または白色)光源を用いることで、光発生素子に挟まれた有機エレクトロルミネッセンス媒体をパターニングせずに済むようにすることが好ましい。カラー画素は、カラー・フィルタ素子を光発生素子と揃えることによって実現される。白色光または広帯域光を出す画素は、光発生素子(例えば光発生素子210d)をフィルタなしのスペース(例えばフィルタなしのスペース230d)と組み合わせることによって形成される。広帯域光または白色光を出す有機EL媒体層のいくつかの例が、例えばアメリカ合衆国特許第6,696,177号に記載されている。しかし本発明は、それぞれの画素が、各画素のために別々にパターニングされた1つ以上の有機エレクトロルミネッセンス媒体サブ層を有する場合にもうまく実施することができる。有機エレクトロルミネッセンス媒体152をより少ないサブ層またはより多いサブ層を有する別の構成にしても本発明をうまく実施することができる。従来技術で知られているように、有機エレクトロルミネッセンス媒体152は、有機材料として小分子材料またはポリマー材料を含んでいる。これら有機エレクトロルミネッセンス媒体層は、従来技術で知られているいくつかの方法(例えば真空チャンバーの中での蒸着、ドナー基板からのレーザー転写、スピンドルコーティングまたはインクジェット印刷装置を用いた溶媒からの堆積)で堆積させることができる。有機エレクトロルミネッセンス媒体152は、約50~400nmの範囲の厚さであることが好ましい。有機エレクトロルミネッセンス媒体152は、電気的に刺激されると光350を発生させる。

10

20

#### 【0026】

上部電極160は、有機エレクトロルミネッセンス媒体152の上に形成される。上部電極160は、透明または半透明である。上部電極160にとって有用な材料として、半透明な薄い金属層(例えば25nm未満の厚さに堆積させることが好ましいアルミニウムまたは銀)や、透明な材料(例えばインジウム・スズ酸化物(ITO))などがある。

#### 【0027】

この実施態様では、図6からわかるように、カラー・フィルタ素子220aが第2の基板300の表面に形成されている。第2の基板300は非常に透明であることが好ましく、既知の材料(例えばガラスや透明なプラスチック)で構成される。カラー・フィルタ素子として使用するための多彩な着色材料が従来技術で知られている。カラー・フィルタ素子を形成する一般的な1つの方法は、基板の上に染料または顔料の溶液をコーティングし、フォトリソグラフィー法を利用してその溶液をパターニングするというものである。本発明を実施するのにこのフォトリソグラフィー法を利用できるが、より好ましい方法として、加熱素子またはレーザー素子を用いてカラー・フィルタ材料をドナー・シートから転写する方法がある。ドナー・シートからカラー・フィルタ素子を転写するための方法と材料の例は、アメリカ合衆国特許第4,965,242号と第5,521,035号に見いだすことができる。好ましい別の方針として、インクジェット印刷装置を用いて溶液からカラー・フィルタ素子を堆積させる方法がある。インクジェット法によってカラー・フィルタ素子を堆積させるための方法と材料の例は、アメリカ合衆国特許第6,743,556号に見いだすことができる。これらの方法は、印刷またはイメージングのパターンを決定する前に電子的に調節してカラー・フィルタ素子の位置を容易に変えられるため特に好ましい(これについてはあとで詳しく説明する)。それに対してフォトリソグラフィーによるパターニングでは、一般に、新しいパターンを形成するのにフォトマスクを製造する必要があるため、複数のマスクを製造すると製造コストが増大する。あるいはフォトマスクを1つ作って単一の画素だけのイメージングまたは少数の画素のイメージングを行なった後、基板全体にわたって移動させる(繰り返す)こともできるであろうが、このようにすると処理時間がかなりかかるため製造のスループットが低下するであろう。したがってより好ましい堆積法は、パターンを電子的に調節した後に各デバイスを処理できる、上に説明したインクジェット印刷法や熱転写法などの“マスクなし”法である。

30

40

#### 【0028】

50

ブラック・マトリックス310が基板100の上方でカラー・フィルタ素子の間に形成されている。ブラック・マトリックス310は、画素の発光領域の間に形成された不透明で吸収性的膜であり、望ましくない反射光を吸収することで画像のコントラストを改善する。ブラック・マトリックス310は、カラー・フィルタ素子のパターニングまたは整列を助けることもできる。ブラック・マトリックス310は、例えばカラー・フィルタ素子を作るのに用いられるインクジェット用液滴の収容機能を持つことができる。あるいは従来技術で知られている追加の壁層を用いてこの機能を実現することもできよう。ブラック・マトリックスは利用しなくてもよいが、使用するほうが好ましい。しかし本発明をうまく実施する上でブラック・マトリックスは必須ではない。

#### 【0029】

10

ここで図1、図2、図3に移り、図5A、図5B、図6に示したOLEDディスプレイ装置も参照し、本発明によるOLEDディスプレイ装置の製造法をこれから説明する。最初の図1は、本発明のディスプレイ装置を製造するための製造プロセス10のブロック・ダイヤグラムである。製造プロセス10は、ディスプレイ・ユニットの製造から始まる（製造プロセス20）。ディスプレイ・ユニットは、カラー・フィルタ素子アレイとカップルした光発生素子アレイを含んでいる。ディスプレイ・ユニットの製造プロセス（製造プロセス20）は、図2にブロック・ダイヤグラムとして詳しく示してある。

#### 【0030】

図2からわかるように、ディスプレイ・ユニットの製造プロセス（製造プロセス20）は、第1の基板100を用意することから始まる（ステップ500）。第1の基板100は、従来技術で一般に使用されているさまざまなタイプの基板の中から選択することができ、例としてガラス、プラスチック、金属ホイル、シリコン・ウエハなどがある。次に、ステップ510において、アクティブ・マトリックス回路と光発生素子アレイを基板100の上に形成する。ステップ510の詳細については図3で詳しく説明する。

20

#### 【0031】

すなわち図3からわかるように、ステップ511において第1のアクティブ・マトリックス回路を第1の基板100の上に形成する。アクティブ・マトリックス回路の製造法は従来技術でよく知られている。アクティブ・マトリックス回路は、公知のさまざまなタイプのもの（例えばアモルファス・シリコン・タイプ、ポリシリコン・タイプ）の中から選択でき、すでに説明したようにさまざまな構成の回路にすることができる。次に、ステップ512において下部電極151を形成する。すでに説明したように、下部電極151は反射性にすることができる、アルミニウム、銀、モリブデンなどの材料を約100～400nmの厚さで含むことができる。下部電極151はいくつかのサブ層からなる構成にすることもできる。その場合、上記の反射性材料を含む1つのサブ層と、透明な材料（例えばインジウム・スズ酸化物（ITO）、インジウム亜鉛酸化物（IZO）など）からなるサブ層とで構成する。下部電極151は、従来技術で知られている方法（例えばスパッタリング）によって基板とアクティブ・マトリックス回路の上方にある層として堆積される。次に、よく知られたフォトフォトリソグラフィー法、湿式エッチング法、プラズマ・エッチング法のいずれかを利用して下部電極151をパターニングする。下部電極151を形成した後、すでに説明したように、場合によっては画素間絶縁層173を設けることができる。次に、ステップ513において第1の基板100を制御された環境下に置く。制御された環境は、不活性な周囲ガス（窒素、アルゴンなど）を含む環境、または減圧された（真空）環境（例えば133Pa未満であり、0.133Pa未満であることが好ましく、0.133mPa未満であることがより好ましい）である。制御された環境は、ドライ・ボックス、または真空チャンバー、または互いに直接に接続されるか移送容器によって接続された複数のドライ・ボックスおよび／または真空チャンバーにすることができる。好ましい制御された環境は、密封された真空容器クラスター・システム、または直列の真空容器システムである。この制御された環境は、水分や酸素の存在下で分解することが知られている有機エレクトロルミネッセンス媒体材料を堆積させるのに役立つ。制御された環境下で、ステップ514において下部電極151の上に有機エレクトロルミネッセンス媒体152を形成する。すでに説明したように、有機エレクトロルミネッセンス媒体152は

30

40

50

、従来技術で知られている異なる複数の有機材料を含む複数のサブ層で構成することが好ましい。これら有機エレクトロルミネッセンス媒体材料を堆積させる好ましい1つの方法は、材料を収容した複数の供給源（例えばグラファイト製ポート）を加熱してその材料を蒸発させたり昇華させたりし、下部電極151と第1の基板100の上に凝集させる方法である。有機エレクトロルミネッセンス媒体材料は、光発生素子の上だけに形成されて外部との電気的接続のために使用できる基板100の周辺領域には形成されないようにするため、シャドウ・マスクを通じて堆積させることが好ましい。有機エレクトロルミネッセンス媒体材料を堆積させる別の方法として、ドナー基板からのレーザー転写や、スピノ・コーティングまたはインクジェット印刷装置を用いた溶媒からの堆積がある。次に、ステップ515において上部電極160を形成する。上部電極160は、すでに説明したように透明または半透明であることが好ましい。半透明な上部電極は、公知の方法（例えば蒸着やスパッタリング）によって金属（例えばアルミニウムや銀）からなる薄い層（25nm以下）を堆積させることによって形成できる。透明な上部電極は、公知の方法（例えばスパッタリング）によって非常に透明な導電性材料（例えばインジウム・スズ酸化物（ITO））を好ましくは約50~400nmの厚さに堆積させることによって形成できる。上部電極の材料は、光発生素子の上だけに形成されて基板100の周辺領域には形成されないようにするため、シャドウ・マスクを通じて堆積させることが好ましい。なぜなら周辺領域は外部との電気的接続に使用されるからである。

### 【0032】

図2に戻ると、製造プロセス20では、ディスプレイ・ユニットを形成するためにアクティブ・マトリックス回路と光発生素子アレイを形成した（ステップ510）後のステップは、光発生素子アレイをテストするステップ（ステップ520）である。好ましい1つのタイプのテスト法は、光発生素子アレイの発光を感知する操作を含んでいる。この方法は、電力を例えばアクティブ・マトリックス回路を通じて光発生素子に印加する操作を含んでいる。光発生素子を個別に光らせること、またはすべての光発生素子を同時に光らせることができる。光検出器、フォト・ダイオード、放射計、CCDカメラ・アレイなどを用いて光発生素子の光出力を検知することができる。テストしている間、光発生素子を单一の輝度強度で光らせること、または最終的なOLEDディスプレイ装置に必要な望む範囲の強度に対応するある範囲の輝度強度で光らせることができる。すでに説明したように有機エレクトロルミネッセンス媒体材料は水分と酸素に敏感であるため、ステップ520は制御された環境の中で実施し、有機エレクトロルミネッセンス媒体と上部電極を形成して（ステップ512と513）からテストする（ステップ520）までの間に光発生素子アレイが実質的に酸素または水分に曝露されないようにすることができる。あるいはテスト（ステップ520）の前に薄膜封止層形成ステップ（図示せず）を実施し、光発生素子アレイを環境中の酸素または水分から保護することもできる。このような薄膜封止層は従来技術で知られており、例えばアメリカ合衆国特許出願公開2001/0052752 A1と2002/0003403 A1に記載されているように、原子層堆積（ALD）法によって堆積させたアルミニウム酸化物層の後にパリーレン層を堆積させた構造がある。薄膜封止層が存在しているこの場合には、光発生素子アレイをテストのために真空環境から取り出しても安全であるため、電力の供給と光出力の測定に用いる装置の少なくとも一部を制御された環境の中に入れたり制御された環境に接続したりする必要はない。そのためそのテスト装置を単純化できる。

### 【0033】

テスト・プロセス（ステップ520）の間に光発生素子を調べ、欠陥のある光発生素子が存在しているかどうかを明らかにする。欠陥のある光発生素子として、異常な明るさになる光発生素子（例えば暗かったり過剰に明るかったりする光発生素子）を挙げができる。欠陥のあるそのような光発生素子が最終的なOLEDディスプレイ装置の画素で用いられるるとすると、それぞれ、欠陥のある暗い画素または欠陥のある明るい画素になるであろう。欠陥のある光発生素子として、電気的に刺激したときに光を発生させることのできない光発生素子も挙げられる。欠陥のあるそのような光発生素子が最終的なOLEDディスプレイ装置の画素で用いられるとすると、欠陥のある死んだ画素になるであろう。欠陥のある

光発生素子として、電力を供給したとき、特にアドレスされていないのに光を出す光発生素子も挙げられる。欠陥のあるそのような光発生素子が最終的なOLEDディスプレイ装置の画素で用いられるとすると、スタック-オン画素という欠陥になるであろう。欠陥のある光発生素子として、望む発光スペクトルとは異なる発光スペクトルを持つ光発生素子も挙げられる。欠陥のあるそのような光発生素子が最終的なOLEDディスプレイ装置の画素で用いられるとすると、その画素は正しくない色を発生させることになろう。光発生素子の他のタイプの欠陥もテスト・プロセス(ステップ520)の間に調べることができる。

#### 【0034】

場合によっては、欠陥のあるいくつかの光発生素子を変化させて欠陥の性質を変えることができる。例えばスタック-オン画素という欠陥は、欠陥のある光発生素子が特にアドレスされていないのに光を発生させる場合に見られることになろう。欠陥のあるそのような光発生素子は、信号を伝える電気的接続線をレーザーで切断するなどの方法により、光を出さない光発生素子に変換することができる。例えば駆動用トランジスタを電源線に接続している電気配線、または駆動用トランジスタを下部電極に接続している電気配線を切断するのにレーザーを用いることができる。

10

#### 【0035】

光発生素子アレイのテスト(ステップ520)の後、欠陥のある光発生素子が存在しているかどうか、または許容できない品質のディスプレイになるほど大量に存在しているかどうかを判断せねばならない(判断ブロック530)。欠陥のある光発生素子が見つからない場合、または許容できるくらいわずかな数しか存在していない場合には、デフォルトのカラー・フィルタ素子アレイ・パターンを利用することができます(ステップ540)。デフォルトのカラー・フィルタ素子アレイ・パターンは、図4Bに示してあるように、異なる色のカラー・フィルタ素子が1つの規則的な繰り返しパターンの配置にされたパターンである。あるいはデフォルトのカラー・フィルタ素子アレイ・パターンは、異なる色のカラー・フィルタ素子があらかじめ決めたランダムな配置にされたものにすることができる。例えば異なる4色の画素(R、G、B、W)からなるあらゆるグループをランダムに選択することができる。ランダムなパターンが本発明にとって有利であるため、以下に説明するように、カラー・フィルタ素子の位置が調節されるのであれば、ディスプレイ装置を見る人は、1つの画素パターンの中での変化を目で検出することはできないであろう。この実施態様では、第2の基板を用意し(ステップ570)、選択したパターン(ここではデフォルトのフィルタ・パターン)でカラー・フィルタ素子をその第2の基板上に製造する(ステップ580)ことによってカラー・フィルタ素子アレイ・パターンを実現する。

20

#### 【0036】

判断ブロック530において欠陥のある1つ以上の光発生素子が存在すると判断された場合には、欠陥のあるその光発生素子の位置を記録する(ステップ550)。位置情報は、光発生素子アレイ中のその光発生素子の位置からなる。この位置情報は、例えば光発生素子の行と列の番号を含むことができる。あるいは位置情報は、光発生素子を間違なく特定する単一の数(例えば第1行と第1列の第1の光発生素子から数えた番号)を含むことができる。他の位置特定システム(例えば光発生素子アレイまたは基板の縁部に対するその光発生素子の位置の物理的測定値)も利用できる。位置情報は、例えばコンピュータまたはコンピュータ・ネットワークにその情報を記憶させることによって記録される(電子的に記録されることが好ましい)。位置情報は、第1の基板または光発生素子アレイの同定に関する情報(例えば“プレート番号”またはシリアル番号)とも組み合わされる。この基板同定情報によって多数の装置を同時に製造することが容易になり、ディスプレイ装置の全製造プロセスが完了する前に基板が移動したり保管されたりした場合でさえ、その位置情報をあとから基板に付隨させることができる。

30

#### 【0037】

ステップ560では、ステップ550において記録された位置情報をを利用してデフォルトのカラー・フィルタ・パターンを調節する。例えば図5Aと図5Bに示してあるように、欠陥のある光発生素子210xは、ステップ520で光発生素子アレイ52をテストしている間に欠陥のあ

40

50

ることが突き止められることになる。デフォルトのカラー・フィルタ・パターン（例えば図4Bの従来のパターン）によれば、欠陥のある光発生素子210xは、欠陥がなかったとすれば青色カラー・フィルタとカップルされたであろう。しかし欠陥のある光発生素子210xは欠陥を持つため、このカップリングがなされたとすると、欠陥のある光発生素子210xの位置の近傍では青色の光を発生させることができないディスプレイ装置になったであろう。そこで本発明により、青色であるカラー・フィルタ素子220mの位置を変え、白色画素の形成に使用されたはずの光発生素子210mの上に位置させる。この場合、フィルタなしのスペース230xの位置も同様に変えて欠陥のある光発生素子210xの上に来るようする。カラー・フィルタ素子220mと光発生素子210xの位置を変えることにより、調節されたカラー・フィルタ・パターンが作り出される。この実施態様では、第2の基板を用意し（ステップ570）、選択したパターン（この場合には調節されたパターン）に従って第2の基板の上にカラー・フィルタ素子を作ることによってカラー・フィルタ・アレイのパターンが実現する。

10

### 【0038】

本発明の第1の実施態様によれば、カラー・フィルタ素子とフィルタなしのスペースの位置を変化させ、欠陥のある光発生素子をフィルタなしのスペースとカップルさせることができが好ましい。その結果、ディスプレイ上の欠陥のある光発生素子の周囲の領域には機能する白色画素が欠如することになる。しかし赤色画素、緑色画素、青色画素が機能するため、得られるディスプレイ装置はそれでもフル・カラー画像を再現することができる。白色とグレー・スケールは、やはり機能する赤色画素、緑色画素、青色画素を組み合わせて生成させることができる。もし欠陥のある光発生素子が、フィルタなしのスペースとカップルしてデフォルト・パターンに従う白色画素を形成したであろう位置に存在しているならば、その位置は調節せず、フィルタなしのスペースとカップルしたままにすることが好ましい。この単純な論理アルゴリズムを図7に示してある。すなわち欠陥のある光発生素子に付随する画素の色がデフォルト・パターンに従うと何色であるかを最初に判断する（判断ブロック700）。デフォルトのカラー画素が白色であるならば、カラー・フィルタ素子アレイのパターンを調節しない（ステップ720）。デフォルトのカラー画素が赤色、緑色、青色のいずれかである場合には、白色画素とあらかじめ決めたカラー画素の位置を切り換えることによってカラー・フィルタ素子アレイのパターン変化させる（ステップ710）。欠陥のある互いに近接した複数の光発生素子を補償するため、対応するデフォルトのカラー・フィルタ素子が代わりの機能する光発生素子の上に来るよう調節するというより複雑な論理アルゴリズムを実現することもできる。欠陥のある画素が白色以外の色となるように選択する別の論理アルゴリズムも実現可能であり、本発明の範囲に含まれる。例えば本発明は、赤色画素（R）、緑色画素（G）、青色画素（B）だけを有するディスプレイ装置に適用でき、その場合には、欠陥のある複数の画素が異なる色の間に均等に分布するようにカラー・フィルタ素子の位置が調節される。すなわちディスプレイは、この別の論理アルゴリズムを利用し、欠陥のある3つの青色画素に対してカラー・フィルタ素子の位置が調節されるのではなく、欠陥のある1つの赤色画素と、欠陥のある1つの青色画素と、欠陥のある1つの緑色画素を持つようにされる。

20

30

### 【0039】

図2に戻ると、上に説明したように、デフォルトのフィルタ・パターン（ステップ540）または調節されたフィルタ・パターン（ステップ560）のいずれかに決まったパターンに従い、カラー・フィルタ素子アレイを第2の基板の上に製造する（ステップ580）。いくつかの方法を利用してカラー・フィルタ素子アレイを製造することができる。カラー・フィルタ素子アレイを製造する好ましい方法は、パターンを電子的に調節できる方法である。例えば1つのインクジェット・ノズルからの堆積またはインクジェット・ノズル・アレイからの堆積や、サーマル・ヘッド（レーザー・ヘッドなど）によるドナー・シートからのカラー・フィルタ材料の転写などの方法がある。インクジェット法によってカラー・フィルタ素子を堆積させるための方法と材料の例は、アメリカ合衆国特許第6,743,556号に見いだすことができる。ドナー・シートからカラー・フィルタ素子を転写するための方法と

40

50

材料の例は、アメリカ合衆国特許第4,965,242号と第5,521,035号に見いだすことができる。

#### 【0040】

カラー・フィルタ素子アレイを形成した後、第1の基板と第2の基板を正確に揃え（ステップ590）、カラー・フィルタ素子が光発生素子の上に重なるようにする。完全に揃うこととはありえないため、カラー・フィルタ素子を光発生素子よりもわずかに大きく作ることで、わずかな不揃いが許容されるようにする。次に、第2の基板を第1の基板に接合する（ステップ600）。これは、例えば水分と空気が非常に浸透しにくいことが好ましい接着剤を第1の基板と第2の基板の間に塗布し、その接着剤を例えば紫外線（UV）に曝露して硬化させることによって実現する。こうすることにより、密封された領域が形成される。場合によっては、従来技術で知られている追加の乾燥剤を密封された領域に収容し（図示していないステップ）、捕捉された水分や拡散した水分をさらに吸収することができる。第1の基板と第2の基板を1組だけ利用して複数のディスプレイ・ユニットを同時に製造することができる。その場合には、複数のディスプレイ・ユニットは、従来技術で知られている方法を利用して切断したり削ったりすることによって分離できる（図示していないステップ）。

10

#### 【0041】

製造プロセス20においてディスプレイ・ユニットが完成すると、OLEDディスプレイ装置を完成させるための製造プロセス10を続けることができる。図1に戻ると、ディスプレイ・ユニットの製造（製造プロセス20）後、メモリ・ユニットを設ける（ステップ800）。メモリ・ユニットは、従来技術で知られているさまざまなタイプのもの（例えばフラッシュ・メモリ、電気的プログラム可能な読み出し専用メモリ（EPROM）、磁気記憶装置（ハード・ドライブなど））の中から選択することができる。

20

#### 【0042】

次に、ステップ550で記録された欠陥のあるすべての光発生素子の位置をメモリ・ユニットに記憶させる（ステップ810）。メモリ・ユニットのサイズを小さくするため、欠陥のある光発生素子だけについて座標の簡単なセット（行番号と列番号）を記憶させる。次に、カラー・フィルタ素子の変更された位置をメモリ・ユニットに記憶させる（ステップ820）。ここでもメモリ・ユニットのサイズを小さくするため、位置が変化したカラー・フィルタ素子だけについて座標の簡単なセット（行番号と列番号）を記憶させる。

30

#### 【0043】

ディスプレイ・ユニットに表示する入力ビデオ信号を変換するための駆動ユニットを設ける（ステップ830）。この駆動ユニットは、特定用途向け集積回路（ASIC）などの回路を含んでいる。この駆動ユニットは、ビデオ信号の再現に必要な明るさのレベルをディスプレイ・ユニットの異なる画素について決定する。本発明によれば、この駆動ユニットは、欠陥のある光発生素子の位置と、メモリ・ユニットに記憶されたカラー・フィルタ素子の変更された位置にも応答する。すでに説明したように、駆動ユニットは、機能する白色画素がないとき、欠陥のある白色画素の領域において赤色画素と緑色画素と青色画素（位置が調節されたカラー・フィルタ素子を含むカラー画素も含む）を利用し、画像の望む色を再現することができる。別の一実施態様では、メモリ・ユニットに欠陥のある光発生素子の位置だけを記憶させ、駆動ユニットの中で、カラー・フィルタ素子の位置の調節を選択する論理アルゴリズムを提供して動作中に必要に応じてカラー・フィルタ素子アレイのパターンを生成させることにより、メモリ・ユニットを小さくすることができる。

40

#### 【0044】

最後に、駆動ユニットとメモリ・ユニットとディスプレイ・ユニットを接続する（ステップ840）。駆動ユニットとメモリ・ユニットは、回路板上の電気的接続線によって接続することができ、その回路板は、可撓性のあるケーブルによってディスプレイ・ユニットに接続される。あるいはメモリ・ユニットと駆動ユニットを場合によっては単一の集積回路の中に製造し、これらのユニットを集積回路の配線によって接続することができる。あるいは薄膜トランジスタを用いてメモリ・ユニットと駆動ユニットの一方または両方を第

50

1の基板上に直接製造し、ディスプレイ・ユニットへの直接的な接続を実現することができる。

#### 【0045】

ここで図8に移ると、本発明を実施するのに役立つ製造ツール400を示してある。製造ツール400は、制御された環境を維持するため中央チェンバー410のまわりに位置するいくつかのチェンバーを備えている。中央チェンバー410は、基板をチェンバー間で移動させるための移送口ボット420を備えている。装入チェンバー401を用いて基板を制御された環境に入れる（ステップ513）。減圧状態の制御された環境にするため、装入チェンバー401は真空ポンプを備えている。装入チェンバー401は複数の基板を収容可能にできるため、複数のデバイスを並列して製造することができる。次に、第1の基板を移送口ボット420によって有機蒸着チェンバー402、403、404、405、406に移動させ、有機エレクトロルミネッセンス媒体の複数の有機サブ層を堆積させる（ステップ514）。それぞれの有機蒸着チェンバーは、有機材料を蒸発させて第1の基板に堆積させるための1つ以上の蒸発源（またはポート）を収容することができる。有機サブ層は、各有機蒸着チェンバーの中に入れたシャドウ・マスクを通じて基板上の選択した領域に堆積させることができる。次に、第1の基板を移送口ボット420によって電極蒸着チェンバー407に移動させ、上部電極515を堆積させる（ステップ515）。電極蒸着チェンバー407は、透明な上部電極材料を堆積させるための1つ以上の蒸発源またはスパッタ・ターゲットを含むことができる。次に、第1の基板を移送口ボット420によってテスト・チェンバー430に移動させる。

#### 【0046】

ここで図9に移ると、テスト・チェンバー430の構成の一例をより詳しく示してある。テスト・チェンバー430は、第1の基板100に電力を供給するとともに光発生素子（例えば光発生素子210a、210b）を光らせるための電気的プローブ431を備えている。テスト・チェンバー430は、光発生素子からの発光を検出する光検出器432も備えている。光検出器432は、制御された環境433の外部に位置する状態が図示されており、ウインドウ434を通して光を検出する。しかし光検出器は制御された環境の中に置くこともできる。光検出器は、コンピュータ435に接続されている。コンピュータ435は、どれかの光発生素子に欠陥があると判断した場合にその光発生素子の位置情報を例えばコンピュータ・ネットワーク上に記憶する。

#### 【0047】

図8に戻ると、第2の基板を装入チェンバー450に入れる。次に、第2の基板はカラー・フィルタ・チェンバー460に移されてカラー・フィルタ素子アレイが形成される。第2の基板も制御された環境（例えば窒素またはアルゴン）に維持される。装入チェンバー450の中を制御された環境にすることが好ましいが、最初にカラー・フィルタ・チェンバー460を制御された環境にすることもできる。あるいは環境を変化させるため、別の装入口ック・チェンバーを整列・接合チェンバー440の前に設置することができる。すでに説明したように、カラー・フィルタ素子アレイを形成するのにいくつかの方法（例えばインクジェット堆積、レーザーを用いた熱転写）を利用できる。インクジェット堆積システムのためのカラー・フィルタ・チェンバー460の一例を図10に示してある。

#### 【0048】

図10からわかるように、赤色インクジェット・ヘッド462Rと、緑色インクジェット・ヘッド462Gと、青色インクジェット・ヘッド462Bとを有するインクジェット装置が配置されてカラー・フィルタ素子（例えばカラー・フィルタ素子220a、220b、220c）のアレイが第2の基板300上に形成される。あるいは単一のインクジェット・ヘッドを用い、異なる色の複数のフィルタ材料が同じヘッドまたは同じノズルに供給されるようにすることもできよう。インクジェット装置は、例えばコンピュータ・ネットワークに接続されたコンピュータ465によって制御される。コンピュータ465は、テスト・チェンバー430において記録された欠陥のある光発生素子に関する位置情報を受け取る。次に、コンピュータ465は、カラー・フィルタ（例えばカラー・フィルタ素子220a、220b、220c）の位置を調節とともにフィルタなしのスペース（例えばフィルタなしのスペース230d）も調節することによ

り、カラー・フィルタ素子アレイのパターンを変えることができる。

#### 【0049】

図8に戻ると、第1の基板を整列・接合チャンバー440の中に移動させる。整列・接合チャンバー440も制御された環境に維持される。この時点で不活性ガス（例えば乾燥窒素）を用い、制御された環境をほぼ大気圧に変化させる。次に第2の基板も整列・接合チャンバー440の中に移動させる。次に2つの基板を揃え、第1の基板上の光発生素子アレイが第2の基板上のカラー・フィルタ素子アレイと揃うようにする。これは、従来技術で知られているように、例えばCCD整列カメラを用いて実現することができる。次に第1の基板と第2の基板を、その周辺部に沿って両者の間に接着剤を塗布することにより接着させてシールを形成する。場合によっては、従来技術で知られているように、2つの基板の間の接着剤シールの中に乾燥剤を入れることができる。第2の基板上のカラー・フィルタ素子アレイを第1の基板上の光発生素子アレイに接着させることでディスプレイ・ユニットが形成される。次にこのディスプレイ・ユニットを取出チャンバー470に移動させて製造ツール400から外す。10

#### 【0050】

ここで図11に移ると、本発明の第2の実施態様によるOLEDディスプレイ装置の断面図を示してある。この実施態様では、カラー・フィルタ素子（例えばカラー・フィルタ素子220a）のアレイが、第1の基板100の上に形成された光発生素子（例えば光発生素子210a）の上方に直接形成されている。カラー・フィルタ素子を光発生素子の上方に形成するこの方法では第2の基板が不要であるため、材料のコストを低下させることができ、より薄い最終ディスプレイ・ユニットが得られ、製造装置が簡単になる。従来の実施態様と同様、ここでもカラー・フィルタ素子はインクジェット印刷などのマスクなし法で堆積させることができが嬉しい。従来の実施態様と同様、カラー・フィルタ素子の位置は、光発生素子アレイをテストすることによって明らかになった欠陥のある光発生素子に関して記録されている位置に応じ、マスクなし法を利用して調節される。20

#### 【0051】

この第2の実施態様では、保護層362を上部電極160とカラー・フィルタ素子（例えばカラー・フィルタ素子220a）の間に形成することが嬉しい。保護層362は、水分や溶媒が含まれている可能性のあるカラー・フィルタ素子を形成している間に、下にある有機エレクトロルミネッセンス媒体152または上部電極160が化学的に分解しないようにするのに役立つ。水分または空気を阻止して下にある有機エレクトロルミネッセンス媒体152または上部電極160が分解しないようにするために、薄膜封止層361も設けることが嬉しい。薄膜封止層361の嬉しい1つの構成は、原子層堆積（ALD）法などの方法によって上部電極160の上に堆積させたアルミニウム酸化物層であり、その後、アルミニウム酸化物層の上にパリーレン化合物からなる保護層362が形成される。このようなアルミニウム酸化物サブ層とパリーレン・サブ層の例が、アメリカ合衆国特許出願公開2001/0052752 A1と2002/0003403 A1に記載されている。薄膜封止層361と保護層362を用いることが嬉しいが、本発明のこの実施態様をうまく実施する上でこれらの層は必須でない。30

#### 【0052】

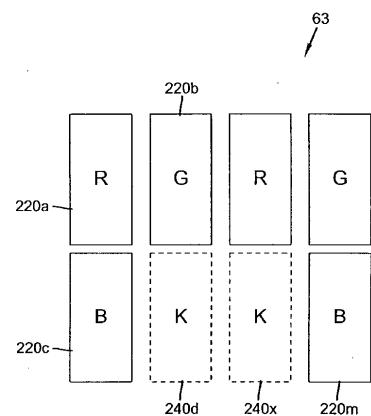

図12を参照してこれから本発明の第3の実施態様を説明する。この第3の実施態様が第1および第2の実施態様と異なるのは、カラー・フィルタ素子アレイの一部として、フィルタなしのスペースの代わりに光阻止素子（例えば光阻止素子240dと240x）が設けられている点である。すなわち図12からわかるように、複数のカラー・フィルタ素子（例えばカラー・フィルタ素子220a、220b、220c、220m）を有するカラー・フィルタ素子アレイ63が設けられている。このカラー・フィルタ素子アレイ63は、すでに説明して図5Aに示してある第1の実施態様の光発生素子アレイ52とカップルさせることができる。40

#### 【0053】

カラー・フィルタ素子アレイ63は、赤色（R）、緑色（G）、青色（B）のカラー・フィルタ素子からなるパターンを含んでいる。このパターンは、光阻止素子（例えば黒色（K）の光阻止素子240d）も含んでいる。これらの光阻止素子は可視光の波長全域で吸収性が50

大きく、カーボン・ブラックや、可視光の波長全域で光を吸収する他の染料、顔料、染料混合物、顔料混合物で構成することができる。このパターンを光発生素子アレイとカップルさせると、赤色画素、緑色画素、青色画素を有するディスプレイ、すなわちRGBタイプのディスプレイになる。この場合、画像を生成させるのに4つの光発生素子につき1つの光発生素子が使用されない。使用されない光発生素子は、光阻止素子が存在しているために黒に（または暗く）見える。

## 【0054】

カラー・フィルタ素子アレイのデフォルト・パターンは、欠陥のある光発生素子が検出されると変更される。この場合、光阻止素子（例えば光阻止素子240x）の位置が変更され、欠陥のある光発生素子の上に来るようになる。欠陥のある光発生素子に付随するはずのカラー・フィルタ素子（例えばカラー・フィルタ素子220m）の位置が変更され、欠陥のない光発生素子の上に来るようになる。このようになっているため、欠陥のある光発生素子が存在しているにもかかわらず、機能するRGB画素の完全なセットを有するディスプレイ装置を形成することができる。光阻止素子を有する本発明のこの第3の実施態様は、光発生素子アレイが（第1の実施態様のように）第2の基板の上に形成されている場合や、（第2の実施態様のように）第1の基板上の光発生素子の上に直接形成されている場合に実施することができる。

## 【符号の説明】

## 【0055】

|      |                  |    |

|------|------------------|----|

| 10   | 製造プロセス           | 20 |

| 20   | 製造プロセス           |    |

| 51   | 光発生素子アレイ         |    |

| 52   | 光発生素子アレイ         |    |

| 61   | カラー・フィルタ素子アレイ    |    |

| 62   | カラー・フィルタ素子アレイ    |    |

| 63   | カラー・フィルタ素子アレイ    |    |

| 100  | 第1の基板            |    |

| 111  | 電力線              |    |

| 112  | データ線             |    |

| 113  | 選択線              | 30 |

| 120  | 選択用トランジスタ        |    |

| 130  | 記憶用キャパシタ         |    |

| 140  | 駆動用トランジスタ        |    |

| 141  | 半導体              |    |

| 141a | ドープされていないサブ層     |    |

| 141b | ドープされたサブ層        |    |

| 143  | ゲート端子            |    |

| 146  | 端子               |    |

| 150  | 有機発光ダイオード        | 40 |

| 150x | 有機発光ダイオード        |    |

| 151  | 下部電極             |    |

| 152  | 有機エレクトロルミネッセンス媒体 |    |

| 160  | 共通上部電極           |    |

| 170  | 短絡回路という欠陥        |    |

| 171  | 絶縁層              |    |

| 172  | 絶縁層              |    |

| 173  | 画素間絶縁層           |    |

| 210a | 光発生素子            |    |

| 210b | 光発生素子            |    |

| 210c | 光発生素子            | 50 |

|      |                |    |

|------|----------------|----|

| 210d | 光発生素子          |    |

| 210e | 光発生素子          |    |

| 210f | 光発生素子          |    |

| 210m | 光発生素子          |    |

| 210x | 光発生素子          |    |

| 220a | カラー・フィルタ素子     |    |

| 220b | カラー・フィルタ素子     |    |

| 220c | カラー・フィルタ素子     |    |

| 220m | カラー・フィルタ素子     |    |

| 230d | フィルタなしのスペース    | 10 |

| 230x | フィルタなしのスペース    |    |

| 240d | 光阻止素子          |    |

| 240x | 光阻止素子          |    |

| 300  | 第2の基板          |    |

| 310  | ブラック・マトリックス    |    |

| 350  | 発光             |    |

| 361  | 薄膜封止層          |    |

| 362  | 保護層            |    |

| 400  | 製造ツール          |    |

| 401  | 装入チェンバー        | 20 |

| 402  | 有機蒸着チェンバー      |    |

| 403  | 有機蒸着チェンバー      |    |

| 404  | 有機蒸着チェンバー      |    |

| 405  | 有機蒸着チェンバー      |    |

| 406  | 有機蒸着チェンバー      |    |

| 407  | 電極蒸着チェンバー      |    |

| 410  | 中央チェンバー        |    |

| 420  | 移送口ボット         |    |

| 430  | テスト・チェンバー      |    |

| 431  | 電気的プローブ        | 30 |

| 432  | 光検出器           |    |

| 433  | 制御された環境        |    |

| 434  | ウインドウ          |    |

| 435  | コンピュータ         |    |

| 440  | 整列・接合チェンバー     |    |

| 450  | 装入チェンバー        |    |

| 460  | カラー・フィルタ・チェンバー |    |

| 462B | 青色インクジェット・ヘッド  |    |

| 462G | 緑色インクジェット・ヘッド  |    |

| 462R | 赤色インクジェット・ヘッド  | 40 |

| 465  | コンピュータ         |    |

| 470  | 取出チェンバー        |    |

| 500  | ステップ           |    |

| 510  | ステップ           |    |

| 511  | ステップ           |    |

| 512  | ステップ           |    |

| 513  | ステップ           |    |

| 514  | ステップ           |    |

| 515  | ステップ           |    |

| 520  | ステップ           | 50 |

|     |        |    |

|-----|--------|----|

| 530 | 判断プロック |    |

| 540 | ステップ   |    |

| 550 | ステップ   |    |

| 560 | ステップ   |    |

| 570 | ステップ   |    |

| 580 | ステップ   |    |

| 590 | ステップ   |    |

| 600 | ステップ   |    |

| 700 | 判断プロック | 10 |

| 710 | ステップ   |    |

| 720 | ステップ   |    |

| 800 | ステップ   |    |

| 810 | ステップ   |    |

| 820 | ステップ   |    |

| 830 | ステップ   |    |

| 840 | ステップ   |    |

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

【図4A】

FIG. 4A

従来技術

【図4B】

FIG. 4B

従来技術

【図5A】

FIG. 5A

【図 5B】

FIG. 5B

【図 6】

FIG. 6

【図 7】

FIG. 7

【図 8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

---

フロントページの続き

(51)Int.Cl. F I

*H 01 L 27/32 (2006.01) G 09 F 9/30 3 6 5 Z*

*G 09 F 9/00 (2006.01) G 09 F 9/30 3 4 9 A*

*G 09 F 9/00 3 3 8*

(74)代理人 100111903

弁理士 永坂 友康

(74)代理人 100102990

弁理士 小林 良博

(74)代理人 100114018

弁理士 南山 知広

(72)発明者 ウィンターズ, ダスティン リー

アメリカ合衆国, ニューヨーク 14580, ウェブスター, ベーンブリッジ レーン 63

審査官 越河 勉

(56)参考文献 特開2004-333699 (JP, A)

特開2006-127910 (JP, A)

特開2004-258488 (JP, A)

特開2001-221995 (JP, A)

特開2003-302641 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 05 B 33 / 10

G 02 B 5 / 20

G 09 F 9 / 00

G 09 F 9 / 30

H 01 L 27 / 32

H 01 L 51 / 50

H 05 B 33 / 12

|                |                                                                                                       |         |            |

|----------------|-------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 具有调整滤波器阵列的OLED显示装置                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP5400614B2</a>                                                                           | 公开(公告)日 | 2014-01-29 |

| 申请号            | JP2009532358                                                                                          | 申请日     | 2007-10-02 |

| [标]申请(专利权)人(译) | 伊斯曼柯达公司                                                                                               |         |            |

| 申请(专利权)人(译)    | 伊士曼柯达公司                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 全球豪迪E.技术Rimitido责任公司                                                                                  |         |            |

| [标]发明人         | ウィンターズダスティンリー                                                                                         |         |            |

| 发明人            | ウィンターズ,ダスティン リー                                                                                       |         |            |

| IPC分类号         | H05B33/10 H05B33/12 H01L51/50 G02B5/20 G09F9/30 H01L27/32 G09F9/00                                    |         |            |

| CPC分类号         | H01L27/322 H01L51/56 H01L2251/5315 H01L2251/568                                                       |         |            |

| FI分类号          | H05B33/10 H05B33/12.E H05B33/14.A H05B33/12.Z G02B5/20.101 G09F9/30.365.Z G09F9/30.349.A G09F9/00.338 |         |            |

| 代理人(译)         | 青木 笃<br>石田 敬<br>南山智博                                                                                  |         |            |

| 优先权            | 11/548040 2006-10-10 US                                                                               |         |            |

| 其他公开文献         | JP2010506375A                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                             |         |            |

## 摘要(译)

制造用于产生图像的OLED显示装置的方法包括形成发光元件阵列;测试光产生元件阵列并记录有缺陷的光产生元件的位置;提供具有至少两种不同颜色的滤色器元件阵列的默认图案;并且响应于有缺陷的光产生元件的记录位置形成滤色器元件阵列,至少一个滤色器元件的位置从默认图案改变。

【図2】

FIG. 2