#### (19) 日本国特許庁(JP)

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2013-238861 (P2013-238861A)

(43) 公開日 平成25年11月28日(2013.11.28)

| (51) Int.Cl. |       |           | F 1  |      |         |    | テーマコート   | ヾ (参考) |

|--------------|-------|-----------|------|------|---------|----|----------|--------|

| G09G         | 3/30  | (2006.01) | G09G | 3/30 | J       |    | 3K1O7    |        |

| G09G         | 3/20  | (2006.01) | GO9G | 3/20 | 624B    |    | 5C080    |        |

| HO1L         | 51/50 | (2006.01) | GO9G | 3/20 | 611H    |    | 5C38O    |        |

|              |       |           | GO9G | 3/20 | 670J    |    |          |        |

|              |       |           | G09G | 3/20 | 641D    |    |          |        |

|              |       |           | 審査請求 | き有   | 請求項の数 5 | ΟL | (全 41 頁) | 最終頁に続く |

(21) 出願番号 特願2013-125579 (P2013-125579) (22) 出願日 平成25年6月14日 (2013.6.14) (62) 分割の表示 特願2012-13763 (P2012-13763) の分割 原出願日 平成14年11月11日 (2002.11.11) (31) 優先権主張番号 特願2001-348032 (P2001-348032) (32) 優先日 平成13年11月13日 (2001.11.13) (33) 優先権主張国 日本国 (JP) (71) 出願人 000153878株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72)発明者 木村 肇 神奈川県厚木市長谷398番地 株式会社 半導体エネルギー研究所内

F ターム (参考) 3K107 AA01 BB01 BB06 BB08 CC33 CC45 EE03 EE57 EE61 HH02 HH04 HH05 5C080 AA06 BB05 DD18 DD23 DD29 JJ02 JJ03 JJ04 JJ05 JJ06

最終頁に続く

# (54) 【発明の名称】表示装置、モジュール及び電子機器

# (57)【要約】 (修正有)

【課題】発光素子の特性ばらつき、劣化に伴う電流値ばらつきを生じにくくする表示装置とその駆動方法を提供する。

【解決手段】トランジスタと、容量素子106と、発光素子と、ソース信号線101と、電流供給線107とを有し、前記発光素子は、前記トランジスタによって決定される電流値に応じた輝度で発光する表示装置の駆動方法であって、前記トランジスタのソースに第1の電位を、前記トランジスタのゲートに映像信号を入力する動作と、前記第1の電位と、前記映像信号とに応じて決定される電位差を、前記容量素子に保持し、前記トランジスタのソースの電位を第2の電位に変化させる動作とを含む。前記容量素子は、トランジスタのゲート・ソース間電圧を保持するため、トランジスタの第1の電極の電位が変化しても、ゲート・ソース間電圧を一定とすることにより電流値を一定とする。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

発光素子を有する画素が設けられ、

前記画素は、

それぞれが導通、非導通の2状態をとる第1および第2のスイッチング素子と、トランジスタと、容量手段と、発光素子とを有し、

前記第1のスイッチング素子の第1の電極には、映像信号が入力され、第2の電極は、前記トランジスタのゲート電極と電気的に接続され、

前記トランジスタの第1の電極は、前記第2のスイッチング素子の第1の電極および、前記発光素子の第1の電極と電気的に接続され、第2の電極は、第1の電源と電気的に接続され、

前記第2のスイッチング素子の第2の電極は、第2の電源と電気的に接続され、

前記発光素子の第2の電極は、第3の電源と電気的に接続され、

前記容量手段は、前記トランジスタのゲート電極と第1の電極との間に設けられていることを特徴とする半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、トランジスタを有する半導体装置の構成に関する。本発明はまた、ガラス、プラスチック等の絶縁体上に作製される薄膜トランジスタ(以後、TFTと表記する)を有する半導体装置を含むアクティブマトリクス型の表示装置の構成に関する。また、このような表示装置を用いた電子機器に関する。

#### 【背景技術】

#### [00002]

近年、エレクトロルミネッセンス(Electro Luminescence: EL)素子等を始めとした発光素子を用いた表示装置の開発が活発化している。発光素子は、自らが発光するために視認性が高く、液晶表示装置(LCD)等において必要なバックライトを必要としないために薄型化に適しているとともに、視野角にほとんど制限が無い。

#### [0003]

ここで、EL素子とは、電場を加えることで発生するルミネッセンスが得られる発光層を有する素子を指す。この発光層においては、一重項励起状態から基底状態に戻る際の発光(蛍光)と、三重項励起状態から基底状態に戻る際の発光(燐光)とがあるが、本発明において、発光装置とは、上述したいずれの発光形態であっても良い。

#### [0004]

E L 素子は、一対の電極 ( 陽極と陰極 ) 間に発光層が挟まれる形で構成され、通常、積層構造をとっている。代表的には、イーストマン・コダック・カンパニーのTangらが提案した「陽極 / 正孔輸送層 / 発光層 / 電子輸送層 / 陰極 」という積層構造が挙げられる。この構造は非常に発光効率が高く、現在研究が進められているEL素子の多くはこの構造が採用されている。

#### [00005]

また、これ以外にも、陽極と陰極との間に、「正孔注入層/正孔輸送層/発光層/電子輸送層」または「正孔注入層/正孔輸送層/発光層/電子輸送層/電子注入層」の順に積層する構造がある。本発明の発光装置に用いる EL素子の構造としては、上述の構造のいずれを採用していても良い。また、発光層に対して蛍光性色素等をドーピングしても良い

# [0006]

本明細書においては、EL素子において、陽極と陰極との間に設けられる全ての層を総称してEL層と呼ぶ。よって、上述の正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層は、全てEL素子に含まれ、陽極、EL層、および陰極で構成される発光素子をEL素子と呼ぶ。

10

20

30

#### [0007]

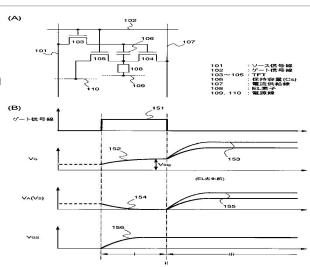

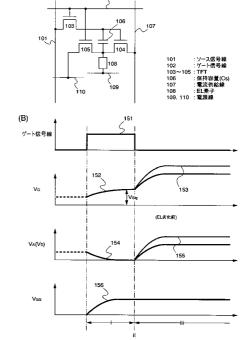

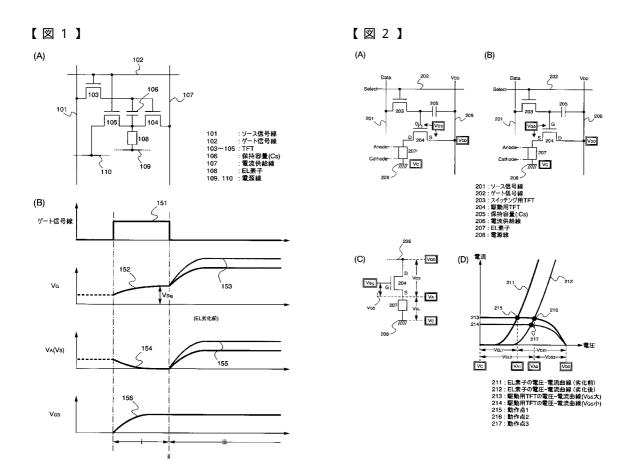

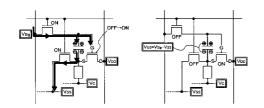

図2(A)(B)に、一般的な発光装置における画素の構成を示す。なお、代表的な発光装置として、EL表示装置を例とする。図2(A)(B)に示した画素は、ソース信号線201、ゲート信号線202、スイッチング用TFT203、駆動用TFT204、容量素子(容量手段)205、電流供給線206、EL素子207、電源線208を有している。図2(A)においては、駆動用TFT204はPチャネル型、図2(B)においては、駆動用TFT204はNチャネル型を用いている。スイッチング用TFT203は、映像信号を画素に入力する際のスイッチとして機能するTFTであるので、ここではその極性は問わない。

#### [0008]

各部の接続関係について説明する。ここで、TFTはゲート、ソース、ドレインの3端子を有するが、ソース、ドレインに関しては、TFTの構造上、明確に区別が出来ない。よって、素子間の接続について説明する際は、ソース、ドレインのうち一方を第1の電極、他方を第2の電極と表記する。TFTのON、OFFについて、各端子の電位等(あるTFTのゲート・ソース間電圧等)について説明が必要な際には、ソース、ドレイン等と表記する。

#### [0009]

また、本明細書において、TFTがONしているとは、TFTのゲート・ソース間電圧がそのしきい値を超え、ソース、ドレイン間に電流が流れる状態をいい、TFTがOFFしているとは、TFTのゲート・ソース間電圧がそのしきい値を下回り、ソース、ドレイン間に電流が流れていない状態をいう。

# [0010]

スイッチング用TFT203のゲート電極は、ゲート信号線202に接続され、第1の電極はソース信号線201に接続され、第2の電極は駆動用TFT204のゲート電極に接続されている。駆動用TFT204の第1の電極は、電流供給線206に接続され、第2の電極はEL素子207の陽極(Anode)に接続されている。EL素子207の陰極(Cathode)は、電源線208に接続されている。電流供給線206と、電源線208とは、互いに電位差を有している。また、駆動用TFT204のゲート・ソース間電圧を保持するために、駆動用TFT204のゲート電極とある一定電位,例えば電流供給線206との間に、容量素子205を設けても良い。

#### [0011]

ゲート信号線202にパルスが入力されてスイッチング用TFT203がONすると、ソース信号線201に出力されてきている映像信号は、駆動用TFT204のゲート電極へと入力される。入力された映像信号の電位に従って、駆動用TFT204のゲート・ソース間電圧が決定し、駆動用TFT204のソース・ドレイン間を流れる電流(以下、ドレイン電流と表記)が決定する。この電流はEL素子207に供給されて発光する。

# [0012]

またTFT等を基板上に作り込み、画素部と周辺回路とを一体形成した表示装置は、小型、軽量という利点を活かし、普及著しいモバイル機器に応用されている。反面、TFTの作製は、成膜、エッチングの繰り返しによる素子形成と、半導体に導電性を与えるための不純物元素の添加等、多くの工程を経てなされるため、工程削減による低コスト化が課題となる。

#### [0013]

そこで、画素部および周辺回路を、単一極性のTFTによって構成すれば、不純物元素の添加工程の一部を省略することが出来る。単一極性のTFTを用いて構成した画素の例としては、図8に示すものが提案されている(例えば、非特許文献1参照)。

### 【先行技術文献】

# 【非特許文献】

#### [0014]

【非特許文献1】カニッキほか(J.Kanicki,J-H.Kim,J.Y.Nahm,Y.He,and R.Hattori)"ア

10

20

30

40

クティブOLEDにおけるアモルファスシリコン薄膜トランジスタ (Amorphous Silicon Thin-Film Transistors Based Active-Matrix Organic Light-Emitting Displays) "アジアディスプレイ/アイディーダブリュ(ASIA DISPLAY/IDW)2001 p . 3 1 5 - 3 1 8

[0015]

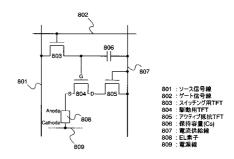

図 8 に示した画素は、ソース信号線 8 0 1、ゲート信号線 8 0 2、スイッチング用TFT 8 0 3、駆動用TFT 8 0 4、アクティブ抵抗TFT 8 0 5、容量素子 8 0 6、電流供給線 8 0 7、EL素子 8 0 8、電源線 8 0 9を有し、TFT 8 0 3~8 0 5 にはNチャネル型TFTを用いている。

[0016]

スイッチング用TFT803のゲート電極は、ゲート信号線802に接続され、第1の電極は、ソース信号線801に接続され、第2の電極は、駆動用TFT804のゲート電極に接続されている。駆動用TFT804の第1の電極は、EL素子808の陽極に接続され、第2の電極は、アクティブ抵抗TFT805の第1の電極に接続されている。アクティブ抵抗TFT805のゲート電極および第2の電極は互いに接続され、電流供給線807に接続されている。EL素子808の陰極は、電源線809に接続され、電流供給線807とは互いに電位差を有する。容量素子806は、駆動用TFT804のゲート電極と電流供給線807との間に設けられ、駆動用TFT804のゲート電極に印加される信号の電位を保持する。

【発明の概要】

【発明が解決しようとする課題】

[0017]

ここで図 2 (A)、図 8 のように、駆動用TFTにNチャネル型TFTを用いた場合の動作について考える。図 2 (C)は、図 2 (A)(B)に示した画素において、電流供給線 2 0 6 - 駆動用TFT 2 0 4 - EL素子 2 0 7 - 電源線 2 0 8 の構成部分のみを図示したものである。駆動用TFT 2 0 4 はNチャネル型としているので、EL素子 2 0 7 の陽極に接続されている側をソース、電流供給線に接続されている側をドレインとする。

[ 0 0 1 8 ]

今、電流供給線 2 0 6 の電位が  $V_{DD}$ 、 E L 素子 2 0 7 の陽極の電位が  $V_A$ 、同じく陰極の電位が  $V_C$ 、駆動用 T F T 2 0 4 のゲート電極の電位が  $V_{Sig}$ であるとき、駆動用 T F T 2 0 4 のゲート・ソース間電圧  $V_{GS}$ は、  $V_{GS}$  = ( $V_{Sig}$  -  $V_A$ )であり、 E L 素子 2 0 7 の陽極・陰極間電圧  $V_{EL}$  は、  $V_{EL}$  = ( $V_A$  -  $V_C$ )である。

[0019]

図 2 ( D ) は、駆動用 T F T 2 0 4 および E L 素子 2 0 7 の電圧・電流特性を示したものである。駆動用 T F T 2 0 4 の電圧・電流曲線と、 E L 素子 2 0 7 の電圧・電流曲線との交点が動作点であり、 E L 素子 2 0 7 を流れる電流値や、 E L 素子の陽極の電位  $V_A$ が決定する。今、 E L 素子 2 0 7 の電圧・電流曲線が 2 1 1、 T F T 2 0 4 の電圧・電流曲線が 2 1 3 で表されるとき、動作点は 2 1 5 にあたり、これによって電流値および  $V_A$  =  $V_A$  1 が決定する。なお、このときの駆動用 T F T 2 0 4 のゲート・ソース間電圧  $V_{GS}$ は、  $V_{GS}$  = ( $V_{Sig}$  -  $V_{A1}$ )で表される。

[0020]

E L 素子 2 0 7 が劣化した場合について考える。 E L 素子 2 0 7 が劣化すると、点灯開始電圧が上昇して、曲線は右にシフトして 2 1 2 で示されるようになる。ここで、仮に駆動用 T F T 2 0 4 が飽和領域で動作しており、かつ E L 素子 2 0 7 の劣化によってゲート・ソース間電圧が変化しないとすると、動作点は 2 1 6 に移る。つまり、  $V_A = V_{A2}$ となる。この場合、駆動用 T F T 2 0 4 のソース・ドレイン間電圧が変化しても、電流値には大きな変化はないため、それほど輝度も変わらない。ところが、今、駆動用 T F T 2 0 4 には N チャネル型 T F T を用いており、 E L 素子 2 0 7 の陽極に接続されている側がソースであるから、駆動用 T F T 2 0 4 のゲート・ソース間電圧  $V_{GS}$ は、  $V_{GS} = (V_{Sig} - V_{A2})$ と、小さくなってしまう。よってこのときの駆動用 T F T 2 0 4 の電圧・電流曲線は 2 1 4 で示されるようになる。従って動作点は 2 1 7 となる。つまり、 E L 素子 2 0 7 の劣

10

20

30

40

(5)

化によって、駆動用TFT204のソース電位が上昇し、ゲート・ソース間電圧が小さくなってしまったため、電流値が大きく変化し、輝度低下につながる。

#### [0021]

よって本発明においては、EL素子に電流を供給するための駆動用TFTにNチャネル型TFTを用いて構成し、かつ前述のようなEL素子の劣化による不具合を解決することの出来る半導体装置を提供することを課題とする。

【課題を解決するための手段】

#### [0022]

前述の課題の要点は、EL素子の劣化によって、EL素子の陽極の電位、すなわち駆動用TFTのソース電位が上昇し、それに伴って駆動用TFTのゲート・ソース間電圧が小さくなる点にあった。

[0023]

EL素子が劣化した場合にも、電流値が変化しないようにするには、EL素子が劣化してEL素子の陽極の電位が上昇したとしても、駆動用TFTのゲート・ソース間電圧に変化が生じないようにする必要がある。

[0024]

そこで本発明においては、ブートストラップ動作を応用した構成を画素に適用した。駆動用TFTのゲート・ソース間に容量素子(電圧保持手段)を設け、ゲート電極に映像信号が入力されている間は、ソースの電位をある値に固定する。

そして、映像信号の入力後、ゲート電極を浮遊状態とする。このとき、駆動用TFTのゲート・ソース間電圧がしきい値を上回っていれば、駆動用TFTがONし、容量素子は映像信号の電位(Vsig)と電源線の電位(Vss)との電位差を保持している。ここで、駆動用TFTのソース電位の固定を解除してやると、EL素子(発光素子)に電流が流れて、陽極の電位、すなわち駆動用TFTのソース電位が上昇する。すると、駆動用TFTのゲート・ソース間に配置された容量素子による結合によって、浮遊状態となっている駆動用TFTのゲート電極の電位も同じだけ上昇することになる。よって、EL素子の劣化によって陽極の電位上昇の値が異なってくる場合にも、その上昇分をゲート電極の電位にそのまま上乗せし、駆動用TFTのゲート・ソース間電圧を一定とすることが出来る。

[0025]

本発明の構成を以下に記す。

[0026]

本発明の表示装置は、発光素子と、映像信号に基づく電圧を保持する電圧保持手段と、少なくとも1つのスイッチング素子を介して前記発光素子及び前記電圧保持手段に接続される電源線と、を有する表示装置であって、前記電圧保持手段は前記発光素子に供給する電流を制御する機能を有し、前記電流は前記映像信号の電位と前記電源線の電位との電位差であることを特徴とする。

[0027]

本発明の表示装置は、発光素子と、映像信号に基づく電圧を保持する電圧保持手段と、前記電圧保持手段に接続されるスイッチング素子と、前記スイッチング素子に接続される電源線と、前記発光素子及び前記電圧保持手段とに接続されるトランジスタと、前記トランジスタに接続される電流供給線と、を有する表示装置であって、前記電圧保持手段は前記映像信号の電位と前記電源線の電位との電位差を保持し、且つ前記トランジスタのゲート・ソース間電圧を制御し、前記トランジスタのゲート・ソース間電圧に基づく電流が前記電流供給線から前記発光素子に供給されることを特徴とする。

[0028]

本発明の表示装置は、発光素子と、映像信号に基づく電圧を保持する電圧保持手段と、前記電圧保持手段と電源線との間に接続されるスイッチング素子と、前記スイッチング素子に接続される電源線と、前記発光素子及び前記電圧保持手段とに接続されるトランジスタと、前記トランジスタに接続される電流供給線と、を有する表示装置であって、前記電圧保持手段は前記映像信号の電位と前記電源線の電位との電位差を保持し、且つ前記ト

10

20

30

40

ランジスタのゲート・ソース間電圧を制御し、前記トランジスタのゲート・ソース間電圧 に基づく電流が前記電流供給線から前記発光素子に供給されることを特徴とする。

#### [0029]

本発明の表示装置は、第1および第2のスイッチング素子と、トランジスタと、容量素子と、発光素子とを有し、前記第1のスイッチング素子の第1の電極はソース信号線と、且つ第2の電極は前記トランジスタのゲート電極とそれぞれ電気的に接続され、前記トランジスタの第1の電極は前記第2のスイッチング素子の第1の電極および、前記発光素子の第1の電極と、且つ第2の電極は電流供給線とそれぞれ電気的に接続され、前記第2のスイッチング素子の第2の電極は、第1の電源線と電気的に接続され、前記発光素子の第2の電極は、第2の電源線と電気的に接続され、前記容量素子は、前記トランジスタのゲート電極と第1の電極との間に設けられている画素を有することを特徴とする。

#### [0030]

本発明の表示装置は、第1乃至第3のスイッチング素子と、トランジスタと、容量素子と、発光素子とを有し、前記第1のスイッチング素子の第1の電極はソース信号線と、且つ第2の電極は前記トランジスタのゲート電極とそれぞれ電気的に接続され、前記トランジスタの第1の電極は前記第2のスイッチング素子の第1の電極および、前記発光素子の第1の電極と、且つ第2の電極は電流供給線とそれぞれ電気的に接続され、前記第2のスイッチング素子の第2の電極は、第1の電源線と電気的に接続され、前記発光素子の第2の電極は、第2の電源線と電気的に接続され、前記容量素子は、前記トランジスタのゲート電極と第1の電極との間に設けられている画素を有することを特徴とする。

#### [0031]

本発明の表示装置は、第1乃至第3のスイッチング素子と、トランジスタと、容量素子と、発光素子とを有し、前記第1のスイッチング素子の第1の電極はソース信号線と、且つ第2の電極は前記トランジスタのゲート電極とそれぞれ電気的に接続され、前記予光素子の第1の電極と、且つ第2の電極は電流供給線とそれぞれ電気的に接続され、前記第2のスイッチング素子の第2の電極は、第1の電源線と電気的に接続され、前記発光素子の第2の電極は、第2の電源線と電気的に接続され、前記容量素子は、前記トランジスタのゲート電極と第1の電極との間に設けられ、前記第3のスイッチング素子の第1の電極は前記トランジスタのゲート電極と、且つ第2の電極は前記トランジスタの第1の電極、前記第2のスイッチング素子の第1の電極及び前記発光素子の第1の電極と、それぞれ電気的に接続されている画素を有することを特徴とする。

#### [0032]

本発明の表示装置は、第1乃至第3のスイッチング素子と、トランジスタと、容量素子と、発光素子とを有し、前記第1のスイッチング素子の第1の電極はソース信号線と、且つ第2の電極は前記トランジスタのゲート電極とそれぞれ電気的に接続され、前記発光素子の第1の電極と、且つ第2の電極は電流供給線とそれぞれ電気的に接続され、前記第2のスイッチング素子の第2の電極は、第1の電源線と電気的に接続され、前記発光素子の第2の電極は、第1の電源線と電気的に接続され、前記発光素子の第1の電極との間に設けられ、前記容量素子は、前記トランジスタのゲート電極と第1の電極との間に設けられ、前記第3のスイッチング素子の第1の電極は前記発光素子の第1の電極と、且つ第2の電極は前記第1の電源線と電気的に接続されている画素を有することを特徴とする。

# [0033]

本発明の表示装置は、前記トランジスタの導電型がNチャネル型であるとき、前記電流供給線 $V_1$ 、前記第1の電源線の電圧 $V_2$ 、前記第2の電源線電圧 $V_3$ は $V_1$  >  $V_2$ 、かつ $V_1$  >  $V_3$ であってもよい。更に、 $V_2$  <  $V_3$ であっても良い。

#### [0034]

また本発明の表示装置は、前記トランジスタの導電型が P チャネル型であるとき、前記電流供給線 V  $_1$ 、前記第 1 の電源線の電位 V  $_2$ 、前記第 2 の電源線の電位 V  $_3$  は V  $_4$  < V  $_2$ 、

10

20

30

40

20

30

40

50

かつ $V_1 < V_3$ であってもよい。更に、 $V_2 > V_3$ であっても良い。

#### [0035]

本発明の表示装置は、ソース信号線と、ゲート信号線と、電流供給線と、第1乃至第3のトランジスタと、容量素子と、発光素子とを有する画素がマトリクス状に設けられた表示装置であって、前記第1のトランジスタのゲート電極は前記第1のゲート信号線と電気的に接続され、第1の電極は前記第2のトランジスタの第1の電極及び前記発光素子の第1の電極と電気的に接続され、第2の電極は第1の電源線、及び当該画素を含まない行に設けられたゲート信号線のいずれかと電気的に接続され、前記第2のトランジスタのゲート電極は、前記第3のトランジスタの第1の電極と電気的に接続され、第2の電極は、前記第2のゲート電極は、前記第3のトランジスタのゲート電極は第2の電源線と電気的に接続され、前記容量素子は前記第2のトランジスタのゲート電極と第1の電極との間に設けられていることを特徴とする。

### [0036]

本発明の表示装置は、ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1乃至第3のトランジスタと、容量素子と、発光素子とを有する画素がマトリクス状に設けられた表示装置であって、前記第1のトランジスタのゲート電極は前記第1のゲート信号線と電気的に接続され、第1の電極は前記第2のトランジスタの第1の電極と面気的に接続され、第2の電極は第1の電源線、及び当れた第1のゲート信号線若しくは第2のゲート信号線のいずれかと電気的に接続され、前記第2のトランジスタのゲート電極は、前記第3のトランジスタのゲート電極は、前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、第2の電極は、前記ソース信号線と電気的に接続され、前記発光素子の第2の電極は第2の電源線と電気的に接続され、前記容量素子は前記第2のトランジスタのゲート電極と第1の電極との間に設けられていることを特徴とする。

#### [0037]

本発明の表示装置は、ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と 、 第 1 乃 至 第 4 の ト ラ ン ジ ス タ と 、 容 量 素 子 と 、 発 光 素 子 と を 有 す る 画 素 が マ ト リ ク ス 状 に設けられた表示装置であって、前記第1のトランジスタのゲート電極は、前記第1のゲ - ト信号線と電気的に接続され、第1の電極は、前記第2のトランジスタの第1の電極お よび、前記発光素子の第1の電極と電気的に接続され、第2の電極は、第1の電源線、当 該 画 素 を 含 ま な い 行 に 設 け ら れ た 第 1 乃 至 第 3 の ゲ ー ト 信 号 線 、 及 び 当 該 画 素 を 含 む 行 に 設 け ら れ た 第 2 の ゲ ー ト 信 号 線 若 し く は 第 3 の ゲ ー ト 信 号 線 の い ず れ か と 電 気 的 に 接 続 さ れ、前記第2のトランジスタのゲート電極は前記第3のトランジスタの第1の電極と電気 的に接続され、第2の電極は前記電流供給線と電気的に接続され、前記第3のトランジス タ の ゲ ー ト 電 極 は 前 記 第 2 の ゲ ー ト 信 号 線 と 電 気 的 に 接 続 さ れ 、 第 2 の 電 極 は 前 記 ソ ー ス 信号線と電気的に接続され、前記発光素子の第2の電極は第2の電源線と電気的に接続さ れ、前記容量素子は、前記第2のトランジスタのゲート電極と第1の電極との間に設けら れ、前記第4のトランジスタのゲート電極は前記第3のゲート信号線と電気的に接続され 第1の電極は前記第2のトランジスタのゲート電極と電気的に接続され、第2の電極は 前 記 第 2 の ト ラ ン ジ ス タ の 第 1 の 電 極 、 前 記 第 1 の 電 源 線 及 び 前 記 第 2 の 電 源 線 の い ず れ かと電気的に接続されていることを特徴とする。

### [ 0 0 3 8 ]

本発明の表示装置は、ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1乃至第4のトランジスタと、容量素子と、発光素子とを有する画素がマトリクス状に設けられた表示装置であって、前記第1のトランジスタのゲート電極は前記第1のゲート信号線と電気的に接続され、第1の電極は前記第2のトランジスタの第1の電極及び前記発光素子の第1の電極と電気的に接続され、第2の電極は第1の電源線、当該画素を含まない行に設けられた第1のゲート信号線若しくは第2のゲート信号線、及び当該画素

20

30

40

50

を含む行に設けられた第2のゲート信号線のいずれかと電気的に接続され、前記第2のトランジスタのゲート電極は、前記第3のトランジスタの第1の電極と電気的に接続され、第2の電極は前記では、自己ので、上では、前記第1のゲート信号線と電気的に接続され、第2の電極は前記ソース信号線と電気的に接続され、前記発光素子の第2の電極は、第2の電源線と電気的に接続され、前記容量素子は、前記第2のトランジスタのゲート電極と第1の電極との間に設けられ、前記第4のトランジスタのゲート電極と電気的に接続され、第1の電極は前記第2のトランジスタのゲート電極と電気的に接続され、第2の電極は、前記第2のトランジスタの第1の電極、前記第1の電源線、及び前記第2の電源線のいずれかと電気的に接続されていることを特徴とする。

[0039]

本発明の表示装置は、ソース信号線と、第1乃至第3のゲート信号線と、電流供給線ス状に設けられた表示装置であって、前記第1のトランジスタの第1の電極は、前記第2のトランジスタの第1の電極と電気的に接続され、第1の電極は第1の電源線、当部を含まるの第1の電極と電気的に接続され、第2の電極は第1の電源線、当部であるまない行に設けられた第1乃至第3のゲート信号線のいずれかと電気的に接続され、には第2のゲート信号線若しくは第3のゲート信号線のいずれかと電気的に接続され、にに対しているのででは前記電流供給線と電気のに接続され、前記第3のトランジスタのゲート電極は前記第3のトランジスタのゲート電極は前記第2の電極は前記第2の電極は前記発光素子の第2の電極と電気的に接続され、前記発光素子の第2の電極と第1の電極との間に接続され、前記第3のドランジスタのゲート電極と第1の電極との間に接続され、第1の電量を記録と電気的に接続され、第1の電極は前記発光素子の第1の電極と電気的に接続され、第1の電極は前記発光素子の第1の電極と電気的に接続され、第2の電極は前記第1の電源線と電気的に接続され、第1の電極は前記発光素子の第1の電極と電気的に接続され、第2の電極は前記第1の電源線と電気的に接続されていることを特徴とする。

[0040]

本発明の表示装置は、ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1乃至第4のトランジスタと、容量素子とを有する画素がマトリのがート電極は前記第2のドランジスタの第1の電極は前記第2のドランジスタの第1の電極と電気的に接続され、第1の電極は第1の電源線、当該回素を含む行に設けられた第1乃至第3のゲート信号線のいずれかと電気的に接続され、第2の電極は第1の電極と電気的に接続され、前記第2のが一ト信号線が行に設けられた第1乃至第3のゲート信号線のいずれかと電気的に接続され、に接続され、第2の電極と電気のドランジスタのゲート電極は前記第3のトランジスタのゲート電極は前記第3のトランジスタのゲート電極は前記第3のトランジスタのゲート電極は前記第3のトランジスタのゲート電極は前記第3のトランジスタのゲート電極は前記第3のトランジスタのゲート電気的に接続され、第2の電極は前記発光素子の第2の電極は前記第2のでは前記第2ので線と電気的に接続され、前記第4のトランジスタのゲート電極とると第1の電極との間に設けられ、前記第4のトランジスタのゲート電極とこの電極との間に設けられ、前記第4の下の第1の電極と電気的に接続されていることを特徴とする。

[0041]

本発明の表示装置は、ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃至第4のトランジスタと、容量素子と、発光素子とを有する画素がマトリクス状に設けられた表示装置であって、前記第1のトランジスタのゲート電極は前記第1のゲート信号線と電気的に接続され、第1の電極は前記第2のトランジスタの第1の電極及び前記発光素子の第1の電極と電気的に接続され、第2の電極は第1の電源線、当該画素を含まない行に設けられた第1乃至第3のゲート信号線、及び当該画素を含む行に設けられた第2のゲート信号線若しくは第3のゲート信号線のいずれかと電気的に接続され、前記第

2のトランジスタのゲート電極は前記第3のトランジスタの第1の電極と電気的に接続され、第2の電極は前記電流供給線と電気的に接続され、前記第3のトランジスタのゲート電極は前記第2のゲート信号線と電気的に接続され、第2の電極は前記ソース信号線と電気的に接続され、前記発光素子の第2の電極は第2の電源線と電気的に接続され、前記容量素子は、前記第2のトランジスタのゲート電極と第1の電極との間に設けられ、前記第2のトランジスタのゲート電極と第1の電極との間の電圧を保持し、前記第4のトランジスタは、前記第2のトランジスタの第2の電極と前記電流供給線との間、又は前記第2のトランジスタの第1の電極と前記発光素子の第1の電極との間に配置され、当該第4のトランジスタのゲート電極は前記第3のゲート信号線と電気的に接続されていることを特徴とする。

[0042]

本発明の表示装置は、ソース信号線と、第1および第2のゲート信号線と、電流供給線 と、第1乃至第4のトランジスタと、容量素子と、発光素子とを有する画素がマトリクス 状に設けられた表示装置であって、前記第1のトランジスタのゲート電極は前記第1のゲ ート信号線と電気的に接続され、第1の電極は前記第2のトランジスタの第1の電極及び 前記発光素子の第1の電極と電気的に接続され、第2の電極は第1の電源線、当該画素を 含まない行に設けられた第 1 のゲート信号線若しくは第 2 のゲート信号線、及び当該画素 を含む行に設けられた第2のゲート信号線のいずれかと電気的に接続され、前記第2のト ランジスタのゲート電極は前記第3のトランジスタの第1の電極と電気的に接続され、第 2の電極は前記電流供給線と電気的に接続され、前記第3のトランジスタのゲート電極は 前記第1のゲート信号線と電気的に接続され、第2の電極は前記ソース信号線と電気的に 接続され、前記発光素子の第2の電極は第2の電源線と電気的に接続され、前記容量素子 は前記第2のトランジスタのゲート電極と第1の電極との間に設けられ、前記第2のトラ ンジスタのゲート電極と第1の電極との間の電圧を保持し、前記第4のトランジスタは、 前 記 第 2 の ト ラ ン ジ ス タ の 第 2 の 電 極 と 前 記 電 流 供 給 線 と の 間 、 又 は 前 記 第 2 の ト ラ ン ジ ス タ の 第 1 の 電 極 と 前 記 発 光 素 子 の 第 1 の 電 極 と の 間 に 配 置 さ れ 、 当 該 第 4 の ト ラ ン ジ ス タのゲート電極は前記第3のゲート信号線と電気的に接続されていることを特徴とする。

[ 0 0 4 3 ]

本発明の表示装置において、前記第 1 および第 3 のトランジスタは同一導電型であって も良い。

[0044]

本発明の表示装置において、前記画素に含まれるトランジスタは同一導電型であっても 良い。

[0045]

本発明の表示装置において、前記第 2 のトランジスタの導電型が N チャネル型であるとき、前記電流供給線の電位  $V_1$ 、前記第 1 の電源線の電位  $V_2$ 、前記第 2 の電源線の電位  $V_3$ は、  $V_1 > V_2$ 、かつ  $V_1 > V_3$ であっても良い。更に、  $V_2 > V_3$ であっても良い。

[0046]

本発明の表示装置は、前記第 2 のトランジスタの導電型が P チャネル型であるとき、前記電流供給線の電位  $V_1$ 、前記第 1 の電源線の電位  $V_2$ 、前記第 2 の電源線の電位  $V_3$ は、  $V_1 < V_2$ 、かつ  $V_1 < V_3$ であっても良い。更に、  $V_2 < V_3$ であっても良い。

[0047]

本発明の表示装置の駆動方法は、第1および第2のスイッチング素子と、トランジスタと、容量素子と、発光素子とを有し、前記第1のスイッチング素子の第1の電極はソース信号線と電気的に接続され、第2の電極は前記トランジスタのゲート電極と電気的に接続され、前記トランジスタの第1の電極は前記第2のスイッチング素子の第1の電極及び前記発光素子の第1の電極と電気的に接続され、第2の電極は電流供給線と電気的に接続され、前記第2のスイッチング素子の第2の電極は第1の電源線と電気的に接続され、前記容量素子は、前記トランジスタのゲート電極と第1の電極との間に設けられている画素を有する表示装置の駆動方

10

20

30

40

20

30

40

50

法であって、前記第1および第2のスイッチング素子を導通し、前記ソース信号線から前記トランジスタに映像信号を入力し、かつ前記トランジスタの第1の電極の電位を固定し、前記第1および第2のスイッチング素子を非導通として、前記トランジスタのゲート電極を浮遊状態とし、前記トランジスタのゲート電極に印加された電位に応じた電流を前記発光素子に供給し、前記容量素子により、前記トランジスタのゲート・ソース間電圧を保持し、前記トランジスタの第1の電極の電位変化量と、前記トランジスタのゲート電極の電位変化量とを等しくすることを特徴とする。

# [0048]

本 発 明 の 表 示 装 置 の 駆 動 方 法 は 、 第 1 乃 至 第 3 の ス イ ッ チ ン グ 素 子 と 、 ト ラ ン ジ ス タ と 、 容 量 素 子 と 、 発 光 素 子 と を 有 し 、 前 記 第 1 の ス イ ッ チ ン グ 素 子 の 第 1 の 電 極 は ソ ー ス 信 号線と電気的に接続され、第2の電極は前記トランジスタのゲート電極と電気的に接続さ れ、前記トランジスタの第1の電極は前記第2のスイッチング素子の第1の電極及び前記 発光素子の第1の電極と電気的に接続され、第2の電極は電流供給線と電気的に接続され 、 前 記 第 2 の ス イ ッ チ ン グ 素 子 の 第 2 の 電 極 は 第 1 の 電 源 線 と 電 気 的 に 接 続 さ れ 、 前 記 発 光素子の第2の電極は第2の電源線と電気的に接続され、前記容量素子は、前記トランジ スタのゲート電極と第1の電極との間に設けられ、前記第3のスイッチング素子の第1の 電 極 は 、 前 記 トラン ジ ス タ の ゲ ー ト 電 極 と 電 気 的 に 接 続 さ れ 、 第 2 の 電 極 は 前 記 トラ ン ジ スタの第1の電極、前記第1の電源線及び前記第2の電源線のいずれかと電気的に接続さ れている画素を有する表示装置の駆動方法であって、前記第1および第2のスイッチング 素子を導通し、前記ソース信号線から前記トランジスタに映像信号を入力し、かつ前記ト ランジスタの第 1 の電極の電位を固定し、前記第 1 および第 2 のスイッチング素子を非導 通として、前記トランジスタのゲート電極を浮遊状態とし、前記トランジスタのゲート電 極に印加された電位に応じた電流を前記発光素子に供給し、前記容量素子により、前記ト ランジスタのゲート・ソース間電圧を保持し、前記トランジスタの第1の電極の電位変化 量 と 、 前 記 ト ラ ン ジ ス タ の ゲ ー ト 電 極 の 電 位 変 化 量 と を 等 し く し 、 前 記 第 3 の ス イ ッ チ ン グ素子を導通して、前記トランジスタのゲート・ソース間電圧をしきい値電圧の絶対値以 下とし、前記発光素子への電流の供給を停止することを特徴とする。

#### [0049]

本 発 明 の 表 示 装 置 の 駆 動 方 法 は 、 第 1 乃 至 第 3 の ス イ ッ チ ン グ 素 子 と 、 ト ラ ン ジ ス タ と 、 容 量 素 子 と 、 発 光 素 子 と を 有 し 、 前 記 第 1 の ス イ ッ チ ン グ 素 子 の 第 1 の 電 極 は ソ ー ス 信 号 線 と 電 気 的 に 接 続 さ れ 、 第 2 の 電 極 は 前 記 ト ラ ン ジ ス タ の ゲ ー ト 電 極 と 電 気 的 に 接 続 さ れ、前記トランジスタの第 1 の電極は前記第 2 のスイッチング素子の第 1 の電極及び前記 発光素子の第1の電極と電気的に接続され、第2の電極は電流供給線と電気的に接続され 、 前 記 第 2 の ス イ ッ チ ン グ 素 子 の 第 2 の 電 極 は 、 第 1 の 電 源 線 と 電 気 的 に 接 続 さ れ 、 記 発 光 素 子 の 第 2 の 電 極 は 、 第 2 の 電 源 線 と 電 気 的 に 接 続 さ れ 、 前 記 容 量 素 子 は 、 前 記 ト ランジスタのゲート電極と第1の電極との間に設けられ、前記第3のスイッチング素子の 第1の電極は、前記発光素子の第1の電極と電気的に接続され、第2の電極は前記第1の 電源線と電気的に接続されている画素を有する表示装置の駆動方法であって、前記第1お よび第2のスイッチング素子を導通し、前記ソース信号線から前記トランジスタへ前記映 像 信 号 を 入 力 し 、 か つ 前 記 ト ラ ン ジ ス タ の 第 1 の 電 極 の 電 位 を 固 定 し 、 前 記 第 1 お よ び 第 2 のスイッチング素子を非導通として、前記トランジスタのゲート電極を浮遊状態とし、 前 記 ト ラ ン ジ ス タ の ゲ ー ト 電 極 に 印 加 さ れ た 電 位 に 応 じ た 電 流 を 前 記 発 光 素 子 に 供 給 し 、 前記容量素子により、前記トランジスタのゲート・ソース間電圧を保持し、前記トランジ ス タ の 第 1 の 電 極 の 電 位 変 化 量 と 、 前 記 ト ラ ン ジ ス タ の ゲ ー ト 電 極 の 電 位 変 化 量 と を 等 し くし、前記第3のスイッチング素子を導通して、前記トランジスタのゲート・ソース間電 圧をしきい値電圧の絶対値以下とし、前記発光素子への電流の供給を停止することを特徴 とする。

### [0050]

本発明の表示装置の駆動方法は、第1乃至第3のスイッチング素子と、トランジスタと、容量素子と、発光素子とを有し、前記第1のスイッチング素子の第1の電極はソース信

#### [0051]

また本発明おいて、スイッチング素子はトランジスタを使用することができる。そして本発明のトランジスタとしては、薄膜トランジスタ(TFT)又はSOI技術を用いて形成されたトランジスタとすることができる。そして、活性層に有機物を利用したトランジスタ、多結晶半導体を用いたものでも、非晶質半導体を用いたものでもよい。例えば、ポリシリコンを用いたTFTや、アモルファスシリコンを用いたTFTを用いることが可能である。

#### 【発明の効果】

#### [0052]

本発明によって、単極性のTFT、特に素子としての電気的特性に優れるNチャネル型TFTを用いて構成した半導体装置において、EL素子の劣化による駆動用TFTのゲート・ソース間電圧の変動を生じない構成とし、よってEL素子が劣化した場合にも輝度の低下を生じにくくすることが可能となった。また、本発明で提案した構成は、特に複雑な構成とすることもなく、画素を構成する素子数を大きく増加させるものでもないため、開口率の低下等のデメリットを負うことなく、適用出来るため、大変有用であるといえる。

#### 【図面の簡単な説明】

# [0053]

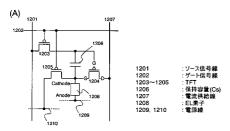

- 【図1】本発明の一実施形態と、その動作を説明する図。

- 【図2】従来構成でTFTを単極性化した場合の動作を説明する図。

- 【図3】図1の構成による回路の動作を説明する図。

- 【図4】本発明の一実施形態と、その動作を説明する図。

- 【図5】本発明の一実施形態と、その動作を説明する図。

- 【図6】本発明の一実施形態と、その動作を説明する図。

- 【図7】駆動用TFTのゲート電極およびソース領域周辺の電位の変化について、本発明と従来例とを比較する図。

- 【図8】単極性のTFTによって構成された画素の一例を紹介する図。

- 【図9】本発明の一実施形態を示す図。

- 【図10】時間階調方式について説明する図。

- 【図11】時間階調方式について説明する図。

- 【図12】本発明の一実施形態と、その動作を説明する図。

- 【図13】半導体装置の作製工程について説明する図。

- 【図14】半導体装置の作製工程について説明する図。

- 【図15】半導体装置の上面図および断面図。

- 【図16】アナログ映像信号を用いて表示を行う半導体装置の構成を示す図。

- 【図17】図16の装置におけるソース信号線駆動回路およびゲート信号線駆動回路の例

10

20

30

30

40

を示す図。

【図18】デジタル映像信号を用いて表示を行う半導体装置の構成を示す図。

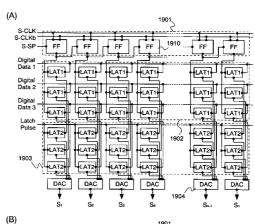

【図19】図18の装置におけるソース信号線駆動回路の例を示す図。

【図20】本発明が適用可能な電子機器の例を示す図。

【図21】本発明の一実施形態と、その動作を説明する図。

【図22】本発明の画素構成の上面図を示す図。

【発明を実施するための形態】

#### [0054]

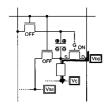

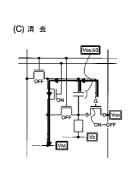

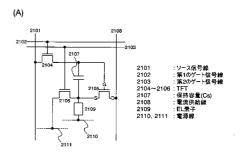

[実施の形態 1] 図 1 (A)に、本発明の実施の一形態を示す。本発明の画素は、ソース信号線 1 0 1、ゲート信号線 1 0 2、第 1 乃至第 3 の T F T 1 0 3~ 1 0 5、容量素子 1 0 6、電流供給線 1 0 7、 E L 素子 1 0 8、電源線 1 0 9、 1 1 0 (第 1 の電源線、第 2 の電源線)とを有する。 T F T 1 0 3 のゲート電極は、ゲート信号線 1 0 2 に接続され、第 1 の電極は、ソース信号線 1 0 1 に接続され、第 2 の電極は、 T F T 1 0 4 のゲート電極に接続されている。 T F T 1 0 4 の第 1 の電極は、電流供給線 1 0 7 に接続され、第 2 の電極は、 T F T 1 0 5 の第 1 の電極および、 E L 素子の第 1 の電極に接続されている。 T F T 1 0 5 の第 1 の電極は、 第 2 の電極は、 第 2 の電極は、 電源線 1 0 1 に接続されている。 E L 素子 1 0 8 の第 2 の電極は、 電源線 1 0 9 に接続されている。 容量素子 1 0 6 は、 T F T 1 0 4 のゲート電極と第 2 の電極との間に設けられ、 T F T のゲート・ソース間電圧を保持する。

# [0055]

今、TFT103~105はいずれもNチャネル型TFTであり、そのゲート・ソース間電圧がしきい値を上回ったとき、ONするものとする。また、EL素子108においては、第1の電極を陽極、第2の電極を陰極とし、陽極の電位を $V_A$ 、陰極の電位、すなわち電源線109の電位を $V_C$ とする。さらに、電流供給線107の電位を $V_D$ とし、電源線110の電位を $V_S$ とする。映像信号の電位は $V_S$ は、とする。

#### [0056]

回路の動作について、図 1 および図 3 を用いて説明する。ここで、TFT 1 0 4 のゲート(G)、ソース(S)、ドレイン(D)を図 3 (A)のように定義する。

# [0057]

ある行において、ゲート信号線 1 0 2 が選択されてTFT 1 0 3、 1 0 5 が O N する。 ソース信号線 1 0 1 より、映像信号が図 3 (A)に示すように、TFT 1 0 4 のゲート電極に入力されて、その電位が  $V_{sig}$ となる。一方、TFT 1 0 5 が O N しているので、  $V_A$  =  $V_{ss}$ となる。このとき、  $V_{ss}$   $V_c$ としておくと、映像信号の書き込み時にはEL素子 1 0 8 に電流が流れない。ただし、  $V_{ss}$  >  $V_c$ となっており、EL素子 1 0 8 に電流が流れても構わない。ここで重要となるのは、  $V_A$ が一定電位に固定されていることである。この動作により、容量素子 1 0 6 の両電極間の電圧は、  $(V_{sig}$  -  $V_{ss}$ )となる。やがて、ゲート信号線 1 0 2 の選択期間が終了し、TFT 1 0 3、 1 0 5 が O F F すると、容量素子 1 0 6 に貯まった電荷の移動経路がなくなり、TFT 1 0 4 のゲート・ソース間電圧( $V_{sig}$  -  $V_{ss}$ )が保持される(図 3 (B))。

# [0058]

ここで、 $(V_{Sig} - V_{SS})$ がTFT104のしきい値を上回っているとき、TFT104がONして電流供給線107からEL素子に電流が流れ始めて発光が始まり(図3(С))、TFT104のソース電位が上昇する。このとき、TFT104のゲート電極は浮遊状態にあり、容量素子106によって、TFT104のゲート・ソース間電圧が保持されているので、ソース電位の上昇に伴って、ゲート電極の電位も上昇する。このとき、TFT104、105においては、そのゲート電極と半導体層(ソース領域あるいはドレイン領域)との間には容量成分が存在するが、容量素子106の容量値を、当該容量成分に対して十分に支配的としておくことにより、TFT104のソース電位の上昇幅と、TFT104のゲート電位の上昇幅とをおおむね等しくすることが出来る。

# [0059]

10

20

30

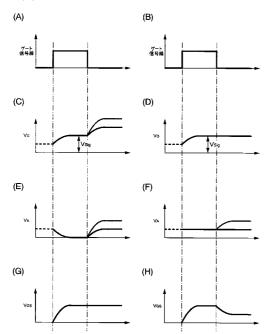

これらの動作を踏まえ、図 1 ( B ) を用いて E L 素子の劣化の有無による動作について考える。図 1 ( B ) において、 1 5 1 はゲート信号線 1 0 2 の電位、 1 5 2 、 1 5 3 は T F T 1 0 4 のゲート電極の電位  $V_G$ 、 1 5 4 、 1 5 5 は E L 素子 1 0 8 の陽極  $V_A$  すなわち T F T 1 0 4 のソース電位、 1 5 6 は T F T 1 0 4 のゲート・ソース間電圧  $V_{GS}$ をそれぞれ模式的に表したものである。

### [0060]

今、図 1 (B)に(i)で示した区間において、ゲート信号線 1 0 2 が選択され、Hレベルとなる。よってこの区間では、映像信号の書き込みが行われてTFT 1 0 4 のゲート電位  $V_G$ が上昇する。また、TFT 1 0 5 が O N しているので、EL素子 1 0 8 の陽極の電位  $V_A$ 、つまりTFT 1 0 4 のソース電位は、 $V_{SS}$ に等しくなる。よって、TFT 1 0 4 のゲート・ソース間電圧  $V_{GS}$ が大きくなる。またこの区間では、 $V_A$  =  $V_{SS}$  <  $V_C$ となっている場合には、映像信号  $V_{Sig}$  の値に関係なく、EL素子 1 0 8 は発光しない。

#### [0061]

(ii)で示したタイミングにおいて、ゲート信号線 1 0 2 の選択が終了して L レベルとなり、TFT 1 0 3 、 1 0 5 が O F F する。このときの  $V_{GS}$  = ( $V_{Sig}$  -  $V_A$ )が、容量素子 1 0 6 に保持される。

# [0062]

続いて、(iii)で示した区間に入り、発光が始まる。このとき、TFT104のゲート・ソース間電圧 V<sub>GS</sub>がそのしきい値を上回っていれば、TFT104がONしてドレイン電流が流れ、EL素子108が発光する。同時に、TFT104のソース電位も上昇する。ここで、前述のとおり、TFT104のゲート電極は浮遊状態となっており、TFT104のソース電位の上昇と同様に上昇する。

#### [0063]

ここで、 E L 素子 1 0 8 が劣化した場合を考える。 E L 素子が劣化すると、前述のとおりある値の電流を E L 素子 1 0 8 に流そうとするとき、陽極・陰極間の電圧が大きくなるため、 1 5 5 で示すように  $V_A$  が上昇する。しかし本発明の場合、  $V_A$  の上昇分だけ、  $V_G$  も上昇するため、結果として  $V_{GS}$  に変化がないことがわかる。

#### [0064]

一方、図7に示すように、図2(B)に示したような従来の構成の場合、一旦映像信号が入力されてその電位が $V_{Sig}$ となると、その後TFT204のゲート電位 $V_{G}$ は変化しない。よって、EL素子207が劣化して $V_{A}$ が上昇すると、TFT204のゲート・ソース間電圧は劣化前よりも小さくなってしまう(図7(G)(H))。このような場合、TFT204を飽和領域で動作させたとしても、動作点における電流値は変化してしまうことになる。よって、EL素子207が劣化し、電圧・電流特性が変化すると、EL素子207に流れる電流が小さくなり、輝度が低下する。

#### [0065]

以上のように、本発明においては、EL素子の劣化に対しても電流値に変化を与えないようにして、EL素子の劣化の影響を除去することが出来る。

#### [0066]

また、電源線の電位  $V_{SS}$ 、  $V_{C}$ はいずれも任意に設定出来るので、  $V_{SS}$  <  $V_{C}$ としておくことによって、 EL 素子に逆バイアスを印加することも容易である。

#### [0067]

なお、TFT103、105は、単なるスイッチング素子として機能すればよく、その極性は問わない。すなわち、画素を構成するTFTを全て単極性としても正常動作が可能となる。図1においては、TFT103、105を同極性とし、ゲート信号線102のみによって制御しているが、異なる第1、第2のゲート信号線を用いて、それぞれのTFTを制御するようにしても良い。この場合はTFT103、105が互いに極性が異なっていても構わない。ただし、画素の開口率等を考えると、配線数は可能な限り少ない本数とするのが望ましい。

# [0068]

50

10

20

30

[実施の形態 2] 図 1 に示した構成によると、画素部に引き回す配線は、ソース信号線、ゲート信号線、電流供給線( $V_{DD}$ )、電源線( $V_{C}$ )、電源線( $V_{SS}$ )の 5 本を必要としていた。本実施形態においては、配線を共用することによって 1 画素あたりの配線の本数を減らし、高開口率化を得られる構成について説明する。

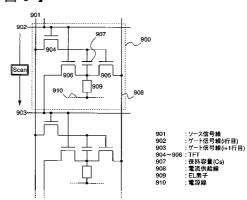

### [0069]

図9に、本実施形態の構成を示す。実施形態1と異なる点は、TFT906の第2の電極が電源線(V<sub>SS</sub>)に接続されていたのに対し、本実施形態では、次行のゲート信号線に接続されている点のみである。点線枠900で示された画素が主行目であるとすると、TFT906の第2の電極は、i+1行目のゲート信号線に接続されている。

#### [0070]

ゲート信号線を選択するパルスの条件としては、Hレベルのときは、TFT904のゲート・ソース間電圧が十分にしきい値を上回ればよい。すなわち、映像信号 V<sub>sig</sub>の最大値に対し、さらにしきい値分以上高い電位であれば良い。これに対し、Lレベルのときは、TFT904が確実にOFFする電位であれば良い。よって、ゲート信号線において、Lレベルの電位を V<sub>ss</sub>に等しくしておく。

#### [0071]

i 行目のゲート信号線が選択されて H レベルとなり、 T F T 9 0 4 、 9 0 6 が O N するとき、 i+1 行目のゲート信号線はまだ選択されていない。すなわち L レベルであり、その電位は V  $_{SS}$ である。よって、 T F T 9 0 6を介して、 E L 素子の陽極の電位 V  $_{A}$ は、実施形態と同じく V  $_{SS}$ に等しくなる。よって、本実施形態に従って配線を共用した場合にも、実施形態 1 と同様の動作を得ることが出来る。

#### [0072]

なお、i行目のゲート信号線が選択されてHレベルとなり、TFT906がONしている期間に、一定の電位Vssを与えることの出来る場所であれば、TFT906の第2の電極の接続先は、i + 1行目のゲート信号線に限定されず、例えばi - 1行目のゲート信号線であっても良いし、それ以外であっても良い。隣接行の信号線を共用する場合には、当該信号線のパルスが互いに重ならないようにするのが望ましい。

#### [0073]

また、実施形態1に記載したように、TFT904、906は単なるスイッチング素子として機能すればよいので、その極性は問わず、図9のように、1本のゲート信号線90 2によって制御されることに限定はしない。

# [0074]

[実施の形態 3] 駆動用TFTのゲート・ソース間電圧を制御して、EL素子に流れる電流値をアナログ量で制御して表示を行う方式をアナログ階調方式と呼ぶ。これに対し、EL素子を輝度100%、0%の2つの状態のみで駆動するデジタル階調方式が提案されている。この方式では、白、黒の2階調しか表現出来ないが、TFTの特性ばらつきの影響を受けにくいというメリットがある。デジタル階調方式によって多階調化を図るには、時間階調方式と組み合わせた駆動方法を用いる。時間階調方式とは、素子が発光している時間の長短によって、階調を表現する方法である。

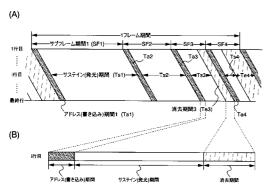

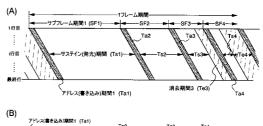

#### [0075]

デジタル階調方式と時間階調方式とを組み合わせた場合、図 1 0 (A)に示すように、 1 フレーム期間を複数のサブフレーム期間に分割する。各サブフレーム期間は、図 1 0 (B)に示すように、アドレス (書き込み) 期間と、サステイン (発光) 期間と、消去期間とを有する。表示ビット数に応じた数のサブフレーム期間を設け、各サブフレーム期間におけるサステイン (発光) 期間の長さを、  $2^{(n-1)}$ :  $2^{(n-2)}$ :・・・: 2: 1 とし、各サステイン (発光) 期間で E L 素子の発光、もしくは非発光の選択をし、 E L 素子が発光している合計期間の長さの差を利用して階調表現を行う。発光している期間が長ければ輝度が高く、短ければ輝度が低くなる。なお、図 1 0 においては 4 ビット階調の例を示しており、 1 フレーム期間は 4 つのサブフレーム期間に分割され、サステイン (発光) 期間の組み合わせによって、  $2^4$  = 1 6 階調を表現出来る。なお、サステイン期間の長さの比は、特に 2 のべき

10

20

30

40

20

30

40

50

乗の比としなくても、階調表現は可能である。また、あるサブフレーム期間をさらに分割 していても良い。

# [0076]

時間階調方式を用いて多階調化を図る場合、下位ビットのサステイン(発光)期間の長さがより短くなるため、サステイン(発光)期間の終了後、直ちに次のアドレス期間を開始しようとすると、異なるサブフレーム期間のアドレス(書き込み)期間が重複する期間が生ずる。その場合、ある画素に入力される映像信号が、同時に異なる画素にも入力されてしまうため、正常な表示が出来なくなる。消去期間は、このような問題を解決するために設けられており、図10(B)に示すように、Ts3の後、およびTs4の後で、異なる2つのアドレス(書き込み)期間が重複しないように設けられる。よって、サステイン(発光)期間が十分に長く、異なる2つのアドレス(書き込み)期間の重複が生ずる心配の無いSF1、SF2においては、消去期間は設けられていない。

# [0077]

このように、デジタル階調方式と時間階調方式とを組み合わせた方法によって駆動するには、EL素子の発光を強制的に停止して消去期間を設ける動作を追加しなければならない場合がある。

#### [0078]

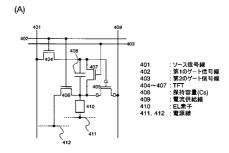

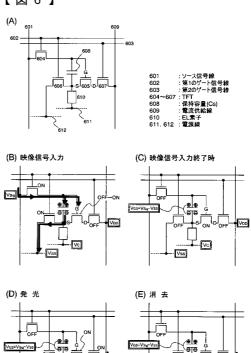

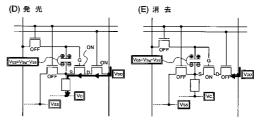

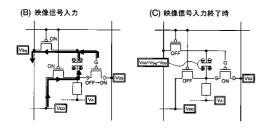

図4(A)は、実施形態1において示した構成の画素に、第2のゲート信号線403、消去用TFT407を追加し、デジタル階調方式と時間階調方式とを組み合わせた駆動方法に対応したものの一例である。消去用TFT407のゲート電極は、第2のゲート信号線403に接続され、第1の電極は、TFT405のゲート電極および容量素子408の第2の電極に接続されている。

#### [0079]

第1のゲート信号線402が選択され、映像信号が入力される動作は、実施の形態1にて示したものと同様であるのでここでは省略する。なお、映像信号の入力が行われている期間においては、第2のゲート信号線はLレベルであり、消去用TFT407はOFFしている。このとき、 $V_{Sig}$ は、TFT405が確実にONするだけの電位もしくは、TFT405がOFFする電位のいずれかの電位をとる。

### [080]

ここで、サステイン(発光)期間から消去期間における動作について、図4および図11を用いて説明する。図11(A)は、図10(A)に示したものと同様であり、1フレーム期間は、図11(B)に示すように、4つのサブフレーム期間を有する。サステイン(発光)期間が短いサブフレーム期間SF3、SF4においては、それぞれ消去期間Te3、Te4を有している。ここでは、SF3での動作を例として説明する。

#### [0081]

映像信号の入力が終了した後、図10(B)に示すように、TFT405のゲート・ソース間電圧 V<sub>GS</sub>に応じた電流がEL素子410に流れて発光する。その後、当該サステイン(発光)期間の終了するタイミングに達すると、第2のゲート信号線403にパルスが入力されてHレベルとなり、消去用TFT407がONし、図4(C)に示すように、TFT907のゲート・ソース間電圧 V<sub>GS</sub>を0とする。よってTFT405がOFFし、EL素子410への電流が遮断され、強制的にEL素子410は非発光となる。

#### [0082]

これらの動作をタイミングチャートとして、図11(C)に示した。サステイン(発光)期間Ts3の後、第3のゲート信号線403にパルスが入力されてEL素子410が非発光となってから、再び第1のゲート信号線402にパルスが入力されて、次の映像信号が入力され始めるまでの期間が消去期間Te3となる。

#### [0083]

また、図 4(A)に示した構成において、TFT406の第2の電極は、電源線412に接続されているが、この電源線412を、実施形態2に示したように、隣接行のゲート信

号線で代用することも出来る。また、本実施形態においては、消去用のTFT407を制御するために、第2のゲート信号線403があるので、TFT406の第2の電極は、第2のゲート信号線403に接続されていても良い。

#### [0084]

また、TFT404、406は同一のゲート信号線402によって制御されているが、 一本ゲート信号線を追加し、異なるゲート信号線によってTFT404、406をそれぞれ制御しても構わない。

#### [0085]

[実施の形態 4] 図 5 (A)に、実施形態 3 とは異なる位置に消去用TFTを設けた例を示す。本実施形態においては、消去用TFT507は、TFT505のゲート電極および容量素子508の第1の電極と、電源線512との間に設けられている。

#### [0086]

駆動方法において、映像信号の入力~発光に関しては、実施形態3と同様、デジタル階調方式と時間階調方式とを組み合わせた方法によれば良いので、ここでは説明を省略し、消去期間における動作について説明する。

#### [0087]

サステイン(発光)期間の終了するタイミングに達すると、第2のゲート信号線503にパルスが入力されてHレベルとなり、消去用TFT507がONし、図5(C)に示すように、TFT505のゲート電極の電位がVssとなる。つまり、消去期間においては、TFT505のゲート・ソース間電圧Vgsが、しきい値を下回るようにしてやれば良い。

#### [0088]

TFT505のソース電位は、少なくともV<sub>SS</sub>に等しいかそれ以上の電位にある。よって、前述の消去用TFT507の動作により、TFT505のゲート・ソース間電圧V<sub>GS</sub>は、V<sub>GS</sub> 0となり、TFT505がOFFする。よってEL素子510が非発光となり、再び第1のゲート信号線502にパルスが入力されて、次の映像信号が入力され始めるまでの期間が消去期間となる。

### [0089]

また、図 5 (A)に示した構成において、TFT506の第2の電極は、電源線512に接続されているが、この電源線512を、実施形態2に示したように、隣接行のゲート信号線で代用することも出来る。また、本実施形態においては、消去用のTFT507を制御するために、第2のゲート信号線503があるので、TFT506の第2の電極は、第2のゲート信号線503に接続されていても良い。

#### [0090]

[実施の形態 5] 図 6 (A)に、実施形態 3、4とは異なる位置に消去用TFTを設けた例を示す。本実施形態においては、消去用TFT607は、TFT605の第1の電極と、電流供給線との間に設けられている。

#### [0091]

#### [0092]

映像信号の入力が完了し、第1のゲート信号線602が非選択となると、TFT605のゲート電極は浮遊状態となり、容量素子608においては、貯まった電荷の移動経路が遮断されるため、ゲート・ソース間電圧 V GS は容量素子608に保持される。

#### [0093]

続いて、第2のゲート信号線603が選択されてHレベルとなり、TFT607がONすることによって図6(D)に示すように電流が流れ、EL素子610の陽極の電位V<sub>A</sub>が上昇して陰極の電位V<sub>C</sub>と電位差を生じ、電流が流れて発光する。なお、映像信号の入力

20

10

30

40

を行っている段階からTFT607がONしていても良い。この場合は、第1のゲート信号線602が非選択となった瞬間、TFT607、605を経てEL素子610に電流が供給され、EL素子610の陽極の電位  $V_C$ と電位差を生じ、電流が流れて発光する。

#### [0094]

サステイン(発光)期間の終了するタイミングに達すると、第2のゲート信号線603が非選択となってLレベルとなり、TFT607がOFFし、電流供給線609からEL素子610への電流経路を遮断する。これによりEL素子610には電流が流れなくなって非発光となる。その後、再び第1のゲート信号線602にパルスが入力されて、次の映像信号が入力され始めるまでの期間が消去期間となる。

[0095]

なお、TFT607は、TFT605の第1の電極と、EL素子610の陽極との間に配置されていても良い。すなわち、電流供給線609からEL素子610への電流経路の間に配置し、消去期間においてEL素子610への電流供給をカットできれば良い。

#### [0096]

[実施の形態 6] 実施形態 3 ~ 5 においては、TFTを追加して消去期間を設ける例について説明してきたが、本実施形態においては、消去用TFTを追加することなく、同様の動作を行う例について説明する。

# [0097]

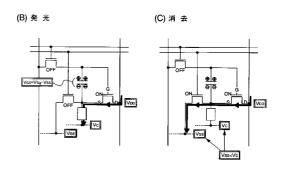

図 2 1 (A)に、構成を示す。構成はおおむね実施形態 1 等に示したものと同様であるが、 T F T 2 1 0 4 、 2 1 0 6 がそれぞれ別のゲート信号線 2 1 0 2 、 2 1 0 3 によって制御される点が異なる。

[0098]

サステイン(発光)期間においては、図 2 1 (B)に示したように、容量素子 2 1 0 7 によって T F T 2 1 0 5 のゲート・ソース間電圧が固定され、それに伴った電流が E L 素子 2 1 0 9 に流れて発光する。

### [0099]

続いて、消去期間に移ると、第2のゲート信号線2103にパルスが入力されてTFT2106がONする。このとき、TFT2106の第2の電極が接続されている電源線21110の電位を、EL素子2109には電流が流れなくなる。よって、このときの電流は、図21(C)に示したように流れる。

[ 0 1 0 0 ]

なお、電源線2111は、他の実施形態においても述べたように、隣接行のゲート信号線を用いても良い。

[0101]

[実施の形態 7] EL素子に電流を供給するTFTには、Nチャネル型TFTを用いてきたが、本発明は、駆動用TFTにPチャネル型TFTを用いての実施も可能である。図1 2 (A)に構成例を示す。

[0102]

回路構成は図 1 ( A ) にて示した N チャネル型 T F T を用いたものと同様であるが、 E L 素子 1 2 0 8 の構成が逆となっており、 T F T 1 2 0 4 の第 2 の電極に接続された側が陰極となり、 電源線 1 2 0 9 に接続された側が陽極となっている点と、電流供給線 1 2 0 7 の電位が  $V_{SS}$ 、電源線 1 2 0 9 の電位が  $V_{A}$ 、電源線 1 2 1 0 の電位が  $V_{DD}$ である点が異なる。ここで、  $V_{SS}$  <  $V_{DD}$ かつ  $V_{A}$  <  $V_{DD}$ である。

# [0103]

回路の動作について、図12(B)~(D)を用いて説明する。なおここでは、TFTの極性はPチャネル型であり、ゲート電極にLレベルが入力されてONし、Hレベルが入力されてOFFするものとする。

# [0104]

50

10

20

30

ある行において、ゲート信号線 1 2 0 2 が選択されてLレベルとなり、TFT 1 2 0 3 、 1 2 0 5 が O N する。ソース信号線 1 2 0 1 より、映像信号が図 1 2 (B)に示すように、TFT 1 2 0 4 のゲート電極に入力されて、その電位が  $V_{Sig}$ となる。一方、TFT 1 2 0 5 が O N しているので、EL素子 1 2 0 8 の陰極の電位  $V_{C}$ は、 $V_{C}$  =  $V_{DD}$ となる。このとき、 $V_{A}$   $V_{DD}$ としておくと、映像信号の書き込み時にはEL素子 1 2 0 8 には電流が流れない。この動作により、容量素子 1 2 0 6 の両電極間の電圧、つまりTFT 1 2 0 4 のゲート・ソース間電圧は、( $V_{Sig}$  -  $V_{DD}$ )となる。やがて、ゲート信号線 1 2 0 2 の選択期間が終了してHレベルとなり、TFT 1 2 0 3 、 1 2 0 5 が O F F すると、容量素子 1 2 0 6 に貯まった電荷の移動経路がなくなり、TFT 1 2 0 4 のゲート・ソース間電圧( $V_{Sig}$  -  $V_{DD}$ )が保持される(図 1 2 (C))。

[0105]

ここで、 $(V_{Sig} - V_{DD})$ がTFT1204のしきい値よりも低くなっているとき、TFT1204がONし、電源線1209~EL素子1208~電流供給線1207間を電流が流れて発光が始まり(図12(D))、TFT1204のソース電位が下降する。このとき、TFT1204のゲート電極は浮遊状態にあり、容量素子1206によって、TFT1204のゲート・ソース間電圧が保持されているので、ソース電位の下降に伴って、ゲート電極の電位も下降する。

[0106]

図12(A)では、画素を構成するTFTには全てPチャネル型TFTを用いているが、TFT1203、1205に関しては、他の実施形態でも述べたように、単なるスイッチング素子として機能すれば良いので、その極性は問わない。また、ゲート信号線1202のみによって、TFT1203、1205が駆動される必要はなく、それぞれのTFTを別のゲート信号線によって制御する構成としていても構わない。

[ 0 1 0 7 ]

以下に、本発明の実施例について記載する。

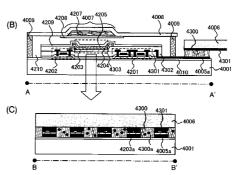

【実施例1】

[0108]

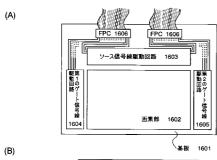

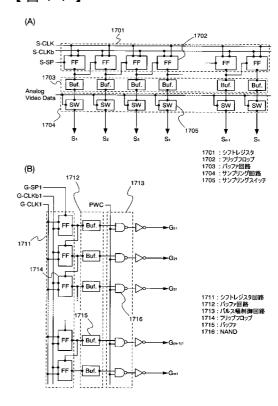

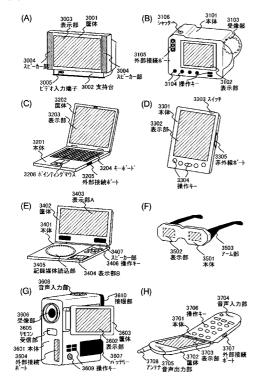

本実施例においては、映像信号にアナログ映像信号を用いて表示を行う発光装置の構成について説明する。図16(A)に、発光装置の構成例を示す。基板1601上に、複数の画素がマトリクス状に配置された画素部1602を有し、画素部周辺には、ソース信号線駆動回路1603および、第1、第2のゲート信号線駆動回路1604、1605を有している。図16(A)においては、2組のゲート信号線駆動回路を用いているが、図1に示した画素のようにゲート信号線が1本である場合には、両側からゲート信号線を同時に制御する。図4、図5に示した画素のように、2本のゲート信号線を有する場合は、それぞれのゲート信号線駆動回路が、それぞれのゲート信号線を制御する。

[0109]

ソース信号線駆動回路 1 6 0 3 、第 1 、第 2 のゲート信号線駆動回路 1 6 0 4 、 1 6 0 5 に入力される信号は、フレキシブルプリント基板(Flexible Print Circuit: FPC) 1 6 0 6 を介して外部より供給される。

[0110]

図16(B)に、ソース信号線駆動回路の構成例を示す。これは、映像信号にアナログ映像信号を用いて表示を行うためのソース信号線駆動回路であり、シフトレジスタ1611 、バッファ1612、サンプリング回路1613を有している。特に図示していないが、必要に応じてレベルシフタ等を追加しても良い。

[0111]

ソース信号線駆動回路の動作について説明する。図 1 7 (A)に、より詳細な構成を示したので、そちらを参照する。

[0112]

シフトレジスタ 1 7 0 1 は、フリップフロップ回路(FF) 1 7 0 2 等を複数段用いてなり、クロック信号(S-CLK)、クロック反転信号(S-CLKb)、スタートパルス(S

10

20

30

40

- S P) が入力される。これらの信号のタイミングに従って、順次サンプリングパルスが 出力される。

# [0113]

シフトレジスタ1701より出力されたサンプリングパルスは、バッファ1703等を通って増幅された後、サンプリング回路へと入力される。サンプリング回路1704は、サンプリングスイッチ(SW)1705を複数段用いてなり、サンプリングパルスが入力されるタイミングに従って、ある列で映像信号のサンプリングを行う。具体的には、サンプリングスイッチにサンプリングパルスが入力されると、サンプリングスイッチ1705がONし、そのときに映像信号が有する電位が、サンプリングスイッチを介して各々のソース信号線へと出力される。

[0114]

続いて、ゲート信号線駆動回路の動作について説明する。図16(C)に示した、第1、第2のゲート信号線駆動回路1604、1605についての詳細な構成の一例を図17(B)に示した。第1のゲート信号線駆動回路は、シフトレジスタ回路1711、バッファ1712を有し、クロック信号(G-CLK1)、クロック反転信号(G-CLKb1)、スタートパルス(G-SP1)に従って駆動される。第2のゲート信号線駆動回路1605も構成は同様で良い。

#### [0115]

シフトレジスタ~バッファの動作については、ソース信号線駆動回路の場合と同様である。バッファによって増幅された選択パルスは、それぞれのゲート信号線を選択する。第 1 のゲート信号線駆動回路によって、第 1 のゲート信号線  $G_{11}$ 、  $G_{21}$ 、・・・、  $G_{m1}$  が順次選択され、第 2 のゲート信号線駆動回路によって、第 2 のゲート信号線  $G_{12}$ 、  $G_{22}$ 、・・、  $G_{m2}$  が順次選択される。図示していないが、第 3 のゲート信号線駆動回路についても第 1 、第 2 のゲート信号線駆動回路と同様であり、第 3 のゲート信号線  $G_{13}$ 、  $G_{23}$ 、・・、  $G_{m3}$  が順次選択される。選択された行において、実施形態にて説明した手順により、画素に映像信号が書き込まれて発光する。

#### [0116]

なお、ここではシフトレジスタの一例として、 D - フリップフロップを複数段用いてなるものを図示したが、デコーダ等によって、信号線を選択出来るような構成としていても良い。

【実施例2】

# [0117]

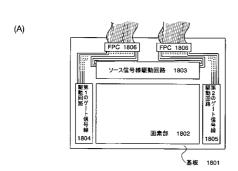

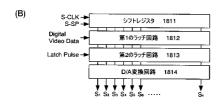

本実施例においては、映像信号にデジタル映像信号を用いて表示を行う発光装置の構成について説明する。図18(A)に、発光装置の構成例を示す。基板1801上に、複数の画素がマトリクス状に配置された画素部1802を有し、画素部周辺には、ソース信号線駆動回路1804、1805を有している。図18(A)においては、2組のゲート信号線駆動回路を用いているが、図1に示した画素のようにゲート信号線が1本である場合には、両側からゲート信号線を同時に制御する。図4、図5に示した画素のように、2本のゲート信号線を有する場合は、それぞれのゲート信号線駆動回路が、それぞれのゲート信号線を制御する。

[0118]

ソース信号線駆動回路 1 8 0 3 、第 1 、第 4 のゲート信号線駆動回路 1 8 0 4 、 1 8 0 5 に入力される信号は、フレキシブルプリント基板(Flexible Print Circuit: FPC) 1 8 0 6 を介して外部より供給される。

#### [0119]

図18(B)に、ソース信号線駆動回路の構成例を示す。これは、映像信号にデジタル映像信号を用いて表示を行うためのソース信号線駆動回路であり、シフトレジスタ1811 、第1のラッチ回路1812、第2のラッチ回路1813、D/A変換回路1814を有している。特に図示していないが、必要に応じてレベルシフタ等を追加しても良い。

[0120]

20

10

30

第1、第2のゲート信号線駆動回路1804、1805については、実施例1にて示したものと同様で良いので、ここでは図示および説明を省略する。

# [0121]

ソース信号線駆動回路の動作について説明する。図 1 9 (A)に、より詳細な構成を示したので、そちらを参照する。

#### [0122]

シフトレジスタ 1 9 0 1 は、フリップフロップ回路(FF) 1 9 1 0 等を複数段用いてなり、クロック信号(S-CLK)、クロック反転信号(S-CLKb)、スタートパルス(S-SP)が入力される。これらの信号のタイミングに従って、順次サンプリングパルスが出力される。

#### [0123]

シフトレジスタ1901より出力されたサンプリングパルスは、第1のラッチ回路19 02に入力される。第1のラッチ回路1902には、デジタル映像信号が入力されており、サンプリングパルスが入力されるタイミングに従って、各段でデジタル映像信号を保持していく。ここでは、デジタル映像信号は3ビット入力されており、各ビットの映像信号を、それぞれの第1のラッチ回路において保持する。1つのサンプリングパルスによって、ここでは3つの第1のラッチ回路が並行して動作する。

### [0124]

第1のラッチ回路1902において、最終段までデジタル映像信号の保持が完了すると、水平帰線期間中に、第2のラッチ回路1903にラッチパルス(Latch Pulse)が入力され、第1のラッチ回路1902に保持されていたデジタル映像信号は、一斉に第2のラッチ回路1903に転送される。その後、第2のラッチ回路1903に保持されたデジタル映像信号は、1行分が同時に、D/A変換回路1904へと入力される。

#### [ 0 1 2 5 ]

第2のラッチ回路1903に保持されたデジタル映像信号がD/A変換回路1904に 入力されている間、シフトレジスタ1901においては再びサンプリングパルスが出力される。以後、この動作を繰り返し、1フレーム分の映像信号の処理を行う。

#### [0126]

D / A 変換回路 1 9 0 4 においては、入力されるデジタル映像信号をデジタル・アナログ変換し、アナログ電圧を有する映像信号としてソース信号線に出力する。

# [0127]

前記の動作が、1水平期間内に、全段にわたって同時に行われる。よって、全てのソース信号線に映像信号が出力される。

#### [0128]

なお、実施例 1 においても述べたとおり、シフトレジスタの代わりにデコーダ等を用いて、信号線を選択出来るような構成としていても良い。

# 【実施例3】

#### [0129]

実施例 2 においては、デジタル映像信号は D / A 変換回路によってデジタル・アナログ変換を受け、画素に書き込まれるが、本発明の半導体装置は、時間階調方式によって階調表現を行うことも出来る。この場合には、図 1 9 (B)に示すように、D / A 変換回路を必要とせず、階調表現は、E L 素子の発光時間の長短によって制御されるので、各ビットの映像信号を並列処理する必要がないため、第 1 および第 2 のラッチ回路も 1 ビット分で良い。このとき、デジタル映像信号は、各ビットが直列に入力され、順次ラッチ回路に保持され、画素に書き込まれる。勿論、必要ビット数分だけのラッチ回路を並列配置していても構わない。

#### 【実施例4】

# [0130]

本明細書では、駆動回路と、スイッチング用TFT及び駆動用TFTを有する画素部とが同一基板上に形成された基板を便宜上アクティブマトリクス基板と呼ぶ。そして本実施

10

20

30

40

20

30

40

50

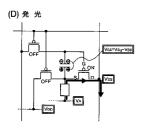

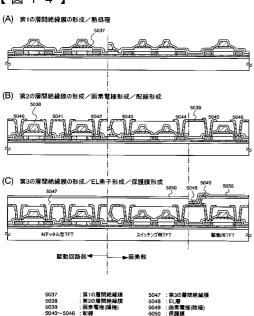

例では前記アクティブマトリクス基板を、単極性のTFTによって作製する工程について、図13、図14を用いて説明する。

# [0131]

基板 5 0 0 0 は、石英基板、シリコン基板、金属基板又はステンレス基板の表面に絶縁膜を形成したものを用いる。また本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いても良い。本実施例ではバリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス等のガラスからなる基板 5 0 0 0 を用いた。

#### [0132]

次いで、基板5000上に酸化珪素膜、窒化珪素膜又は酸化窒化珪素膜などの絶縁膜から成る下地膜5001を形成する。本実施例の下地膜5001は2層構造で形成したが、前記絶縁膜の単層構造又は前記絶縁膜を2層以上積層させた構造であっても良い。

#### [ 0 1 3 3 ]

# [0134]

続いて、下地膜5001上に半導体層5002~5005を形成する。半導体層5002~5005は公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)により25~80[nm](好ましくは30~60[nm])の厚さで半導体膜を成膜する。次いで前記半導体膜を公知の結晶化法(レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法等)を用いて結晶化させる。そして、得られた結晶質半導体膜を所望の形状にパターニングして半導体層5002~5005を形成する。なお前記半導体膜としては、非晶質半導体膜、微結晶半導体膜、結晶質半導体膜、又は非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体膜などを用いても良い。

### [0135]

本実施例では、プラズマCVD法を用いて、膜厚55[nm]の非晶質珪素膜を成膜した。そして、ニッケルを含む溶液を非晶質珪素膜上に保持させ、この非晶質珪素膜に脱水素化(500[ ]、1時間)を行った後、熱結晶化(550[ ]、4時間)を行って結晶質珪素膜を形成した。その後、フォトリソグラフィ法を用いたパターニング処理によって半導体層5002~5005を形成した。

# [0136]

なおレーザ結晶化法で結晶質半導体膜を作製する場合のレーザは、連続発振またはパルス発振の気体レーザ又は固体レーザを用いれば良い。前者の気体レーザとしては、エキシマレーザ、  $YAGVO_4V$ ーザ、 YLFVーザ、  $YAIO_3V$ ーザ、 ガラスレーザ、  $VAIO_4V$ ーザ、 VI0 (VI0 (

#### [0137]

また出力10[W]の連続発振のYVO₄レーザから射出されたレーザ光は、非線形光学

20

30

40

50

素子により高調波に変換する。さらに、共振器の中に  $Y V O_4$ 結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または楕円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は  $0.01\sim100$  [MW / cm²] 程度(好ましくは  $0.1\sim100$  [MW / cm²] 程度(好ましくは  $0.1\sim100$  [MW / cm²]) が必要である。そして、  $1.0\sim2000$  [cm / s] 程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射する。

#### [0138]

また上記のレーザを用いる場合には、レーザ発振器から放射されたレーザビームを光学系で線状に集光して、半導体膜に照射すると良い。結晶化の条件は適宜設定されるが、エキシマレーザを用いる場合はパルス発振周波数 3 0 0 [Hz]とし、レーザーエネルギー密度を 1 0 0 ~ 7 0 0 [mJ/cm²] (代表的には 2 0 0 ~ 3 0 0 [mJ/cm²]) とすると良い。また Y A G レーザを用いる場合には、その第 2 高調波を用いてパルス発振周波数 1 ~ 3 0 0 [Hz]とし、レーザーエネルギー密度を 3 0 0 ~ 1 0 0 0 [mJ/cm²] (代表的には 3 5 0 ~ 5 0 0 [mJ/cm²]) とすると良い。そして幅 1 0 0 ~ 1 0 0 0 [ $\mu$ m] (好ましくは幅 4 0 0 [ $\mu$ m]) で線状に集光したレーザ光を基板全面に渡って照射し、このときの線状ビームの重ね合わせ率(オーバーラップ率)を 5 0 ~ 9 8 [%]として行っても良い。

#### [0139]

しかしながら本実施例では、結晶化を助長する金属元素を用いて非晶質珪素膜の結晶化を行ったため、前記金属元素が結晶質珪素膜中に残留している。そのため、前記結晶質珪素膜上に50~100[nm]の非晶質珪素膜を形成し、加熱処理(RTA法やファーネスアニール炉を用いた熱アニール等)を行って、該非晶質珪素膜中に前記金属元素を拡散させ、前記非晶質珪素膜は加熱処理後にエッチングを行って除去する。その結果、前記結晶質珪素膜中の金属元素の含有量を低減または除去することができる。

#### [0140]

なお半導体層 5 0 0 2 ~ 5 0 0 5 を形成した後、TFTのしきい値を制御するために微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。

#### [0141]

次いで、半導体層 5 0 0 2 ~ 5 0 0 5 を覆うゲート絶縁膜 5 0 0 6 を形成する。ゲート絶縁膜 5 0 0 6 はプラズマ C V D 法やスパッタ法を用いて、膜厚を 4 0 ~ 1 5 0 [nm] として珪素を含む絶縁膜で形成する。本実施例では、ゲート絶縁膜 5 0 0 6 としてプラズマ C V D 法により酸化窒化珪素膜を 1 1 5 [nm] の厚さに形成した。勿論、ゲート絶縁膜 5 0 0 6 は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

### [0142]

なおゲート絶縁膜 5 0 0 6 として酸化珪素膜を用いる場合には、プラズマ C V D 法で T E O S (Tetraethyl Orthosilicate) と  $O_2$  とを混合し、反応圧力 4 0 [Pa]、基板温度 3 0 0 ~ 4 0 0 [ ] とし、高周波 (1 3 . 5 6 [MHz]) 電力密度 0 . 5 ~ 0 . 8 [W/cm²] で放電させて形成しても良い。上記の工程により作製される酸化珪素膜は、その後 4 0 0 ~ 5 0 0 [ ]の熱アニールによって、ゲート絶縁膜 5 0 0 6 として良好な特性を得ることができる

# [ 0 1 4 3 ]

次いで、ゲート絶縁膜 5 0 0 6 上に膜厚 2 0 ~ 1 0 0 [nm]の第 1 の導電膜 5 0 0 7 と、膜厚 1 0 0 ~ 4 0 0 [n]mの第 2 の導電膜 5 0 0 8 とを積層形成する。本実施例では、膜厚 3 0 [nm]の T a N 膜からなる第 1 の導電膜 5 0 0 7 と、膜厚 3 7 0 [nm]のW 膜からなる第 2 の導電膜 5 0 0 8 を積層形成した。

# [0144]

本実施例では、第1の導電膜5007であるTaN膜はスパッタ法で形成し、Taのターゲットを用いて、窒素を含む雰囲気内でスパッタ法で形成した。また第2の導電膜5008であるW膜は、Wのターゲットを用いたスパッタ法で形成した。その他に6フッ化タングステン(WF<sub>6</sub>)を用いる熱СVD法で形成することもできる。いずれにしてもゲート

20

30

40

50

電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20[μ cm]以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。従って、本実施例では、高純度のW(純度99.999[%])のターゲットを用いたスパッタ法で、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9~20[μ cm]を実現することができた。

[ 0 1 4 5 ]

なお本実施例では、第1の導電膜5007をTaN膜、第2の導電膜5008をW膜としたが、第1の導電膜5007及び第2の導電膜5008を構成する材料は特に限定されない。第1の導電膜5007及び第2の導電膜5008は、Ta、W、Ti、Mo、Al、Cu、Cr、Ndから選択された元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶珪素膜に代表される半導体膜やAgPdCu合金で形成してもよい。

[0146]

次いで、フォトリソグラフィ法を用いてレジストからなるマスク5009を形成し、電極及び配線を形成するための第1のエッチング処理を行う。第1のエッチング処理では第1及び第2のエッチング条件で行う。(図13(B))

[0147]

本実施例では第1のエッチング条件として、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF $_4$ とС $_1$ 2とO $_2$ とを用い、それぞれのガス流量比を25:25:10[sccm]とし、1.0[Pa]の圧力でコイル型の電極に500[W]のRF(13.56[MHz])電力を投入してプラズマを生成してエッチングを行った。基板側(試料ステージ)にも150[W]のRF(13.56[MHz])電力を投入し、実質的に負の自己バイアス電圧を印加した。そしてこの第1のエッチング条件によりW膜をエッチングして第1の導電層5007の端部をテーパー形状とした。

[0148]

続いて、レジストからなるマスク5009を除去せずに第2のエッチング条件に変更し、エッチング用ガスにCF $_4$ とС $_1$ 2とを用い、それぞれのガス流量比を30:30[sccm] とし、1.0[Pa]の圧力でコイル型の電極に500[W]のRF(13.56[MHz])電力を投入してプラズマを生成して15秒程度のエッチングを行った。基板側(試料ステージ)にも20[W]のRF(13.56[MHz])電力を投入し、実質的に負の自己バイアス電圧を印加した。第2のエッチング条件では第1の導電層5007及び第2の導電層5008とも同程度にエッチングを行った。なお、ゲート絶縁膜5006上に残渣を残すことなくエッチングするためには、10~20[%]程度の割合でエッチング時間を増加させると良い。【0149】

上記の第1のエッチング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層5007及び第2の導電層5008の端部がテーパー形状となる。こうして、第1のエッチング処理により第1の導電層5007と第2の導電層50008から成る第1の形状の導電層5010~5014を形成した。ゲート絶縁膜5006においては、第1の形状の導電層5010~5014で覆われない領域が20~50m程度エッチングされたため、膜厚が薄くなった領域が形成された。

[0150]

次いで、レジストからなるマスク5009を除去せずに第2のエッチング処理を行う。 (図13(C))第2のエッチング処理では、エッチングガスにSF $_6$ とС $_1$ 2とO $_2$ を用い、それぞれのガス流量比を24:12:24(sccm)とし、1.3Paの圧力でコイル側の電力に700WのRF(13.56MHz)電力を投入してプラズマを生成して25秒程度のエッチングを行った。基板側(試料ステージ)にも10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加した。こうして、W膜を選択的にエッチングして、第2の形状の導電層5015~5019を形成した。このとき、第1の導電層5015~5

018aは、ほとんどエッチングされない。

#### [0151]

そして、レジストからなるマスク5009を除去せずに第1のドーピング処理を行い、半導体層5002~5005にN型を付与する不純物元素を低濃度に添加する。第1のドーピング処理はイオンドープ法又はイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を1×10 $^{13}$ ~5×10 $^{14}$  [atoms/cm²]とし、加速電圧を40~80[keV]として行う。本実施例ではドーズ量を5.0×10 $^{13}$  [atoms/cm²]とし、加速電圧を50[keV]として行った。N型を付与する不純物元素としては、15族に属する元素を用いれば良く、代表的にはリン(P)又は砒素(As)を用いられるが、本実施例ではリン(P)を用いた。この場合、第2の形状の導電層5015~5019がN型を付与する不純物元素に対するマスクとなって、自己整合的に第1の不純物領域(N--領域)5020~5023を形成した。そして第1の不純物領域5020~5023には1×10 $^{18}$ ~1×10 $^{20}$  [atoms/cm³]の濃度範囲でN型を付与する不純物元素が添加された。

### [ 0 1 5 2 ]

続いてレジストからなるマスク 5 0 0 9 を除去した後、新たにレジストからなるマスク 5 0 2 4 を形成して、第 1 のドーピング処理よりも高い加速電圧で第 2 のドーピング処理を行う。イオンドープ法の条件はドーズ量を 1 × 1 0  $^{13}$  ~ 3 × 1 0  $^{15}$  [atoms/cm²]とし、加速電圧を 6 0 ~ 1 2 0 [keV]として行う。本実施例では、ドーズ量を 3 . 0 × 1 0  $^{15}$  [atoms/cm²]とし、加速電圧を 6 5 [keV]として行った。第 2 のドーピング処理は第 2 の導電層 5 0 1 5 b ~ 5 0 1 8 b を不純物元素に対するマスクとして用い、第 1 の導電層 5 0 1 5 a ~ 5 0 1 8 a のテーパー部の下方の半導体層に不純物元素が添加されるようにドーピングを行う。

# [0153]

上記の第 2 のドーピング処理を行った結果、第 1 の導電層と重なる第 2 の不純物領域(N - 領域、Lov領域) 5 0 2 6 、 5 0 2 9 には 1 × 1 0  $^{18}$  ~ 5 × 1 0  $^{19}$  [atoms/cm³] の濃度範囲でN型を付与する不純物元素が添加された。また第 3 の不純物領域(N + 領域) 5 0 2 5 、 5 0 2 8 、 5 0 3 1 、 5 0 3 4 には 1 × 1 0  $^{19}$  ~ 5 × 1 0  $^{21}$  [atoms/cm³] の濃度範囲でN型を付与する不純物元素が添加された。また、第 1 、第 2 のドーピング処理を行った後、半導体層 5 0 0 2 ~ 5 0 0 5 において、不純物元素が全く添加されない領域又は微量の不純物元素が添加された領域が形成された。本実施例では、不純物元素が全く添加されない領域又は微量の不純物元素が添加された領域をチャネル領域 5 0 2 7 、 5 0 3 0 、 5 0 3 3 、 5 0 3 6 とよぶ。また前記第 1 のドーピング処理により形成された第 1 の不純物領域(N - - 領域) 5 0 2 0 ~ 5 0 2 3 のうち、第 2 のドーピング処理においてレジスト 5 0 2 4 で覆われていた領域が存在するが、本実施例では、引き続き第 1 の不純物領域(N - - 領域、LDD領域) 5 0 3 2 、 5 0 3 5 とよぶ。

#### [0154]

なお本実施例では、第2のドーピング処理のみにより、第2の不純物領域(N-領域)5026、5029及び第3の不純物領域(N+領域)5025、5028、5031、5034を形成したが、これに限定されない。ドーピング処理を行う条件を適宜変えて、複数回のドーピング処理で形成しても良い。

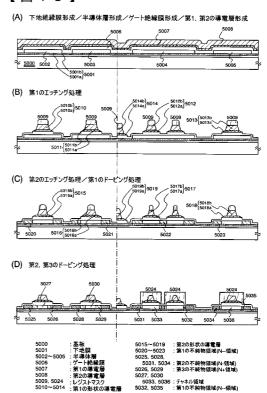

# [0155]

次いで図14(A)に示すように、レジストからなるマスク5024を除去して第1の層間絶縁膜5037を形成する。この第1の層間絶縁膜5037としては、プラズマCVD法またはスパッタ法を用い、厚さを100~200[nm]として珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚100[nm]の酸化窒化珪素膜を形成した。勿論、第1の層間絶縁膜5037は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

### [0156]

次いで、加熱処理(熱処理)を行って、半導体層の結晶性の回復、半導体層に添加された不純物元素の活性化を行う。この加熱処理はファーネスアニール炉を用いる熱アニール法

10

20

30

40

で行う。熱アニール法としては、酸素濃度が1[ppm]以下、好ましくは0.1[ppm]以下の窒素雰囲気中で400~700[ ]で行えばよく、本実施例では410[ ]、1時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。

### [ 0 1 5 7 ]

また、第1の層間絶縁膜5037を形成する前に加熱処理を行っても良い。ただし、第1の導電層5015a~5019a及び、第2の導電層5015b~5019bを構成する材料が熱に弱い場合には、本実施例のように配線等を保護するため第1の層間絶縁膜5037(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後で熱処理を行うことが好ましい。

[0158]

上記の様に、第1の層間絶縁膜5037(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後に熱処理することにより、活性化処理と同時に、半導体層の水素化も行うことができる。水素化の工程では、第1の層間絶縁膜5037に含まれる水素により半導体層のダングリングボンドが終端される。

[0159]

なお、活性化処理のための加熱処理とは別に、水素化のための加熱処理を行っても良い 、

[0160]

ここで、第 1 の層間絶縁膜 5 0 3 7 の存在に関係なく、半導体層を水素化することもできる。水素化の他の手段として、プラズマにより励起された水素を用いる手段(プラズマ水素化)や、 3 ~ 1 0 0 [%]の水素を含む雰囲気中において、 3 0 0 ~ 4 5 0 [ ]で 1 ~ 1 2 時間の加熱処理を行う手段でも良い。

[0161]

次いで、第1の層間絶縁膜5037上に、第2の層間絶縁膜5038を形成する。第2の層間絶縁膜5038としては、無機絶縁膜を用いることができる。例えば、CVD法によって形成された酸化珪素膜や、SOG(Spin On Glass)法によって塗布された酸化珪素膜等を用いることができる。また、第2の層間絶縁膜5038として、有機絶縁膜を用いることができる。例えば、ポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アクリル等の膜を用いることができる。

また、アクリル膜と酸化窒化珪素膜の積層構造を用いても良い。

[0162]

本実施例では、膜厚1.6 [µm]のアクリル膜を形成した。第2の層間絶縁膜5038によって、基板上5000に形成されたTFTによる凹凸を緩和し、平坦化することができる。特に、第2の層間絶縁膜5038は平坦化の意味合いが強いので、平坦性に優れた膜が好ましい。

[0163]

次いで、ドライエッチングまたはウエットエッチングを用い、第 2 の層間絶縁膜 5 0 3 8、第 1 の層間絶縁膜 5 0 3 7、およびゲート絶縁膜 5 0 0 6 をエッチングし、不純物領域 5 0 2 5 、 5 0 2 8 、 5 0 3 1 、 5 0 3 4 に達するコンタクトホールを形成する。

[0164]

次いで、透明導電膜からなる画素電極 5 0 3 9 を形成する。透明導電膜としては、酸化インジウムと酸化スズの化合物(Indium Tin Oxide: I T O)、酸化インジウムと酸化亜鉛の化合物、酸化亜鉛、酸化スズ、酸化インジウム等を用いることができる。また、前記透明導電膜にガリウムを添加したものを用いてもよい。

画素電極がEL素子の陽極に相当する。

[0165]

本実施例では、ITOを110[nm]厚さで成膜、その後パターニングし、画素電極50 39を形成した。

[0166]

10

20

30

40

20

30

40

50

次いで、各不純物領域とそれぞれ電気的に接続される配線 5 0 4 0 ~ 5 0 4 6 を形成する。なお本実施例では、配線 5 0 4 0 ~ 5 0 4 6 は、膜厚 1 0 0 [nm]の T i 膜と、膜厚 3 5 0 [nm]の A 1 膜と、膜厚 1 0 0 [nm]の T i 膜との積層膜をスパッタ法で連続形成し、所望の形状にパターニングして形成する。

### [0167]

もちろん、三層構造に限らず、単層構造あるいは二層構造でもよいし、四層以上の積層構造にしてもよい。また配線の材料としては、AlとTiに限らず、他の導電膜を用いても良い。例えば、TaN膜上にAlやCuを形成し、さらにTi膜を形成した積層膜をパターニングして配線を形成してもよい。

# [0168]

ここで、画素電極 5 0 3 9 上の一部と、配線 5 0 4 5 の一部を重ねて形成することによって、配線 5 0 4 5 と画素電極 5 0 3 9 の電気的接続をとっている(図 1 4 (B))。

# [0169]

以上の工程により図14(B)に示すように、Nチャネル型TFTを有する駆動回路部と、スイッチング用TFT、駆動用TFTとを有する画素部を同一基板上に形成することができる。

#### [0170]

駆動回路部のNチャネル型TFTは、ゲート電極の一部を構成する第1の導電層5015aと重なる低濃度不純物領域5026(Lov領域)、ソース領域またはドレイン領域として機能する高濃度不純物領域5025とを有している。

#### [0171]

画素部において、Nチャネル型のスイッチング用TFTは、ゲート電極の外側に形成される低濃度不純物領域 5 0 3 2 (Loff領域)、ソース領域またはドレイン領域として機能する高濃度不純物領域 5 0 3 1 とを有している。

# [0172]

次いで、第3の層間絶縁膜5047を形成する。第3の層間絶縁膜5047としては、無機絶縁膜や有機絶縁膜を用いることができる。無機絶縁膜としては、CVD法によって形成された酸化珪素膜や、SOG(Spin On Glass)法によって塗布された酸化珪素膜、あるいは、スパッタ法によって形成された窒化酸化珪素膜等を用いることができる。また、有機絶縁膜としては、アクリル樹脂膜等を用いることができる。

#### [0173]

第 2 の層間絶縁膜 5 0 3 8 と第 3 の層間絶縁膜 5 0 4 7 の組み合わせの例を以下に挙げる。

#### [0174]

第2の層間絶縁膜5038として、アクリルとスパッタ法によって形成された窒化酸化珪素膜の積層膜を用い、第3の層間絶縁膜5047として、スパッタ法によって形成して形成した窒化酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁膜5047としてもSOG法によって形成した酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁度5047として、SOG法によって形成した酸化珪素膜とプラズマCVD法によりた酸化珪素膜の積層膜を用いる組み合わせがある。また、第2の層間絶縁膜5047としてプラズマCVD法によてで、アクリルを用いる組み合わせがある。また、第2の層間絶縁膜5047としてプラズマCVD法によってある。また、第2の層間絶縁膜5038として、アクリルとプラズマCVD法によってある。また、第2の層間絶縁膜5047としてアクリルを用いる組み合わせがある。また、第3の層間絶縁膜5047としてアクリルを用いる組み合わせがある。

#### [0175]

第3の層間絶縁膜5047の画素電極5039に対応する位置に開口部を形成する。第

3の層間絶縁膜は、バンクとして機能する。開口部を形成する際、ウエットエッチング法を用いることで容易にテーパー形状の側壁とすることが出来る。開口部の側壁が十分になだらかでないと段差に起因する EL層の劣化が顕著な問題となってしまうため、注意が必要である。

# [0176]

第 3 の層間絶縁膜 5 0 4 7 中に、カーボン粒子や金属粒子を添加し、抵抗率を下げ、静電気の発生を抑制してもよい。この際、抵抗率は、 $1 \times 1 0^6 \sim 1 \times 1 0^{12}$ [ m](好ましくは、 $1 \times 1 0^8 \sim 1 \times 1 0^{10}$ [ m])となるように、カーボン粒子や金属粒子の添加量を調節すればよい。

#### [0177]

次いで、第3の層間絶縁膜5047の開口部において露出している画素電極5039上に、EL層5048を形成する。

#### [0178]

EL層5048としては、公知の有機発光材料や無機発光材料を用いることができる。

#### [0179]

有機発光材料としては、低分子系有機発光材料、高分子系有機発光材料、中分子系有機材料を自由に用いることができる。なお、本明細書中においては、中分子系有機発光材料とは、昇華性を有さず、かつ、分子数が20以下または連鎖する分子の長さが10[µm]以下の有機発光材料を示すものとする。

# [0180]

EL層5048は通常、積層構造である。代表的には、コダック・イーストマン・カンパニーのTangらが提案した「正孔輸送層/発光層/電子輸送層」という積層構造が挙げられる。また他にも、陽極上に正孔注入層/正孔輸送層/発光層/電子輸送層、または正孔注入層/正孔輸送層/発光層/電子輸送層/電子注入層の順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。

#### [0181]

本実施例では蒸着法により低分子系有機発光材料を用いてEL層 5 0 4 8 を形成している。具体的には、正孔注入層として 2 0 [nm]厚の銅フタロシアニン(C u P c )膜を設け、その上に発光層として 7 0 [nm]厚のトリス - 8 - キノリノラトアルミニウム錯体(A 1 q  $_3$ )膜を設けた積層構造としている。 A 1 q  $_3$ にキナクリドン、ペリレンもしくは D C M 1 といった蛍光色素を添加することで発光色を制御することができる。

# [0182]

なお、図 1 4 ( C ) では一画素しか図示していないが、複数の色、例えば、 R (赤)、 G (緑)、 B (青) の各色に対応した E L 層 5 0 4 8 を作り分ける構成とすることができる。

# [0183]

また、高分子系有機発光材料を用いる例として、正孔注入層として 2 0 [nm]のポリチオフェン(PEDOT)膜をスピン塗布法により設け、その上に発光層として 1 0 0 [nm]程度のパラフェニレンビニレン(PPV)膜を設けた積層構造によって EL層 5 0 4 8 を構成しても良い。なお、PPVの 共役系高分子を用いると、赤色から青色まで発光波長を選択できる。また、電子輸送層や電子注入層として炭化珪素等の無機材料を用いることも可能である。

#### [0184]

なお、EL層5048は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等が、明確に区別された積層構造を有するものに限定されない。つまり、EL層5048は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等を構成する材料が、混合した層を有する構造であってもよい。

#### [0185]

例えば、電子輸送層を構成する材料(以下、電子輸送材料と表記する)と、発光層を構成する材料(以下、発光材料と表記する)とによって構成される混合層を、電子輸送層と発光層との間に有する構造の EL層 5048であってもよい。

10

20

30

40

20

30

40

50

#### [0186]

次に、EL層5048の上には導電膜からなる画素電極5049が設けられる。本実施例の場合、導電膜としてアルミニウムとリチウムとの合金膜を用いる。

勿論、公知のMgAg膜(マグネシウムと銀との合金膜)を用いても良い。画素電極5049がEL素子の陰極に相当する。陰極材料としては、周期表の1族もしくは2族に属する元素からなる導電膜もしくはそれらの元素を添加した導電膜を自由に用いることができる

# [0187]

画素電極 5 0 4 9 まで形成された時点でEL素子が完成する。なお、EL素子とは、画素電極 (陽極) 5 0 3 9 、EL層 5 0 4 8 及び画素電極 (陰極) 5 0 4 9 で形成された素子を指す。

[ 0 1 8 8 ]

EL素子を完全に覆うようにしてパッシベーション膜5050を設けることは有効である。パッシベーション膜5050としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いることができる

[0189]

カバレッジの良い膜をパッシベーション膜 5 0 5 0 として用いることが好ましく、炭素膜、特に D L C (ダイヤモンドライクカーボン)膜や C N 膜を用いることは有効である。 D L C 膜は室温から 1 0 0 [ ]以下の温度範囲で成膜可能であるため、耐熱性の低い E L 層 5 0 4 7 の上方にも容易に成膜することができる。また、 D L C 膜は酸素に対するブロッキング効果が高く、 E L 層 5 0 4 8 の酸化を抑制することが可能である。

[0190]

なお、第3の層間絶縁膜5047を形成した後、パッシベーション膜5050を形成するまでの工程をマルチチャンバー方式(またはインライン方式)の成膜装置を用いて、大気解放せずに連続的に処理することは有効である。

[0191]

なお、実際には図14(C)の状態まで完成したら、さらに外気に曝されないように、気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)や透光性のシーリング材でパッケージング(封入)することが好ましい。その際、シーリング材の内部を不活性雰囲気にしたり、内部に吸湿性材料(例えば酸化バリウム)を配置したりするとEL素子の信頼性が向上する。

[0192]

また、パッケージング等の処理により気密性を高めたら、基板 5 0 0 0 上に形成された素子又は回路から引き回された端子と外部信号端子とを接続するためのコネクタ(フレキシブルプリントサーキット:FPC)を取り付けて製品として完成する。

[0193]

また、本実施例で示す工程に従えば、発光装置の作製に必要なフォトマスクの数を抑えることが出来る。その結果、工程を短縮し、製造コストの低減及び歩留まりの向上に寄与することが出来る。

【実施例5】

[0194]

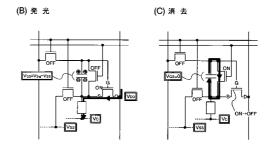

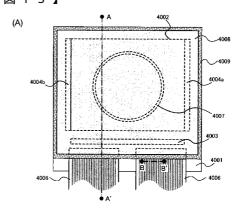

本実施例では、本発明を用いて発光装置を作製した例について、図15を用いて説明する。

[0195]

図15は、TFTが形成された素子基板をシーリング材によって封止することによって 形成された発光装置の上面図であり、図15(B)は、図15(A)のA・A′における断面 図、図15(C)は図15(A)のB・B′における断面図である。

[0196]

基板4001上に設けられた画素部4002と、ソース信号線駆動回路4003と、第

20

30

40

50

1 及び第 2 のゲート信号線駆動回路 4 0 0 4 a、 4 0 0 4 bとを囲むようにして、シール材 4 0 0 9 が設けられている。また画素部 4 0 0 2 と、ソース信号線駆動回路 4 0 0 3 と、第 1 及び第 2 のゲート信号線駆動回路 4 0 0 4 a、 4 0 0 4 bとの上にシーリング材 4 0 0 8 が設けられている。よって画素部 4 0 0 2 と、ソース信号線駆動回路 4 0 0 3 と、第 1 及び第 2 のゲート信号線駆動回路 4 0 0 4 a、 4 0 0 4 bとは、基板 4 0 0 1 とシール材 4 0 0 9 とシーリング材 4 0 0 8 とによって、充填材 4 2 1 0 で密封されている。

[0197]

また基板 4 0 0 1 上に設けられた画素部 4 0 0 2 と、ソース信号線駆動回路 4 0 0 3 と、第 1 及び第 2 のゲート信号線駆動回路 4 0 0 4 a、 4 0 0 4 b とは、複数のTFTを有している。図 1 5 (B)では代表的に、下地膜 4 0 1 0 上に形成された、ソース信号線駆動回路 4 0 0 3 に含まれるTFT(但し、ここではNチャネル型TFTとPチャネル型TFTを図示する) 4 2 0 1 及び画素部 4 0 0 2 に含まれるTFT 4 2 0 2 を図示した。

[0198]

TFT4201及び4202上には層間絶縁膜(平坦化膜) 4301が形成され、その上にTFT4202のドレインと電気的に接続する画素電極(陽極) 4203が形成される。画素電極4203としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化 亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したものを用いても良い。

[0199]

そして、画素電極 4 2 0 3 の上には絶縁膜 4 3 0 2 が形成され、絶縁膜 4 3 0 2 は画素電極 4 2 0 3 の上に開口部が形成されている。この開口部において、画素電極 4 2 0 3 の上には有機発光層 4 2 0 4 が形成される。有機発光層 4 2 0 4 は公知の有機発光材料または無機発光材料を用いることができる。また、有機発光材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

[0200]

有機発光層4204の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。 また、有機発光層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入 層を自由に組み合わせて積層構造または単層構造とすれば良い。

[0201]

有機発光層4204の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極4205が形成される。また、陰極4205と有機発光層4204の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、有機発光層4204を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極4205を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。そして陰極4205は所定の電圧が与えられている。

[0202]

以上のようにして、画素電極(陽極) 4 2 0 3 、有機発光層 4 2 0 4 及び陰極 4 2 0 5 からなる発光素子 4 3 0 3 が形成される。そして発光素子 4 3 0 3 を覆うように、絶縁膜 4 3 0 2 上に保護膜 4 3 0 3 が形成されている。保護膜 4 3 0 3 は、発光素子 4 3 0 3 に酸素や水分等が入り込むのを防ぐのに効果的である。

[ 0 2 0 3 ]

4 0 0 5 a は電源線に接続された引き回し配線であり、TFT420 2 の第 1 の電極に接続されている。引き回し配線 4 0 0 5 a はシール材 4 0 0 9 と基板 4 0 0 1 との間を通り、異方導電性フィルム 4 3 0 0 を介してFPC 4 0 0 6 が有するFPC用配線 4 3 0 1 に電気的に接続される。

[ 0 2 0 4 ]

シーリング材4008としては、ガラス材、金属材(代表的にはステンレス材)、セラミ

ックス材、プラスチック材(プラスチックフィルムも含む)を用いることができる。プラスチック材としては、FRP(Fiberglass Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

# [0205]

但し、発光素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

#### [0206]

また、充填材 4 2 1 0 としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、 P V C (ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコン樹脂、 P V B (ポリビニルブチラル)または E V A (エチレンビニルアセテート)を用いることができる。

本実施例では充填材として窒素を用いた。

#### [0207]

また充填材4210を吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる物質にさらしておくために、シーリング材4008の基板4001側の面に凹部4007を設けて吸湿性物質または酸素を吸着しうる物質4207を配置する。そして、吸湿性物質または酸素を吸着しうる物質4207は凹部4007に保持されている。なお凹部カバー材4208は目の細かいメッシュ状になっており、空気や水分は通し、吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質4207を設けることで、発光素子4303の劣化を抑制できる。

# [0208]

図 1 5 (C)に示すように、画素電極 4 2 0 3 が形成されると同時に、引き回し配線 4 0 0 5 a 上に接するように導電性膜 4 2 0 3 a が形成される。

#### [0209]

また、異方導電性フィルム 4 3 0 0 は導電性フィラー 4 3 0 0 a を有している。基板 4 0 0 1 と F P C 4 0 0 6 とを熱圧着することで、基板 4 0 0 1 上の導電性膜 4 2 0 3 a と F P C 4 0 0 6 上の F P C 用配線 4 3 0 1 とが、導電性フィラー 4 3 0 0 a によって電気的に接続される。

### 【実施例6】

# [0210]

本発明において、三重項励起子からの燐光を発光に利用できる有機発光材料を用いることで、外部発光量子効率を飛躍的に向上させることができる。これにより、発光素子の低消費電力化、長寿命化、および軽量化が可能になる。

# [0211]

ここで、三重項励起子を利用し、外部発光量子効率を向上させた報告を示す。

(T.Tsutsui, C.Adachi, S.Saito, Photochemical Processes in Organized Molecular Systems, ed.K.Honda, (Elsevier Sci.Pub., Tokyo,1991) p.437.)

#### [0212]

上記の論文により報告された有機発光材料(クマリン色素)の分子式を以下に示す。

# [ 0 2 1 3 ]

20

10

30

# 【化1】

# [0214]

10

(M.A.Baldo, D.F.O'Brien, Y.You, A.Shoustikov, S.Sibley, M.E.Thompson, S.R.For rest, Nature 395 (1998) p.151.)

# [0215]

上記の論文により報告された有機発光材料(Pt錯体)の分子式を以下に示す。

# [0216]

# 【化2】

$$\begin{array}{c|c} Et & Et \\ \hline \\ N & N \\ \hline \\ Et & Et \\ \hline \\ Et & Et \\ \end{array}$$

# [0217]

30

(M.A.Baldo, S.Lamansky, P.E.Burrrows, M.E.Thompson, S.R.Forrest, Appl.Phys.Let t.,75 (1999) p.4.) (T.Tsutsui, M.-J.Yang, M.Yahiro, K.Nakamura, T.Watanabe, T.ts uji, Y.Fukuda, T.Wakimoto, S.Mayaguchi, Jpn.Appl.Phys., 38 (12B) (1999) L1502.)

# [0218]

上記の論文により報告された有機発光材料(Ir錯体)の分子式を以下に示す。

# [0219]

# 【化3】

# 40

# [0220]

以上のように三重項励起子からの燐光発光を利用できれば原理的には一重項励起子から

の蛍光発光を用いる場合より3~4倍の高い外部発光量子効率の実現が可能となる。

#### 【実施例7】

# [0221]

発光素子を用いた発光装置は自発光型であるため、液晶ディスプレイに比べ、明るい場所での視認性に優れ、視野角が広い。従って、様々な電子機器の表示部に用いることができる。

#### [0222]

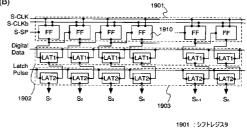

本発明の発光装置を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。特に、斜め方向から画面を見る機会が多い携帯情報端末は、視野角の広さが重要視されるため、発光装置を用いることが望ましい。それら電子機器の具体例を図20に示す。

#### [0223]

図20(A)は発光素子表示装置であり、筐体3001、支持台3002、表示部3003、スピーカー部3004、ビデオ入力端子3005等を含む。本発明の発光装置は表示部3003に用いることができる。発光装置は自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示部とすることができる。なお、発光素子表示装置は、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる

# [0224]

図 2 0 ( B ) はデジタルスチルカメラであり、本体 3 1 0 1 、表示部 3 1 0 2 、受像部 3 1 0 3 、操作キー 3 1 0 4 、外部接続ポート 3 1 0 5 、シャッター 3 1 0 6 等を含む。本発明の発光装置は表示部 3 1 0 2 に用いることができる。

#### [0225]

図 2 0 ( C ) はノート型パーソナルコンピュータであり、本体 3 2 0 1 、筐体 3 2 0 2 、表示部 3 2 0 3 、キーボード 3 2 0 4 、外部接続ポート 3 2 0 5 、ポインティングマウス 3 2 0 6 等を含む。本発明の発光装置は表示部 3 2 0 3 に用いることができる。

#### [0226]

図 2 0 (D)はモバイルコンピュータであり、本体 3 3 0 1 、表示部 3 3 0 2 、スイッチ 3 3 0 3 、操作キー 3 3 0 4 、赤外線ポート 3 3 0 5 等を含む。本発明の発光装置は表示部 3 3 0 2 に用いることができる。

# [0227]

図20(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体3401、筐体3402、表示部A3403、表示部B3404、記録媒体(DVD等)読込部3405、操作キー3406、スピーカー部3407等を含む。表示部A3403は主として画像情報を表示し、表示部B3404は主として文字情報を表示するが、本発明の発光装置はこれら表示部A、B3403、3404に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

#### [ 0 2 2 8 ]

図 2 0 (F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体 3 5 0 1 、表示部 3 5 0 2 、アーム部 3 5 0 3 を含む。本発明の発光装置は表示部 3 5 0 2 に用いることができる。

# [0229]

図 2 0 (G)はビデオカメラであり、本体 3 6 0 1 、表示部 3 6 0 2 、筐体 3 6 0 3 、外部接続ポート 3 6 0 4 、リモコン受信部 3 6 0 5 、受像部 3 6 0 6 、バッテリー 3 6 0 7 、音声入力部 3 6 0 8 、操作キー 3 6 0 9 等を含む。本発明の発光装置は表示部 3 6 0 2 に用いることができる。

10

20

30

#### [0230]

図20(H)は携帯電話であり、本体3701、筐体3702、表示部3703、音声入力部3704、音声出力部3705、操作キー3706、外部接続ポート3707、アンテナ3708等を含む。本発明の発光装置は表示部3703に用いることができる。なお、表示部3703は黒色の背景に白色の文字を表示することで携帯電話の消費電流を抑えることができる。

#### [0231]

なお、将来的に有機発光材料の発光輝度が高くなれば、出力した画像情報を含む光をレンズ等で拡大投影してフロント型若しくはリア型のプロジェクターに用いることも可能となる。

[0232]

また、上記電子機器はインターネットやCATV(ケーブルテレビ)などの電子通信回線を通じて配信された情報を表示することが多くなり、特に動画情報を表示する機会が増してきている。有機発光材料の応答速度は非常に高いため、発光装置は動画表示に好ましい

#### [0233]

また、発光装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。従って、携帯情報端末、特に携帯電話や音響再生装置のような文字情報を主とする表示部に発光装置を用いる場合には、非発光部分を背景として文字情報を発光部分で形成するように駆動することが望ましい。

[0234]

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また、本実施例の電子機器は実施例 1 ~ 6 に示したいずれの構成の発光装置を用いても良い。

#### 【実施例8】

#### [0235]

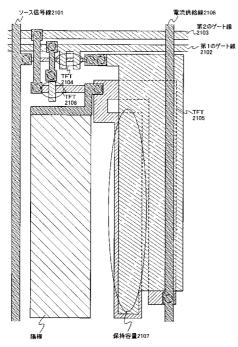

本実施例では、図21に示す画素構成の上面図を、図22を用いて説明する。

#### [0236]

図22には、TFTを形成する領域に同一層(同一レイヤ)をパターニングして複数の活性層が設けられ、次に第1のゲート線2102、第2のゲート線2103、各トランジスタのゲート電極とが同一層(同一レイヤ)をパターニングして設けられ、その後ソース信号線2101、電流供給線2108とが同一層(同一レイヤ)をパターニングして設けられ、最後にEL素子(発光素子)の第1の電極(ここでは陽極とする)が設けられている。

# [ 0 2 3 7 ]

そして、第1のゲート線2102の一部がゲート電極となる選択用のTFT2104が設けられている。TFT2104は、一つの活性層にゲート電極が二つ設けられたダブルゲート構造とすることで、一つの活性層に一つのゲート電極が設けられたシングルゲート構造と比べて選択(スイッチング)を確実に行うことができる。また、TFT2104は一つの活性層にゲート電極が三つ以上設けられたマルチゲート構造とすることも可能である。

[ 0 2 3 8 ]

また、TFTのバラツキを低減するためにTFT2105のチャネル長(L)が大きくなるよう設けている。更に、Lを大きくすることにより、TFTの飽和領域を平らにすることができる。

# [0239]

また、第2のゲート線2103にコンタクトを介して接続されるゲート電極を有するTFT2106が設けられている。また、活性層と、走査線と同一の層とで形成された保持容量2107が設けられている。

### [0240]

20

10

30

このような各TFTの構成は、ゲート電極が半導体膜(チャネル形成領域) の上にあるトップゲート型構造やその逆のボトムゲート型構造を用い、不純物領域(ソース領域又はドレイン領域)にはオフセット構造やGOLD構造を用いればよい。

# 【図3】

# (A) 映像信号入力

(B) 映像信号入力終了時

(C) 発 光

【図4】

【図5】

(A)

(B) 発 光

【図6】

# 【図7】

# 【図8】

【図9】

# 【図10】

# 【図11】

# 【図12】

# 【図13】

【図14】

【図15】

# 【図16】

# 【図17】

# 【図18】

# 【図19】

1901: シフトレジスタ 1902:第1のラッチ回路 1903:第2のラッチ回路 1904:D/A変換回路 1910:フリップフロップ

# 【図20】

# 【図21】

# 【図22】

#### 【手続補正書】

【提出日】平成25年6月14日(2013.6.14)

【手続補正2】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

第1乃至第4のトランジスタと、第1の容量素子と、前記第1のトランジスタのソース 又はドレインの一方と電気的に接続された第1の発光素子と、を有し、

前記第1のトランジスタは、前記第1の発光素子に電流を供給することができる機能を 有し、

前記第2のトランジスタは、前記第1のトランジスタのゲートに映像信号を供給することができる機能を有し、

<u>前記第3のトランジスタは、前記第1のトランジスタのソース又はドレインの一方に第</u> 1の電位を供給することができる機能を有し、

前記第4のトランジスタは、ソース又はドレインが前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、且つゲートが前記第3のトランジスタのゲートと電気的に絶縁されており、

前記容量素子は、第1の電極が前記第1のトランジスタのゲートと電気的に接続され、 且つ第2の電極が前記第1のトランジスタのソース又はドレインの一方と電気的に接続されていることを特徴とする表示装置。

#### 【請求項2】

第1乃至第4のトランジスタと、第1の容量素子と、前記第1のトランジスタのソース 又はドレインの一方と電気的に接続された第1の発光素子と、を有し、

前記第1のトランジスタは、前記第1の発光素子に電流を供給することができる機能を 有し、

<u>前記第2のトランジスタは、前記第1のトランジスタのゲートに映像信号を供給することができる機能を有し、</u>

<u>前記第3のトランジスタは、前記第1のトランジスタのソース又はドレインの一方に第</u>1の電位を供給することができる機能を有し、

前記第4のトランジスタは、ソース又はドレインが前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、且つゲートが前記第3のトランジスタのゲートと電気的に絶縁されており、

前記容量素子は、前記第1のトランジスタのゲートと前記第1のトランジスタのソース 又はドレインの一方との間の電圧を保持することができる機能を有することを特徴とする 表示装置。

# 【請求項3】

請求項1又は請求項2において、

前記第2のトランジスタのゲート又は前記第3のトランジスタのゲートは、第5のトランジスタのソース又はドレインの一方と電気的に接続されており、

前記第 5 のトランジスタのソース又はドレインの他方は、第 2 の発光素子と電気的に接続されていることを特徴とする表示装置。

#### 【請求項4】

請求項1乃至請求項3のいずれか一項に記載の表示装置と、 FPCと、を有することを特徴とするモジュール。

#### 【請求項5】

請求項4に記載のモジュールと、

操作キーと、を有することを特徴とする電子機器。

# フロントページの続き

(51) Int.CI. F I テーマコード (参考)

H 0 5 B 33/14 A

F 夕一厶(参考) 5C380 AA01 AB06 AB12 AB18 AB22 AB23 AB24 AB25 AB34 BA12 BA36 BD02 BD07 BD08 BD09 CA02 CA04 CA05 CA08 CA12 CA23 CA24 CA32 CA49 CA57 CB01 CB26 CC02 CC26 CC27 CC30 CC30 CC33 CC38 CC39 CC55 CC62 CC63 CC77 CD012 CD013 CD014 CF07 CF09 CF10 CF22 CF24 CF48 CF64 CF70 DA02

DA06 DA09 DA47

| 专利名称(译)        | 显示设备,模块和电子设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号        | JP2013238861A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2013-11-28 |  |  |  |

| 申请号            | JP2013125579                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2013-06-14 |  |  |  |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |  |  |  |

| 申请(专利权)人(译)    | 半导体能源研究所有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |  |  |  |

| [标]发明人         | 木村肇                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |  |  |  |

| 发明人            | 木村 肇                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |  |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 G09G3/32 H01L27/32 H04M1/73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |  |  |  |

| CPC分类号         | G09G3/2022 G09G3/3233 G09G3/3266 G09G3/3291 G09G2300/0426 G09G2300/0842 G09G2310 /0251 G09G2310/0256 G09G2310/027 G09G2310/061 G09G2320/043 G09G2330/08 G09G2330/10 H01L27/3244 H04W52/027 Y02D70/00 H01L27/1255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.611.H G09G3/20.670.J G09G3/20.641.D H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |  |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/BB06 3K107/BB08 3K107/CC33 3K107/CC45 3K107/EE03 3K107 /EE57 3K107/EE61 3K107/HH02 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD18 5C080/DD23 5C080/DD29 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/AB12 5C380/AB18 5C380/AB22 5C380/AB23 5C380/AB24 5C380/AB25 5C380 /AB34 5C380/BA12 5C380/BA36 5C380/BD02 5C380/BD07 5C380/BD08 5C380/BD09 5C380/CA02 5C380/CA04 5C380/CA05 5C380/CA08 5C380/CA12 5C380/CA23 5C380/CA24 5C380/CA32 5C380 /CA49 5C380/CA57 5C380/CB01 5C380/CB26 5C380/CC02 5C380/CC26 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC38 5C380/CC39 5C380/CC55 5C380/CC62 5C380/CC63 5C380/CC77 5C380 /CD012 5C380/CD013 5C380/CD014 5C380/CF07 5C380/CF09 5C380/CF10 5C380/CF22 5C380 /CF24 5C380/CF48 5C380/CF64 5C380/CF70 5C380/DA02 5C380/DA06 5C380/DA09 5C380/DA47 |         |            |  |  |  |

| 优先权            | 2001348032 2001-11-13 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

| 其他公开文献         | JP5648088B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |

# 摘要(译)

本发明提供一种显示装置及其驱动方法,其不太可能引起发光元件的特性变化和由于劣化导致的电流值的变化。 发光元件包括晶体管,电容元件,发光元件,源信号线101和电流供应线107.发光元件根据由晶体管确定的电流值以亮度发光。在驱动显示装置的方法中,向晶体管的源极输入第一电位的操作,从源信号线向晶体管的栅极输入视频信号的操作,以及第一电位以及保持根据电容元件中的视频信号确定的电位差,并将晶体管的源极的电位改变为第二电位的操作。为了保持晶体管的栅极-源极电压,即使晶体管的第一电极的电位改变,电容元件也通过保持栅极-源极电压恒定来保持电流值恒定。 [选图]图1