(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-48186

(P2012-48186A)

(43) 公開日 平成24年3月8日(2012.3.8)

| (51) Int.Cl.                   | F 1                          | テーマコード (参考)                                                                          |

|--------------------------------|------------------------------|--------------------------------------------------------------------------------------|

| <b>G09G 3/30</b> (2006.01)     | G09G 3/30                    | J 5C080                                                                              |

| <b>G09G 3/20</b> (2006.01)     | G09G 3/20                    | 622E 5C380                                                                           |

|                                | G09G 3/20                    | 622R                                                                                 |

|                                | G09G 3/20                    | 660F                                                                                 |

|                                | G09G 3/20                    | 680S                                                                                 |

| 審査請求 未請求 請求項の数 31 O L (全 28 頁) |                              |                                                                                      |

| (21) 出願番号                      | 特願2010-272805 (P2010-272805) | (71) 出願人 308040351                                                                   |

| (22) 出願日                       | 平成22年12月7日 (2010.12.7)       | 三星モバイルディスプレイ株式会社                                                                     |

| (31) 優先権主張番号                   | 10-2010-0082514              | Samsung Mobile Display Co., Ltd.                                                     |

| (32) 優先日                       | 平成22年8月25日 (2010.8.25)       | 大韓民国京畿道龍仁市器興区農書洞山24                                                                  |

| (33) 優先権主張国                    | 韓国(KR)                       | San #24 Nongseo-Dong, Giheung-Gu, Yongin-City, Gyeonggi-Do 446-711 Republic of KOREA |

| (74) 代理人 100083806             |                              |                                                                                      |

| 弁理士 三好 秀和                      |                              |                                                                                      |

| (74) 代理人 100095500             |                              |                                                                                      |

| 弁理士 伊藤 正和                      |                              |                                                                                      |

最終頁に続く

(54) 【発明の名称】両方向走査駆動装置及びこれを利用した表示装置

## (57) 【要約】

【課題】有機発光表示装置の表示部に含まれている画素に伝達される走査信号を両方向に伝達して駆動させる方式において、多様なアプリケーションを実現できる走査駆動装置を提供する。

【解決手段】本発明の一実施形態に係る走査駆動装置は、複数の画素を含む表示部に少なくとも二種類の互いに異なる走査信号をそれぞれ生成して伝達する走査駆動装置が、前記少なくとも二種類の互いに異なる走査信号をそれぞれ生成する複数のシフトレジスタで構成される複数の順次駆動部を含み、所定のシフトレジスタで生成された走査信号は次のシフトレジスタの入力信号として伝達され、同時に前記走査信号は、走査駆動装置の決められた駆動方向に対応して、前記所定のシフトレジスタが含まれている順次駆動部と隣接する前の段の順次駆動部のシフトレジスタまたは次の段の順次駆動部のシフトレジスタに入力信号として伝達される。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

複数の画素を含む表示部に少なくとも二種類の互いに異なる走査信号をそれぞれ生成して伝達する走査駆動装置が、前記少なくとも二種類の互いに異なる走査信号をそれぞれ生成する複数のシフトレジスタからなる複数の順次駆動部を含み、

所定のシフトレジスタで生成された走査信号は、次のシフトレジスタの入力信号として伝達されると同時に、前記走査信号は、走査駆動装置の決められた駆動方向に対応して、前記所定のシフトレジスタが含まれている順次駆動部と隣接する前の段の順次駆動部のシフトレジスタまたは次の段の順次駆動部のシフトレジスタに入力信号として伝達される走査駆動装置。

10

**【請求項 2】**

前記駆動方向が順方向の場合、前記走査信号は、前記所定のシフトレジスタが含まれている順次駆動部と隣接する次の段の順次駆動部のシフトレジスタに入力信号として伝達され、

前記駆動方向が逆方向の場合、前記走査信号は、前記所定のシフトレジスタが含まれている順次駆動部と隣接する前の段の順次駆動部のシフトレジスタに入力信号として伝達される、請求項 1 に記載の走査駆動装置。

**【請求項 3】**

前記少なくとも二種類の互いに異なる走査信号は、

前記複数の画素それぞれに含まれている駆動トランジスタのゲート電圧を初期化させる初期化信号、及び前記複数の画素それぞれに対応するデータ信号を伝達するスイッチングトランジスタのスイッチング動作を制御する走査信号である、請求項 1 に記載の走査駆動装置。

20

**【請求項 4】**

前記初期化信号は、前記走査信号より先に生成されて伝達される、請求項 3 に記載の走査駆動装置。

**【請求項 5】**

前記複数のシフトレジスタは、

前記複数の画素それぞれに含まれている駆動トランジスタのゲート電圧を初期化させる初期化信号を生成する第 1 シフトレジスタ、及び前記複数の画素それぞれに対応するデータ信号を伝達するスイッチングトランジスタのスイッチング動作を制御する走査信号を生成する第 2 シフトレジスタである、請求項 1 に記載の走査駆動装置。

30

**【請求項 6】**

前記第 2 シフトレジスタは、前記初期化信号が入力信号として伝達されて、前記初期化信号を所定の第 1 期間ほどシフトさせて前記走査信号を生成する、請求項 5 に記載の走査駆動装置。

**【請求項 7】**

前記第 1 シフトレジスタで生成された初期化信号が前記第 2 シフトレジスタの入力信号として伝達される時点に同期されて、前記初期化信号は、走査駆動装置の決められた駆動方向に対応して、前記第 1 シフトレジスタを含む順次駆動部と隣接した前の段の順次駆動部または次の段の順次駆動部の第 1 シフトレジスタに入力信号として伝達される、請求項 5 に記載の走査駆動装置。

40

**【請求項 8】**

前記駆動方向が順方向の場合、前記初期化信号は、前記第 1 シフトレジスタを含む順次駆動部と隣接する次の段の順次駆動部の第 1 シフトレジスタに入力信号として伝達され、

前記駆動方向が逆方向の場合、前記初期化信号は前記第 1 シフトレジスタを含む順次駆動部と隣接する前の段の順次駆動部の第 1 シフトレジスタに入力信号として伝達される、請求項 7 に記載の走査駆動装置。

**【請求項 9】**

前記複数の順次駆動部のうちの奇数段の複数の順次駆動部それぞれは、

50

第1クロック信号に同期されて、順方向開始信号（最初の段の場合）及び当該段の順次駆動部と隣接する前の段の順次駆動部のシフトレジスタで生成された走査信号、または当該段の順次駆動部と隣接する次の段の順次駆動部のシフトレジスタで生成された走査信号及び逆方向開始信号（最後の段の場合）を第1入力信号として受け、前記第1入力信号及び第1初期化信号にそれぞれ対応して、第2クロック信号及び第1電源電圧のうちの一つを第1走査信号として出力する第1シフトレジスタ；及び

前記第2クロック信号に同期されて前記第1走査信号を第2入力信号として受け、前記第2入力信号及び第2初期化信号にそれぞれ対応して、第1クロック信号及び第1電源電圧のうちの一つを第2走査信号として出力する第2シフトレジスタを含む、請求項1に記載の走査駆動装置。

10

#### 【請求項10】

前記複数の順次駆動部のうちの偶数段の複数の順次駆動部それは、

第2クロック信号に同期されて、当該段の順次駆動部と隣接する前の段の順次駆動部のシフトレジスタで生成された走査信号、または当該段の順次駆動部と隣接する次の段の順次駆動部のシフトレジスタで生成された走査信号及び逆方向開始信号（最後の段の場合）を第3入力信号として受け、前記第3入力信号及び第2初期化信号にそれぞれ対応して、第1クロック信号及び第1電源電圧のいずれか一つを第1走査信号として出力する第1シフトレジスタ；及び

前記第1クロック信号に同期されて、前記第1走査信号を第4入力信号として受け、前記第4入力信号及び第1初期化信号にそれぞれ対応して、第2クロック信号及び第1電源電圧のいずれか一つを第2走査信号として出力する第2シフトレジスタを含む、請求項1に記載の走査駆動装置。

20

#### 【請求項11】

前記第2クロック信号は、前記第1クロック信号と半周期ほど位相差を有する、請求項9または10に記載の走査駆動装置。

#### 【請求項12】

前記第1初期化信号は、前記第2クロック信号に同期されるか、または所定の期間ほど遅れて発生し、

前記第2初期化信号は、前記第1クロック信号に同期されるか、または所定の期間ほど遅れて発生する、請求項9または10に記載の走査駆動装置。

30

#### 【請求項13】

前記第1走査信号と第2走査信号の位相差は、前記第1クロック信号と第2クロック信号の位相差と同一である、請求項9または10に記載の走査駆動装置。

#### 【請求項14】

前記第1シフトレジスタは、

順方向駆動制御信号によってターンオンされて、前記順方向開始信号（最初の段の場合）及び前記当該段の順次駆動部と隣接する前の段の順次駆動部のシフトレジスタで生成された第3走査信号を前記第1入力信号として伝達する第1トランジスタ；

逆方向駆動制御信号によってターンオンされて、前記当該段の順次駆動部と隣接する次の段の順次駆動部のシフトレジスタで生成された第4走査信号及び前記逆方向開始信号（最後の段の場合）を前記第1入力信号として伝達する第2トランジスタ；

前記第1クロック信号によってターンオンされて、第3走査信号または第4走査信号を伝達する第3トランジスタ；

前記第3走査信号または第4走査信号の伝達を受け、前記第3走査信号または第4走査信号の電圧レベルによってターンオンされて、前記第1電源電圧を伝達する第4トランジスタ；

前記第1初期化信号に対応して伝達される第2電源電圧に対応してターンオンされて、前記第1電源電圧を伝達する第5トランジスタ；

前記第1初期化信号によってターンオンされて、前記第2電源電圧を前記第5トランジスタのゲート電極が接続された第1ノードに伝達する第6トランジスタ；

40

50

前記第3トランジスタを通じて伝達された第3走査信号または第4走査信号の電圧レベルによってターンオンされて、前記第2クロック信号を前記第1走査信号として出力する第7トランジスタ；及び

前記第1ノードに伝達された第2電源電圧に対応してターンオンされ、前記第1電源電圧を前記第1走査信号として出力する第8トランジスタを含む、請求項9に記載の走査駆動装置。

#### 【請求項15】

前記第1シフトレジスタは、

前記第1ノードに接続する一電極及び前記第1電源電圧に接続する他電極を含む第1キャパシタ；及び

前記第7トランジスタのゲート電極に接続する一電極及び前記第1シフトレジスタの出力端に接続する他電極を含む第2キャパシタをさらに含む、請求項14に記載の走査駆動装置。

#### 【請求項16】

前記第2シフトレジスタは、

前記第2クロック信号によってターンオンされて、前記第1走査信号を伝達する第9トランジスタ；

前記第1走査信号の伝達を受けて前記第1走査信号の電圧レベルによってターンオンされて、前記第1電源電圧を伝達する第10トランジスタ；

前記第2初期化信号に対応して伝達される第2電源電圧に対応してターンオンされて、前記第1電源電圧を伝達する第11トランジスタ；

前記第2初期化信号によってターンオンされて、前記第2電源電圧を前記第11トランジスタのゲート電極が接続された第2ノードに伝達する第12トランジスタ；

前記第9トランジスタを通じて伝達された第1走査信号の電圧レベルによってターンオンされて、前記第1クロック信号を前記第2走査信号として出力する第13トランジスタ；及び

前記第2ノードに伝達された第2電源電圧に対応してターンオンされて、前記第1電源電圧を前記第2走査信号として出力する第14トランジスタを含む、請求項9に記載の走査駆動装置。

#### 【請求項17】

前記第2シフトレジスタは、

前記第2ノードに接続する一電極及び前記第1電源電圧に接続する他電極を含む第3キャパシタ；及び

前記第13トランジスタのゲート電極に接続する一電極及び前記第2シフトレジスタの出力端に接続する他電極を含む第4キャパシタをさらに含む、請求項16に記載の走査駆動装置。

#### 【請求項18】

前記第1シフトレジスタは、

順方向駆動制御信号によってターンオンされて、前記当該段の順次駆動部と隣接する前の段の順次駆動部のシフトレジスタで生成された第5走査信号を前記第3入力信号として伝達する第1スイッチ；

逆方向駆動制御信号によってターンオンされて、前記当該段の順次駆動部と隣接する次の段の順次駆動部のシフトレジスタで生成された第6走査信号及び前記逆方向開始信号（最後の段の場合）を前記第3入力信号として伝達する第2スイッチ；

前記第2クロック信号によってターンオンされて、第5走査信号または第6走査信号を伝達する第3スイッチ；

前記第5走査信号または第6走査信号の伝達を受けて前記第5走査信号または第6走査信号の電圧レベルによってターンオンされて、前記第1電源電圧を伝達する第4スイッチ；

前記第2初期化信号に対応して伝達される第2電源電圧に対応してターンオンされて、

10

20

30

40

50

前記第1電源電圧を伝達する第5スイッチ；

前記第2初期化信号によってターンオンされて、前記第2電源電圧を前記第5スイッチのゲート電極が接続された第3ノードに伝達する第6スイッチ；

前記第3スイッチを通じて伝達された第5走査信号または第6走査信号の電圧レベルによってターンオンされて、前記第1クロック信号を前記第1走査信号として出力する第7スイッチ；及び

前記第3ノードに伝達された第2電源電圧に対応してターンオンされて、前記第1電源電圧を前記第1走査信号として出力する第8スイッチを含む、請求項10に記載の走査駆動装置。

#### 【請求項19】

前記第1シフトレジスタは、

前記第3ノードに接続する一電極及び前記第1電源電圧に接続する他電極を含む第5キャパシタ；及び

前記第7スイッチのゲート電極に接続する一電極及び前記第1シフトレジスタの出力端に接続する他電極を含む第6キャパシタをさらに含む、請求項18に記載の走査駆動装置。

#### 【請求項20】

前記第2シフトレジスタは、

前記第1クロック信号によってターンオンされて、前記第1走査信号を伝達する第9スイッチ；

前記第1走査信号の伝達を受けて前記第1走査信号の電圧レベルによってターンオンされて、前記第1電源電圧を伝達する第10スイッチ；

前記第1初期化信号に対応して伝達される第2電源電圧に対応してターンオンされて、前記第1電源電圧を伝達する第11スイッチ；

前記第1初期化信号によってターンオンされて、前記第2電源電圧を前記第11スイッチのゲート電極が接続された第4ノードに伝達する第12スイッチ；

前記第9スイッチを通じて伝達された第1走査信号の電圧レベルによってターンオンされて、前記第2クロック信号を前記第2走査信号として出力する第13スイッチ；及び

前記第4ノードに伝達された第2電源電圧に対応してターンオンされて、前記第1電源電圧を前記第2走査信号として出力する第14スイッチを含む、請求項10に記載の走査駆動装置。

#### 【請求項21】

前記第2シフトレジスタは、

前記第4ノードに接続する一電極及び前記第1電源電圧に接続する他電極を含む第7キャパシタ；及び

前記第13スイッチのゲート電極に接続する一電極及び前記第2シフトレジスタの出力端に接続する他電極を含む第8キャパシタをさらに含む、請求項20に記載の走査駆動装置。

#### 【請求項22】

複数の画素を含む表示部；

前記複数の画素それぞれに少なくとも二種類の互いに異なる走査信号を伝達する走査駆動装置；

前記複数の画素それぞれにデータ信号を伝達するデータ駆動部；

前記複数の画素それぞれに発光制御信号を伝達する発光制御駆動部；及び

前記走査駆動装置、データ駆動部、及び発光制御駆動部の駆動を制御する複数の制御信号を生成してそれぞれ伝達する信号制御部を含み、

前記走査駆動装置は前記少なくとも二種類の互いに異なる走査信号をそれぞれ生成する複数のシフトレジスタで構成された複数の順次駆動部を含み、

所定のシフトレジスタで生成された走査信号は、次のシフトレジスタの入力信号として伝達されると同時に、前記走査信号は、走査駆動装置の決められた駆動方向に対応して、

10

20

30

40

50

前記所定のシフトレジスタが含まれている順次駆動部と隣接する前の段の順次駆動部のシフトレジスタまたは次の段の順次駆動部のシフトレジスタに入力信号として伝達される表示装置。

**【請求項 2 3】**

前記信号制御部は、前記駆動装置の駆動方向を決定する順方向駆動制御信号及び逆方向駆動制御信号を生成して伝達する、請求項 2 2 に記載の表示装置。

**【請求項 2 4】**

前記順方向駆動制御信号及び逆方向駆動制御信号は相互反転した信号である、請求項 2 3 に記載の表示装置。

**【請求項 2 5】**

前記駆動方向が順方向の場合、前記走査信号は、前記所定のシフトレジスタが含まれている順次駆動部と隣接する次の段の順次駆動部のシフトレジスタに入力信号として伝達され、

前記駆動方向が逆方向の場合、前記走査信号は、前記所定のシフトレジスタが含まれている順次駆動部と隣接する前の段の順次駆動部のシフトレジスタに入力信号として伝達される、請求項 2 2 に記載の表示装置。

**【請求項 2 6】**

前記少なくとも二種類の互いに異なる走査信号は、

前記複数の画素それぞれに含まれている駆動トランジスタのゲート電圧を初期化させる初期化信号、及び前記複数の画素それぞれに対応するデータ信号を伝達するスイッチングトランジスタのスイッチング動作を制御する走査信号である、請求項 2 2 に記載の表示装置。

**【請求項 2 7】**

前記初期化信号は、前記走査信号より先に生成されて伝達される、請求項 2 6 に記載の表示装置。

**【請求項 2 8】**

前記複数のシフトレジスタは、

前記複数の画素それぞれに含まれている駆動トランジスタのゲート電圧を初期化させる初期化信号を生成する第 1 シフトレジスタ、及び前記複数の画素それぞれに対応するデータ信号を伝達するスイッチングトランジスタのスイッチング動作を制御する走査信号を生成する第 2 シフトレジスタである、請求項 2 2 に記載の表示装置。

**【請求項 2 9】**

前記第 2 シフトレジスタは、前記初期化信号が入力信号として伝達されて、前記初期化信号を所定の第 1 期間ほどシフトさせて前記走査信号を生成する、請求項 2 8 に記載の表示装置。

**【請求項 3 0】**

前記第 1 シフトレジスタで生成された初期化信号が前記第 2 シフトレジスタの入力信号として伝達される時点に同期されて、前記初期化信号は走査駆動装置の決められた駆動方向に対応して、前記第 1 シフトレジスタを含む順次駆動部と隣接した前の段の順次駆動部または次の段の順次駆動部の第 1 シフトレジスタに入力信号として伝達される、請求項 2 8 に記載の表示装置。

**【請求項 3 1】**

前記駆動方向が順方向の場合、前記初期化信号は、前記第 1 シフトレジスタを含む順次駆動部と隣接する次の段の順次駆動部の第 1 シフトレジスタに入力信号として伝達され、

前記駆動方向が逆方向の場合、前記初期化信号は、前記第 1 シフトレジスタを含む順次駆動部と隣接する前の段の順次駆動部の第 1 シフトレジスタに入力信号として伝達される、請求項 3 0 に記載の表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

10

20

30

40

50

本発明は、両方向走査駆動装置及びこれを利用した表示装置に関し、より詳しくは、複数の画素を含む表示部を順方向または逆方向の両方向に円滑に駆動することができるよう、複数の画素に含まれている所定のトランジスタに供給される走査信号を、順序を変えずに供給する両方向走査駆動装置と、これを含む表示装置に関する。

【背景技術】

【0002】

近来、陰極線管（Cathode Ray Tube）の短所である重量と体積を減らせる各種平板表示装置が開発されている。平板装置としては、液晶表示装置（Liquid Crystal Display : LCD）、電界放出表示装置（Liquid Crystal Display : FED）、プラズマ表示パネル（Liquid Crystal Display : PDP）、及び有機発光表示装置（Liquid Crystal Display）などがある。10

【0003】

平板表示装置のうち、有機発光表示装置は、電子と正孔の再結合によって光を発生する有機発光ダイオード（Liquid Crystal Display、OLED）を利用して映像を表示するものであって、速い応答速度を有すると共に、低い消費電力で駆動され、発光効率、輝度、及び視野角に優れた長所があつて注目されている。

【0004】

通常、有機発光表示装置は、有機発光ダイオードを駆動する方式により、パッシブマトリックス型有機発光表示装置（PMOLED）と、アクティブマトリックス型有機発光表示装置（AMOLED）に分類される。20

【0005】

パッシブマトリックス型は、陽極と陰極を互いに直交するように形成し、陰極ラインと陽極ラインを選択して駆動する方式であり、アクティブマトリックス型は、薄膜トランジスタとキャパシタを各ピクセル内に集積して、キャパシタ容量によって電圧を維持するようとする駆動方式である。パッシブマトリックス型は、構造が簡単で、安価であるが、大型または高精密度のパネルの実現が困難である。反面、アクティブマトリックス型は、大型及び高精密度のパネルの実現が可能であるが、その制御方法が技術的に難しく、比較的に高価であるという問題がある。

【0006】

解像度、コントラスト、動作速度の観点で、単位画素ごとに選択して点灯するアクティブマトリックス型有機発光表示装置（AMOLED）が主流となっている。30

【0007】

アクティブマトリックス型有機発光表示装置は、一般に、マトリックス状に配列される画素を含む表示装置、画素と接続されたデータ線にデータ信号を伝達するデータ駆動装置、及び画素と接続された走査線に走査信号を伝達するための走査駆動装置を備える。

【0008】

走査駆動装置の駆動方式は、走査駆動装置に含まれている多数のシフトレジスタを利用して、ライン単位で画素を選択して、水平期間ごとに走査信号を順次に供給することである。データ駆動部は、走査信号によってライン単位で選択された画素にデータ信号を供給する。このことにより、画素それぞれはデータ信号に対応する所定の電流を有機発光ダイオードに供給して、データ信号に対応する所定の画像を表示する。40

【0009】

一方、走査駆動装置が走査信号を順次に画素に伝達する一方向方式の駆動は、最近、視野角特性を考慮して、使用目的が多様化され、設置位置によって表示パネルを多様に反転させて使用する携帯用通信機器またはデジタル映像機器には適用できることで、両方向方式の駆動が提案されている。

【0010】

このような両方向方式の駆動方法を使用する走査駆動装置が、順方向や逆方向の方向性と無関係に駆動されるためには、走査駆動装置から出力されて表示パネルの画素に伝達される走査信号が、常に一定の時間的順序を有して伝達される必要があり、このための走査50

駆動装置の回路設計及び開発が要求される。

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明はこのような問題点に鑑みてなされたものであって、有機発光表示装置の表示部に含まれている画素に伝達される走査信号を両方向に伝達して駆動させる方式において、多様なアプリケーションを実現できる走査駆動装置を提供することに目的がある。

【0012】

また、本発明は、両方向走査駆動が可能な走査駆動装置において、どの方向を選択しても画素に含まれているトランジスタに伝達される走査信号の順序が変わらないことにより、上下反転した画像の実現が自由に表現され、使用的な便宜性が向上した走査駆動装置を提案し、このような走査駆動装置を含む有機発光表示装置を提供することに他の目的がある。

【0013】

本発明が目的とする技術的課題は、以上で言及した技術的課題に制限されず、言及されないまた他の技術的課題は本発明の記載から当該分野における通常の知識を有する者に明確に理解されるはずである。

【課題を解決するための手段】

【0014】

上記目的を達成するための本発明の一実施形態に係る走査駆動装置は、複数の画素を含む表示部に少なくとも二種類の互いに異なる走査信号をそれぞれ生成して伝達する走査駆動装置が、前記少なくとも二種類の互いに異なる走査信号をそれぞれ生成する複数のシフトレジスタで構成される複数の順次駆動部を含む。

【0015】

この時、所定のシフトレジスタで生成された走査信号は、次のシフトレジスタの入力信号として伝達され、同時に前記走査信号は、走査駆動装置の決められた駆動方向に対応して、前記所定のシフトレジスタが含まれている順次駆動部と隣接する前の段の順次駆動部のシフトレジスタまたは次の段の順次駆動部のシフトレジスタに入力信号として伝達される。

【0016】

前記駆動方向が順方向の場合、前記走査信号は、前記所定のシフトレジスタが含まれている順次駆動部と隣接する次の段の順次駆動部のシフトレジスタに入力信号として伝達される。一方、前記駆動方向が逆方向の場合、前記走査信号は、前記所定のシフトレジスタが含まれている順次駆動部と隣接する前の段の順次駆動部のシフトレジスタに入力信号として伝達される。

【0017】

本発明において、前記少なくとも二種類の互いに異なる走査信号は、前記複数の画素それぞれに含まれている駆動トランジスタのゲート電圧を初期化させる初期化信号、及び前記複数の画素それぞれに対応するデータ信号を伝達するスイッチングトランジスタのスイッチング動作を制御する走査信号とすることができます。

【0018】

この時、前記初期化信号は前記走査信号より先に生成されて伝達される。

【0019】

本発明の一実施形態において、前記複数のシフトレジスタは、前記複数の画素それぞれに含まれている駆動トランジスタのゲート電圧を初期化させる初期化信号を生成する第1シフトレジスタ、及び前記複数の画素それぞれに対応するデータ信号を伝達するスイッチングトランジスタのスイッチング動作を制御する走査信号を生成する第2シフトレジスタである。

【0020】

この時、前記第2シフトレジスタは、前記初期化信号を入力信号として伝達を受けて、

10

20

30

40

50

前記初期化信号を所定の第1期間ほどシフトさせて前記走査信号を生成する。

【0021】

また、前記第1シフトレジスタで生成された初期化信号が前記第2シフトレジスタの入力信号として伝達される時点に同期されて、前記初期化信号は、走査駆動装置の決められた駆動方向に対応して、前記第1シフトレジスタを含む順次駆動部と隣接した前の段の順次駆動部または次の段の順次駆動部の第1シフトレジスタに入力信号として伝達される。

【0022】

万一、前記駆動方向が順方向の場合、前記初期化信号は、前記第1シフトレジスタを含む順次駆動部と隣接する次の段の順次駆動部の第1シフトレジスタに入力信号として伝達される。

10

【0023】

一方、前記駆動方向が逆方向の場合、前記初期化信号は、前記第1シフトレジスタを含む順次駆動部と隣接する前の段の順次駆動部の第1シフトレジスタに入力信号として伝達される。

【0024】

前記複数の順次駆動部のうちの奇数段の複数の順次駆動部それぞれは、第1クロック信号に同期されて、順方向開始信号（最初の段の場合）及び当該段の順次駆動部と隣接する前の段の順次駆動部のシフトレジスタで生成された走査信号、または当該段の順次駆動部と隣接する次の段の順次駆動部のシフトレジスタで生成された走査信号及び逆方向開始信号（最後の段の場合）を第1入力信号として受け、前記第1入力信号及び第1初期化信号にそれぞれ対応して、第2クロック信号及び第1電源電圧のいずれか一つを第1走査信号として出力する第1シフトレジスタ；及び前記第2クロック信号に同期されて、前記第1走査信号を第2入力信号として受け、前記第2入力信号及び第2初期化信号にそれぞれ対応して、第1クロック信号及び第1電源電圧のいずれか一つを第2走査信号として出力する第2シフトレジスタを含む。

20

【0025】

本発明の一実施形態として、複数の順次駆動部を構成する複数のシフトレジスタは、少なくとも2つ以上で複数の順次駆動部を構成することができ、複数のシフトレジスタは順次に連結することができる。

30

【0026】

一方、前記複数の順次駆動部のうちの偶数段の複数の順次駆動部それぞれは、第2クロック信号に同期されて、当該段の順次駆動部と隣接する前の段の順次駆動部のシフトレジスタで生成された走査信号、または当該段の順次駆動部と隣接する次の段の順次駆動部のシフトレジスタで生成された走査信号及び逆方向開始信号（最後の段の場合）を第3入力信号として受け、前記第3入力信号及び第2初期化信号にそれぞれ対応して、第1クロック信号及び第1電源電圧のいずれか一つを第1走査信号として出力する第1シフトレジスタ；及び前記第1クロック信号に同期されて、前記第1走査信号を第4入力信号として受け、前記第4入力信号及び第1初期化信号にそれぞれ対応して、第2クロック信号及び第1電源電圧のいずれか一つを第2走査信号として出力する第2シフトレジスタを含む。

40

【0027】

この時、前記第2クロック信号は、前記第1クロック信号と半周期ほど位相差を有することができるが、これに必ずしも制限されるわけではない。

【0028】

また、前記第1初期化信号は、前記第2クロック信号に同期されるか、または所定期間ほど遅れて発生し、前記第2初期化信号は、前記第1クロック信号に同期されるか、または所定期間ほど遅れて発生することができる。

【0029】

前記第1走査信号と第2走査信号の位相差は、前記第1クロック信号と第2クロック信号の位相差と同一である。

50

## 【0030】

前記第1クロック信号、第2クロック信号、第1初期化信号、及び第2初期化信号の周期は、少なくとも1水平周期以上とすることができますが、これに必ずしも制限されるわけではない。

## 【0031】

本発明の一実施形態に係る前記第1シフトレジスタは、順方向駆動制御信号によってターンオンされて、前記順方向開始信号（最初の段の場合）及び前記当該段の順次駆動部と隣接する前の段の順次駆動部のシフトレジスタで生成された第3走査信号を前記第1入力信号として伝達する第1トランジスタ；逆方向駆動制御信号によってターンオンされて、前記当該段の順次駆動部と隣接する次の段の順次駆動部のシフトレジスタで生成された第4走査信号及び前記逆方向開始信号（最後の段の場合）を前記第1入力信号として伝達する第2トランジスタ；前記第1クロック信号によってターンオンされて、第3走査信号または第4走査信号を伝達する第3トランジスタ；前記第3走査信号または第4走査信号の伝達を受けて、前記第3走査信号または第4走査信号の電圧レベルによってターンオンされて、前記第1電源電圧を伝達する第4トランジスタ；前記第1初期化信号に対応して伝達される第2電源電圧に対応してターンオンされて、前記第1電源電圧を伝達する第5トランジスタ；前記第1初期化信号によってターンオンされて、前記第2電源電圧を前記第5トランジスタのゲート電極が接続された第1ノードに伝達する第6トランジスタ；前記第3トランジスタを通じて伝達された第3走査信号または第4走査信号の電圧レベルによってターンオンされて、前記第2クロック信号を前記第1走査信号として出力する第7トランジスタ；及び前記第1ノードに伝達された第2電源電圧に対応してターンオンされて、前記第1電源電圧を前記第1走査信号として出力する第8トランジスタを含む。10

## 【0032】

前記第1シフトレジスタは、前記第1ノードに接続する一電極及び前記第1電源電圧に接続する他電極を含む第1キャパシタ；及び前記第7トランジスタのゲート電極に接続する一電極及び前記第1シフトレジスタの出力端に接続する他電極を含む第2キャパシタをさらに含む。20

## 【0033】

一方、前記第2シフトレジスタは、前記第2クロック信号によってターンオンされて、前記第1走査信号を伝達する第9トランジスタ；前記第1走査信号の伝達を受けて、前記第1走査信号の電圧レベルによってターンオンされて、前記第1電源電圧を伝達する第10トランジスタ；前記第2初期化信号に対応して伝達される第2電源電圧に対応してターンオンされて、前記第1電源電圧を伝達する第11トランジスタ；前記第2初期化信号によってターンオンされて、前記第2電源電圧を前記第11トランジスタのゲート電極が接続された第2ノードに伝達する第12トランジスタ；前記第9トランジスタを通じて伝達された第1走査信号の電圧レベルによってターンオンされて、前記第1クロック信号を前記第2走査信号として出力する第13トランジスタ；及び前記第2ノードに伝達された第2電源電圧に対応してターンオンされて、前記第1電源電圧を前記第2走査信号として出力する第14トランジスタを含む。30

## 【0034】

前記第2シフトレジスタは、前記第2ノードに接続する一電極及び前記第1電源電圧に接続する他電極を含む第3キャパシタ；及び前記第13トランジスタのゲート電極に接続する一電極及び前記第2シフトレジスタの出力端に接続する他電極を含む第2キャパシタをさらに含む。40

## 【0035】

前記トランジスタは、PMOSトランジスタまたはNMOSトランジスタで実現することができる。

## 【0036】

前記複数の順次駆動部のうちの偶数段の複数の順次駆動部を構成する前記第1シフトレジスタは、順方向駆動制御信号によってターンオンされて、前記当該段の順次駆動部と隣接する前記順次駆動部のシフトレジスタで生成された走査信号を前記第1入力信号として伝達するトランジスタを含む。50

接する前の段の順次駆動部のシフトレジスタで生成された第5走査信号を前記第3入力信号として伝達する第1スイッチ；逆方向駆動制御信号によってターンオンされて、前記当該段の順次駆動部と隣接する次の段の順次駆動部のシフトレジスタで生成された第6走査信号及び前記逆方向開始信号（最後の段の場合）を前記第3入力信号として伝達する第2スイッチ；前記第2クロック信号によってターンオンされて、第5走査信号または第6走査信号を伝達する第3スイッチ；前記第5走査信号または第6走査信号の伝達を受けて、前記第5走査信号または第6走査信号の電圧レベルによってターンオンされて、前記第1電源電圧を伝達する第4スイッチ；前記第2初期化信号に対応して伝達される第2電源電圧に対応してターンオンされて、前記第1電源電圧を伝達する第5スイッチ；前記第2初期化信号によってターンオンされて、前記第2電源電圧を前記第5スイッチのゲート電極が接続された第3ノードに伝達する第6スイッチ；前記第3ス位置を通じて伝達された第5走査信号または第6走査信号の電圧レベルによってターンオンされて、前記第1クロック信号を前記第1走査信号として出力する第7スイッチ；及び前記第3ノードに伝達された第2電源電圧に対応してターンオンされて、前記第1電源電圧を前記第1走査信号として出力する第8スイッチを含む。

## 【0037】

前記第1シフトレジスタは、前記第3ノードに接続する一電極及び前記第1電源電圧に接続する他電極を含む第5キャパシタ；及び前記第7スイッチのゲート電極に接続する一電極及び前記第1シフトレジスタの出力端に接続する他電極を含む第6キャパシタをさらに含む。

## 【0038】

一方、偶数段の複数の順次駆動部を構成する前記第2シフトレジスタは、前記第1クロック信号によってターンオンされて、前記第1走査信号を伝達する第9スイッチ；前記第1走査信号の伝達を受けて、前記第1走査信号の電圧レベルによってターンオンされて、前記第1電源電圧を伝達する第10スイッチ；前記第1初期化信号に対応して伝達される第2電源電圧に対応してターンオンされて、前記第1電源電圧を伝達する第11スイッチ；前記第1初期化信号によってターンオンされて、前記第2電源電圧を前記第11スイッチのゲート電極が接続された第4ノードに伝達する第12スイッチ；前記第9スイッチを通じて伝達された第1走査信号の電圧レベルによってターンオンされて、前記第2クロック信号を前記第2走査信号として出力する第13スイッチ；及び前記第4ノードに伝達された第2電源電圧に対応してターンオンされて、前記第1電源電圧を前記第2走査信号として出力する第14スイッチを含む。

## 【0039】

前記第2シフトレジスタは、前記第4ノードに接続する一電極及び前記第1電源電圧に接続する他電極を含む第7キャパシタ；及び前記第13スイッチのゲート電極に接続する一電極及び前記第2シフトレジスタの出力端に接続する他電極を含む第8キャパシタをさらに含む。

## 【0040】

前記スイッチは、PMOSトランジスタまたはNMOSトランジスタで実現することができる。

## 【0041】

上記目的を達成するための本発明の表示装置は、複数の画素を含む表示部；前記複数の画素それぞれに少なくとも二種類の互いに異なる走査信号を伝達する走査駆動装置；前記複数の画素それぞれにデータ信号を伝達するデータ駆動部；前記複数の画素それぞれに発光制御信号を伝達する発光制御駆動部；及び前記走査駆動装置、データ駆動部、及び発光制御駆動部の駆動を制御する複数の制御信号を生成してそれぞれ伝達する信号制御部を含む。

## 【0042】

特に、前記走査駆動装置は、前記少なくとも二種類の互いに異なる走査信号をそれぞれ生成する複数のシフトレジスタで構成された複数の順次駆動部を含み、所定のシフトレジ

スタで生成された走査信号は次のシフトレジスタの入力信号として伝達され、同時に前記走査信号は、走査駆動装置の決められた駆動方向に対応して、前記所定のシフトレジスタが含まれている順次駆動部と隣接する前の段の順次駆動部のシフトレジスタまたは次の段の順次駆動部のシフトレジスタに入力信号として伝達される。

【0043】

この時、前記信号制御部は、前記駆動装置の駆動方向を決定する順方向駆動制御信号及び逆方向駆動制御信号を生成して伝達することができる。

【0044】

前記順方向駆動制御信号及び逆方向駆動制御信号は相互反転した信号である。したがって、表示装置の走査駆動装置は前記順方向駆動制御信号及び逆方向駆動制御信号の制御によって一つの駆動方向に決定されるが、駆動方向に無関係に前記複数の画素それぞれに伝達される少なくとも二種類の互いに異なる走査信号の順序が一定である。

10

【発明の効果】

【0045】

本発明によれば、表示装置の表示部に含まれている画素に走査信号を両方向に伝達して多様に駆動させられる走査駆動装置と、これを含む有機発光表示装置を提供することができる。

【0046】

また、両方向走査駆動が可能な走査駆動装置において、どの方向を選択しても、画素に含まれているトランジスタに伝達される走査信号の順序が変わることなく、上下反転した画像を自由に実現できるので、有機発光表示装置の使用及び応用の便宜性を提供することができる。

20

【図面の簡単な説明】

【0047】

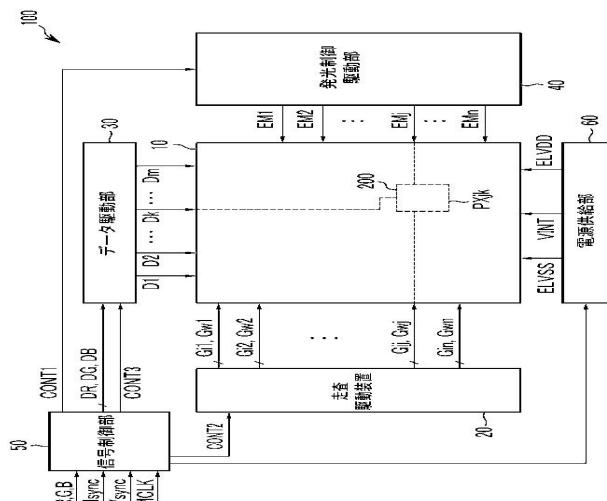

【図1】本発明の一実施形態に係る表示装置のブロック図である。

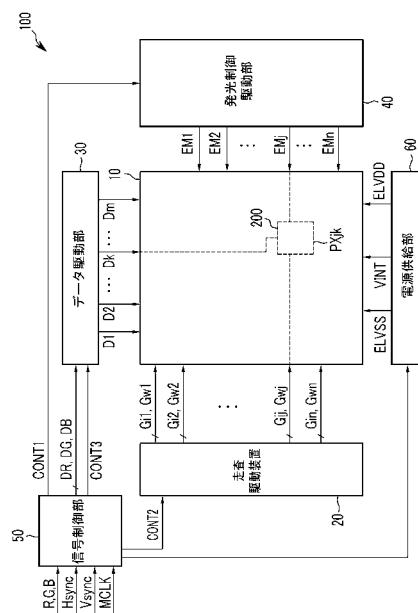

【図2】従来の駆動方式の走査駆動装置と画素を含む表示装置のブロック図である。

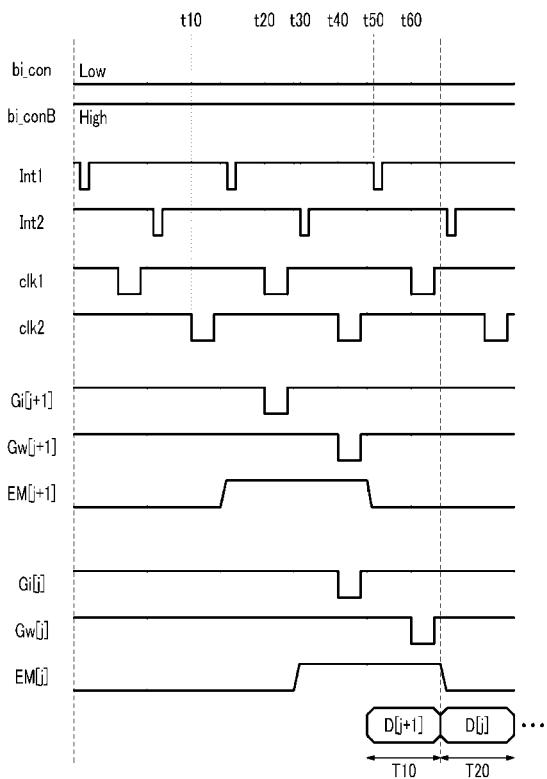

【図3】従来の表示装置の駆動信号を示す信号波形図である。

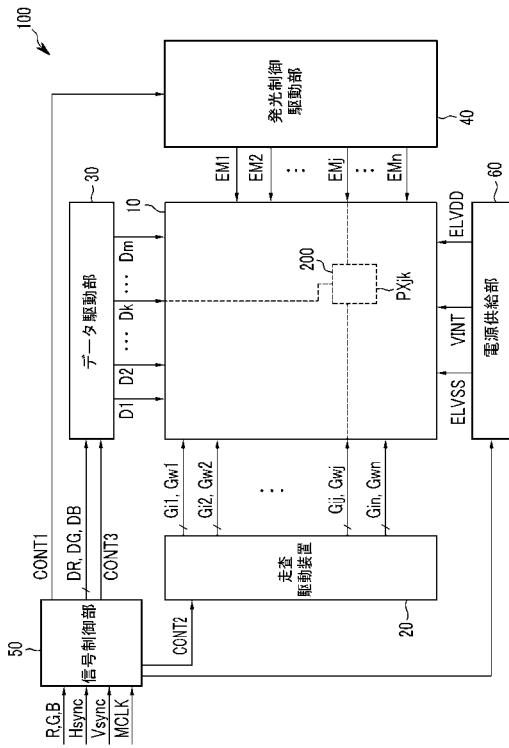

【図4】本発明の一実施形態に係る駆動方式の走査駆動装置と画素を含む表示装置のブロック図である。

30

【図5】本発明の一実施形態に係る走査駆動装置の回路図である。

【図6】本発明の一実施形態に係る走査駆動装置の順方向駆動による駆動信号波形図である。

【図7】本発明の一実施形態に係る走査駆動装置の逆方向駆動による駆動信号波形図である。

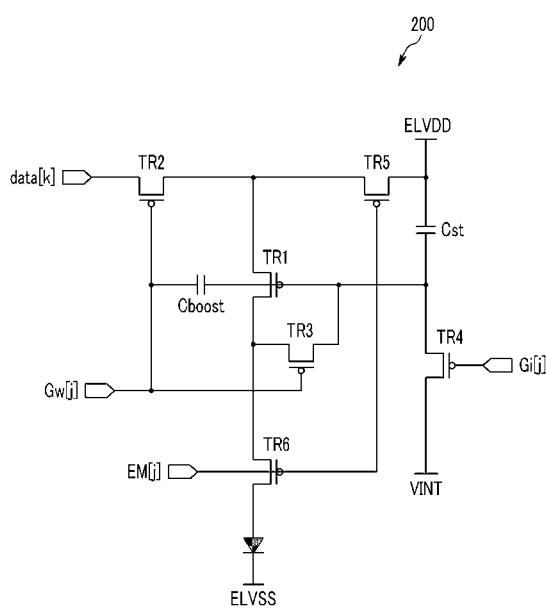

【図8】本発明の一実施形態に係る表示装置に含まれている画素の回路図である。

【発明を実施するための形態】

【0048】

以下、添付した図面を参照して、本発明の実施形態について本発明が属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。本発明は種々の異なる形態に実現でき、ここで説明する実施形態に限られない。

40

【0049】

また、種々の実施形態において、同一の構成を有する構成要素に対しては同一の符号を付け、代表的に第1実施形態で説明し、その他の実施形態では第1実施形態とは異なる構成についてのみ説明する。

【0050】

本発明を明確に説明するために説明上不必要的部分は省略し、明細書の全体にわたって同一または類似する構成要素に対しては同一の参照符号を付ける。

【0051】

明細書の全体において、ある部分が他の部分と「接続」されているという時、これは「直接的に接続」されている場合だけでなく、その中間に他の素子を介在して「電気的に接

50

続」されている場合も含む。また、ある部分がある構成要素を「含む」という時、これは特に反対になる記載がない限り、他の構成要素を除くことではなく、他の構成要素をさらに含むことを意味する。

#### 【0052】

図1は、本発明の一実施形態に係る表示装置の構造を示すブロック図である。

#### 【0053】

本発明の一実施形態に係る表示装置100は、複数の画素を含む表示部10、表示部10に複数の走査信号を伝達する走査駆動装置20、表示部10に複数のデータ信号を伝達するデータ駆動部30、表示部10に複数の発光制御信号を伝達する発光制御駆動部40、表示部10に所定の駆動電源を供給する電源供給部60、並びに走査駆動装置20、データ駆動部30、及び発光制御駆動部40で生成されて伝達する信号を制御するための複数の制御信号を供給する信号制御部50を含む。10

#### 【0054】

表示部10は、複数の画素200が行列状に配列され、各画素200それぞれは、データ駆動部30から伝達されるデータ信号による駆動電流の流れに対応する光を発光する有機発光ダイオード(図示せず)を含む。

#### 【0055】

前記画素200それぞれに、行方向に形成されて走査信号を伝達する複数の走査線( $G_{i1} \sim G_{in}$ 、及び $G_{w1} \sim G_{wn}$ )、及び列方向に形成されてデータ信号を伝達する複数のデータ線( $D_1 \sim D_m$ )が配列される。また、画素200それぞれに、行方向に形成され、発光制御信号を伝達する複数の発光制御線( $E_{M1} \sim E_{Mn}$ )がさらに配列される。20

#### 【0056】

つまり、複数の画素200のうちの一画素( $P_{Xjk}$ )は、それぞれ対応する少なくとも2つの走査線( $G_{ij}$ 、 $G_{wj}$ )、1つのデータ線( $D_k$ )、及び1つの発光制御線( $E_{Mj}$ )と接続される。しかし、一つの実施形態に過ぎず、これに必ずしも制限されることではなく、少なくとも二つ以上の走査線が対応する画素に接続することができる。

#### 【0057】

画素( $P_{Xjk}$ )は対応するデータ信号によって有機発光ダイオードに電流を供給し、有機発光ダイオードは供給された電流によって所定輝度の光を発光する。30

#### 【0058】

表示部10の動作に必要な第1電源電圧( $ELVDD$ )、第2電源電圧( $ELVSS$ )、及び初期電源電圧( $VINT$ )は電源供給部60から伝達される。

#### 【0059】

走査駆動装置20は、表示部10に複数の走査信号を印加する手段で、少なくとも2種類の複数の走査線( $G_{i1} \sim G_{in}$ 、及び $G_{w1} \sim G_{wn}$ )と接続して、複数の走査信号それぞれを複数の走査線のうちの対応する走査線に伝達する。

#### 【0060】

走査駆動装置20は、信号制御部50から供給される走査駆動制御信号( $CONT2$ )によって、表示部10に含まれている複数の画素行に接続された少なくとも二つの走査線に走査信号をそれぞれ順に生成して伝達するが、具体的な回路構成図については後述する。40

#### 【0061】

本発明の一実施形態に係る走査駆動装置20は、両方向駆動する場合にも前記二つの走査線にそれぞれ印加される走査信号の順序が変わらないように伝達できる。

#### 【0062】

データ駆動部30は、信号制御部50から伝達された映像データ信号( $DR$ 、 $DG$ 、 $DB$ )から複数のデータ信号を生成して、表示部10に接続された複数のデータ線( $D_1 \sim D_m$ )に伝達する。データ駆動部30の駆動は、信号制御部50から供給されるデータ駆動制御信号( $CONT3$ )によって作動する。50

## 【0063】

発光制御駆動部40は、信号制御部50から供給される発光制御駆動部制御信号(CONT1)によって、表示部10に接続された複数の発光制御線(EM1～EMn)に複数の発光制御信号を生成して伝達する。

## 【0064】

表示部10に含まれている複数の画素は、対応する発光制御信号の伝達を受け、それに基づいてデータ信号に対応するデータ電圧で有機発光ダイオードを発光させて画像を表示する。

## 【0065】

表示装置100に含まれている走査駆動装置20は、一般に、図2のブロック図のような構成を有し、既存の一方向に表示部10の画素をスキャンして駆動する。 10

## 【0066】

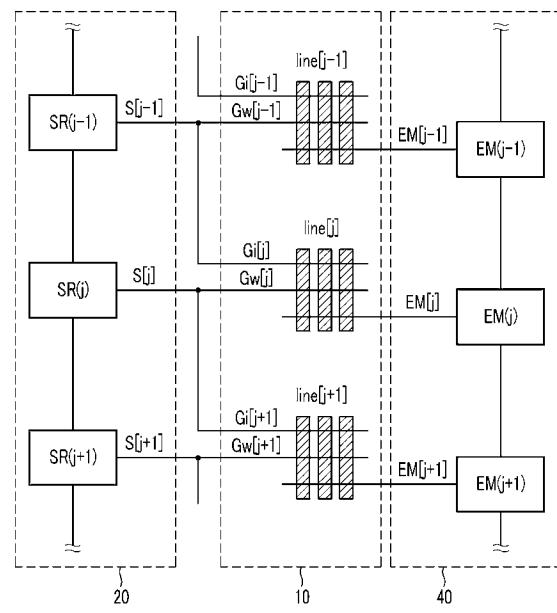

図2は、既存の表示装置100の一部構成を示すブロック図で、具体的には、表示部10に接続された走査線、発光制御線と接続された走査駆動装置20、及び発光制御駆動部40の一部シフトレジストを模式化した図面である。

## 【0067】

図2を参照すれば、既存の走査駆動装置20は、表示部10の画素ラインに接続された走査線に接続された対応するシフトレジスタを複数個含んで構成される。具体的に、表示部10の画素ラインごとに少なくとも二種類の走査信号が伝達される少なくとも二つの走査線が接続される。所定の画素ラインに対応する走査駆動装置20のシフトレジスタの出力端から出力される出力信号は、前記所定の画素ラインと接続された走査線及び次の画素ラインと接続された走査線に同時にそれぞれ供給される。また、前記出力信号は次の段のシフトレジスタの入力信号として使用される。 20

## 【0068】

つまり、表示部10のj-1番目画素ラインと接続された走査線に接続された走査駆動装置20のシフトレジスタ(SR(j-1))から出力される出力信号(S[j-1])は、j-1番目画素ラインに含まれている複数の画素それぞれの走査信号(Gw[j-1])として伝達され、同時に次のj番目画素ラインに含まれている複数の画素それぞれの初期化信号(Gi[j])として伝達される。

## 【0069】

また、j-1番目シフトレジスタ(SR(j-1))の出力信号(S[j-1])は、次の段のj番目シフトレジスタ(SR(j))の入力信号として伝達される。 30

## 【0070】

このことにより、j番目シフトレジスタ(SR(j))が作動して出力信号(S[j])を生成し、前記出力信号(S[j])はj番目画素ラインに含まれている複数の画素それぞれに走査信号(Gw[j])として伝達されると同時に、次の段のj+1番目画素ラインに含まれている複数の画素それぞれに初期化信号(Gi[j+1])として伝達される。

## 【0071】

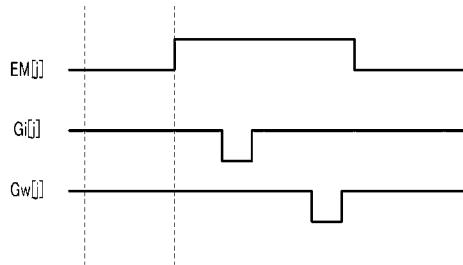

このような方式により、各画素ラインに含まれている複数の画素には初期化信号及び走査信号が順に伝達されて、図3の信号波形図によって駆動される。つまり、図3の波形図のような形態で、j番目画素ラインに接続された複数の画素それぞれに初期化信号(Gi[j])と走査信号(Gw[j])が順に伝達された後、画素に伝達された発光制御信号(EM[j])によってj番目画素ラインの複数の画素は発光して映像を表示する。 40

## 【0072】

既存の駆動方式において、各画素ラインに対応して接続された走査線に対応する複数のシフトレジスタは、上から下の方向に順に出力信号が伝達されて駆動される。

## 【0073】

それにより、表示部10の複数の画素ラインごとに接続された二つの走査線を通じて伝達される走査駆動装置20の出力信号は、初期化信号(Gi)が走査信号(Gw)より時間的に先に伝達される。 50

## 【0074】

しかし、このような駆動方式で駆動される既存の走査駆動装置20を逆方向駆動方式で適用する場合、所定の画素ラインに接続された二つの走査線のいずれか一つの走査線に伝達される初期化信号( $G_i$ )より、他の走査線に伝達される走査信号( $G_w$ )が先に生成されて伝達されるので、画素の駆動が不可能になる問題が発生する。

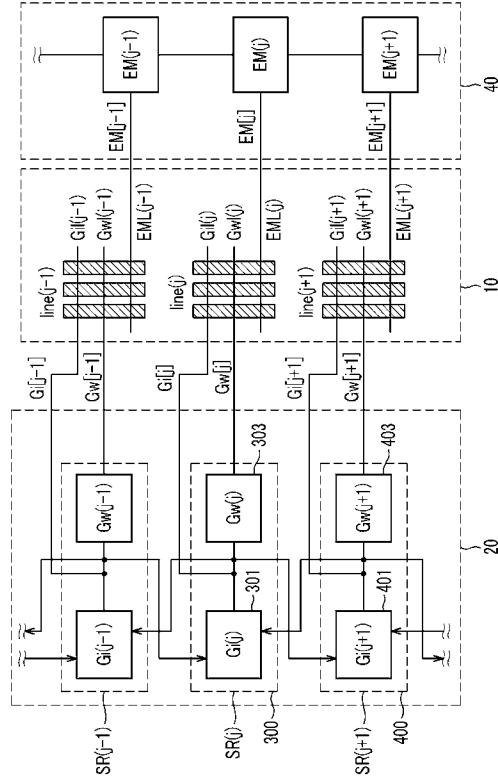

## 【0075】

図4は、このような問題点を解決して、両方向に駆動しても複数の画素に供給される初期化信号及び走査信号の順序が変わらないことを特徴とする本発明による走査駆動装置20の一部を含む表示装置の構成図である。

## 【0076】

図4を参照すれば、複数の画素を含む表示部10の各画素ラインに少なくとも2つの走査線( $G_{i1}$ 、 $G_{w1}$ )と1つの発光制御では( $EML$ )が接続される。図4には示されていないが、各画素ラインに含まれている画素それぞれにデータ線が接続されて、当該画素が走査信号によって選択される時、データ線にデータ信号を伝送する。

10

## 【0077】

前記各画素ラインに接続された走査線( $G_{i1}$ 、 $G_{w1}$ )は2つを示したが、これに限らず、各画素の回路構造によって構成されるトランジスタのゲート電極に接続され、スイッチング動作を制御する信号を伝達する走査線を追加的にさらに含むことができる。

20

## 【0078】

図4の実施形態に係る本発明の走査駆動装置20は、表示部10の画素ラインごとに応し、順次に各段が隣接する段と接続された複数のシフトレジスタ(… $SR(j-1)$ 、 $SR(j)$ 、 $SR(j+1)$ …)を含む。前記シフトレジスタは、それぞれ2個のサブシフトレジスタを含むが、2個のサブシフトレジスタは、複数の画素ラインに接続された走査線( $G_{i1}$ 、 $G_{w1}$ )のうちの第1走査線( $G_{i1}$ )に接続して、第1走査信号を供給する第1シフトレジスタ(… $G_{i(j-1)}$ 、 $G_{i(j)}$ 、 $G_{i(j+1)}$ …)、及び複数の画素ラインに接続された走査線( $G_{i1}$ 、 $G_{w1}$ )のうちの第2走査線( $G_{w1}$ )に接続して、第2走査信号を供給する第2シフトレジスタ(… $G_{w(j-1)}$ 、 $G_{w(j)}$ 、 $G_{w(j+1)}$ …)である。

30

## 【0079】

第1シフトレジスタと第2シフトレジスタは互いに接続されており、前記第1シフトレジスタで生成された第1走査信号が、前記第2シフトレジスタを駆動させる入力信号として伝達される。このことにより、前記第2シフトレジスタは第2走査信号を生成して、複数の画素ラインに接続された第2走査線に第2走査信号を伝達する。したがって、第1走査信号と第2走査信号が生成されて伝達される時期に差があり、第1走査信号が複数の画素ラインに先に伝達される。第1走査信号は、複数の画素ラインに含まれている複数の画素それぞれに初期化信号として伝達され、初期化電圧で各画素をリセットさせる。

## 【0080】

また、前記第1走査信号は、複数の画素ラインに接続された第1走査線に供給されると同時に、走査駆動装置20の方向駆動制御信号(図示せず)によって選択された駆動方向に従ってシフトレジスタの当該段の前の段または次の段の第1シフトレジスタに供給される。

40

## 【0081】

これにより、前記第1走査信号が伝達された段の第1シフトレジスタが動作して、対応する第1走査信号を生成するようになる。

## 【0082】

具体的に、図4の図面において、複数の画素ラインのうちのj番目画素ラインに含まれている複数の画素それぞれに接続された走査駆動装置20を参照して説明する。

## 【0083】

前記j番目画素ラインに対応する走査駆動装置20の複数のシフトレジスタはj段のシ

50

フレジスタ300であり、j段のシフトレジスタ300は第1シフトレジスタ301と第2シフトレジスタ303で構成される。

【0084】

第1シフトレジスタ301は、j番目画素ラインに接続された第1走査線( $G_i[1(j)]$ )に接続して、第1走査信号( $G_i[j]$ )を生成して伝達する。

【0085】

これと同時に、生成された第1走査信号( $G_i[j]$ )は第2シフトレジスタ303の入力端に伝達されて、第2シフトレジスタ303を駆動させ、第2シフトレジスタ303はj番目画素ラインに接続された第2走査線( $G_w[1(j)]$ )に接続されて、第2走査信号( $G_w[j]$ )を生成して伝達する。

10

【0086】

また、第1走査信号( $G_i[j]$ )は、走査駆動装置20の方向駆動制御信号(図示せず)によって選択された駆動方向に従ってj段シフトレジスタ300の前の段であるj-1段シフトレジスタ( $S_R(j-1)$ )、または次の段であるj+1段シフトレジスタ400に供給される。

【0087】

より具体的には、走査駆動装置20の方向駆動制御信号によって選択した駆動方向が、表示部10の上から下の順方向であれば、第1走査信号( $G_i[j]$ )は次の段のj+1段シフトレジスタ400の第1シフトレジスタ401の入力端に供給されて、第1シフトレジスタ401を駆動させる。一方、駆動方向が表示部10の下から上の逆方向であれば、第1走査信号( $G_i[j]$ )は前の段のj-1段シフトレジスタ( $S_R(j-1)$ )の第1シフトレジスタ( $G_i(j-1)$ )の入力端に供給されて、第1シフトレジスタ( $G_i(j-1)$ )を駆動させる。

20

【0088】

従って、本発明の一実施形態に係る走査駆動装置20のシフトレジスタは、駆動方向が順方向及び逆方向のいずれの方向に駆動されても、各画素ラインに対応するシフトレジスタで生成されて伝達される第1走査信号及び第2走査信号の時間的順序が同一である。

【0089】

つまり、複数のシフトレジスタのそれぞれで生成されて表示部10の各画素ラインに伝達される第1走査信号及び第2走査信号は、前記複数のシフトレジスタが順方向に駆動されるかまたは逆方向に駆動されるかの方向性と無関係に、第1走査信号が先に生成及び伝達された後に、第2走査信号が生成及び伝達されるので、表示部10の複数の画素が常に安定的に駆動できる。

30

【0090】

図4に示した走査駆動装置20の一実施形態に係る具体的な回路構成図は図5に示した。

【0091】

図4に示した走査駆動装置20は、順次に相互接続された複数のシフトレジスタを含む。

【0092】

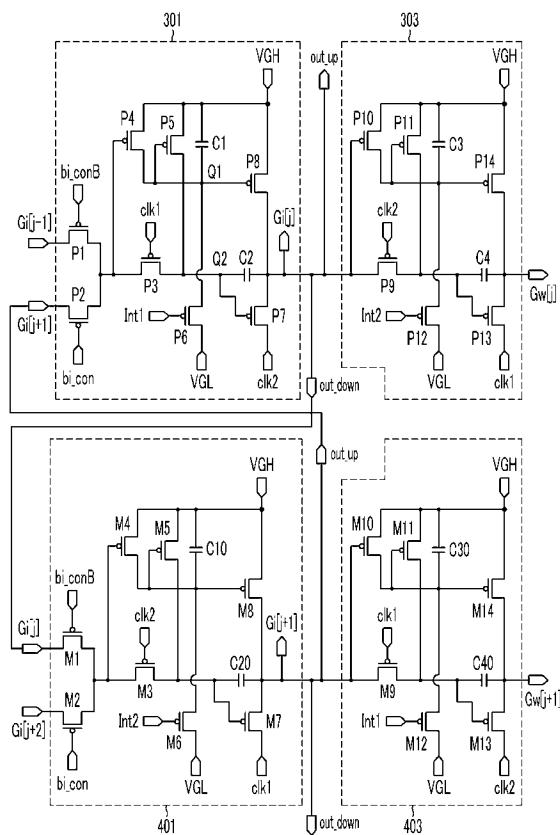

図5に示した走査駆動装置20の回路図は、複数のシフトレジスタのうちのj段シフトレジスタ300(図4に示す)と、次の段のj+1段シフトレジスタ400(図4に示す)に関するものである。

40

【0093】

j段シフトレジスタ300は、j段の第1シフトレジスタ301と、j段の第2シフトレジスタ303とを含み、j+1段シフトレジスタ400は、j+1段の第1シフトレジスタ401と、j+1段の第2シフトレジスタ403とを含む。

【0094】

j段第1シフトレジスタ301は二つの入力端、つまり、前の段のj-1段の第1シフトレジスタ(図示せず)から伝達された第1走査信号( $G_i[j-1]$ )と、次の段のj+

50

1段の第1シフトレジスタ401から伝達された第1走査信号( $G_i[j+1]$ )とがそれぞれ入力される二つの入力端を有する。

#### 【0095】

また、 $j$ 段第1シフトレジスタ301は一つの出力端を有し、前記出力端を通じて $j$ 段に対応する表示部10の $j$ 番目画素ラインに接続された第1走査線に、第1走査信号( $G_i[j]$ )を生成して出力する。

#### 【0096】

これと同時に、第1走査信号( $G_i[j]$ )は第2シフトレジスタ303の入力端に伝達される。また、第1走査信号( $G_i[j]$ )は $j$ 段の前の段または次の段の第1シフトレジスタの入力端に伝達される。

10

#### 【0097】

一方、 $j$ 段第2シフトレジスタ303は一つの出力端を有し、入力端を通じて伝達された第1走査信号( $G_i[j]$ )によって駆動されて、前記出力端を通じて $j$ 段に対応する表示部10の $j$ 番目画素ラインに接続された第2走査線に、第2走査信号( $G_w[j]$ )を生成して出力する。

#### 【0098】

したがって、一つの $j$ 段シフトレジスタ300を通じて生成される第1走査信号( $G_i[j]$ )及び第2走査信号( $G_w[j]$ )は、時間的に間隙を有して、第1走査信号( $G_i[j]$ )が対応する画素ラインに含まれている複数の画素それぞれに先に伝達される。

20

#### 【0099】

画素の回路図を参照して後述するが、第1走査信号( $G_i[j]$ )は、画素駆動時のリセットのための初期化電圧を印加するための初期化信号として動作する。また、続けて伝達される第2走査信号( $G_w[j]$ )は、画素を選択してデータ信号を印加することができるよう、画素のスイッチング動作を制御する走査信号として機能する。

#### 【0100】

$j$ 段の第1シフトレジスタ301を通じて生成された第1走査信号( $G_i[j]$ )は、前の段または次の段の第1シフトレジスタの入力端に伝達されるが、順方向駆動の場合、第1走査信号( $G_i[j]$ )は次の段の $j+1$ 段の第1シフトレジスタ401の入力端に伝達され、逆方向駆動の場合、第1走査信号( $G_i[j]$ )は前の段の $j-1$ 段の第1シフトレジスタ(図示せず)の入力端に伝達される。

30

#### 【0101】

これにより、順方向駆動の場合、第1走査信号( $G_i[j]$ )が伝達された $j+1$ 段の第1シフトレジスタ401は、出力端に $j+1$ 番目画素ラインの複数の画素に伝達される第1走査信号( $G_i[j+1]$ )を生成して出力する。

#### 【0102】

以下、より具体的に、図4及び図5に示した $j$ 段シフトレジスタ300及び $j+1$ 段シフトレジスタ400の構成について説明する。

#### 【0103】

まず、図4に示した $j$ 段シフトレジスタ300の第1シフトレジスタ301は、図5に示すように複数のトランジスタ(P1～P8)及び複数のキャパシタ(C1、C2)を含む。

40

#### 【0104】

ここで、複数のトランジスタ(P1～P14、M1～M14)は、PMOSトランジスタで構成できるが、これに必ずしも制限されることではない。

#### 【0105】

図5に示した回路の構成部において、スイッチとしてPMOSトランジスタを使用する。

#### 【0106】

PMOSトランジスタは、ゲート、ソース、及びドレイン電極を含み、ゲート電極に入力される電圧レベルとソース端子の電圧差によって導通程度が決定される。

50

## 【0107】

j段の第1シフトレジスタ301は、二つの入力端を通じて、前の段または次の段で生成された第1走査信号の伝達を受けることができる。

## 【0108】

前の段のj-1段の第1シフトレジスタ(図示せず)から伝達された第1走査信号(G<sub>i[j-1]</sub>)は、第1シフトレジスタ301の第1トランジスタ(P1)がターンオンされる時、ソース電極からドレイン電極を通過して伝達される。この時、第1トランジスタ(P1)のスイッチング動作を制御する信号は、走査駆動装置の順方向駆動制御信号(b<sub>i\_c\_o\_n\_B</sub>)である。

## 【0109】

一方、次の段のj+1段の第1シフトレジスタ401から伝達された第1走査信号(G<sub>i[j+1]</sub>)は、第1シフトレジスタ301の第2トランジスタ(P2)がターンオンされる時、ソース電極からドレイン電極を通過して伝達される。この時、第2トランジスタ(P2)のスイッチング動作を制御する信号は、走査駆動装置の逆方向駆動制御信号(b<sub>i\_c\_o\_n</sub>)である。

10

## 【0110】

j段の第1シフトレジスタ301の二つの入力端を通じて供給される2つの第1走査信号のうちのいずれか一つの第1走査信号が、走査駆動装置の駆動方向の決定によって伝達される。走査駆動装置の駆動方向を決定する順方向駆動制御信号(b<sub>i\_c\_o\_n\_B</sub>)及び逆方向駆動制御信号(b<sub>i\_c\_o\_n</sub>)は、相互電圧レベルが反転した信号であるので、走査駆動装置の方向性を決定することができる。つまり、順方向駆動のためには所定の期間の間に順方向駆動制御信号(b<sub>i\_c\_o\_n\_B</sub>)によって第1トランジスタ(P1)がターンオンされ、逆方向駆動のためには所定の期間の間に逆方向駆動制御信号(b<sub>i\_c\_o\_n</sub>)によって第2トランジスタ(P2)がターンオンされる。

20

## 【0111】

万一、走査駆動装置のシフトレジスタが最初の段であり、走査駆動装置が順方向に駆動する場合、第1トランジスタ(P1)を通じて伝達される入力信号は所定の順方向開始信号であり得る。反対に、走査駆動装置のシフトレジスタが最後の段であり、走査駆動装置が逆方向に駆動する場合、第2トランジスタ(P2)を通じて伝達される入力信号は、所定の逆方向開始信号であり得る。

30

## 【0112】

一方、本発明の一実施形態に係る走査駆動装置の各段の第1シフトレジスタは、入力端を通じて伝達される入力信号(前の段または次の段の第1走査信号)以外にも、少なくとも2以上のパルスからなる第1クロック信号(c<sub>1\_k\_1</sub>)、第1クロック信号(c<sub>1\_k\_1</sub>)と半周期ほど位相差を有する第2クロック信号(c<sub>1\_k\_2</sub>)、及び第2クロック信号(c<sub>1\_k\_2</sub>)に同期されて発生するかまたは所定時間遅れて発生する第1初期化信号(I<sub>n\_t\_1</sub>)、または第1クロック信号(c<sub>1\_k\_1</sub>)に同期されて発生するかまたは所定時間遅れて発生する第2初期化信号(I<sub>n\_t\_2</sub>)の伝達を受ける。したがって、前記第1シフトレジスタは入力信号(前の段または次の段の第1走査信号)を所定の期間ほどシフトさせて、当該段の第1走査信号を生成する。

40

## 【0113】

本発明の一実施形態に係る走査駆動装置の各段の第2シフトレジスタは、入力端を通じて伝達される入力信号(当該段の第1走査信号)以外にも、少なくとも2以上のパルスからなる第1クロック信号(c<sub>1\_k\_1</sub>)、第1クロック信号(c<sub>1\_k\_1</sub>)と半周期ほど位相差を有する第2クロック信号(c<sub>1\_k\_2</sub>)、及び第2クロック信号(c<sub>1\_k\_2</sub>)に同期されて発生するかまたは所定時間遅れて発生する第1初期化信号(I<sub>n\_t\_1</sub>)、または第1クロック信号(c<sub>1\_k\_1</sub>)に同期されて発生するかまたは所定時間遅れて発生する第2初期化信号(I<sub>n\_t\_2</sub>)の伝達を受ける。したがって、前記第2シフトレジスタは入力信号(当該段の第1走査信号)を所定の期間ほどシフトさせて、当該段の第2走査信号を生成する。

50

## 【0114】

本発明の一実施形態に係る走査駆動装置を構成する各段のシフトレジスタの第1シフトレジスタと第2シフトレジスタの回路構成は同一であるか、第1クロック信号( $c_{1k1}$ )と第2クロック信号( $c_{1k2}$ )相互間、及び第1初期化信号( $I_{nt1}$ )と第2初期化信号( $I_{nt2}$ )相互間が、互いに後先になって供給される構造である。

## 【0115】

また、走査駆動装置の各段に該当する複数の第1シフトレジスタ相互間または複数の第2シフトレジスタ相互間の回路構成も同一であるが、隣接する段間の第1クロック信号( $c_{1k1}$ )と第2クロック信号( $c_{1k2}$ )相互間、及び第1初期化信号( $I_{nt1}$ )と第2初期化信号( $I_{nt2}$ )相互間が互いに後先になつて供給される構造である。 10

## 【0116】

$j$ 段の第1シフトレジスタ301の第1トランジスタ( $P_1$ )は、前の段の $j-1$ 段の第1シフトレジスタから伝達された第1走査信号( $G_i[j-1]$ )が供給されるソース電極、順方向駆動制御信号( $b_{i\_conB}$ )が供給されるゲート電極、及び第3トランジスタ( $P_3$ )のソース電極に接続するドレイン電極を含む。

## 【0117】

第2トランジスタ( $P_2$ )は、次の段の $j+1$ 段の第1シフトレジスタ401から伝達された第1走査信号( $G_i[j+1]$ )が供給されるソース電極、逆方向駆動制御信号( $b_{i\_con}$ )が供給されるゲート電極、及び第3トランジスタ( $P_3$ )のソース電極に接続するドレイン電極を含む。 20

## 【0118】

第3トランジスタ( $P_3$ )は、第1トランジスタ( $P_1$ )のドレイン電極及び第2トランジスタ( $P_2$ )のドレイン電極と接続されたソース電極、第1クロック信号( $c_{1k1}$ )に接続されるゲート電極、及び第2キャパシタ( $C_2$ )の一電極に接続するドレイン電極を含む。

## 【0119】

第3トランジスタ( $P_3$ )は、第1クロック信号( $c_{1k1}$ )により、順方向駆動の場合に第1走査信号( $G_i[j-1]$ )、または逆方向駆動の場合に第1走査信号( $G_i[j+1]$ )を、第7トランジスタ( $P_7$ )のゲート電極に伝達する。

## 【0120】

第4トランジスタ( $P_4$ )は、順方向駆動の場合に第1走査信号( $G_i[j-1]$ )、または逆方向駆動の場合に第1走査信号( $G_i[j+1]$ )により、ソース電極に接続された第1電源電圧( $VGH$ )を第8トランジスタ( $P_8$ )のゲート電極に伝達する。 30

## 【0121】

第5トランジスタ( $P_5$ )は、第1電源電圧( $VGH$ )と接続するソース電極、第1キャパシタ( $C_1$ )の一電極と第8トランジスタ( $P_8$ )のゲート電極との接続点( $Q_1$ )と接続するゲート電極、及び第2キャパシタ( $C_2$ )の一電極に接続するドレイン電極を含む。

## 【0122】

実施形態によって第5トランジスタ( $P_5$ )は直列接続された少なくとも2つのトランジスタを含むことができ、前記少なくとも2つのトランジスタは第2電源電圧( $VGL$ )によってターンオンできる。 40

## 【0123】

第5トランジスタ( $P_5$ )は、第1初期化信号( $I_{nt1}$ )に応答してターンオンされた第6トランジスタ( $P_6$ )によって伝達される第2電源電圧( $VGL$ )によってスイッチング動作が制御される。第5トランジスタ( $P_5$ )がターンオンすれば、第7トランジスタ( $P_7$ )に第1電源電圧( $VGH$ )を伝達する。

## 【0124】

第6トランジスタ( $P_6$ )は、第2電源電圧( $VGL$ )に接続されるソース電極、第1初期化信号( $I_{nt1}$ )に接続されるゲート電極、及び第1キャパシタ( $C_1$ )の一電極

10

20

30

40

50

と第8トランジスタ(P8)のゲート電極及び第5トランジスタ(P5)のゲート電極との接続点(Q1)と接続されるドレイン電極を含む。

【0125】

第6トランジスタ(P6)は、第1初期化信号(Init1)によって第2電源電圧(VGL)を第5トランジスタ(P5)及び第8トランジスタ(P8)に伝達する。

【0126】

第7トランジスタ(P7)は、第2クロック信号(c1k2)に接続されたソース電極、第2キャパシタ(C2)の一電極に接続されたゲート電極、及び第1シフトレジスタ301の出力端に接続するドレイン電極を含む。

【0127】

第7トランジスタ(P7)は、前記出力端に、順方向駆動の場合に第1走査信号(Gi[j-1])、または逆方向駆動の場合に第1走査信号(Gi[j+1])に応答して、第2クロック信号(c1k2)の電圧レベルでj番目画素ラインに伝達される第1走査信号(Gi[j])を出力する。

【0128】

前記出力されたj番目画素ラインに伝達される第1走査信号(Gi[j])は、前の段と次の段の第1シフトレジスタの入力端にそれぞれ供給される。

【0129】

また、同時にj段の第2シフトレジスタ303の入力端に供給される。

【0130】

第8トランジスタ(P8)は、第1電源電圧(VGH)と接続するソース電極、接続点(Q1)と接続するゲート電極、及び第1シフトレジスタ301の出力端に接続するドレイン電極を含む。

【0131】

第8トランジスタ(P8)は、第1初期化信号(Init1)に応答してターンオンされた第6トランジスタ(P6)を通じて第2電源電圧(VGL)の伝達を受けてターンオンすれば、前記出力端に第1電源電圧(VGH)をj番目画素ラインに伝達される第1走査信号(Gi[j])として出力する。

【0132】

第1キャパシタ(C1)は、第8トランジスタ(P8)のゲート電極、第5トランジスタ(P5)のゲート電極、第6トランジスタ(P6)のドレイン電極、及び第4トランジスタ(P4)のドレイン電極との接続点(Q1)と接続される一電極、及び第1電源電圧(VGH)に接続される他電極を含む。

【0133】

第2キャパシタ(C2)は、第7トランジスタ(P7)のゲート電極と接続する一電極、並びに第8トランジスタ(P8)のドレイン電極、第7トランジスタ(P7)のドレイン電極、及び第1シフトレジスタ301の出力端に接続する他電極を含む。

【0134】

第2キャパシタ(C2)の一電極と第7トランジスタ(P7)のゲート電極との接続点(Q2)では、第7トランジスタ(P7)のスイッチング動作を制御する電圧が伝達される。

【0135】

j段の第2シフトレジスタ303は、第1シフトレジスタ301の第3トランジスタ(P3)乃至第8トランジスタ(P8)にそれぞれ対応する第9トランジスタ(P9)乃至第14トランジスタ(P14)を含んで同一に構成される。

【0136】

また、第2シフトレジスタ303は、第1シフトレジスタ301の第1キャパシタ(C1)及び第2キャパシタ(C2)にそれぞれ対応する第3キャパシタ(C3)及び第4キャパシタ(C4)を同一に含む。

【0137】

10

20

30

40

50

但し、第1シフトレジスタ301に伝達される第1クロック信号( $c_{1k1}$ )、第2クロック信号( $c_{1k2}$ )、及び第1初期化信号( $I_{nt1}$ )に対応して、第2シフトレジスタ303には第2クロック信号( $c_{1k2}$ )、第1クロック信号( $c_{1k1}$ )、及び第2初期化信号( $I_{nt2}$ )が伝達される。

## 【0138】

図5に示した走査駆動装置において、 $j$ 段の第1シフトレジスタ301及び第2シフトレジスタ303の構成は、同様に次の段の $j+1$ 段の第1シフトレジスタ401及び第2シフトレジスタ403にも適用される。

## 【0139】

しかし、第1クロック信号( $c_{1k1}$ )と第2クロック信号( $c_{1k2}$ )相互間、及び第1初期化信号( $I_{nt1}$ )と第2初期化信号( $I_{nt2}$ )相互間が互いに変わって入力される。 10

## 【0140】

具体的な構成は、既に $j$ 段の第1シフトレジスタ301及び第2シフトレジスタ303で説明したので省略する。

## 【0141】

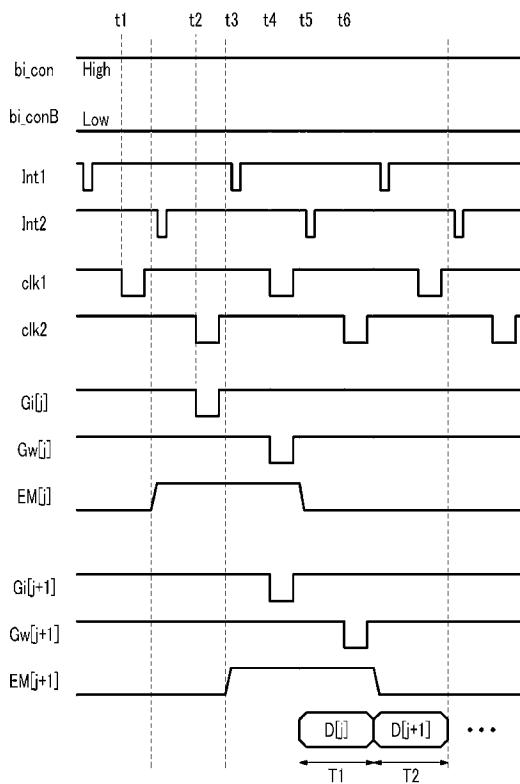

図5による実施形態の走査駆動装置が動作する駆動信号波形図を、図6及び図7に示した。

## 【0142】

図6は、本発明の一実施形態に係る走査駆動装置の順方向駆動による駆動信号波形図であり、図7は逆方向駆動による駆動信号波形図である。 20

## 【0143】

図6及び図7において、 $T_1$ 、 $T_2$ 、 $T_{10}$ 、 $T_{20}$ のような期間が1水平周期(1H)であると仮定し、図6及び図7による信号波形図において、第1クロック信号( $c_{1k1}$ )、第2クロック信号( $c_{1k2}$ )、第1初期化信号( $I_{nt1}$ )、及び第2初期化信号( $I_{nt2}$ )の一周期は、それぞれ2水平周期とする。

## 【0144】

まず、走査駆動装置の順方向駆動による信号波形図を示した図6を参照すれば、走査駆動装置が動作する期間の間に、順方向駆動制御信号( $b_{i\_conB}$ )はロー電圧レベルであり、逆方向駆動制御信号( $b_{i\_con}$ )は順方向駆動制御信号( $b_{i\_conB}$ )が反転したハイ電圧レベルであることが分かる。 30

## 【0145】

したがって、順方向駆動制御信号( $b_{i\_conB}$ )が伝達される第1シフトレジスタ301の第1トランジスタ( $P_1$ )がターンオンされ、逆方向駆動制御信号( $b_{i\_co}$ )が伝達される第1シフトレジスタ301の第2トランジスタ( $P_2$ )はターンオフされる。

## 【0146】

時点 $t_1$ で第1クロック信号( $c_{1k1}$ )がローレベルのパルスで伝達される時、第3トランジスタ( $P_3$ )がターンオンすれば、第1トランジスタ( $P_1$ )を通過して伝達される $j-1$ 段の第1シフトレジスタの第1走査信号( $G_{i[j-1]}$ )のロー電圧レベルが、第7トランジスタ( $P_7$ )のゲート電極に伝達される。これにより、時点 $t_2$ で第7トランジスタ( $P_7$ )がターンオンすれば、第2クロック信号( $c_{1k2}$ )が第7トランジスタ( $P_7$ )を通過して第1シフトレジスタ301の出力端に伝達され、第1走査信号( $G_{i[j]}$ )として生成される。つまり、 $j$ 番目画素ラインの複数の画素それぞれに伝達される第1走査信号( $G_{i[j]}$ )の電圧レベルは、第2クロック信号( $c_{1k2}$ )の電圧レベルによる。 40

## 【0147】

一方、時点 $t_1$ ～時点 $t_2$ の期間の間に第1トランジスタ( $P_1$ )を通過して伝達される $j-1$ 段の第1シフトレジスタの第1走査信号( $G_{i[j-1]}$ )は、ロー電圧レベルで第4トランジスタ( $P_4$ )のゲート電極にも同時に伝達される。 50

## 【0148】

これにより、第4トランジスタ(P4)がターンオンされて第1電源電圧(VGH)を第8トランジスタ(P8)のゲート電極に伝達し、第8トランジスタ(P8)がターンオフされる。これにより、第8トランジスタ(P8)を通じてハイ電圧レベルの第1電源電圧(VGH)が出力されず、j段第1シフトレジスタ301の出力端信号(Gi[j])は第2クロック信号(c1k2)の電圧レベルに基づくようになる。

## 【0149】

次に、j段第1シフトレジスタ301の第1走査信号(Gi[j])が出力された後の時点t3で、第1初期化信号(Init1)はローレベルパルスで伝達される。

## 【0150】

第1初期化信号(Init1)が伝達された第6トランジスタ(P6)は、それに対応してスイッチングターンオンされて、ロー電圧レベルである第2電源電圧(VGL)を接続点(Q1)に伝達する。

10

## 【0151】

ロー電圧レベルである第2電源電圧(VGL)が印加される第5トランジスタ(P5)と第8トランジスタ(P8)はそれぞれターンオンされるが、第5トランジスタ(P5)を通じてハイ電圧レベルである第1電源電圧(VGH)が接続点(Q2)に伝達され、第8トランジスタ(P8)を通じてハイ電圧レベルである第1電源電圧(VGH)がj段の第1シフトレジスタ301の出力端信号(Gi[j])として伝達される。したがって、時点t3で出力端信号(Gi[j])はハイレベルに変わる。この時、第5トランジスタ(P5)を通じて接続点(Q2)に伝達された第1電源電圧(VGH)は第7トランジスタ(P7)のゲート電極に印加されて、第7トランジスタ(P7)をターンオフさせる。

20

## 【0152】

上述した駆動方式と同一な方式でj段の第1シフトレジスタ301の出力端信号である第1走査信号(Gi[j])が入力信号として伝達されたj段の第2シフトレジスタ303が駆動される。

## 【0153】

つまり、時点t2でローレベルパルスで伝達される第2クロック信号(c1k2)によって第9トランジスタ(P9)がターンオンすれば、ロー電圧レベルの第1走査信号(Gi[j])が第13トランジスタ(P13)のゲート電極に伝達されて、第13トランジスタ(P13)をターンオンさせる。これにより、時点t4で第1クロック信号(c1k1)の電圧レベルが第13トランジスタ(P13)を通じてj段の第2シフトレジスタ303の出力端に伝達され、第1クロック信号(c1k1)の電圧レベルが第2走査信号(Gw[j])の電圧レベルになる。

30

## 【0154】

j段の第1シフトレジスタ301から出力される第1走査信号(Gi[j])と、j段の第2シフトレジスタ303から出力される第2走査信号(Gw[j])とは、時点t2～時点t4の期間ほど位相差を有して、j番目画素ラインの第1走査線及び第2走査線にそれぞれ伝達される。

40

## 【0155】

図6において、前記位相差は、第1クロック信号(c1k1)と第2クロック信号(c1k2)の位相差である半周期(1水平周期)の期間であって、実施形態によって多様に調整できるのはもちろんである。

## 【0156】

j番目画素ラインの第1走査線及び第2走査線を通じて第1走査信号(Gi[j])と第2走査信号(Gw[j])が伝達される間に、j番目画素ラインの複数の画素が選択され、発光制御信号(EM[j])はハイレベルに維持される。この期間の間に複数の画素それぞれは、第1走査信号(Gi[j])によって保存された映像データ電圧を初期化し、次いで第2走査信号(Gw[j])によって新しく表示される映像データ信号によるデータ電圧の印加を受ける。この期間の間に発光制御信号(EM[j])はハイレベルに維持されるので

50

、発光が行われない。第2走査信号( $G_w[j]$ )が伝達された後に発光制御信号( $E_M[j]$ )がローレベルに変化すれば、当該画素の有機発光ダイオードが印加されたデータ電圧に対応して発光する。

#### 【0157】

一方、順方向に駆動される本発明の一実施形態に係る走査駆動装置において、時点 $t_2$ に $j$ 段の第1シフトレジスタ301の出力端信号である第1走査信号( $G_i[j]$ )は、次の段の $j+1$ 段の第1シフトレジスタ401の入力信号として伝達される。この時、時点 $t_2$ で $j+1$ 段の第1シフトレジスタ401にロー電圧レベルの第2クロック信号( $c_{1k2}$ )が同時に伝達されるので、上述した駆動過程と同一の過程を経て、時点 $t_4$ で $j+1$ 段の第1シフトレジスタ401の出力端に、第1クロック信号( $c_{1k1}$ )に対応する電圧レベルが $j+1$ 段の第1走査信号( $G_i[j+1]$ )として出力される。

10

#### 【0158】

これにより、 $j+1$ 段の第1走査信号( $G_i[j+1]$ )が入力信号として伝達される $j+1$ 段の第2シフトレジスタ403は、 $j$ 段の第2シフトレジスタ303と同様な駆動方式により、時点 $t_6$ で第2クロック信号( $c_{1k2}$ )に対応する電圧レベルを有する $j+1$ 段の第2走査信号( $G_w[j+1]$ )を出力する。

#### 【0159】

図7は、図5に示した実施形態に係る走査駆動装置20を逆方向に駆動させた時の信号波形図である。

#### 【0160】

図7は、図6のような方式で走査駆動装置に含まれている各シフトレジスタが動作するので、詳しい説明は省略する。

#### 【0161】

但し、図7は逆方向駆動であるので、所定の駆動期間の間に逆方向駆動制御信号( $b_i\_c\_on$ )はロー電圧レベルであり、順方向駆動制御信号( $b_i\_c\_onB$ )はそれに反転したハイ電圧レベルであるので、各段の第1シフトレジスタは、逆方向駆動制御信号( $b_i\_c\_on$ )に対応してターンオンされたトランジスタを通じ、下段の第1走査信号を入力信号として伝達を受けるようになる。

#### 【0162】

また、図7の波形図は、第1走査信号及び第2走査信号の発生順序が、下段である $j+1$ 段のシフトレジスタを通じて先に生成された後、上段である $j$ 段のシフトレジスタを通じて生成される。

#### 【0163】

$j+1$ 段の第1シフトレジスタ401が先に駆動して、時点 $t_20$ で $j+1$ 段の第1走査信号( $G_i[j+1]$ )を出力すれば、 $j+1$ 段の第1走査信号( $G_i[j+1]$ )は $j+1$ 段の第2シフトレジスタ403の入力端に伝達されて、時点 $t_{40}$ で $j+1$ 段の第2走査信号( $G_w[j+1]$ )を出力する。

#### 【0164】

それと同時に、逆方向駆動方式であるので、 $j+1$ 段の第1走査信号( $G_i[j+1]$ )が時点 $t_{20}$ で $j$ 段の第1シフトレジスタ301の入力端に伝達されて、時点 $t_{40}$ で $j$ 段の第1走査信号( $G_i[j]$ )を出力する。

#### 【0165】

これにより、 $j$ 段の第1走査信号( $G_i[j]$ )は、時点 $t_{40}$ で $j$ 段の第2シフトレジスタ303の入力端に伝達されて、時点 $t_{60}$ で $j$ 段の第2走査信号( $G_w[j]$ )を出力する。

#### 【0166】

図5の本発明の一実施形態に係る走査駆動装置は、図6及び図7の駆動波形図から分かるように、順方向及び逆方向の方向性に無関係に、常に第1走査信号を先に生成及び出力して、第2走査信号を生成及び出力する。

#### 【0167】

10

20

30

40

50

これは、前記生成された第1走査信号を、前の段または次の段の第1シフトレジスタ及び当該段の第2シフトレジスタでそれぞれ同時に入力信号として伝達を受けて、前の段または次の段の第1走査信号と当該段の第2走査信号を同時に生成するので可能である。

#### 【0168】

従って本発明の一実施形態に係る走査駆動装置によれば、両方向の駆動に多様に適用することができるので、両方向駆動の表示装置の使用便宜性を向上することができる。

#### 【0169】

図8は、本発明の一実施形態に係る表示装置の画素の回路図を示す。特に、図1に示した表示装置に含まれている本発明の一実施形態に係る走査駆動装置20から伝達された走査信号によって駆動される画素の回路図である。

10

#### 【0170】

具体的に、表示部10に含まれている複数の画素ラインのうち、j番目画素ラインに含まれている複数の画素のうちの走査駆動装置20と接続された第1走査線( $G_{ij}$ )及び第2走査線( $G_{wj}$ )と接続し、発光制御駆動部40と接続された発光制御線( $E_{Mj}$ )と接続され、データ駆動部30と接続された複数のデータ線のうちのk番目データ線( $D_k$ )に接続された画素200を一例として説明する。

#### 【0171】

図8に示した回路図は一つの実施形態を示したものであり、必ずしもこのような回路構造に制限されることはもちろんである。また、画素200を構成する複数のトランジスタはPMOSトランジスタ(PMOS)として例示したが、NMOSトランジスタ(NMOS)で実現することも可能である。

20

#### 【0172】

図8の画素200は、初期化電圧( $V_{INT}$ )と駆動トランジスタ(TR1)のゲート電極の間に接続された初期化トランジスタ(TR4)、駆動電源電圧( $E_{LVD}\text{DD}$ )と有機発光ダイオード(LED)のアノード電極の間に接続された駆動トランジスタ(TR1)、駆動トランジスタ(TR1)のソース電極と対応するデータ線に接続されたスイッチングトランジスタ(TR2)、及び駆動トランジスタ(TR1)のドレイン電極と有機発光ダイオード(LED)のアノード電極の間に接続された発光制御トランジスタ(TR6)を含む。

#### 【0173】

具体的に、初期化トランジスタ(TR4)は、第1走査信号( $G_{i[j]}$ )に対応して初期化電圧( $V_{INT}$ )を駆動トランジスタ(TR1)のゲート電極に伝達して、駆動トランジスタ(TR1)のゲート電極の電圧値を初期化させる。

30

#### 【0174】

スイッチングトランジスタ(TR2)は、第2走査信号( $G_{w[j]}$ )に対応してスイッチング動作が制御され、対応するデータ線を通じてデータ信号( $data[k]$ )を駆動トランジスタ(TR1)に伝達する。

#### 【0175】

図8の実施形態に係る本発明の画素200は、駆動トランジスタ(TR1)のゲート電極とドレイン電極の間に接続されたスイッチ(TR3)をさらに含むことができる。スイッチ(TR3)のゲート電極に第2走査信号( $G_{w[j]}$ )が同時に伝達され、それに対応してスイッチ(TR3)が動作する。

40

#### 【0176】

スイッチ(TR3)がターンオンされる時に、駆動トランジスタ(TR1)はダイオード接続してしきい電圧を補償するようになる。

#### 【0177】

したがって、スイッチングトランジスタ(TR2)とスイッチ(TR3)は、それぞれゲート電極に同一の第2走査信号( $G_{w[j]}$ )が伝達され、それに対応してスイッチング動作するので、駆動トランジスタ(TR1)のしきい電圧が補償される期間の間に画素200にデータ信号が伝達される。

50

## 【0178】

これにより、駆動トランジスタ（TR1）は、スイッチングトランジスタ（TR2）を通じて伝達されたデータ信号（data[k]）に対応する駆動電流を有機発光ダイオード（OLED）に伝達する。

## 【0179】

発光制御トランジスタ（TR6）は駆動トランジスタ（TR1）のドレイン電極と有機発光ダイオード（OLED）のアノード電極との間で、発光制御信号（EM[j]）がゲート電極に伝達されてスイッチング動作を行い、前記データ信号に対応する駆動電流に有機発光ダイオード（OLED）を発光させる。

## 【0180】

図8の実施形態によれば、駆動電源電圧（ELVDD）と駆動トランジスタ（TR1）のソース電極との間に発光制御トランジスタ（TR5）を追加的にさらに含むことができる。

## 【0181】

図5乃至図7の走査駆動装置の回路図と信号波形図で説明した通り、走査駆動装置の駆動方向が順方向または逆方向であっても画素200の発光制御トランジスタ（TR4）に供給される第1走査信号（Gi[n]）が、画素200のスイッチングトランジスタ（TR2）とスイッチ（TR3）に供給される第2走査信号（Gw[n]）より先に伝達されるので、画素200は常に安定的に初期化電圧（VINT）によってリセットされた後、駆動トランジスタ（TR1）のしきい電圧を補償し、データ信号の伝達を受けて表示できるよう駆動される。

## 【0182】

以上、本発明の具体的な実施形態と関連して本発明を説明したが、これは例示に過ぎず、本発明はこれに制限されない。当業者は本発明の範囲を逸脱せずに、説明された実施形態を変更または変形することができ、このような変更または変形も本発明の範囲に属する。また、明細書で説明した各構成要素の物質は、当業者が公知された多様な物質から容易に選択して代替できる。また、当業者は本明細書で説明された構成要素のうちの一部を性能の劣化なしに省略したり、性能を改善するために構成要素を追加することができる。これだけでなく、当業者は工程環境や装備によって本明細書で説明した方法段階の順序を変更することもできる。従って、本発明の範囲は、説明された実施形態でなく、特許請求の範囲及びその均等物によって決定されなければならない。

## 【符号の説明】

## 【0183】

- 10 表示部

- 20 走査駆動装置

- 30 データ駆動部

- 40 発光制御駆動部

- 50 信号制御部

- 60 電源供給部

- 100 表示装置

- 200 画素

10

20

30

40

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 張 桓 壽

大韓民国京畿道龍仁市器興区農書洞山24 三星モバイルディスプレイ株式會社内

(72)発明者 鄭 鎮 泰

大韓民国京畿道龍仁市器興区農書洞山24 三星モバイルディスプレイ株式會社内

(72)発明者 嚴 基 明

大韓民国京畿道龍仁市器興区農書洞山24 三星モバイルディスプレイ株式會社内

F ターム(参考) 5C080 AA06 BB05 CC03 EE23 FF11 JJ02 JJ03 JJ04 KK07 KK43

5C380 AA01 AB06 AB34 AC11 CA12 CB01 CB16 CB17 CB26 CB30

CC06 CC07 CC26 CC27 CC33 CC39 CC52 CC55 CC64 CD026

CF08 DA02 DA06 DA26 DA47

|                |                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 双向扫描驱动装置和使用该装置的显示装置                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2012048186A</a>                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2012-03-08 |

| 申请号            | JP2010272805                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2010-12-07 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 三星移动显示的股票会社                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 張桓壽<br>鄭鎮泰<br>嚴基明                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 发明人            | 張桓壽<br>鄭鎮泰<br>嚴基明                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G09G3/30 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | G09G3/3225 G09G2310/0283 G09G2320/028                                                                                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/30.J G09G3/20.622.E G09G3/20.622.R G09G3/20.660.F G09G3/20.680.S G09G3/3233 G09G3 /3266 G09G3/3291                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/CC03 5C080/EE23 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080 /JJ04 5C080/KK07 5C080/KK43 5C380/AA01 5C380/AB06 5C380/AB34 5C380/AC11 5C380/CA12 5C380/CB01 5C380/CB16 5C380/CB17 5C380/CB26 5C380/CB30 5C380/CC06 5C380/CC07 5C380 /CC26 5C380/CC27 5C380/CC33 5C380/CC39 5C380/CC52 5C380/CC55 5C380/CC64 5C380/CD026 5C380/CF08 5C380/DA02 5C380/DA06 5C380/DA26 5C380/DA47 |         |            |

| 代理人(译)         | 三好秀<br>伊藤雅一                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 优先权            | 1020100082514 2010-08-25 KR                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 其他公开文献         | <a href="#">JP5813311B2</a>                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                           |         |            |

### 摘要(译)

提供一种能够在系统中实现各种应用的扫描驱动器，在该系统中，传输到有机发光二极管显示装置的显示单元中包括的像素的扫描信号在两个方向上传输和驱动。根据本发明示例性实施例的扫描驱动装置是产生至少两个不同的扫描信号并将其传输到包括多个像素的显示单元的扫描驱动装置。扫描信号包括多个顺序驱动单元，每个顺序驱动单元包括产生不同的扫描信号的多个移位寄存器，并且由预定移位寄存器生成的扫描信号作为输入信号被发送到下一个移位寄存器。是上级顺序驱动单元的移位寄存器或与包括预定移位寄存器的顺序驱动单元相邻的下一级顺序驱动单元的移位寄存器，对应于确定的扫描驱动器的驱动方向。作为输入信号传输到移位寄存器。[\[选型图\]图1](#)