(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-301934

(P2009-301934A)

(43) 公開日 平成21年12月24日(2009.12.24)

(51) Int.Cl.

H05B 33/10 (2006.01)

H01L 51/50 (2006.01)

F 1

H05B 33/10

H05B 33/14

テーマコード(参考)

3K107

A

審査請求 未請求 請求項の数 1 O L (全 7 頁)

(21) 出願番号

特願2008-156668 (P2008-156668)

(22) 出願日

平成20年6月16日 (2008.6.16)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100096828

弁理士 渡辺 敏介

(74) 代理人 100110870

弁理士 山口 芳広

(72) 発明者 須貝 浩士

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 吉永 秀樹

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

F ターム(参考) 3K107 AA01 CC45 GG57

(54) 【発明の名称】有機EL表示装置の製造方法

## (57) 【要約】

**【課題】**有機EL表示装置のショート欠陥をオープン破壊するにあたって、有機EL表示装置の欠陥や機能の低下を来すことなく、生産性が高い有機EL表示装置の製造方法を提供する。

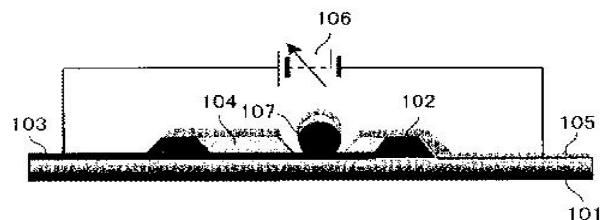

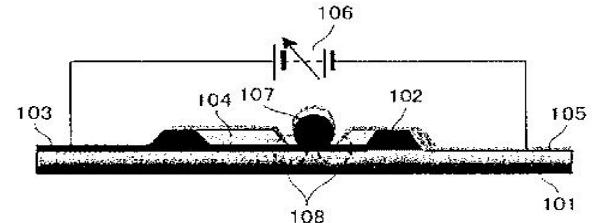

**【解決手段】**第一の電極103を有する基板101上に、有機EL層104と、第二の電極105とを形成する。第二の電極を形成する際に、第一の電極103と第二の電極105との間に、それぞれの取出電極部を介して電圧を印加しながら行い、成膜時に発生する欠陥(初期のショート欠陥108)をオープン破壊する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

第一の電極を有する基板上に、有機EL層と、第二の電極とを形成した有機EL表示装置の製造方法において、

前記第一の電極と前記第二の電極との間に、それぞれの取出電極部を介して電圧を印加しながら前記第二の電極を形成して、成膜時に発生する欠陥をオープン破壊することを特徴とする有機EL表示装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

10

本発明は、有機EL表示装置の製造方法に関するものである。

**【背景技術】****【0002】**

有機EL表示装置は、自発光性で視認性が高く、液晶表示素子に比べて薄型軽量化が可能であるため、近年盛んに開発が進められている。有機EL表示装置は、第一の電極と発光層を含む有機EL層と第二の電極との積層構造をなす有機EL素子の集合体で構成され、それぞれの電極は外部回路と接続するための取出電極部と導通がとられている。

**【0003】**

このような有機EL表示装置の例として、互いに直交する陽極線と陰極線との交点位置に有機EL素子をマトリクス状に配置したパッシブマトリックス式表示装置が提案されている。また他の例として、マトリクス状に配置した有機EL素子のそれぞれに TFT を付加して制御するアクティブマトリックス式表示装置が提案されている。

20

**【0004】**

有機EL表示装置は、第一の電極と第二の電極のショートが原因となって、当該画素に駆動電流が流れなくなり、非点灯画素となる欠陥を生じることが知られている。

**【0005】**

このような不都合に対処するため、ショート箇所を分断し欠陥防止を行おうとする提案がある（特許文献1参照）。また、完成された一対の電極間に電圧を印加するエージング処理を行って、ショート欠陥をオープン破壊させて欠陥防止を行おうとする提案がある（特許文献2参照）。

30

**【0006】**

【特許文献1】特開2004-199970号公報

【特許文献2】特開2003-282253号公報

**【発明の開示】****【発明が解決しようとする課題】****【0007】**

上述した第一の電極と第二の電極のショートの原因としては次の三つの形態が考えられる。まず初めに、第一の電極の表面粗度異常がある。第一の電極形成時の異常による電極表面の凹凸形状と想定される。この種の異常は、電極形成後の検査で除外されることが多く、実際の有機EL表示装置の製造工程ではほとんど見られない。

40

**【0008】**

次に、有機EL層のピンホールによるものがある。有機EL層の蒸着時の異常によるものと想定され、蒸着材料と第一の電極間の界面密着不良、または異物が介在するも密着が弱く有機材料の一部を伴って脱落したものなどが考えられる。実際には、有機EL層は複数の機能層の積層構造体であるため、第一の電極が露出するほどのピンホールを生じることは稀である。

**【0009】**

最後に、第一の電極上への異物等の付着によるものがある。蒸着堆積膜には異方性があるため、異物周りの側面及び異物に遮られた第一の電極上には蒸着層の断層が形成され、第一の電極の一部が露出することがある。この部分に第二の電極が堆積形成されると、シ

50

ヨート欠陥となる。実際の有機EL表示装置の製造工程では、この種の異常が大半を占める。

#### 【0010】

一般に、有機EL層は、全体でも膜厚が数100nm以下であるため、電極間に異物が介在することでショートが発生しやすい。しかも、第一の電極上においてサブミクロノオーダーの異物付着を防止するのは非常に困難であるため、非点灯画素欠陥の防止対策の大きな問題となっている。

#### 【0011】

これらの問題に対処するために、上述した特許文献1に記載された技術のように、ショート箇所を分断し欠陥防止を行おうとする提案がある。特許文献1に記載された方法は、全面点灯させた有機EL表示装置の非点灯画素を光学顕微鏡で捉えて位置を求める。そして、求められた位置に基づき、非点灯画素を赤外線温度画像検出顕微鏡で捉えて、発熱したショート箇所の位置を求める。さらに、求められた位置に基づき、ショート箇所を光学顕微鏡で捉えるとともに、光学顕微鏡と同一の光軸でレーザを照射して、発熱箇所であるショート箇所を分断するものである。

10

#### 【0012】

しかし、このような提案によると、非点灯画素欠陥を防止するために多大な時間と工程が必要となり、ひいてはパネルの製造コストを押し上げることになる。

#### 【0013】

一方で、上述した特許文献2に記載された技術のように、完成された一対の電極間に電圧を印加するエージング処理を行って、ショート欠陥をオープン破壊させ欠陥防止を行おうとする提案もある。オープン破壊とは、ショート欠陥を不導体化させることである。オープン破壊は、エージングの際に生じるジューク熱によって、当該膜欠陥部に対応する電極を破壊してオープン状態（絶縁状態）としたり、酸化して不導体化したりする等の現象により発生すると考えられる。

20

#### 【0014】

しかし、このような提案によると、一旦形成されたショート欠陥をオープン破壊するにはかなりの困難を伴う。パッシブマトリックス表示装置であれば、ショート欠陥を切ったと同時に素子が破損され、あるいは熱劣化してしまうことがある。アクティブマトリックス表示装置であれば、TFTの許容電流以下ではショート欠陥を破壊できる可能性が低くなる。

30

#### 【0015】

本発明は、上述した問題に鑑み提案されたもので、有機EL表示装置のショート欠陥をオープン破壊するにあたって、有機EL表示装置の欠陥や機能の低下を来すことなく、生産性が高い有機EL表示装置の製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0016】

本発明の有機EL表示装置の製造方法は、上述した目的を達成するため、以下の特徴点を備えている。すなわち、本発明の有機EL表示装置の製造方法は、第一の電極を有する基板上に、有機EL層と、第二の電極とを形成した有機EL表示装置の製造方法に関するものである。そして、前記第一の電極と前記第二の電極との間に、それぞれの取出電極部を介して電圧を印加しながら前記第二の電極を形成して、成膜時に発生する欠陥をオープン破壊することを特徴とするものである。

40

#### 【発明の効果】

#### 【0017】

本発明の有機EL表示装置の製造方法によれば、第一の電極と第二の電極との間にショート欠陥が形成される初期の段階で、ショート欠陥をオープン破壊することが可能となる。第二の電極形成初期の時点において、ショート欠陥は未だ分子レベルの微小なサイズにあることから、有機EL層の耐圧未満の電圧とわずかな電流で本操作は可能となる。そして、発生するジューク熱はわずかに抑えられ、周辺部への熱劣化の影響や画素ならびに配

50

線の断線はほとんど見られない。また、これら一連の初期のショート欠陥のオープン破壊のための工程は、第二の電極形成工程と並行して行うことができるので、新たな工程時間を省略することができる。

#### 【0018】

したがって、非点灯画素欠陥のない有機EL表示装置を、生産性良く製造することができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

以下、図面を参照して、本発明に係る有機EL表示装置の製造方法の実施形態を説明する。

10

#### 【0020】

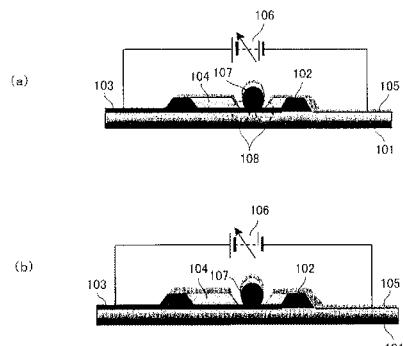

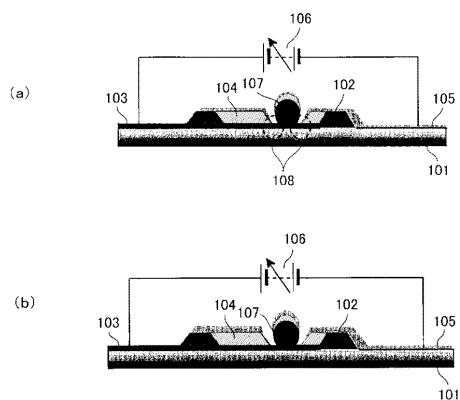

図1は、本発明の実施形態に係る有機EL表示装置の製造方法を説明するもので、(a)は初期のショート欠陥を有する有機EL表示装置の模式図、(b)はショート欠陥をオープン破壊した後の有機EL表示装置の模式図である。なお、図1において、101は基板、102は画素バンク、103は第一の電極、104は有機EL層、105は第二の電極(取出電極部を含む)、106は電源、107は異物、108は初期のショート欠陥をそれぞれ示す。

#### 【0021】

本発明の実施形態に係る製造方法で製造される有機EL表示装置は、第一の電極103を有する基板101上に、有機EL層104と、第二の電極105とが形成されている。そして、第一の電極103と第二の電極105との間に、それぞれの取出電極部を介して電源106から電圧を印加しながら第二の電極105を形成して、成膜時に発生するショート欠陥をオープン破壊するようになっている。

20

#### 【0022】

ショート欠陥は、一旦形成されてしまうとオープン破壊することが困難になる。例えば、図1(a)に示すように、異物107によって、初期のショート欠陥108が発生することがある。そこで、本発明の実施形態に係る有機EL表示装置の製造方法では、図1(a)に示すように、第二の電極105を形成する工程中に、有機EL層104を形成する有機材料の耐圧以下の微小な電圧を第一の電極103と第二の電極105の間に印加しておく。そして、第二の電極105が第一の電極103と分子レベルの接触をしたときには、微小なジユール熱の効果によってオープン破壊がなされ、図1(b)に示すように、非点灯画素欠陥を回避しながら第二の電極105が形成される。

30

#### 【0023】

次に、有機EL表示装置の表示形式に応じた駆動方法について説明する。

#### 【0024】

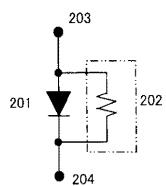

図2は、パッシブマトリックス方式の有機EL表示装置において、画素に初期のショート欠陥が付随した状態を示す画素回路図である。図2において、201は画素、202は初期のショート欠陥、203は陽極、204は陰極をそれぞれ示す。

#### 【0025】

図2に示すように、画素回路の陽極203及び陰極204は、それぞれ複数の画素201を取りまとめて、それぞれ基板上の任意の位置に配置された取出電極部(不図示)に接続されている。画素201と初期のショート欠陥202には、その取出電極部を介して複数の画素201をまとめて電圧が印加されている。陽極203と陰極204との間において初期のショート欠陥202が形成される過程で、ショート欠陥202が細いうちにオープン破壊が行われ、ショート欠陥202が途切れる。このときの電圧は、有機材料の耐圧以下であれば漸増、漸減させてもよく、また、第二の電極(陰極204)の形成開始から断続的に印加してもよい。

40

#### 【0026】

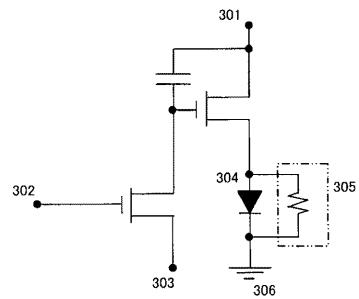

図3は、アクティブマトリックス方式の有機EL表示装置において、画素に初期のショート欠陥が付随した状態を示す画素回路図である。なお、図3において、301は陽極、

50

302はパルス信号、303はビデオ電流信号、304は画素、305は初期のショート欠陥、306は陰極をそれぞれ示す。

#### 【0027】

図3に示すように、画素回路の陽極301及び陰極306は、それぞれ複数の画素304を取りまとめて、それぞれ基板上の任意の位置に配置された取出電極部(不図示)に接続されている。また、パルス信号302及びビデオ電流信号303を与え、画素304と初期のショート欠陥305に電圧が印加される。陽極301と陰極306との間ににおいて初期のショート欠陥305が形成される過程で、ショート欠陥305が細いうちにオープン破壊が行われ、ショート欠陥305が途切れる。このときの電圧は、有機材料の耐圧以下であれば漸増、漸減させてもよく、また、第二の電極(陰極306)の形成開始から断続的に印加してもよい。

10

#### 【0028】

第二の電極の形成工程は、真空成膜装置によるマスク成膜で行われる。この際、有機EL表示装置の取出電極部は、マスクで遮蔽された領域に存在する。この取出電極部のマスクにプローブを配備して、不要部分は絶縁化処理を講じることにより、成膜中の電圧印加が可能となる。

#### 【0029】

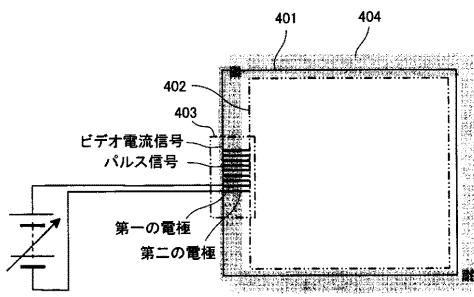

図4は、アクティブマトリックス方式の有機EL表示装置におけるマスク成膜を示す模式図である。なお、図4において、401は基板、402は第二の電極成膜領域、403は取出電極部、404はマスクをそれぞれ示す。

20

#### 【0030】

図4に示すように、マスク404の取出電極部403に独立して必要な電力及び信号を与えることで、初期のショート欠陥のオープン破壊が可能となる。複数枚の有機EL表示装置を配置したアレイ基板においては、複数枚分の取出電極部403を集約してから、電力及び信号を供給してもかまわない。

#### 【実施例】

#### 【0031】

次に、具体的な実施例について説明する。

#### 【0032】

#### 【実施例1】

実施例1として、2インチ角のTFT基板の上に、以下に示す公知の材料を用いて有機EL表示装置を作製した。すなわち、第一の電極としてCrを配設したTFT基板に、UV／オゾン洗浄処理を施した上に、正孔輸送層、発光層、電子輸送層、電子注入層からなる有機発光層を、それぞれ以下に示す材料によって真空蒸着法で形成した。

30

#### 【0033】

正孔輸送層として、NPDを50nmの膜厚で成膜した。

#### 【0034】

発光層として、アルミキレート錯体(A1q<sub>3</sub>)とクマリン6を100:6の重量比率で共蒸着し50nmの膜厚で形成した。

40

#### 【0035】

電子輸送層として、フェナントロリン化合物を10nmの膜厚で形成した。

#### 【0036】

さらに、電子注入層として、上記のフェナントロリン化合物と炭酸セシウムCs<sub>2</sub>CO<sub>3</sub>を100:1の重量比で共蒸着し40nmの膜厚で形成した。

#### 【0037】

この上に、第二の電極として、スパッタリング法によるITO薄膜を、圧力1.6Pa、電力700W、Arガス40sccm, O<sub>2</sub>ガス0.1sccmの条件で形成した。スパッタチャンバーには、基板の取出電極部にプローブを配備して、信号には全面点灯の信号を供給し、電源線には最大15Vを供給しながら成膜を行った。第二の電極は、60秒間で60nmの膜厚になるよう成膜した。電圧印加は、成膜10秒後から0.3V/sの

50

勾配で電源電圧を50秒間昇圧し、成膜後10秒間は15Vを維持して画素を形成した。

【0038】

その後、封止ガラスで表示画素部を封止して、有機EL表示装置を完成させた。

【0039】

このようにして作製した有機EL表示装置を点灯しながら、光学顕微鏡（倍率200倍）で全面観察し、非点灯画素の計数を行ったところ、3箇所の非点灯画素と100個以上の発光画素内黒点が計数された。発光画素内の黒点を観察したところ、黒点周りにはオープン破壊で絶縁化された領域が存在することが確認された。

【0040】

[比較例1]

比較例1として、基板に対して電圧無印加で第二の電極形成を行うこと以外は、実施例1と同様の方法で、有機EL表示装置を作製した。このようにして作製した有機EL表示装置を、実施例1と同様の方法で観察し、非点灯画素の計数を行ったところ、100個以上の非点灯画素が計数された。このように、比較例1は、実施例1に比べて非点灯画素数が多いことがわかった。

10

【図面の簡単な説明】

【0041】

【図1】(a)は初期のショート欠陥を有する有機EL表示装置の模式図、(b)はショート欠陥をオープン破壊した後の有機EL表示装置の模式図。

【図2】パッシブマトリックス方式の有機EL表示装置において、画素に初期のショート欠陥が付随した状態を示す画素回路図。

20

【図3】アクティブマトリックス方式の有機EL表示装置において、画素に初期のショート欠陥が付随した状態を示す画素回路図。

【図4】アクティブマトリックス方式の有機EL表示装置におけるマスク成膜を示す模式図。

【符号の説明】

【0042】

101 基板

102 画素バンク

103 第一の電極

30

104 有機EL層

105 第二の電極（取出電極部を含む）

106 電源

107 異物

108 ショート欠陥

201 画素

202 ショート欠陥

203 陽極

204 陰極

301 陽極

40

302 パルス信号

303 ビデオ電流信号

304 画素

305 ショート欠陥

306 陰極

401 基板

402 第二の電極成膜領域

403 取出電極部

404 マスク

【図1】

【図3】

【図2】

【図4】

|                |                                  |         |            |

|----------------|----------------------------------|---------|------------|

| 专利名称(译)        | 有机EL表示装置の制造方法                    |         |            |

| 公开(公告)号        | <a href="#">JP2009301934A</a>    | 公开(公告)日 | 2009-12-24 |

| 申请号            | JP2008156668                     | 申请日     | 2008-06-16 |

| [标]申请(专利权)人(译) | 佳能株式会社                           |         |            |

| 申请(专利权)人(译)    | 佳能公司                             |         |            |

| [标]发明人         | 須貝 浩士<br>吉永 秀樹                   |         |            |

| 发明人            | 須貝 浩士<br>吉永 秀樹                   |         |            |

| IPC分类号         | H05B33/10 H01L51/50              |         |            |

| F1分类号          | H05B33/10 H05B33/14.A            |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/CC45 3K107/GG57 |         |            |

| 代理人(译)         | 渡辺圭佑<br>山口 芳広                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>        |         |            |

### 摘要(译)

解决的问题：提供一种具有高生产率而不会在有机EL显示装置的短缺陷的公开破坏中引起有机EL显示装置的缺陷和功能劣化的高生产率的有机EL显示装置的制造方法。解决方案：在具有第一电极103的基板101上形成有机EL层104和第二电极105。当形成第二电极时，在第一电极103与第二电极105之间，通过各引出电极部施加电压的同时，在成膜时产生的缺陷（初期短缺陷的开放销毁108）。[选型图]图1