(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-288593

(P2009-288593A)

(43) 公開日 平成21年12月10日(2009.12.10)

| (51) Int.Cl.                | F 1            | テーマコード (参考) |

|-----------------------------|----------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J    | 3K107       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 624B | 5C080       |

| <b>H05B 33/08</b> (2006.01) | G09G 3/20 642B |             |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 611H |             |

|                             | HO5B 33/08     |             |

審査請求 未請求 請求項の数 3 O L (全 22 頁) 最終頁に続く

|           |                              |          |                                                 |

|-----------|------------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2008-142057 (P2008-142057) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号          |

| (22) 出願日  | 平成20年5月30日 (2008.5.30)       | (74) 代理人 | 100082131<br>弁理士 稲本 義雄                          |

|           |                              | (74) 代理人 | 100121131<br>弁理士 西川 孝                           |

|           |                              | (72) 発明者 | 妹尾 佑樹<br>東京都品川区西五反田3丁目9番17号<br>ソニーエンジニアリング株式会社内 |

|           |                              | (72) 発明者 | 内野 勝秀<br>東京都港区港南1丁目7番1号 ソニー株<br>式会社内            |

最終頁に続く

(54) 【発明の名称】パネルおよび駆動制御方法

## (57) 【要約】

【課題】画素ごとの輝度のばらつきを改善することができるようとする。

【解決手段】サンプリング用トランジスタ31のゲートgとソースsとの間に補助容量251を設けた場合、サンプリング用トランジスタ31の寄生容量Cwsが大となること等しい。サンプリング用トランジスタ31の寄生容量Cwsが大となるということは、フィールドスルーバイオード降下量自体は大きくなるが、画素201ごとのフィールドスルーバイオード降下量のばらつきは小さくなる。これにより、フィールドスルーバイオード降下による画素ごとの輝度のばらつきを改善することができる。本発明は、例えば、ELパネルに適用できる。

【選択図】図26

図26

## 【特許請求の範囲】

## 【請求項 1】

ダイオード特性を有し、駆動電流に応じて発光する発光素子と、

映像信号をサンプリングするサンプリング用トランジスタと、

前記駆動電流を前記発光素子に供給する駆動用トランジスタと、

前記発光素子のアノード側と前記駆動用トランジスタのゲートに接続され、所定の電位

を保持する保持容量と、

前記サンプリング用トランジスタのゲートとソースに接続され、所定の電位を保持する

補助容量と

を有する画素回路

を備えるパネル。

10

## 【請求項 2】

前記補助容量の静電容量は、前記サンプリング用トランジスタの寄生容量より大である

請求項 1 に記載のパネル

## 【請求項 3】

ダイオード特性を有し、駆動電流に応じて発光する発光素子と、映像信号をサンプリングするサンプリング用トランジスタと、前記駆動電流を前記発光素子に供給する駆動用トランジスタと、前記発光素子のアノード側と前記駆動用トランジスタのゲートに接続され、所定の電位を保持する保持容量と、前記サンプリング用トランジスタのゲートとソースに接続され、所定の電位を保持する補助容量とを有する画素回路を備えるパネルが、

20

発光させる輝度に対応する前記映像信号の信号電位を前記保持容量に供給する場合に、

前記サンプリング用トランジスタのゲートを高電位に設定し、

前記補助容量は、前記サンプリング用トランジスタのゲートが高電位に設定されたとき

、所定の電位を保持する

駆動制御方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、パネルおよび駆動制御方法に関し、特に、画素ごとの輝度のばらつきを改善

することができるようとするパネルおよび駆動制御方法に関する。

30

## 【背景技術】

## 【0002】

発光素子として有機 E L (Electro Luminescent) デバイスを用いた平面自発光型のパネル (E L パネル) の開発が近年盛んになっている。有機 E L デバイスは、ダイオード特性を有し、有機薄膜に電界をかけると発光する現象を利用したデバイスである。有機 E L デバイスは印加電圧が 10 V 以下で駆動するため低消費電力である。また有機 E L デバイスは自ら光を発する自発光素子であるため、照明部材を必要とせず軽量化及び薄型化が容易である。さらに有機 E L デバイスの応答速度は数 μ s 程度と非常に高速であるので、動画表示時の残像が発生しない。

40

## 【0003】

有機 E L デバイスを画素に用いた平面自発光型のパネルの中でも、とりわけ駆動素子として薄膜トランジスタを各画素に集積形成したアクティブマトリクス型のパネルの開発が盛んである。アクティブマトリクス型平面自発光パネルは、例えば以下の特許文献 1 乃至 5 に記載されている。

## 【0004】

- 【特許文献 1】特開 2003 - 255856 号公報

- 【特許文献 2】特開 2003 - 271095 号公報

- 【特許文献 3】特開 2004 - 133240 号公報

- 【特許文献 4】特開 2004 - 029791 号公報

- 【特許文献 5】特開 2004 - 093682 号公報

50

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

以上のような有機ELデバイスを画素に用いた平面自発光型のパネルについては、さらなる改良が求められており、例えば、画素ごとの輝度のばらつきを少なくすることが要求されている。

**【0006】**

本発明は、このような状況に鑑みてなされたものであり、画素ごとの輝度のばらつきを改善することができるようとするものである。

**【課題を解決するための手段】**

10

**【0007】**

本発明の一側面のパネルは、ダイオード特性を有し、駆動電流に応じて発光する発光素子と、映像信号をサンプリングするサンプリング用トランジスタと、前記駆動電流を前記発光素子に供給する駆動用トランジスタと、前記発光素子のアノード側と前記駆動用トランジスタのゲートに接続され、所定の電位を保持する保持容量と、前記サンプリング用トランジスタのゲートとソースに接続され、所定の電位を保持する補助容量とを有する画素回路を備える。

**【0008】**

20

本発明の一側面の駆動制御方法は、ダイオード特性を有し、駆動電流に応じて発光する発光素子と、映像信号をサンプリングするサンプリング用トランジスタと、前記駆動電流を前記発光素子に供給する駆動用トランジスタと、前記発光素子のアノード側と前記駆動用トランジスタのゲートに接続され、所定の電位を保持する保持容量と、前記サンプリング用トランジスタのゲートとソースに接続され、所定の電位を保持する補助容量とを有する画素回路を備えるパネルが、発光させる輝度に対応する前記映像信号の信号電位を前記保持容量に供給する場合に、前記サンプリング用トランジスタのゲートを高電位に設定し、前記補助容量は、前記サンプリング用トランジスタのゲートが高電位に設定されたとき、所定の電位を保持する。

**【0009】**

30

本発明の一側面においては、発光させる輝度に対応する映像信号の信号電位を保持容量に供給する場合に、サンプリング用トランジスタのゲートが高電位に設定され、補助容量において、所定の電位が保持される。

**【発明の効果】****【0010】**

本発明の一側面によれば、画素ごとの輝度のばらつきを改善することができる。

**【発明を実施するための最良の形態】****【0011】**

最初に、本発明の理解を容易にし、且つ、背景を明らかにするため、有機ELデバイスを用いたパネル（以下、ELパネルと称する）の基本となる構成と動作について図1乃至図12を参照して説明する。

**【0012】**

40

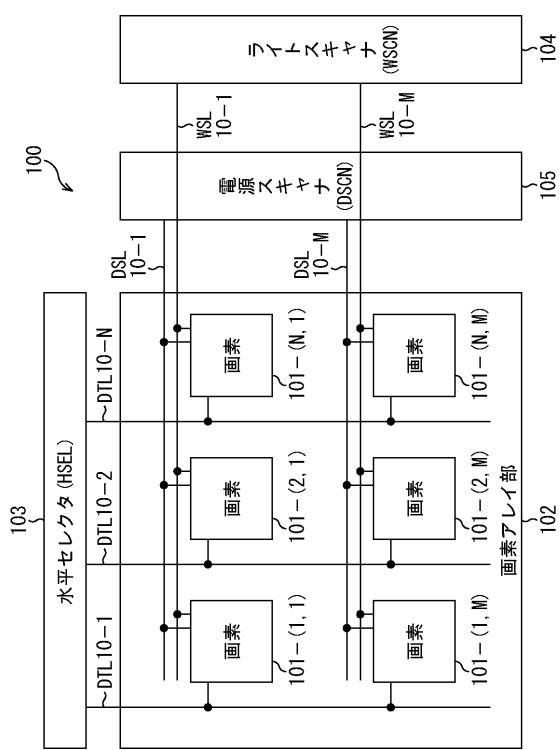

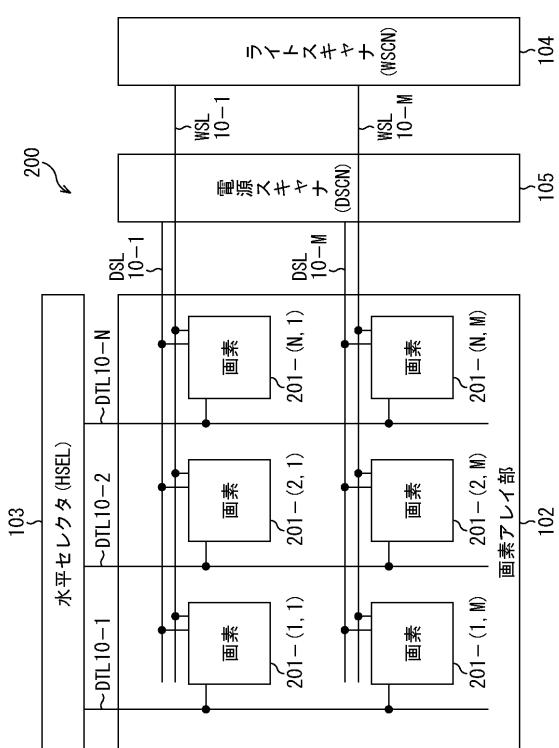

図1は、基本となるELパネルの構成例を示すブロック図である。

**【0013】**

図1のELパネル100は、N×M個の画素（画素回路）101-（1,1）乃至101-（N,M）が行列状に配置されている画素アレイ部102と、これを駆動する駆動部である水平セレクタ（HSEL）103、ライトスキャナ（WSCN）104、および電源スキャナ（DSCN）105とにより構成されている。

**【0014】**

また、ELパネル100は、M本の走査線WSL10-1乃至10-M、M本の電源線DSL10-1乃至10-M、およびN本の映像信号線DTL10-1乃至10-Nも有する。

50

## 【0015】

なお、以下において、走査線 WSL10-1 乃至 10-M、映像信号線 DTL10-1 乃至 10-N、画素 101-(1, 1) 乃至 101-(N, M)、または電源線 DSL10-1 乃至 10-M のそれぞれを特に区別する必要がない場合、単に、走査線 WSL10、映像信号線 DTL10、画素 101、または電源線 DSL10 と称する。

## 【0016】

画素 101-(1, 1) 乃至 101-(N, M) のうちの第 1 行目の画素 101-(1, 1) 乃至 101-(N, 1) は、走査線 WSL10-1 でライトスキャナ 104 と、電源線 DSL10-1 で電源スキャナ 105 とそれぞれ接続されている。また、画素 101-(1, 1) 乃至 101-(N, M) のうちの第 M 行目の画素 101-(1, M) 乃至 101-(N, M) は、走査線 WSL10-M でライトスキャナ 104 と、電源線 DSL10-M で電源スキャナ 105 とそれぞれ接続されている。画素 101-(1, 1) 乃至 101-(N, M) の行方向に並ぶその他の画素 101 についても同様である。10

## 【0017】

また、画素 101-(1, 1) 乃至 101-(N, M) のうちの第 1 列目の画素 101-(1, 1) 乃至 101-(1, M) は、映像信号線 DTL10-1 で水平セレクタ 103 と接続されている。画素 101-(1, 1) 乃至 101-(N, M) のうちの第 N 列目の画素 101-(N, 1) 乃至 101-(N, M) は、映像信号線 DTL10-N で水平セレクタ 103 と接続されている。画素 101-(1, 1) 乃至 101-(N, M) の列方向に並ぶその他の画素 101 についても同様である。20

## 【0018】

ライトスキャナ 104 は、走査線 WSL10-1 乃至 10-M に水平周期 (1H) で順次制御信号を供給して画素 101 を行単位で線順次走査する。電源スキャナ 105 は、線順次走査に合わせて電源線 DSL10-1 乃至 10-M に第 1 電位 (後述する Vcc) または第 2 電位 (後述する Vss) の電源電圧を供給する。水平セレクタ 103 は、線順次走査に合わせて各水平期間内 (1H) で映像信号となる信号電位 Vsig と基準電位 Vofs を切換えて列状の映像信号線 DTL10-1 乃至 10-M に供給する。

## 【0019】

図 1 のように構成される E-L パネル 100 に、ソースドライバおよびゲートドライバとからなるドライバ IC (Integrated Circuit) が付加されることによりパネルモジュールが構成され、さらに、パネルモジュールに、電源回路、画像 LSI (Large Scale Integration) などを付加したものが表示装置となる。E-L パネル 100 を含む表示装置は、例えば、携帯電話機、デジタルスチルカメラ、デジタルビデオカメラ、テレビジョン受像機、プリンタ等の表示部として使用することができる。30

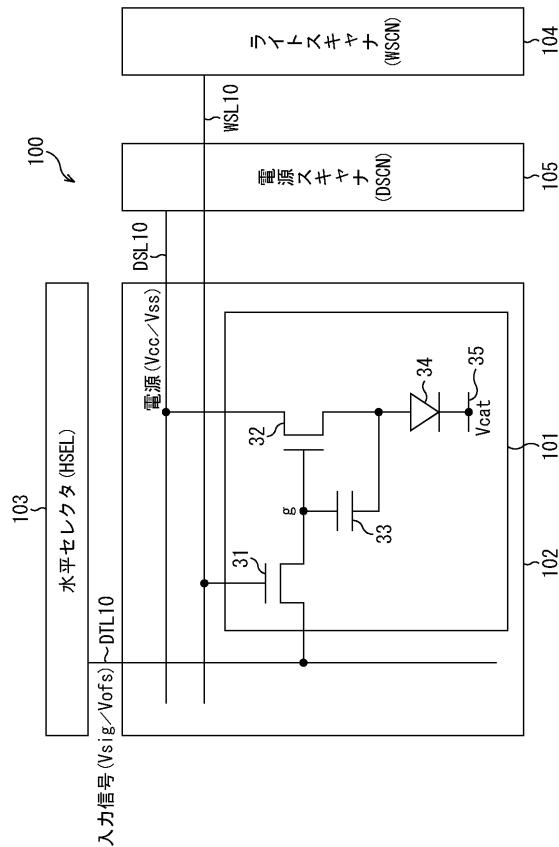

## 【0020】

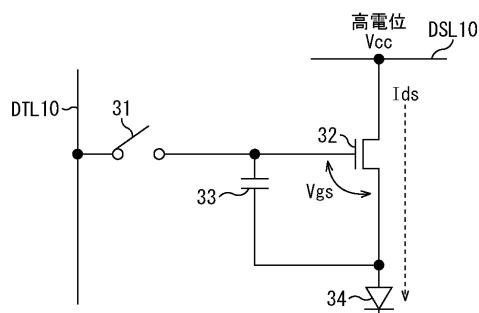

図 2 は、図 1 に示した E-L パネル 100 に含まれる N × M 個の画素 101 のうちの 1 つの画素 101 を拡大することにより、画素 101 の詳細な構成を示したブロック図である。。

## 【0021】

なお、図 2 において画素 101 と接続されている走査線 WSL10、映像信号線 DTL10、および電源線 DSL10 は、図 1 から明らかのように、画素 101-(n, m) (n = 1, 2, ..., N, m = 1, 2, ..., M) に対して、走査線 WSL10-(n, m)、映像信号線 DTL10-(n, m)、および電源線 DSL10-(n, m) となる。40

## 【0022】

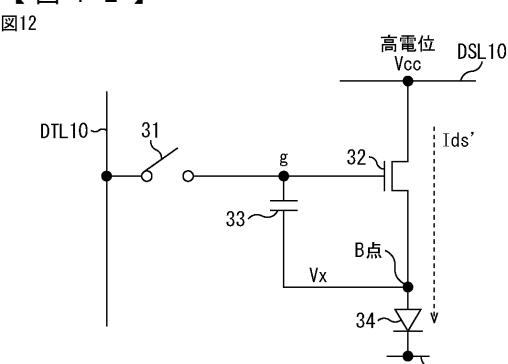

図 2 の画素 101 は、サンプリング用トランジスタ 31、駆動用トランジスタ 32、保持容量 33、および発光素子 34 を有する。サンプリング用トランジスタ 31 のゲートは走査線 WSL10 と接続され、サンプリング用トランジスタ 31 のドレインは映像信号線 DTL10 と接続されるとともに、ソースが駆動用トランジスタ 32 のゲート g と接続されている。50

## 【0023】

駆動用トランジスタ32のソースs及びドレインdの一方は発光素子34のアノードに接続され、他方が電源線DSL10に接続される。保持容量33は、駆動用トランジスタ32のゲートgと発光素子34のアノードに接続されている。また、発光素子34のカソードは所定の電位Vcatに設定されている配線35に接続されている。この電位VcatはGNDレベルであり、従って、配線35は接地配線である。以下、配線35を接地配線35と称する。

## 【0024】

サンプリング用トランジスタ31および駆動用トランジスタ32は、いずれもNチャネル型トランジスタであり、低温ポリシリコンよりも安価に作成できるアモルファスシリコンで作成することができるため、画素回路の製造コストをより安価にすることができる。

10

## 【0025】

有機EL素子はダイオード特性を有する電流発光素子であり、発光素子34は、供給される電流値IdSに応じた階調の発光を行う。

## 【0026】

以上のように構成される画素101において、サンプリング用トランジスタ31が、走査線WSL10から供給された制御信号に応じてオン（導通）すると、保持容量33は、映像信号線DTL10を介して水平セレクタ103から供給された電荷を蓄積して保持する。駆動用トランジスタ32は、第1電位Vccにある電源線DSL10から電流の供給を受け、保持容量33に保持された信号電位Vsigに応じて駆動電流IdSを発光素子34に流す。発光素子34に所定の駆動電流IdSが流れることにより、画素101が発光する。

20

## 【0027】

画素101は、閾値補正機能を有する。閾値補正機能とは、駆動用トランジスタ32の閾値電圧Vthに相当する電圧を保持容量33に保持させる機能であり、これにより、ELパネル100の画素毎のばらつきの原因となる駆動用トランジスタ32の閾値電圧Vthの影響をキャンセルすることができる。

## 【0028】

また、画素101は、上述した閾値補正機能に加え、移動度補正機能も有する。移動度補正機能とは、保持容量33に信号電位Vsigを保持する際、駆動用トランジスタ32の移動度μに対する補正を信号電位Vsigに加える機能である。

30

## 【0029】

さらに、画素101は、ブーストストラップ機能も備えている。ブーストストラップ機能とは、駆動用トランジスタ32のソース電位Vsの変動にゲート電位Vgを連動させる機能であり、これにより、駆動用トランジスタ32のゲートgとソースs間の電圧Vgsを一定に維持することが出来る。

## 【0030】

なお、閾値補正機能、移動度補正機能、およびブーストストラップ機能については、後述する図7、図11、および図12などでも説明する。

40

## 【0031】

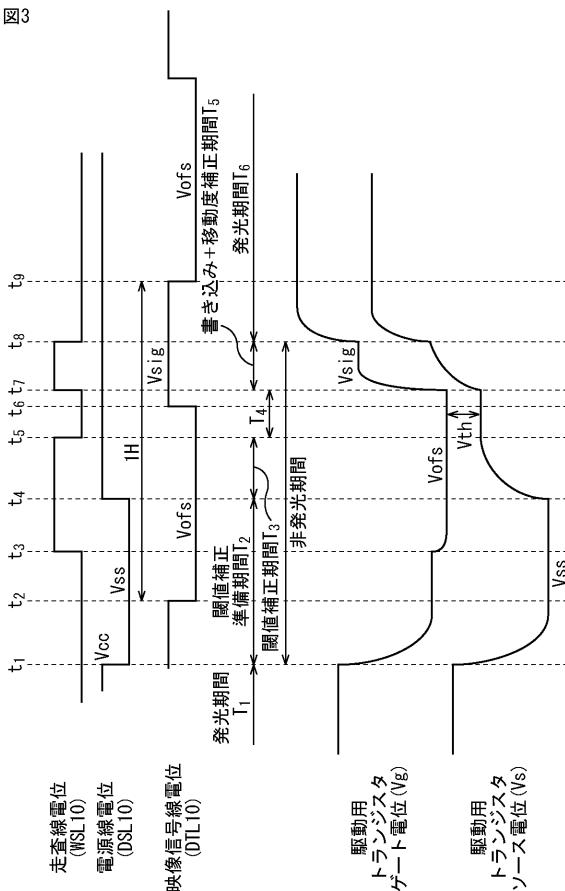

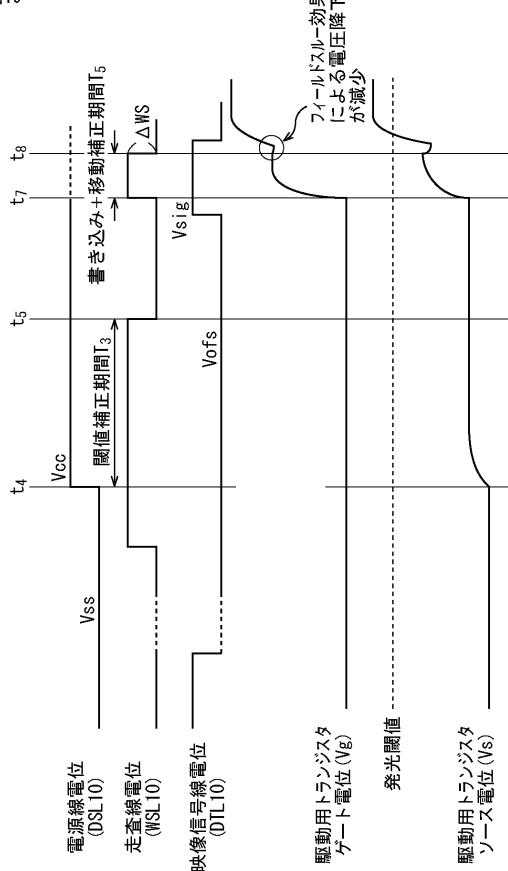

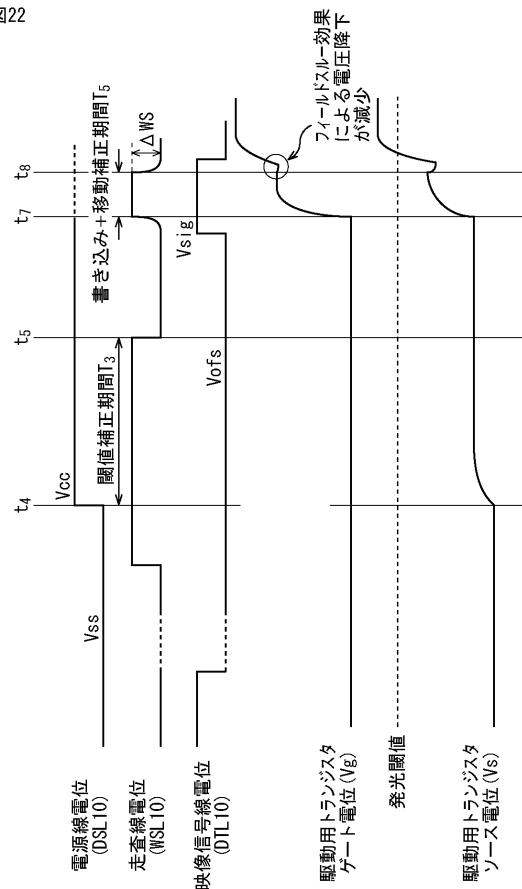

図3は、画素101の動作を説明するタイミングチャートである。

## 【0032】

図3は、同一の時間軸（画面横方向）に対する走査線WSL10、電源線DSL10、および映像信号線DTL10の電位変化と、それに対応する駆動用トランジスタ32のゲート電位Vg及びソース電位Vsの変化を示している。

## 【0033】

図3において、時刻t<sub>1</sub>までの期間は、前の水平期間（1H）の発光がなされている発光期間T<sub>1</sub>である。

## 【0034】

発光期間T<sub>1</sub>が終了した時刻t<sub>1</sub>から時刻t<sub>4</sub>までは、駆動用トランジスタ32のゲート

50

電位  $V_g$  及びソース電位  $V_s$  を初期化することで閾電圧補正動作の準備を行う閾値補正準備期間  $T_2$  である。

#### 【0035】

閾値補正準備期間  $T_2$  では、時刻  $t_1$ において、電源スキャナ105が、電源線DSL10の電位を高電位である  $V_{ccc}$  から低電位である  $V_{sss}$  に切換える。時刻  $t_2$ において、水平セレクタ103が、映像信号線DTL10の電位を信号電位  $V_{sig}$  から基準電位  $V_{ofs}$  に切換える。次に、時刻  $t_3$ において、ライトスキャナ104が、走査線WSL10の電位を高電位に切換える、サンプリング用トランジスタ31をオンさせる。これにより、駆動用トランジスタ32のゲート電位  $V_g$  が基準電位  $V_{ofs}$  にリセットされ、且つ、ソース電位  $V_s$  が映像信号線DTL10の低電位  $V_{sss}$  にリセットされる。

10

#### 【0036】

時刻  $t_4$  から時刻  $t_5$  までは、閾値補正動作を行う閾値補正期間  $T_3$  である。閾値補正期間  $T_3$  では、時刻  $t_4$  において、電源スキャナ105により、電源線DSL10の電位が高電位  $V_{ccc}$  に切換えられ、閾値電圧  $V_{th}$  に相当する電圧が、駆動用トランジスタ32のゲート  $g$  とソース  $s$  との間に接続された保持容量33に書き込まれる。

#### 【0037】

時刻  $t_5$  から時刻  $t_7$  までの書き込み + 移動度補正準備期間  $T_4$  では、走査線WSL10の電位が高電位から低電位一旦切換えられるとともに、時刻  $t_7$  の前の時刻  $t_6$  において、水平セレクタ103が、映像信号線DTL10の電位を基準電位  $V_{ofs}$  から階調に応じた信号電位  $V_{sig}$  に切換える。

20

#### 【0038】

そして、時刻  $t_7$  から時刻  $t_8$  までの書き込み + 移動度補正期間  $T_5$  において、映像信号の書き込みと移動度補正動作が行われる。即ち、時刻  $t_7$  から時刻  $t_8$  までの間、走査線WSL10の電位が高電位に設定され、これにより、映像信号の信号電位  $V_{sig}$  が閾値電圧  $V_{th}$  に足し込まれる形で保持容量33に書き込まれると共に、移動度補正用の電圧  $V_\mu$  が保持容量33に保持された電圧から差し引かれる。

#### 【0039】

書き込み + 移動度補正期間  $T_5$  終了後の時刻  $t_8$  において、走査線WSL10の電位が低電位に設定され、それ以降、発光期間  $T_6$  として、信号電圧  $V_{sig}$  に応じた発光輝度で発光素子34が発光する。信号電圧  $V_{sig}$  は、閾値電圧  $V_{th}$  に相当する電圧と移動度補正用の電圧  $V_\mu$  とによって調整されているため、発光素子34の発光輝度は駆動用トランジスタ32の閾値電圧  $V_{th}$  や移動度  $\mu$  のばらつきの影響を受けることがない。

30

#### 【0040】

なお、発光期間  $T_6$  の最初でブートストラップ動作が行われ、駆動用トランジスタ32のゲート ソース間電圧  $V_{gs} = V_{sig} + V_{th} - V_\mu$  を一定に維持したまま、駆動用トランジスタ32のゲート電位  $V_g$  及びソース電位  $V_s$  が上昇する。

#### 【0041】

また、時刻  $t_8$  から所定時間経過後の時刻  $t_9$  において、映像信号線DTL10の電位が、信号電位  $V_{sig}$  から基準電位  $V_{ofs}$  に落とされる。図3において、時刻  $t_2$  から時刻  $t_9$  までの期間は水平期間(1H)に相当する。

40

#### 【0042】

以上のようにして、ELパネル100では、駆動用トランジスタ32の閾値電圧  $V_{th}$  や移動度  $\mu$  のばらつきの影響を受けることがなく、発光素子34を発光させることができる。

#### 【0043】

図4乃至図12を参照して、画素101の動作についてさらに詳細に説明する。

#### 【0044】

図4は、発光期間  $T_1$  の画素101の状態を示している。

#### 【0045】

発光期間  $T_1$  では、サンプリング用トランジスタ31がオフ(走査線WSL10の電位

50

が低電位)、かつ電源線 D S L 1 0 の電位が高電位 V c c となっており、駆動用トランジスタ 3 2 が駆動電流 I d s を発光素子 3 4 に供給している。このとき駆動用トランジスタ 3 2 は飽和領域で動作するよう設定されているため、発光素子 3 4 に流れる駆動電流 I d s は、駆動用トランジスタ 3 2 のゲートソース間電圧 V g s に応じて次式(1)で表される値をとる。

## 【数1】

$$I_{ds} = \frac{1}{2} \mu \frac{W}{L} C_{ox} (V_{gs} - V_{th})^2 \quad \dots (1)$$

## 【0046】

式(1)において、 $\mu$ は移動度を示し、Wはゲート幅を表し、Lはゲート長を表し、 $C_{ox}$ は単位面積あたりのゲート酸化膜容量を示す。また、 $V_{gs}$ は、駆動用トランジスタ 3 2 のゲートgとソースs間の電圧(ゲートソース間電圧)であり、 $V_{th}$ は、駆動用トランジスタ 3 2 の閾値電圧である。なお、飽和領域とは、( $V_{gs} - V_{th} < V_{ds}$ )の条件を満たした状態をいう( $V_{ds}$ は、駆動用トランジスタ 3 2 のソースsとドレインd間の電圧)。

## 【0047】

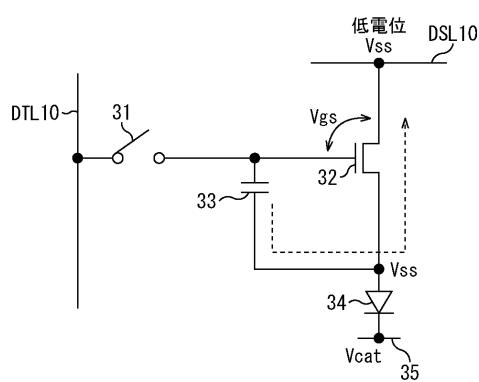

そして、閾値補正準備期間  $T_2$  の最初の時刻  $t_1$  において、図5に示すように、電源スキヤナ 1 0 5 は、電源線 D S L 1 0 の電位を高電位 V c c (第1電位)から低電位 V s s (第2電位)に切換える。このとき電源線 D S L 1 0 の電位 V s s が発光素子 3 4 の閾値電圧  $V_{the1}$  とカソード電位  $V_{cat}$  の和よりも小さければ ( $V_{ss} < V_{the1} + V_{cat}$ ) 発光素子 3 4 は消光し、駆動用トランジスタ 3 2 の電源線 D S L 1 0 と接続された側がソースsとなる。また、発光素子 3 4 のアノードは電位 V s s に充電される。

## 【0048】

次に、図6に示すように、時刻  $t_2$  において、水平セレクタ 1 0 3 が映像信号線 D T L 1 0 の電位を基準電位  $V_{ofs}$  にした後、時刻  $t_3$  において、ライトスキヤナ 1 0 4 が、走査線 W S L 1 0 の電位を高電位に切換えることより、サンプリング用トランジスタ 3 1 をオンにする。これにより、駆動用トランジスタ 3 2 のゲート電位  $V_g$  は  $V_{ofs}$  となり、ゲートソース間電圧  $V_{gs}$  は、 $V_{ofs} - V_{ss}$  という値をとる。ここで、駆動用トランジスタ 3 2 のゲートソース間電圧  $V_{gs}$  である ( $V_{ofs} - V_{ss}$ ) は、次の閾値補正期間  $T_3$  で閾値補正動作を行うため、閾値電圧  $V_{th}$  よりも大である ( $V_{ofs} - V_{ss} > V_{th}$ ) 必要がある。逆に言うと、( $V_{ofs} - V_{ss} > V_{th}$ ) の条件を満たすように、電位  $V_{ofs}$  および  $V_{ss}$  が設定される。

## 【0049】

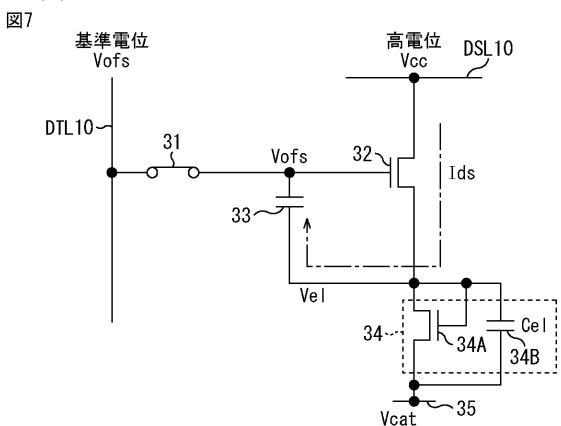

そして、閾値補正期間  $T_3$  の最初の時刻  $t_4$  において、図7に示すように、電源スキヤナ 1 0 5 が電源線 D S L 1 0 の電位を低電位 V s s から高電位 V c c に切換えると、駆動用トランジスタ 3 2 の発光素子 3 4 のアノードと接続されている側がソースsとなり、図7において1点鎖線で示されるように電流が流れれる。

## 【0050】

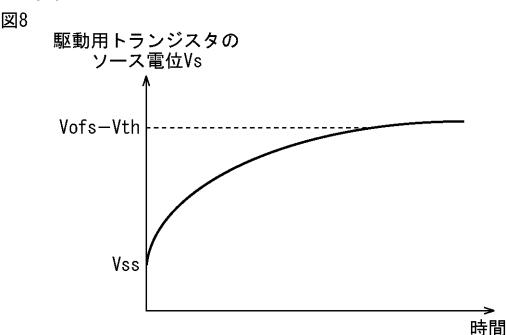

ここで、発光素子 3 4 は、等価的にダイオード 3 4 A と寄生容量を  $C_{el}$  とする保持容量 3 4 B で表すことができ、発光素子 3 4 のリーク電流が駆動用トランジスタ 3 2 に流れ電流よりもかなり小さい ( $V_{el} = V_{cat} + V_{the1}$  を満たす) という条件の下では、駆動用トランジスタ 3 2 に流れ電流は保持容量 3 3 と 3 4 B を充電するために使用される。発光素子 3 4 のアノード電位  $V_{el}$  (駆動用トランジスタ 3 2 のソース電位  $V_s$ ) は、図8に示されるように、駆動用トランジスタ 3 2 を流れ電流に応じて上昇する。所定時間経過後、駆動用トランジスタ 3 2 のゲートソース間電圧  $V_{gs}$  が  $V_{th}$  という値をとる。また、このときの発光素子 3 4 のアノード電位  $V_{el}$  は ( $V_{ofs} - V_{th}$ ) である。ここで、発光素子 3 4 のアノード電位  $V_{el}$  は、発光素子 3 4 の閾値電圧  $V_{the1}$  とカソード電位  $V_{cat}$  の和以下となっている ( $V_{el} = (V_{ofs} - V_{th}) - (V_{cat} + V_{the1})$ )。

## 【0051】

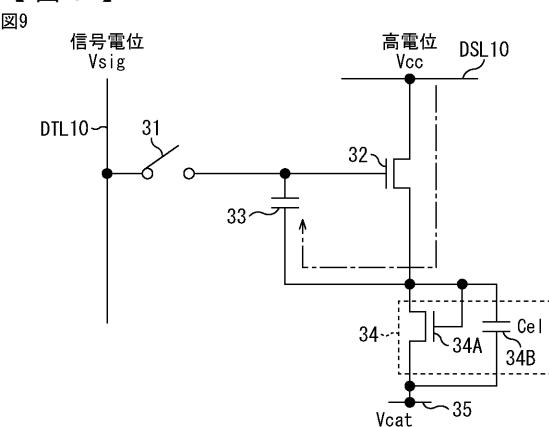

その後、時刻  $t_5$ において、図9に示されるように、走査線W S L 1 0の電位が高電位から低電位に切替えられ、サンプリング用トランジスタ3 1がオフして閾値補正動作(閾値補正期間  $T_3$ )が完了する。

## 【0052】

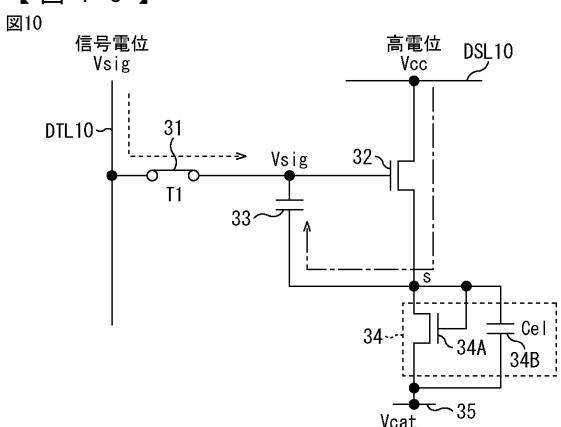

続く書き込み+移動度補正準備期間  $T_4$ の時刻  $t_6$ において、水平セレクタ1 0 3によって、映像信号線D T L 1 0の電位が、基準電位  $V_{of s}$ から、階調に応じた信号電位  $V_{sig}$ に切換えられた(図9)後、書き込み+移動度補正期間  $T_5$ に入り、図10に示されるように、時刻  $t_7$ において、走査線W S L 1 0の電位が高電位に設定されることでサンプリング用トランジスタ3 1がオンして、映像信号の書き込みと移動度補正動作が行われる。駆動用トランジスタ3 2のゲート電位  $V_g$ は、サンプリング用トランジスタ3 1がオンしているため信号電位  $V_{sig}$ となるが、サンプリング用トランジスタ3 1には電源線D S L 1 0からの電流が流れるため、駆動用トランジスタ3 2のソース電位  $V_s$ は、時間とともに上昇していく。

10

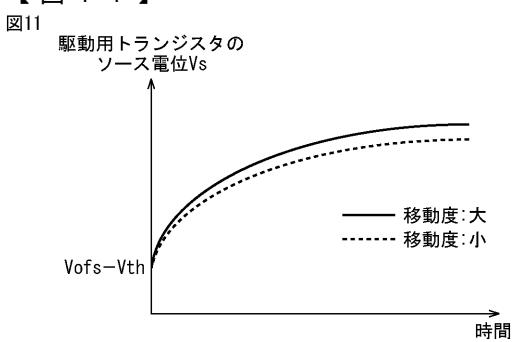

## 【0053】

駆動用トランジスタ3 2の閾値補正動作は既に完了している。よって、式(1)の右辺の $(V_{gs} - V_{th})^2$ の項は、 $(V_{gs} - V_{th})^2 = \{(V_{sig} - (V_{of s} - V_{th})) - V_{th}\}^2 = (V_{sig} - V_{of s})^2$ となり、閾値電圧  $V_{th}$ の項の影響はなくなるので、駆動用トランジスタ3 2が流す電流  $I_{ds}$ は、移動度  $\mu$ を反映したものとなる。具体的には、図11に示されるように、移動度  $\mu$ が大きい場合には、駆動用トランジスタ3 2が流す電流  $I_{ds}$ は大きくなり、ソース電位  $V_s$ の上昇も早い。一方、移動度  $\mu$ が小さい場合には、駆動用トランジスタ3 2が流す電流  $I_{ds}$ は小さくなり、ソース電位  $V_s$ の上昇は遅くなる。換言すると、一定時間経過時点では、移動度  $\mu$ が大きい場合には、駆動用トランジスタ3 2のソース電位  $V_s$ の上昇量  $V_\mu$ (電位補正值)は大きくなり、移動度  $\mu$ が小さい場合には、駆動用トランジスタ3 2のソース電位  $V_s$ の上昇量  $V_\mu$ (電位補正值)は小さくなる。これによって、各画素1 0 1の駆動用トランジスタ3 2のゲートソース間電圧  $V_{gs}$ のバラツキが、移動度  $\mu$ を反映して小さくなり、一定時間経過後の各画素1 0 1のゲートソース間電圧  $V_{gs}$ は、移動度  $\mu$ のバラツキを完全に補正した電圧となる。

20

## 【0054】

30

時刻  $t_8$ において、走査線W S L 1 0の電位が低電位に設定されることでサンプリング用トランジスタ3 1がオフして、書き込み+移動度補正期間  $T_5$ が終了し、発光期間  $T_6$ となる(図12)。

## 【0055】

発光期間  $T_6$ では、駆動用トランジスタ3 2のゲートソース間電圧  $V_{gs}$ は一定であるので、駆動用トランジスタ3 2は一定電流  $I_{ds'}$ を発光素子3 4に供給し、発光素子3 4のアノード電位  $V_{e1}$ は、発光素子3 4に一定電流  $I_{ds'}$ という電流が流れる電圧  $V_x$ まで上昇し、発光素子3 4は発光する。駆動用トランジスタ3 2のソース電位  $V_s$ が上昇すると、保持容量3 3のブートストラップ機能により、駆動用トランジスタ3 2のゲート電位  $V_g$ も連動して上昇する。

40

## 【0056】

発光素子3 4のI-V特性により、発光時間が長くなると、図12に示されるB点の電位は時間とともに変化する(経時劣化する)。しかしながら、駆動用トランジスタ3 2のゲートソース間電圧  $V_{gs}$ は一定値に保たれているので、発光素子3 4に流れる電流は変化しない。したがって、I-V特性により発光素子3 4が経時劣化しても、一定電流  $I_{ds'}$ が流れ続けるので、発光素子3 4の輝度が変化することはない。

## 【0057】

以上のように、画素1 0 1を備える図2のE Lパネル1 0 0においては、閾値補正機能および移動度補正機能によって画素1 0 1ごとの閾値電圧  $V_{th}$ 及び移動度  $\mu$ の相違を補正することができる。また、発光素子3 4の経時変動(劣化)も補正することができる。

50

【 0 0 5 8 】

これにより、図2のELパネル100を用いた表示装置では、高品位な画質を得ることが可能である。

【 0 0 5 9 】

ところで、画素 101 が発光するときの輝度は、上述したように、発光素子 34 に供給される電流値  $I_{ds'}$  ( $I_{ds}$ ) によって決まるが、この電流値  $I_{ds'}$  は、駆動用トランジスタ 32 のゲートソース間電圧  $V_{gs}$  に応じて式(1)で決定される。したがって、駆動用トランジスタ 32 のゲートソース間電圧  $V_{gs}$  に変化があると、画素 101 の輝度は変化する。そして、このゲートソース間電圧  $V_{gs}$  の変化量が画素 101 ごとに異なると、EL パネル 100 全体としては、輝度のばらつきが生ずることになる。

【 0 0 6 0 】

図3を参照して説明したように、書き込み+移動度補正期間 $T_5$ 終了後の発光期間 $T_6$ では、最初にブートストラップ動作が行われ、駆動用トランジスタ32のゲート電位 $V_g$ 及びソース電位 $V_s$ が、駆動用トランジスタ32のゲート-ソース間電圧 $V_{gs}$ (=  $V_{si} + V_{th} - V_\mu$ )を一定に維持したまま上昇し、駆動用トランジスタ32のソース電位 $V_s$ が、発光を始める所定の閾値(発光閾値)を超えたとき、画素101(発光素子34)は発光する。

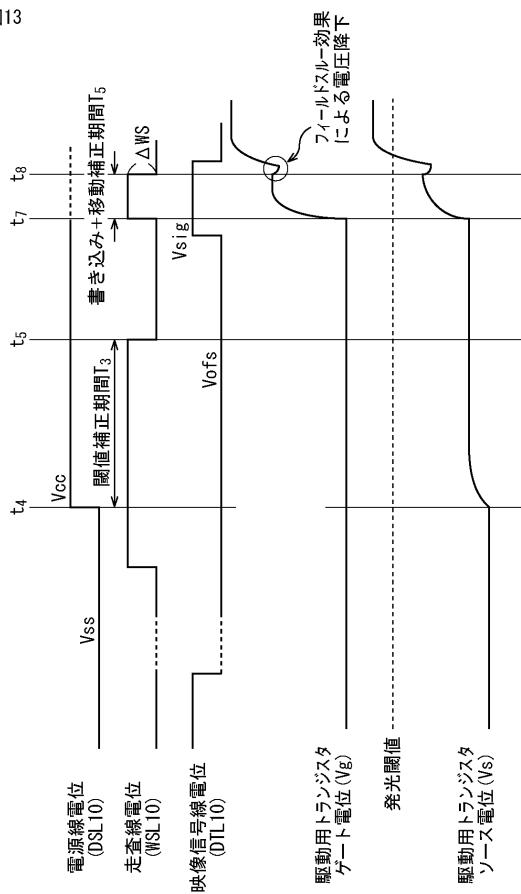

【 0 0 6 1 】

ここで、ブートストラップ動作時の駆動用トランジスタ32のゲート電位 $V_g$ について詳細にみてみると、図13において丸で囲んで示すように、書き込み+移動度補正期間 $T_5$ 終了後の時刻 $t_8$ において走査線W<sub>S</sub>L10の電位が高電位から低電位に変化したとき、フィールドスルーフィルタ効果により、駆動用トランジスタ32のゲート電位 $V_g$ が一瞬降下する現象が発生する。

〔 0 0 6 2 〕

このときの駆動用トランジスタ 3 2 のゲート電位  $V_g$  の降下量（以下、フィールドスルーバッテリ電圧降下量と称する）は、次式（2）で表すことができる。

【 0 0 6 3 】

【数2】

$$\text{フィードスルー電圧降下量} = \frac{\frac{C_{ws}}{C_{el}(C_s + C_{gs})} + C_{ws} + C_{gd}}{\frac{C_{el} + C_s + C_{gs}}{C_{el}(C_s + C_{gs})} + C_{ws} + C_{gd}} \times \Delta WS$$

... (2)

【 0 0 6 4 】

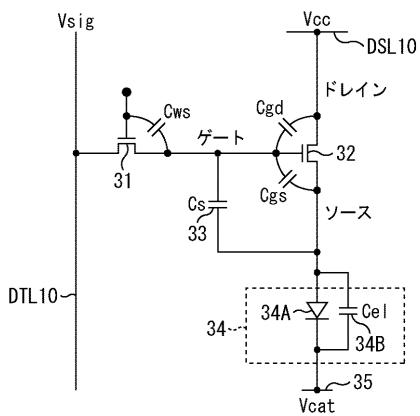

式(2)において、WSは、走査線WSL10の電位の変化量を表す。また、Ce1は発光素子34の寄生容量(等価的に表される保持容量34Bの静電容量)であり、Cwsはサンプリング用トランジスタ31の寄生容量(サンプリング用トランジスタ31のゲートソース間に発生する寄生容量)であり、Csは保持容量33の蓄積容量である。Cgsは駆動用トランジスタ32のゲートソース間に発生する寄生容量であり、Cgdは駆動用トランジスタ32のゲートドレイン間に発生する寄生容量である。

〔 0 0 6 5 〕

サンプリング用トランジスタ 3-1 の寄生容量  $C_{ws}$ 、駆動用トランジスタ 3-2 のゲートソース間の寄生容量  $C_{gs}$ 、および、駆動用トランジスタ 3-2 のゲート-ドレイン間の寄生容量  $C_{gd}$  を含む画素 101 の等価回路（画素回路 101）を図 1-4 に示す。

【 0 0 6 6 】

フィールドスルーフィールド効果により、駆動用トランジスタ  $3\text{~}2$  のゲート電位  $V_g$  が一瞬降下する現象が発生すること自体は、E-Lパネル  $1\text{~}0\text{~}0$  の全画素が一様に降下するのであれば、E-Lパネル  $1\text{~}0\text{~}0$  の画素ごとの輝度ばらつきとしては見えないので問題はない。

【 0 0 6 7 】

しかしながら、フィールドスルー電圧降下量が画素 101 ごとに異なる場合には、そのばらつきが画素ごとの輝度のばらつきとなるため、パネル全体の画質の低下につながり、問題となる。例えば、隣接画素の輝度差が 1 % 以上となると輝度ムラとして視認することができ、問題となる。

【0068】

式(2)からわかるように、フィールドスルー電圧降下量が最も影響を受けるのは、サンプリング用トランジスタ 31 の寄生容量 Cws である。

【0069】

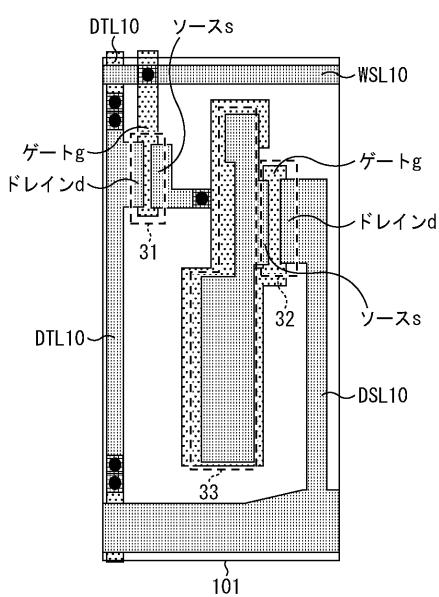

サンプリング用トランジスタ 31 および駆動用トランジスタ 32 に関する部分の画素 101 の配線パターンのレイアウトを図 15 に示す。

10

【0070】

図 15 に示されるように、サンプリング用トランジスタ 31 のゲート g は第 1 の金属層で形成され、サンプリング用トランジスタ 31 のソース s 及びドレイン d は第 2 の金属層で形成される。また、駆動用トランジスタ 32 のゲート g は第 1 の金属層で形成され、駆動用トランジスタ 32 のソース s 及びドレイン d は第 2 の金属層で形成される。保持容量 33 は第 1 の金属層と第 2 の金属層で形成される。

【0071】

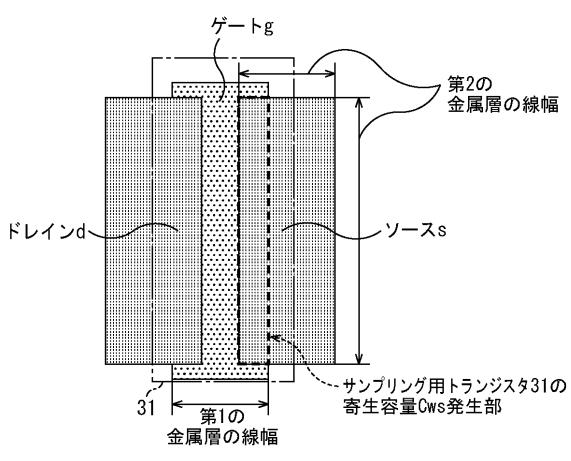

図 16 は、図 15 のサンプリング用トランジスタ 31 周辺を拡大した図である。

【0072】

フィールドスルー電圧降下量に最も影響を及ぼすサンプリング用トランジスタ 31 の寄生容量 Cws が発生する部分は、画素 101 を上方から見た場合に、図 16 において点線で示されている、ソース s としての第 2 の金属層と、ゲート g としての第 1 の金属層の重複部分である。

20

【0073】

従って、フィールドスルー電圧降下量のばらつきに最も影響を及ぼすサンプリング用トランジスタ 31 の寄生容量 Cws のばらつきは、つまりは、露光処理の第 1 の金属層を形成するプロセスおよび第 2 の金属層を形成するプロセスにおける、サンプリング用トランジスタ 31 のゲート g として第 1 の金属層を形成するときのパターニング誤差と、サンプリング用トランジスタ 31 のソース s として第 2 の金属層を形成するときのパターニング誤差に起因する。換言すれば、サンプリング用トランジスタ 31 のゲート g としての第 1 の金属層の線幅のばらつきと、サンプリング用トランジスタ 31 のソース s としての第 2 の金属層の線幅のばらつきに起因する。

30

【0074】

しかしながら、金属層形成時のパターニング誤差を完全になくすることは困難である。

【0075】

そこで、以下では、フィールドスルー電圧降下による画素ごとの輝度のばらつきを改善するようにした E-L パネルについて説明する。

【0076】

図 17 は、本発明を適用した E-L パネル 200 の実施の形態の構成例を示すブロック図である。

40

【0077】

なお、図 17において、上述した E-L パネル 100 と対応する部分については同一の符号を付してあり、その説明は適宜省略する。

【0078】

即ち、図 17 の E-L パネル 200 では、画素アレイ部 102 において、上述した画素 101 と異なる構成を有する画素 201 - (1, 1) 乃至 201 - (N, M) が行列状に配置されている点が、E-L パネル 100 と異なる。以下において、画素 201 - (1, 1) 乃至 201 - (N, M) のそれぞれを特に区別する必要がない場合、画素 101 と同様に、単に画素 201 と称する。

【0079】

50

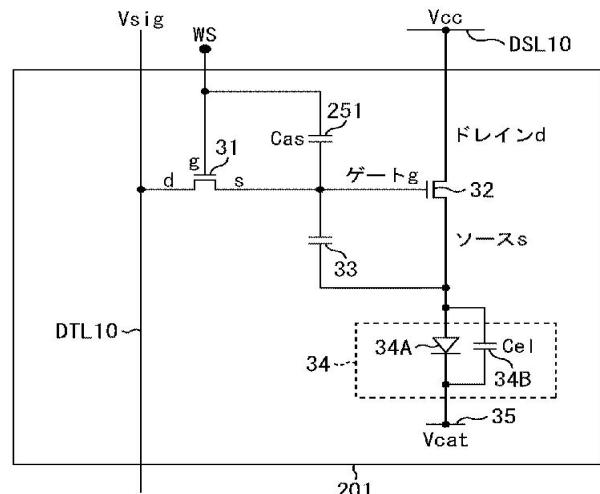

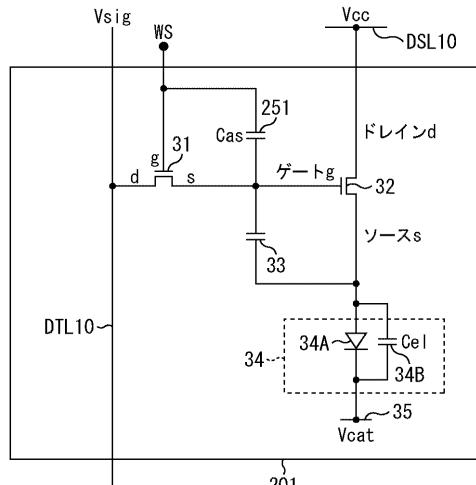

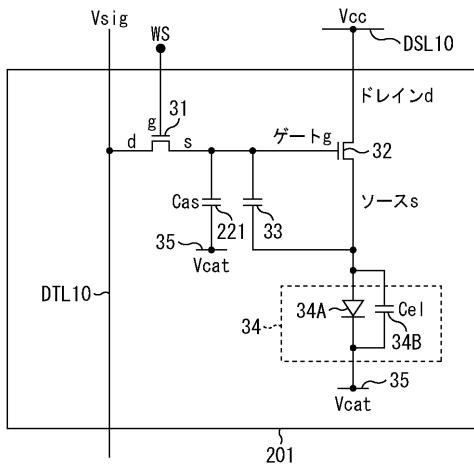

図18は、画素201の第1の実施の形態の構成例を示している。

【0080】

図18の画素201において、画素101と対応する部分については同一の符号を付してあり、その説明は適宜省略する。後述する画素201のその他の実施の形態についても同様である。

【0081】

図18の画素201は、サンプリング用トランジスタ31のソースsと、接地配線35に接続されている補助容量221が新たに設けられている点が、画素101と異なる。ここで、補助容量221の静電容量Casは、サンプリング用トランジスタ31の寄生容量Cwsよりも大である( $C_{ws} < C_{as}$ )。

10

【0082】

書き込み+移動度補正期間 $T_5$ において、画素201では、図10を参照して説明したように、走査線WSL10の電位が高電位に設定されることでサンプリング用トランジスタ31がオンする。これにより、映像信号線DTL10の電位であって、階調に応じた信号電位Vsigの映像信号が保持容量33および補助容量221に供給される。その後、走査線WSL10の電位が低電位に設定され、サンプリング用トランジスタ31がオフしたとき、補助容量221に蓄えられた電荷により、駆動用トランジスタ32のゲート電位Vgの変化が鈍る。

【0083】

即ち、サンプリング用トランジスタ31のソースsと接地配線35の間に、静電容量Casの補助容量221を設けることで、時刻 $t_8$ における走査線WSL10の電位の切り替えに伴う、駆動用トランジスタ32のゲート電位Vgの変化を鈍らさせることができる。

20

【0084】

そして、駆動用トランジスタ32のゲート電位Vgの変化が鈍ることで、図19において丸で囲んで示すように、フィールドスルーレ電圧降下量を小さくすることができる。フィールドスルーレ電圧降下量が小さくなると、パネル200を構成する画素201ごとの輝度のばらつきも小さくなるので、フィールドスルーレ電圧降下による画素ごとの輝度のばらつきを改善することができる。

【0085】

換言すれば、ゲートgとして第1の金属層の線幅と、ソースsとして第2の金属層の線幅に、ばらつきが生じていたとしても、サンプリング用トランジスタ31のソースsと、接地配線35との間に、静電容量Casの補助容量221を設けることで、画素ごとの輝度のばらつきを改善する(抑制する)ことができる。

30

【0086】

図20は、図15に示した画素101に対応する画素201の配線パターンレイアウトであって、補助容量221を設ける場合の画素201の配線パターンレイアウトを示している。

【0087】

図20において、補助容量221は、その点線内の第1の金属層と第2の金属層の対向する部分に相当する。補助容量221のサンプリング用トランジスタ31のソースsと接続される電極は、サンプリング用トランジスタ31のソースsと同様に第2の金属層で形成し、補助容量221の接地配線35と接続される電極は、第1の金属層で形成することができる。従って、画素201内に容易に補助容量221を形成することができる。

40

【0088】

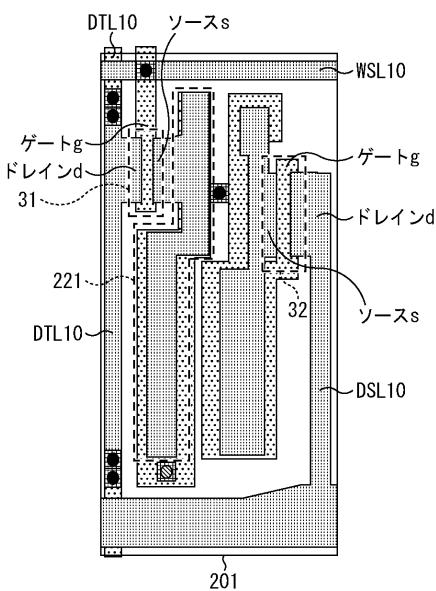

図21は、画素201の第2の実施の形態の構成例を示している。

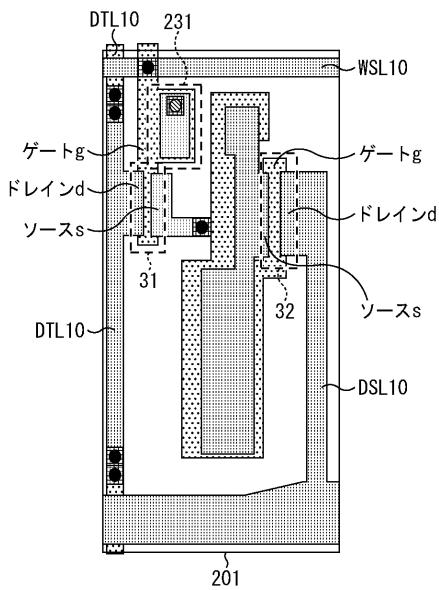

【0089】

図21の画素201は、サンプリング用トランジスタ31のゲートgと、接地配線35に接続されている補助容量231が新たに設けられている点が、画素101と異なる。ここで、補助容量231の静電容量Casは、サンプリング用トランジスタ31の寄生容量Cwsよりも大である( $C_{ws} < C_{as}$ )。

50

## 【0090】

書き込み + 移動度補正期間  $T_5$ において、図10を参照して説明したように、サンプリング用トランジスタ31がオンし、その後、オフする。画素201では、サンプリング用トランジスタ31がオンされたとき、即ち、走査線W<sub>SL</sub>10の電位が高電位に設定されたとき、補助容量231は、そこに供給される電荷を蓄え、所定の電位を保持する。サンプリング用トランジスタ31がオフしたとき、補助容量231に蓄えられた電荷により、駆動用トランジスタ32のゲート電位V<sub>g</sub>の変化が鈍る。

## 【0091】

即ち、サンプリング用トランジスタ31のゲートgと接地配線35との間に、静電容量C<sub>as</sub>の補助容量231を設けることで、図22に示すように、書き込み + 移動度補正期間  $T_5$ における書き込みパルスを鈍らせることができる。即ち、時刻t<sub>7</sub>および時刻t<sub>8</sub>における走査線W<sub>SL</sub>10の電位の切り替えを鈍らせることができる。

10

## 【0092】

そして、書き込みパルスが鈍ることで、図22において丸を囲んで示すように、フィールドスルーバッファ降下量を小さくすることができる。フィールドスルーバッファ降下量が小さくなると、パネル200を構成する画素201ごとの輝度のばらつきも小さくなるので、フィールドスルーバッファ降下による画素ごとの輝度のばらつきを改善することができる。

## 【0093】

従って、第2の実施の形態においても、第1の実施の形態と同様に、画素ごとの輝度のばらつきを改善する（抑制する）ことができる。

20

## 【0094】

なお、第1の実施の形態においては、駆動用トランジスタ32のゲート電位V<sub>g</sub>の変化を直接鈍らせることでフィールドスルーバッファ降下量を小さくしたが、第2の実施の形態では、駆動用トランジスタ32のゲート電位V<sub>g</sub>の変化を直接鈍らせることによる効果（フィールドスルーバッファ降下量の縮小）と、書き込みパルスが鈍ることに起因して駆動用トランジスタ32のゲート電位V<sub>g</sub>の変化を鈍らせることによる効果（フィールドスルーバッファ降下量の縮小）の両方を奏する。

## 【0095】

図23は、補助容量231を設ける場合の画素201の配線パターンレイアウトを示している。

30

## 【0096】

図23において、補助容量231は、その点線内の第1の金属層と第2の金属層の対向する部分に相当する。補助容量231のサンプリング用トランジスタ31のゲートgと接続される電極は、サンプリング用トランジスタ31のゲートgと同様に第1の金属層で形成し、補助容量231の接地配線35と接続される電極は、第2の金属層で形成することができる。従って、画素201内に容易に補助容量231を形成することができる。

## 【0097】

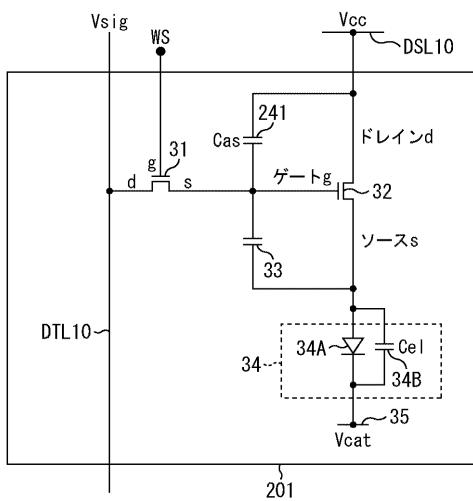

図24は、画素201の第3の実施の形態の構成例を示している。

## 【0098】

図24の画素201は、駆動用トランジスタ32のゲートgとドレインdに接続されている補助容量241が新たに設けられている点が、画素101と異なる。ここで、補助容量241の静電容量C<sub>as</sub>は、サンプリング用トランジスタ31の寄生容量C<sub>ws</sub>よりも大である（C<sub>ws</sub> < C<sub>as</sub>）。

40

## 【0099】

図7を参照して説明したように、閾値補正期間  $T_3$ の最初の時刻t<sub>4</sub>において、電源スキヤナ105が電源線D<sub>SL</sub>10の電位を低電位V<sub>ss</sub>から高電位V<sub>cc</sub>に切換えると、駆動用トランジスタ32の発光素子34のアノードと接続されている側がソースsとなり、保持容量33に向けて電流が流れ、保持容量33において電荷が蓄積される。このとき、補助容量241も、電荷を蓄積し、所定の電位を保持する。

## 【0100】

50

駆動用トランジスタ32のゲートgとドレインdとの間に補助容量241を設けた場合、図14に示した寄生容量を含む画素101の等価回路からも分かるように、駆動用トランジスタ32のゲートドレイン間に発生する寄生容量Cgdが大となることと等しい。

#### 【0101】

駆動用トランジスタ32のゲートドレイン間に発生する寄生容量Cgdが大となると、式(2)の第1項である分数の分子は変わらず分母が大となることから、フィールドスルーレ電圧降下量を小さくすることができる。フィールドスルーレ電圧降下量が小さくなると、パネル200を構成する画素201ごとの輝度のばらつきも小さくなるので、フィールドスルーレ電圧降下による画素ごとの輝度のばらつきを改善することができる。

#### 【0102】

従って、第3の実施の形態においても、画素ごとの輝度のばらつきを改善する(抑制する)ことができる。

#### 【0103】

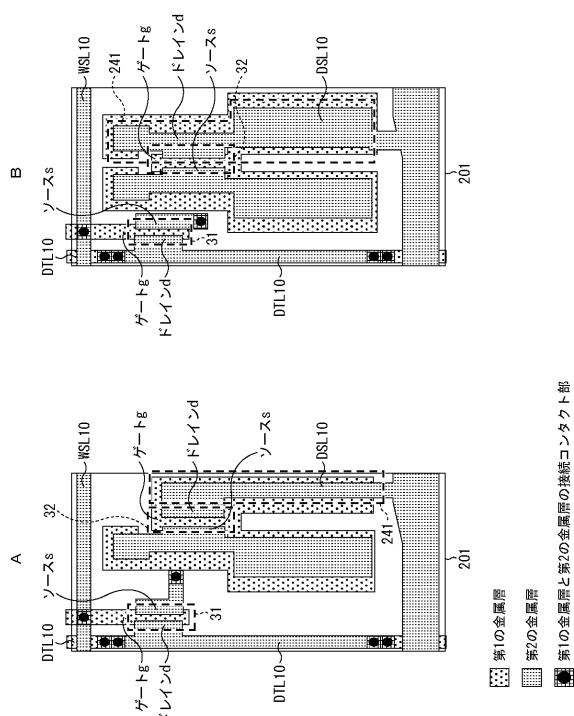

図25は、補助容量241を設ける場合の画素201の配線パターンレイアウトを示している。

#### 【0104】

図25Aと図25Bに示される画素201の配線パターンレイアウトでは、新たに設ける補助容量241を形成するための金属層の構成は同一であるが、配線パターンの形状が異なる。

#### 【0105】

即ち、図25Aおよび図25Bのいずれにおいても、補助容量241は、その点線内の第1の金属層と第2の金属層の対向する部分に相当する(ただし、駆動用トランジスタ32部分を除く)。また、図25Aと図25Bのいずれにおいても、補助容量241の駆動用トランジスタ32のドレインdと接続される電極は、駆動用トランジスタ32のドレインdと同様に第2の金属層で形成され、補助容量241の駆動用トランジスタ32のゲートgと接続される電極は、駆動用トランジスタ32のゲートgと同様に第1の金属層で形成される。従って、画素201内に容易に補助容量241を形成することができる。

#### 【0106】

図25Bに示される画素201の配線パターンレイアウトでは、補助容量241を形成する第1および第2の金属層の配線パターンの形状が、駆動用トランジスタ32を中心として図面左右方向に線対称となるような形状となっている。換言すれば、補助容量241を形成する第1および第2の金属層の配線パターンの形状が、保持容量33を形成する第1および第2の金属層の配線パターンの形状と線対称となるように形成されている。

#### 【0107】

このように補助容量241の配線パターンを線対称に形成することにより、画素201内の配線パターンレイアウトが隣接する画素201どうしでミラー反転するようにELパネル200が構成されている場合、レーザアニール処理工程において、全画素のトランジスタに対して均等に(同一の照射条件で)レーザが照射されるので、レーザ照射方向によるシリコン結晶性にばらつきが生じることを抑制することができ、これにより、TFT特性のバラツキを抑えることができる。さらに、TFT特性のバラツキを抑えることで、画素ごとの輝度のばらつきを改善する(抑制する)ことができる。

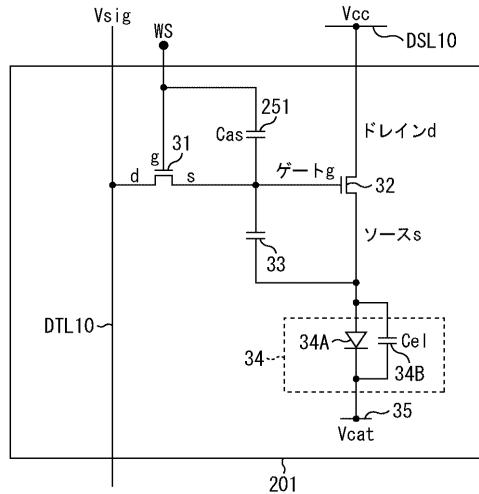

#### 【0108】

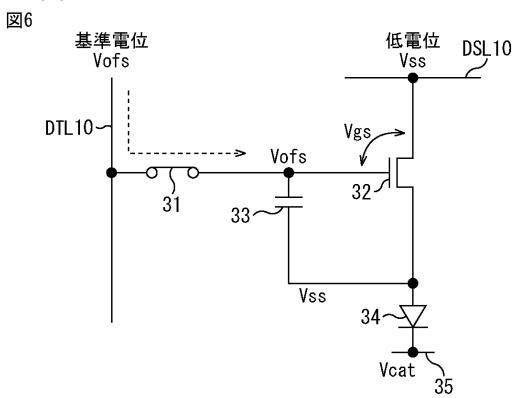

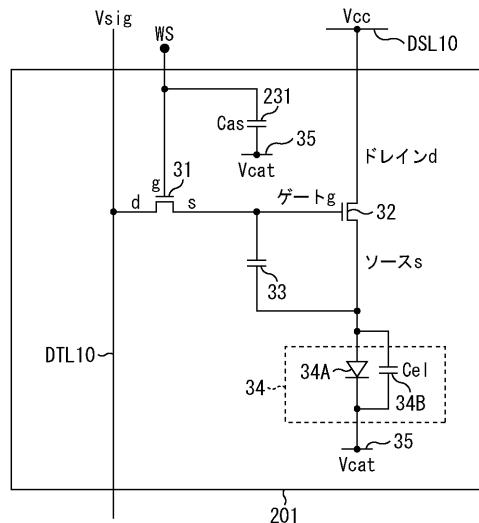

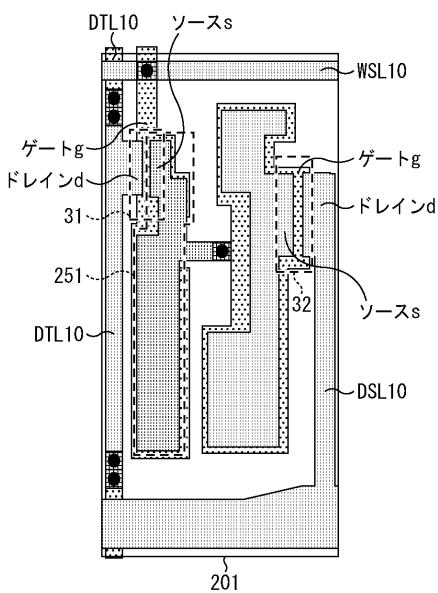

図26は、画素201の第4の実施の形態の構成例を示している。

#### 【0109】

図26の画素201は、サンプリング用トランジスタ31のゲートgとソースsに接続されている補助容量251が新たに設けられている点が、画素101と異なる。ここで、補助容量251の静電容量Casは、サンプリング用トランジスタ31の寄生容量Cwsよりも大である( $C_{ws} < C_{as}$ )。

#### 【0110】

上述したように、書き込み+移動度補正期間 $T_5$ に、サンプリング用トランジスタ31

10

20

30

40

50

がオンし、その後、オフする。画素 201 では、サンプリング用トランジスタ 31 がオンされたとき、即ち、走査線 WSL10 の電位が高電位に設定されたとき、補助容量 251 は、そこに供給される電荷を蓄え、所定の電位を保持する。

#### 【0111】

サンプリング用トランジスタ 31 のゲート g とソース s との間に補助容量 251 を設けた場合、図 14 に示した画素 101 の等価回路からも分かるように、サンプリング用トランジスタ 31 の寄生容量 Cws が大となることと等しい。

#### 【0112】

サンプリング用トランジスタ 31 の寄生容量 Cws が大となるということは、式(2)において、第 1 項の分数の分子と分母に含まれる寄生容量 Cws がともに大となり、フィールドスルーレ電圧降下量自体は大きくなる。しかしながら、製造プロセスにおける第 1 の金属層と第 2 の金属層の線幅の誤差(製造誤差)から生じるサンプリング用トランジスタ 31 の寄生容量 Cws は、補助容量 251 の静電容量 Cas に比して小さくなる。同様に、駆動用トランジスタ 32 のゲート ソース間に発生する寄生容量 Cgs、および、駆動用トランジスタ 32 のゲート ドレイン間に発生する寄生容量 Cgd の影響も、補助容量 251 の静電容量 Cas に比して小さくなる。

#### 【0113】

従って、フィールドスルーレ電圧降下量自体は大きくなつたとしても、画素 201 ごとのフィールドスルーレ電圧降下量のばらつきは小さくなる。換言すれば、全画素のフィールドスルーレ電圧降下量の分散(?)を小さくすることができる。

#### 【0114】

従って、第 4 の実施の形態においても、画素ごとの輝度のばらつきを改善する(抑制する)ことができる。

#### 【0115】

図 27 は、補助容量 251 を設ける場合の画素 201 の配線パターンレイアウトを示している。

#### 【0116】

図 27 において、補助容量 251 は、その点線内の第 1 の金属層と第 2 の金属層の対向する部分に相当する(ただし、駆動用トランジスタ 32 部分を除く)。補助容量 251 のサンプリング用トランジスタ 31 のゲート g と接続される電極は、サンプリング用トランジスタ 31 のゲート g と同様に第 1 の金属層で形成し、補助容量 231 のサンプリング用トランジスタ 31 のソース s と接続される電極は、サンプリング用トランジスタ 31 のソース s と同様に第 2 の金属層で形成することができる。従って、画素 201 内に容易に補助容量 251 を形成することができる。

#### 【0117】

以上のように、第 1 乃至第 4 の実施の形態の画素 201 を有する ELPANEL200 によれば、画素ごとの輝度のばらつきを改善することができるので、ELPANEL200 を用いた表示装置では、輝度ムラのない高品位な画質を得ることが可能である。

#### 【0118】

なお、ELPANEL200 は、上述した第 1 乃至第 4 の実施の形態の画素 201 の構成のいずれか 1 つを採用して構成するものでもよいし、第 1 乃至第 4 の実施の形態の画素 201 のうちの 2 つ以上を併用するものでもよい。

#### 【0119】

また、上述した第 1 乃至第 4 の実施の形態では、新たに設けた補助容量 221、231、241、および 251 の静電容量 Cas を、いずれも同一のものとしたが、補助容量 221、231、241、および 251 の静電容量は必ずしも同一である必要はない。また、静電容量 Cas はサンプリング用トランジスタ 31 の寄生容量 Cws よりも大きいほどよい。

#### 【0120】

本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨

を逸脱しない範囲において種々の変更が可能である。

【図面の簡単な説明】

【0 1 2 1】

【図1】基本となるELパネルの構成例を示すブロック図である。

【図2】画素の詳細な構成例を示したブロック図である。

【図3】画素の動作を説明するタイミングチャートである。

【図4】画素の動作について詳細に説明する図である。

【図5】画素の動作について詳細に説明する図である。

【図6】画素の動作について詳細に説明する図である。

【図7】画素の動作について詳細に説明する図である。

10

【図8】画素の動作について詳細に説明する図である。

【図9】画素の動作について詳細に説明する図である。

【図10】画素の動作について詳細に説明する図である。

【図11】画素の動作について詳細に説明する図である。

【図12】画素の動作について詳細に説明する図である。

【図13】フィールドスルー効果による電圧降下について説明する図である。

【図14】寄生容量を含む画素の等価回路を示す図である。

【図15】画素の配線パターンレイアウトを示す図である。

【図16】サンプリング用トランジスタ部分の配線パターンレイアウトの拡大図である。

20

【図17】本発明を適用したELパネルの実施の形態の構成例を示すブロック図である。

【図18】図17のELパネルの画素の第1の実施の形態の構成例を示す図である。

【図19】図18の画素による効果を説明する図である。

【図20】図18の画素を採用した場合の配線パターンレイアウトを示す図である。

【図21】図17のELパネルの画素の第2の実施の形態の構成例を示す図である。

【図22】図21の画素による効果を説明する図である。

【図23】図21の画素を採用した場合の配線パターンレイアウトを示す図である。

【図24】図17のELパネルの画素の第3の実施の形態の構成例を示す図である。

【図25】図24の画素を採用した場合の配線パターンレイアウトを示す図である。

【図26】図17のELパネルの画素の第4の実施の形態の構成例を示す図である。

30

【図27】図26の画素を採用した場合の配線パターンレイアウトを示す図である。

【符号の説明】

【0 1 2 2】

200 ELパネル , 201 画素(画素回路) , 221 , 231 , 241 , 2

51 補助容量

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図11】

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

■ 第1の金属層

■ 第2の金属層

- 第1の金属層

- 第2の金属層

- 第1の金属層と第2の金属層の接続コンタクト部

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

■ 第1の金属層

■ 第2の金属層

■ 第1の金属層と第2の金属層の接続コンタクト部

■ 第1の金属層とカソード層の接続コンタクト部

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

図24

■ 第1の金属層

■ 第2の金属層

■ 第1の金属層と第2の金属層の接続コンタクト部

■ 第2の金属層とカソード層の接続コンタクト部

【図25】

図25

【図26】

図26

【図27】

図27

■ 第1の金属層

■ 第2の金属層

■ 第1の金属層と第2の金属層の接続コンタクト部

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

H 0 5 B 33/14

A

G 0 9 G 3/30

K

(72)発明者 佐川 裕志

東京都港区港南1丁目7番1号 ソニー株式会社内

F ターム(参考) 3K107 AA01 BB01 CC31 EE03 HH04

5C080 AA06 BB05 DD05 EE29 FF11 HH09 JJ02 JJ03 JJ04 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 面板和驱动控制方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP2009288593A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2009-12-10 |

| 申请号            | JP2008142057                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2008-05-30 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 妹尾佑樹<br>内野勝秀<br>佐川裕志                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 妹尾 佑樹<br>内野 勝秀<br>佐川 裕志                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H05B33/08 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | Y02B20/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.642.B G09G3/20.611.H H05B33/08 H05B33/14.A G09G3/30.K G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC31 3K107/EE03 3K107/HH04 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE29 5C080/FF11 5C080/HH09 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/AB22 5C380/AC07 5C380/AC09 5C380/AC11 5C380/AC20 5C380/BA28 5C380/BA36 5C380/BA38 5C380/BA39 5C380/BA40 5C380/BB02 5C380/BB05 5C380/BD02 5C380/CA08 5C380/CA12 5C380/CA54 5C380/CB01 5C380/CB27 5C380/CB31 5C380/CC02 5C380/CC03 5C380/CC04 5C380/CC06 5C380/CC07 5C380/CC27 5C380/CC33 5C380/CC41 5C380/CC62 5C380/CC77 5C380/CD012 5C380/CD022 5C380/CD032 5C380/CE01 5C380/DA02 5C380/DA06 5C380/DA47 5C380/HA03 5C380/HA06 5C380/HA08 |         |            |

| 代理人(译)         | 西川 孝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

## 摘要(译)

要解决的问题：能够改善每个像素的亮度变化。解决方案：当存储电容器251设置在采样晶体管31的栅极g和源极s之间时，它等于采样晶体管31的寄生电容Cws变大的事实。采样晶体管31的寄生电容Cws变大的事 实意味着尽管场直通电压降本身增加，但是每个像素201的场通电压降量 的变化减小。结果，可以改善由于场直通电压降引起的每个像素的亮度 变化。本发明可以应用于例如EL面板。 .The 26