(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4559847号

(P4559847)

(45) 発行日 平成22年10月13日(2010.10.13)

(24) 登録日 平成22年7月30日(2010.7.30)

(51) Int.Cl.

F 1

|             |              |                  |      |      |       |

|-------------|--------------|------------------|------|------|-------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J     |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 612 F |

| <b>H03F</b> | <b>3/343</b> | <b>(2006.01)</b> | G09G | 3/20 | 623 B |

| <b>H03M</b> | <b>1/74</b>  | <b>(2006.01)</b> | G09G | 3/20 | 642 B |

|             |              |                  | G09G | 3/20 | 680 G |

請求項の数 5 (全 53 頁) 最終頁に続く

(21) 出願番号 特願2004-500412 (P2004-500412)

(86) (22) 出願日 平成15年4月23日 (2003.4.23)

(86) 国際出願番号 PCT/JP2003/005165

(87) 国際公開番号 WO2003/092165

(87) 国際公開日 平成15年11月6日 (2003.11.6)

審査請求日 平成18年4月20日 (2006.4.20)

(31) 優先権主張番号 特願2002-127638 (P2002-127638)

(32) 優先日 平成14年4月26日 (2002.4.26)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2003-74549 (P2003-74549)

(32) 優先日 平成15年3月18日 (2003.3.18)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 302020207

東芝モバイルディスプレイ株式会社

埼玉県深谷市幡羅町一丁目9番地2

(74) 代理人 110000899

特許業務法人 松田国際特許事務所

(74) 代理人 100092794

弁理士 松田 正道

(72) 発明者 柏植 仁志

東京都港区港南四丁目1番8号 東芝松下

ディスプレイテクノロジー株式会社内

審査官 武田 悟

最終頁に続く

(54) 【発明の名称】有機発光素子を用いた表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

共通ゲート線と、

前記共通ゲート線に設けられ、基準電流の入力をうける電流分配手段と、

前記共通ゲート線を介して前記電流分配手段からカレントミラー方式にて分配される前記基準電流に基づき駆動電流を生成する複数の駆動電流生成手段と、

前記基準電流を生成する基準電流生成手段とを有する、電流出力型駆動装置の駆動用半導体回路を複数備えた、有機発光素子を用いた表示装置であって、

前記基準電流生成手段は、

前記基準電流を決定するための少なくとも2つの抵抗素子群を有し、

隣り合う一対の前記駆動用半導体回路において、

一方の前記駆動用半導体回路の少なくとも1つの前記抵抗素子群である第1の抵抗素子群と、他方の前記駆動用半導体回路の少なくとも1つの前記抵抗素子群である第2の抵抗素子群とが接続されており、前記第1及び第2の抵抗素子群に流れる電流により前記基準電流が決定されることを特徴とする、有機発光素子を用いた表示装置。

## 【請求項 2】

前記駆動電流生成手段に用いられる半導体素子群のチャネル面積の総和に対する前記電流分配手段に用いられる半導体素子群のチャネル面積の総和の比が、0.01以上0.5以下である請求項1に記載の有機発光素子を用いた表示装置。

## 【請求項 3】

10

20

前記駆動電流生成手段に用いられる半導体素子群の半導体素子の（チャネル幅）／（チャネル長）の値が、0.01以上0.6以下である請求項1に記載の有機発光素子を用いた表示装置。

**【請求項4】**

前記共通ゲート線の全抵抗値を、前記基準電流生成手段により生成された前記基準電流の値に対する前記共通ゲート線のゲート電圧の最大値と最小値の差の電圧を前記基準電流の0.5%の値で割った値もしくは1Kのうち大きい方の値以上5M以下とした請求項1に記載の有機発光素子を用いた表示装置。

**【請求項5】**

前記駆動用半導体回路は、前記駆動電流生成手段により生成された前記駆動電流を、第1の切り替え手段を介して、有機発光素子に供給するようにし、前記第1の切り替え手段と逆の状態を決定する第2の切り替え手段を介して、前記駆動電流生成手段に所定電流値が流れるようにする電流経路形成部を有する、請求項1に記載の有機発光素子を用いた表示装置。

10

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、有機電界発光素子など、電流量により階調表示を行う表示装置に用いる電流出力を行う電流駆動型表示装置の駆動用半導体回路群等に関する。

**【0002】**

20

**【従来の技術】**

有機発光素子は、自発光素子であるため、液晶表示装置で必要とされるバックライトが不要であり、視野角が広いなどの利点から、次世代表示装置として期待されている。

**【0003】**

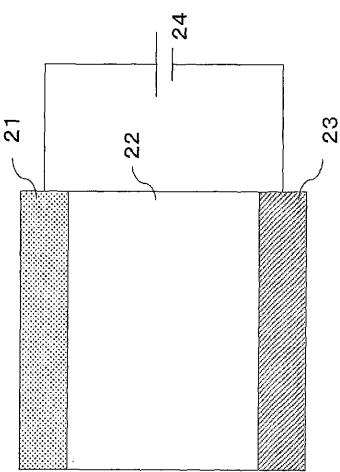

一般的な有機発光素子の素子構造の断面図を図2に示す。有機層22が陰極21及び陽極23により挟まれた構成となっている。これに直流電源24を接続すると、陽極23から正孔が、陰極21から電子が有機層22に注入される。注入された正孔及び電子は有機層22内を電源24により形成された電界により対極に移動する。移動途中ににおいて電子と正孔が有機層22内で再結合し、励起子を生成する。励起子のエネルギーが失活する過程において発光が観測される。発光色は励起子の持つエネルギーにより異なり、およそ有機層22の持つエネルギーバンドギャップの値に対応したエネルギーの波長を持つ光となる。

30

**【0004】**

有機層内で発生した光を外部に取り出すため、電極のうち少なくとも一方は可視光領域で透明な材料が用いられる。陰極には、有機層への電子注入を容易にするため仕事関数の低い材料が用いられる。例えば、アルミニウム、マグネシウム、カルシウムなどである。耐久性、さらなる低仕事関数化のためにこれらの合金や、アルミニリチウム合金といった材料が用いられることがある。

**【0005】**

一方陽極は正孔注入の容易性からイオン化ポテンシャルの大きいものを用いる。また陰極が透明性を持たないため、こちらの電極に透明性材料を用いることが多い。そのため一般的には、ITO(Indium Tin Oxide)、金、インジウム亜鉛酸化物(IZO)などが用いられる。

40

**【0006】**

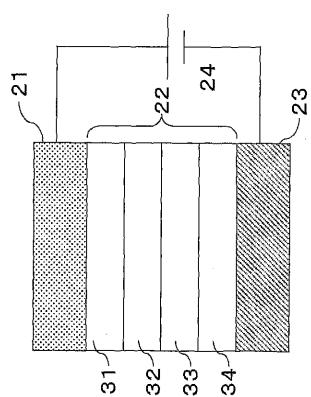

近年では低分子材料を用いた有機発光素子において、発光効率を高めるため、図3(a)のように有機層22を複数の層(この場合4層)で構成されることがある。電子注入層31は陰極21から電子を有機層内へ注入しやすくするために設けたものである。同様に正孔注入層34も陽極23からの正孔の注入しやすさを高めるために用いられる。これらの注入層は有機層22の膜厚に対しおよそ5%から20%程度の厚さで形成されることが多い。これにより有機層内に注入される電子正孔両キャリアの数を増加させることが可能

50

となる。これらの層に用いられる材料は、電子注入層 3 1 の場合電子親和力の値が陰極 2 1 の仕事関数に近く、正孔注入層 3 4 の場合、イオン化ポテンシャルの値が陽極 2 3 の値に近いものが用いられる。

#### 【 0 0 0 7 】

一方、電子輸送層 3 2 及び正孔輸送層 3 3 に用いられる材料は輸送するキャリアの移動度が高いものである。またいずれか一方の層が高い蛍光性を持つ材料であり、発光に寄与する層である。つまり、どちらかの層が発光層の役割もあわせて持っている。今現在、電子輸送性の発光材料が多いため一般的には電子輸送層 3 2 が発光層を兼ね、この層において、注入移動してきた電子正孔両キャリアの再結合がなされ、光を外部に放出している。よって電子輸送層 3 2 は、所望の波長を持った光を放出する材料を用いるということになる。代表的な材料として、緑色ではアルミニウムキノリン錯体、赤色ではユーロピウム錯体などがあげられる。なお発光層として用いる場合、1 つの層は必ずしも一つの材料で構成されるとは限らず、ある材料（ホスト材料）の中に、蛍光性色素（ゲスト材料）が分散されて構成される場合もある。

#### 【 0 0 0 8 】

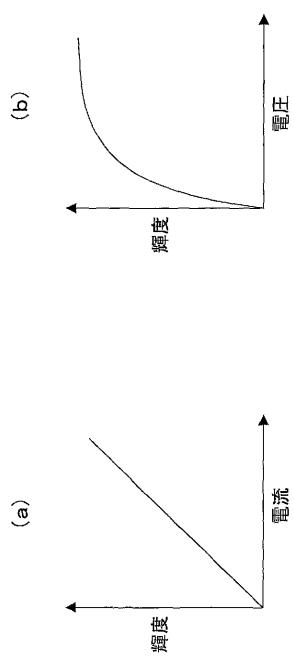

このようにして形成された有機発光素子は図 4 ( a ) に示すように、輝度は電流に対し比例し、図 4 ( b ) に示すように、電圧に対しては非線形な関係となる。それゆえ階調制御を行うには、電流値により制御を行う方がよい。

#### 【 0 0 0 9 】

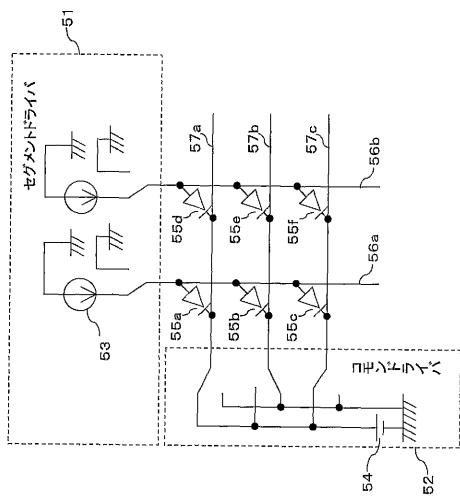

有機発光素子をパッシブマトリクス型表示装置に組み込んだ場合の例を図 5 に示す。有機発光素子 5 5 はセグメント信号線 5 6 及びコモン信号線 5 7 の交点に配置され、コモンドライバ 5 2 の操作により同一セグメント信号線 5 6 上の有機発光素子のうちのいずれか 1 つにのみセグメント信号線 5 6 からの電流を流すようにする。セグメント信号線 5 6 に流れる電流により階調表示を行う。

#### 【 0 0 1 0 】

従って、セグメントドライバ 5 1 は電流出力型のドライバである必要がある。

#### 【 0 0 1 1 】

一方、アクティブマトリクス型の場合、大きく分けて電圧駆動方式と電流駆動方式の 2 通りがある。

#### 【 0 0 1 2 】

電圧駆動方式は電圧出力型のソースドライバを用い、画素内部において電圧を電流に変換し、変換した電流を有機発光素子に供給する方法である。

#### 【 0 0 1 3 】

電流駆動方式は電流出力型のソースドライバを用い、画素内部では 1 水平走査期間出力された電流値を保持する機能のみを持たせ、ソースドライバと同じ電流値を有機発光素子に供給する方法である。

#### 【 0 0 1 4 】

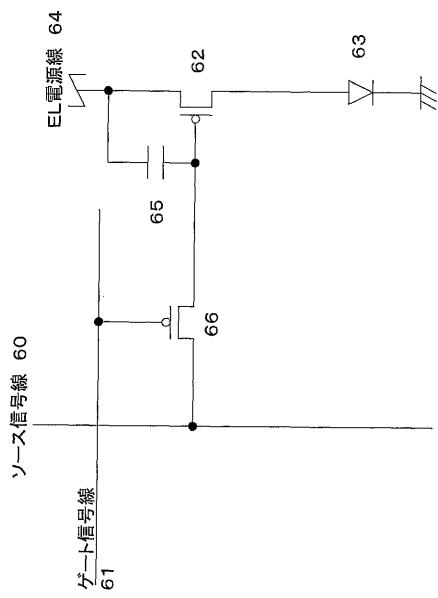

電圧駆動方式の画素内の回路構成の一例を図 6 に示す。ソース信号線 6 0 から供給された電圧は、当該画素選択期間内にトランジスタ 6 6 を通して駆動用トランジスタ 6 2 に印加される。なお、蓄積容量 6 5 は、画素選択期間が終わった後も 1 フレーム間情報を保持するために用いられる。

#### 【 0 0 1 5 】

駆動用トランジスタ 6 2 のゲート電圧 - ドレイン電流特性に応じて、EL 電源線 6 4 から有機発光素子 6 3 に電流が流れる。ソース信号線 6 0 に印加する電圧値を変えることで有機発光素子 6 3 に流れる電流量を変化させることが可能である。

#### 【 0 0 1 6 】

しかし、この方式では、駆動用トランジスタ 6 2 の電圧電流特性にはばらつきがあるとばらつきに応じて、有機発光素子に流れる電流にはばらつきが生じる問題がある。

#### 【 0 0 1 7 】

この画素回路は低温ポリシリコンプロセスによって形成されることが多い。低温ポリシ

10

20

30

40

50

リコンプロセスでは、多結晶化の際に用いられるレーザー照射量にむらがでやすく、この照射むらに応じてトランジスタの特性もばらつきが発生する。プロセス上でこの照射むらをなくすことが難しいため、このような電圧駆動方式においてはレーザー照射方向に対応した筋が発生し、表示むらが発生する問題がある。

#### 【0018】

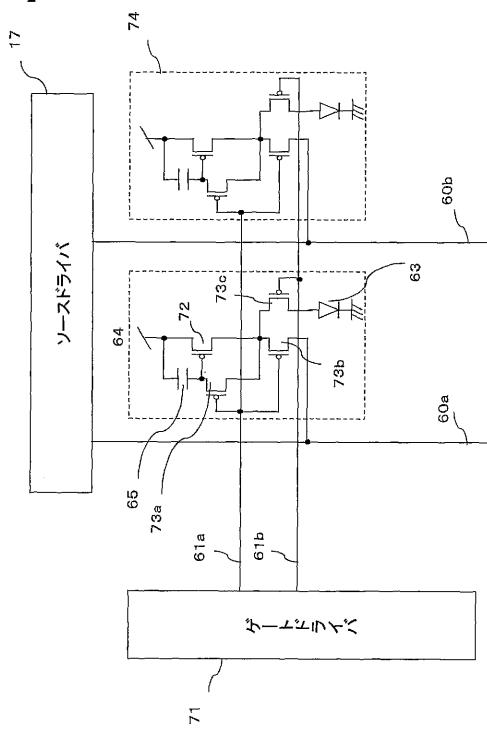

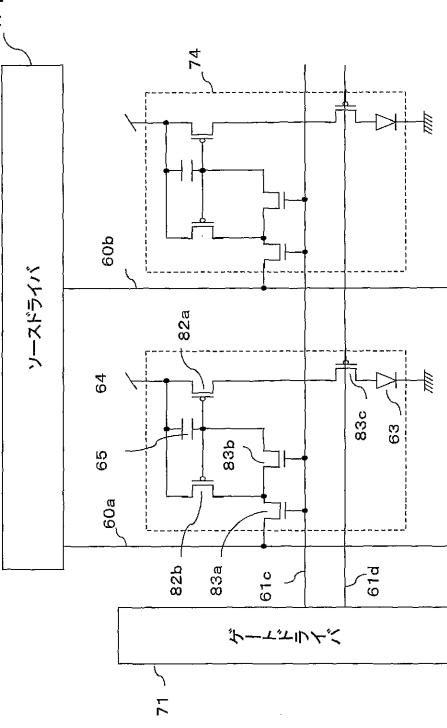

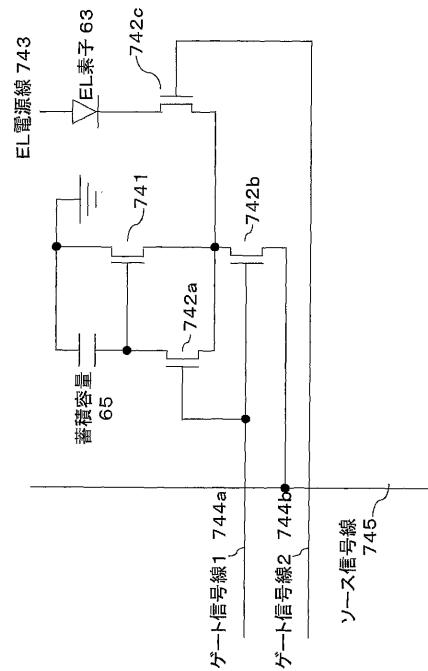

一方、電流駆動方式の例を図7及び図8に示す。図7の方式は画素回路にカレントコピア方式を用いたもの、図8の方式はカレントミラー方式を用いたものである。

#### 【0019】

図9(a)(b)に図7の画素74の動作時の回路を示す。

#### 【0020】

画素が選択されたときには図9(a)に示すようにその行のゲート信号線61aはスイッチを導通状態とするように、61bは非導通状態となるようにゲートドライバ71から信号が出力される。このときの画素回路の様子を図9(a)に示す。このときソースドライバ17に引き込まれる電流であるソース信号線60に流れる電流は点線101で示した経路を流れる。よってトランジスタ72にはソース信号線60に流れる電流と同一電流が流れる。すると節点102の電位はトランジスタ72の電流電圧特性に応じた電位となる。

#### 【0021】

次に非選択状態となるとゲート信号線61により図9(b)に示すような回路となる。EL電源線64から有機発光素子63に103で示す点線の経路で電流が流れる。この電流は節点102の電位とトランジスタ72の電流電圧特性により決まる。

#### 【0022】

図9(a)と(b)において節点102の電位は変化しない。従って同一トランジスタ72に流れるドレン電流は図9(a)と(b)において同一となる。これによりソース信号線60に流れる電流値と同じ値の電流が有機発光素子63に流れる。トランジスタ72の電流電圧特性にばらつきがあっても原理上電流101と103の値には影響がなく、トランジスタの特性ばらつきの影響のない均一な表示を実現できる。

#### 【0023】

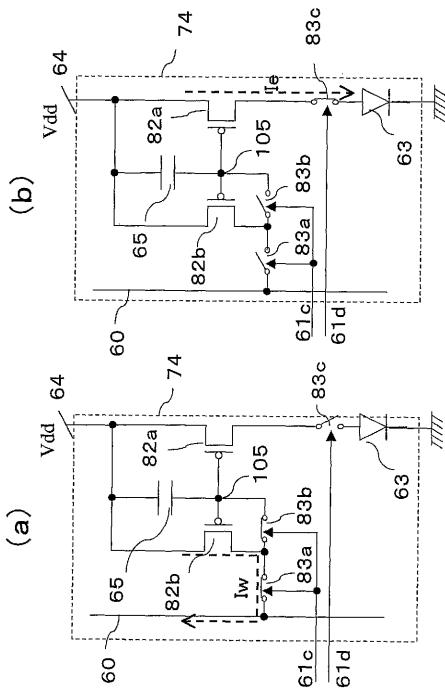

図8のカレントミラー方式の場合においても同様に、行選択時には図10(a)のIwに示す経路でソース信号線60に流れる電流が、画素内を流れる。電流Iwがトランジスタ82bに流れるときのゲート電位に対応した電圧が節点105にかかる。

#### 【0024】

行非選択時には図10(b)のIeに示す経路の電流が画素内を流れる。蓄積容量65により節点105の電位は(a)と(b)の期間の間保持される。そのため、トランジスタ82aと82bの特性が等しければ、Iw = Ieとなる。

#### 【0025】

トランジスタ特性のばらつきに対して有機発光素子に流れる電流が変化する可能性があるが、電圧駆動の場合に比べ、トランジスタ82aと82bは同一画素回路内にあり、近接配置とすることで、電流ばらつきを小さくすることが可能である。電圧駆動にくらべ、表示むらは少ない。

#### 【0026】

従って、均一な表示を得るために電流駆動方式を用いる必要があり、そのためにはソースドライバ17は電流出力型のドライバICでなければならない。

#### 【0027】

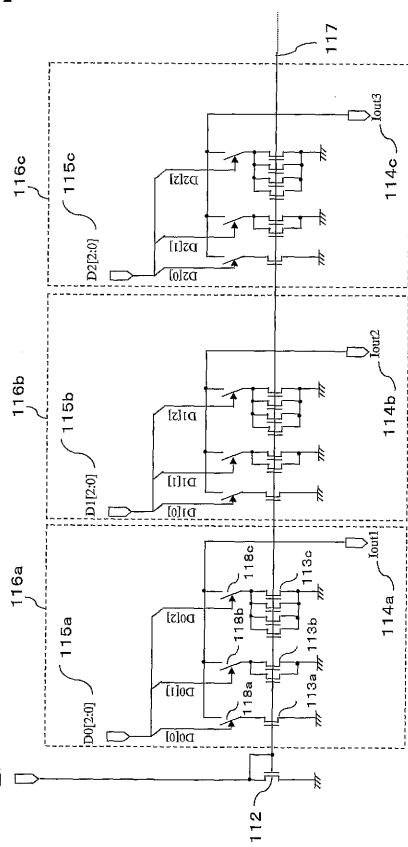

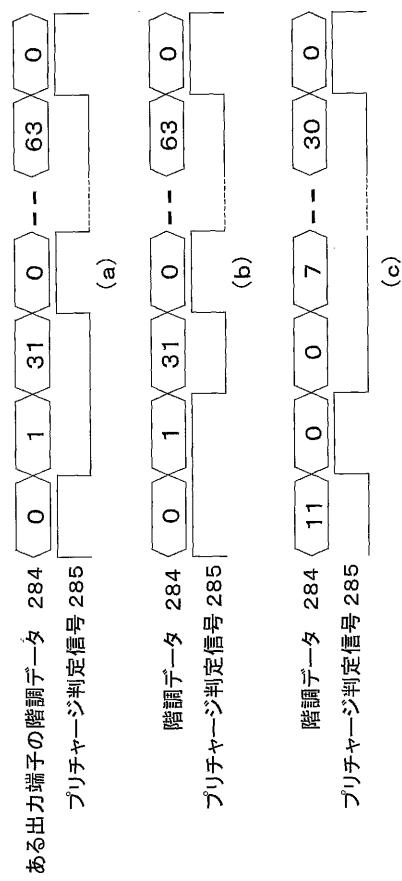

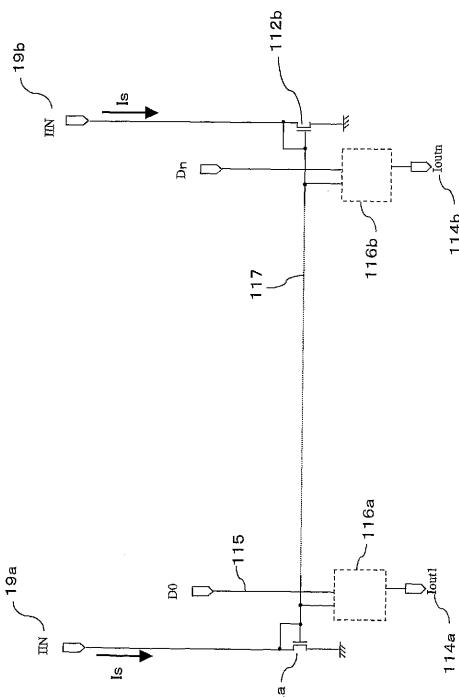

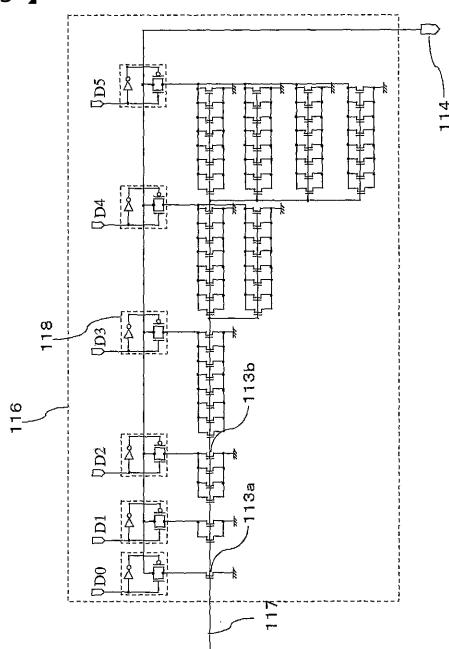

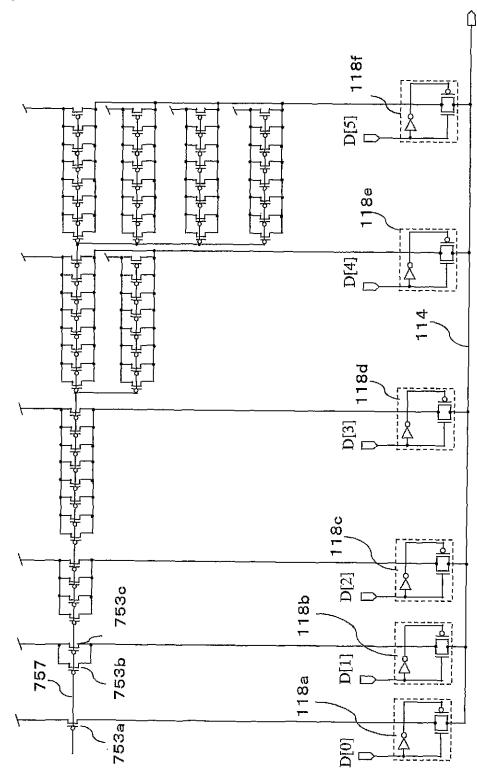

階調に応じた電流値を出力する電流ドライバICの出力段の例を図11に示す。表示階調データ115に対し、デジタルアナログ変換部116によりアナログの電流出力を114より行う。アナログデジタル変換部は、複数個（少なくとも階調データ115のビット数）の階調表示用電流源113とスイッチ118及び、1つあたりの階調表示用電流源113が流す電流値を規定する共通ゲート線117から構成される。

#### 【0028】

10

20

30

40

50

図11では3ビットの入力115に対しアナログ電流を出力する。ビットの重みに応じた数の電流源113を電流出力114に接続するかをスイッチ118により選択することで、例えばデータ1の場合は、電流源113が1つ分の電流、データ7の場合は7つ分の電流といったように階調に応じた電流が出力できる。この構成をドライバの出力数に応じた数だけ116を並べることで電流出力型ドライバが実現可能である。トランジスタ113の温度特性を補償するため共通ゲート線117の電圧は分配用ミラートランジスタ112により決められる。トランジスタ112と電流源群113はカレントミラー構成となり、基準電流19の値に応じて1階調あたりの電流が決められる。この構成により、階調により出力電流が変化し、かつ1階調あたりの電流は基準電流により決まる。

## 【0029】

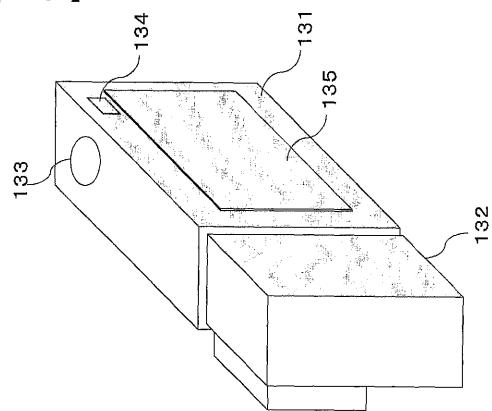

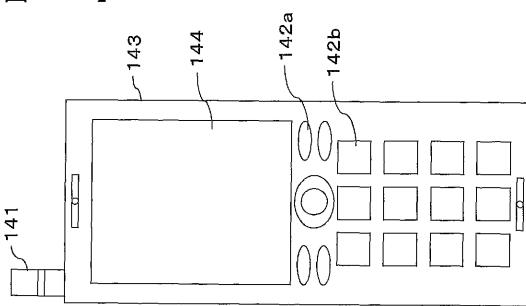

10

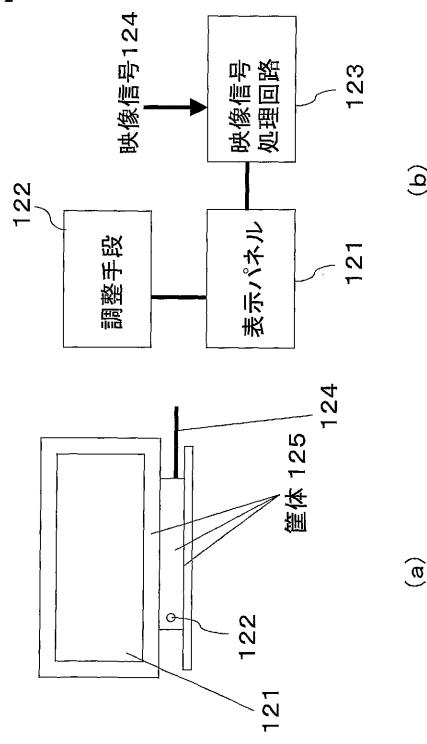

有機発光素子を用いた表示装置の例を図12から図14に示す。図12(a)、(b)はテレビ、図13はデジタルカメラもしくはデジタルビデオカメラ、図14は携帯情報端末を示している。有機発光素子は応答速度が速いため動画を表示する機会の多いこれらの表示装置にふさわしい表示パネルである。

## 【0030】

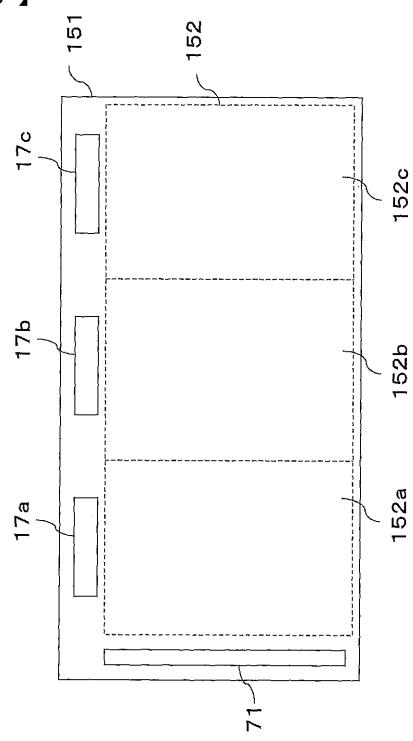

これらの表示装置のソース信号線数が増加すると、図15に示すように1つの表示パネル151に対し複数の電流出力型ソースドライバIC17を用いる必要がでてくる。このときドライバIC17の出力電流がチップ間で1%以上のばらつきを持つと152aから152cの各表示領域で輝度が異なりブロックむらが発生する。従ってドライバIC17のカスケード接続対策が必要である。

20

## 【0031】

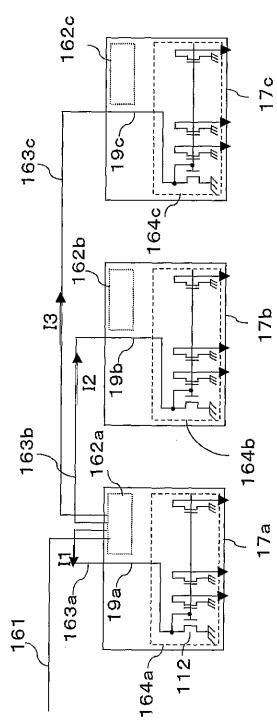

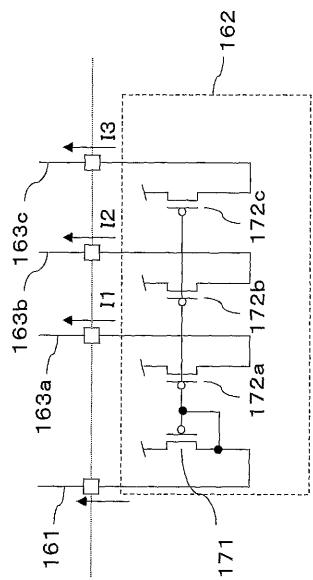

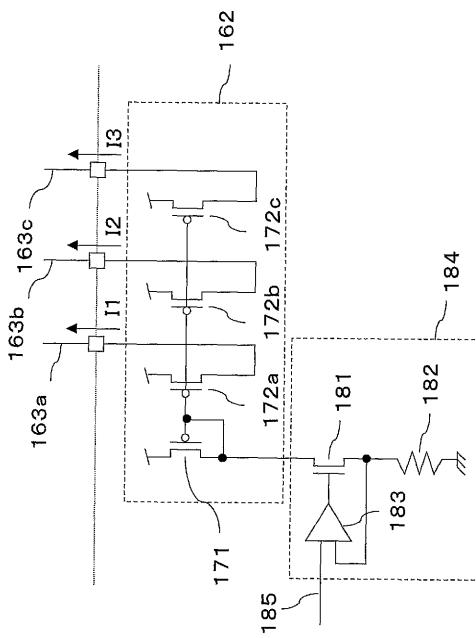

異なるチップ間で出力電流のばらつきを小さくするには、基準電流19の値をそろえる必要がある。基準電流をそろえる従来技術として図16(例えば、特開2000-293245号公報を参照)、図19にあげる方式が知られている。なお出力段164については詳細な記載がないため、図3で説明した出力段を適用している。

## 【0032】

図16の方法では、1つの元電流161をドライバIC17内の基準電流分配部162に入力し、複数の基準電流を生成する。図17に基準電流分配部の回路構成例を示す。カレントミラー回路により、元電流161に対し複数の基準電流163aから163cを出力する。この基準電流163を各ドライバIC17にそれぞれ供給することによりカスケード接続されるすべてのドライバIC17の基準電流を等しくすることで、ブロックむらをなくす。なお、161は電流でなくとも、電圧入力とし、図18に示す演算增幅器183への接続線185に接続する方法もある。電流電圧変換部184により電圧が電流に変化され、抵抗182に流れる電流が元電流となる。これをカレントミラーにより分配し基準電流163を出力する構成とする方法もある。抵抗182はドライバIC17内に内蔵してもよいし、外付けとしてもよい。

30

## 【0033】

図19に示す、同一基準電流を複数のドライバIC17に供給する第2の方法では、第1のドライバである17aには直接出力段164に基準電流161を入力する。電流受け渡し部191では、トランジスタ201を共通ゲート線117に接続し、基準電流に対してカレントミラー構成をとる。これをそのまま出力すると電流の向きが逆になるため、トランジスタ202、203からなるカレントミラー構成によりさらに電流方向を変えることで192により別のドライバIC17に基準電流を供給する。これにより、各ドライバICに同一基準電流が流れる。

40

## 【0034】

## 【発明が解決しようとする課題】

図16の構成において、ドライバICを複数個用いた表示装置を作る場合、基準電流分配部162の電流出力数により、複数配置可能なドライバICの数が制約される。例えば図17の構成では3つまでしか並べることができない。また162を外に配置すると別に半導体回路が必要となるため、実装コストやモジュール構成が複雑になるという問題があ

50

る。

#### 【0035】

また、図20に示す構成においては、基準電流を生成するのに2回カレントミラー回路を通す必要があり、ばらつきが大きくなりやすい。ばらつき抑制のためにはトランジスタサイズを大きくする必要があるためチップサイズを大きくする必要がでてくる。またチップ1つごとに2段のカレントミラーを通るため、N(N:自然数)個チップ接続の場合、2N回カレントミラーを繰り返すため、元電流161とN個目の基準電流がずれやすい。

#### 【0036】

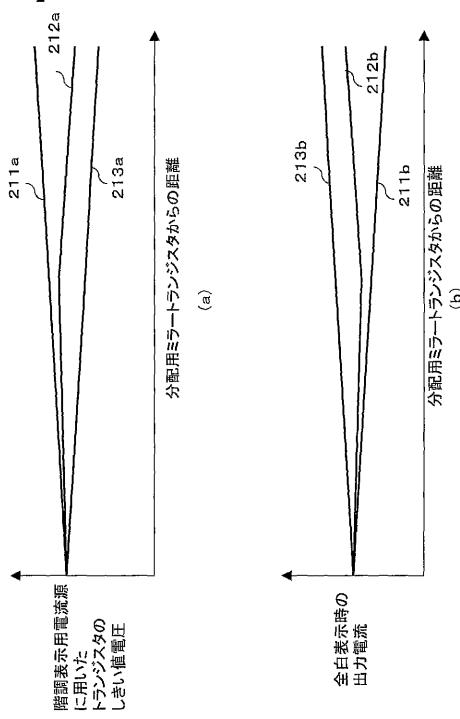

また、出力段の構成においても図11の構成でカレントミラーにより各出力の1階調あたりの電流を規定する方法では、カレントミラーの性質上、ミラー元のトランジスタと、出力用トランジスタの距離が離れるにつれてトランジスタの特性ばらつきの影響を受けやすくなる。

#### 【0037】

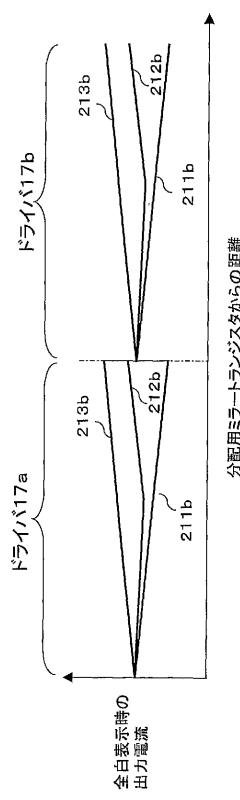

例えば左端に分配用ミラートランジスタ112を配置し、デジタルアナログ変換部116を出力パッド近傍に配置する。その際に、シリコンウエハー内で図21(a)に示すようなしきい値電圧のずれがあると、出力電流が図21(b)のようにドライバICの左右端で異なる。例えばしきい値電圧が211aのように変動すると、カレントミラーを形成する共通ゲート線117の電圧は等しいことから、左端のミラー元に比べ、右端の電流出力は小さくなる。同様に212ab、213abのような関係になる。

#### 【0038】

そのため、たとえ基準電流値がすべてのドライバIC17で等しくてもこのように出力特性を持つドライバICを複数個並べた場合、図22に示すようにドライバICの境界において電流値に差が発生する。これによりブロックむらが発生する。

#### 【0039】

電流ドライバICにおいて、ICごとのむらをなくすためには、基準電流を等しく入力できるようにすること、同一チップの左右端の電流値をそろえなければならないという課題がある。

#### 【0040】

##### 【課題を解決するための手段】

上記の課題を解決するために、第1の本発明は、

共通ゲート線と、

前記共通ゲート線に設けられ、基準電流の入力をうける電流分配手段と、

前記共通ゲート線を介して前記電流分配手段からカレントミラー方式にて分配される前記基準電流に基づき駆動電流を生成する複数の駆動電流生成手段と、

前記基準電流を生成する基準電流生成手段とを有する、電流出力型駆動装置の駆動用半導体回路を複数備えた、有機発光素子を用いた表示装置であって、

前記基準電流生成手段は、

前記基準電流を決定するための少なくとも2つの抵抗素子群を有し、

隣り合う一対の前記駆動用半導体回路において、

一方の前記駆動用半導体回路の少なくとも1つの前記抵抗素子群である第1の抵抗素子群と、他方の前記駆動用半導体回路の少なくとも1つの前記抵抗素子群である第2の抵抗素子群とが接続されており、前記第1及び第2の抵抗素子群に流れる電流により前記基準電流が決定されることを特徴とする、有機発光素子を用いた表示装置である。

#### 【0042】

また、第2の本発明は、

前記駆動電流生成手段に用いられる半導体素子群のチャネル面積の総和に対する前記電流分配手段に用いられる半導体素子群のチャネル面積の総和の比が、0.01以上0.5以下である第1の本発明の有機発光素子を用いた表示装置である。

#### 【0043】

また、第3の本発明は、

10

20

30

40

50

前記駆動電流生成手段に用いられる半導体素子群の半導体素子の（チャネル幅）／（チャネル長）の値が、0.01以上0.6以下である第1の本発明の有機発光素子を用いた表示装置である。

## 【0044】

また、第4の本発明は、

前記共通ゲート線の全抵抗値を、前記基準電流生成手段により生成された前記基準電流の値に対する前記共通ゲート線のゲート電圧の最大値と最小値の差の電圧を前記基準電流の0.5%の値で割った値もしくは1Kのうち大きい方の値以上5M以下とした第1の本発明の有機発光素子を用いた表示装置である。

## 【0045】

10

また、第5の本発明は、

前記駆動用半導体回路は、前記駆動電流生成手段により生成された前記駆動電流を、第1の切り替え手段を介して、有機発光素子に供給するようにし、前記第1の切り替え手段と逆の状態を決定する第2の切り替え手段を介して、前記駆動電流生成手段に所定電流値が流れるようにする電流経路形成部を有する、第1の本発明の有機発光素子を用いた表示装置である。

## 【0046】

また、本発明に関連する第1の発明は、

共通ゲート線と、

前記共通ゲート線の両端に設けられ、基準電流の入力をうける第1および第2の電流分配手段と、前記共通ゲート線に沿って設けられ、前記電流分配手段からカレントミラー方式にて分配される前記基準電流に基づき駆動電流を生成する複数の駆動電流生成手段とを有する駆動電流出力機構と、前記電流分配手段の近傍に設けられ、基準電圧を有する基準電圧信号および前記基準電圧より高い電圧を有する所定の電源から前記基準電流を生成する基準電流生成手段とを備えた駆動用半導体回路を、それぞれの前記共通ゲート線の端部が隣り合うように複数配列してなる電流駆動型表示装置の駆動用半導体回路群であって、

隣り合う一対の前記駆動用半導体回路において隣り合う一対の前記基準電流生成手段は、互いに相手の前記駆動用半導体回路から前記所定の電源を取得し、これと自らに供給される前記基準電圧信号とから前記基準電流を生成し、

前記駆動用半導体回路は、

20

前記隣り合う一対の前記基準電流生成手段のそれぞれの前記所定の電源と、その電源にそれぞれ対応する前記一対の前記基準電流生成手段との間に設けられた、直列接続された複数の抵抗素子を少なくとも有し、

前記直列接続された複数の抵抗素子の一部は前記隣り合う一対の駆動用半導体回路の一方のチップ上に形成されており、残りは前記隣り合う一対の駆動用半導体回路の一方のチップ上に形成されている電流駆動型表示装置の駆動用半導体回路群である。

## 【0047】

また、本発明に関連する第2の発明は、共通ゲート線と、前記共通ゲート線の両端に設けられ、基準電流の入力をうける第1および第2の電流分配手段と、前記共通ゲート線に沿って設けられ、前記電流分配手段からカレントミラー方式にて分配される前記基準電流に基づき駆動電流を生成する複数の駆動電流生成手段とを有する駆動電流出力機構と、前記電流分配手段の近傍に設けられ、基準電圧を有する基準電圧信号および前記基準電圧より高い電圧を有する所定の電源から前記基準電流を生成する基準電流生成手段とを備えた駆動用半導体回路を、それぞれの前記共通ゲート線の端部が隣り合うように複数配列してなる電流駆動型表示装置の駆動用半導体回路群であって、

40

隣り合う一対の前記駆動用半導体回路において隣り合う一対の前記基準電流生成手段は、互いに相手の前記駆動用半導体回路から前記所定の電源を取得し、これと自らに供給される前記基準電圧信号とから前記基準電流を生成し、

前記隣り合う一対の前記基準電流生成手段のそれぞれの前記所定の電源と、その電源にそれぞれ対応する前記一対の前記基準電流生成手段との間にそれぞれ設けられた抵抗素子

50

が設けられている電流駆動型表示装置の駆動用半導体回路群である。

**【0048】**

また、本発明に関連する第3の発明は、前記駆動電流生成手段に用いられる半導体素子群のチャネル面積の総和に対する前記第1および第2の電流分配手段に用いられる半導体素子群のチャネル面積の総和の比が、実質上0.01以上0.5以下である本発明に関連する第1または第2の発明の電流出力型駆動装置の駆動用半導体回路群である。

**【0049】**

また、本発明に関連する第4の発明は、前記駆動電流生成手段に用いられる半導体素子群の半導体素子の(チャネル幅)/(チャネル長)の値が、実質上0.01以上0.6以下である本発明に関連する第1または第2の発明の電流出力型駆動装置の駆動用半導体回路群である。10

**【0050】**

また、本発明に関連する第5の発明は、前記共通ゲート線の全抵抗値を、実質上、使用プロセスにおける基準電流値に対するゲート電圧の最大値と最小値の差の電圧を前記基準電流の実質上0.5%の値( $I_s \times 0.005$ )で割った値( $V_{gb} - V_{gw}$ )/( $I_s \times 0.005$ )もしくは1Kのうち大きい方の値以上5M以下とした本発明に関連する第1または第2の発明の電流出力型駆動装置の駆動用半導体回路群である。

**【0051】**

また、本発明に関連する第6の発明は、前記入力信号に応じて、前記駆動電流生成手段を出力段に接続するか否かを第1の切り替え手段群により決定する駆動用半導体回路群において、前記第1の切り替え手段群と逆の状態を決定する第2の切り替え手段群を介して、前記駆動電流生成手段に所定電流値が流れるようにする電流経路形成部を有する本発明に関連する第1または第2の発明の電流出力型駆動装置の駆動用半導体回路群である。20

**【0052】**

また、本発明に関連する第7の発明は、基準電流の入力をうける第1および第2の電流分配手段と、前記電流分配手段から分配される前記基準電流に基づき駆動電流を生成する複数の駆動電流生成手段とを有する駆動電流出力機構と、基準電圧を有する基準電圧信号および前記基準電圧より高い電圧を有する所定の電源から前記基準電流を生成する基準電流生成手段とを備えた電流駆動型表示装置の駆動用半導体回路を、それぞれの前記基準電流の出力が隣り合うように複数配列してなる駆動用半導体回路群であって、30

隣り合う一対の前記駆動用半導体回路において、それぞれの前記基準電流生成手段は、互いに相手の前記駆動用半導体回路から前記所定の電源を取得し、これと自らに供給される前記基準電圧信号とから前記基準電流を生成し、

前記駆動電流出力機構は多段構造を有し、

前記多段構造の各段は、少なくとも一つの、電流源および前記電流源から複数の出力を取り出す受け渡し部を有する組を有し、

前記多段構造の第1の段の電流源は前記電流分配手段から分配される前記基準電流であって、

前記多段構造の最終段の受け渡し部の前記複数の出力は前記駆動電流であって、最終段を除く前記各段の受け渡し部の前記複数の出力は、それぞれ下段の前記組の前記電流源に与えられているものである。40

電流駆動型表示装置の駆動用半導体回路群である。

**【0053】**

また、本発明に関連する第8の発明は、前記駆動用半導体回路は、前記隣り合う一対の前記駆動用半導体回路のそれぞれの基準電流生成手段の前記所定の電源と、その電源にそれぞれ対応する前記一対の前記基準電流生成手段との間に設けられた、直列接続された複数の抵抗素子を少なくとも有し、

前記直列接続された複数の抵抗素子の一部は、前記隣り合う一対の駆動用半導体回路の一方のチップ上に形成されており、残りは前記隣り合う一対の駆動用半導体回路の他方のチップ上に形成されている本発明に関連する第7の発明の電流駆動型表示装置の駆動用半50

導体回路群である。

**【0054】**

また、本発明に関連する第9の発明は、前記駆動用半導体回路は、

前記隣り合う一対の前記駆動用半導体回路のそれぞれの基準電流生成手段の前記所定の電源と、その電源にそれぞれ対応する前記一対の前記基準電流生成手段との間に設けられた、並列接続された複数の抵抗素子を少なくとも有し、

前記並列接続された複数の抵抗素子の一部は、前記隣り合う一対の駆動用半導体回路の一方のチップ上に形成されており、残りは前記隣り合う一対の駆動用半導体回路の他方のチップ上に形成されている本発明に関連する第7の発明の電流駆動型表示装置の駆動用半導体回路群である。

10

**【0055】**

また、本発明に関連する第10の発明は、前記基準電流生成手段のそれぞれの前記所定の電源と、その電源にそれぞれ対応する前記一対の前記基準電流生成手段との間に設けられた抵抗素子を備えた本発明に関連する第7の発明の電流駆動型表示装置の駆動用半導体回路群である。

**【0056】**

また、本発明に関連する第11の発明は、本発明に関連する第1から10のいずれかの発明の駆動用半導体回路群を具備した表示装置である。

**【0057】**

**【発明の実施の形態】**

20

以下本発明の実施の形態について、図面を参照しながら説明を行う。

**【0058】**

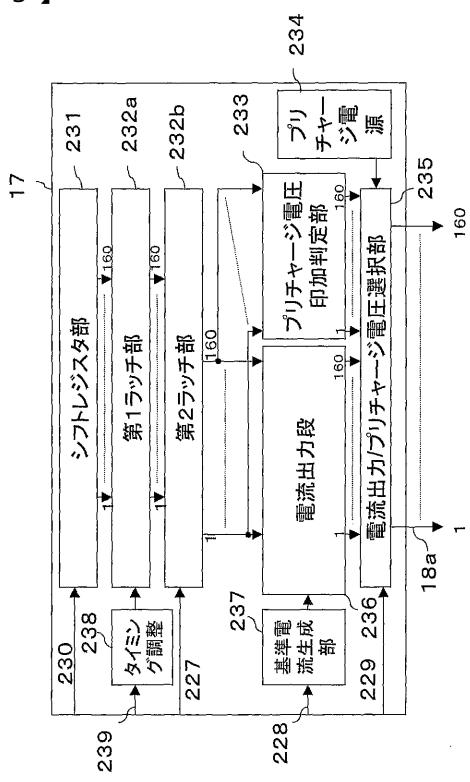

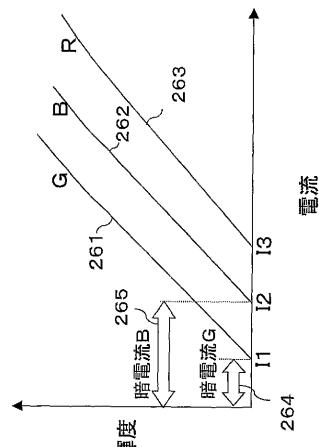

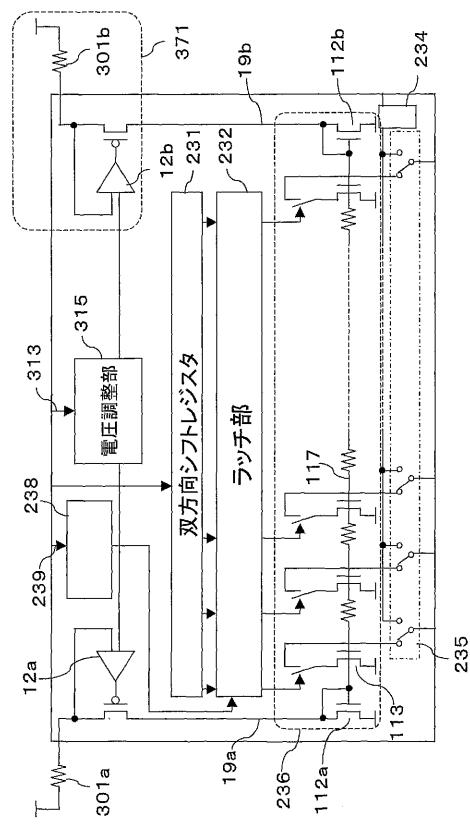

本発明の実施の形態における電流出力型ソースドライバIC17の構成を図23に示す。この例ではシフトレジスタの段数が160で160出力を持つドライバである。出力数は単に1出力あたりに必要なシフトレジスタ231及びラッチ部232、電流出力段236、プリチャージ電圧印加判定部233、電流出力／プリチャージ電圧選択部235の数を出力数の増減に応じて、増減させることで実現可能であるため、任意の出力数に対応可能である。ただし、出力数が増加するとチップサイズが大きくなりすぎることと、汎用性がなくなるため600程度くらいが実用上最大である。

**【0059】**

30

図23の構成において映像信号239の入力をシフトレジスタ部231及び2つのラッチ部232により各出力端子に分配する。分配された映像信号は電流出力段236とプリチャージ電圧印加判定部233に入力される。電流出力段236では、映像信号と基準電流生成部237により生成された基準電流から、階調に応じた電流値を出力する。一方プリチャージ電圧印加判定部233では、映像信号により階調に応じた電流を出力するかプリチャージ電圧を出力するかどうか判定するための信号を生成する。プリチャージ電圧印加判定部233の出力信号に応じてドライバIC17の外部に階調に応じた電流を出すか、プリチャージ電源234から供給される電圧を供給するか選択する電流出力／プリチャージ電圧選択部235を介してドライバIC17外部に電流もしくは電圧が出力される。

**【0060】**

40

プリチャージ電源234から出力される電圧は、表示パネルに黒を表示するために必要な電圧値となる。このプリチャージ電圧を印加する方法はアクティブマトリクス型表示装置に電流出力に応じて階調表示を行うためのドライバIC17特有の構成である。なお、パッシブマトリクス用のドライバICではプリチャージ電圧印加判定部233、プリチャージ電源234、電流出力／プリチャージ電圧選択部235は必要ない。

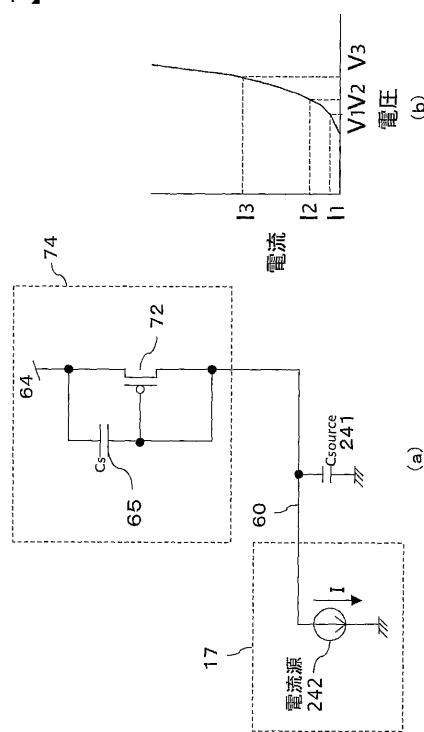

**【0061】**

例えば図7に示す画素構成のアクティブマトリクス型表示装置において、ソース信号線からある画素に所定電流値を書き込む場合について考える。このときの1画素の等価回路は図9(a)に示すようになり、さらにプリチャージ回路がない場合のソースドライバIC17の出力段から画素までの電流経路に関係する回路を抜き出した回路は図24(a)

50

のようになる。

#### 【0062】

階調に応じた電流  $I$  がドライバ IC 17 内から、電流源 242 という形で引き込み電流として流れる。この電流はソース信号線 60 を通じて、画素 74 内部に取り込まれる。取り込まれた電流は駆動トランジスタ 72 を流れる。つまり、選択された画素 74 において EL 電源線 64 から駆動トランジスタ 72、ソース信号線 60 を介して、ソースドライバ IC 17 に電流  $I$  が流れる。

#### 【0063】

映像信号が変化して電流源 242 の電流値が変化すると、駆動トランジスタ 72 及びソース信号線 60 に流れる電流も変化する。そのときソース信号線の電圧は駆動トランジスタ 72 の電流 - 電圧特性に応じて変化する。駆動トランジスタ 72 の電流電圧特性が図 24 (b) である場合、例えば電流源 242 が流す電流値が  $I_2$  から  $I_1$  に変化したとすると、ソース信号線の電圧は  $V_2$  から  $V_1$  に変化することになる。この電圧の変化は電流源 242 の電流によっておこる。

10

#### 【0064】

ソース信号線 60 には浮遊容量 241 が存在する。 $V_2$  から  $V_1$  までソース信号線電圧を変化させるにはこの浮遊容量の電荷を引き抜く必要がある。この引き抜きにかかる時間

$T$  は、 $Q$  ( 浮遊容量の電荷 ) =  $I$  ( ソース信号線に流れる電流 ) ×  $T$  =  $C$  ( 浮遊容量値 ) ×  $V$  となる。ここで  $V$  ( 白表示時から黒表示時間の信号線振幅 ) は 5 [ V ]、 $C = 10 \text{ pF}$ 、 $I = 10 \text{ nA}$  とすると、 $T = 50 \text{ ミリ秒}$  必要となる。これは  $QCIF +$  サイズ ( 画素数  $176 \times 220$  ) を  $60 \text{ Hz}$  のフレーム周波数で駆動させるとの、1 水平走査期間 ( $75 \mu\text{s}$ ) よりも長くなるため、仮に、白表示画素の下の画素に黒表示を行おうとすると、ソース信号線電流が変化途中に画素に電流を書き込むためのスイッチトランジスタ 73a、73b が閉じてしまうため、中間調が画素にメモリーされることにより白と黒の中間の輝度で画素が光ってしまうことを意味する。

20

#### 【0065】

階調が低くなるほど  $I$  の値が小さくなり、浮遊容量 241 の電荷を引き抜きにくくなるため、所定輝度に変化する前の信号が画素内部に書き込まれてしまうという問題がある。この問題は低階調表示ほど顕著に現れる。極端にいうと黒表示時は電流源 242 の電流は 0 であり、電流を流さずに浮遊容量の 241 の電荷を引き抜くことは不可能である。

30

#### 【0066】

そこで、電流源 242 にくらべてインピーダンスの低い電圧源を用意し、必要に応じてソース信号線 60 に印加する構成をとることにした。この電圧源が図 23 のプリチャージ電源 234 に相当し、印加できるための機構が 235 である。

#### 【0067】

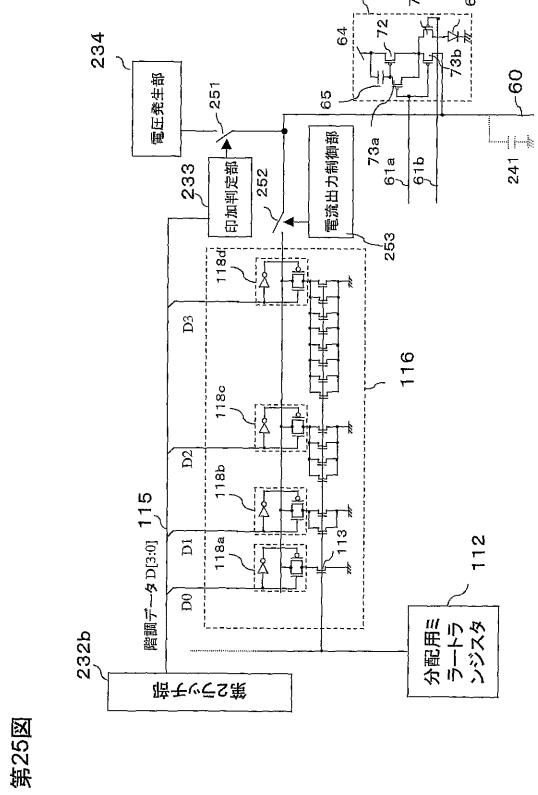

1 つのソース信号線 60 に対する概略回路を図 25 に示す。電圧発生部 234 から供給される電圧をソース信号線 60 に印加することで、浮遊容量 241 の電荷を充放電できるようにした。電圧発生部 234 から供給される電圧は、図 24 (b) の特性に応じて各階調電流に対応した電圧を供給できるようにしてもよいが、電圧発生回路にも階調データ 115 に応じたデジタルアナログ変換部が必要となるため回路規模が大きくなること、画素ごとに駆動トランジスタ 72 は特性ばらつきをもっているため同一階調電流に対し、対応する電圧が異なる。そのためデジタルアナログ変換部を設けて階調に応じた電圧を出してても、所定電流がかきこまれる訳でなく、その後所定電流まで電流源 116 により補正する必要がある。

40

#### 【0068】

このようなことから、実用上は電圧発生部 234 で発生する電圧は最も電流値の書き込みが難しい黒階調に対応した電圧のみ発生することが費用 ( チップ面積 ) 対効果の面で十分であるといえる。

#### 【0069】

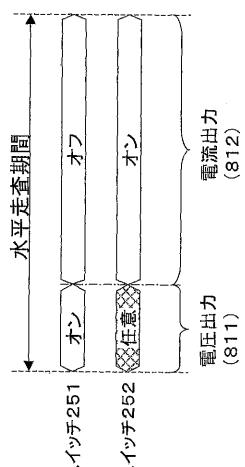

スイッチ 251 及び 252 の 1 水平走査期間内での動作タイミングを図 81 に示す。水

50

平走査期間のはじめに、浮遊容量 241 の電荷をリセットするため電圧発生部 234 からのプリチャージ電圧を印加する（期間 811）。電圧により電荷をリセットすることからこの期間は短くても目的を達するため最大 2 μ秒程度あればよい。次に期間 822 では、スイッチ 252 のみを導通状態とし、階調に応じた電流を画素 74 に供給する。なお期間 822 により所定の電流値を書き込む動作が遅く、なるべく期間 822 を長くとりたいために、期間 811 は最大 1 水平走査期間の 10% 程度にしておく必要がある。

#### 【0070】

さらに、スイッチ 251 の制御機構としてプリチャージ電圧印加判定部 233 の出力を用いることで、入力階調データの値に応じて、プリチャージ電圧をいれるかいれないか選択することが可能となる（選択プリチャージ機能）。

10

#### 【0071】

電圧発生部 234 から出力される電圧値が、黒階調時の電流に対応した電圧（以降黒電圧という）のみとしたことから、例えば、階調データ 115 が連続した複数の水平走査間にわたって白の階調を表示するとした場合、ソース信号線は黒、白、黒、白状態を繰り返すことになる。もし、プリチャージを行わない場合、白状態が連続して発生することになる。つまりプリチャージを行うことによりかえって、信号線の変化を激しくすることになる上、白表示時の電流によっては、白になりきらず書き込み電流不足を生じるおそれがある。

#### 【0072】

そこで、プリチャージ判定部 233 を用いて、電流が比較的たくさん流れる階調ではプリチャージを行わず、黒階調付近の所定電流に変化しにくい階調のみプリチャージ電源 234 のアシストを受けるようにすればよい。そのためプリチャージ電圧印加判定部 233 は各出力に設け、階調データ 115 の値によりスイッチ 251 の操作を変更できるようにしている。判定出力は、階調 0（黒）の時のみプリチャージ電圧を入れる期間があり、その他の階調表示時にはプリチャージ電圧を入れないようにすることが最も効果がある。最低階調時の輝度を低くすることでコントラストも上昇し、より美しい絵が表示可能となる。

20

#### 【0073】

表示素子として用いる有機発光素子においては、発光色ごとに素子構成が異なり、キャリア注入効率、キャリア移動度、蛍光体の量子効率などが異なってくるため、発光開始電流が、発光色ごとに異なる可能性がある。

30

#### 【0074】

例を図 26 の電流 - 輝度の対応を示す直線 261 から 263 に示す。緑色は I1 以上、青色は I2 以上、赤色は I3 以上の電流を流すと発光する。すると画素 74 の駆動トランジスタ 72 のばらつきがないと仮定しても、図 24 (b) のように黒電圧が表示色ごとに V1 から V3 と異なってくる。低電流になるほど所定電流に変わるもの時間がかかることから、1つの電源でプリチャージ電圧を設定しようとすると、V1 の電圧をすべての素子に印加することになる。

#### 【0075】

このようにすれば、黒表示時にぼやっと光る黒浮きはなくなるが、次に白を表示しようとしたときに、プリチャージが無いときに比べ、赤表示画素では (V3 - V1) の電圧分これまでより余分に変化させる必要がある。そのため次に白表示を行う際に、電圧変化分が大きくなる分白まで変化しにくくなる問題が発生する。

40

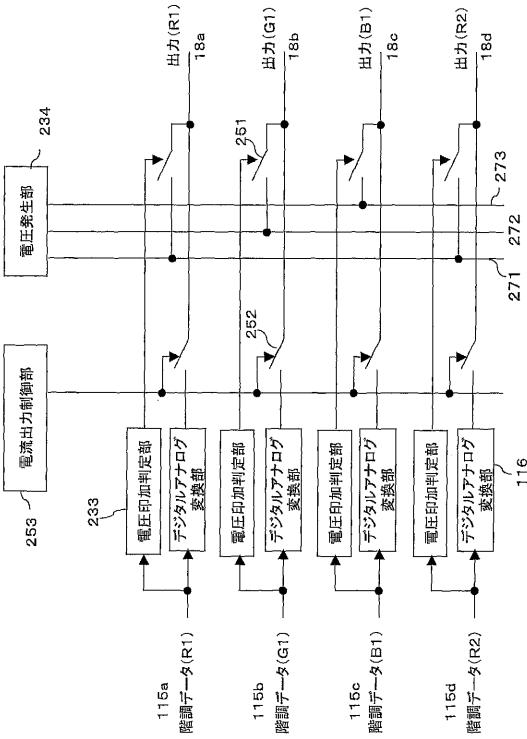

#### 【0076】

そこで、プリチャージ電源 234 を表示色ごとに別に設けることとした。ブロック図を図 27 に示す。ここで R は赤色、G は緑色、B は青色発光素子への出力として説明を行う。なお、表示色は、赤緑青の 3 原色でなくてもシアン、イエロー、マゼンダの 3 色でも構わない。

#### 【0077】

電圧発生部 234 の出力を 3 つ設け、出力 271 は R のソース信号線へ出力を行い、2

50

72はG、273はBへ出力する。このとき271の出力電圧は画素74の駆動トランジスタ72がI3の電流を流すときのソース信号線60の電圧とほぼ等しい電圧を出力するように設定する。出力272、273もそれぞれI1、I2の電流が画素トランジスタ72に流れるときのソース信号線60電圧とほぼ等しい値を出力すればよい。これによって、表示色ごとに適正な電圧値を画素に直接印加することができる。

#### 【0078】

従って、電流出力時に変化させるソース信号線電位は少なくてすむため、より短い時間で所定の電流値に変化させることができ、書き込み不足がおきにくい構成となる。

#### 【0079】

ところで、全画面が黒表示といったソース信号線の変化がないパターンにおいては、1フレームのはじめのみプリチャージ電圧を印加すれば、あとは黒電流のみでも十分所定の階調が流れる。

#### 【0080】

つまり同じ黒表示時においても、前の水平走査期間でソース信号線に流した電流値によって、電流のみで所定電流値まで変化する時間が異なり、変化量が大きくなるほど、変化に時間がかかる。例えば白表示後の黒表示をするには時間がかかるが、黒表示後に黒表示を行う場合には信号線は駆動トランジスタ72のばらつき分のみの変化となるため変化に要する時間は短い。

#### 【0081】

そこで、階調データ239に同期して、プリチャージ電圧を印加するかどうかを判定する信号（プリチャージ判定信号281）を色ごとに導入することで、任意の階調で、もしくは同一階調でもプリチャージありなしを選択できるような構成を導入することも可能である。

#### 【0082】

このときのドライバIC17の構成を図28に示す。階調データ239に対し、プリチャージ判定信号281を付加する。これに伴い、ラッチ部282もプリチャージ判定信号をラッチする必要があるため、映像信号ビット数+1ビットのラッチ部を持つようにする。

#### 【0083】

プリチャージ電圧を印加するか、階調に応じた電流を出力するかは、プリチャージ判定信号線285及び、プリチャージON/OFF信号229により電流出力／プリチャージ電圧選択部235で決められ、プリチャージON/OFF信号229及び、プリチャージ判定信号線285がともにプリチャージをするという信号がきたときに、プリチャージ電源234より供給される電圧が18に出力される。その他の期間では、電流出力段からの電流が18に出力される。

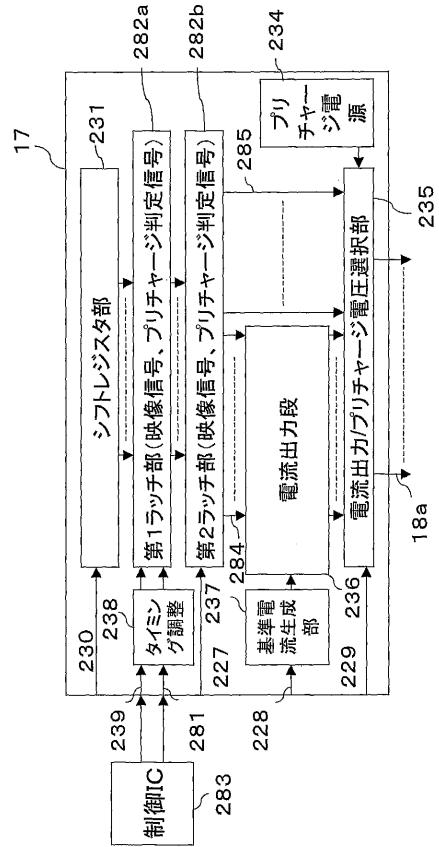

#### 【0084】

例えば、図29(a)では階調0のときにプリチャージを入れるようにした例、図29(b)では階調0と1の時にプリチャージを入れた例、図29(c)では階調0のときでかつ、前期間での階調が0でないときにプリチャージを入れた場合（階調0の時にプリチャージするが、連続する場合には階調0でもプリチャージを行わない）をそれぞれ示している。

#### 【0085】

この方法では、前の方法と異なり同一階調でも、1水平走査期間前のソース信号線の状態に応じてプリチャージをしたりしなかったりを選択できる利点がある。

#### 【0086】

なお、このプリチャージ判定信号は制御IC283から供給される。制御IC283のコマンド操作により図29(a)から(c)に示したようにプリチャージ判定信号281のパターンを変更させて出力することができる。

#### 【0087】

ソース信号線の容量や、1水平走査期間の長さに応じて、ソースドライバIC17外部

10

20

30

40

50

から柔軟にプリチャージの設定を変更させることができ、汎用性がますという利点がある。

**【0088】**

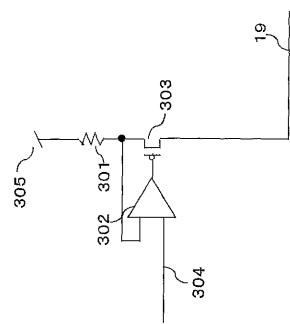

図30は基準電流発生回路を示した図である。基準電流は図11で示した出力段の構成において、1階調あたりの電流値を規定するものである。そのためドライバIC17ごとの基準電流19ばらつきが小さくなければ、ICの境目でブロックむらが発生する。

**【0089】**

そこで図30に示すようなフィードバックがかかる基準電流発生回路の構成とする。この回路では基準電流19は電源305と基準電圧信号線304の電位差を抵抗素子301で割った値となる。電流19のばらつきは、抵抗素子301のばらつき及び演算増幅器302の入力偏差により決まる。

**【0090】**

抵抗素子301のばらつきは市販されているチップ抵抗素子であれば0.5%程度に抑えられる。

**【0091】**

一方演算増幅器302の入力偏差は15mV程度である。そこで抵抗両端の電位差を15mVに対して大きくすることで出力偏差の影響を小さくすることができる。例えば2V以上電位差がある構成とすれば出力偏差によるばらつきは0.75%以下とすることが可能となる。

**【0092】**

このようにして、ドライバIC17間での基準電流のばらつきを1%以内に抑えた電流源を形成する。

**【0093】**

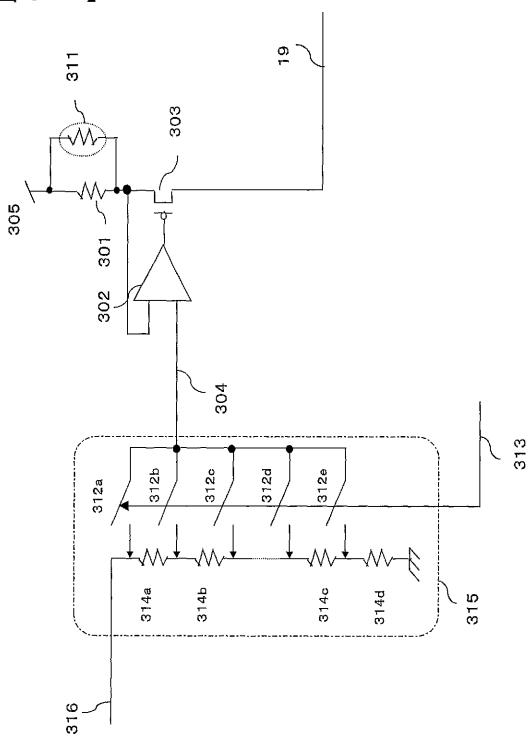

さらにこの電流源は図31のような構成にすることで、温度特性の補償やプログラマブルに基準電流値を変更できるようになる。

**【0094】**

温度特性の補償としては抵抗素子301に並列に温度補償素子311をいれ、温度によって抵抗値をえることで、基準電流量をえることが可能となり、有機発光素子の温度特性を補償することが可能である。有機発光素子はわずかながら電流対輝度特性において温度依存性を持ち、温度が高くなるほど輝度が低下する。そこで温度補償素子311により、温度が高くなると電流量が増加するように301と311の合成抵抗を下げるようすれば、温度特性を補償できる。

**【0095】**

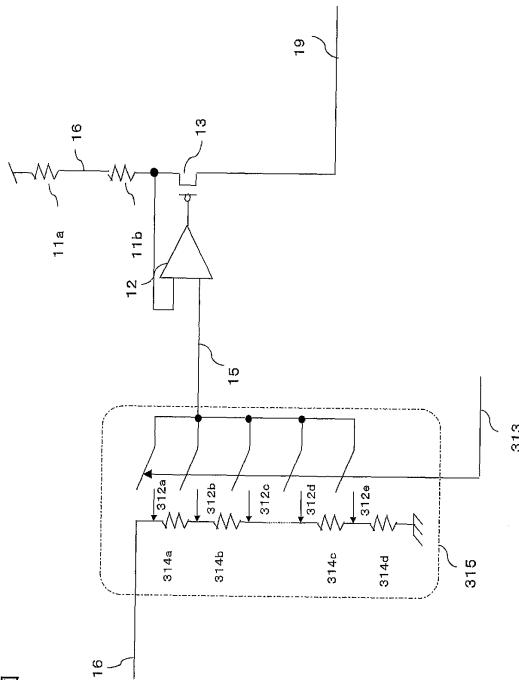

また、電圧調節部315を設けたことで制御データ313の値により、基準電圧信号線304の電圧値を変化させられ、基準電流が変化する。

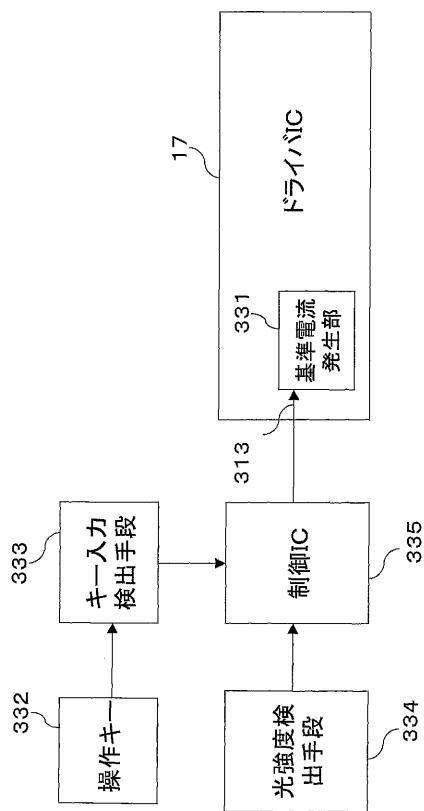

**【0096】**

この機能は例えば図14の携帯情報端末の表示装置に組み込まれた半導体回路において、携帯情報端末の電池の持ちをよくするため、キー142への入力時には所定の基準電流19を流し、一定時間後には基準電流を下げ表示パネルの輝度を低下させ、表示パネル及び半導体回路の消費電力を小さくするということを可能にする。

**【0097】**

これを実現するための回路ブロックを図33に示す。操作キーに対し、キー入力を検出するための検出手段333を設け、キー入力されたかどうか判別する。判定結果を制御IC335に送る。制御IC335はソースドライバIC17の基準電流発生部331の発生電流値を制御する制御データ313の値を書き換える。これによって、発生する基準電流値をキー入力されたかどうかにより変更することが可能となる。制御IC335にカウント機能を設ければ、一定時間後に元の設定に戻すといったことも可能となる。

**【0098】**

同様に、視認性を高めるため外光により表示パネルの輝度を変化させたい場合においても、光強度検出手段334の検出結果を基に、基準電流を設定する制御データ313の値

10

20

30

40

50

を書き換え、強い外光下では輝度を高くし、周りが暗い場合には輝度を抑えて低電力化をはかることも可能となる。

#### 【0099】

複数のチップを1つの表示装置に並べて配置した場合には、図32のように基準電流発生部の接続を行うことで1つのドライバIC17の制御データを書き換えることで他のすべてのドライバIC17の基準電流を変化させることができるとなる。この方法は1つのドライバIC17での電圧調節部315出力を、同一表示パネル内のすべてのドライバIC17の基準電圧信号線304に接続することで、基準電圧のチップ間ばらつきを小さくする。さらに、制御データ313及び基準電圧324の入力は一つのドライバIC17のみでよいため、外部入力信号線の配線引き回しが少なくなり、表示パネルの額縁を狭くすることが可能となる。また従来の基準電流を各ドライバに分配することに比べて、電圧を分配するこの方式はばらつきがないため有効である。同一電流を分配するのは難しいが、同一電圧を分配することは容易だからである。10

#### 【0100】

このようにして基準電流をドライバIC間でばらつきなく供給することが可能となる。

#### 【0101】

次に、出力段の構成について考える。

#### 【0102】

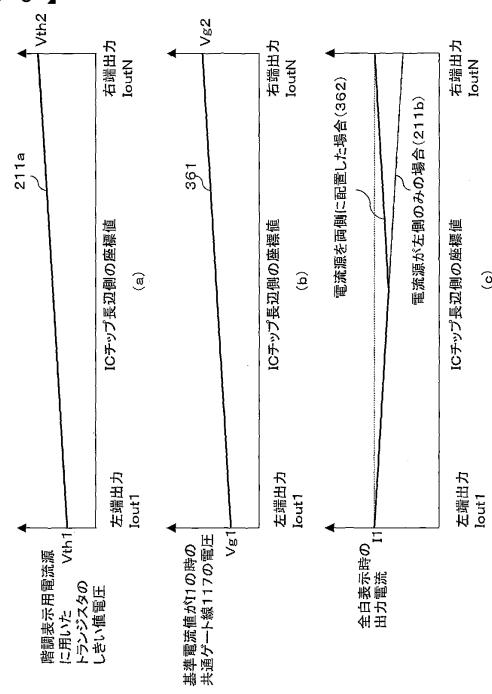

本実施の形態のドライバIC17の電流出力部は図34に示すような構成である。図11の構成に比べ基準電流19を出力段の両端から供給するようにしたことが異なる。映像信号データを出力電流量に変換するデジタルアナログ変換部116は例えば6ビットデータの場合図35の構成になる。ここで、階調表示用電流源113はビットの重みに応じた個数を用いて出力しているが、個数の代わりにチャネル幅を広げるという方法でもかまわないとする。20

#### 【0103】

また共通ゲート線117は高い抵抗を持つ材料により形成する。これにより、図36(a)に示すようなチップ両端でのトランジスタのしきい値電圧の変化211aがあった場合でも、共通ゲート線117の配線抵抗により、共通ゲート線117の電位をチップ左右端で異ならせることができとなり(図中直線361を参照)、これにより、従来右端のゲート電圧がVg1であったのがVg2まで上昇させることができる。出力電流値はゲート電圧により決まるため、図11の構成のときの211bから、362に示すような電流出力に変化する。これによって、左右の電流値を等しくすることが可能となる。30

#### 【0104】

同一チップの左右端の電流出力が等しくなり、1階調あたりの電流値を規定する基準電流がチップ間でばらつき無く供給できるような構成となるため、ドライバIC17の境目に発生しやすいブロックむらをなくすことが実現できる。

#### 【0105】

そのときのドライバICの概略ブロック図を図37に示す。

#### 【0106】

電流出力段236はカレントミラーにより構成される。ウエハー内のトランジスタ特性のなだらかな変化に対応するため、共通ゲート線117は高抵抗材料により構成される。チップ左右端に供給する基準電流発生部は371に示すような構成となり、左右のばらつきは最大でも0.7%程度に抑えられる。使用する外付抵抗301にはばらつきの小さいものを用いればさらに小さくすることも可能である。制御データ313により出力電圧値が異なる電圧調節部315の出力を左右の基準電流発生部371のオペアンプ12に入力することで、左右の基準電流19a及び19bは等しい値となる上に、制御データ313により同時に変化させることができる。40

#### 【0107】

入力映像信号239はタイミング調節部238により外部配線での遅延を調節し内部回路と同期させた後、双方向シフトレジスタ231の出力に応じて、各出力端子に分配され50

、水平走査期間値を保持するため 2 段のラッチ部 232 でラッチされる。ラッチされた映像信号データが電流出力段 236 に入力される。

#### 【0108】

電流出力段 236 はカレントミラー構成により、基準電流 19 を各出力に分配する。この図ではミラー元のトランジスタが 112 で、分配された電流を流すトランジスタが 113 となる。

#### 【0109】

分配された電流は、ラッチ部 232 から出力されたデータに基づきオンオフを行う階調表示用電流源 113 のドレイン側に設けられたスイッチ 118 を介して出力される。この例では 1 ビットであるので、データが 0 のときはスイッチ 118 がオフであり、電流が 0 10 、データが 1 の時は出力電流は 113 のトランジスタ 1 つ分の電流が流れる。この電流値は 112 のトランジスタとのミラー比及び基準電流値により決められる。なお、1 ビット以外でも各出力に図 35 の構成を持つ回路を配置すること、6 ビット 256 階調の出力を行うことも可能である。

#### 【0110】

電流出力はさらに電流出力 / プリチャージ電圧選択部 235 に入力される。これは図 24 で示した低階調表示時において、微少電流により浮遊容量の電荷を変化させることが難しいことに対し、電圧源により電荷の充放電を行うためのものである。プリチャージ電源 234 からの出力と、電流出力部の電流出力のいずれかを出力するか選択できる切り替え部が存在する。なお、この切り替え部は図 37 の構成以外でも図 25 の 251 、 252 に示すような 2 つのスイッチを設けてもよい。このスイッチにドライバ IC17 と表示パネルを電気的に切り離すハイインピーダンス出力を行わせる機能を設けてもよい。

20

#### 【0111】

電流出力を行うための階調表示用電流源 113 のトランジスタサイズによっては端子ごとの出力電流ばらつきが発生する。トランジスタサイズ（チャネル面積）と出力電流ばらつきの関係を図 38 に示す。基準電流のばらつきを考慮に入れ、チップ内、チップ間の隣接端子間のばらつきを 1 % 以内にする必要があることから図 38 における出力電流のばらつき（出力段での電流ばらつき）は 0.5 % 以下にすることが望ましく、階調表示用電流源 113 のトランジスタサイズは 30 平方ミクロン以上あることがよい。

30

#### 【0112】

なお図 37 ではプリチャージを行うかどうかの判定信号については、全体構成を説明するのみであることから省略した。図 23 、 28 の構成の 2 通りが考えられるため、図 23 の構成とする場合ラッチ部、プリチャージパルスによりスイッチを制御する回路を設ける。図 28 では、各色の映像信号に対し 1 ビット信号を増やした構成とし、1 ビット増やしたラッチ出力とプリチャージパルスによりスイッチを制御する構成にすればよい。

#### 【0113】

このように構成された電流ドライバ IC17 を用いて、図 39 に示すような表示を行うと、394 に示す行は、他の行の白表示に比べ輝度が高くなり、395 に示す部分は、他の行の白表示に比べ輝度が低くなる現象が、発生しやすい。

40

#### 【0114】

輝度が高くなる部分 394 （ここでは輝線と呼ぶ）は、ドライバ IC17 の端子で黒信号を出力する端子の数が少なくなる行で発生し、輝度が低くなる部分 395 （ここでは黒線と呼ぶ）は、ドライバ IC17 の端子で黒信号を出力する端子の数が多くなる行で発生する。

#### 【0115】

図 7 もしくは図 8 のような画素構成を持つ表示装置において、ドライバ IC17 の出力端子に接続されたソース信号線の電圧は、図 39 の信号線（列） 396 及び信号線（列） 397 において、図 40 に示すような、電圧波形となる。ここで、Vb は画素が黒を表示するときの電圧で、Vw は画素が白を表示するときの電圧である。

#### 【0116】

50

列396に対応するソース信号線の電圧波形は、図40(a)に示すように図39に示した画像に対応して、期間401では黒を示す電圧を、期間402では白を示す電圧を、期間403では黒を示す電圧を出力する。

#### 【0117】

一方、列397に対応するソース信号線の電圧波形は、図40(b)に示すように、1フレームの全ての期間において、白を示す電圧を出力する。このとき、行394の表示期間では電圧が低下する方向にハザードが発生し、より輝度が高くなる。行395の表示期間では電圧が上昇する方向にハザードが発生し、より輝度が低くなる。その結果、図39の行394では、他の白表示時に比べ輝度が高くなるため輝線が発生し、行395では、他の白表示時に比べ輝度が低くなるため、黒線が発生する。

10

#### 【0118】

このようなソース信号線電圧にハザードが出る要因について説明を行う。

#### 【0119】

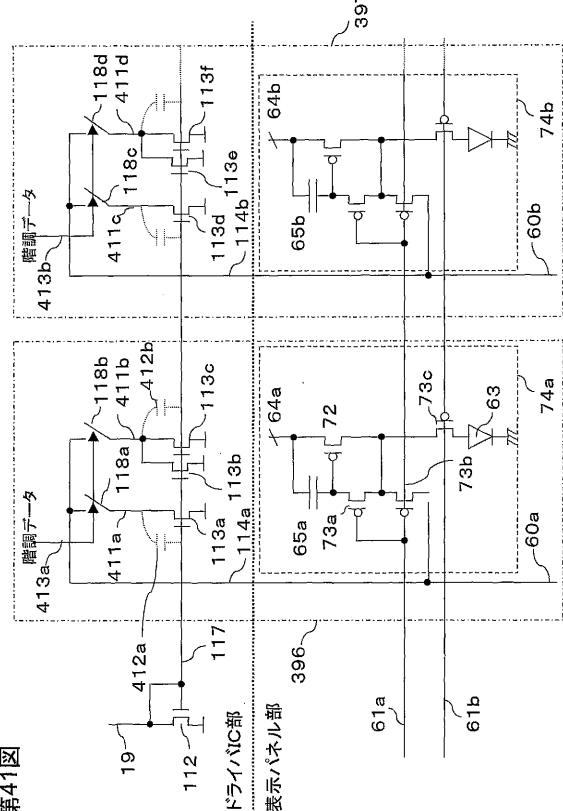

ドライバIC17の出力段回路と、表示パネル部の画素74を接続したときの回路を図41に示す。この例では、列396、397に対応する2列のみを示す。なお、ここでは階調データが2ビットのときで説明を行うが、一般にN(N:自然数)ビットでも同様な説明が可能である。

#### 【0120】

図39の期間398では、階調データ413aは黒データを、413bでは白データを出力する。これにより、スイッチ118a及び118bは非導通状態となり、スイッチ118cと118dは導通状態となる。これにより、トランジスタ113のドレイン電圧は、節点411aと411bではドライバIC17のグランド電位に近い値(図40に示した電圧Vdb)となり、411c及び411dは、ソース信号線60bの電位Vwと等しくなる。ソース信号線60aの電位はVbとなる。画素74aに黒を書きこんでいるとすると、スイッチ118a及び118bが非導通状態であるため、ソース信号線60aはドライバIC17と切り離された状態にある。

20

#### 【0121】

一方画素74a内部においては、ゲート信号線61の操作によりトランジスタ73a及び73bは導通状態、73cは非導通状態となる。また、ソース信号線60aにつながる他の全ての画素はゲート信号線の操作により、ソース信号線から電気的に切り離された状態にある。ソース信号線60aは、電源64とトランジスタ72を介して接続された状態にある。トランジスタ72を介して電流が流れる経路がないため、トランジスタ72は電流が流れなくなるように、ドレイン電位を上昇させる。従って電圧Vbはほぼ電源電圧64に等しくなる。

30

#### 【0122】

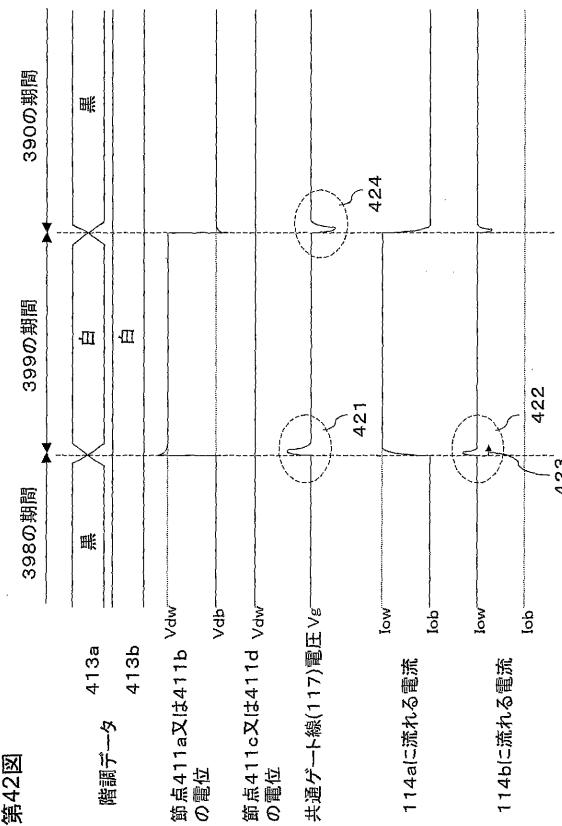

この状態で階調データ413aのみを図42に示すように、白信号とする。するとスイッチ118a及び118bは導通状態となる。その瞬間、411a及び411bの電位は、ソース信号線60aの電位まで上昇する。この変化がトランジスタ113に寄生する容量412を介して、容量結合として共通ゲート信号線117に伝播する。その結果、図42に示すように、ゲート電圧がハザード的に上昇する期間421が発生する。全ての出力トランジスタ113は同一の共通ゲート信号線117の電圧に基づいて、電流を出力しているため、ゲート信号線のハザードは全てのドライバ出力18に影響する。

40

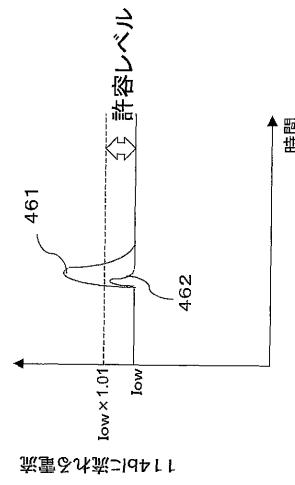

#### 【0123】

データ413bは変化しないため、スイッチ118c及び118dの状態は変化しないが、ゲート信号線117の電圧が期間421のように変化したため、422に示すように、出力電流が変化する。所定の電流値IoWと異なる電流値が outputされる期間423が一水平走査期間に比べ長いと、ゲート信号線61によりソース信号線から画素回路が切り離されるときに規定される画素74に書き込まれる電流値がIoWに比べ大きくなるため、所定輝度に比べ、高い輝度がEL素子63より出力される。

#### 【0124】

50

同様に、階調データ413aが白から黒に変化した場合においても、スイッチ118a及び118bが閉じたとたんに、411a及び411bの電圧がVdwからVdbに変化し、この変化が、浮遊容量412を通じて共通ゲート信号線117に伝播することで、期間424のようにゲート電圧が低下し、スイッチ118bに流れる電流も低下する。これにより、同様にこのハザードが一水平走査期間以上にわたって発生すると、ハザードがでた期間に対応した画素は所定輝度に比べ低い輝度で表示を行う。

#### 【0125】

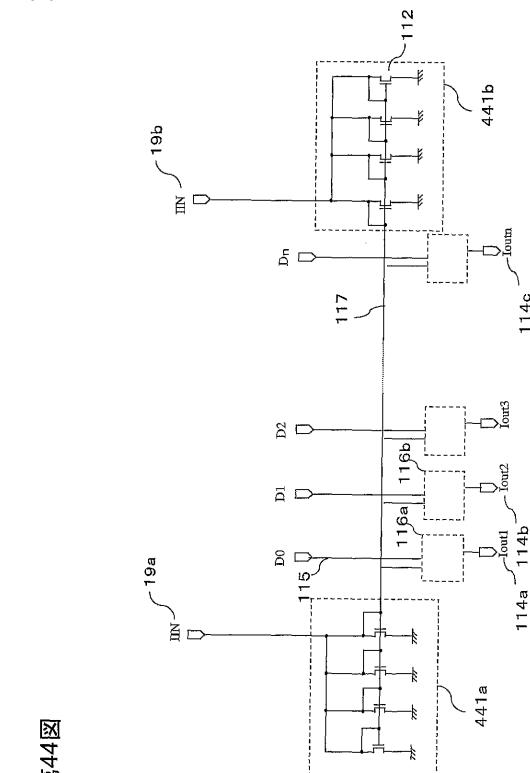

そこで、本実施の形態では、輝線及び黒線をなくす方法として、大きく3つの方法について説明を行う。第1の方法としては、ゲート信号線117のゆれを抑制する方法。第2の方法としては、黒表示時におけるトランジスタ113のドレイン電位を高くして、ゲート信号線117のゆれの原因となるデータ変化時の電圧変化量を小さくする。第3の方法としては、ゲート信号線117の電圧の変化に対し、出力電流の変化を小さくし、ゲート信号線がゆれても、出力に影響しないようにする。以下、順に図面を交えながら3つの方法について説明を行う。

#### 【0126】

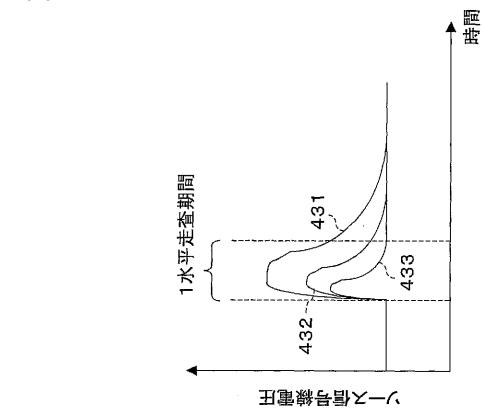

図44は第1の方法の実施例である。図34と比較して、ゲート信号線117の電位を定める分配用ミラートランジスタ112の数を増やしたことが特徴である。これによりミラー比が変わるために、基準電流入力19の電流値も対応して増加させる。

#### 【0127】

図42のゲート電位のハザード部421を拡大したものを図43に示す。図34の構成においては、曲線431に示すようなゲート電圧の変化があり、1水平走査期間内では、所定の電圧に戻らない。ここでミラートランジスタ112の数を増加させると、曲線432、更に数を増やすと曲線433に示される変化を生じる。433に示す曲線であれば、水平走査期間内に所定電圧値に戻るため、画素には所定の電流値が書き込まれる。

#### 【0128】

なお、分配用ミラートランジスタ112の数を増やす代わりに、トランジスタのサイズを大きくしても同様に実現可能である。

#### 【0129】

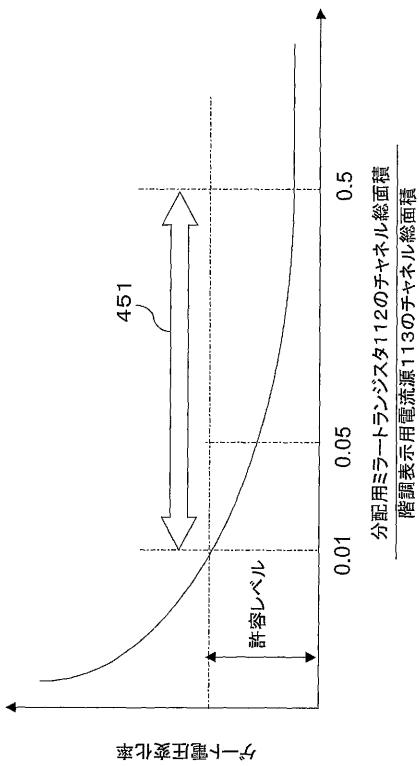

分配用ミラートランジスタ112のサイズは図45の範囲451に示される大きさが望ましい。すなわち、ゲート電圧の変化率が、許容レベル以下であるような範囲である。この許容レベルは出力電流の変化量が1%以内であれば、他の行との輝度差が視認できないことを考慮し、出力電流の変化が1%以内に収まる電圧変動レベルを示している。（図46において曲線462で示される）電圧の揺れはトランジスタ113の浮遊容量を介して発生するため、階調表示用電流源のチャネル面積及び個数により決まる。従って分配用ミラートランジスタ112の総サイズはトランジスタ113の総サイズに対する比により定義される。

#### 【0130】

今回、さまざまな分配用トランジスタサイズ及び個数を作成し、評価を行った結果、（分配用ミラートランジスタ112のチャネル総面積）/（階調表示用電流源113のチャネル総面積）とゲート変化率の関係が図45に示す曲線であらわされた。

#### 【0131】

このグラフによると分配用ミラートランジスタ112のチャネル総面積が階調表示用電流源113のチャネル総面積の1%以上、好ましくは5%以上あれば、輝線および黒線はなくなる。一方、50%以上ではゲート電圧の変化率が低減しなくなる。従って50%以上では、どのような面積で設計しても、ハザードに影響しない。チップ面積を小さく造る観点から、50%以下にすることが好ましい。

#### 【0132】

よって、分配用ミラートランジスタ112のチャネル総面積は、範囲451のように階調表示用電流源113のチャネル総面積の1%以上50%以下、好ましくは5%以上50%以下になるように、設計するようにすればよい。

10

20

30

40

50

**【0133】**

なお、チップ間での、基準電流対ある階調出力電流の比のばらつきをおさえるためには、分配用ミラートランジスタ112と、階調表示用電流源113は同一サイズ、同一レイアウトで設計することが望ましい。トランジスタの数の増減により上記の面積比を実現することがよい。これにより、複数のドライバIC17を並べて使用する表示装置でも、基準電流に対する出力電流の比のチップ間ばらつきが小さくなるためブロックむらのない表示が実現できる。

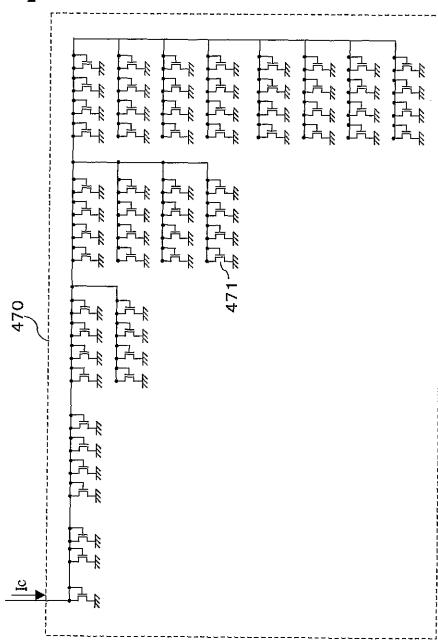

**【0134】**

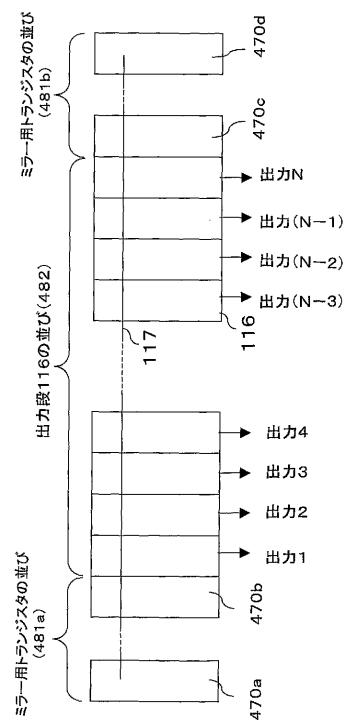

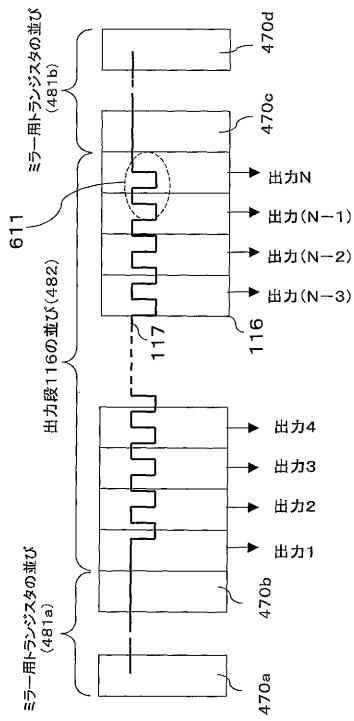

例えれば63階調表示で160出力のドライバICの場合、1出力にはトランジスタ113を63個並べる。この63個並んだ出力段を、出力数である160個用意する。更に、出力段を160出力の両端に9個ずつ用意し、トランジスタのドレインゲート間を短絡することで、63個のミラートランジスタ112を形成する。このときの回路を図47に示す。このようにすれば、ほぼ同一レイアウト、同一チャネルサイズで、カレントミラーを形成できるため、チップ間のミラー比のばらつきを小さくできる。この場合の分配用ミラートランジスタのチャネル総面積と、階調表示用電流源のチャネル総面積の比は、 $18 / 160 = 0.11$ であり、輝線黒線は発生しない。一般にN出力の場合におけるミラー用トランジスタの並びと出力段の並び116は図48に示すように配置することが望ましい。ミラー用トランジスタの並び481a及び481bの数はそれぞれ等しく、出力段の数に応じて図45に示す範囲で配置する。

**【0135】**

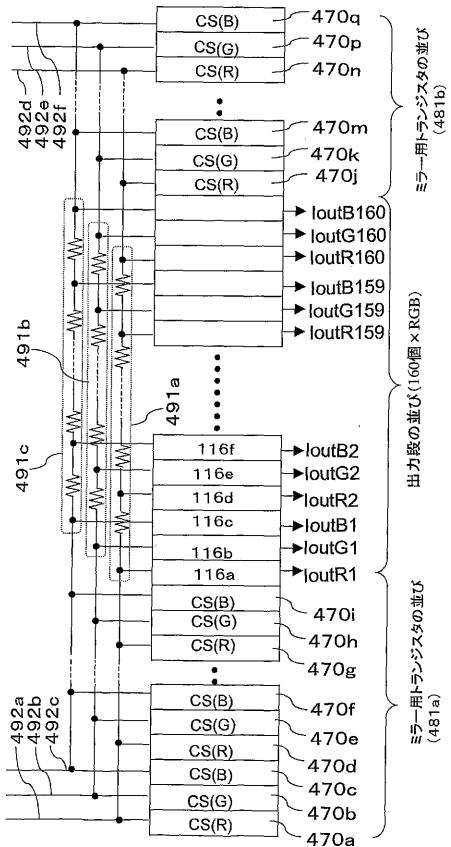

図48ではモノクロの場合で説明したが、カラーパネルにおいては図49に示すような配置とする。この例では3原色として、赤、緑、青を用い、それぞれが独立に1階調あたりの電流を設定できるように、共通ゲート線、分配用ミラートランジスタを色ごとに独立に用意した。赤色表示用の回路はRを、緑色表示用の回路はGを青色表示用の回路はBを末尾に記した。共通ゲート信号線は赤表示用として491a、緑表示用として491b、青表示用として491cを用意した。これにより、階調表示用電流源113のゲート電位が色ごとに異なる値に設定できるため、使用的表示素子の電流・輝度特性及び色度座標値に応じてホワイトバランスや、最大輝度の調整が可能となる。基準電流は色ごとに左右2ヶ所、合計6ヶ所から入力される。基準電流生成部を3倍用意する。

**【0136】**

同一色で複数の分配用ミラートランジスタ群470からなる、ミラー用トランジスタの並び481では図49に示すように色ごとに固めて配置するのではなく、赤緑青の3原色を1組とし、その組数を増やすようにした。これにより、トランジスタが広範囲にわたり配置されるため、局所的なしきい値電圧の変化の影響を小さくすることが可能となる。また、色ごとにミラー比がずれるという心配もなくなる。図49ではCS(R)で示したもののが赤色表示用の分配用ミラートランジスタ群470で、CS(G)で示したもののが緑色表示用の分配用ミラートランジスタ群470で、CS(B)で示したもののが青色表示用の分配用ミラートランジスタ群470である。

**【0137】**

次に第2の方法について説明を行う。

**【0138】**

第2の方法は、共通ゲート線117の電圧を揺らす原因となる、階調表示用電流源113のドレン電圧の変化量を小さくする方法である。変化量を小さくすることで、容量結合により変化するゲート線117の変化量も小さくすることが可能になる。

**【0139】**

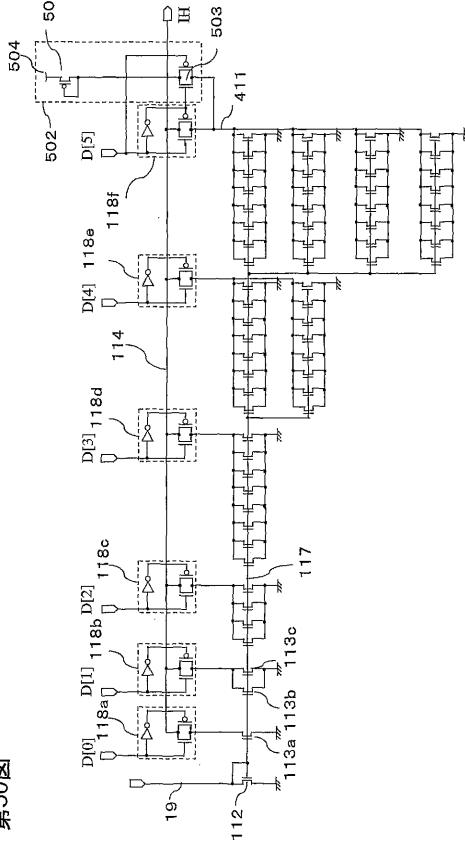

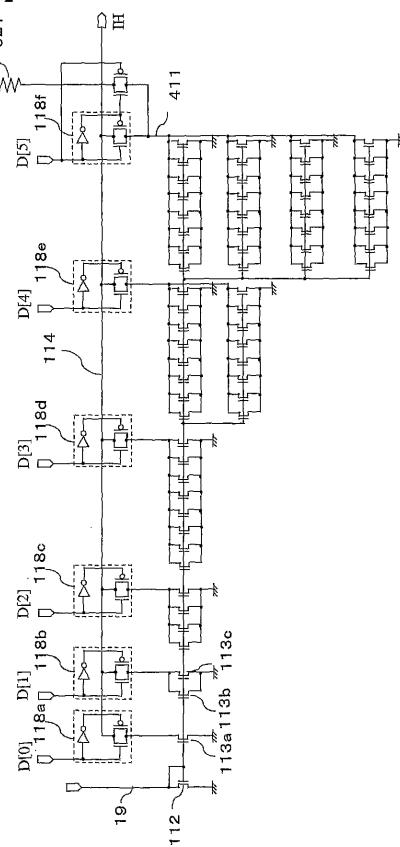

図50に1出力分のデジタルアナログ変換部116及び分配用トランジスタの回路を示す。この例では階調データを6ビットとしている。502に示す回路を附加したことが本発明の特徴である。スイッチ118fと503を相補的に動作させることにより節点411はソース信号線もしくはトランジスタ501に接続され、階調表示用電流源113に常に電流を流すことが可能となる。

10

20

30

40

50

**【0140】**

従来の方法では、スイッチ118が非導通状態となると、トランジスタ113に流れる電流経路がなくなるにもかかわらず、トランジスタ113は電流を流そうとするため、ドレイン電圧を低くする。その結果、最も低くなる場合で、ドライバICのグランド電位まで411の電位が低下する。

**【0141】**

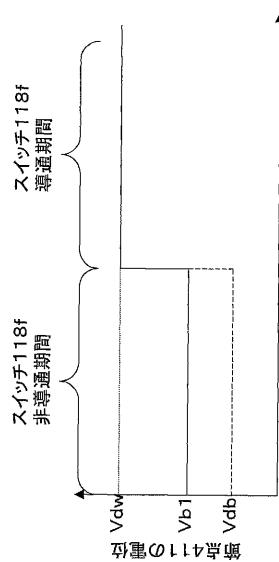

一方本実施の形態においては、スイッチ118が非導通であっても、スイッチ503が導通状態となり、トランジスタ501を介して、電源504から113に電流が供給される。このときの411の電圧はトランジスタ501のチャネルサイズ及び電源504の電圧によるが、図51に示すようなVb1の電位まで上昇させることが可能である（従来の電位はVdb。ここでVb1 > Vdb）。これにより、スイッチ118のオンオフによる節点411の電位変化が小さくなることで、浮遊容量を介して変動する共通ゲート線117の電位変動を小さくすることが可能となる。

10

**【0142】**

ダイオード接続されたトランジスタ501のゲート電圧 - ドレイン電流特性を画素74に用いられる駆動トランジスタ72と揃えるか、よりゲート電位が低くなるような、トランジスタサイズとするとより効果がある。

**【0143】**

画素74にソースドライバIC17から電流を供給する場合、ゲート信号線61の操作により、画素の等価回路は図24に示されるようになる。ドライバIC17のドレイン電極にはソース信号線60、駆動トランジスタ72を介して電源64に接続される。このとき502で示した部分の回路と画素74の回路は蓄積容量をのぞき同一構成であることがわかる。（ゲート電圧を保持する必要がないため502の回路では蓄積容量は不要）従って電源501と64、トランジスタ72と501が同一特性で形成できれば、節点411の電位はほぼ等しくなることが期待できる。

20

**【0144】**

ソース信号線の電位は、階調に応じて変化し、最低電圧は、白（最高階調）のときで、最高電圧は階調1の場合で、階調に応じて、その間の電位で変化する。従って、スイッチ118fが非導通、503が導通状態にあるときの411の電位は、上記ソース信号線の電圧変化の範囲内にすれば、スイッチ118fが導通状態になったときの電位変化が小さくできる。501のトランジスタサイズは、図50の場合は階調32に対応する電流が501に流れたときに、411の電圧がソース信号線の変化範囲内にあるように設計する。

30

**【0145】**

図50では6ビット階調データのときの最上位ビットに付加回路502を接続した場合で説明を行ったが、一般に、付加回路502にあるトランジスタ501のトランジスタサイズは、付加回路502が接続された信号線に接続されたトランジスタ数に一致する階調（ここでKとおく）の電流が、501に流れたときに、トランジスタ501のゲート電圧が、ソース信号線60の取りうる電圧可変範囲に入るよう設計すれば、一般にJビット階調データの階調Kを出力するトランジスタのドレイン電圧の変化を抑えることが可能となる。

40

**【0146】**

従って図50の場合でも、D[0]からD[4]の信号線にも502のような回路を用いてよい。

**【0147】**

また、図52に示すように、トランジスタ501の代わりに抵抗素子521を用いても同様に実現可能である。他にも、スイッチ118fが非導通状態になっても、トランジスタ113に常に電流が流れるような回路構成ができれば、抵抗、トランジスタ以外の素子を用いてもかまわない。

**【0148】**

次に第3の方法について説明を行う。

50

**【0149】**

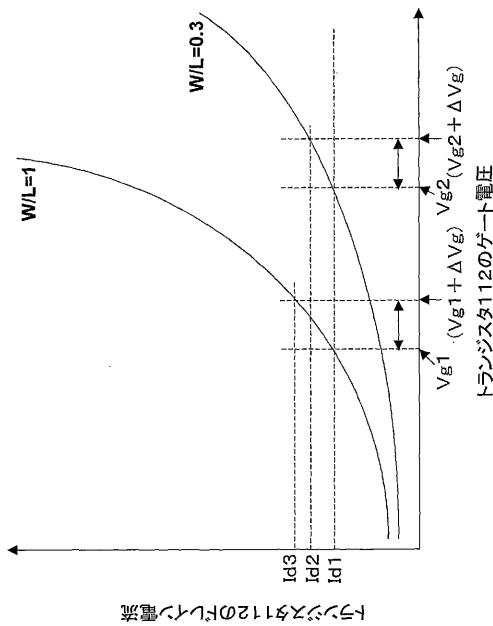

基準電流を分配するためのミラートランジスタ112のチャネル幅／チャネル長（以下W／Lとする）を変化させると、ドレイン電流対ゲート電圧の特性が変化する。図53に示すように、W／Lを小さくすると、ゲート電圧の変化に対するドレイン電流の変化が小さくなる。

**【0150】**

今基準電流19の値をI<sub>d1</sub>とする。このとき、階調データの変化点で、共通ゲート線117（ここでは、トランジスタ112のゲート電圧に一致）がV<sub>g</sub>変化したとする。ドレイン電流の変化は図53に示すように、W／L=1に比べ、W／L=0.3のほうが小さくなる。トランジスタ32とトランジスタ33はカレントミラーを形成しているため、このドレイン電流の変化は、トランジスタ113の出力電流の変化に対応する。ドレイン電流の変化が小さければ、たとえ共通ゲート信号線117の電圧が変化しても、輝線黒線がでないようにできる。10

**【0151】**

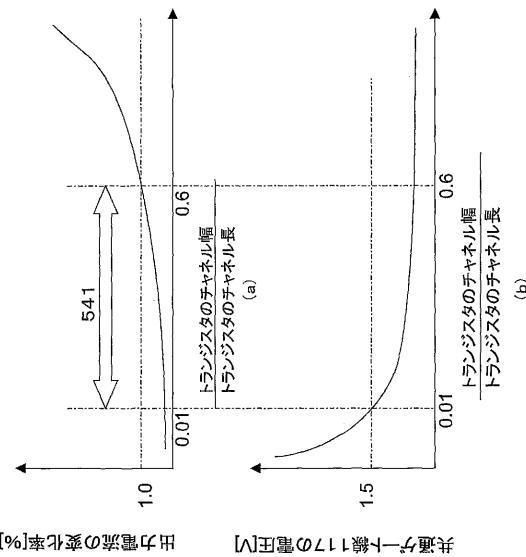

そこで、図54(a)(b)にそれぞれ示すように、W／Lの違いに対する出力電流の変化率を測定した。（チャネル面積は一定）その結果、W／Lが0.6以下のときゲート線117の電圧揺れに対し、出力電流変化が1%以内に収まる。電流変化量が1%以内であれば、輝度変化を視認できない。よって、図39の394に示す部分と、他の部分における白の輝度差がわからなくなるため、輝線が見えない。黒線についても同様である。

**【0152】**

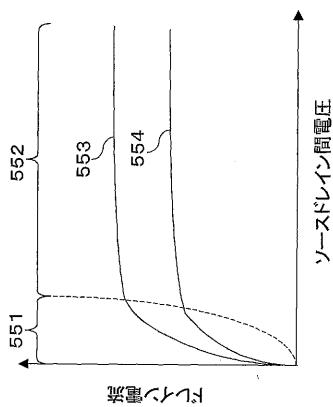

W／Lの値を小さくすると、同一ドレイン電流を得るために必要なゲート電圧が上昇する。W／Lが0.01以下になると、ゲート電圧は1.5Vを超える。（1つの階調表示用電流源113に流れる電流が10nA～100nA程度のとき）階調表示用電流源113のドレイン電流対ソースドレイン間電圧の特性を図55の曲線553、554に示す。出力の負荷によらず、一定の電流を出力するためには点線部より右の範囲552で示した、飽和領域でトランジスタ113を動作させる必要がある。飽和領域でトランジスタ113を動作させるためには、トランジスタ113のゲート電圧より高いドレイン電圧が必要である。従って、図54(a)(b)においてW／Lが0.01以下となり、ゲート電圧が1.5V以上必要となると、ドレイン電圧も1.5V必要である。動作マージンを見越すと2V程度必要。さらにソース信号線電圧（=113のドレイン電圧）は階調信号により異なり、白～黒レベルに必要な振幅は2V程度必要である。その他、配線抵抗、スイッチのオン抵抗による電圧ロスがある。合計すると必要な電圧は5V程度となる。ドライバIC17としては、この程度の電圧レベルの耐圧が必要である。20

**【0153】**

一方でドライバIC17のチップサイズを小さくするために、微細プロセスを用いる。携帯電話向けでは、更にドライバIC17内部にメモリやコントローラの機能を設ける。微細プロセスを用いるため、耐圧も大きくすることができず、現実的には5V程度までしか上げられない。

**【0154】**

このような観点から、W／Lの下限値はICの耐圧によりきめられ、0.01よりは小さくすることができない。W／Lのとりうる範囲は図54の範囲541で示すように0.01以上0.6以下が望ましい。この範囲であれば、輝線黒線が発生せず、また微細ルールによるチップサイズの削減効果が期待できる。40

**【0155】**

なお、以上の第1から第3までの方法を組み合わせて実施してもよい。組み合わせることにより、動作マージンが広くなる効果があるし、より、輝線黒線がでにくくなる。

**【0156】**

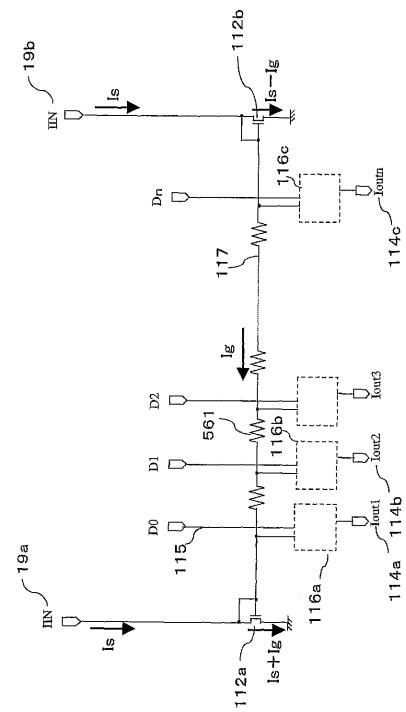

図34に示したように、ウエハー内のトランジスタのしきい値電圧の変化を補償するために、両側から基準電流19を供給する実施例において、図21(a)に示したように、トランジスタのしきい値電圧の変化があるとすると、共通ゲート信号線117の電位は右50

側が高く、左側が低くなることになる。すると図56に示すように、共通ゲート線117に電流 $I_g$ が流れる。左右に配置された分配用ミラートランジスタ112のドレイン電流は変化し、ミラートランジスタ112aでは共通ゲートから流れ込む電流が増加するため $I_s + I_g$ となり、ミラートランジスタ112bでは $I_s - I_g$ となる。

#### 【0157】

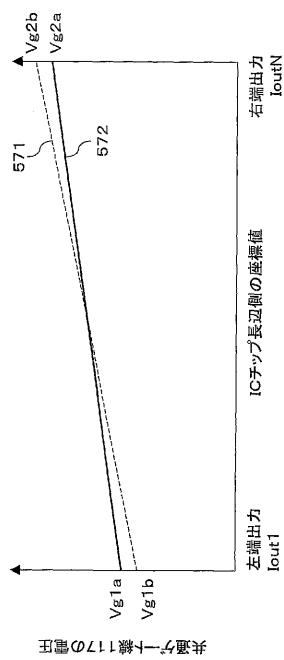

ドレイン電流が変化したことから、共通ゲート線117は変化し、ドレイン電流が増加した左側の電圧は上昇し、ドレイン電流が減少した右側の電圧は低下する。その結果、共通ゲート線117の電圧は図57に示すように、 $I_g$ が流れない場合(直線571)に比べ、直線572に示したように電圧が変化する。

#### 【0158】

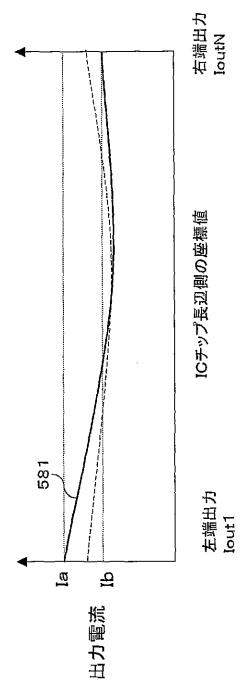

これにより両端の出力電流が図58の曲線581に示すように、左端では、ゲート電圧が上がった分増加し $I_a$ となり、右端では、ゲート電圧が低下した分減少し $I_b$ となる。両端で $I_a - I_b$ の差が発生する。この状態でドライバIC17を複数個用いて表示を行うとドライバIC17の境目で $I_a - I_b$ の分に応じて境目が見える恐れがある。

#### 【0159】

基準電流19をより正確に出力段に分配するために、出力段116と分配用ミラートランジスタ群470は図48に示すように配置することが好ましい。6ビット出力をを行うドライバの場合の出力段116の構成を図35、分配用ミラートランジスタ群470の構成を図47に示す(6ビット以外でも、トランジスタ113の数にあわせてトランジスタ471を配置すれば同様な効果が得られる)。

#### 【0160】

図35と図47で異なる点は、63個のn型トランジスタのドレインにスイッチ118があるかどうかの違いがあるのみである。そこで、トランジスタ113及び471の並びを同一としてレイアウトを行うと、よりミラー比を正確にすることが可能である。基準電流と出力電流のミラー比を変更する場合、分配用ミラートランジスタ群470を配置する個数を変化させればよい。

#### 【0161】

例えば、両側に1つずつ合計2個の場合、基準電流値に対する63階調表示時の出力電流の比は1となる。両側に5個ずつ合計10個設けた場合の比は1/5となる。なお、左右の出力電流値をそろえる必要があるため、図48のミラー用トランジスタの並び481aを構成する分配用ミラートランジスタ群470の数と、ミラー用トランジスタの並び481bを構成する分配用ミラートランジスタ群470の数を同一にする必要がある。

#### 【0162】

また、図45の範囲内に(分配用ミラートランジスタ112のチャネル総面積)/(階調表示用電流源113のチャネル総面積)の値がなるようにする方法も、同様に、ミラー用トランジスタの並び481を構成する分配用ミラートランジスタ群470の数を調整することで実現可能である。

#### 【0163】

図48ではモノクロの場合で説明したが、カラーパネルにおいては図49に示すような配置とする。この例では3原色として、赤、緑、青を用い、それぞれが独立に1階調あたりの電流を設定できるように、共通ゲート線、分配用ミラートランジスタを色ごとに独立に用意した。赤色表示用の回路はRを、緑色表示用の回路はGを青色表示用の回路はBを末尾に記した。共通ゲート信号線は赤表示用として491a、緑表示用として491b、青表示用として491cを用意した。

#### 【0164】

これにより、階調表示用電流源113のゲート電位が色ごとに異なる値に設定できるため、使用する表示素子の電流-輝度特性及び色度座標値に応じてホワイトバランスや、最大輝度の調整が可能となる。基準電流は色ごとに左右2ヶ所、合計6ヶ所から入力される。基準電流生成部を3倍用意する。

#### 【0165】

10

20

30

40

50

同一色で複数の分配用ミラートランジスタ群470からなる、ミラー用トランジスタの並び481では図49に示すように色ごとに固めて配置するのではなく、赤緑青の3原色を1組とし、その組数を増やすようにした。これにより、トランジスタが広範囲にわたり配置されるため、局所的なしきい値電圧の変化の影響を小さくすることが可能となる。また、色ごとにミラービギンがずれるという心配もなくなる。図49ではCS(R)で示したもののが赤色表示用の分配用ミラートランジスタ群490で、CS(G)で示したもののが緑色表示用の分配用ミラートランジスタ群490で、CS(B)で示したもののが青色表示用の分配用ミラートランジスタ群490である。

#### 【0166】

さて、左右の出力電流値がずれないようにするためには、図56に示した共通ゲート線117に流れる電流 $I_g$ を小さくする。分配用ミラートランジスタ112のドレイン電流が左右で1%以内のずれであれば、出力のずれも1%以内となるため、ドライバIC17の境目は認識されない。つまり $I_s$ に対し $(I_s + I_g) - (I_s - I_g) = 2 \times I_g$ の値が1%以下となればよい。

#### 【0167】

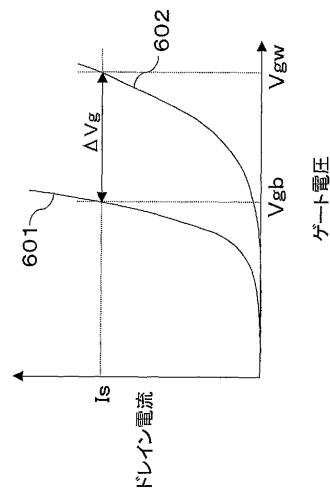

オームの法則から $I_g$ は共通ゲート線117の両端の電位差を抵抗値で割った値になる。 $I_g$ は小さいほどよいため、最大値を規定する必要がある。 $I_g$ が最大となるのは、共通ゲート線117の両端の電位差が最大となるときで、左右の分配用ミラートランジスタ112のうち一方が、しきい値低移動度高、他方がしきい値高移動度低となる場合である。このとき、一方はゲート電圧最小、他方が最大となることから、差が大きくなる。図60に分配用ミラートランジスタ112のゲート電圧ドレイン電流特性を示す。ここで601はしきい値低移動度高の特性を示し、602はしきい値高移動度低の特性を示している。図56に示すように、601、602の特性を持つトランジスタに基準電流 $I_s$ を流すと、601のゲート電圧が $V_{gb}$ 、602のゲート電圧が $V_{gw}$ となる。すると、共通ゲート線117にかかる電圧は $V_g = (V_{gb} - V_{gw})$ となる。ここから $I_g = (V_{gb} - V_{gw}) / R_g$ となる。ここで $R_g$ は共通ゲート線117の総抵抗値である。

#### 【0168】

ドライバIC17の境目が見えない条件は $(2 \times I_g) = (I_s \times 0.01)$ であったから結局、共通ゲート線117の総抵抗値 $R_g$ と基準電流 $I_s$ は次のような関係である必要がある。 $(V_{gb} - V_{gw}) / R_g = (I_s \times 0.005)$

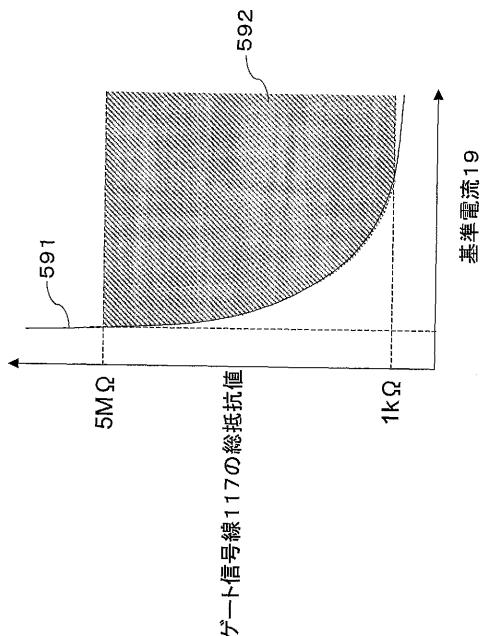

ここで、 $V_{gb}$ 、 $V_{gw}$ は使用プロセスにより決まっているためあらかじめわかるため、基準電流を決めると、必要なゲート抵抗値が決まる。図59に基準電流19に対し、とりうるゲート信号線117の総抵抗値の範囲を示す。ドライバIC17の境目をなくすには範囲592内にある必要がある。

#### 【0169】

総抵抗値の最小値は $(V_{gb} - V_{gw}) / R_g = (I_s \times 0.005)$ を満たすか、1kΩの大きいほうとなる。共通ゲート線のコンタクトの抵抗、配線抵抗などから1kΩ以下にすることが難しいためである。(実現できたとしても回路規模が大きくなるためコストがかさむ)

また抵抗値が大きいほど $I_g$ が小さくなるため左右の違いがなくなるが、5MΩが最大である。実現可能な最大シート抵抗値の関係からゲート信号線117の抵抗値を5MΩ以上にしようとすると、図61に示すように、共通ゲート線117の配線の一部を折り曲げてなる折り曲げ部611を設けることで長くする必要がでてくる。またゲート線の抵抗値が高くなると、ノイズに弱くなる。ノイズに弱くなる上に、配線長を確保するため、図61のように配線するとアンテナのようになりノイズを拾いやすくなる。ゲート信号線117の電位がノイズにより変動すると、出力電流に影響を及ぼす。従って図61のように配線をまげなくてもすむ最大の抵抗値である5MΩが最大値となる。

#### 【0170】

以上のことから、基準電流19に対し、ゲート線117の抵抗値は592の領域にすることでチップ両端の電流の差によるチップの境目のむらを防止することが可能である。な

10

20

30

40

50

お、上記の各数値は実質上の値であって、例えば数%など、所定の誤差があつてもよい。

**【0171】**

以上のような出力段の構成とすることで、ドライバIC17の左右端の電流ばらつきが小さくなり、チップの境目に発生するブロックむらがない表示が可能である。

**【0172】**

以上のように方法においては、基準電流を生成するための基準電流発生部のうち抵抗素子301がドライバIC17外付けの部品で形成されていた。実装部品点数の削減及びアレー上配線引き回しを簡略化するためには、抵抗素子の内蔵化が必要である。本実施の形態では次にこの抵抗素子301を内蔵した場合においても、基準電流19のばらつきが小さくなる構成を考案した。

10

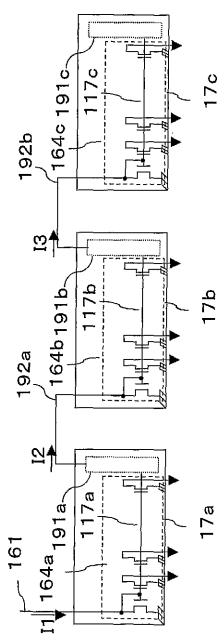

**【0173】**

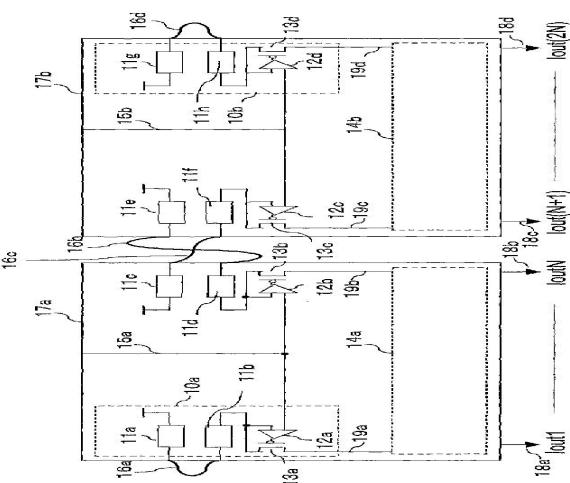

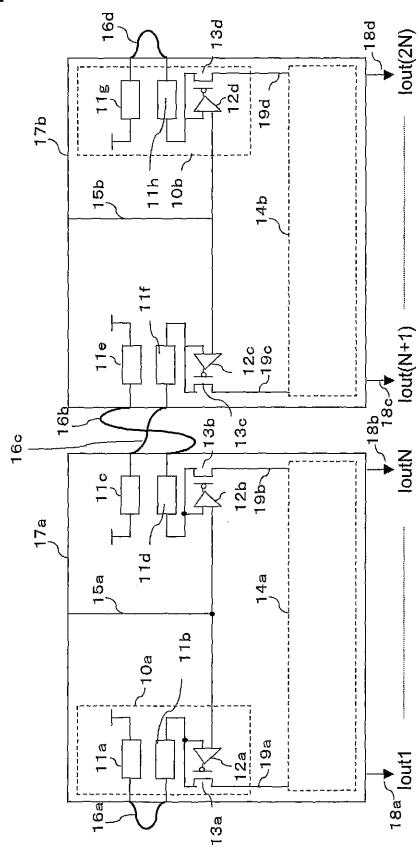

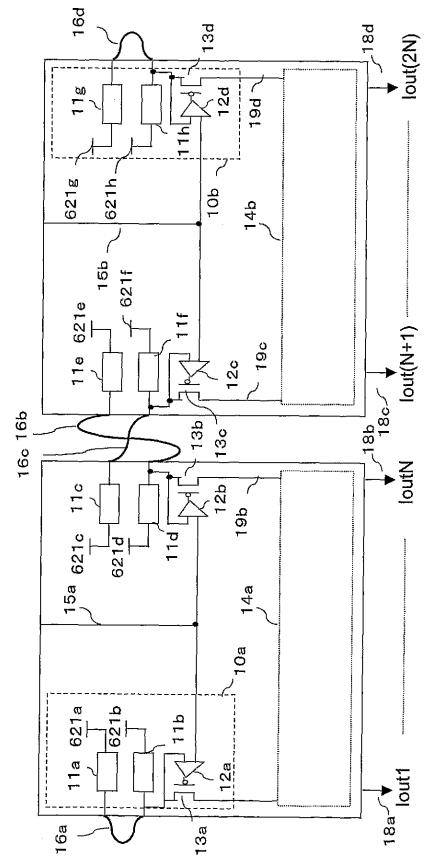

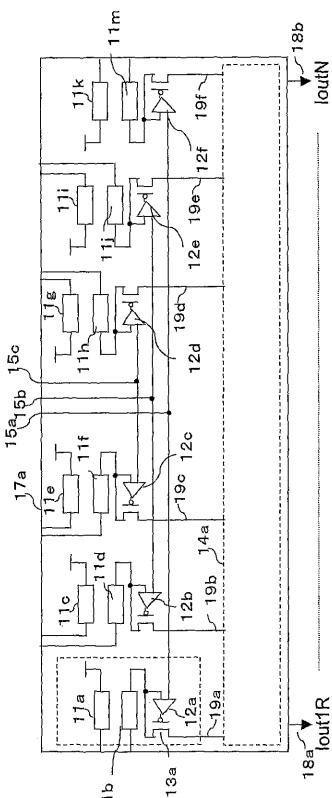

この基準電流19のばらつきを少なくするために図1及び図62の構成を考案した。

**【0174】**

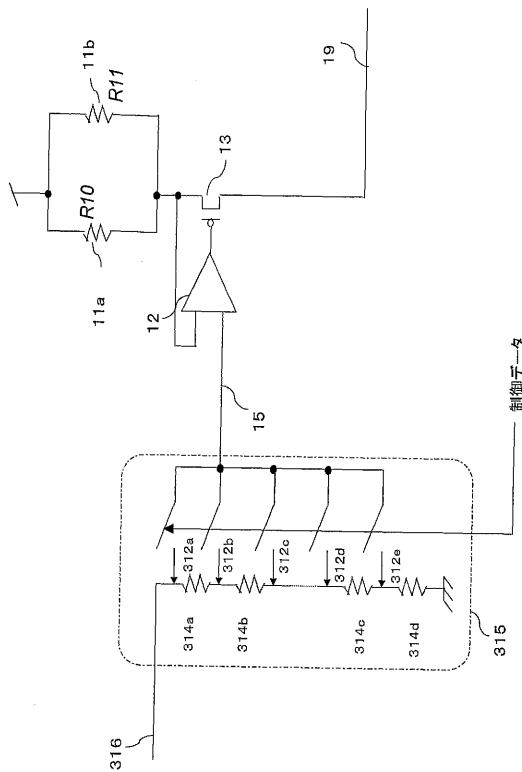

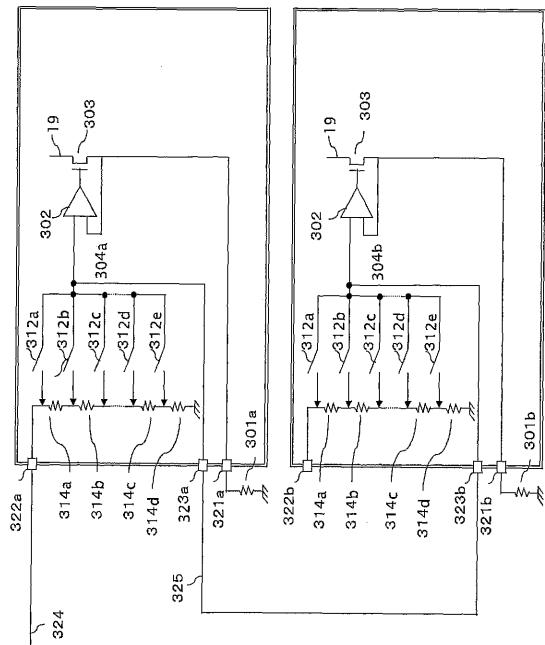

第1の方法である図1について説明を行う。

**【0175】**

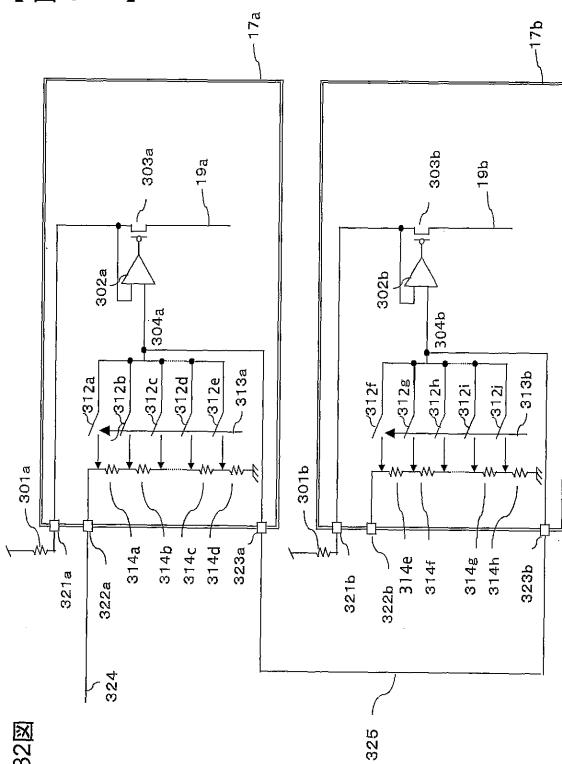

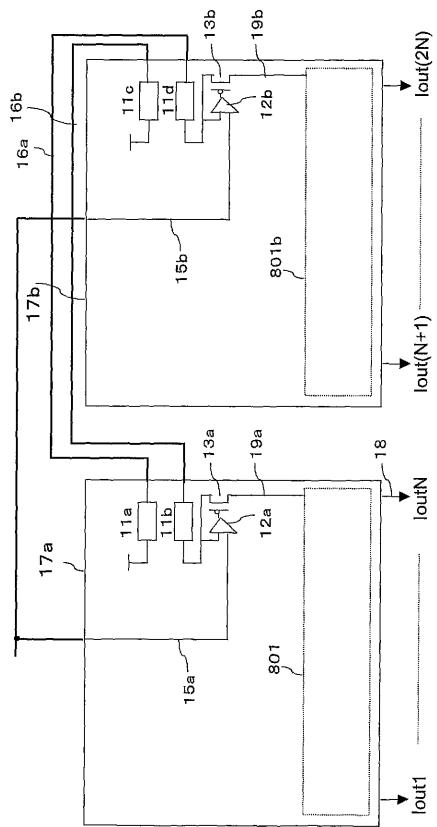

図1の方法では、チップ内の2つの基準電流源を形成するために、図30で示した構成要素が2つずつ、チップ内に内蔵されている。また、抵抗素子301については2パートに分割し、全部で4パート存在(11a～11d)する。抵抗値の精度の問題から通常抵抗は外付けとすることが多いが、本実施の形態では内蔵する構成とした。外付け部品を少なくすることが可能であり、コスト及び実装面積が削減可能である。

20

**【0176】**

ドライバIC17を1つ使いにした場合、もしくは複数チップ使用の場合において、他のドライバICと隣接しない場合、電流源は図1の10aに示すような構成とする。

**【0177】**

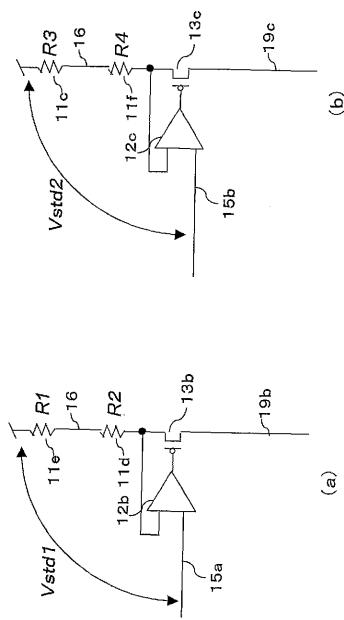

2つのドライバIC17が接する場合における電流源の構成は図1の中央部に示した2つの電流源の構成のようになる。外部配線16により2つ必要な抵抗素子11のうち一方を異なるIC17から取り込むようにした。ドライバ17aの右端の定電流源回路を図66(a)に、ドライバ17bの左端の定電流源回路を図66(b)に示す。図66の各構成要素についての番号は図1と対応している。

**【0178】**

30

抵抗素子11は隣り合うIC17の両方から1つずつ持ってきている。図66(a)では抵抗素子11dはIC17aから、抵抗素子11eはIC17bのものである。また図66(b)では抵抗素子11cはIC17aから、抵抗素子11fはIC17bのものである。抵抗素子11の抵抗値を図66のように定義すると、I19bに流れる電流(I19b)は $V_{std1} / (R1 + R2)$ であり、I19cに流れる電流(I19c)は $V_{std2} / (R3 + R4)$ となる。15a及び15bの基準電圧信号線はIC17外部にて接続するので、 $V_{std1} = V_{std2}$ となる。従ってI19bとI19cが異なる要因になるのは、4つの抵抗素子11のばらつきによる。IC17内部で抵抗を作成するには、拡散抵抗とポリシリコン抵抗がある。よりばらつきの少ない抵抗を作成するには、ポリシリコン抵抗を用いるほうがよく、チップ間及びロット間を含めるとおよそ5%程度のばらつきである。しかし、同一チップ内に近接して2つの抵抗素子11を作成した場合、抵抗値のばらつきは0.1%程度となる。よって図1及び図66の各図に示す抵抗素子11cと11d間(R3とR2)、11eと11f間(R1とR4)のばらつきは0.1%に抑えられる。従って、I19bとI19c間でのばらつきの要因となる(R1 + R2)と(R3 + R4)間のばらつきは、0.1の2乗平均である0.14%となる。

40

**【0179】**

このように、電流値を決める抵抗を隣接する2つのチップから相互にとることで、チップ間及びロット間ばらつきとは無関係となり、5%程度ばらつきのあるポリシリコン抵抗でも実用可能となる。よって、内蔵抵抗、ブロックむらのできないドライバIC17が実現可能である。

50

**【0180】**

なお、以上の説明においてはモノクロ出力のドライバとして説明を行ったが、マルチカラー出力のドライバにも適用可能である。表示色数倍同一回路を用意すればよい。例えば、赤、緑、青の3色出力の場合、図65に示すように3つの同一回路を同一IC内にいれ、それぞれを赤用、緑用、青用として使用すればよい。

**【0181】**

また、図1では2個のドライバIC17で説明を行ったが、一般にM(M:任意の自然数)個のドライバICを並べた場合にも同様に実施が可能である。その例を図64に示す。

**【0182】**

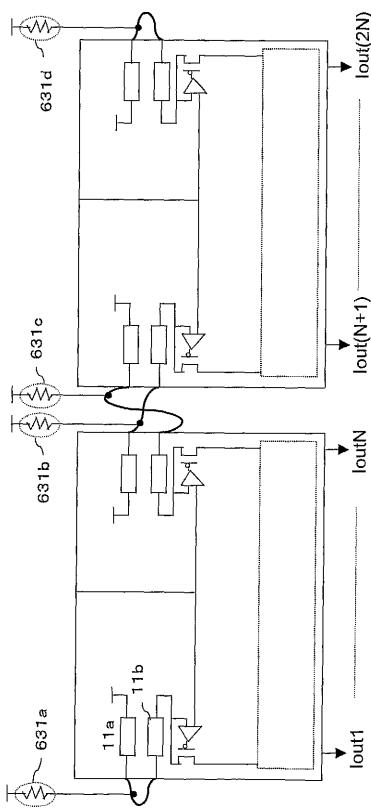

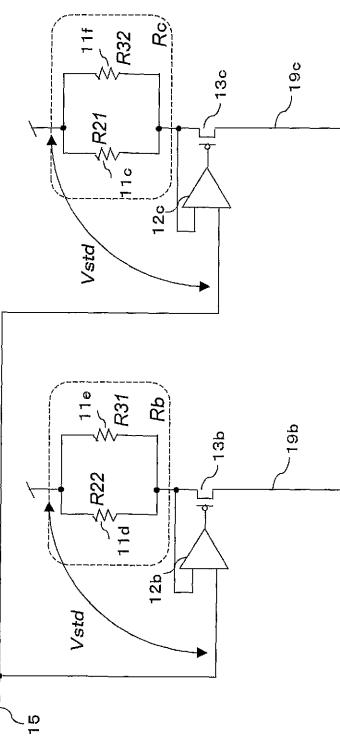

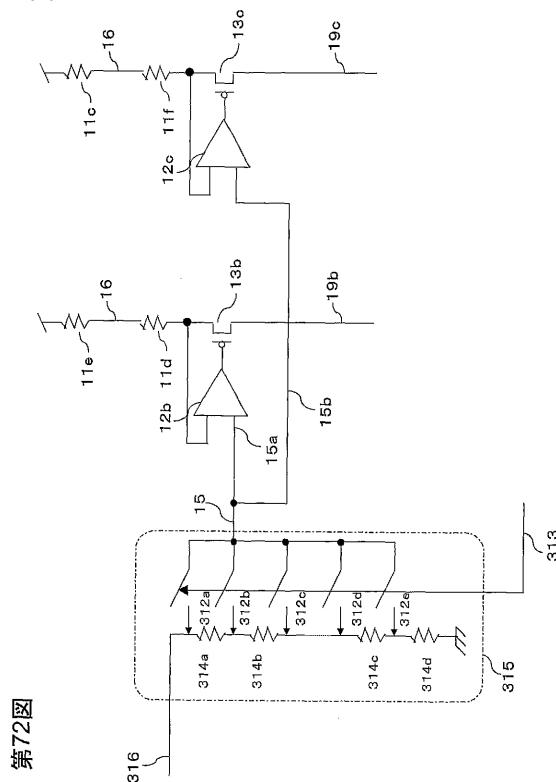

図62は第2の実施の形態である。

10

**【0183】**

図1と異なる点は、抵抗素子11の接続方法である。4つの抵抗素子とも、外部接続端と逆の端子は電源と接続されている。

**【0184】**

基準電流生成部の回路図を図67に示す。なおここでは基準電圧信号線15はICチップ外で接続している。

**【0185】**

基準電流19のばらつきは、第1の実施例と同様に、抵抗値のばらつきにより決まる。抵抗R21とR22、抵抗R31とR32は同一チップ内にあるため、この間のばらつきは0.1%程度となる。従って、R22とR31の合成抵抗Rbと、R21とR32の合成抵抗Rc間でのばらつきは0.14%のばらつきとなる。

20

**【0186】**

この場合にもチップ間ばらつきの影響が見かけ上なくなるため、ポリシリコン抵抗で作成しても、ブロックむらのない表示が可能となる。

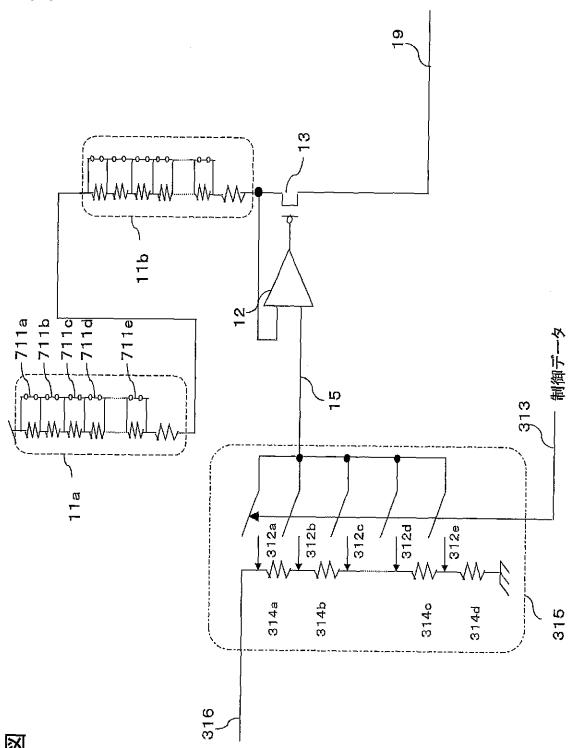

**【0187】**

以上の説明において、基準電圧信号線15は外部よりアナログ電圧を入力した例で説明を行ったが、図70に示すようにして、アナログ電圧をプログラマブルに変更できるようにもよい。図70では、制御データ313に応じて、スイッチ312のオンオフ状態が変化し、基準電圧15の値が変化する。制御データ313に応じて、基準電流19の値、ひいては表示パネルの輝度を変えることが可能である。第1の実施例では図70のように、第2の実施例では図73に示すような構成となる。

30

**【0188】**

なお図1のように複数のドライバIC17を用いる場合、図70の回路をIC17ごとに個別に動作させてもよいが、図72に示すように複数の基準電流発生回路に供給する基準電圧信号線15を1つの電圧調整部315により制御してもよい。このようにIC17内部において、基準電流19を調整できるような構成にすることで、例えば図14に示すような携帯情報端末において、電池のもちをよくするために、ボタン142が操作されたときには、通常の輝度で表示を行い、ある一定時間がたった後には輝度を低下させるということが可能となる。

40

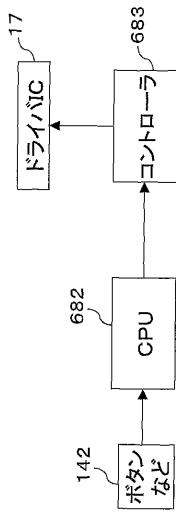

**【0189】**

具体的には、図14及び図68に示すようにボタン142において入力が発生したときにCPU682に情報転送する。CPUはコントローラ683に信号を送り、コントローラ683により、ドライバIC17内部の制御データを書き換え、基準電圧15をあらかじめ定められたデフォルト値に設定する。一方、CPU682にて、ある一定時間をカウントし、一定時間後にはコントローラ683に再び信号を送り、コントローラ683はドライバIC17の制御データを書き換え、基準電圧信号線15の電圧を低下させることで、輝度を下げる。極端には、基準電流がほとんど流れないような基準電圧15の設定が電圧調整部315により行えるようにしてもよい。

**【0190】**

50

これにより、ドライバIC17内部に流れる電流値を下げることが可能であり、さらに、表示素子に流れる電流も下げることで、消費電力を下げることも可能となる。

#### 【0191】

他にも、図14のボタンなど142に代わって、光センサを用いれば、表示パネルの周辺環境（周りの明るさ）により、輝度を調整できるという利点がある。このドライバIC17が主に用いられる有機発光素子では、暗闇の中では視認性が高く、明るい外光下（例えば太陽光下）では視認性が低い。

#### 【0192】

そこで、光センサにより、周囲の照度が高いときには、CPU、コントローラの制御により、ドライバIC17の基準電流をたくさん流すようにし、周囲の照度が低いときには、ドライバIC17の基準電流を少なくするようにするということが可能である。周囲の環境に応じて最も見やすい輝度で表示するという制御が可能になるという利点がある。

10

#### 【0193】

このドライバIC17が複数用いられ、図1に示す第1の形態を実施する場合には、図70のような構成となる。ここでは、定電流源回路は1つしか記載していないが、複数の定電流源回路を1つの電圧調節部315で制御してもよい。例えば図72のような構成が考えられる。

#### 【0194】

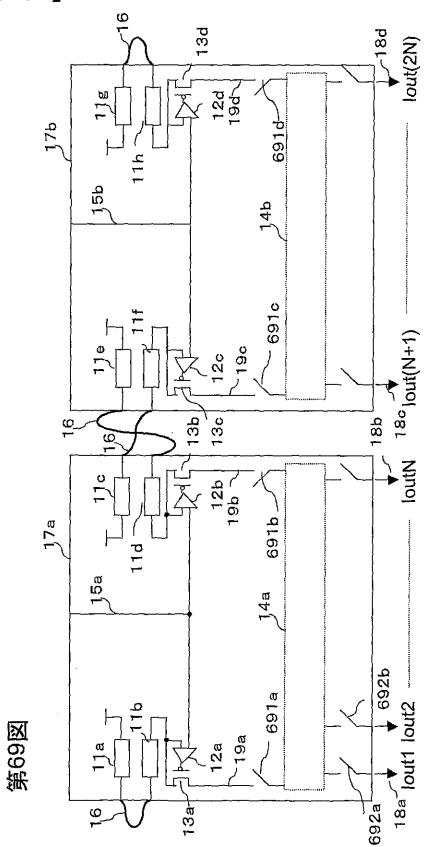

低電力化への方法としては、図69のような構成をとることも可能である。図1の構成に対し、基準電流線19にスイッチ691を設けた。スイッチ691を非導通状態とすることで、基準電流を0にすることができ、IC17内部で消費する電力を削減することが可能である。

20

#### 【0195】

温度特性を持つ表示素子を表示部に用いた表示装置においては、温度特性を補償するための機能が必要となる。例えば、温度によって電流・輝度特性が変化し、同一電流入力に対し、輝度が変化するということが発生する素子もある。

#### 【0196】

輝度を一定に保つには、温度に応じて基準電流を変化させればよい。例えば温度補償素子631を抵抗11に並列に接続する方法がある。これにより、合成抵抗値は温度により変化し、基準電流19も変化する。この変化を温度特性を補償するような方向に変化させることで、温度変化に強い表示装置を実現することが可能となる。

30

#### 【0197】

図1の構成において温度特性補償を行う場合には図63のように温度補償素子631をつければよい。温度によって、基準電流を決める抵抗値が変化するため温度特性補償が可能となる。

#### 【0198】

ポリシリコン抵抗のはらつきはチップ内近接ではおよそ0.1%、チップ間、ロット間では5%程度である。この範囲であれば、本発明を用いることでロックむらをなくすことができる。しかし、プロセス上の問題等ではらつきが大きくなることもある。はらつきが大きくなると不良品となり、ドライバIC17の歩留まりが低下する。そこで、図71に示すように、抵抗素子11の抵抗値を調整できるような機能を設けることで、はらつき範囲からはずれたドライバICも、はらつき範囲内の値にすることで、良品とすることが可能となる。

40

#### 【0199】

具体的には抵抗素子11を複数のパートに分割する。複数のパートのうちのいくつかのパートは配線ショート（711）する。抵抗素子11aの抵抗値を大きくするには、短絡した配線711をFIB等でパターンカットすればよい。抵抗値をどれだけ大きくするかは、パターンカットする配線711の数で調整可能である。抵抗素子11bについても同様であり、本発明で用いたすべての抵抗素子11に適応可能である。これにより抵抗素子11の抵抗値を調整することで、はらつきを低下させ良品判定となるようにする。

50

**【0200】**

このようにより多くのドライバICを良品とできる構成とすることで、歩留まりが上昇し、低コストかつむらの少ない表示装置が実現可能となる。

**【0201】**

ここまででは画素74の用いられるトランジスタがp型のトランジスタの時の例を示したが、n型トランジスタを用いても同様に実現可能である。

**【0202】**

図74はカレントミラー型の画素構成をn型トランジスタで形成したときの1画素分の回路である。電流が流れる向きが逆になり、それに伴って電源電圧が変わる。従ってソース信号線745を流れる電流はソースドライバIC17から画素74に向かって流れる必要がある。出力段14の構成は図75に示すように、ドライバIC外部に電流を吐き出すようp型トランジスタのカレントミラー構成となる。基準電流の向きも同様に反転し、図1の構成に対し、図76の構成に変える必要がある。

10

**【0203】**

複数のドライバIC17の基準電圧制御部を同時に制御する方法も同様に図77に示すようになる。

**【0204】**

このように画素に用いるトランジスタがp、n両方において適用することが可能である。

**【0205】**

20

電流出力段14が図34で示す構成である場合、先に述べたとおり、図21(a)に示すようなしきい値特性を持つウエハーを使用したときに、出力電流が端子ごとに傾斜を持って出力される。図34の構成により、左右端の電流値はほぼ同一にすることが可能であるが、全出力端子にわたってそろえることは難しい。一般的には隣接間の出力ばらつきが1%以内であれば、表示に支障はなく、閾値特性の傾きがその範囲内であればよい。しかし、IC作成時のプロセスばらつき、製膜装置の状態等によっては傾きが急になることがあり、その場合、該当するICは不良品となり歩留まりが悪くなることが考えられる。

**【0206】**

そこで、本実施の形態ではさらに、図21(a)のような傾きによらず、均一な表示が実現できる構成を実現し、さらにそのICを複数個使ったときのプロックむらを防ぐ方法を考案した。

30

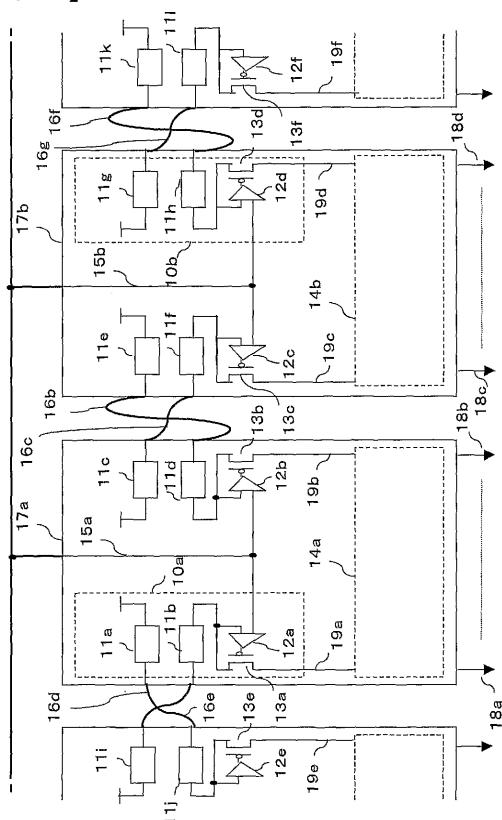

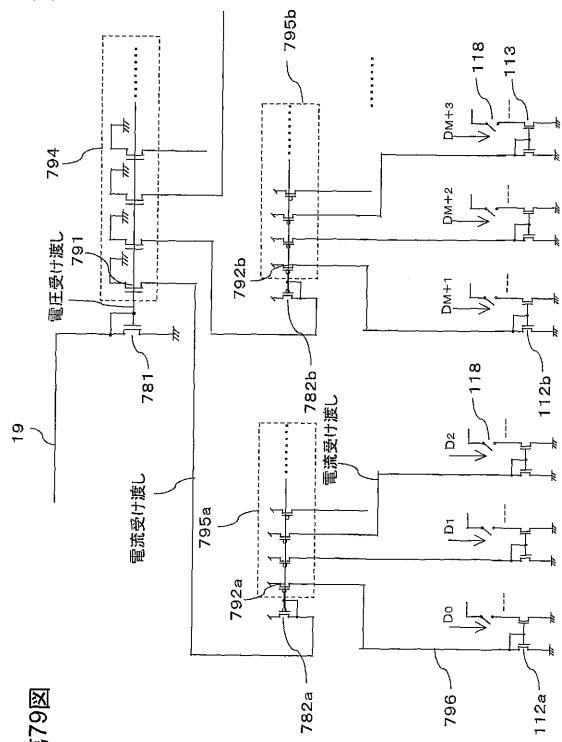

**【0207】**

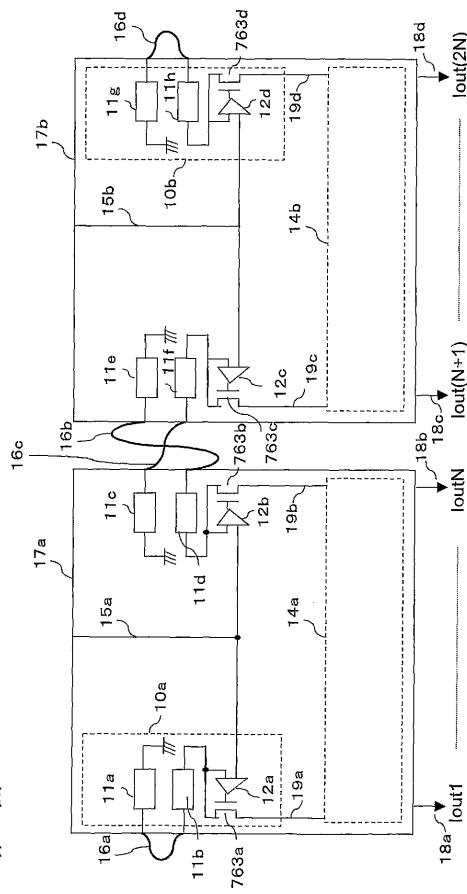

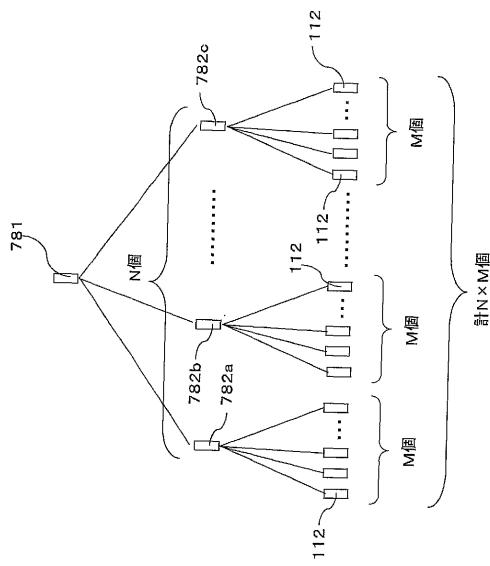

均一表示を実現するために、基準電流を各出力に分配し、出力ごとに設けられた基準電流を元に、階調表示を行うこととする。電流分配を行う方法を図78及び79に、出力段の構成を図35に示す。

**【0208】**

各出力への基準電流の分配は3段階により行われる。1つの基準電流源781(親電流源)からまずN個の電流源782(子電流源)に電流を分配する。さらに子電流源782の電流をM個の電流源112(孫電流源)に分配する。これにより、1つの基準電流から、 $M \times N$ 個の電流を分配することが可能となった。

40

**【0209】**

この図では1つの電流源を $M \times N$ 個に分配するにあたり、2回に分けて電流分配を行っている。分配回数に付いては1回でも、3回以上であっても実現可能であるが、2から3回で分割を行うことが最もよい。

**【0210】**

各分配手段における電流ばらつきが、分配回数の増加に伴い出力電流のばらつきとして影響する。各分配段階でのばらつきの2乗平均として、出力に影響を及ぼすため、隣接出力のばらつきを1%以内に収めるためには、分配回数を少なくするか、1回の分配でのばらつきを小さくする必要がある。1回の分配でのばらつきを小さくするには一般的にはトランジスタサイズを大きくするしかなく、トランジスタサイズの増大はチップ面積の増大

50

にもつながり、IC17のチップが大きくなるという欠点ができる。また分配回数がおおいとそれだけトランジスタの数も多くなるため、これもまたチップ面積が増大する。それゆえ分配回数は多くても3回程度である。

#### 【0211】

一方、1回ですべての出力に分配する場合は出力数が30以内のものでは有効であるが、100出力を超えるドライバICでは適用しにくい。1回の分配で出力数だけ電流を分配するには少なくとも、出力数+1個のトランジスタからなるカレントミラーを形成する必要がある。カレントミラーは一般的にはミラーを形成するトランジスタ同士を近接配置することで、近接ではトランジスタ特性がほぼ等しいということを利用して、ミラーを行っている。出力数+1個のカレントミラーを形成すると、ミラー元のトランジスタと、ミラー先のトランジスタの配置が遠くなるものが発生するため、正確にミラーすることがしにくくなる。1回に分配する個数を多くても30個程度にすることが望ましい。10

#### 【0212】

図79に電流分配の方法を示す。基準電流19に対し、親電流源781とトランジスタ791によりN個の電流に分配する。このとき、トランジスタの組794と781は近接に配置し、N個の電流にばらつきがないようにする。次に、分配された各電流をさらにM個の電流に分配する。このときもトランジスタ782と795は近接に配置し、特性ばらつきによる電流ばらつきを抑える。出力ごとに基準電流を分配できた。この分配した電流796（孫基準電流）を元に図35に示すような構成で、入力階調データに応じた電流を出力線114から出力する。（この例では6ビットのデータに応じて、適切な電流量を出力する）なおM及びNは任意の自然数でよいが、特に2以上30以下が好ましい。20

#### 【0213】

ドライバIC17は、長方形型に作成されることが多く、その長辺側に出力パットを並べることが多い。電流出力段14の各出力はチップ面積の有効利用から、当該出力パッドの近くに置くことが多い。そのため、M×N出力のドライバICでは、1番目の出力段と、M×N番目の出力段は10~25mm程度はなれていることが多い。1つの基準電流を、M×N個に分配する際には、各出力までの引きまわしも重要になる。図79の構成では、カレントミラーを形成し、電圧の形で情報を受け渡す部分については、近接に配置し、電流の形で情報が受け渡されるところで、出力段の近傍まで引きまわしを行うようにした。このようにすることで、10~25mm離れた出力へもばらつき少なく分配が可能となる。30

#### 【0214】

さて、以上のような出力電流段を持つドライバIC17を複数個用いて表示を行う場合に、ブロックむらを防ぐには、各ICに同一量の基準電流を供給する必要がある。

#### 【0215】

図80に2つのドライバIC17間で基準電流19のばらつきが小さくなる構成を示す。

#### 【0216】

基準電流値を決める基準電圧15は外部で接続することで、同一電圧が供給される。次に抵抗素子11は第1及び第2の実施の形態と同様に2つに分割し、1つを隣接IC、1つを当該ICに内蔵されたものを用いることで、11b、11cの合成抵抗値と11a、11dの合成抵抗値間のばらつきは、内蔵ポリシリコン抵抗のチップ内ばらつきである0.1%の2乗平均である0.14%程度である。基準電流は0.14%のばらつきですむ。これは実施例1及び2と同等である。これにより図78、79の構成を用いたドライバIC19においてもチップ境目に発生するブロックむらのない表示が可能となった。40

#### 【0217】

以上の説明においてはモノクロ出力のドライバとして説明を行ったが、マルチカラー出力のドライバにも適用可能である。表示色数倍同一回路を用意すればよい。例えば、赤、緑、青の3色出力の場合、図65に示すように3つの同一回路を同一IC内にいれ、それぞれを赤用、緑用、青用として使用すればよい。

10

20

30

40

50

**【0218】**

以上の説明において、トランジスタはMOSトランジスタとしたが、MISトランジスタやバイポーラトランジスタでも同様に適用可能である。

**【0219】**

またトランジスタは結晶シリコン、低温ポリシリコン、高温ポリシリコン、アモルファスシリコン、ガリウム砒素化合物などどの材質でも本発明を適用可能である。

**【0220】**

表示素子として、有機発光素子で説明を行ったが、無機エレクトロルミネッセンス素子、発光ダイオードなど電流と輝度が比例関係となる表示素子ならどのような素子を用いても実施可能である。

10

**【0221】**

なお、上記の実施の形態において、ドライバICであるIC17aおよび17bは、本発明の駆動用半導体回路に相当する。また、基準電流生成部10a、10bおよび同等の部分は、本発明の基準電流生成手段に相当する。また、電流出力段14a、14bは本発明に関連する発明の駆動電流出力機構に相当する。

**【0222】**

また、共通ゲート線117は本発明の共通ゲート線に相当し、分配用ミラートランジスタ112a、112bは本発明の電流分配手段に相当する。また、デジタル・アナログ変換部116a～116cは本発明の駆動電流生成手段に相当する。また、電源51およびそれと同等の部分は本発明に関連する発明の所定の電源に相当し、基準電圧信号線15から入力される基準電圧信号は、本発明に関連する発明の基準電圧信号に相当する。

20

**【0223】**

また、抵抗素子11c～11fは本発明に関連する第1の発明の直列接続された複数の抵抗素子に相当し、特に図1に示す抵抗素子11c、11dが本発明に関連する第1の発明の、隣り合う一対の駆動用半導体回路の一方のチップ上に形成された抵抗素子である場合、同図に示す抵抗素子11e、11fは隣り合う一対の駆動用半導体回路の他方のチップ上に形成された抵抗素子に対応することになる。

**【0224】**

また、図78に示す基準電流の分配の構成は、本発明に関連する発明の駆動電流出力機構の多段構造に相当する。

30

**【0225】****【発明の効果】**

以上のように本発明によれば、同一ドライバIC内での左右端の出力電流値をそろえ、さらに出力電流値を決める基準電流をチップ内、チップ間とも同一電流にすることができるため、複数のドライバICを用いて表示を行う表示装置においてドライバICのばらつきに起因するドライバIC境界で発生する輝度むらをなくすことが可能となった。これにより電流出力型ドライバICのカスケード接続が実現できる。また、本発明の基準電流生成部を用いることで従来外付け部品を用いていた抵抗を内蔵することが可能となり、実装部品点数の削減及びアレー配線の簡略化が可能となった。

40

**【図面の簡単な説明】**

【図1】本発明の実施の形態におけるドライバICの基準電流発生部と複数個使用したときの外部接続結線を示した図である。

【図2】有機発光素子の構造を示した図である。

【図3】有機層が複数存在する有機発光素子の構造を示した図である。

【図4】有機発光素子の電流-電圧-輝度特性を示した図である。

【図5】有機発光素子を用いたパッシブマトリクス型表示装置を示した図である。

【図6】有機発光素子を用いたアクティブマトリクス型表示装置における1画素分の画素回路の1例を示した図である。

【図7】カレントコピア構成の画素回路を用いたアクティブマトリクス型表示装置の回路を示した図である。

50

【図 8】カレントミラー構成の画素回路を用いたアクティブマトリクス型表示装置の回路を示した図である。

【図 9】カレントコピア回路の動作を示した図である。

【図 10】カレントミラー回路の動作を示した図である。

【図 11】電流出力型ドライバの各出力へ電流を出力するための回路を示した図である。

【図 12】本発明の実施の形態を用いた表示装置として、テレビに適用した場合を示した図である。

【図 13】本発明の実施の形態を用いた表示装置として、デジタルカメラに適用した場合を示した図である。

【図 14】本発明の実施の形態を用いた表示装置として、携帯情報端末に適用した場合を示した図である。 10

【図 15】複数のソースドライバ IC を用いた表示パネルを示した図である。

【図 16】従来の方法における複数のドライバ IC をカスケード接続する方法を示した図である。

【図 17】図 16 における基準電流分配部の回路例を示した図である。

【図 18】図 16 における基準電流分配部の回路と、基準電流を発生する回路の例を示した図である。

【図 19】従来の方法における複数のドライバ IC をカスケード接続する方法を示した図である。

【図 20】図 19 における電流受け渡し部 191 の回路例を示した図である。 20

【図 21】同一 IC チップ内におけるトランジスタのしきい値電圧の分布とそれに伴う出力電流値の分配用ミラー-トランジスタからの距離依存性を示した図である。

【図 22】図 21 (b) の出力特性をもつドライバ IC を 2 つ接続したときの各出力電流値を示した図である。

【図 23】本発明の実施の形態におけるドライバ IC の回路ブロック図である。

【図 24】カレントコピア構成の画素回路において、画素にソース信号線電流が流れるとときの等価回路を示した図である。

【図 25】1 出力端子における電流出力とプリチャージ電圧印加部及び切り替えスイッチの関係を示した図である。

【図 26】発光色による輝度対電流特性の違いを示した図である。 30

【図 27】表示色ごとに異なるプリチャージ電圧を出力することができる回路ブロックを示した図である。

【図 28】1 ドット分の映像信号ごとにプリチャージを行うかどうか外部から選択できるようにしたときのドライバ IC のブロック図である。

【図 29】階調データとプリチャージ判定信号の関係を示した図である。

【図 30】基準電流生成部の回路を示した図である。

【図 31】制御データにより、生成される基準電流を変更できる基準電流生成部を示した図である。

【図 32】複数のドライバ IC に同一の基準電流を供給するための回路と外部配線を示した図である。 40

【図 33】基準電流をキー入力もしくは外光により変更するための回路ブロック図である。

【図 34】本発明の実施の形態における左右端の電流値が等しくなる電流出力段を示した図である。

【図 35】映像信号データから対応する電流を出力するためのデジタルアナログ変換部を示した図である。

【図 36】図 34 の出力段を用いた場合の、IC チップ内トランジスタしきい値電圧の変化と、それに対応する出力電流特性を示した図である。

【図 37】図 31、図 34 の回路構成を利用したドライバ IC の回路図である。

【図 38】図 35 の階調表示用電流源 113 のトランジスタサイズと出力電流ばらつきの 50

関係を示した図である。

【図39】輝線及び黒線が発生する場所を示すための表示画像例を示した図である。

【図40】図39に示す画像表示を行った場合における396、397の列のソース信号線電圧波形を示した図である。

【図41】ドライバICの出力段と画素回路の接続を示した図である。

【図42】入力データに対応したドライバICの出力段の各部の電圧、電流波形を示した図である。

【図43】図42の421部におけるハザードが、ミラートランジスタの数により変化することを示した図である。

【図44】基準電流源を分配するためのミラートランジスタの数を増やした場合の図である。10

【図45】分配用ミラートランジスタのチャネル総面積 / 階調表示用電流源のチャネル総面積とゲート電圧変化率の関係を示した図である。

【図46】図42における421のハザードの許容レベルを示した図である。

【図47】分配用ミラートランジスタ群を示した図である。

【図48】分配用ミラートランジスタ及び電流出力段のレイアウト概略図である。

【図49】マルチカラー表示を行うドライバICにおける分配用ミラートランジスタ及び電流出力段のレイアウト概略図である。

【図50】節点411の電位変化量を抑えるために、トランジスタを付加した場合のデジタルアナログ変換部を示した図である。20

【図51】スイッチ118fと節点411の電位の関係を示した図である。

【図52】図50において、トランジスタの代わりに抵抗を用いた場合の図である。

【図53】ゲートとドレイン電極が接続されたトランジスタ32の、ゲート電圧対ドレイン電流の関係を示した図である。

【図54】トランジスタのチャネル幅 / チャネル長に対する出力電流の変化率ならびにゲート信号線電圧の関係を示した図である。

【図55】トランジスタ113のソースドレイン間電圧対ドレイン電流の関係を示した図である。

【図56】本発明の実施の形態における電流出力段の構成において、基準電流、ゲート電流、分配用ミラートランジスタの流れる電流の関係を示した図である。30

【図57】共通ゲート線に電流が流れる場合と流れない場合での各出力での共通ゲート線の電圧分布を示した図である。

【図58】共通ゲート信号線に電流が流れた場合の各端子の出力電流の分布を示した図である。

【図59】基準電流値に対して、ゲート信号線に必要な抵抗値の範囲を示した図である。

【図60】分配用ミラートランジスタのゲート電圧とドレイン電流特性を示した図である。40

【図61】ゲート信号線の抵抗を高くするための配線方法の例を示した図である。

【図62】第2の実施の形態において抵抗素子を並列接続してカスケード接続を行う例を示した図である。

【図63】図1の構成に、温度補償機能を設ける場合を示した図である。

【図64】2つ以上のドライバICをカスケード接続する場合の外部結線を示した図である。

【図65】マルチカラー出力を行うドライバICにおける基準電流発生部を示した図である。

【図66】図1における、2つの異なるICにした図である。

【図67】複数のドライバICを用いて第2の実施の形態を実施した場合の2つの基準電流生成部において、2つの基準電流のばらつきが少なくなる回路例を示した図である。

【図68】図14に示した携帯情報端末のボタン入力により、本発明のドライバICの制御を行うためのブロック図である。50

【図69】本発明の第1の実施の形態から、基準電流を切斷することで、消費電力を低減させる方法を示した図である。

【図70】図31に示した定電流源回路において、異なるドライバICの抵抗も用いた場合を示した図である。

【図71】図70に示した定電流回路において、抵抗の値をトリミング操作により変更できるようにした機能を持たせたときの回路を示した図である。

【図72】複数のドライバICを用いた場合における、電子ボリュームを用いた基準電流発生部の接続例を示した図である。

【図73】第2の実施の形態における1つの基準電流生成部の回路を示した図である。

【図74】n型トランジスタを用いた場合のカレントコピアを用いた画素回路を示した図である。10

【図75】画素回路にn型トランジスタを用いた場合のドライバICの出力段を示した図である。

【図76】n型トランジスタを画素に適用した表示装置における、本発明のドライバICの概略回路を示した図である。

【図77】n型トランジスタを画素回路に適用した場合の基準電流発生部と、基準電流を発生する元となる電圧を複数のドライバICに分配する方法を示した図である。

【図78】基準電流を各出力に分配する概念を示した図である。

【図79】基準電流を分配する回路を示した図である。

【図80】基準電流を各出力に分配する実施の形態における、複数のドライバICの接続関係を示した図である。20

【図81】1水平走査期間内でのプリチャージ電圧を行う期間と階調データに基づく電流を出力する期間の関係を示した図である。

【符号の説明】

- 10 基準電流生成部

- 11 抵抗素子

- 12 演算増幅器

- 13 トランジスタ

- 14 電流出力段

- 15 基準電圧信号線

- 16 外部配線

- 17 ドライバIC

- 18 電流出力

- 19 基準電流線

30

【図1】

第1圖

【 図 2 】

第2回

【図3】

第三圖

【図4】

第4回

【図5】

第5図

【図6】

第6図

【図7】

第7図

【図8】

第8図

【図9】

第9図

【図10】

第10図

【図11】

第11図

【図12】

第12図

【図13】

第13図

【図14】

第14図

【図15】

第15図

【図16】

第16図

【図17】

第17図

【図18】

第18図

【図19】

【図 2 1】

【図 2 2】

第21図

【図 2 3】

第22図

【図 2 4】

第24図

第23図

【 図 2 5 】

第25回

【図27】

第27回

【図26】

第26圖

【図28】

第28回

【図29】

【図30】

第30図

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図41】

【図42】

【図43】

【図44】

【図45】

第45図

【図46】

第46図

【図47】

第47図

【図48】

第48図

【図49】

第49図

【図50】

第50図

【図51】

第51図

【図52】

第52図

【図 5 3】

第53圖

【図54】

第54回

【図55】

第55圖

【図56】

第56回

【図 5 7】

第57図

【図 5 8】

第58図

【図 5 9】

第59図

【図 6 0】

第60図

【図 6 1】

第61図

【図 6 2】

第62図

【図 6 3】

第63図

【図 6 4】

第64図

【図 6 5】

第65図

【図 6 6】

第66図

【図 6 7】

第67図

【図 6 8】

第68図

【図 6 9】

【図70】

【図71】

【図72】

第71回

【図73】

第73図

【図74】

第74図

【図75】

第75図

【図76】

第76図

【図 7 7】

【図 7 8】

第77図

【図 7 9】

第78図

【図 8 0】

第80図

【図 8 1】

第81図

---

フロントページの続き

(51)Int.Cl.

F I

H 0 3 F 3/343

A

H 0 3 M 1/74

(56)参考文献 特開2003-66906 (JP, A)

特開2003-91261 (JP, A)

特開2001-42821 (JP, A)

特開2001-42827 (JP, A)

特許第4460841 (JP, B2)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/38

H03F 3/343

H03M 1/74

H01L 51/50

|                |                                                                                             |         |            |

|----------------|---------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 使用有机发光装置的显示装置                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP4559847B2</a>                                                                 | 公开(公告)日 | 2010-10-13 |

| 申请号            | JP2004500412                                                                                | 申请日     | 2003-04-23 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                              |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                |         |            |

| 当前申请(专利权)人(译)  | 东芝移动显示器有限公司                                                                                 |         |            |

| [标]发明人         | 柘植仁志                                                                                        |         |            |

| 发明人            | 柘植 仁志                                                                                       |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H03F3/343 H03M1/74 H03M1/06                                               |         |            |

| CPC分类号         | H03M1/06 G09G3/30                                                                           |         |            |

| FI分类号          | G09G3/30.J G09G3/20.612.F G09G3/20.623.B G09G3/20.642.B G09G3/20.680.G H03F3/343.A H03M1/74 |         |            |

| 代理人(译)         | 松田 正道                                                                                       |         |            |

| 审查员(译)         | 武田 悟                                                                                        |         |            |

| 优先权            | 2002127638 2002-04-26 JP<br>2003074549 2003-03-18 JP                                        |         |            |

| 其他公开文献         | JPWO2003092165A5<br>JPWO2003092165A1                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                   |         |            |

### 摘要(译)

在电流输出型半导体电路中，当通过一个显示板中的多个半导体电路进行显示时，半导体电路的不均匀性导致不同半导体电路的每个块中的亮度不均匀。在电流输出级14a和14b中，电流镜电路形成在芯片的两端，并且从两端提供用作灰度显示的参考的参考电流。此外，通过增加对每个输出进行分配的电流镜电路的栅极线的电阻值，补偿芯片中的晶体管阈值偏差，并使左右两端的输出电流一致。此外，通过使参考电流产生电阻器11c至11f至少在相邻的半导体电路之间相互连接，参考电流对准，并且所有半导体电路上的电流值的变化为1%或更小。结果，可以消除在芯片边界处产生的不均匀性。