(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-113260

(P2010-113260A)

(43) 公開日 平成22年5月20日(2010.5.20)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 624B        |

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | J           |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 680G        |

|                             | G09G 3/20 | 670A        |

|                             | G09G 3/20 | 641P        |

審査請求 未請求 請求項の数 2 O L (全 28 頁) 最終頁に続く

|           |                              |          |                                                   |

|-----------|------------------------------|----------|---------------------------------------------------|

| (21) 出願番号 | 特願2008-287383 (P2008-287383) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号            |

| (22) 出願日  | 平成20年11月10日 (2008.11.10)     | (74) 代理人 | 100082131<br>弁理士 稲本 義雄                            |

|           |                              | (74) 代理人 | 100121131<br>弁理士 西川 孝                             |

|           |                              | (72) 発明者 | 山下 淳一<br>東京都港区港南1丁目7番1号 ソニー株式会社内                  |

|           |                              | (72) 発明者 | 内野 勝秀<br>東京都港区港南1丁目7番1号 ソニー株式会社内                  |

|           |                              |          | F ターム (参考) 3K107 AA01 BB01 CC26 EE03 EE07<br>HH05 |

|           |                              |          | 最終頁に続く                                            |

(54) 【発明の名称】パネルおよび電子回路

(57) 【要約】

【課題】ダスト付着に起因する画素の滅点を防ぐ。

【解決手段】画素部111は、マトリクス状に配置された複数の画素毎に、2つのアノード142a-1, 142a-2を有し、駆動電流により発光する有機EL素子142-1, 142-2と、2つのアノード142a-1, 142a-2にそれぞれ駆動電流を供給するTFT回路141-1, 141-2と、2つのアノード142a-1, 142a-2同士を接続する蓄積容量201とを備えている。本発明は、例えば、パネルに適用できる。

【選択図】図26

## 【特許請求の範囲】

## 【請求項 1】

マトリクス状に配置された複数の画素毎に、

K 個（K は 2 以上の整数値）のアノードを有し、駆動電流により発光する発光素子と

、

前記 K 個のアノード毎に設けられ、前記 K 個のアノードにそれぞれ前記駆動電流を供給する駆動回路と、

前記 K 個のアノード同士を接続する蓄積容量と

を備える

パネル。

10

## 【請求項 2】

マトリクス状に配置された複数の画素毎に、

K 個（K は 2 以上の整数値）のアノードを有し、駆動電流により発光する発光素子と

、

前記 K 個のアノード毎に設けられ、前記 K 個のアノードにそれぞれ前記駆動電流を供給する駆動回路と、

前記 K 個のアノード同士を接続する蓄積容量と

を有する

パネル

を備える電子回路。

20

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、パネルおよび電子回路に関し、ダスト付着に起因する画素の減点を防ぐことができるようになった、パネルおよび電子回路に関する。

## 【背景技術】

## 【0002】

発光素子として有機 E L (Electro-luminescent) 素子を用いた平面自発光型のパネル（以下、有機 E L パネルと称する）の開発が近年盛んになっている（例えば、特許文献 1 乃至 6 参照）。

30

## 【0003】

有機 E L パネルは、有機 E L 素子の発光部位に電界をかけると発光する現象を利用したデバイスである。有機 E L パネルは、印加電圧が 10 V 以下で駆動するため低消費電力であるという特長を有している。有機 E L パネルは、自ら光を発する自発光デバイスであるため、照明部材を必要とせず軽量化及び薄型化が容易にできるという特長を有している。また、有機 E L パネルは、その応答速度が数 μ s 程度と非常に高速であるので、動画表示時の残像が発生しないという特長を有している。

## 【0004】

このような有機 E L パネルに用いられている有機 E L 素子の構造は、カソードとアノードの間に発光部位を有する構造となっている。有機 E L 素子のアノードに電荷が供給されると、発光部位を介して、カソードとアノードの間に電流が流れる。これにより、発光部位に所定の電流が流れ、有機 E L 素子は発光する。なお、発光のために有機 E L 素子に流す電流を、以下、駆動電流と称する。

40

## 【特許文献 1】特開 2003 - 255856 号公報

## 【特許文献 2】特開 2003 - 271095 号公報

## 【特許文献 3】特開 2004 - 133240 号公報

## 【特許文献 4】特開 2004 - 029791 号公報

## 【特許文献 5】特開 2004 - 093682 号公報

## 【特許文献 6】特開 2008 - 65200 号公報

## 【発明の開示】

50

**【発明が解決しようとする課題】****【0005】**

しかしながら、有機EL素子の発光部位は、数10nm～数100nmという非常に薄い層として形成されている。そのため、この発光部位の蒸着工程等でダストが付着すると、有機EL素子のアノードとカソードとの間が電気的にショートしてしまうことがある。この場合、有機EL素子は、駆動電流が流れず、発光しない。その結果、ダストが付着した有機EL素子が点灯しない点状欠陥となり、その有機EL素子の画素が滅点となってしまう場合があった。

**【0006】**

本発明は、このような状況に鑑みてなされたものであり、ダスト付着に起因する画素の滅点を防ぐことができるようとするものである。

10

**【課題を解決するための手段】****【0007】**

本発明の一側面のパネルは、マトリクス状に配置された複数の画素毎に、K個のアノードを有し、駆動電流により発光する発光素子と、前記K個のアノード毎に設けられ、前記K個のアノードにそれぞれ前記駆動電流を供給する駆動回路と、前記K個のアノード同士を接続する蓄積容量とを備えるパネル。

**【0008】**

本発明の一側面の電子回路は、上述した本発明の一側面のパネルを備える電子回路である。

20

**【0009】**

本発明の一側面においては、マトリクス状に配置された複数の画素毎に、K個のアノードを有し、駆動電流により発光する発光素子と、前記K個のアノード毎に設けられ、前記K個のアノードにそれぞれ前記駆動電流を供給する駆動回路と、前記K個のアノード同士を接続する蓄積容量とを備えるパネルが提供される。

**【発明の効果】****【0010】**

本発明の一側面によれば、ダスト付着に起因する画素の滅点を防ぐことができる。

**【発明を実施するための最良の形態】****【0011】**

最初に、本発明の理解を容易にし、且つ、背景を明らかにするため、従来の有機ELパネルの基本となる構成と、その構成における問題点について、図1乃至6を参照して説明する。

30

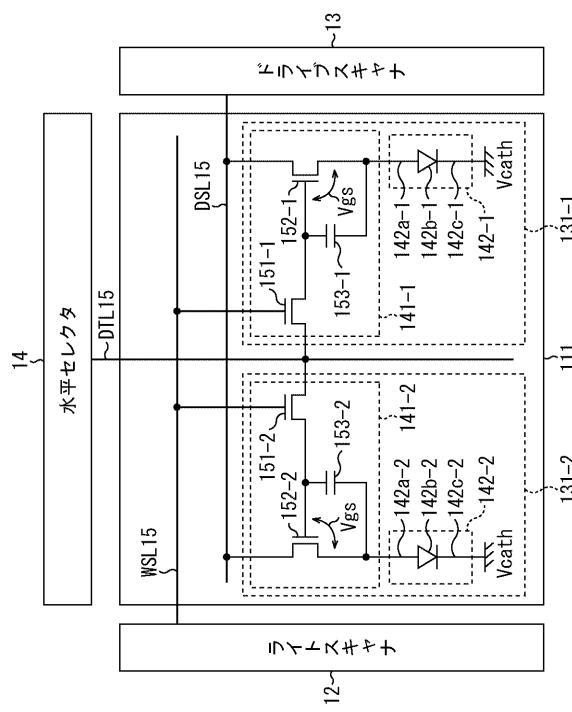

**【0012】**

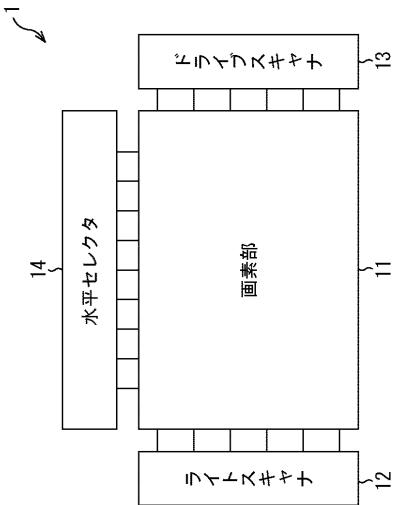

図1は、従来の有機ELパネルの構成例を示すブロック図である。

**【0013】**

従来の有機ELパネル1には、画素部11が設けられている。従来の有機ELパネル1にはまた、画素部11を駆動する駆動部として、ライトスキャナ12、ドライブスキャナ13、及び水平セレクタ14が設けられている。

**【0014】**

従来の有機ELパネル1は、マトリクス状に配置されたN×Mの画素から構成される画像を表示することができる。なお、N,Mは1以上の任意の整数値である。

40

**【0015】**

詳細には、N×Mの各画素はそれぞれ、R(Red)画素、G(Green)画素、及びB(Blue)画素から構成される。即ち、R画素、G画素、及びB画素はそれぞれ、N×M個存在する。そこで、以下、1つの画素とは、R画素、G画素、またはB画素を意味するものとする。また、以下、R画素、G画素、及びB画素をまとめて、特にRGB画素群と称する。

**【0016】**

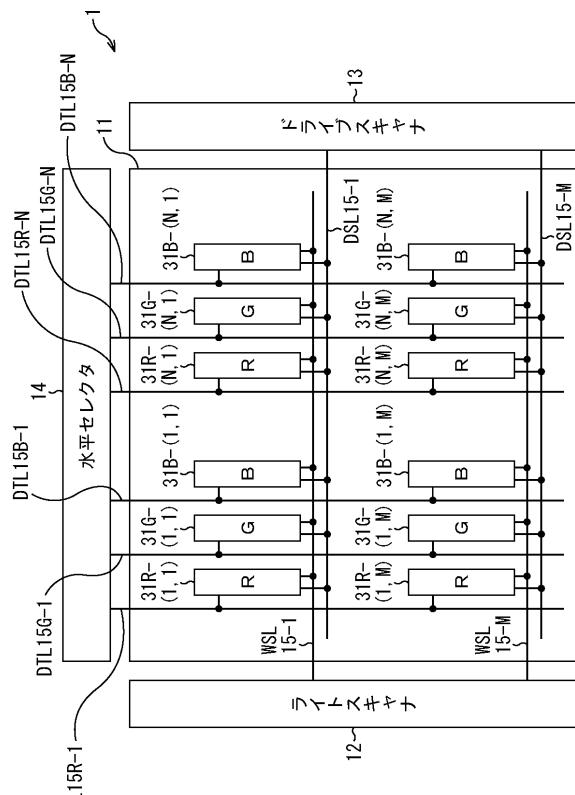

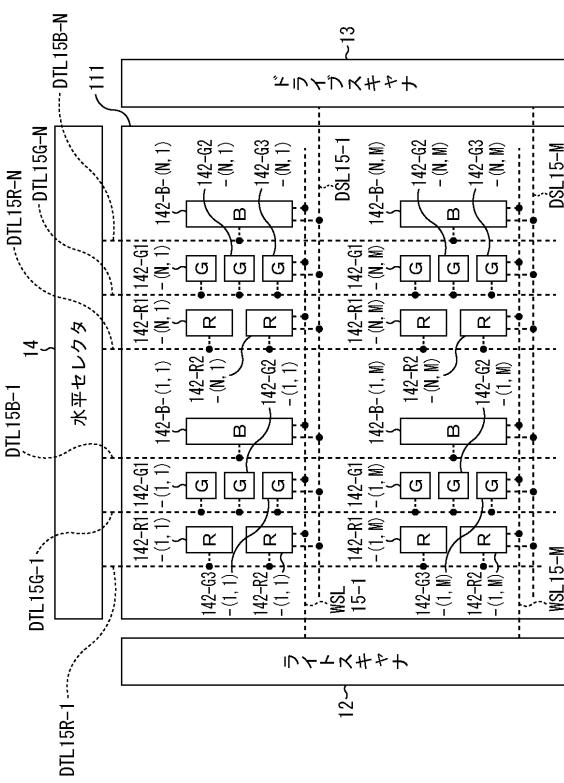

画素部11(以下、適宜、従来の画素部11と称する)は、1つの画素の表示を担当す

50

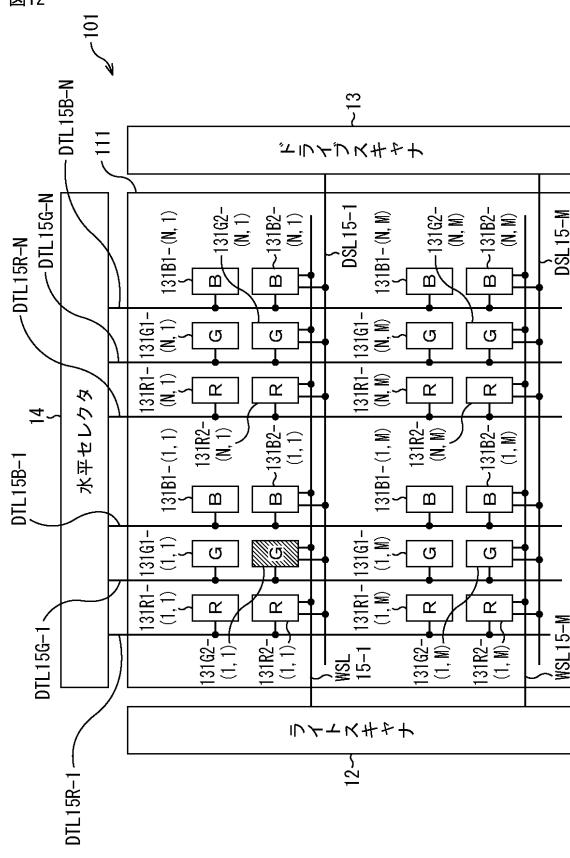

る画素回路が、図2に示されるようにマトリクス状に配置されて構成されている。即ち、図2は、従来の画素部11の構成例を示すブロック図である。

#### 【0017】

従来の画素部11には、R画素について、 $N \times M$ 個の画素回路31R-(1,1)乃至31R-(N,M)が設けられている。G画素について、 $N \times M$ 個の画素回路31G-(1,1)乃至31G-(N,M)が設けられている。B画素について、 $N \times M$ 個の画素回路31B-(1,1)乃至31B-(N,M)が設けられている。

#### 【0018】

ここで、1つのRGB画素群を構成するR画素、G画素、及びB画素の各画素回路31をまとめて、画素回路群と称する。 $N \times M$ のRGB画素群のそれぞれに対応付けられた各画素回路群が、マトリクス状に配置されて従来の画素部11が構成される。例えば、第m行第n列(mは、1乃至Mのうちの任意の整数値。nは、1乃至Nのうちの任意の整数値)の画素回路群は、画素回路31R-(n,m)、31G-(n,m)、31B-(n,m)から構成され、従来の画素部11のうちの第m行第n列の位置に配置される。

10

#### 【0019】

なお、以下、R画素の画素回路31R-(1,1)乃至31R-(N,M)、G画素の画素回路31G-(1,1)乃至31G-(N,M)、B画素の画素回路31B-(1,1)乃至31B-(N,M)のそれぞれを特に区別する必要がない場合、R画素の画素回路31R、G画素の画素回路31G、及びB画素の画素回路31Bのそれぞれと称する。即ち、とあるRGB画素群に着目している場合、そのRGB画素群に対応する画素回路を、R画素の画素回路31R、G画素の画素回路31G、及びB画素の画素回路31Bと呼称して説明する。

20

#### 【0020】

従来の画素部11は、M本の走査線WSL15-1乃至WSL15-M、M本の電源線DSL15-1乃至DSL15-M、並びに、R画素についてのN本の信号線DTL15R-1乃至DTL15R-N、G画素についてのN本の信号線DTL15G-1乃至DTL15G-N、及びB画素についてのN本の信号線DTL15B-1乃至DTL15B-Nも有している。

30

#### 【0021】

なお、以下、走査線WSL15-1乃至WSL15-M、電源線DSL15-1乃至DSL15-Mのそれぞれを特に区別する必要がない場合、走査線WSL15、電源線DSL15のそれぞれと称する。また、R画素の信号線DTL15R-n、G画素の信号線DTL15G-n、B画素の信号線DTL15B-nを特に区別する必要がない場合、信号線DTL-nと称する。

40

#### 【0022】

第m行のR画素についての画素回路31R-(1,m)乃至31R-(N,m)、第m行のG画素についての画素回路31G-(1,m)乃至31G-(N,m)、並びに、第m行のB画素についての画素回路31B-(1,m)乃至31B-(N,m)は、走査線WSL15-mでライトスキャナ12と、電源線DSL15-mでドライブスキャナ13とそれぞれ接続されている。

#### 【0023】

また、第n列のR画素についての画素回路31R-(n,1)乃至31R-(n,M)は、信号線WSL15R-nで水平セレクタ14と接続されている。第n列のG画素についての画素回路31G-(n,1)乃至31G-(n,M)は、信号線WSL15G-nで水平セレクタ14と接続されている。第n列のB画素についての画素回路31B-(n,1)乃至31B-(n,M)は、信号線WSL15B-nで水平セレクタ14と接続されている。

#### 【0024】

ライトスキャナ12は、走査線WSL15-1乃至WSL15-Mに水平期間(1H)で順次制御信号を供給して各色(R,G,B)の画素の画素回路31を行単位で線順次走

50

査する。ドライブスキャナ 13 は、線順次走査に合わせて電源線 D S L 15 - 1 乃至 15 - M に第 1 電位（後述する V<sub>c c</sub>）または第 2 電位（後述する V<sub>s s</sub>）の電源電圧を供給する。水平セレクタ 14 は、線順次走査に合わせて各水平期間（1 H）内で映像信号となる信号電位 V<sub>s i g</sub> と基準電位 V<sub>o f s</sub> とを切換えて列状の各色についての信号線 D T L - 1 乃至 D T L - N に供給する。

#### 【0025】

図 3 は、各色（R, G, B）の画素の画素回路 31 のうちのひとつの構成例を示したブロック図である。

#### 【0026】

図 3 の画素回路 31 は、TFT（Thin Film Transistor）回路 41 と有機 EL 素子 42 とから構成される。なお、TFT 回路 41 の素子構成は、2 Tr (transistor) + 1 C (capacitor) と呼ばれている。TFT 回路 41 は、書き込みトランジスタ 51、駆動トランジスタ 52、蓄積容量 53 から構成される。有機 EL 素子 42 は、アノード 42a、発光部位 42b、及びカソード 42c から構成されている。

#### 【0027】

書き込みトランジスタ 51 のゲートは走査線 W S L 15 と接続されている。書き込みトランジスタ 51 のドレインは信号線 D T L 15 と接続されている。書き込みトランジスタ 51 のソースは、駆動トランジスタ 52 のゲートと接続されている。駆動トランジスタ 52 のソースは有機 EL 素子 42 のアノード 42a に接続されている。駆動トランジスタ 52 のドレインは電源線 D S L 15 に接続されている。蓄積容量 53 は、駆動トランジスタ 52 のゲートと有機 EL 素子 42 のアノード 42a の間に接続されている。有機 EL 素子 42 のカソード 42c は所定の電位 V<sub>c a t h</sub> に設定されている。

#### 【0028】

図 4 は、図 3 の構成の画素回路 31 を含む従来の画素部 11 の断面レイアウトの一例を示す図である。

#### 【0029】

図 4において、ユーザは、図中上から下の垂直方向に、従来の画素部 11 を視認する。なお、以下の説明では、図 4 中上側の面を上面と称し、同図中下側の面を下面と称する。

#### 【0030】

基板 71 の上面には、TFT 回路 41 が配置されている。従来の画素部 11 の製造時ににおいて、TFT 回路 41 が配置された後に、平坦化膜 72 が積層される。但し、TFT 回路 41 の上面の一部には、平坦化膜 72 は積層されない。換言すると、平坦化膜 72 のうち、TFT 回路 41 の上面の一部に相当する部分には、穴があいている。平坦化膜 72 の平坦化された上面であって、上述の穴を含む部分には、有機 EL 素子 42 のアノード 42a が形成される。アノード 42a は、平坦化膜 72 の穴に挿入される部分（図 4 中 TFT 回路 41 まで下方に伸びる逆台形の部分）を有しており、その部分で TFT 回路 41 に直接に接続されている。また、平坦化膜 72 の上面には、補助配線 73 も配置される。アノード 42a と補助配線 73 は、例えば、同じ膜として積層される。その膜の上には、有機 EL 素子 42 の発光部位 42b が積層されて形成される。有機 EL 素子 42 のうち、発光部位 42b が形成された後に、カソード 42c が積層される。図 4 の例では、全てのカソード 42c が一体の連続膜として形成されている。また、2 つの発光部位 42b の間の部分にもカソード 42c が形成される。よって、この部分で補助配線 73 とカソード 42c とは直接に接続される。アノード 42a、発光部位 42b、及びカソード 42c がこのように形成されることで、有機 EL 素子 42 が構成される。

#### 【0031】

このような構成の従来の画素部 11 の製造工程のうち、図 4 に示される発光部位 42b の蒸着工程等でダストが付着する場合がある。例えば、図 5 に示されるようなダスト DU が付着する場合がある。

#### 【0032】

図 5 は、ダスト DU が付着した場合の従来の画素部 11 の断面レイアウトの一例を示す図

10

20

30

40

50

である。

【0033】

図5では、ダストDUは、アノード42aの上面から、発光部位42bを貫通し、カソード42cまで達するように付着している。このようにダストDUが付着すると、ダストDUが付着した有機EL素子42のアノード42aとカソード42cの間が電気的にショートしてしまう場合が多々存在する。このような場合、ダストDUが付着している発光部位42bには駆動電流が流れなくなり、その有機EL素子42は発光しなくなる。

【0034】

例えば、1行1列目のG画素についての有機EL素子42、即ち、図6に示される画素回路31G-(1,1)に含まれる有機EL素子42にダストDUが付着すると、このG画素が滅点となる。

【0035】

画素の滅点は、有機ELパネルといったフラットパネルディスプレイに対する市場クレームの大きな要素である。したがって、このような市場クレームの対策としては、ダスト付着に起因する画素の滅点を防ぐことは非常に重要である。

【0036】

そこで、本発明人は、ダスト付着に起因する画素の滅点を防ぐことができる手法として、次のような手法を発明した。

【0037】

即ち、従来の有機ELパネル1では、図4と図5に示されるように、1つの画素について、1つの有機EL素子42のアノード42aが用いられていた。このため、有機EL素子42の発光部位42bにダスト(図5の例ではダストDU)が付着すると、カソード42cとアノード42aとが電気的にショートをしてしまい、結果として画素が滅点となってしまっていた。

【0038】

但し、ダストは、非常に小さいものであり、それゆえ、有機EL素子の発光部位における占有面積も非常に小さくなる。この場合、1つの画素について、有機EL素子のアノードが2以上存在すれば、2以上のアノードのうち、1つのみにダストが接触し、他のものにはダストが接触しない。よって、ダストが接触したアノードとカソードの間は電気的にショートを起こし、その間の発光部位は確かに発光しないかもしれない。しかしながら、他のアノードとカソード電極との間には正常に駆動電流が流れ、その間の発光部位は発光することになる。よって、画素全体として輝度は低下するが、滅点自体を防ぐことができる、という技術的思想を本発明人はした。

【0039】

そこで、本発明人は、1つの画素について、アノードを2以上に分割し、分割された2以上のアノード毎にTFT回路をそれぞれ接続する、という手法を発明した。以下、かかる手法をアノード分割手法と称する。

【0040】

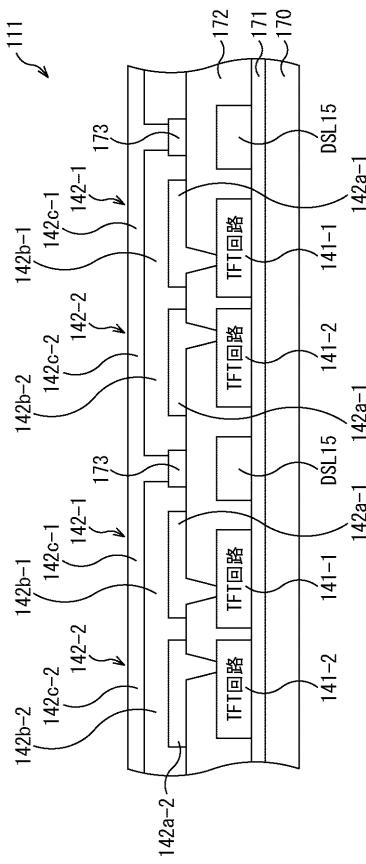

具体的には例えば、アノード分割手法を適用した場合の画素部の断面レイアウトの一例が図7に示されている。なお、以下、アノード分割手法を適用した場合の画素部を、本発明の画素部111と称する。

【0041】

図7において、ユーザは、図中上から下の垂直方向に、本発明の画素部111を視認する。なお、以下の説明では、図7中上側の面を上面と称し、同図中下側の面を下面と称する。

【0042】

基板171の下面には、遮光メタル170が形成される。基板171の上面には、1つの画素につき、2つのTFT回路141-1, 141-2が配置される。また、基板171の上面には電源線DSL15も配置される。

【0043】

10

20

30

40

50

本発明の画素部 111 の製造時において、TFT 回路 141-1, 141-2 が配置された後に、平坦化膜 172 が積層される。但し、TFT 回路 141-1, 141-2 の各上面の一部には、平坦化膜 172 は積層されない。換言すると、平坦化膜 172 のうち、TFT 回路 141-1, 141-2 の各上面の一部に相当する各部分には、穴があいている。

#### 【0044】

平坦化膜 172 の平坦化された上面であって、上述の TFT 回路 141-1 の上面の穴を含む部分には、アノード 142a-1 が形成される。アノード 142a-1 は、平坦化膜 172 の穴に挿入される部分（図 7 中 TFT 回路 141-1 まで下方に伸びる逆台形の部分）を有しており、その部分で TFT 回路 141-1 に直接に接続されている。10

#### 【0045】

同様に、平坦化膜 172 の平坦化された上面であって、上述の TFT 回路 141-2 の上面の穴を含む部分には、アノード 142a-2 が形成される。アノード 142a-2 は、平坦化膜 172 の穴に挿入される部分（図 7 中 TFT 回路 141-2 まで下方に伸びる逆台形の部分）を有しており、その部分で TFT 回路 141-2 に直接に接続されている。20

#### 【0046】

このように、図 7 の例では、1つの画素について、2つのアノード 142a-1, 142a-2 と、TFT 回路 141-1, 141-2 が設けられている。即ち、図 7 の例は、アノード分割手法のうち、アノードの分割数を 2 つにした場合の手法の一例が適用された例となっている。20

#### 【0047】

この場合、等価回路的に、1つの画素には、アノード 142a-1 を含む有機 EL 素子と、アノード 142a-2 を含む有機 EL 素子とが存在すると把握することができる。そこで、以下、前者の有機 EL 素子を有機 EL 素子 142-1 と称し、後者の有機 EL 素子を有機 EL 素子 142-2 と称する。そして、有機 EL 素子 142-1 のアノード 142a-1 以外の構成要素を、発光部位 142b-1、カソード 142c-1 とそれぞれ称する。同様に、有機 EL 素子 142-2 のアノード 142a-2 以外の構成要素を、発光部位 142b-2、カソード 142c-2 とそれぞれ称する。30

#### 【0048】

この場合、アノード 142a-1, 142a-2 は、補助配線 73 とともに同じ膜として平坦化膜 172 の上面に積層される。以下、この膜を、分割アノード膜 ML と称する。分割アノード膜 ML については、図 10 を参照して後述する。30

#### 【0049】

分割アノード膜 ML の上には、発光部位 142b-1, 142b-2 が積層されて形成される。なお、図 7 の例では、発光部位 142b-1, 142b-2 が一体の膜として形成されている。発光部位 142b-1, 142b-2 を一体として形成している膜を、以下、適宜、発光部位層 142b と称する。発光部位層 142b の上には、カソード 142c-1, 142c-2 が積層されて形成される。なお、図 7 の例では、全画素のカソード 142c-1, 142c-2 が全て一体の連続膜として形成されている。この一体の連続膜を、以下、適宜、カソード 142c と称する。また、2つの発光部位層 142b の間の部分にもカソード 142c が形成される。よって、この部分で補助配線 173 とカソード 142c とは直接に接続される。40

#### 【0050】

以上の本発明の画素部 111 の構成を、1つの画素についての等価回路として考え直してみる。従来の画素部 11 では、図 3 に示されるように、1つの画素に対して 1 つの画素回路 31 のみが設けられていた。これに対して、本発明の画素部 111 では、図 8 に示されるように、1つの画素に対して 2 つの画素回路 131-1, 131-2 が設けられる。

#### 【0051】

図 8 の画素回路 131-1, 131-2 の単体自体の構成は、画素回路 31 と基本的に

同様の構成となっている。

#### 【0052】

即ち、画素回路 131-1 / 131-2 は、TFT 回路 141-1 / 141-2 と有機 EL 素子 142-1 / 142-2 とから構成される。TFT 回路 141-1 / 141-2 は、書き込みトランジスタ 151-1 / 151-2、駆動トランジスタ 152-1 / 152-2、及び蓄積容量 153-1 / 153-2 から構成される。有機 EL 素子 142-1 / 142-2 は、アノード 142a-1 / 142a-2、発光部位 142b-1 / 142b-2、及びカソード 142c-1 / 142c-2 から構成されている。

#### 【0053】

書き込みトランジスタ 151-1, 151-2 の各ゲートは同一の走査線 WSL15 と接続されている。書き込みトランジスタ 151-1, 151-2 の各ドレインは同一の信号線 DTL15 と接続されている。書き込みトランジスタ 151-1 / 151-2 のソースは、駆動トランジスタ 152-1 / 152-2 のゲートと接続されている。駆動トランジスタ 152-1 / 152-2 のソースは有機 EL 素子 142-1 / 142-2 のアノード 142a-1 / 142a-2 に接続されている。駆動トランジスタ 152-1 / 152-2 のドレインは電源線 DSL15 に接続されている。蓄積容量 153-1 / 153-2 は、駆動トランジスタ 152-1 / 152-2 のゲートと有機 EL 素子 142-1 / 142-2 のアノード 142a-1 / 142a-2との間に接続されている。有機 EL 素子 142-1 / 142-2 のカソード 142c-1 / 142c-2 は所定の電位 V cath に設定されている。

10

20

#### 【0054】

このように、図 8 の画素回路 131-1, 131-2 の単体はそれぞれ、図 3 の画素回路 31 と同様に構成される。従って、画素回路 131-1, 131-2 の単体はそれぞれ、画素回路 31 と同様の発光動作を行う。但し、画素回路 131-1, 131-2 はそれぞれ、同一の走査線 WSL15、同一の電源線 DSL15、同一の信号線 DTL15 に接続されているので、同一タイミングで発光動作を行う。

#### 【0055】

このように、図 8 の例の TFT 回路 141-1, 141-2 は、TFT 回路 41 と同様の構成、即ち、2Tr + 1C と称される回路構成を有している。しかしながら、TFT 回路 141-1, 141-2 は、図 8 の例の構成に限定されず、例えば、3 個以上のトランジスタを含む構成を取るようにしてよい。

30

#### 【0056】

また、書き込みトランジスタ 151-1, 151-2 及び駆動トランジスタ 152-1, 152-2 は、いずれも N チャネル型トランジスタとして構成されている。したがって、書き込みトランジスタ 151-1, 151-2 及び駆動トランジスタ 152-1, 152-2 は、低温ポリシリコンよりも安価に作成できるアモルファスシリコンで作成することができる。そのため、製造コストをより安価にすることができる。

#### 【0057】

ただし、駆動トランジスタ 152-1, 152-2 は、N チャネル型トランジスタで構成する必要は特になく、P チャネル型トランジスタで構成してもよい。

40

#### 【0058】

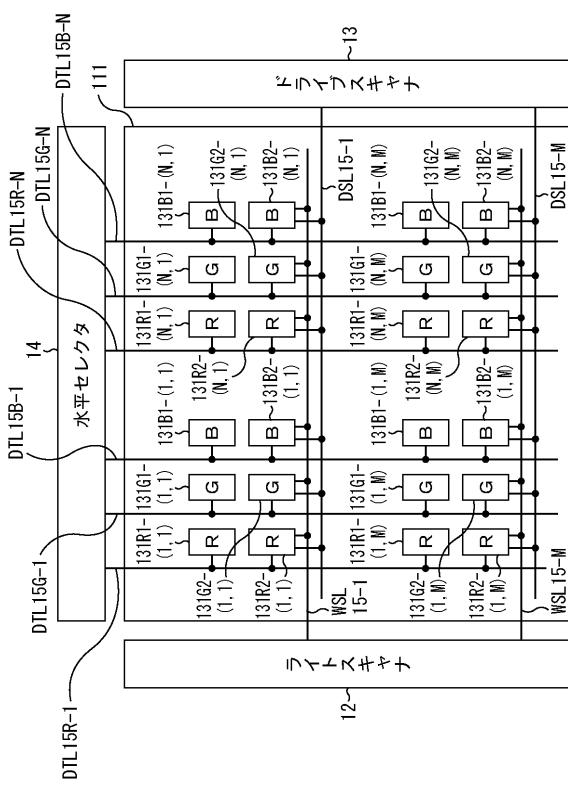

このように、本発明の画素部 111 は、1 つの画素につき 2 つの画素回路 131-1, 131-2 を有している。よって、従来と同様に、N × M 個の RGB 画素群からなる画像を表示させる場合には、本発明の画素部 111 は、例えば図 9 に示されるように構成される。即ち、図 9 は、本発明の画素部 111 の構成例を示すプロック図である。

#### 【0059】

即ち、第 m 行第 n 列 (m は、1 乃至 M のうちの任意の整数値。n は、1 乃至 N のうちの任意の整数値) の R 画素に対しては、2 つの画素回路 131R1-(n, m), 131R2-(n, m) が設けられている。画素回路 131R1-(n, m), 131R2-(n, m) は、本発明の画素部 111 のうちの第 m 行第 n 列の R 画素の位置に直列的に配置さ

50

れる。なお、任意の画素位置の R 画素について説明する場合、画素回路 1 3 1 R 1 - ( n , m ) , 1 3 1 R 2 - ( n , m ) のそれぞれを、画素回路 1 3 1 R 1 , 1 3 1 R 2 のそれと称する。

#### 【 0 0 6 0 】

同様に、第 m 行第 n 列の G 画素に対しては、2 つの画素回路 1 3 1 G 1 - ( n , m ) , 1 3 1 G 2 - ( n , m ) が設けられている。画素回路 1 3 1 G 1 - ( n , m ) , 1 3 1 G 2 - ( n , m ) は、本発明の画素部 1 1 1 のうちの第 m 行第 n 列の G 画素の位置に直列的に配置される。なお、任意の画素位置の G 画素について説明する場合、画素回路 1 3 1 G 1 - ( n , m ) , 1 3 1 G 2 - ( n , m ) のそれを、画素回路 1 3 1 G 1 , 1 3 1 G 2 のそれと称する。

10

#### 【 0 0 6 1 】

第 m 行第 n 列の B 画素に対しては、2 つの画素回路 1 3 1 B 1 - ( n , m ) , 1 3 1 B 2 - ( n , m ) が設けられている。画素回路 1 3 1 B 1 - ( n , m ) , 1 3 1 B 2 - ( n , m ) は、本発明の画素部 1 1 1 のうちの第 m 行第 n 列の B 画素の位置に直列的に配置される。なお、任意の画素位置の B 画素について説明する場合、画素回路 1 3 1 B 1 - ( n , m ) , 1 3 1 B 2 - ( n , m ) のそれを、画素回路 1 3 1 B 1 , 1 3 1 B 2 のそれと称する。

#### 【 0 0 6 2 】

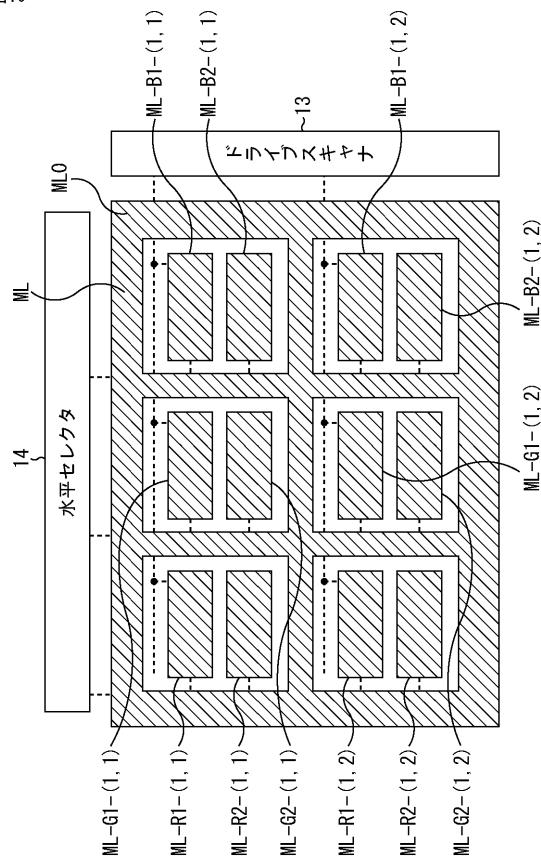

このような図 9 の構成を有する本発明の画素部 1 1 1 のうち、1 行 1 列と 1 行 2 列の R G B 画素群についての分割アノード膜 M L の平面レイアウトの一例が、図 1 0 に示されている。図 1 0 中網掛けされている部分が、分割アノード膜 M L が形成されている部分である。

20

#### 【 0 0 6 3 】

図 1 0 において、画素回路 1 3 1 R 1 - ( 1 , 1 ) 内のアノード 1 4 2 a - 1 は、分割アノード膜 M L の長方形形状の部分 M L - R 1 - ( 1 , 1 ) として形成される。画素回路 1 3 1 R 2 - ( 1 , 1 ) 内のアノード 1 4 2 a - 2 は、分割アノード膜 M L の長方形形状の部分 M L - R 2 - ( 1 , 1 ) として形成される。画素回路 1 3 1 G 1 - ( 1 , 1 ) 内のアノード 1 4 2 a - 1 は、分割アノード膜 M L の長方形形状の部分 M L - G 1 - ( 1 , 1 ) として形成される。画素回路 1 3 1 G 2 - ( 1 , 1 ) 内のアノード 1 4 2 a - 2 は、分割アノード膜 M L の長方形形状の部分 M L - G 2 - ( 1 , 1 ) として形成される。画素回路 1 3 1 B 1 - ( 1 , 1 ) 内のアノード 1 4 2 a - 1 は、分割アノード膜 M L の長方形形状の部分 M L - B 1 - ( 1 , 1 ) として形成される。画素回路 1 3 1 B 2 - ( 1 , 1 ) 内のアノード 1 4 2 a - 2 は、分割アノード膜 M L の長方形形状の部分 M L - B 2 - ( 1 , 1 ) として形成される。また、補助配線 1 7 3 は、分割アノード膜 M L の格子状の部分 M L O として形成される。

30

#### 【 0 0 6 4 】

以上、図 7 乃至図 1 0 を参照して、本発明が適用されるアノード分割手法、及び、そのアノード分割手法（そのうちの分割数が 2 の場合の手法）が適用された有機 E L パネルについて説明してきた。

40

#### 【 0 0 6 5 】

この有機 E L パネルにおいて、図 1 1 に示されるように、発光部位 1 4 2 b - 1 , 1 4 2 b - 2 を含む発光部位層にダスト DU が付着したとする。この場合、ダスト DU は、非常に小さいものであり、それゆえ、有機 E L 素子の発光部位における占有面積も非常に小さい。よって、ダスト DU は、アノード 1 4 2 a - 1 , 1 4 2 a - 2 のうちの一方のみと接触する。例えば図 1 1 の例では、ダスト DU は、アノード 1 4 2 a - 2 のみと接触し、アノード 1 4 2 a - 1 とは接触していない。

#### 【 0 0 6 6 】

よって、ダスト DU が接触したアノード 1 4 2 a - 2 とカソード 1 4 2 c - 2 との間は電気的にショートを起こすので、有機 E L 素子 1 4 2 - 2 は発光しない場合がある。これに対して、ダスト DU が接触していないアノード 1 4 2 a - 1 とカソード 1 4 2 c - 1 との間

50

は、正常に駆動電流が流れるので、有機EL素子142-1は発光する。従って、画素全体からすると、ダストDUが接触していない場合の輝度に対して半分の輝度になるが、発光することに変わりはないので滅点とはならない。

#### 【0067】

例えば、ダストDUが付着した画素が1行1列目のG画素であるとする。この場合、図12に示される2つの画素回路131G1-(1,1), 131G2-(1,2)のうち、画素回路131G2-(1,2)が担当する有機EL素子142-2は発光しないが、画素回路131G1-(1,2)が担当する有機EL素子142-1は発光する。よって、1行1列目のG画素は、ダストDUが接触していない場合の輝度に対して半分の輝度になるが、発光することに変わりはないので滅点とはならない。10

#### 【0068】

その結果、滅点として認識される画素の数が減るので、有機ELパネルの歩留まり向上を図ることができるようになる。

#### 【0069】

以上の内容を、本発明が適用されるアノード分割手法の効果として一般的に表現すると、次のようなことになる。

#### 【0070】

即ち、とある画素について、有機EL素子の発光部位層にたとえダストが付着しても、そのダストは、発光部位層における占有面積が非常に小さい。よって、ダストは、K個のアノード(Kは、2以上の整数値。上述した図7乃至図10の例ではK=2)のうちの1つだけと接触することになる。20

#### 【0071】

この場合、K個のアノードのうち、ダストと接触している1つのアノードとカソードとの間では確かに電気的ショートが発生する。しかしながら、それ以外のK-1個のアノードのそれぞれとカソードとの間では電気的ショートは発生しない。よって、K-1個のアノードのそれぞれとカソードとの間を各駆動電流が正常に流れることにより、その間に形成されている発光部位層は通常に発光する。

#### 【0072】

即ち、1つの画素について、K個のアノードの全てとカソードとの間をそれぞれ正常に流れる全駆動電流により発光部位層の全てが発光した場合、その画素の輝度を、100[%]の輝度とする。この場合、ダストが発光部位層に付着すると、ダストが接触しないK-1個のアノードのそれぞれとカソードとの間に形成されている発光部位層は通常に発光する。即ち、ダストが接触している1個のアノードとカソードとの間に形成されている発光部位層のみが発光しない。よって、画素全体の輝度は、{(K-1)/K}×100[%]の輝度となる。即ち、ダストが発光部位層に付着すると、付着しない場合と比較して確かに輝度は低下する。しかしながら、輝度は0%にはならず、画素全体が滅点となることはない。30

#### 【0073】

つまり、ダストが付着した画素(以下、対象画素と称する)は、従来では滅点となるため、その輝度レベルは周りの画素に対して0%となり、人の目に異常画素として視認されやすかった。この異常画素として視認されやすい度合いを、以下、視認度と称する。これに対して、本発明が適用されるアノード分割手法を適用することで、その輝度レベルは周りの画素と比較して{(K-1)/K}×100[%]となり、視認度が低下することになる。例えば、K=3, 4のそれぞれとした場合、それぞれの輝度レベルは周りの画素と比較して67%、75%のそれぞれとなり、視認度が低下していくことになる。40

#### 【0074】

アノードの分割数Kを増やすほど、輝度レベルは上がる。即ち、周りの画素に対する輝度レベルの低下度合いは抑制される。よって、視認度もより一段と低下することになる。

#### 【0075】

ここで、アノードの分割数Kを増やすということは、画素部に配置されるTFT回路の50

数もその分だけ増加することを意味する。しかしながら、画素部にレイアウトできる TFT 回路の数は限られており、アノードの分割数  $K$  を単純に増加させることは困難である。そこで、1つのRGB画素群に必要な画素回路（TFT回路と有機EL素子とからなる回路）の総数  $L$  は固定しておき、即ち、総数  $L$  個（ $L$  は3の倍数の任意の整数值）の画素回路を、R画素、G画素、B画素（以下、各色画素と適宜称する）のそれぞれ一律に分配する（ $L / 3$  個ずつに分配する）のではなく、適宜比率を変えて分配するとよい。この場合、RGB画素群のレイアウト構成としては、 $L$  個の有機EL素子は、各色画素に分配されたとおりに配置し、 $L$  個のTFT回路は、各色画素への分配にはこだわらず、各色画素の位置に（ $L / 3$ ）個ずつ均等に配置するとよい。

## 【0076】

10

即ち、本発明の画素部111により表示される画像は、R画素、G画素、及びB画素の3つの色画素から構成されるRGB画素群を1組として、そのRGB群がマトリクス状に配置されて構成される画像である。この場合、RGB画素群に設けられるアノードの総数は $L$ 個に固定され、R画素のアノードの個数  $K_1$  と、G画素のアノードの個数  $K_2$  と、B画素のアノードの個数  $K_3$  とは、 $K_1 + K_2 + K_3 = L$ となることを条件に、それぞれ独立して決定される。

## 【0077】

20

そして、個数  $K_1$ 、個数  $K_2$ 、および、個数  $K_3$  の中に  $3 / L$  よりも小さい個数  $K_s$  と、 $3 / L$  よりも大きい個数  $K_b$  を含む場合、個数  $K_b$  のアノードを有する色画素のTFT回路（駆動回路）のうち、 $3 / L$  個のTFT回路は、個数  $K_b$  のアノードを有する色画素の位置に配置され、残りの（ $K_b - L$ ）個のTFT回路は、個数  $K_s$  のアノードを有する色画素の位置に配置させる。

## 【0078】

30

例えば、視認度が低くて寿命が短いB画素については画素回路の数を減らし、その分だけG画素についての画素回路の数を増加させることができる。具体的には例えば、上述の例に対応させて、1つのRGB画素群における画素回路の総数  $L = 6$  とする。以下、1つのRGB画素群において、2個のR画素用の画素回路を、上述した例にあわせて、画素回路131R1, 131R2と称する。3個のG画素用の画素回路を、上述した例にあわせて、画素回路131G1, 131G2, 131G3と称する。1個のB画素用の画素回路を、上述した例にあわせて、画素回路131Bと称する。また、これらの画素回路の各構成要素を示す各符号も、上述した例にあわせて付されるとする。

## 【0079】

40

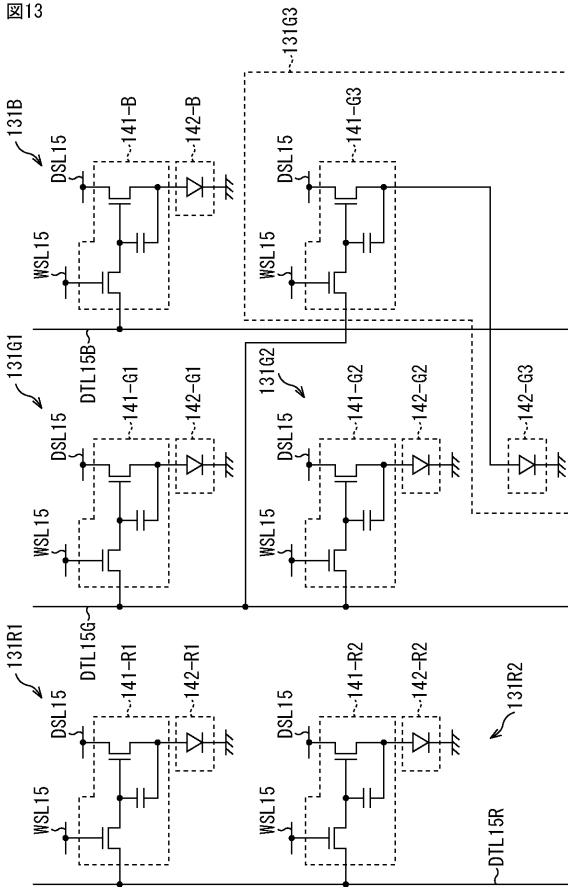

この場合、RGB画素群のレイアウト構成としては、例えば図13に示される通りになる。

## 【0080】

即ち、2個（=  $3 / L$  個）のR画素用の画素回路131R1, 131R2のうち、有機EL素子142-R1, 142-R2はR画素の位置（図13中左側の位置）に配置される。3個（=  $3 / L$  よりも大きい個数  $K_b = 3$  個）のG画素用の画素回路131G1, 131G2, 131G3のうち、有機EL素子142-G1, 142-G2, 142-G3はG画素の位置（図13中、中央の位置）に配置される。1個（=  $3 / L$  よりも小さい個数  $K_s = 1$  個）のB画素用の画素回路131Bのうち、有機EL素子142-BはB画素の位置（図13中、右側の位置）に配置される。

## 【0081】

50

これに対して、TFT回路は、R画素、G画素、及びB画素の各位置に、2個ずつ均等に配置される。即ち、R画素の位置（図13中左側の位置）には、2個のR画素用のTFT回路141-R1, 141-R2が配置される。

## 【0082】

G画素の位置（図13中、中央の位置）には、3個（=  $3 / L$  よりも大きい個数  $K_b = 3$  個）のG画素用のTFT回路141-G1, 141-G2, 141-G3のうち、2個（=  $3 / L$  個）のG画素用のTFT回路141-G1, 141-G2が配置される。残り

50

の1個(=残りの( $K_b - L$ )個)のG画素用のTFT回路141-G3は、B画素の位置(図13中右側の位置)に配置される。即ち、B画素の位置(図13中右側の位置)には、B画素用のTFT回路141-Bと、G画素用のTFT回路141-G3との2個が配置される。

#### 【0083】

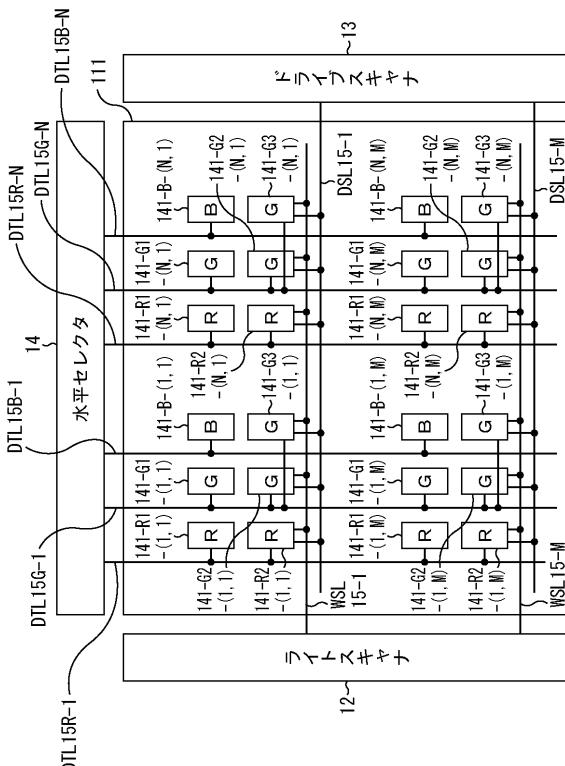

よって、本発明の画素部111全体としては、有機EL素子のレイアウト構成は図14に示される通りになる。これに対して、TFT回路のレイアウト構成は図15に示される通りになる。

#### 【0084】

以上のように、1つのRGB画素群において有機EL素子全体の総数をL個として、L個の有機EL素子を、視認度に応じた個数ずつ各色画素に分配することができる。即ち、視認度の高い色の画素については、有機EL素子の数を増加させることができる。これにより、有機ELパネルの歩留まりをさらに一段と向上させることができる。

10

#### 【0085】

以下、図16乃至図25を参照して、画素回路の動作について説明する。

#### 【0086】

但し、本発明の各色画素に対して、2以上の画素回路が対応づけられることがある。この場合、2以上の画素回路のそれぞれは、同一の走査線WSL15、同一の電源線DSL15、及び同一の信号線DTL15に接続される。よって、2以上の画素回路は、同一タイミングで発光動作を行う。そこで、以下、1つの画素回路の動作についてのみ説明する。さらに、1つの画素回路自体の構成はいずれも、図8の画素回路131-1または131-2と同様の構成となる。そこで、以下、画素回路131-1または131-2を画素回路131と称して、その画素回路131の動作として説明する。

20

#### 【0087】

画素回路131において、書き込みトランジスタ151が、走査線WSL15から供給された制御信号に応じてオン(導通)すると、蓄積容量153は、信号線DTL15を介して水平セレクタ14から供給された電荷を蓄積して保持する。駆動トランジスタ152は、高電位Vccにある電源線DSL15から電流の供給を受け、蓄積容量153に保持された信号電位Vsigに応じて駆動電流Idsを有機EL素子142に流す。有機EL素子142に所定の駆動電流Idsが流れることにより、画素回路131が発光する。

30

#### 【0088】

画素回路131は、閾値補正機能を有する。閾値補正機能とは、駆動トランジスタ152の閾値電圧Vthに相当する電圧を蓄積容量153に保持させる機能であり、これにより、有機ELパネル101の画素毎のバラつきの原因となる駆動トランジスタ152の閾値電圧Vthの影響をキャンセルすることができる。

#### 【0089】

また、画素回路131は、上述した閾値補正機能に加え、移動度補正機能も有する。移動度補正機能とは、蓄積容量153に信号電位Vsigを保持する際、駆動トランジスタ152の移動度 $\mu$ に対する補正を信号電位Vsigに加える機能である。

40

#### 【0090】

さらに、画素回路131は、ブートストラップ機能も備えている。ブートストラップ機能とは、駆動トランジスタ152のソース電位Vsの変動にゲート電位Vgを連動させる機能であり、これにより、駆動トランジスタ152のゲートとソース間の電圧(以下、ゲートソース間電圧と称する)Vgsを一定に維持することが出来る。

#### 【0091】

なお、閾値補正機能、移動度補正機能、及びブートストラップ機能については、後述する図20、図24、及び図25などでも説明する。

#### 【0092】

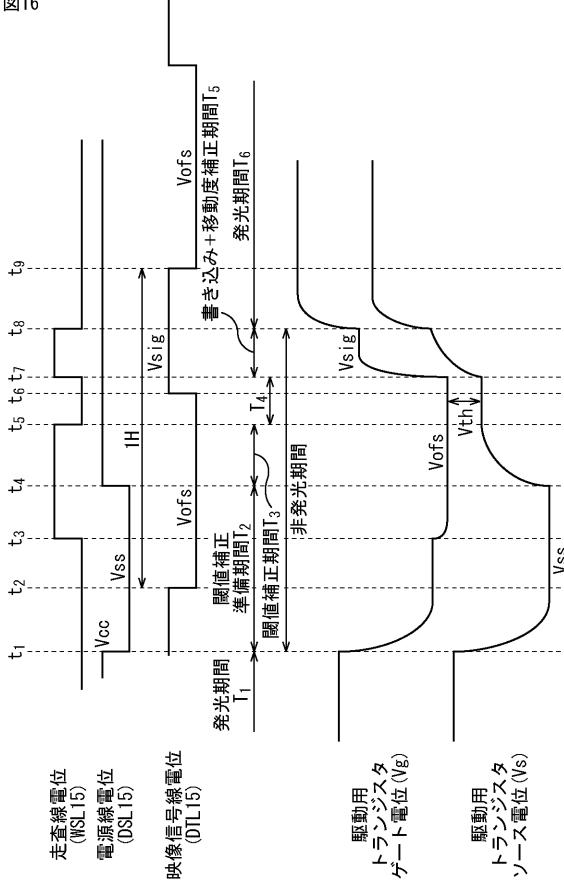

図16は、画素回路131の動作を説明するタイミングチャートである。

#### 【0093】

50

図16は、同一の時間軸(図横方向)に対する走査線W S L 1 5、電源線D S L 1 5、及び信号線D T L 1 5の電位変化と、それに対応する駆動トランジスタ152のゲート電位V<sub>g</sub>及びソース電位V<sub>s</sub>の変化を示している。

#### 【0094】

図16において、時刻t1までの期間は、前の水平期間(1H)の発光がなされている発光期間T1である。

#### 【0095】

発光期間T1が終了した時刻t1から時刻t4までは、駆動トランジスタ152のゲート電位V<sub>g</sub>及びソース電位V<sub>s</sub>を初期化することで閾値補正動作の準備を行う閾値補正準備期間T2である。

10

#### 【0096】

閾値補正準備期間T2では、時刻t1において、ドライブスキャナ13が、電源線D S L 1 5の電位を高電位であるV<sub>c c</sub>から低電位であるV<sub>s s</sub>に切換え、時刻t2において、水平セレクタ14が、信号線D T L 1 5の電位を信号電位V<sub>s i g</sub>から基準電位V<sub>o f s</sub>に切換える。次に、時刻t3において、ライトスキャナ12が、走査線W S L 1 5の電位を高電位に切換え、書き込みトランジスタ151をオンさせる。これにより、駆動トランジスタ152のゲート電位V<sub>g</sub>が基準電位V<sub>o f s</sub>にリセットされ、且つ、ソース電位V<sub>s</sub>が信号線D T L 1 5の低電位V<sub>s s</sub>にリセットされる。

#### 【0097】

時刻t4から時刻t5までは、閾値補正動作を行う閾値補正期間T3である。閾値補正期間T3では、時刻t4において、ドライブスキャナ13により、電源線D S L 1 5の電位が高電位V<sub>c c</sub>に切換えられ、閾値電圧V<sub>t h</sub>に相当する電圧が、駆動トランジスタ152のゲートとソースとの間に接続された蓄積容量153に書き込まれる。

20

#### 【0098】

時刻t5から時刻t7までの書き込み+移動度補正準備期間T4では、走査線W S L 1 5の電位が高電位から低電位一旦切換えられるとともに、時刻t7の前の時刻t6において、水平セレクタ14が、信号線D T L 1 5の電位を基準電位V<sub>o f s</sub>から階調に応じた信号電位V<sub>s i g</sub>に切換える。

#### 【0099】

そして、時刻t7から時刻t8までの書き込み+移動度補正期間T5において、映像信号の書き込みと移動度補正動作が行われる。即ち、時刻t7から時刻t8までの間、走査線W S L 1 5の電位が高電位に設定され、これにより、映像信号の信号電位V<sub>s i g</sub>が閾値電圧V<sub>t h</sub>に足し込まれる形で蓄積容量153に書き込まれると共に、移動度補正用の電圧V<sub>μ</sub>が蓄積容量153に保持された電圧から差し引かれる。

30

#### 【0100】

書き込み+移動度補正期間T5終了後の時刻t8において、走査線W S L 1 5の電位が低電位に設定され、それ以降、発光期間T6として、信号電圧V<sub>s i g</sub>に応じた発光輝度で有機EL素子142が発光する。信号電圧V<sub>s i g</sub>は、閾値電圧V<sub>t h</sub>に相当する電圧と移動度補正用の電圧V<sub>μ</sub>とによって調整されているため、有機EL素子142の発光輝度は駆動トランジスタ152の閾値電圧V<sub>t h</sub>や移動度μのバラつきの影響を受けることがない。

40

#### 【0101】

なお、発光期間T6の最初でブートストラップ動作が行われ、駆動トランジスタ152のゲートソース間電圧V<sub>g s</sub>=V<sub>s i g</sub>+V<sub>t h</sub>-V<sub>μ</sub>を一定に維持したまま、駆動トランジスタ152のゲート電位V<sub>g</sub>及びソース電位V<sub>s</sub>が上昇する。

#### 【0102】

また、時刻t8から所定時間経過後の時刻t9において、信号線D T L 1 5の電位が、信号電位V<sub>s i g</sub>から基準電位V<sub>o f s</sub>に落とされる。図16において、時刻t2から時刻t9までの期間は水平期間(1H)に相当する。

#### 【0103】

以上のようにして、画素回路 131 の構成を有する有機 EL パネル 101 では、駆動トランジスタ 152 の閾値電圧  $V_{th}$  や移動度  $\mu$  のバラつきの影響を受けることがなく、有機 EL 素子 142 を発光させることができる。

【0104】

図 17 乃至 図 25 を参照して、画素回路 131 の動作についてさらに詳細に説明する。

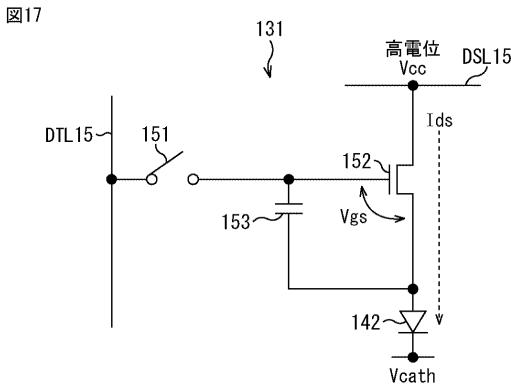

【0105】

図 17 は、発光期間  $T_1$  の画素回路 131 の状態を示している。

【0106】

発光期間  $T_1$  では、書き込みトランジスタ 151 がオフ（走査線  $W_{SL15}$  の電位が低電位）、かつ電源線  $D_{SL15}$  の電位が高電位  $V_{CC}$  となっており、駆動トランジスタ 152 が駆動電流  $I_{ds}$  を有機 EL 素子 142 に供給している。このとき駆動トランジスタ 152 は飽和領域で動作するように設定されているため、有機 EL 素子 142 に流れる駆動電流  $I_{ds}$  は、駆動トランジスタ 152 のゲートソース間電圧  $V_{gs}$  に応じて次式(1)で表される値をとる。

【0107】

【数1】

$$I_{ds} = \frac{1}{2} \mu \frac{W}{L} C_{ox} (V_{gs} - V_{th})^2$$

・・・(1)

10

20

【0108】

式(1)において、 $\mu$  は移動度を示し、 $W$  はゲート幅を表し、 $L$  はゲート長を表し、 $C_{ox}$  は単位面積あたりのゲート酸化膜容量を示す。また、 $V_{gs}$  は、駆動トランジスタ 152 のゲートとソース間の電圧（ゲートソース間電圧）であり、 $V_{th}$  は、駆動トランジスタ 152 の閾値電圧である。なお、飽和領域とは、( $V_{gs} - V_{th} < V_{ds}$ ) の条件を満たした状態をいう ( $V_{ds}$  は、駆動トランジスタ 152 のソースとドレイン間の電圧)。

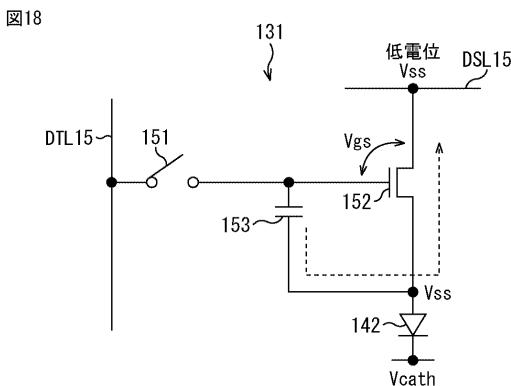

【0109】

そして、閾値補正準備期間  $T_2$  の最初の時刻  $t_1$  において、図 18 に示されるように、ドライブスキャナ 13 は、電源線  $D_{SL15}$  の電位を高電位  $V_{CC}$  (第 1 電位) から低電位  $V_{SS}$  (第 2 電位) に切換える。このとき電源線  $D_{SL15}$  の電位  $V_{SS}$  が有機 EL 素子 142 の閾値電圧  $V_{thel}$  とカソード電位  $V_{cathe}$  の和よりも小さければ ( $V_{SS} < V_{thel} + V_{cathe}$ ) 有機 EL 素子 142 は消光し、駆動トランジスタ 152 の電源線  $D_{SL15}$  と接続された側がソースとなる。また、有機 EL 素子 142 のアノードは電位  $V_{SS}$  に充電される。

30

【0110】

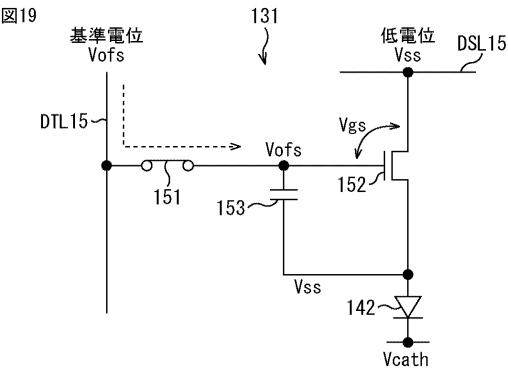

次に、図 19 に示されるように、時刻  $t_2$  において、水平セレクタ 14 が信号線  $D_{TL15}$  の電位を基準電位  $V_{off}$  にした後、時刻  $t_3$  において、ライトスキャナ 12 が、走査線  $W_{SL15}$  の電位を高電位に切換えることより、書き込みトランジスタ 151 をオンにする。これにより、駆動トランジスタ 152 のゲート電位  $V_g$  は  $V_{off}$  となり、ゲートソース間電圧  $V_{gs}$  は、 $V_{off} - V_{SS}$  という値をとる。ここで、駆動トランジスタ 152 のゲートソース間電圧  $V_{gs}$  である ( $V_{off} - V_{SS}$ ) は、次の閾値補正期間  $T_3$  で閾値補正動作を行うため、閾値電圧  $V_{th}$  よりも大である ( $V_{off} - V_{SS} > V_{th}$ ) 必要がある。逆に言うと、( $V_{off} - V_{SS} > V_{th}$ ) の条件を満たすように、電位  $V_{off}$  及び  $V_{SS}$  が設定される。

40

【0111】

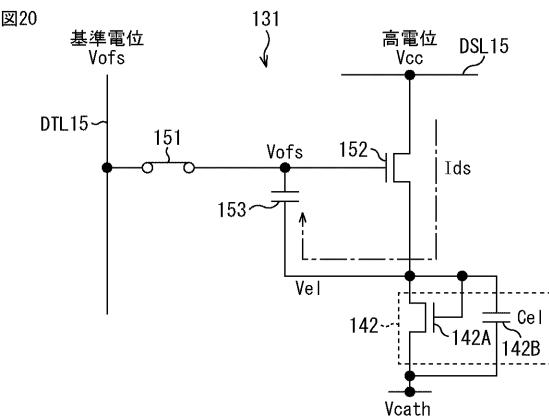

そして、閾値補正期間  $T_3$  の最初の時刻  $t_4$  において、図 20 に示されるように、ドライブスキャナ 13 が電源線  $D_{SL15}$  の電位を低電位  $V_{SS}$  から高電位  $V_{CC}$  に切換えると、駆動トランジスタ 152 の有機 EL 素子 142 のアノードと接続されている側がソースとなり、図 20 において 1 点鎖線で示されるように電流が流れる。

50

## 【0112】

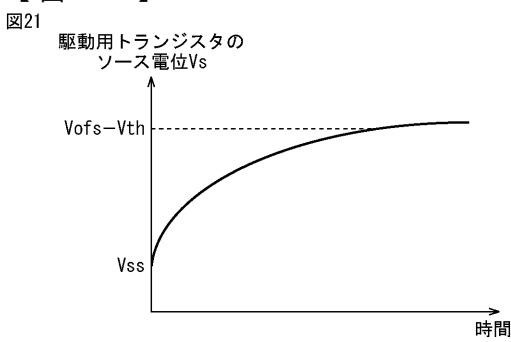

ここで、有機EL素子142は、等価的にダイオード142Aと寄生容量をC<sub>e1</sub>とする有機EL容量142Bで表すことができ、有機EL素子142のリーク電流が駆動トランジスタ152に流れる電流よりもかなり小さい( $V_{e1} - V_{cath} + V_{the1}$ を満たす)という条件の下では、駆動トランジスタ152に流れる電流は蓄積容量153と142Bを充電するために使用される。有機EL素子142のアノード電位V<sub>e1</sub>(駆動トランジスタ152のソース電位V<sub>s</sub>)は、図21に示されるように、駆動トランジスタ152を流れる電流に応じて上昇する。所定時間経過後、駆動トランジスタ152のゲートソース間電圧V<sub>gs</sub>がV<sub>th</sub>という値をとる。また、このときの有機EL素子142のアノード電位V<sub>e1</sub>は( $V_{ofs} - V_{th}$ )である。ここで、有機EL素子142のアノード電位V<sub>e1</sub>は、有機EL素子142の閾値電圧V<sub>the1</sub>とカソード電位V<sub>cath</sub>の和以下となっている( $V_{e1} = (V_{ofs} - V_{th}) - (V_{cath} + V_{the1})$ )。

10

## 【0113】

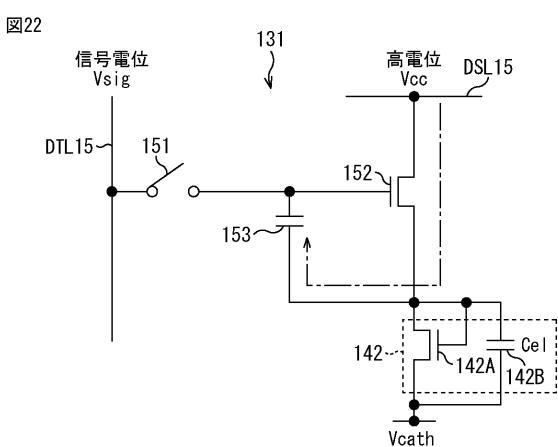

その後、時刻t5において、図22に示されるように、走査線WSL15の電位が高電位から低電位に切替えられ、書き込みトランジスタ151がオフして閾値補正動作(閾値補正期間T3)が完了する。

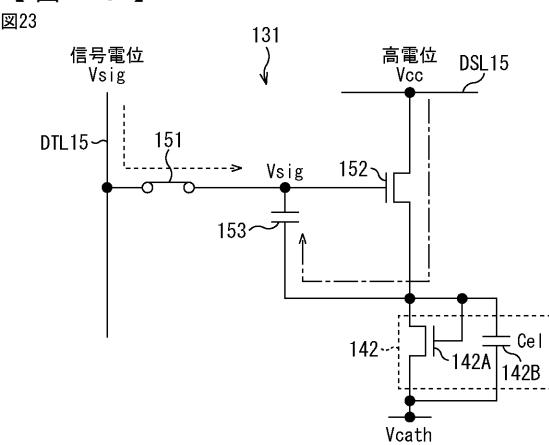

## 【0114】

続く書き込み+移動度補正準備期間T4の時刻t6において、水平セレクタ14によって、信号線DTL15の電位が、基準電位V<sub>ofs</sub>から、階調に応じた信号電位V<sub>sig</sub>に切換えられた(図22)後、書き込み+移動度補正期間T5に入り、図23に示されるように、時刻t7において、走査線WSL15の電位が高電位に設定されることで書き込みトランジスタ151がオンして、映像信号の書き込みと移動度補正動作が行われる。駆動トランジスタ152のゲート電位V<sub>g</sub>は、書き込みトランジスタ151がオンしているため信号電位V<sub>sig</sub>となるが、書き込みトランジスタ151には電源線DSL15からの電流が流れるため、駆動トランジスタ152のソース電位V<sub>s</sub>は、時間とともに上昇していく。

20

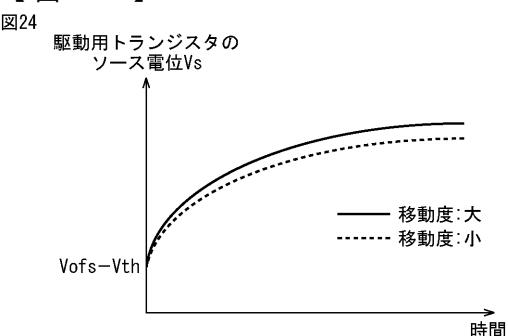

## 【0115】

駆動トランジスタ152の閾値補正動作は既に完了している。よって、式(1)の右辺の( $V_{gs} - V_{th}$ )<sub>2</sub>の項は、( $V_{gs} - V_{th}$ )<sub>2</sub> = {( $V_{sig} - (V_{ofs} - V_{th})$ ) - V<sub>th</sub>}<sub>2</sub> = ( $V_{sig} - V_{ofs}$ )<sub>2</sub>となり、閾値電圧V<sub>th</sub>の項の影響はなくなるので、駆動トランジスタ152が流す駆動電流I<sub>ds</sub>は、移動度μを反映したものとなる。具体的には、図24に示されるように、移動度μが大きい場合には、駆動トランジスタ152が流す駆動電流I<sub>ds</sub>は大きくなり、ソース電位V<sub>s</sub>の上昇も早い。一方、移動度μが小さい場合には、駆動トランジスタ152が流す駆動電流I<sub>ds</sub>は小さくなり、ソース電位V<sub>s</sub>の上昇は遅くなる。換言すると、一定時間経過時点では、移動度μが大きい場合には、駆動トランジスタ152のソース電位V<sub>s</sub>の上昇量V<sub>μ</sub>(電位補正值)は大きくなり、移動度μが小さい場合には、駆動トランジスタ152のソース電位V<sub>s</sub>の上昇量V<sub>μ</sub>(電位補正值)は小さくなる。これによって、各画素回路131の駆動トランジスタ152のゲートソース間電圧V<sub>gs</sub>のバラツキが、移動度μを反映して小さくなり、一定時間経過後の各画素回路131のゲートソース間電圧V<sub>gs</sub>は、移動度μのバラツキを完全に補正した電圧となる。

30

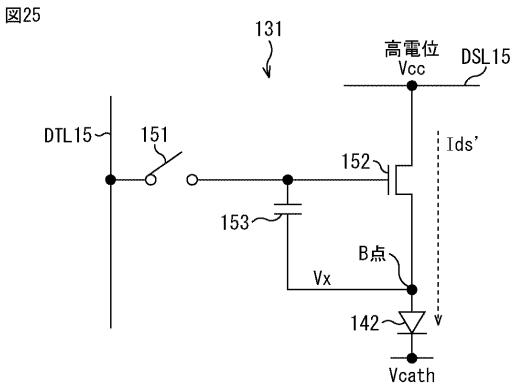

## 【0116】

時刻t8において、走査線WSL15の電位が低電位に設定されることで書き込みトランジスタ151がオフして、書き込み+移動度補正期間T5が終了し、発光期間T6となる(図25)。

40

## 【0117】

発光期間T6では、駆動トランジスタ152のゲートソース間電圧V<sub>gs</sub>は一定であるので、駆動トランジスタ152は一定電流I<sub>ds'</sub>を有機EL素子142に供給し、有機EL素子142のアノード電位V<sub>e1</sub>は、有機EL素子142に一定電流I<sub>ds'</sub>という電流が流れる電圧V<sub>x</sub>まで上昇し、有機EL素子142は発光する。駆動トランジスタ1

50

52のソース電位V<sub>s</sub>が上昇すると、蓄積容量153のブートストラップ機能により、駆動トランジスタ152のゲート電位V<sub>g</sub>も連動して上昇する。

【0118】

有機EL素子142のI-V特性により、発光時間が長くなると、図25に示されるB点の電位は時間とともに変化する（経時劣化する）。しかしながら、駆動トランジスタ152のゲートソース間電圧V<sub>gs</sub>は一定値に保たれているので、有機EL素子142に流れる電流は変化しない。したがって、I-V特性により有機EL素子142が経時劣化しても、一定電流I<sub>ds</sub>が流れ続けるので、有機EL素子142の輝度が変化することはない。

【0119】

このような画素回路131が1つの画素に対して設けられることで、本発明の画素部111は構成されている。例えば、上述した図8の例では、1つの画素に対して、2つの画素回路131-1, 131-2が設けられる。

【0120】

このような図8の画素回路131-1, 131-2のうち、図11に示されるように、発光部位142b-1, 142b-2を含む発光部位層にダストDUが付着したとする。この場合、ダストDUは、非常に小さいものであるから、アノード142a-2のみと接触し、アノード142a-1とは接触していない。

【0121】

よって、ダストDUが接触したアノード142a-2とカソード142c-2との間は電気的にショートを起こすので、有機EL素子142-2は発光しない場合がある。これに対して、ダストDUが接触していないアノード142a-1とカソード142c-1との間は、正常に駆動電流が流れるので、有機EL素子142-1は発光する。従って、画素全体からすると、ダストDUが接触していない場合の輝度に対して半分の輝度になるが、発光することに変わりはないので減点とはならない。

【0122】

しかしながら、ダストDUが付着した画素についての、ダスト付着が接触していない別の画素に対する輝度の低下率は少ない方が好ましい。その分だけ、異常画素として視認されやすい度合いである視認度を低下させることができるからである。

【0123】

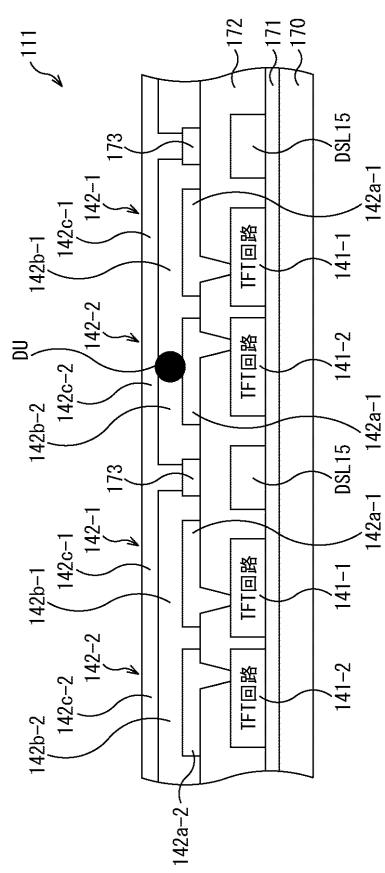

そこで、本発明人は、さらに視認度を低下させる手法として、画素内で分割したアノード同士を蓄積容量で接続する、という手法（以下、アノード間蓄積容量手法と称する）を発した。

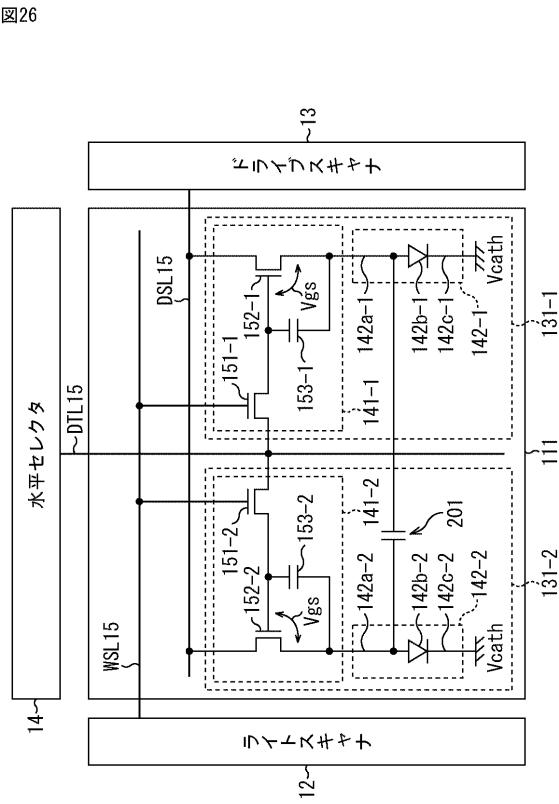

【0124】

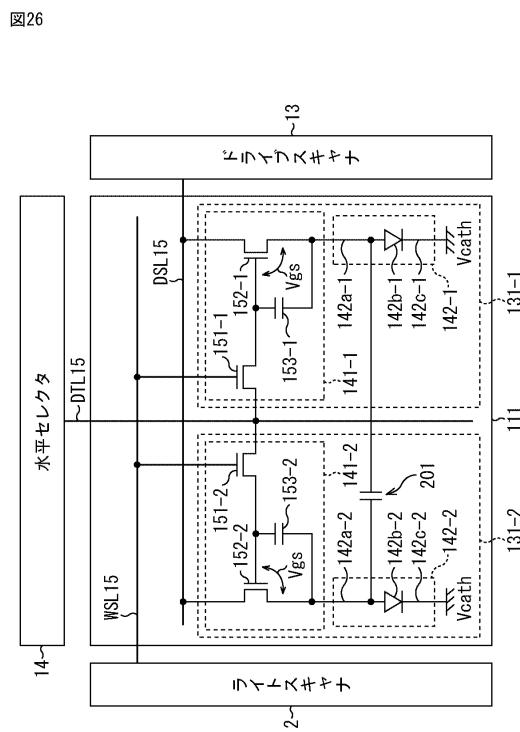

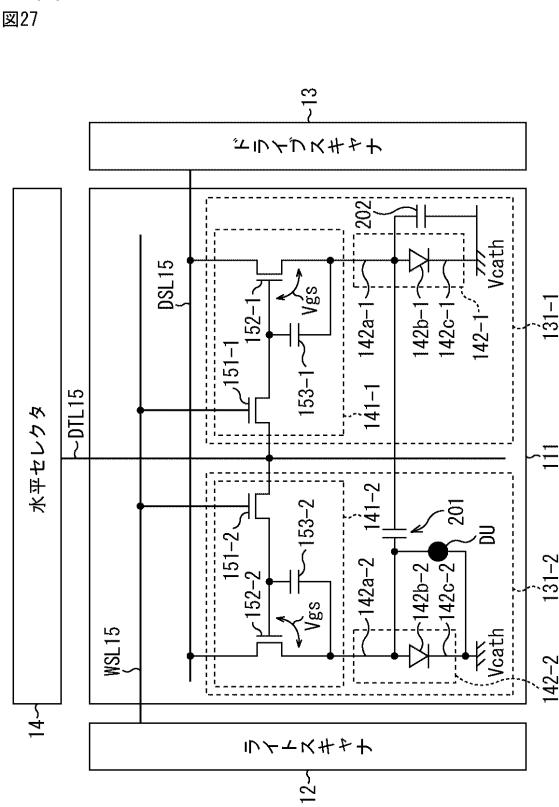

例えば、図8の例の画素回路131-1, 131-2に対して、アノード間蓄積容量手法を採用すると、図26に示されるようになる。即ち、図26の例の構成では、図8の例の構成に対して、画素回路131-1の有機EL素子142-1のアノード142a-1と、画素回路131-2の有機EL素子142-2のアノード142a-2との間に、蓄積容量201が接続されている。

【0125】

この場合、ダストDUが付着していない正常状態（有機EL素子142-1, 142-2が共に発光する状態）では、アノード142-1, 142-2はどちらも同様の動作をするので、蓄積容量201は、有機EL素子142-1, 142-2の発光輝度のどちらにも貢献しない。

【0126】

しかしながら、図11に示されるような場合、即ち、ダストDUがアノード142a-2のみと接触し、アノード142a-1とは接触していない場合、図27に示されるように、アノード142a-1はカソード電位に接地される。よって、ダストDUが付着していない有機EL素子142-1側に、容量202とともに、蓄積容量201が接続されたことと等価になる。これにより、有機EL素子142-1側の入力ゲインが上昇し、移動度補

10

20

30

40

50

正動作もかかりにくくなるので、輝度が上昇する。

【0127】

これにより、ダストDUが接触した画素についての、ダストDUが付着していない別の画素に対する輝度の低下率は少なくなる。よって、視認度をその分だけ低下させることができ。さらに、このようにダストDUが接触していない有機EL素子142-1側の輝度を自動的に上昇させることができるので、外部メモリなどを使用する必要がない。

【0128】

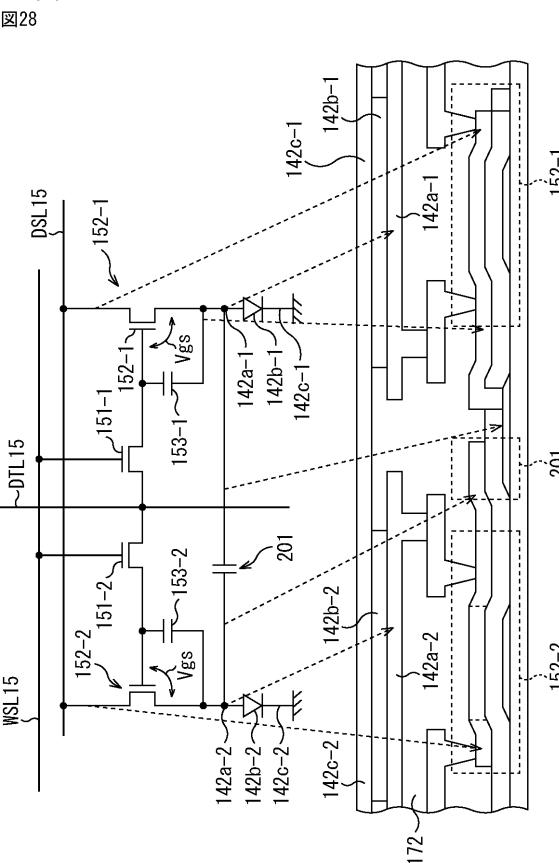

図28は、本発明の画素部111のうち、図26の構成の1つの画素部分についての断面レイアウトの一例を示している。

【0129】

基本的には、図28の例の断面レイアウトでは、図7の例の断面レイアウトに対して、TFT回路141-1（図28の例では、駆動トランジスタ152-1のみが図示）と、TFT回路142-2（図28の例では、駆動トランジスタ152-2のみが図示）との間に、蓄積容量201が配置されている。

【0130】

ところで、図16を用いて説明した画素回路131の動作において、閾値補正期間T3の終了の書き込み+移動度補正準備期間T4は、数 $\mu$ s程度であった。即ち、閾値補正期間T3の終了後数 $\mu$ s程度で、書き込み+移動度補正期間T5が開始され、映像信号の書き込みと移動度補正動作が行われる。

【0131】

ここで、本発明の画素部111として図26の例の構成が採用され、図11に示される状態となっている場合、即ち、ダストDUがアノード142a-2のみと接触し、アノード142a-1とは接触していない場合を考える。

【0132】

この場合、ダストDUが付着している側の画素回路131-2では、閾値補正期間T3のアノード142a-2の電位は、信号線電位（基準電位）Vofs-閾値電圧Vthであり、カソード142c-2の電位Vcathよりも低い。よって、アノード142a-2の電位は、カソード142c-2の電位Vcathに向かって上昇してしまう。

【0133】

この上昇中は、ダストDUが付着していない側（正常な側）の画素回路131-1では、アノード142a-1に接続される蓄積容量201の容量が小さくみえてしまうという結果を生む。その結果、この状態のまま、ダストDUが付着していない側（正常な側）の画素回路131-1で映像信号の書き込みと移動度補正動作が行われると、蓄積容量201の効果、即ち、有機EL画素142-1の輝度上昇の効果は十分に得られないことになる。

【0134】

そこで、本発明人は、さらに、閾値補正動作終了後に、閾値補正期間T3のアノード142a-2の電位をカソード142c-2の電位Vcathまでカソード電位まで完全にリーキさせた状態になったとき、例えば、閾値補正動作終了後に水平期間（1H）だけあけた後、映像信号の書き込みと移動度補正動作を行う、という手法を発明した。

【0135】

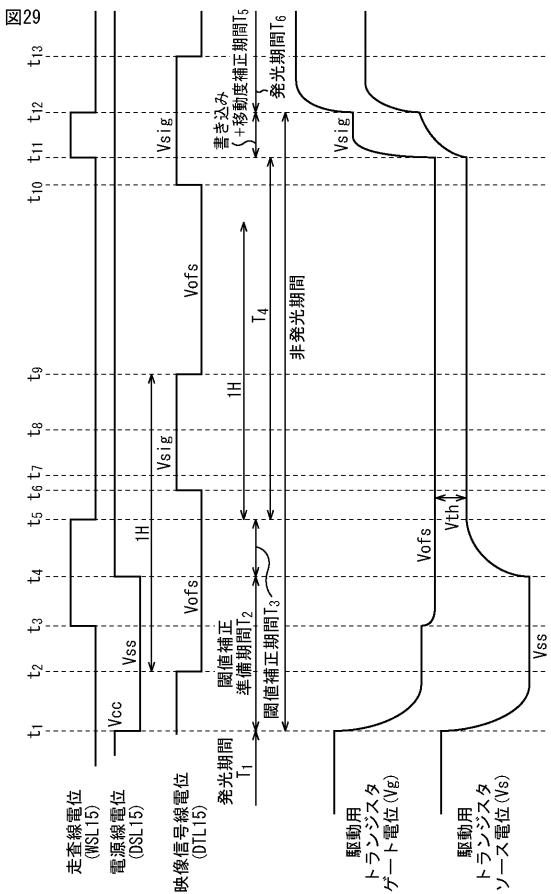

かかる手法を適用した場合の画素回路131の動作を説明するタイミングチャートが図29に示されている。以下の動作は、画素毎に図26の構成を有する本発明の画素部111全体に当てはまる動作である。ただし、本発明の理解を容易なものとすべく、図11に示される状態となっている場合、即ち、ダストDUがアノード142a-2のみと接触し、アノード142a-1とは接触していない場合における、ダストDUが付着していない側の画素回路131-1の動作を想定する。即ち、以下、画素回路131とは、ダストDUが付着している側の画素回路131-2の相手側、即ち、画素回路131-1を想定する。

【0136】

図29は、同一の時間軸（図横方向）に対する走査線WSL15、電源線DSL15、及び信号線DTL15の電位変化と、それに対応する駆動トランジスタ152のゲート電

10

20

30

40

50

位  $V_g$  及びソース電位  $V_s$  の変化を示している。

【0137】

時刻  $t_1$  乃至時刻  $t_5$  まで、即ち、閾値補正期間  $T_3$  が終了するまでの動作は、図 16 の例の動作と同様である。よって、この間の動作の説明は省略する。

【0138】

時刻  $t_5$  から時刻  $t_{11}$ までの書き込み + 移動度補正準備期間  $T_4$  では、走査線  $W_S L 15$  の電位が高電位から低電位一旦切換えるとともに、時刻  $t_{11}$  の前の時刻  $t_{10}$ において、水平セレクタ  $14$  が、信号線  $D_T L 15$  の電位を基準電位  $V_{off}$  から階調に応じた信号電位  $V_{sig}$  に切換える。

【0139】

なお、図 16 の例と同様に、水平セレクタ  $14$  が、時刻  $t_6$ において、信号線  $D_T L 15$  の電位を基準電位  $V_{off}$  から階調に応じた信号電位  $V_{sig}$  に切換える、時刻  $t_9$ において、信号線  $D_T L 15$  の電位を信号電位  $V_{sig}$  から基準電位  $V_{off}$  に再度切り替える。

【0140】

図 16 の例では、この時刻  $t_6$  と時刻  $t_9$  の間の時刻  $t_7$  と時刻  $t_8$ との間に、走査線  $W_S L 15$  の電位が高電位になっている。このため、時刻  $t_7$  と時刻  $t_8$ との間が書き込み + 移動度補正期間  $T_5$ となっていた。

【0141】

しかしながら、図 29 に示されるように、時刻  $t_7$  は、閾値補正期間  $T_3$  が終了してから水平期間 (1H) をまだ経過していない。そこで、図 29 の例では、時刻  $t_6$  乃至  $t_9$  の間も、走査線  $W_S L 15$  の電位は低電位のまま維持され、書き込み + 移動度補正期間  $T_5$  が開始されないようになされている。

【0142】

即ち、図 29 の例では、閾値補正期間  $T_3$  が終了してから水平期間 (1H) を経過したよりも後の時刻  $t_{10}$ になると、上述の如く、信号線  $D_T L 15$  の電位が基準電位  $V_{off}$  から階調に応じた信号電位  $V_{sig}$  に切換える、その後の時刻  $t_{11}$  から時刻  $t_{12}$ までの書き込み + 移動度補正期間  $T_5$ において、映像信号の書き込みと移動度補正動作が行われる。即ち、時刻  $t_{11}$  から時刻  $t_{12}$ までの間、走査線  $W_S L 15$  の電位が高電位に設定され、これにより、映像信号の信号電位  $V_{sig}$  が閾値電圧  $V_{th}$  に足し込まれる形で蓄積容量  $153$  に書き込まれると共に、移動度補正用の電圧  $V_\mu$  が蓄積容量  $153$  に保持された電圧から差し引かれる。

【0143】

書き込み + 移動度補正期間  $T_5$  終了後の時刻  $t_{12}$ において、走査線  $W_S L 15$  の電位が低電位に設定され、それ以降、発光期間  $T_6$ として、信号電圧  $V_{sig}$  に応じた発光輝度で有機 EL 素子  $142$  が発光する。信号電圧  $V_{sig}$  は、閾値電圧  $V_{th}$  に相当する電圧と移動度補正用の電圧  $V_\mu$  によって調整されているため、有機 EL 素子  $142$  の発光輝度は駆動トランジスタ  $152$  の閾値電圧  $V_{th}$  や移動度  $\mu$  のバラつきの影響を受けることがない。

【0144】

さらに、ダストDUが付着していない有機 EL 素子  $142$  (図 27 の例では有機 EL 素子  $142-1$ ) に、容量  $202$  とともに、蓄積容量  $201$  が接続されたことと等価になっているので、有機 EL 素子  $142$  の入力ゲインが上昇し、移動度補正動作もかかりにくくなるので、輝度がさらに上昇することになる。

【0145】

なお、図 26 乃至図 29 の説明では、理解を容易なものとすべく上述した他の例とあわせたため、1つの画素のアノードの分割数  $K$  は 2 とされた。しかしながら、アノードの分割数  $K$  は、2 に限定されず、3 以上であっても、上述した各種内容は同様にあてはまる。

【0146】

以上のように、画素回路  $131$  を備える有機 EL パネルにおいては、閾値補正機能及び

10

20

30

40

50

移動度補正機能によって画素回路 131ごとの閾値電圧  $V_{th}$  及び移動度  $\mu$  の相違を補正することができる。また、有機EL素子 142の経時変動(劣化)も補正することができる。

#### 【0147】

これにより、画素回路 131を備える有機ELパネルを用いた表示装置では、高品位な画質を得ることが可能である。有機ELパネルを用いた表示装置とは、例えば次のような装置をいう。即ち、有機ELパネルに、ソースドライバやゲートドライバを含むドライバ I C (Integrated Circuit)が付加されることによりパネルモジュールが構成される。さらに、パネルモジュールに、電源回路、画像 L S I (Large Scale Integration)などが付加されて、表示装置が構成される。

10

#### 【0148】

有機ELパネルを用いた表示装置は、様々な電子機器、例えば、デジタルスチルカメラやデジタルビデオカメラ、ノート型パーソナルコンピュータ、携帯電話、テレビジョン受像機など、電子機器に入力された、若しくは、電子機器内で生成した映像信号を画像若しくは映像として表示するあらゆる分野の電子機器のディスプレイに適用することが可能である。以下この様な表示装置が適用された電子機器の例を示す。

#### 【0149】

例えば、本発明は、電子機器の一例であるテレビジョン受像機に適用できる。このテレビジョン受像機は、フロントパネル、フィルターガラス等から構成される映像表示画面を含み、本発明の表示装置をその映像表示画面に用いることにより作製される。

20

#### 【0150】

例えば、本発明は、電子機器の一例であるデジタルスチルカメラに適用できる。このデジタルカメラは、撮像レンズ、表示部、コントロールスイッチ、メニュースイッチ、シャッター等を含み、本発明の表示装置をその表示部に用いることにより作製される。

#### 【0151】

例えば、本発明は、電子機器の一例であるノート型パーソナルコンピュータに適用できる。このノート型パーソナルコンピュータにおいて、その本体には文字等を入力するとき操作されるキー ボードを含み、その本体カバーには画像を表示する表示部を含む。このノート型パーソナルコンピュータは、本発明の表示装置をその表示部に用いることにより作製される。

30

#### 【0152】

例えば、本発明は、電子機器の一例である携帯端末装置に適用できる。この携帯端末装置は、上部筐体と下部筐体とを有している。この携帯端末装置の状態としては、それらの2つの筐体が開いた状態と、閉じた状態とが存在する。この携帯端末装置は、上述した上側筐体と下側筐体との他、連結部(ここではヒンジ部)、ディスプレイ、サブディスプレイ、ピクチャーライト、カメラ等を含み、本発明の表示装置をそのディスプレイやサブディスプレイに用いることにより作製される。

#### 【0153】

例えば、本発明は、電子機器の一例であるデジタルビデオカメラに適用可能である。デジタルビデオカメラは、本体部、前方を向いた側面に被写体撮影用のレンズ、撮影時のスタート/ストップスイッチ、モニター等を含み、本発明の表示装置をそのモニターに用いることにより作製される。

40

#### 【0154】

なお、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

#### 【図面の簡単な説明】

#### 【0155】

【図1】従来の有機ELパネルの構成例を示すブロック図である。

【図2】従来の画素部11の構成を示すブロック図である。

【図3】各色(R, G, B)の画素の画素回路31のうちのひとつの構成例を示したブロ

50

ック図である。

【図4】従来の画素部11の断面レイアウトの一例を示す図である。

【図5】ダストDUが付着した場合の従来の画素部11の断面レイアウトの一例を示す図である。

【図6】従来の画素部11を構成する1つの画素回路31の画素が発光しない状態を示す図である。

【図7】本発明の画素部111の断面レイアウトの一例を示す図である。

【図8】本発明の画素部111において、1つの画素に対して設けられた2つの画素回路131-1, 131-2の構成の一例を示すブロック図である。

【図9】本発明の画素部111を構成する各色画素の画素回路の一例を示すブロック図である。 10

【図10】分割アノード膜MLの平面レイアウトの一例を示す図である。

【図11】ダストDUが付着した場合の本発明の画素部11の断面レイアウトの一例を示す図である。

【図12】本発明の画素部111を構成する1つの画素回路131が発光しない状態を示す図である。

【図13】RGB画素群のレイアウト構成の一例を示す図である。

【図14】有機EL素子のレイアウト構成の一例を示す図である。

【図15】TFT回路のレイアウト構成の一例を示す図である

【図16】図8の画素回路131の動作を説明するタイミングチャートである。 20

【図17】図8の画素回路131の動作について詳細に説明する図である。

【図18】図8の画素回路131の動作について詳細に説明する図である。

【図19】図8の画素回路131の動作について詳細に説明する図である。

【図20】図8の画素回路131の動作について詳細に説明する図である。

【図21】駆動トランジスタ152のソース電位Vsの時間変化を示す図である。

【図22】図8の画素回路131の動作について詳細に説明する図である。

【図23】図8の画素回路131の動作について詳細に説明する図である。

【図24】駆動トランジスタ152のソース電位Vsの時間変化を示す図である。

【図25】図8の画素回路131の動作について詳細に説明する図である。

【図26】本発明の画素部111において、1つの画素に対して設けられた2つの画素回路131-1, 131-2の構成の一例であって、図8とは異なる構成例を示すブロック図である。 30

【図27】図26の2つの画素回路131-1, 131-2のうち、画素回路131-2側にダストが付着した場合の等価回路を構成の示すブロック図である。

【図28】図26の構成を有する本発明の画素部111の断面レイアウトの一例を示す図である。

【図29】図26の構成を有する画素回路131の動作を説明するタイミングチャートである。

#### 【符号の説明】

【0156】

1 有機ELパネル, 11 画素部, 12 ライトスキャナ, 13 ドライブス

キヤナ, 14 水平セレクタ, WSL15 走査線, DSL15 電源線, DT

L15 信号線, 31 画素回路, 41 TFT回路, 42 有機EL素子, 4

2a アノード, 42b 発光部位, 42c カソード, 101 有機ELパネル

, 111 画素部, 131-1 及び 131-2 画素回路, 141-1 及び 141

-2 TFT回路, 142-1 及び 142-2 有機EL素子, 142a アノード

, 142b-1 及び 142b-2 発光部位, 142c カソード, 201 蓄積

容量 40

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図8】

図8

【図7】

図7

【図9】

【図11】

【 図 1 0 】

【図12】

【図 1 3】

図13

【図 1 5】

図15

【図 1 4】

図14

【図 1 6】

図16

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図 29】

---

フロントページの続き

(51)Int.Cl. F I テーマコード(参考)

H 05 B 33/14 A

F ターム(参考) 5C080 AA06 BB05 CC03 DD01 EE28 EE30 FF07 FF11 HH09 JJ02

JJ03 JJ04 JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 面板和电子电路                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2010113260A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2010-05-20 |

| 申请号            | JP2008287383                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2008-11-10 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 山下淳一<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 山下淳一<br>内野勝秀                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/20 G09G3/30 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/20.624.B G09G3/30.J G09G3/20.680.G G09G3/20.670.A G09G3/20.641.P H05B33/14.A<br>G09G3/3233 G09G3/3266 G09G3/3275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC26 3K107/EE03 3K107/EE07 3K107/HH05 5C080/AA06 5C080/<br>/BB05 5C080/CC03 5C080/DD01 5C080/EE28 5C080/EE30 5C080/FF07 5C080/FF11 5C080/HH09<br>5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/AB22<br>5C380/AB23 5C380/AB34 5C380/AB41 5C380/AB42 5C380/AC07 5C380/AC08 5C380/AC09 5C380/<br>/AC11 5C380/AC12 5C380/BA28 5C380/BA29 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BD02<br>5C380/CA08 5C380/CB01 5C380/CB26 5C380/CC02 5C380/CC03 5C380/CC04 5C380/CC06 5C380/<br>/CC07 5C380/CC26 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC62 5C380/CC77 5C380/CD012<br>5C380/CD022 5C380/CE01 5C380/DA02 5C380/DA06 5C380/DA47 5C380/HA03 5C380/HA05 5C380/<br>/HA06 5C380/HA12 5C380/HA13 |         |            |

| 代理人(译)         | 西川孝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

要解决的问题：防止由于灰尘粘附导致的像素点亮。 ŽSOLUTION：在以矩阵形式排列的多个像素中的每一个中，像素部分111包括具有两个阳极142a-1和142a-2并通过驱动发光的有机EL元件142-1,142-2。电流，TFT电路141-1和141-2分别向两个阳极142a-1和142a-2提供驱动电流，以及连接两个阳极142a-1,142a-2的累积电容201。 Ž