(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-233287

(P2007-233287A)

(43) 公開日 平成19年9月13日(2007.9.13)

| (51) Int.CI.                | F 1                  | テーマコード (参考) |

|-----------------------------|----------------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J 3K107    |             |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 624B 5C080 |             |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 642A       |             |

|                             | G09G 3/20 611H       |             |

|                             | H05B 33/14 A         |             |

審査請求 未請求 請求項の数 6 O L (全 15 頁)

|           |                            |          |                                                   |

|-----------|----------------------------|----------|---------------------------------------------------|

| (21) 出願番号 | 特願2006-58114 (P2006-58114) | (71) 出願人 | 302020207<br>東芝松下ディスプレイテクノロジー株式会社<br>東京都港区港南4-1-8 |

| (22) 出願日  | 平成18年3月3日 (2006.3.3)       | (74) 代理人 | 100058479<br>弁理士 鈴江 武彦                            |

|           |                            | (74) 代理人 | 100091351<br>弁理士 河野 哲                             |

|           |                            | (74) 代理人 | 100088683<br>弁理士 中村 誠                             |

|           |                            | (74) 代理人 | 100108855<br>弁理士 蔵田 昌俊                            |

|           |                            | (74) 代理人 | 100075672<br>弁理士 峰 隆司                             |

最終頁に続く

(54) 【発明の名称】表示装置、アレイ基板、及び表示装置の駆動方法

## (57) 【要約】

【課題】画素に映像信号として電流信号を供給する表示装置において、低階調画像を表示した場合に表示ムラが発生する。

【解決手段】画素PXは、制御端子と電源端子ND<sub>ps</sub>1に接続された第1端子とそれらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子DRと、表示素子OLEDと、第2端子と電源端子ND<sub>ps</sub>2との間で表示素子OLEDと直列に接続されたスイッチSWaと、第2端子と制御端子と映像信号線DLとの接続をそれらが互いに接続された状態とそれらが互いから切離された状態との間で切り替え可能なスイッチ群SWb, SWcと、一方の電極が制御端子に接続されたキャパシタCと、キャパシタCの他方の電極と定電位端子ND<sub>cp</sub>1との間に接続されたスイッチSWeと、キャパシタCの他方の電極と定電位端子ND<sub>cp</sub>2との間に接続されたスイッチSWdとを具備する。

【選択図】 図2

図2

**【特許請求の範囲】****【請求項 1】**

マトリクス状に配列した複数の画素と、前記複数の画素が形成する列に対応して配列した複数の映像信号線とを具備し、前記複数の画素の各々は、

制御端子と、第1電源端子に接続された第1端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子と、

表示素子と、

前記第2端子と第2電源端子との間で前記表示素子と直列に接続された出力制御スイッチと、

前記第2端子と前記制御端子と前記映像信号線との接続をそれらが互いに接続された第1状態とそれらが互いから切断された第2状態との間で切り替え可能なスイッチ群と、

一方の電極が前記制御端子に接続されたキャパシタと、

前記キャパシタの他方の電極と第1定電位端子との間に接続された第1電位シフトスイッチと、

前記キャパシタの前記他方の電極と前記第1定電位端子とは異なる電位に設定可能な第2定電位端子との間に接続された第2電位シフトスイッチとを具備したことを特徴とする表示装置。

**【請求項 2】**

定電位線をさらに具備し、前記第1定電位端子は前記第1電源端子に接続され、前記第2定電位端子は前記定電位線に接続されたことを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記スイッチ群は、前記第2端子と前記映像信号線との間に接続された選択用スイッチと、前記第2端子と前記制御端子との間に接続されたダイオード接続スイッチとを含んだことを特徴とする請求項1に記載の表示装置。

**【請求項 4】**

前記発光素子は有機EL素子であることを特徴とする請求項1に記載の表示装置。

**【請求項 5】**

マトリクス状に配列した複数の画素回路と、前記複数の画素回路が形成する列に対応して配列した複数の映像信号線とを具備し、前記複数の画素回路の各々は、

制御端子と、電源端子に接続された第1端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子と、

画素電極と、

前記第2端子と前記画素電極との間に接続された出力制御スイッチと、

前記第2端子と前記制御端子と前記映像信号線との接続をそれらが互いに接続された第1状態とそれらが互いから切断された第2状態との間で切り替え可能なスイッチ群と、

一方の電極が前記制御端子に接続されたキャパシタと、

前記キャパシタの他方の電極と第1定電位端子との間に接続された第1電位シフトスイッチと、

前記キャパシタの前記他方の電極と前記第1定電位端子とは異なる電位に設定可能な第2定電位端子との間に接続された第2電位シフトスイッチとを具備したことを特徴とするアレイ基板。

**【請求項 6】**

請求項1に記載の表示装置を駆動する方法であって、

前記複数の画素を行毎に順次選択し、選択した行が含む複数の画素の各々では書き動作を実施し、非選択の行が含む複数の画素の各々では表示動作を実施し、

前記書き動作は、前記出力制御スイッチ及び前記第1電位シフトスイッチを開くと共に前記第2電位シフトスイッチを閉じ且つ前記スイッチ群を前記第1状態としている間に前記第1電源端子と前記映像信号線との間に電流信号としての映像信号を流し、その後、前記スイッチ群を前記第1状態から前記第2状態へと切り替え、これと同時又はその後に前記第2電位シフトスイッチを開き、その後、前記第1電位シフトスイッチを閉じることを

10

20

30

40

50

含み、

前記表示動作は、前記第1電位シフトスイッチを閉じると共に前記第2電位シフトスイッチを開き且つ前記スイッチ群を前記第2状態としている間に前記出力制御スイッチを閉じて、前記表示素子に前記駆動電流を流すことを含み、

前記駆動制御素子が前記制御端子と前記第1端子との電位差をより小さくすることにより前記駆動電流の大きさをより大きくする場合には前記第1定電位端子の電位を前記第2定電位端子の電位と比較してより高くし、前記駆動制御素子が前記制御端子と前記第1端子との電位差をより大きくすることにより前記駆動電流の大きさをより大きくする場合には前記第1定電位端子の電位を前記第2定電位端子の電位と比較してより低くすることを特徴とする駆動方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置、アレイ基板、及び表示装置の駆動方法に関する。

【背景技術】

【0002】

有機エレクトロルミネッセンス(EL)表示装置のように発光素子の光学特性をそれに流す駆動電流によって制御する表示装置では、駆動電流がばらつくと、輝度むら等の画質不良が生じる。それゆえ、そのような表示装置でアクティブマトリクス駆動方式を採用した場合には、駆動電流の大きさを制御する駆動制御素子の特性が各画素間でほぼ同一であることが要求される。しかしながら、この表示装置では、通常、駆動制御素子をガラス基板などの絶縁体上に形成するため、その特性にばらつきを生じ易い。

20

【0003】

以下の特許文献1には、画素回路がカレントミラー回路を含んだ有機EL表示装置が記載されている。

【0004】

この画素回路は、駆動制御素子であるnチャネル電界効果トランジスタと、有機EL素子と、キャパシタとを含んでいる。nチャネル電界効果トランジスタのソースは低電位の電源線に接続されており、キャパシタはnチャネル電界効果トランジスタのゲートと先の電源線との間に接続されている。また、有機EL素子の陽極は、より高電位の電源線に接続されている。

30

【0005】

この画素回路は、以下の方法で駆動する。

まず、nチャネル電界効果トランジスタのドレインとゲートとを接続し、この状態でnチャネル電界効果トランジスタのドレイン-ソース間に映像信号に対応した大きさの電流 $I_{sig}$ を流す。この動作により、キャパシタの両電極間の電圧は、nチャネル電界効果トランジスタのチャネルに電流 $I_{sig}$ を流すのに必要なゲート-ソース間電圧に設定される。

【0006】

次に、nチャネル電界効果トランジスタのドレインとゲートとの接続を断ち、キャパシタの両電極間の電圧を保持する。続いて、nチャネル電界効果トランジスタのドレインを有機EL素子の陰極に接続する。これにより、有機EL素子には、先の電流 $I_{sig}$ とほぼ等しい大きさの駆動電流 $I_{drv}$ が流れる。有機EL素子は、この駆動電流 $I_{drv}$ の大きさに対応した輝度で発光する。

40

【0007】

このように、上記の構成を採用すると、書込期間において映像信号として供給した電流 $I_{sig}$ とほぼ等しい大きさの駆動電流 $I_{drv}$ を、書込期間に続く表示期間においてもnチャネル電界効果トランジスタのドレインとソースとの間に流すことができる。それゆえ、nチャネル電界効果トランジスタの閾値 $V_{th}$ だけでなく移動度や寸法などが駆動電流 $I_{drv}$ に与える影響も排除することができる。

50

**【0008】**

しかしながら、上記の表示装置には、小さな駆動電流  $I_{drv}$  に対応した映像信号  $I_{sig}$  の書き込みが難しいという問題がある。そのため、この表示装置では、低階調画像を表示した場合に表示ムラが発生し易い。

**【特許文献1】米国特許第6373454号明細書****【発明の開示】****【発明が解決しようとする課題】****【0009】**

本発明の目的は、画素に映像信号として電流信号を供給する表示装置において、低階調画像を表示した場合に表示ムラが発生するのを防止することにある。

10

**【課題を解決するための手段】****【0010】**

本発明の第1側面によると、マトリクス状に配列した複数の画素と、前記複数の画素が形成する列に対応して配列した複数の映像信号線とを具備し、前記複数の画素の各々は、制御端子と、第1電源端子に接続された第1端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子と、表示素子と、前記第2端子と第2電源端子との間で前記表示素子と直列に接続された出力制御スイッチと、前記第2端子と前記制御端子と前記映像信号線との接続をそれらが互いに接続された第1状態とそれらが互いから切断された第2状態との間で切り替え可能なスイッチ群と、一方の電極が前記制御端子に接続されたキャパシタと、前記キャパシタの他方の電極と第1定電位端子との間に接続された第1電位シフトスイッチと、前記キャパシタの前記他方の電極と前記第1定電位端子とは異なる電位に設定可能な第2定電位端子との間に接続された第2電位シフトスイッチとを具備したことを特徴とする表示装置が提供される。

20

**【0011】**

本発明の第2側面によると、マトリクス状に配列した複数の画素回路と、前記複数の画素回路が形成する列に対応して配列した複数の映像信号線とを具備し、前記複数の画素回路の各々は、制御端子と、電源端子に接続された第1端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子と、画素電極と、前記第2端子と前記画素電極との間に接続された出力制御スイッチと、前記第2端子と前記制御端子と前記映像信号線との接続をそれらが互いに接続された第1状態とそれらが互いから切断された第2状態との間で切り替え可能なスイッチ群と、一方の電極が前記制御端子に接続されたキャパシタと、前記キャパシタの他方の電極と第1定電位端子との間に接続された第1電位シフトスイッチと、前記キャパシタの前記他方の電極と前記第1定電位端子とは異なる電位に設定可能な第2定電位端子との間に接続された第2電位シフトスイッチとを具備したことを特徴とするアレイ基板が提供される。

30

**【0012】**

本発明の第3側面によると、第1側面に係る表示装置を駆動する方法であって、前記複数の画素を行毎に順次選択し、選択した行が含む複数の画素の各々では書き動作を実施し、非選択の行が含む複数の画素の各々では表示動作を実施し、前記書き動作は、前記出力制御スイッチ及び前記第1電位シフトスイッチを開くと共に前記第2電位シフトスイッチを閉じ且つ前記スイッチ群を前記第1状態としている間に前記第1電源端子と前記映像信号線との間に電流信号としての映像信号を流し、その後、前記スイッチ群を前記第1状態から前記第2状態へと切り替え、これと同時に前記第2電位シフトスイッチを開き且つ前記スイッチ群を前記第2状態としている間に前記出力制御スイッチを開じて、前記表示素子に前記駆動電流を流すことを含み、前記駆動制御素子が前記制御端子と前記第1端子との電位差をより小さくすることにより前記駆動電流の大きさをより大きくする場合には前記第1定電位端子の電位を前記第2定電位端子の電位と比較してより高くし、前記駆動制御素子が前記制御端子と前記第1端子との電位差をより大きくすることにより前記駆動電流の大

40

50

きさをより大きくする場合には前記第1定電位端子の電位を前記第2定電位端子の電位と比較してより低くすることを特徴とする駆動方法が提供される。

【発明の効果】

【0013】

本発明によると、画素に映像信号として電流信号を供給する表示装置において、低階調画像を表示した場合に表示ムラが発生するのを防止することが可能となる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の態様について、図面を参照しながら詳細に説明する。なお、各図において、同様又は類似した機能を発揮する構成要素には同一の参照符号を付し、重複する説明は省略する。

10

【0015】

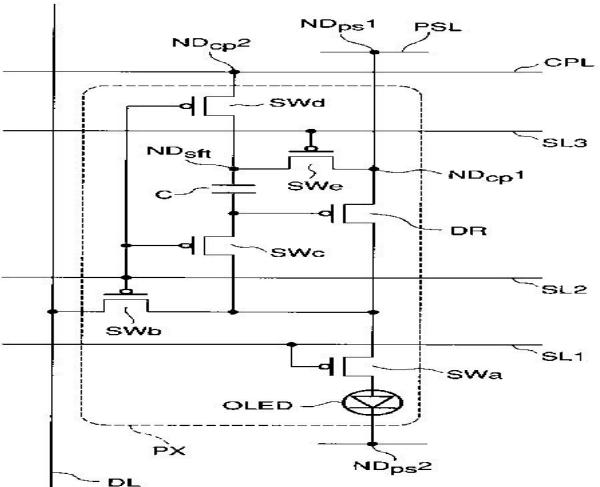

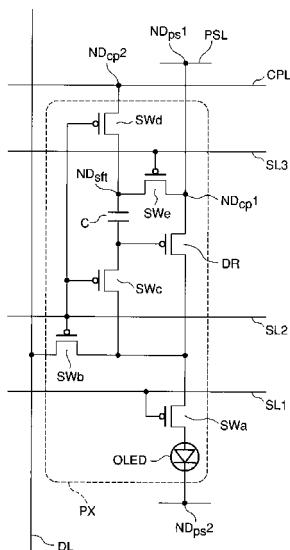

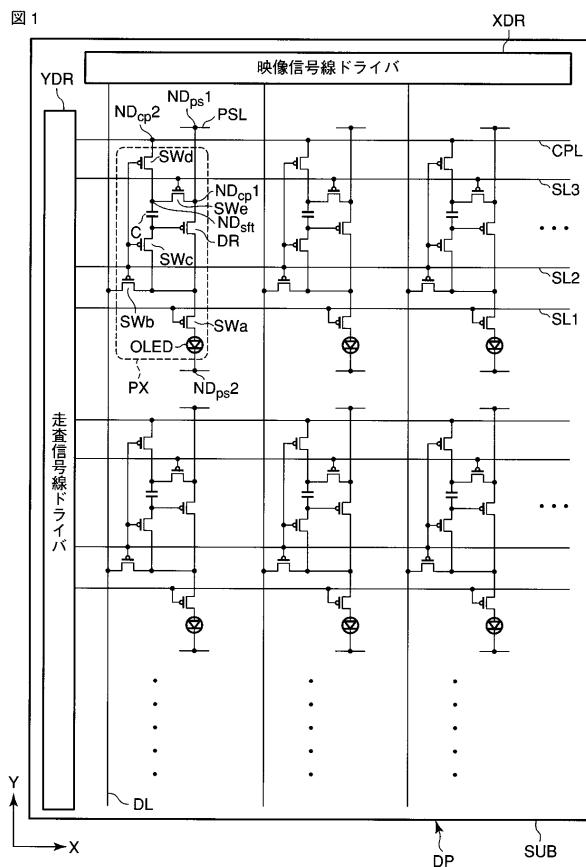

図1は、本発明の一態様に係る表示装置を概略的に示す平面図である。図2は、図1の表示装置が含む画素の等価回路図である。

【0016】

この表示装置は、アクティブマトリクス型駆動方式を採用した表示装置である。この表示装置は、表示パネルDPと、映像信号線ドライバXDRと、走査信号線ドライバYDRと、図示しないコントローラとを含んでいる。

【0017】

表示パネルDPは、例えば、ガラス基板などの絶縁基板SUBを含んでいる。絶縁基板SUB上では、画素PXがマトリクス状に配列している。各画素PXの構成については、後で説明する。

20

【0018】

絶縁基板SUB上には、さらに、映像信号線DLと、走査信号線SL1乃至SL3と、電源線PSLと、定電位線CPLとが配置されている。

【0019】

映像信号線DLは、各々が画素PXが形成する列に沿ったY方向に延びており、画素PXが形成する行に沿ったX方向に及びこれら行に対応して配列している。映像信号線DLは、映像信号線ドライバXDRに接続されている。

【0020】

走査信号線SL1は、各々がX方向に延びてあり、画素PXが形成する行に対応してY方向に配列している。走査信号線SL2は、各々がX方向に延びてあり、画素PXが形成する行に対応してY方向に配列している。走査信号線SL3は、各々がX方向に延びてあり、画素PXが形成する行に対応してY方向に配列している。走査信号線SL1乃至SL3は、走査信号線ドライバYDRに接続されている。

30

【0021】

電源線PSLは、画素PXに電力を供給する。電源線PSLの配置は任意であり、例えば、画素PXが形成する列に対応して配置するか、又は、画素PXが形成する行に対応して配置することができる。前者の場合、電源線PSLは、映像信号線ドライバXDRに接続してもよい。後者の場合、電源線PSLは、走査信号線ドライバYDRに接続してもよい。本態様では、電源線PSLは、画素PXが形成する列に対応して配置し、映像信号線ドライバXDRに接続することとする。

40

【0022】

定電位線CPLは、画素PXに定電位を供給する。定電位線CPLの配置は任意であり、例えば、画素PXが形成する行に対応して配置するか、又は、画素PXが形成する列に対応して配置することができる。前者の場合、定電位線CPLは、映像信号線ドライバXDRに接続してもよい。後者の場合、定電位線CPLは、走査信号線ドライバYDRに接続してもよい。本態様では、定電位線CPLは、画素PXが形成する行に対応して配置し、走査信号線ドライバYDRに接続している。

【0023】

10

20

30

40

50

各画素 P X は、駆動制御素子 D R と、発光素子 O L E D と、出力制御スイッチ S W a と、選択用スイッチ S W b と、ダイオード接続スイッチ S W c と、キャパシタ C と、第 1 電位シフトスイッチ S W e と、第 2 電位シフトスイッチ S W d とを含んでいる。

#### 【 0 0 2 4 】

駆動制御素子 D R は、制御端子と、第 1 電源端子 N D<sub>p,s</sub> 1 に接続された第 1 端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第 2 端子とを含んでいる。駆動制御素子 D R は、電界効果トランジスタなどのトランジスタを 1 つ又は複数含んでいる。本態様では、駆動制御素子 D R として p チャネル薄膜トランジスタを使用しており、そのソースは電源端子 N D<sub>p,s</sub> 1 に接続している。

#### 【 0 0 2 5 】

発光素子 O L E D は、例えば、有機 E L 素子、無機 E L 素子、発光ダイオードである。本態様では、発光素子 O L E D として、画素電極と対向電極とそれらの間に介在した活性層とを含んだ有機 E L 素子を使用している。また、本態様では、画素電極及び対向電極をそれぞれ陽極及び陰極とし、対向電極は第 1 電源端子 N D<sub>p,s</sub> 1 と比較してより低い電位に設定される第 2 電源端子 N D<sub>p,s</sub> 2 に接続している。

#### 【 0 0 2 6 】

出力制御スイッチ S W a は、駆動制御素子 D R の第 2 端子と第 2 電源端子 N D<sub>p,s</sub> 2との間で表示素子 O L E D と直列に接続されている。出力制御スイッチ S W a は、駆動制御素子 D R と表示素子 O L E Dとの間に接続してもよく、或いは、表示素子 O L E D と電源端子 N D<sub>p,s</sub> 2 との間に接続してもよい。この出力制御スイッチ S W a のスイッチング動作は、走査信号線ドライバ Y D R から走査信号線 S L 1 を介して供給される走査信号によって制御される。

#### 【 0 0 2 7 】

出力制御スイッチ S W a としては、例えは、1 つ又は複数のトランジスタ、特には電界効果トランジスタ、を使用することができる。本態様では、出力制御スイッチ S W a として p チャネル薄膜トランジスタを使用しており、そのソースは駆動制御素子 D R のドレインに接続し、ドレインは表示素子 O L E D の画素電極に接続し、ゲートは走査信号線 S L 1 に接続している。

#### 【 0 0 2 8 】

選択用スイッチ S W b 及びダイオード接続スイッチ S W c は、映像信号線 D L と駆動制御素子 D R の第 2 端子と制御端子との接続をそれらが互いに接続された第 1 状態とそれらが互いから切断された第 2 状態との間で切り替え可能なスイッチ群を構成している。本態様では、選択用スイッチ S W b は駆動制御素子 D R の第 2 端子と映像信号線 D L との間に接続し、ダイオード接続スイッチ S W c は駆動制御素子 D R の第 2 端子と制御端子との間に接続している。その代わりに、選択用スイッチ S W b を映像信号線 D L と駆動制御素子 D R の制御端子との間に接続し、且つ、ダイオード接続スイッチ S W c を駆動制御素子 D R の第 2 端子と制御端子との間に接続してもよい。或いは、選択用スイッチ S W b を駆動制御素子 D R の第 2 端子と映像信号線 D L との間に接続し、且つ、ダイオード接続スイッチ S W c を映像信号線 D L と駆動制御素子 D R の制御端子との間に接続してもよい。

#### 【 0 0 2 9 】

選択用スイッチ S W b 及びダイオード接続スイッチ S W c のスイッチング動作は、走査信号線ドライバ Y D R から走査信号線を介して供給される走査信号によって制御する。本態様では、それらのスイッチング動作を、走査信号線ドライバ Y D R から走査信号線 S L 2 を介して供給される走査信号によって制御する構成を採用している。その代わりに、選択用スイッチ S W b のスイッチング動作とダイオード接続スイッチ S W c のスイッチング動作とを別々に制御可能な構成を採用してもよい。すなわち、画素 P X の行毎に走査信号線を 1 本追加し、ダイオード接続スイッチ S W c のスイッチング動作を、走査信号線ドライバ Y D R から走査信号線 S L 2 を介して供給される走査信号によって制御する代わりに、走査信号線ドライバ Y D R から追加した走査信号線を介して供給される走査信号によって制御してもよい。

10

20

30

40

50

## 【0030】

選択用スイッチ SW b には、例えば、電界効果トランジスタなどのトランジスタを単独で又は複数を組み合わせて使用することができる。本態様では、選択用スイッチ SW b として p チャネル薄膜トランジスタを使用しており、そのソースは駆動制御素子 DR のドレインに接続し、ドレインは映像信号線 DL に接続し、ゲートは走査信号線 SL 2 に接続している。

## 【0031】

ダイオード接続スイッチ SW c には、例えば、電界効果トランジスタなどのトランジスタを単独で又は複数を組み合わせて使用することができる。本態様では、ダイオード接続スイッチ SW c として p チャネル薄膜トランジスタを使用しており、そのソースは駆動制御素子 DR のゲートに接続し、ドレインは駆動制御素子 DR のドレインに接続し、ゲートは走査信号線 SL 2 に接続している。

10

## 【0032】

キャパシタ C の一方の電極は、駆動制御素子 DR の制御端子に接続されている。キャパシタ C は、各書き期間において設定した駆動制御素子 DR の制御端子と第 1 端子との間の電圧を、その書き期間に続く表示期間に亘って保持する。

## 【0033】

第 1 電位シフトスイッチ SW e は、第 1 定電位端子 ND<sub>c<sub>p</sub></sub> 1 とキャパシタ C の他方の電極との間に接続されている。すなわち、第 1 電位シフトスイッチ SW e とキャパシタ C とは、第 1 定電位端子 ND<sub>c<sub>p</sub></sub> 1 と駆動制御素子 DR の制御端子との間でこの順に直列に接続されている。この第 1 電位シフトスイッチ SW e のスイッチング動作は、走査信号線ドライバ Y DR から走査信号線 SL 3 を介して供給される走査信号によって制御される。

20

## 【0034】

第 1 電位シフトスイッチ SW e には、例えば、電界効果トランジスタなどのトランジスタを単独で又は複数を組み合わせて使用することができる。本態様では、第 1 電位シフトスイッチ SW e として p チャネル薄膜トランジスタを使用しており、そのソースは第 1 定電位端子 ND<sub>c<sub>p</sub></sub> 1 に接続し、ドレインはキャパシタ C を介して駆動制御素子 DR のゲートに接続し、ゲートは走査信号線 SL 3 に接続している。また、本態様では、第 1 定電位端子 ND<sub>c<sub>p</sub></sub> 1 は第 1 電源端子 ND<sub>p<sub>s</sub></sub> 1 に接続している。第 1 定電位端子 ND<sub>c<sub>p</sub></sub> 1 を第 1 電源端子 ND<sub>p<sub>s</sub></sub> 1 に接続する代わりに、電源線 PS L 及び定電位線 CPL とは別に定電位線を敷設し、この追加の定電位線上のノードを第 1 定電位端子 ND<sub>c<sub>p</sub></sub> 1 として利用してもよい。

30

## 【0035】

第 2 電位シフトスイッチ SW d は、第 2 定電位端子 ND<sub>c<sub>p</sub></sub> 2 とキャパシタ C の他方の電極との間に接続されている。すなわち、第 2 電位シフトスイッチ SW d とキャパシタ C とは、第 2 定電位端子 ND<sub>c<sub>p</sub></sub> 2 と駆動制御素子 DR の制御端子との間でこの順に直列に接続されている。

## 【0036】

第 2 電位シフトスイッチ SW d のスイッチング動作は、走査信号線ドライバ Y DR から走査信号線を介して供給される走査信号によって制御される。本態様では、スイッチ SW b 乃至 SW d のスイッチング動作を、走査信号線ドライバ Y DR から走査信号線 SL 2 を介して供給される走査信号によって制御する構成を採用している。その代わりに、第 2 電位シフトスイッチ SW d のスイッチング動作と選択用スイッチ SW b 及び / 又はダイオード接続スイッチ SW c のスイッチング動作とを別々に制御可能な構成を採用してもよい。すなわち、画素 PX の行毎に走査信号線を 1 本追加し、第 2 電位シフトスイッチ SW d のスイッチング動作を、走査信号線ドライバ Y DR から走査信号線 SL 2 を介して供給される走査信号によって制御する代わりに、走査信号線ドライバ Y DR から追加した走査信号線を介して供給される走査信号によって制御してもよい。

40

## 【0037】

第 2 電位シフトスイッチ SW d には、例えば、電界効果トランジスタなどのトランジス

50

タを単独で又は複数を組み合わせて使用することができる。本態様では、第2電位シフトスイッチSWdとしてpチャネル薄膜トランジスタを使用しており、そのソースは第2定電位端子ND<sub>cp</sub>2に接続し、ドレインはキャパシタCを介して駆動制御素子DRのゲートに接続し、ゲートは走査信号線SL2に接続している。また、本態様では、第2定電位端子ND<sub>cp</sub>2は定電位線CPL上のノードである。

#### 【0038】

映像信号線ドライバXDRには、映像信号線DLが接続されている。映像信号線ドライバXDRは、図示しないコントローラに接続されている。コントローラは、映像信号線ドライバXDRに、シリアル信号としてのデジタル映像信号とスタート信号及びクロック信号を含む制御信号とを出力する。映像信号線ドライバXDRは、これら信号に基づいて、各映像信号線に電流信号としてのアナログ映像信号を出力する。

#### 【0039】

本態様では、映像信号線ドライバXDRには、電源線PSLがさらに接続されている。コントローラは、映像信号線ドライバXDRに第1及び第2電源電圧を出力する。映像信号線ドライバXDRは、これら第1及び第2電源電圧を電源線PSL及び第2電源端子ND<sub>ps</sub>2にそれぞれ出力する。

#### 【0040】

走査信号線ドライバYDRには、走査信号線SL1乃至SL3が接続されている。走査信号線ドライバYDRは、図示しないコントローラに接続されている。コントローラは、走査信号線ドライバYDRに、スタート信号及びクロック信号を含む制御信号を出力する。走査信号線ドライバYDRは、これら信号に基づいて、走査信号線SL1乃至SL3に電圧信号としての走査信号を出力する。

#### 【0041】

本態様では、走査信号線ドライバYDRには、定電位線CPLがさらに接続されている。コントローラは、走査信号線ドライバYDRに第3電源電圧を出力する。走査信号線ドライバYDRは、この第3電源電圧を定電位線CPLに出力する。

#### 【0042】

第1電源端子ND<sub>ps</sub>1、第2電源端子ND<sub>ps</sub>2、第1定電位端子ND<sub>cp</sub>1、第2定電位端子ND<sub>cp</sub>2の電位は、以下のように設定する。本態様のように、駆動制御素子DRがその制御端子と第1端子との電位差をより小さくすることにより駆動電流の大きさをより大きくする場合には、第1電源端子ND<sub>ps</sub>1は第2電源端子ND<sub>ps</sub>2と比較してより高電位とし、第1定電位端子ND<sub>cp</sub>1は第2定電位端子ND<sub>cp</sub>2と比較してより高電位とする。駆動制御素子DRとしてnチャネル電界効果トランジスタを使用したときのように、駆動制御素子DRがその制御端子と第1端子との電位差をより大きくすることにより駆動電流の大きさをより大きくする場合には、第1電源端子ND<sub>ps</sub>1は第2電源端子ND<sub>ps</sub>2と比較してより低電位とし、第1定電位端子ND<sub>cp</sub>1は第2定電位端子ND<sub>cp</sub>2と比較してより低電位とする。

#### 【0043】

なお、アレイ基板は、例えば、上述した表示パネルDPから活性層及び対向電極を省略した構造に相当する。アレイ基板は、この構造に加え、映像信号線ドライバXDR及び/又は走査信号線ドライバYDRをさらに含んでいてもよい。

#### 【0044】

この表示装置は、例えば、以下の方法により駆動する。

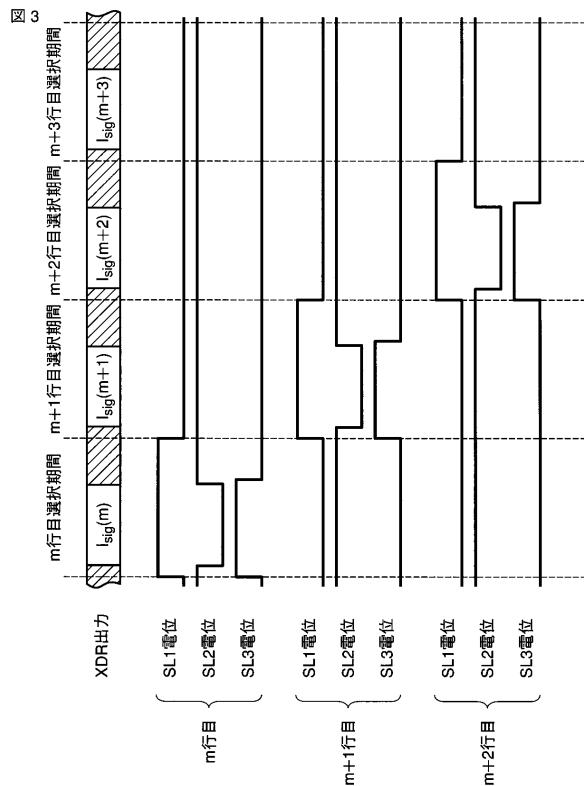

図3は、図1に示す表示装置の駆動方法の一例を概略的に示すタイミングチャートである。図中、横軸は時間を示し、縦軸は電位を示している。

#### 【0045】

図3において、「XDR出力」のうち、「I<sub>sig</sub>(m)」と表記した期間は映像信号線ドライバXDRが映像信号線DLに映像信号I<sub>sig</sub>(m)を出力する期間を示している。また、図3において、「SL1電位」乃至「SL3電位」で示す波形は、走査信号線SL1乃至SL3の電位をそれぞれ示している。

10

20

30

40

50

## 【0046】

図3の方法では、画素P Xを行毎に順次選択する。そして、選択した行が含む画素P Xでは書込動作を実施し、非選択の行が含む画素P Xでは表示動作を実施する。

## 【0047】

例えば、m行目の画素P Xで或る階調を表示する場合、m行目の画素P Xを選択する期間、すなわち、m行目選択期間、では、走査信号線ドライバY DRから、走査信号線SL 1に、m行目の画素P Xが含むスイッチSW aを開く走査信号を出力する。そして、スイッチSW aを開いている期間内に、以下の書込動作を行う。

## 【0048】

まず、走査信号線ドライバY DRから、m行目の画素P Xが接続された走査信号線SL 3に、スイッチSW eを開く走査信号を出力する。次いで、走査信号線ドライバY DRから、m行目の画素P Xが接続された走査信号線SL 2に、スイッチSW b乃至SW dを閉じる走査信号を出力する。この状態で、映像信号線ドライバX DRから、映像信号線DLに、m行目の画素P Xに書き込むべき映像信号を出力する。すなわち、m行目の画素P Xにおいて、ノードND<sub>soft</sub>の電位を定電位端子ND<sub>cp</sub> 2の電位と等しくし且つ駆動制御素子DRのゲート及びドレインを映像信号線DLに接続した状態で、駆動制御素子DRに書込電流I<sub>sig</sub>(m)を流す。これにより、駆動制御素子DRのゲート電位V<sub>g</sub>は、駆動制御素子DRが書込電流I<sub>sig</sub>(m)を流すときのゲート-ソース間電圧V<sub>gs(0)</sub>と第1電源端子ND<sub>ps</sub> 1の電位V<sub>ps</sub> 1との和V<sub>gs(0)</sub> + V<sub>ps</sub> 1と等しくなる。

10

## 【0049】

一定時間経過後、走査信号線ドライバY DRから、m行目の画素P Xが接続された走査信号線SL 2に、スイッチSW b乃至SW dを開く走査信号を出力する。なお、スイッチSW b乃至SW dのスイッチング動作を別々に制御可能である場合には、スイッチSW cを開いた後にスイッチSW b及びSW dを開いてもよい。

20

## 【0050】

その後、走査信号線ドライバY DRから、m行目の画素P Xが接続された走査信号線SL 3に、スイッチSW eを開じる走査信号を出力する。これにより、駆動制御素子DRのゲート電位V<sub>g</sub>は、電位V<sub>gs(0)</sub> + V<sub>ps</sub> 1から、定電位端子ND<sub>cp</sub> 1の電位V<sub>cp</sub> 1と定電位端子ND<sub>cp</sub> 2の電位V<sub>cp</sub> 2との差V<sub>cp</sub> 1 - V<sub>cp</sub> 2だけシフトする。本態様では、電位V<sub>cp</sub> 1は電位V<sub>ps</sub> 1と等しいので、ゲート電位V<sub>g</sub>は電位V<sub>gs(0)</sub> + 2 × V<sub>ps</sub> 1 - V<sub>cp</sub> 2と等しくなる。

30

## 【0051】

以上により、m行目の画素P Xでの書込動作を終了する。なお、m行目の画素P Xの選択期間は、この画素P Xで書込動作を行っている期間であり、m行目の画素P Xの非選択期間は、この画素P Xで書込動作を行っていない期間である。

## 【0052】

この書込動作を終了した後、m行目の画素P Xでは表示動作を開始する。すなわち、走査信号線ドライバY DRから、m行目の画素P Xが接続された走査信号線SL 1に、スイッチSW aを開じる走査信号を出力する。スイッチSW aを開じている間、スイッチSW b乃至SW dは開いたままとし、スイッチSW eは閉じたままとしておく。

40

## 【0053】

スイッチSW aを開じている間、発光素子OLE Dには、駆動制御素子DRのゲート電位V<sub>g</sub>(=V<sub>gs(0)</sub> + 2 × V<sub>ps</sub> 1 - V<sub>cp</sub> 2)と第1定電位端子ND<sub>cp</sub> 1の電位V<sub>cp</sub> 1(=V<sub>ps</sub> 1)の差V<sub>gs(0)</sub> + V<sub>ps</sub> 1 - V<sub>cp</sub> 2に対応した大きさの駆動電流I<sub>drv</sub>(m)が流れる。例えば、電位V<sub>ps</sub> 1が6V、電位V<sub>cp</sub> 2が5V、電圧V<sub>gs(0)</sub>が4.5Vである場合、5.5Vのゲート-ソース間電圧に対応した大きさの駆動電流I<sub>drv</sub>(m)が流れる。発光素子OLE Dは、この駆動電流I<sub>drv</sub>(m)の大きさに対応した輝度で発光する。

## 【0054】

選択期間においてスイッチSW dを開いたままとし且つスイッチSW eを閉じたままと

50

した場合、書込動作により、駆動制御素子 D R のゲート - ソース間電圧  $V_{gs}$  は電圧  $V_{gs}(0)$  に設定される。これに対し、図 3 を参照しながら説明した駆動方法では、スイッチ S W d 及び S W e を用いた電位のシフトを行うので、書込動作により、駆動制御素子 D R のゲート - ソース間電圧  $V_{gs}$  は電圧  $V_{gs}(0) + V_{ps}1 - V_{cp}2$  に設定される。それゆえ、電位  $V_{ps}1$  が電位  $V_{cp}2$  と比較してより高ければ、図 3 を参照しながら説明した方法によると、電位のシフトを行わない場合と比較して、m 行目の画素 P X で低階調を表示するための書込電流  $I_{sig}(m)$  をより大きくすることができる。したがって、本態様によると、低階調画像を表示した場合に表示ムラが発生するのを防止することができる。

#### 【0055】

また、本態様では、定電位線 C P L を敷設すると共に、各画素 P X 内にスイッチ S W d 及び S W e を配置している。このような構造によると、以下に説明するように、映像信号線 D L の電位変動などに起因したクロストークを生じ難い。10

#### 【0056】

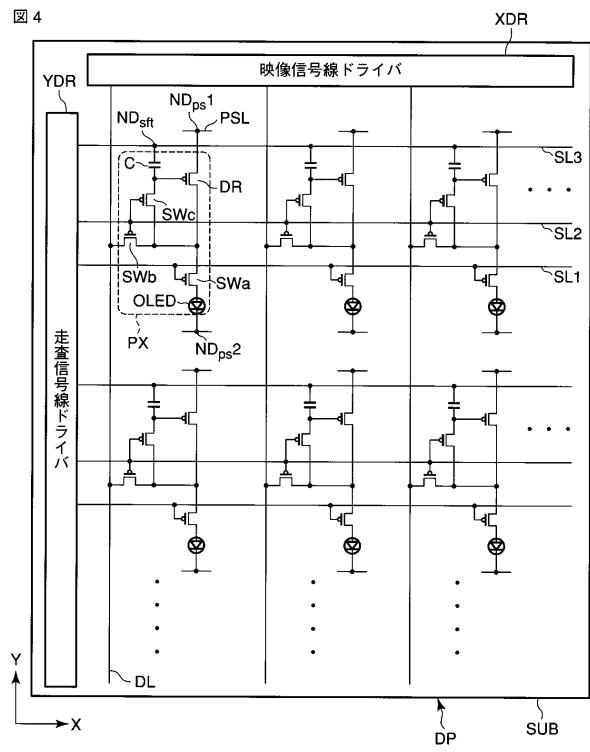

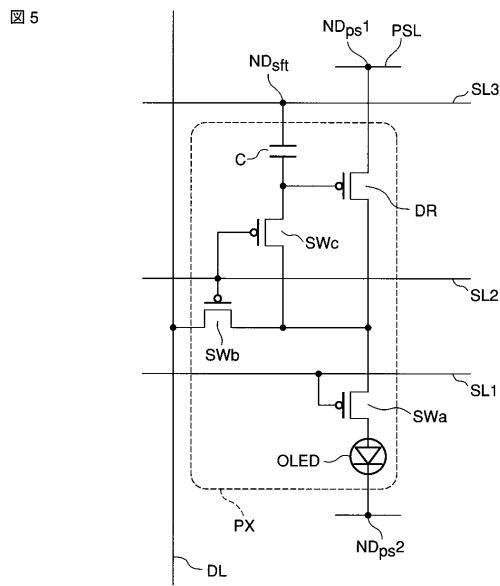

図 4 は、比較例に係る表示装置を概略的に示す平面図である。図 5 は、図 4 の表示装置が含む画素の等価回路図である。

#### 【0057】

図 4 の表示装置は、以下の構成を除き、図 1 の表示装置と同様である。すなわち、図 4 の表示装置は、定電位線 C P L を含んでいない。また、この表示装置の画素 P X は、図 5 に示すように、スイッチ S W d 及び S W e を含んでおらず、キャパシタ C は駆動制御素子 D R のゲートと走査信号線 S L 3との間に接続している。20

#### 【0058】

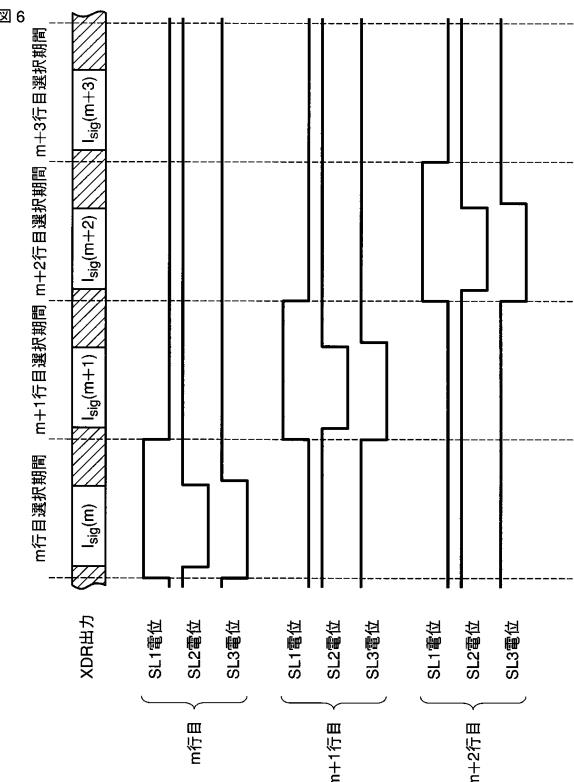

図 6 は、図 4 に示す表示装置の駆動方法の一例を概略的に示すタイミングチャートである。図中、横軸は時間を示し、縦軸は電位を示している。

#### 【0059】

図 6において、「X D R 出力」のうち、「 $I_{sig}(m)$ 」と表記した期間は映像信号線ドライバ X D R が映像信号線 D L に映像信号  $I_{sig}(m)$  を出力する期間を示している。また、図 6において、「S L 1 電位」乃至「S L 3 電位」で示す波形は、走査信号線 S L 1 乃至 S L 3 の電位をそれぞれ示している。20

#### 【0060】

図 6 の方法では、画素 P X を行毎に順次選択する。そして、選択した行が含む画素 P X では書込動作を実施し、非選択の行が含む画素 P X では表示動作を実施する。30

#### 【0061】

例えば、m 行目の画素 P X で或る階調を表示する場合、m 行目の画素 P X を選択する期間、すなわち、m 行目選択期間、では、走査信号線ドライバ Y D R から、走査信号線 S L 1 に、m 行目の画素 P X が含むスイッチ S W a を開く走査信号を出力する。そして、スイッチ S W a を開いている期間内に、以下の書込動作を行う。

#### 【0062】

まず、走査信号線ドライバ Y D R から、走査信号線 S L 3 に、その電位を第 1 電位  $V_1$  に設定する走査信号を出力する。次に、走査信号線ドライバ Y D R から、m 行目の画素 P X が接続された走査信号線 S L 2 に、スイッチ S W b 及び S W c を閉じる走査信号を出力する。この状態で、映像信号線ドライバ X D R から、映像信号線 D L に、m 行目の画素 P X に書き込むべき映像信号を出力する。すなわち、m 行目の画素 P X において、ノード N D<sub>soft</sub> の電位を電位  $V_1$  に設定し且つ駆動制御素子 D R のゲート及びドレインを映像信号線 D L に接続した状態で、駆動制御素子 D R に書込電流  $I_{sig}(m)$  を流す。これにより、駆動制御素子 D R のゲート電位  $V_g$  は、駆動制御素子 D R が書込電流  $I_{sig}(m)$  を流すときのゲート - ソース間電圧  $V_{gs}(0)$  と第 1 電源端子 N D<sub>ps</sub> 1 の電位  $V_{ps}1$  との和  $V_{gs}(0) + V_{ps}1$  と等しくなる。40

#### 【0063】

一定時間経過後、走査信号線ドライバ Y D R から、m 行目の画素 P X が接続された走査信号線 S L 2 に、スイッチ S W b 及び S W c を開く走査信号を出力する。50

## 【0064】

その後、走査信号線ドライバYDRから、m行目の画素PXが接続された走査信号線SL3に、その電位を第2電位V2に設定する走査信号を出力する。これにより、駆動制御素子DRのゲート電位Vgは、電位Vgs(0)+Vps1から、電位V2と電位V1との差V2-V1だけシフトする。すなわち、ゲート電位Vgは電位Vgs(0)+Vps1+V2-V1と等しくなる。以上により、m行目の画素PXでの書き動作を終了する。

## 【0065】

この書き動作を終了した後、m行目の画素PXでは表示動作を開始する。すなわち、走査信号線ドライバYDRから、m行目の画素PXが接続された走査信号線SL1に、スイッチSWaを閉じる走査信号を出力する。スイッチSWaを閉じている間、スイッチSWb及びSWcは開いたままとし、スイッチSWEPは閉じたままとしておく。10

## 【0066】

スイッチSWaを閉じている間、発光素子OLEDには、駆動制御素子DRのゲート電位Vg(=Vgs(0)+Vps1+V2-V1)と第1定電位端子NDcp1の電位Vcp1(=Vps1)の差Vgs(0)+V2-V1に対応した大きさの駆動電流Idrv(m)が流れれる。発光素子OLEDは、この駆動電流Idrv(m)の大きさに対応した輝度で発光する。20

## 【0067】

以上の説明から明らかなように、図6を参照しながら説明した方法でも、電位V2が電位V1と比較してより高ければ、電位のシフトを行わない場合と比較して、m行目の画素PXで低階調を表示するための書き電流Isig(m)をより大きくすることができる。しかしながら、この方法では、駆動制御素子DRのゲートは、選択期間だけでなく非選択期間においても、キャパシタCを介して走査信号線SL3に接続される。非選択期間において、走査信号線SL3の電位が例えば映像信号線DLとの容量結合の影響で変動した場合には、駆動制御素子DRのゲート電位も変動する可能性がある。その結果、このゲート電位の変動に伴って、駆動電流Idrv(m)の大きさも変動し、表示素子OLEDの輝度も変動する。

## 【0068】

これに対し、本態様では、定電位線CPLを敷設すると共に画素PX内にスイッチSWd及びSWEPを配置することにより、キャパシタCを走査信号線と接続することなく、駆動制御素子DRのゲート電位のシフトを可能としている。したがって、本態様によると、走査信号線の映像信号線DLとの容量結合に起因して表示素子OLEDの輝度が変動することはない。すなわち、本態様によると、映像信号線DLの電位変動などに起因したクロストークを生じ難い。30

## 【0069】

以上説明した表示装置には、様々な変形が可能である。

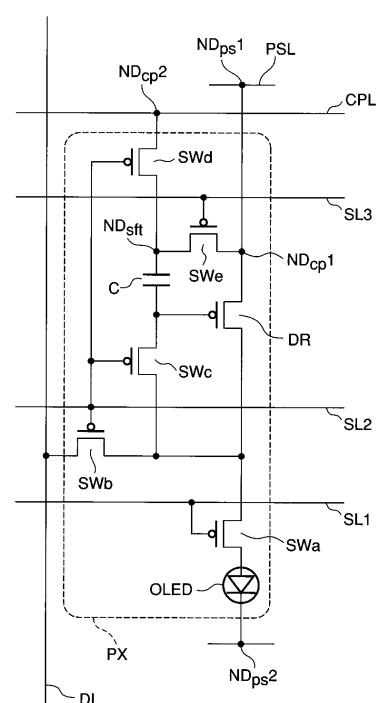

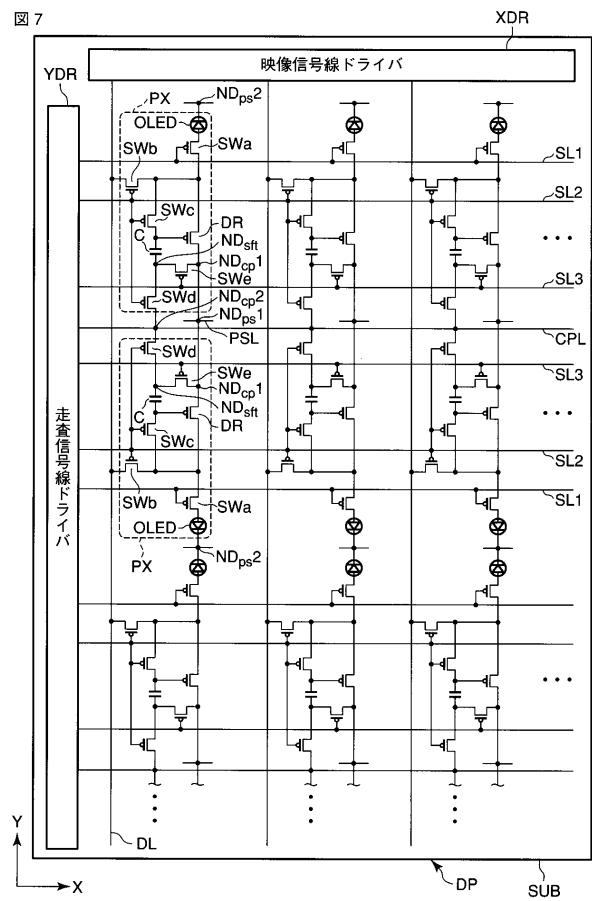

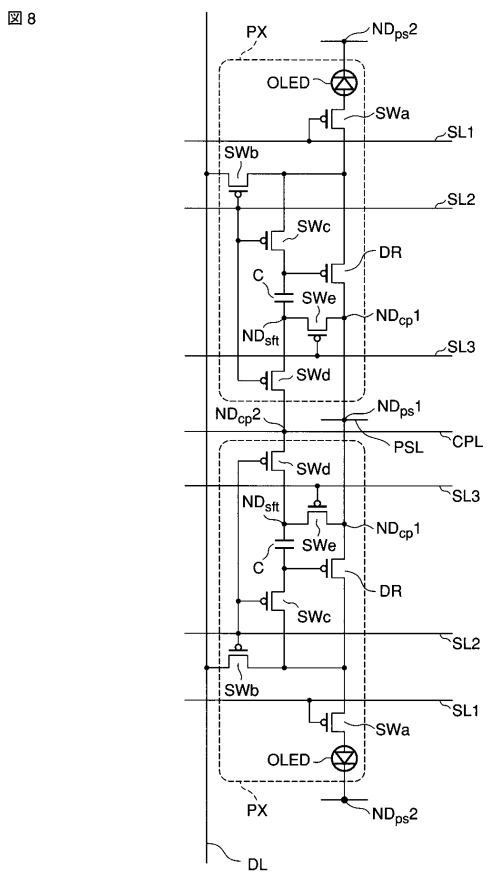

図7は、一変形例に係る表示装置を概略的に示す平面図である。図8は、図7の表示装置が含む画素の等価回路図である。

## 【0070】

この表示装置は、以下の構成を除き、図1及び図2を参照しながら説明した表示装置とほぼ同様である。すなわち、この表示装置では、定電位線CPLは、画素PXが形成する行毎には敷設されておらず、画素PXが形成する行の2つにつき1本の割合で敷設されている。そして、隣り合う1対の行で1本の定電位線CPLを共用している。このような構造を採用すると、図1及び図2を参照しながら説明した構造と比較して、配線数を低減することができる。40

## 【0071】

なお、図7及び図8には、隣り合う1対の行で1本の定電位線CPLを共用する例を示したが、隣り合う1対の列で1本の定電位線CPLを共用する構造を採用することもできる。すなわち、Y方向に延びた定電位線CPLを画素PXが形成する列の2つにつき1本の割合で敷設し、隣り合う1対の列で1本の定電位線CPLを共用させればよい。50

## 【図面の簡単な説明】

## 【0072】

【図1】本発明の一態様に係る表示装置を概略的に示す平面図。

【図2】図1の表示装置が含む画素の等価回路図。

【図3】図1に示す表示装置の駆動方法の一例を概略的に示すタイミングチャート。

【図4】比較例に係る表示装置を概略的に示す平面図。

【図5】図4の表示装置が含む画素の等価回路図。

【図6】図4に示す表示装置の駆動方法の一例を概略的に示すタイミングチャート。

【図7】一変形例に係る表示装置を概略的に示す平面図。

【図8】図7の表示装置が含む画素の等価回路図。

10

## 【符号の説明】

## 【0073】

C ... キャパシタ、CPL ... 定電位線、DL ... 映像信号線、DP ... 表示パネル、DR ... 駆動制御素子、ND<sub>cp1</sub> ... 定電位端子、ND<sub>cp2</sub> ... 定電位端子、ND<sub>ps1</sub> ... 電源端子、ND<sub>ps2</sub> ... 電源端子、ND<sub>sft</sub> ... ノード、OLED ... 発光素子、PSL ... 電源線、PX ... 画素、SL1 ... 走査信号線、SL2 ... 走査信号線、SL3 ... 走査信号線、SUB ... 絶縁基板、SWa ... 出力制御スイッチ、SWb ... 選択用スイッチ、SWc ... ダイオード接続スイッチ、SWd ... 電位シフトスイッチ、SWe ... 電位シフトスイッチ、XDR ... 映像信号線ドライバ、YDR ... 走査信号線ドライバ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 青木 良朗

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 3K107 AA01 BB01 CC33 EE03 HH04 HH05

5C080 AA06 BB05 DD05 EE29 FF11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置，阵列基板和驱动显示装置的方法                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 公开(公告)号        | <a href="#">JP2007233287A</a>                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2007-09-13 |

| 申请号            | JP2006058114                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2006-03-03 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 青木良朗                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 青木 良朗                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/30.J G09G3/20.624.B G09G3/20.642.A G09G3/20.611.H H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C380/AA01 5C380/AB06 5C380/AB45 5C380/BB02 5C380/BB05 5C380/BB08 5C380/CA08 5C380/CA13 5C380/CB01 5C380/CB17 5C380/CB19 5C380/CC18 5C380/CC19 5C380/CC26 5C380/CC33 5C380/CC39 5C380/CC42 5C380/CC52 5C380/CC64 5C380/CD014 5C380/CD016 5C380/DA06 5C380/DA35 |         |            |

| 代理人(译)         | 河野 哲<br>中村诚                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

### 摘要(译)

在将电流信号作为视频信号提供给像素的显示装置中，当显示低灰度图像时出现显示不均匀。驱动像素PX，该像素PX包括控制端子，连接到电源端子NDps1的第一端子，以及用于输出具有与它们之间的电压相对应的大小的驱动电流的第二端子。控制元件DR，显示元件OLED，与显示元件OLED串联连接的开关SWa在第二端子和电源端子ND ps2，第二端子，控制端子和视频信号线DL之间。开关组SWb，SWc可以在它们彼此连接的状态和它们彼此断开的状态，一个电极连接到控制端子的电容器C以及电容器C之间切换连接。开关SWe连接在另一电极与恒电位端子ND cp1之间，开关SWd连接在电容器C的另一电极与恒电位端子ND cp 2之间。要做。[选择图]图2