**【特許請求の範囲】****【請求項 1】**

走査信号線と、前記走査信号線と交差した映像信号線と、前記走査信号線と前記映像信号線との交差部近傍に配置された画素とを具備し、

前記画素のそれぞれは、流れる電流の大きさに応じて光学特性が変化する表示素子と、書込期間において前記映像信号線を介して供給される映像信号が書き込まれるとともに前記書込期間に続く有効表示期間において前記映像信号に対応した大きさの駆動電流を前記表示素子に流す駆動電流制御回路と、前記書込期間に先立つ補正期間において前記映像信号線を介してリセット信号が供給されるとともに前記リセット信号を利用して前記駆動電流制御回路の前記画素間での特性のばらつきを補正する特性補正回路とを備え、

前記特性補正回路により前記駆動電流制御回路の特性を補正する特性補正動作と前記駆動電流制御回路に前記映像信号を書き込む書込動作とのそれぞれを前記画素の行毎に順次行うとともに、或る行の前記画素に対する前記補正期間内にそれよりも前の行の前記画素に対して前記書込動作を行うように構成されたことを特徴とするアクティブマトリクス型表示装置。

**【請求項 2】**

或る行の前記画素に対する前記補正期間と次の行の前記画素に対する前記補正期間とを部分的に重ね合わせるように構成されたことを特徴とする請求項 1 に記載のアクティブマトリクス型表示装置。

**【請求項 3】**

前記駆動電流制御回路は、制御端子と第 1 電源端子に接続された第 1 端子とそれらの間の電圧に対応した大きさで駆動電流を出力する第 2 端子とを備えた駆動電流制御素子と、前記第 1 端子と前記制御端子との間に接続された第 1 キャパシタと、入力端子が前記映像信号線に接続されるとともにその導通状態が前記走査信号線を介して供給される走査信号に応じて切り替わる選択用スイッチとを含み、

前記特性補正回路は、前記選択用スイッチの出力端子と前記制御端子との間に接続された第 2 キャパシタと、前記第 2 端子と前記制御端子との間に接続された補正用スイッチと、入力端子が前記第 2 端子に接続された出力制御用スイッチとを含み、

前記表示素子は前記出力制御用スイッチの出力端子と第 2 電源端子との間に接続されたことを特徴とする請求項 1 または請求項 2 に記載のアクティブマトリクス型表示装置。

**【請求項 4】**

走査信号線と、前記走査信号線と交差した映像信号線と、前記走査信号線と前記映像信号線との交差部近傍に配置された画素とを具備し、

前記画素のそれぞれは、制御端子と第 1 電源端子に接続された第 1 端子とそれらの間の電圧に対応した大きさで駆動電流を出力する第 2 端子とを備えた駆動電流制御素子と、前記第 1 端子と前記制御端子との間に接続された第 1 キャパシタと、入力端子が前記映像信号線に接続されるとともにその導通状態が前記走査信号線を介して供給される走査信号に応じて切り替わる選択用スイッチと、前記選択用スイッチの出力端子と前記制御端子との間に接続された第 2 キャパシタと、前記第 2 端子と前記制御端子との間に接続された補正用スイッチと、入力端子が前記第 2 端子に接続された出力制御用スイッチと、前記出力制御用スイッチの出力端子と第 2 電源端子との間に接続されるとともに流れる電流の大きさに応じて光学特性が変化する表示素子とを備え、

書込期間においては、前記映像信号線から前記選択用スイッチを介して前記第 2 キャパシタの前記選択用スイッチ側の端子に映像信号を供給する書込動作を行い、

前記書込期間に続く有効表示期間においては、前記選択用スイッチ及び前記補正用スイッチを非導通状態とし且つ前記出力制御用スイッチを導通状態として前記駆動電流を前記表示素子に流し、

前記書込期間に先立つ補正期間においては、前記映像信号線から前記選択用スイッチを介して前記第 2 キャパシタの前記選択用スイッチ側の端子にリセット信号を供給するとともに前記出力制御用スイッチを非導通状態とし且つ前記補正用スイッチを導通状態として

10

20

30

40

50

前記駆動電流制御素子の特性を反映した補正信号を前記制御端子に供給することを含む特性補正動作を行い、

前記特性補正動作と前記書込動作とのそれぞれを前記画素の行毎に順次行うとともに、前記補正期間内であって前記リセット信号の供給よりも後に前記特性補正動作を行っている前記画素の前記選択用スイッチ及び前記補正用スイッチの少なくとも一方を非導通状態とする分離期間を設け、或る行の前記画素に対する前記分離期間内にそれよりも前の行の前記画素に対して前記書込動作を行うように構成されたことを特徴とするアクティブマトリクス型表示装置。

## 【請求項5】

前記分離期間には前記特性補正動作を行っている前記画素の前記補正用スイッチを導通状態としたまま前記選択用スイッチを非導通状態とすることを特徴とする請求項4に記載のアクティブマトリクス型表示装置。

### 【請求項 6】

前記分離期間には前記特性補正動作を行っている前記画素の前記選択用スイッチ及び前記補正用スイッチの双方を非導通状態とし、

前記特性補正期間のそれぞれにおいては前記分離期間の後に前記映像信号線から供給される信号を前記映像信号から前記リセット信号へと切り替えるとともに前記特性補正動作を行っている前記画素の前記選択用スイッチ及び前記補正用スイッチの双方を再び導通状態とすることを特徴とする請求項4に記載のアクティブマトリクス型表示装置。

## 【請求項 7】

前記画素のそれぞれの前記選択用スイッチ及び前記補正用スイッチは同一の制御線を介して供給される制御信号により導通状態が制御されることを特徴とする請求項6に記載のアクティブマトリクス型表示装置。

## 【請求項8】

前記表示素子は有機EL素子であることを特徴とする請求項1乃至請求項7の何れか1項に記載のアクティブマトリクス型表示装置。

## 【請求項9】

走査信号線と、前記走査信号線と交差した映像信号線と、前記走査信号線と前記映像信号線との交差部近傍に配置された画素とを具備し、前記画素のそれぞれは、流れる電流の大きさに応じて光学特性が変化する表示素子と、書き込期間において前記映像信号線を介して供給される映像信号が書き込まれるとともに前記書き込期間に続く有効表示期間において前記映像信号に対応した大きさの駆動電流を前記表示素子に流す駆動電流制御回路と、前記書き込期間に先立つ補正期間において前記映像信号線を介してリセット信号が供給されるとともに前記リセット信号を利用して前記駆動電流制御回路の前記画素間での特性のばらつきを補正する特性補正回路とを備えたアクティブマトリクス型表示装置の駆動方法であって、

前記特性補正回路により前記駆動電流制御回路の特性を補正する特性補正動作と前記駆動電流制御回路に前記映像信号を書き込む書き込動作とのそれぞれを前記画素の行毎に順次行うとともに、或る行の前記画素に対する前記補正期間内にそれよりも前の行の前記画素に対して前記書き込動作を行うことを特徴とするアクティブマトリクス型表示装置の駆動方法。

## 【請求項 10】

或る行の前記画素に対する前記補正期間と次の行の前記画素に対する前記補正期間とを部分的に重ね合わせることを特徴とする請求項9に記載のアクティブマトリクス型表示装置の駆動方法。

## 【請求項 1 1】

前記駆動電流制御回路は、制御端子と第1電源端子に接続された第1端子とそれらの間の電圧に対応した大きさで駆動電流を出力する第2端子とを備えた駆動電流制御素子と、前記第1端子と前記制御端子との間に接続された第1キャパシタと、入力端子が前記映像信号線に接続されるとともにその導通状態が前記走査信号線を介して供給される走査信号

に応じて切り替わる選択用スイッチとを含み、

前記特性補正回路は、前記選択用スイッチの出力端子と前記制御端子との間に接続された第2キャパシタと、前記第2端子と前記制御端子との間に接続された補正用スイッチと、入力端子が前記第2端子に接続された出力制御用スイッチとを含み、

前記表示素子は前記出力制御用スイッチの出力端子と第2電源端子との間に接続されたことを特徴とする請求項9または請求項10に記載のアクティブマトリクス型表示装置の駆動方法。

【請求項12】

走査信号線と、前記走査信号線と交差した映像信号線と、前記走査信号線と前記映像信号線との交差部近傍に配置された画素とを具備し、前記画素のそれぞれは、制御端子と第1電源端子に接続された第1端子とそれらの間の電圧に対応した大きさで駆動電流を出力する第2端子とを備えた駆動電流制御素子と、前記第1端子と前記制御端子との間に接続された第1キャパシタと、入力端子が前記映像信号線に接続されるとともにその導通状態が前記走査信号線を介して供給される走査信号に応じて切り替わる選択用スイッチと、前記選択用スイッチの出力端子と前記制御端子との間に接続された第2キャパシタと、前記第2端子と前記制御端子との間に接続された補正用スイッチと、入力端子が前記第2端子に接続された出力制御用スイッチと、前記出力制御用スイッチの出力端子と第2電源端子との間に接続されるとともに流れる電流の大きさに応じて光学特性が変化する表示素子とを備えたアクティブマトリクス型表示装置の駆動方法であって、

書込期間においては、前記映像信号線から前記選択用スイッチを介して前記第2キャパシタの前記選択用スイッチ側の端子に映像信号を供給する書込動作を行い、

前記書込期間に続く有効表示期間においては、前記選択用スイッチ及び前記補正用スイッチを非導通状態とし且つ前記出力制御用スイッチを導通状態として前記駆動電流を前記表示素子に流し、

前記書込期間に先立つ補正期間においては、前記映像信号線から前記選択用スイッチを介して前記第2キャパシタの前記選択用スイッチ側の端子にリセット信号を供給するとともに前記出力制御用スイッチを非導通状態とし且つ前記補正用スイッチを導通状態として前記駆動電流制御素子の特性を反映した補正信号を前記制御端子に供給することを含む特性補正動作を行い、

前記特性補正動作と前記書込動作とのそれぞれを前記画素の行毎に順次行うとともに、前記補正期間内であって前記リセット信号の供給よりも後に前記特性補正動作を行っている前記画素の前記選択用スイッチ及び前記補正用スイッチの少なくとも一方を非導通状態とする分離期間を設け、或る行の前記画素に対する前記分離期間内にそれよりも前の行の前記画素に対して前記書込動作を行うことを特徴とするアクティブマトリクス型表示装置の駆動方法。

【請求項13】

前記分離期間には前記特性補正動作を行っている前記画素の前記補正用スイッチを導通状態としたまま前記選択用スイッチを非導通状態とすることを特徴とする請求項12に記載のアクティブマトリクス型表示装置の駆動方法。

【請求項14】

前記分離期間には前記特性補正動作を行っている前記画素の前記選択用スイッチ及び前記補正用スイッチの双方を非導通状態とし、

前記特性補正期間のそれぞれにおいては前記分離期間の後に前記映像信号線から供給される信号を前記映像信号から前記リセット信号へと切り替えるとともに前記特性補正動作を行っている前記画素の前記選択用スイッチ及び前記補正用スイッチの双方を再び導通状態とすることを特徴とする請求項12に記載のアクティブマトリクス型表示装置の駆動方法。

【請求項15】

前記画素のそれぞれの前記選択用スイッチ及び前記補正用スイッチは同一の制御線を介して供給される制御信号により導通状態が制御されることを特徴とする請求項14に記載

10

20

30

40

50

のアクティブマトリクス型表示装置の駆動方法。

【請求項 1 6】

前記表示素子は有機EL素子であることを特徴とする請求項10乃至請求項15の何れか1項に記載のアクティブマトリクス型表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置及びその駆動方法に係り、特にはアクティブマトリクス型表示装置及びその駆動方法に関する。

【背景技術】

【0002】

近年、有機エレクトロ・ルミネッセンス（以下、ELという）表示装置は、その軽量、薄型、高輝度という特徴により、携帯電話に代表される携帯用情報機器などのディスプレイとして注目を集めている。典型的な有機EL表示装置では、書き期間において書き込んだ映像信号に対応した大きさの駆動電流が、それに続く発光期間において有機EL素子に流れ続けるように、各画素にメモリ性を付与している。すなわち、アクティブマトリクス駆動方式を採用している。

【0003】

ところで、この有機EL表示装置では、映像信号に対応して駆動電流 $I_d$ の大きさを制御する駆動制御素子（駆動用トランジスタ）の閾値電圧 $V_{th}$ が画素間でばらつくのに起因して、表示ムラが発生することがある。この問題に対しては、各画素に閾値キャンセル回路を設けて駆動用トランジスタの特性を補正することが提案されている（以下の特許文献1を参照のこと）。

【0004】

この回路によると、駆動電流 $I_d$ に閾値 $V_{th}$ が与える影響を最小とすることができます。したがって、画素間で駆動用トランジスタの閾値 $V_{th}$ がばらついていたとしても、そのようなばらつきが有機EL素子に供給する駆動電流 $I_d$ に与える影響を低減することができる。

【0005】

しかしながら、この技術では、或る行に対して特性補正動作及び書き動作を行った後に次の行に対して特性補正動作及び書き動作を行うという方法を採用している。すなわち、一水平走査期間内に特性補正動作と書き動作との双方を行っている。そのため、特性補正動作と書き動作との双方に十分な時間を割り当てることが難しく、その結果、表示ムラが十分には解消されないという問題がある。

【特許文献1】米国特許第6,229,506号明細書

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明の目的は、特性補正動作と書き動作との双方に十分な時間を割り当てることが可能な表示装置及びその駆動方法を提供することにある。

【課題を解決するための手段】

【0007】

本発明の第1側面によると、走査信号線と、前記走査信号線と交差した映像信号線と、前記走査信号線と前記映像信号線との交差部近傍に配置された画素とを具備し、前記画素のそれぞれは、流れる電流の大きさに応じて光学特性が変化する表示素子と、書き期間において前記映像信号線を介して供給される映像信号が書き込まれるとともに前記書き期間に続く有効表示期間において前記映像信号に対応した大きさの駆動電流を前記表示素子に流す駆動電流制御回路と、前記書き期間に先立つ補正期間において前記映像信号線を介してリセット信号が供給されるとともに前記リセット信号を利用して前記駆動電流制御回路の前記画素間での特性のばらつきを補正する特性補正回路とを備え、前記特性補正回路に

10

20

30

40

50

より前記駆動電流制御回路の特性を補正する特性補正動作と前記駆動電流制御回路に前記映像信号を書き込む書込動作とのそれぞれを前記画素の行毎に順次行うとともに、或る行の前記画素に対する前記補正期間内にそれよりも前の行の前記画素に対して前記書込動作を行うように構成されたことを特徴とするアクティブマトリクス型表示装置が提供される。

#### 【 0 0 0 8 】

本発明の第2側面によると、走査信号線と、前記走査信号線と交差した映像信号線と、前記走査信号線と前記映像信号線との交差部近傍に配置された画素とを具備し、前記画素のそれぞれは、制御端子と第1電源端子に接続された第1端子とそれらの間の電圧に対応した大きさで駆動電流を出力する第2端子とを備えた駆動電流制御素子と、前記第1端子と前記制御端子との間に接続された第1キャパシタと、入力端子が前記映像信号線に接続されるとともにその導通状態が前記走査信号線を介して供給される走査信号に応じて切り替わる選択用スイッチと、前記選択用スイッチの出力端子と前記制御端子との間に接続された第2キャパシタと、前記第2端子と前記制御端子との間に接続された補正用スイッチと、入力端子が前記第2端子に接続された出力制御用スイッチと、前記出力制御用スイッチの出力端子と第2電源端子との間に接続されるとともに流れる電流の大きさに応じて光学特性が変化する表示素子とを備え、書込期間においては、前記映像信号線から前記選択用スイッチを介して前記第2キャパシタの前記選択用スイッチ側の端子に映像信号を供給する書込動作を行い、前記書込期間に続く有効表示期間においては、前記選択用スイッチ及び前記補正用スイッチを非導通状態とし且つ前記出力制御用スイッチを導通状態として前記駆動電流を前記表示素子に流し、前記書込期間に先立つ補正期間においては、前記映像信号線から前記選択用スイッチを介して前記第2キャパシタの前記選択用スイッチ側の端子にリセット信号を供給するとともに前記出力制御用スイッチを非導通状態とし且つ前記補正用スイッチを導通状態として前記駆動電流制御素子の特性を反映した補正信号を前記制御端子に供給することを含む特性補正動作を行い、前記特性補正動作と前記書込動作とのそれぞれを前記画素の行毎に順次行うとともに、前記補正期間内であって前記リセット信号の供給よりも後に前記特性補正動作を行っている前記画素の前記選択用スイッチ及び前記補正用スイッチの少なくとも一方を非導通状態とする分離期間を設け、或る行の前記画素に対する前記分離期間内にそれよりも前の行の前記画素に対して前記書込動作を行うように構成されたことを特徴とするアクティブマトリクス型表示装置が提供される。

#### 【 0 0 0 9 】

本発明の第3側面によると、走査信号線と、前記走査信号線と交差した映像信号線と、前記走査信号線と前記映像信号線との交差部近傍に配置された画素とを具備し、前記画素のそれぞれは、流れる電流の大きさに応じて光学特性が変化する表示素子と、書込期間において前記映像信号線を介して供給される映像信号が書き込まれるとともに前記書込期間に続く有効表示期間において前記映像信号に対応した大きさの駆動電流を前記表示素子に流す駆動電流制御回路と、前記書込期間に先立つ補正期間において前記映像信号線を介してリセット信号が供給されるとともに前記リセット信号を利用して前記駆動電流制御回路の前記画素間での特性のばらつきを補正する特性補正回路とを備えたアクティブマトリクス型表示装置の駆動方法であって、前記特性補正回路により前記駆動電流制御回路の特性を補正する特性補正動作と前記駆動電流制御回路に前記映像信号を書き込む書込動作とのそれぞれを前記画素の行毎に順次行うとともに、或る行の前記画素に対する前記補正期間内にそれよりも前の行の前記画素に対して前記書込動作を行うことを特徴とするアクティブマトリクス型表示装置の駆動方法が提供される。

#### 【 0 0 1 0 】

本発明の第4側面によると、走査信号線と、前記走査信号線と交差した映像信号線と、前記走査信号線と前記映像信号線との交差部近傍に配置された画素とを具備し、前記画素のそれぞれは、制御端子と第1電源端子に接続された第1端子とそれらの間の電圧に対応した大きさで駆動電流を出力する第2端子とを備えた駆動電流制御素子と、前記第1端子と前記制御端子との間に接続された第1キャパシタと、入力端子が前記映像信号線に接続

10

20

30

40

50

されるとともにその導通状態が前記走査信号線を介して供給される走査信号に応じて切り替わる選択用スイッチと、前記選択用スイッチの出力端子と前記制御端子との間に接続された第2キャパシタと、前記第2端子と前記制御端子との間に接続された補正用スイッチと、入力端子が前記第2端子に接続された出力制御用スイッチと、前記出力制御用スイッチの出力端子と第2電源端子との間に接続されるとともに流れる電流の大きさに応じて光学特性が変化する表示素子とを備えたアクティブマトリクス型表示装置の駆動方法であって、書込期間においては、前記映像信号線から前記選択用スイッチを介して前記第2キャパシタの前記選択用スイッチ側の端子に映像信号を供給する書込動作を行い、前記書込期間に続く有効表示期間においては、前記選択用スイッチ及び前記補正用スイッチを非導通状態とし且つ前記出力制御用スイッチを導通状態として前記駆動電流を前記表示素子に流し、前記書込期間に先立つ補正期間においては、前記映像信号線から前記選択用スイッチを介して前記第2キャパシタの前記選択用スイッチ側の端子にリセット信号を供給するとともに前記出力制御用スイッチを非導通状態とし且つ前記補正用スイッチを導通状態として前記駆動電流制御素子の特性を反映した補正信号を前記制御端子に供給することを含む特性補正動作を行い、前記特性補正動作と前記書込動作とのそれを前記画素の行毎に順次行うとともに、前記補正期間内であって前記リセット信号の供給よりも後に前記特性補正動作を行っている前記画素の前記選択用スイッチ及び前記補正用スイッチの少なくとも一方を非導通状態とする分離期間を設け、或る行の前記画素に対する前記分離期間内にそれよりも前の行の前記画素に対して前記書込動作を行うことを特徴とするアクティブマトリクス型表示装置の駆動方法が提供される。

10

20

30

40

## 【0011】

或る行の画素に対する補正期間と次の行の画素に対する補正期間とは、部分的に重ね合わせててもよい。

## 【0012】

駆動電流制御回路は、制御端子と第1電源端子に接続された第1端子とそれらの間の電圧に対応した大きさで駆動電流を出力する第2端子とを備えた駆動電流制御素子と、第1端子と制御端子との間に接続された第1キャパシタと、入力端子が映像信号線に接続されるとともにその導通状態が走査信号線を介して供給される走査信号に応じて切り替わる選択用スイッチとを含んでいてもよい。また、特性補正回路は、選択用スイッチの出力端子と制御端子との間に接続された第2キャパシタと、第2端子と制御端子との間に接続された補正用スイッチと、入力端子が第2端子に接続された出力制御用スイッチとを含んでいてもよい。この場合、表示素子は出力制御用スイッチの出力端子と第2電源端子との間に接続されていてもよい。

## 【0013】

分離期間には、特性補正動作を行っている画素の補正用スイッチを導通状態としたまま選択用スイッチを非導通状態としてもよい。

## 【0014】

或いは、分離期間には、特性補正動作を行っている画素の選択用スイッチを導通状態としたまま補正用スイッチを非導通状態としてもよい。

## 【0015】

或いは、分離期間には、特性補正動作を行っている画素の選択用スイッチ及び補正用スイッチの双方を非導通状態としてもよい。この場合、特性補正期間のそれぞれにおいては、分離期間の後に、映像信号線から供給される信号を映像信号からリセット信号へと切り替えるとともに特性補正動作を行っている画素の選択用スイッチ及び補正用スイッチの双方を再び導通状態としてもよい。さらに、この場合、画素のそれぞれの選択用スイッチ及び補正用スイッチは、同一の制御線を介して供給される制御信号により導通状態が制御されてもよい。

また、表示素子は有機EL素子であってもよい。

## 【発明の効果】

## 【0016】

50

本発明によると、特性補正動作と書込動作との双方に十分な時間を割り当てることが可能な表示装置及びその駆動方法が提供される。

【発明を実施するための最良の形態】

【0017】

以下、本発明の態様について、図面を参照しながら詳細に説明する。なお、各図において、同様または類似する構成要素には同一の参照符号を付し、重複する説明は省略する。

【0018】

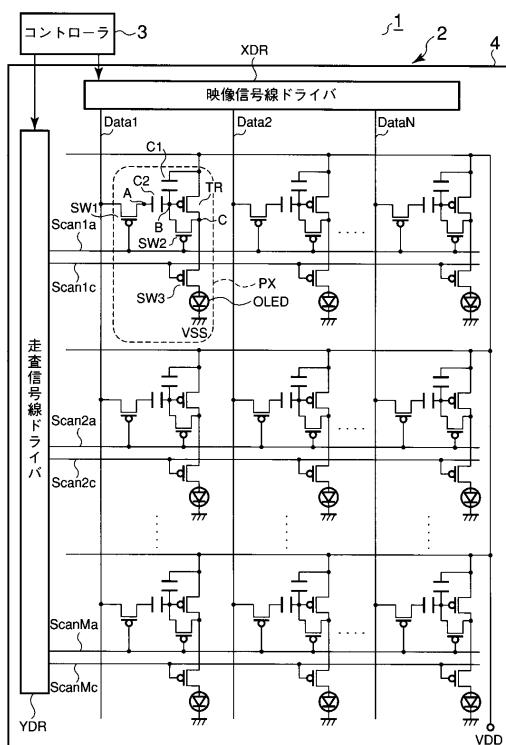

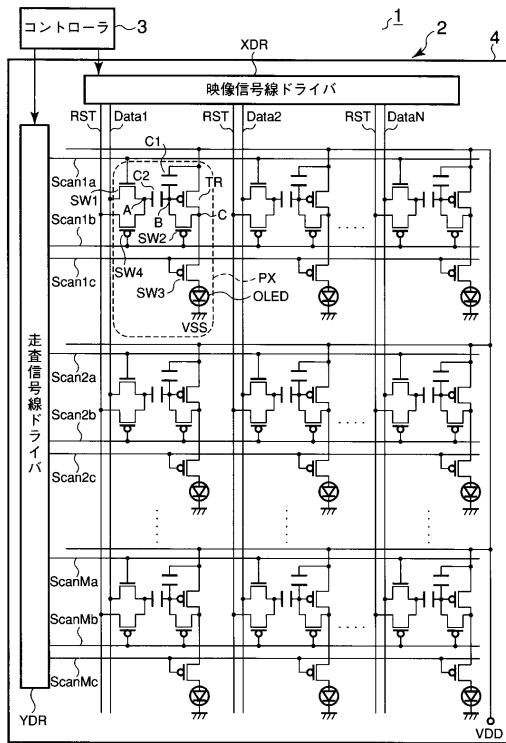

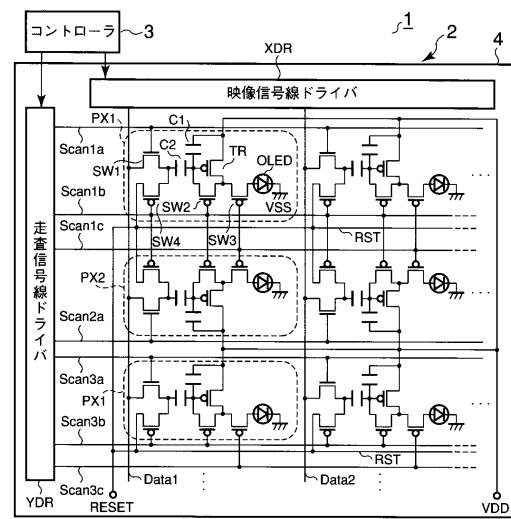

図1は、本発明の一態様に係る表示装置を概略的に示す平面図である。なお、ここでは、一例として、有機EL表示装置を描いている。

【0019】

この有機EL表示装置1は、有機ELパネル2と、有機ELパネル2の表示動作を制御するコントローラ3とを備えている。

【0020】

有機ELパネル2は、例えば17型XGAの表示領域を有しており、ガラス板等の光透過性及び絶縁性を有する支持基板4上でマトリクス状に配列した複数の画素PXと、これら画素PXの行に沿って延在した複数本の走査信号線ScanMa, ScanMb, ScanMcと、これら画素PXの行と略直交する方向に延在した複数本の映像信号線DataNと、走査信号線ScanMa, ScanMb, ScanMcのそれぞれを順次駆動する走査信号線ドライバYDRと、映像信号線DataNを駆動する映像信号線ドライバXDRとを備えている。

10

20

20

30

40

【0021】

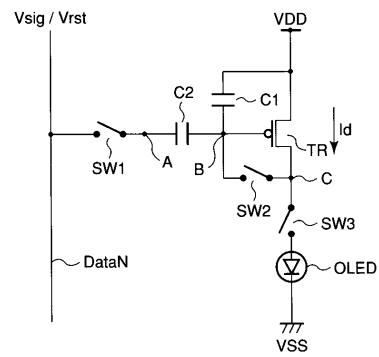

各画素PXは、発光素子として自己発光素子である有機EL素子OLEDを備えるとともに、駆動電流制御回路と特性補正回路とを備えている。

【0022】

駆動電流制御回路は、駆動電流制御素子TRと、選択用スイッチSW1と、キャパシタC1とを備えている。ここでは、一例として、駆動電流制御素子TRにpチャネル薄膜トランジスタ(以下、TFTという)を使用するとともに、選択用スイッチSW1にnチャネルTFTを使用している。これらTFTは、例えば、その活性層に多結晶シリコン膜を用いたものであり、走査信号線ドライバYDR及び映像信号線ドライバXDRを構成するTFTと同一工程で形成され得る。

【0023】

駆動電流制御素子TRは、一対の電源端子VDD, VSS間で有機EL素子OLEDと直列に接続されている。駆動電流制御素子TRは、その制御端子と電源端子VDDとの間の電圧に対応した大きさの駆動電流を有機EL素子OLEDに対して出力する。

【0024】

選択用スイッチSW1は、映像信号線DataNと駆動電流制御素子TRの制御端子との間に接続されている。すなわち、選択用スイッチSW1は、そのソースが映像信号線DataNに接続され、ドレインが後述のキャパシタC2を介して駆動電流制御素子TRの制御端子に接続され、ゲートが対応する走査信号線ScanMaに接続されている。選択用スイッチSW1は、映像信号線DataNとキャパシタC2の選択用スイッチSW1側の端子との間の導通/非導通を走査信号線ScanMaを介して供給される第1走査信号に応じて切り替える。

【0025】

キャパシタC1は、電源端子VDDと駆動電流制御素子TRの制御端子との間に接続されている。キャパシタC1は、駆動電流制御素子TRの制御端子と電源端子VDDとの間の電圧を所定期間ほぼ一定に保持する役割を果たす。

【0026】

具体的には、選択用スイッチSW1は、書込動作に対応して走査信号線ドライバYDRから走査信号線ScanMaを介して供給される第1走査信号により映像信号線DataNと駆動電流制御素子TRの制御端子との間を導通状態とした際に、映像信号線ドライバ

50

X D R から映像信号線 D a t a N を介して供給される信号、例えば映像信号 V sig(= 0 ~ 4 V)、をノード A に出力する。駆動電流制御素子 T R は、選択用スイッチ S W 1 が output する映像信号 V sig に対応した大きさの駆動電流 I d を有機 E L 素子 O L E D に供給する。

【 0 0 2 7 】

なお、選択用スイッチ S W 1 は、特性補正動作に対応して走査信号線 ドライバ Y D R から走査信号線 S c a n M b を介して供給される第 2 走査信号により駆動電流制御素子 T R の制御端子と出力端子の間を導通状態とした際には、映像信号線 ドライバ X D R から映像信号線 D a t a N を介して供給されるリセット信号 V r s t (= 8 V) をノード A に出力する。また、電源端子 V D D , V S S は、例えば、+ 1 0 V 及び 0 V の電位にそれぞれ設定される。

10

【 0 0 2 8 】

特性補正回路は、ここでは閾値キャンセル回路であり、補正用スイッチ S W 2 と、出力制御用スイッチ S W 3 と、キャパシタ C 2 とを備えている。なお、ここでは、一例として、補正用スイッチ S W 2 及び出力制御用スイッチ S W 3 に、p チャネル T F T を使用している。

【 0 0 2 9 】

補正用スイッチ S W 2 は、駆動電流制御素子 T R の出力端子と制御端子との間に接続されている。補正用スイッチ S W 2 は、駆動電流制御素子 T R の出力端子と制御端子との間の導通 / 非導通を走査信号線 S c a n M b を介して供給される第 2 走査信号に応じて切り替える。

20

【 0 0 3 0 】

出力制御用スイッチ S W 3 は、駆動電流制御素子 T R の出力端子と有機 E L 素子 O L E D との間に直列接続されている。出力制御用スイッチ S W 3 は、駆動電流制御素子 T R の出力端子と有機 E L 素子 O L E D との間の導通 / 非導通を走査信号線 S c a n M c を介して供給される第 3 走査信号に応じて切り替える。

【 0 0 3 1 】

キャパシタ C 2 は、選択用スイッチ S w 1 と駆動電流制御素子 T R の制御端子との間に接続されている。キャパシタ C 2 は、ノード A , B 間での電荷の移動を防ぐとともにノード A の電位変化に対応したノード B の電位変化を可能としている。

30

【 0 0 3 2 】

有機 E L 素子 O L E D は、赤、緑、または青のルミネセンス性有機化合物を含む薄膜である発光層を含んだ有機物層を陰極と陽極との間に介在させた構造を有している。有機 E L 素子 O L E D は、有機物層に電子及び正孔を注入しこれらを再結合させることにより励起子を生成させ、この励起子の失活時に生じる光放出により発光する。

【 0 0 3 3 】

なお、有機薄膜層は、陽極バッファ層、発光層、陰極バッファ層の 3 層を積層した構造や、これらを機能的に複合した 2 層あるいは単層構造であってもよい。

【 0 0 3 4 】

コントローラ 3 は、有機 E L パネル 2 の外部に配置されるプリント基板上に形成され、走査信号線 ドライバ Y D R 及び映像信号線 ドライバ X D R の動作を制御する。コントローラ 3 は、外部から供給されるデジタル映像信号及び同期信号を受け取り、垂直走査タイミングを制御する垂直走査制御信号及び水平走査タイミングを制御する水平走査制御信号を同期信号に基づいて発生し、これら垂直走査制御信号及び水平走査制御信号をそれぞれ走査信号線 ドライバ Y D R 及び映像信号線 駆動ドライバ X D R に供給するとともに、水平及び垂直走査タイミングに同期してデジタル映像信号を映像信号線 ドライバ X D R に供給する。

40

【 0 0 3 5 】

映像信号線 ドライバ X D R は、各水平走査期間において、水平走査制御信号の制御の上で、デジタル映像信号をアナログ形式に変換するとともに、それにより得られる映像信号 V sig を複数の映像信号線 D a t a N に対して並列的に供給する。また、映像信号線 D

50

ライバ X D R は、各水平走査期間において、水平走査制御信号の制御のもとで、リセット信号 Vrst を複数の映像信号線 Data N に対して並列的に供給する。

【 0 0 3 6 】

走査信号線ドライバ Y D R は、垂直走査制御信号の制御のもとで、各表示期間 (= 1 フレーム期間 + 垂直プランギング期間 = 補正期間 + 書込期間 + 有効表示期間) において、例えば、第 1 接続期間、分離期間、第 2 接続期間 + 書込期間、有効表示期間に対応して選択用スイッチ SW 1 をオン状態 オフ状態 オン状態 オフ状態 のように変化させる第 1 走査信号を複数本の走査信号線 Scan Ma に順次供給する。なお、この例では、補正期間は、リセット期間と閾値キャンセル期間との和に等しい。また、この例では、第 1 接続期間はリセット期間と閾値キャンセル期間の始めの一部との和であり、第 2 接続期間は閾値キャンセル期間の終わりの一部であり、分離期間は第 1 接続期間及び第 2 接続期間との間に設けられる期間(閾値キャンセル期間の中間の期間)であって、特性補正動作中に一時画素と対応映像信号線とを電気的に切り離す期間である。さらに、ここでは、第 1 接続期間に対応して選択用スイッチ SW 1 をオン状態とするレベルの第 1 走査信号の或る走査信号線 Scan (m - 1) a への供給を開始してから次の走査信号線 Scan ma への供給を開始するまでの期間を 1 水平走査期間 (1 H) と定める。

10

【 0 0 3 7 】

各行の選択用スイッチ SW 1 は、それに対応する走査信号線 Scan Ma から供給される第 1 走査信号により、1 表示期間につき 1 回のみの第 1 接続期間、第 2 接続期間、及び書込期間に映像信号線 Data N とノード A との間を導通させ、他の期間は非導通とする。駆動電流制御素子 TR は、選択用スイッチ SW 1 の導通状態にある書込期間に映像信号線 Data N を介して供給される映像信号 Vsig に対応した駆動電流 Id を、書込期間に続く有効表示期間(発光期間)において有機 EL 素子 OLED に供給する。これら映像信号 Vsig は、映像信号の更新周期である 1 表示期間毎に更新される。

20

【 0 0 3 8 】

また、走査信号線ドライバ Y D R は、走査信号線 Scan Ma に関して説明したのと同様に、垂直走査制御信号の制御のもとで、各表示期間において、例えば、第 1 接続期間、分離期間、第 2 接続期間、書込期間 + 有効表示期間に対応して補正用スイッチ SW 2 をオン状態 オフ状態 オン状態 オフ状態 のように変化させる第 2 走査信号を、複数本の走査信号線 Scan Mb に順次供給する。各行の補正用スイッチ SW 2 は、それに対応する走査信号線 Scan Mb から供給される第 2 走査信号により、1 表示期間につき 1 回のみの第 1 接続期間及び第 2 接続期間に駆動電流制御素子 TR の出力端子と制御端子との間を導通させ、他の期間は非導通とする。

30

【 0 0 3 9 】

さらに、走査信号線ドライバ Y D R は、走査信号線 Scan Ma に関して説明したのと同様に、垂直走査制御信号の制御のもとで、各表示期間において、例えば、リセット期間、閾値キャンセル期間 + 書込期間、有効表示期間に対応して出力制御用スイッチ SW 3 をオン状態 オフ状態 オン状態 のように変化させる第 3 走査信号を、複数本の走査信号線 Scan Mc に順次供給する。各行の出力制御用スイッチ SW 3 は、それに対応する走査信号線 Scan Mc から供給される第 3 走査信号により、1 表示期間につき 1 回のみのリセット期間及び有効表示期間に駆動電流制御素子 TR と有機 EL 素子 OLED との間を導通させ、他の期間は非導通とする。

40

【 0 0 4 0 】

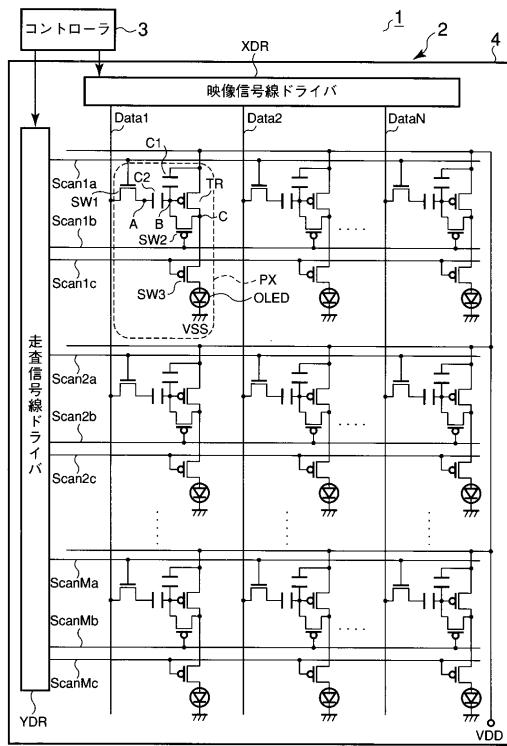

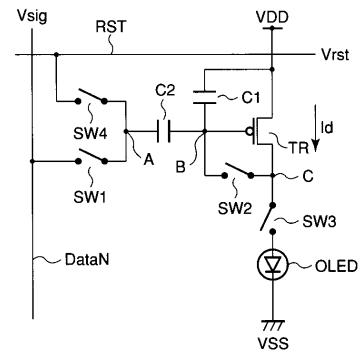

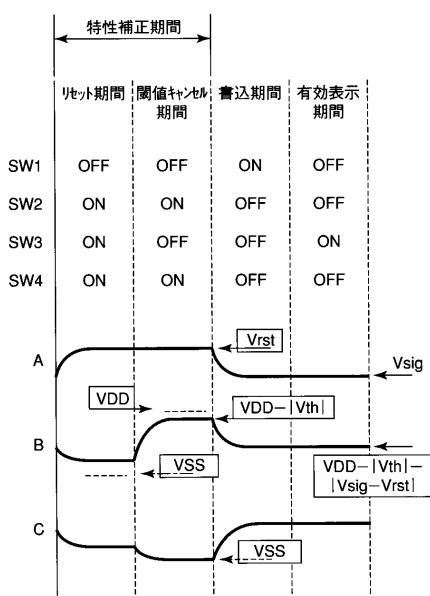

図 2 は、図 1 に示す表示装置 1 の画素 PX の等価回路図である。

上述のように、各画素 PX は、有機 EL 素子 OLED 及び駆動電流制御回路に加え、特性補正回路を備えている。また、駆動電流制御回路は、駆動電流制御素子 TR と選択用スイッチ SW 1 とキャパシタ C 1 とを備えており、特性補正回路は、補正用スイッチ SW 2 と出力制御用スイッチ SW 3 とキャパシタ C 2 とを備えている。これらスイッチ SW 1 乃至 SW 3 は、書込期間に先立つ補正期間において、駆動電流制御素子 TR の制御電圧をこの駆動電流制御素子 TR の閾値電圧 Vth とほぼ等しいレベルに初期化するために図 3 に示

50

す関係でオン／オフされる。

【0041】

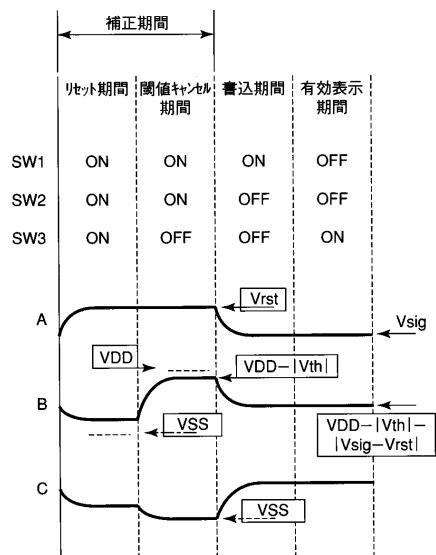

図3は、図2に示す画素P Xの駆動方法の一例を示す図である。

図3に示すように、補正期間はリセット期間と閾値キャンセル期間とを含んでいる。なお、この例では、補正期間内に分離期間は設けていない。

【0042】

リセット期間では、駆動電流制御素子T Rの入力端子と制御端子との間の電圧をその閾値電圧V thより大きくなるよう設定する。具体的には、スイッチS W 1乃至S W 3をオン状態とする。また、リセット期間では、映像信号線ドライバX D Rから各映像信号線D a t a Nにリセット信号V rstを供給する。この動作により、ノードAの電位は選択用スイッチS W 1を介して供給されるリセット信号V rstにより上昇し、ノードB及びCの電位は補正用スイッチS W 2を介して流れる放電電流により低下する。

【0043】

これに続く閾値キャンセル期間では、スイッチS W 1, S W 2をオン状態に維持したまま、出力制御用スイッチS W 3をオフ状態に設定する。これにより、ノードBの電位は、補正用スイッチS W 2を介して流れる充電電流によって駆動電流制御素子T Rの閾値電圧V thとほぼ等しいレベルにまで上昇する。なお、この際、キャパシタC 2のノードA側の電極には、リセット信号V rstが供給されている。

【0044】

書込期間では、選択用スイッチS W 1をオン状態とし、スイッチS W 2及びS W 3をオフ状態とする。これにより、ノードAには、選択用スイッチS W 1を介して供給されるリセット信号V rstに代わり、映像信号V sigが選択用スイッチS W 1を介して供給される。その結果、ノードBの電位は、閾値電圧V thと映像信号V sigとの和にほぼ等しくなる。

【0045】

有効表示期間では、出力制御用スイッチS W 3をオン状態とし、スイッチS W 1, S W 2をオフ状態とする。これにより、駆動電流I dが出力制御用スイッチS W 3を介して有機EL素子O L E Dに供給される。ここで、駆動電流I dは、リセット信号V rstと映像信号V sigとの電位差により決定されることになり、駆動電流制御素子T Rの閾値電圧V thが画素P X間でばらついていたとしても、そのようなばらつきが駆動電流I dに与える影響を排除することができる。

【0046】

さて、本態様では、この表示装置1を以下に説明するように駆動する。

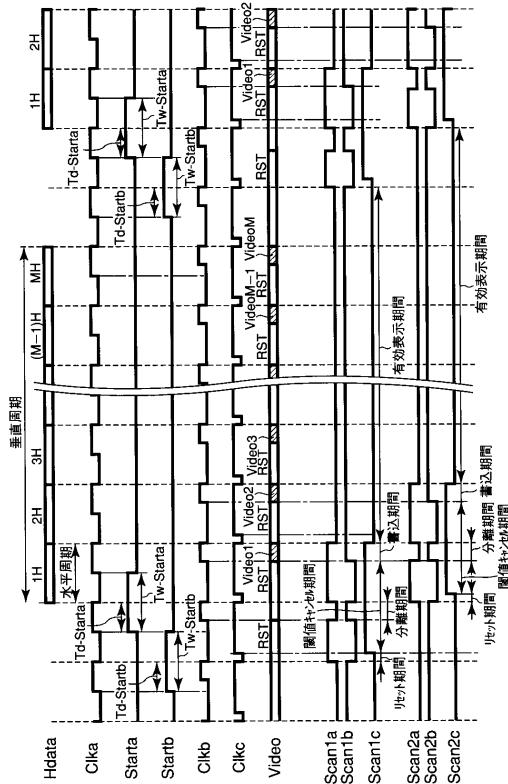

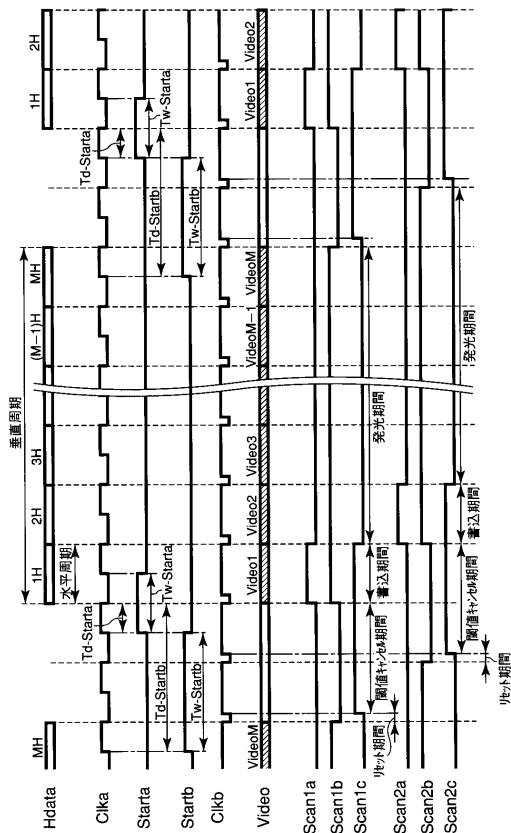

図4は、図1に示す表示装置1で利用可能な駆動方法の一例を示すタイミングチャートである。なお、図4に示す参照符号C 1 k a, C 1 k bはクロック信号を示し、S t a r t a, S t a r t bはスタート信号を示し、V i d e oは映像信号を示しており、これらは何れもコントローラ3が出力する信号である。また、図4に示す参照符号S c a n M a, S c a n M b, S c a n M cは、それぞれ、走査信号線ドライバY D Rが走査信号線S c a n M a, S c a n M b, S c a n M cに出力する走査信号を示している。

【0047】

走査信号線ドライバY D Rは、スタート信号S t a r t a及びクロック信号C 1 k aから各水平走査期間に対応した1水平期間の幅(T w - S t a r t a)の第1パルスを生成するシフトレジスタと、スタート信号S t a r t b及びクロック信号C 1 k aから1水平走査期間の整数倍の幅(T w - S t a r t b)の第2パルスを生成するシフトレジスタとを備えている。走査信号線ドライバY D Rは、第1及び第2パルスとクロック信号C 1 k bとから第1走査信号を生成し、これを第1走査信号線S c a n M aに順次出力する。また、走査信号線ドライバY D Rは、第1及び第2パルスとクロック信号C 1 k bとから第2走査信号を生成し、これを第2走査信号線S c a n M bに順次出力する。さらに、走査信号線ドライバY D Rは、第1及び第2パルスとクロック信号C 1 k cとから第3走査信号を生成し、これを第3走査信号線S c a n M cに順次出力する。

【0048】

10

20

30

40

50

具体的には、走査信号線ドライバYDRは、リセット期間では、第1走査信号線ScanMaに選択レベル（ここではHighレベル）の第1走査信号を供給するとともに、第2及び第3走査信号線ScanMb, ScanMcに選択レベル（ここではLowレベル）の第2及び第3走査信号をそれぞれ供給する。

#### 【0049】

閾値キャンセル期間では、走査信号線ドライバYDRは、まず、第1走査信号線ScanMaに選択レベル（ここではHighレベル）の第1走査信号を供給し、第2走査信号線ScanMbに選択レベル（ここではLowレベル）の第2走査信号を供給し、第3走査信号線ScanMcには非選択レベル（ここではHighレベル）の走査信号を供給する。なお、この期間とリセット期間との和は第1接続期間である。

10

#### 【0050】

次に、走査信号線ドライバYDRは、第3走査信号線ScanMcに非選択レベル（ここではHighレベル）の走査信号を供給したまま、第1走査信号線ScanMaに非選択レベル（ここではLowレベル）の第1走査信号を供給し、第2走査信号線ScanMbに非選択レベル（ここではHighレベル）の第2走査信号を供給する。この期間は、分離期間（補正休止期間）である。

#### 【0051】

その後、走査信号線ドライバYDRは、第3走査信号線ScanMcに非選択レベル（ここではHighレベル）の走査信号を供給したまま、再度、第1走査信号線ScanMaに選択レベル（ここではHighレベル）の第1走査信号を供給し、第2走査信号線ScanMbに選択レベル（ここではLowレベル）の第2走査信号を供給する。この期間は、第2接続期間である。

20

#### 【0052】

補正期間に続く書込期間では、走査信号線ドライバYDRは、第1走査信号線ScanMaに選択レベル（ここではHighレベル）の第1走査信号を供給するとともに、第2及び第3走査信号線ScanMb, ScanMcに非選択レベル（ここではHighレベル）の第2及び第3走査信号をそれぞれ供給する。

#### 【0053】

有効表示（発光）期間では、走査信号線ドライバYDRは、走査信号線ScanMa, ScanMcにLowレベルの走査信号を供給し、走査信号線ScanMbにHighレベルの走査信号を供給する。

30

#### 【0054】

本態様では、或る行の画素PXへの特性補正動作（=リセット動作+閾値キャンセル動作）を開始してから終了するまでの間に、それよりも前の行の画素PXに対して書込動作を行う。そして、典型的には、或る行の画素PXに対して特性補正動作を行う補正期間と次の行の画素に対して特性補正動作を行う補正期間とを部分的に重ね合わせる。こうすると、或る行の画素PXへの特性補正動作と書込動作との双方を完了した後に次の行の画素PXへの特性補正動作を開始する場合に比べ、有効表示（発光）期間を十分に長く設定しつつ（有効表示期間が1表示期間に占める割合は50%以上であることが望ましい）、特性補正動作と書込動作との双方に十分な時間を割り当てることが可能となる。

40

#### 【0055】

また、本態様では、補正期間に分離期間を設け、或る行の画素PXを映像信号線DataNから分離している間に、それよりも前の行の画素PXに対する書込動作を実施する。そのため、リセット信号Vrstを供給するためのリセット信号線を別途設けることなく、或る行の画素PXに対して特性補正動作を行う補正期間とそれよりも前の行の画素PXに対して書込動作を行う書込期間とを重ね合わせることができる。したがって、配線数の増加を伴うことなく、有効表示期間を十分に長く設定しつつ、特性補正動作と書込動作との双方に十分な時間を割り当てることが可能となる。

#### 【0056】

このように、本態様によると、特性補正動作と書込動作との双方に十分な時間を割り当

50

てることができる。また、本態様によると、これを実現するうえで配線数の増加を伴うことがない。したがって、本態様によると、比較的少ない配線数で、駆動電流制御回路の特性の画素 P X 間でのばらつきに起因した表示ムラを十分に解消することができる。

#### 【0057】

図 4 を参照して説明した駆動方法には様々な変形が可能である。これについては、図 5 及び図 6 を参照しながら説明する。

#### 【0058】

図 5 は、図 1 に示す表示装置 1 で利用可能な駆動方法の例を示す図である。図 5 は、図 1 に示す表示装置 1 で利用可能な駆動方法の他の例を示す図である。

#### 【0059】

図 5 及び図 6 には、(M - 1) 行目の画素 P X と M 行目の画素 P X について、補正期間、書込期間、有効表示期間におけるスイッチ SW1 乃至 SW3 の導通状態を描いている。なお、図中、「ON / OFF」はそのスイッチがオン状態及びオフ状態の何れでもよいことを示している。また、「映像信号 / リセット信号」の欄に記載した「RST」は映像信号線 DataN にはリセット信号 Vrst が供給されていることを示しており、「VideoM」は映像信号線 DataN には M 行目の画素 P X に対応した映像信号 Vsig が供給されていることを示している。

#### 【0060】

図 5 に示すように、映像信号線 DataN に (M - 1) 行目の画素 P X に対応した映像信号 Vsig, すなわち VideoM - 1, を供給している間、M 行目の画素 P X では補正用スイッチ SW2 はオン状態としてもよい。すなわち、図 4 を参照しながら説明した例では、分離期間において閾値キャンセル動作を中断したが、分離期間に閾値キャンセル動作を継続することもできる。この場合も、先に説明したのと同様の効果を得ることができる。

#### 【0061】

また、図 5 に示す駆動方法では、映像信号線 DataN に (M - 1) 行目の画素 P X に対応した映像信号 Vsig, すなわち VideoM - 1, を供給している間、M 行目の画素 P X では選択用スイッチ SW1 をオフ状態としたが、図 6 に示すように、その間、M 行目の画素 P X の選択用スイッチ SW1 はオン状態としてもよい。すなわち、図 6 に示すように、映像信号線 DataN に (M - 1) 行目の画素 P X に対して書込動作を実施している間、M 行目の画素 P X で補正用スイッチ SW2 をオフ状態とすれば、その間に M 行目の画素 P X の選択用スイッチ SW1 をオン状態としても、先に説明したのと同様の効果を得ることができる。

#### 【0062】

以上説明したように、図 4 を参照して説明した駆動方法には様々な変形が可能である。

#### 【0063】

また、上述した駆動方法は、図 1 に示したのとは異なる回路構成を有する表示装置でも利用可能である。

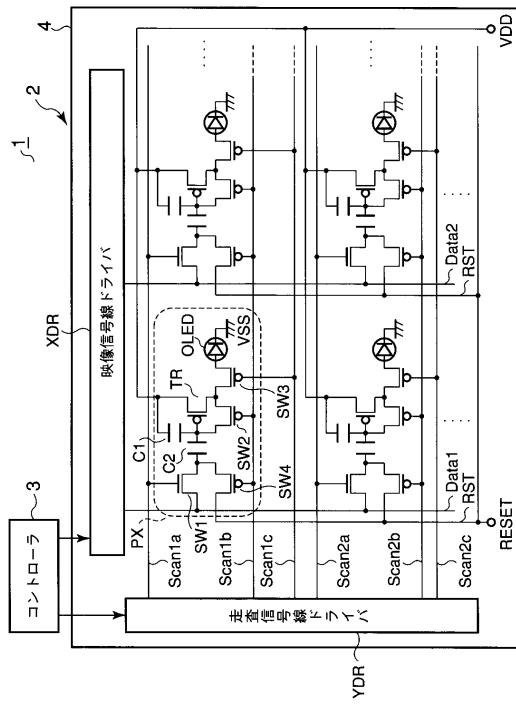

#### 【0064】

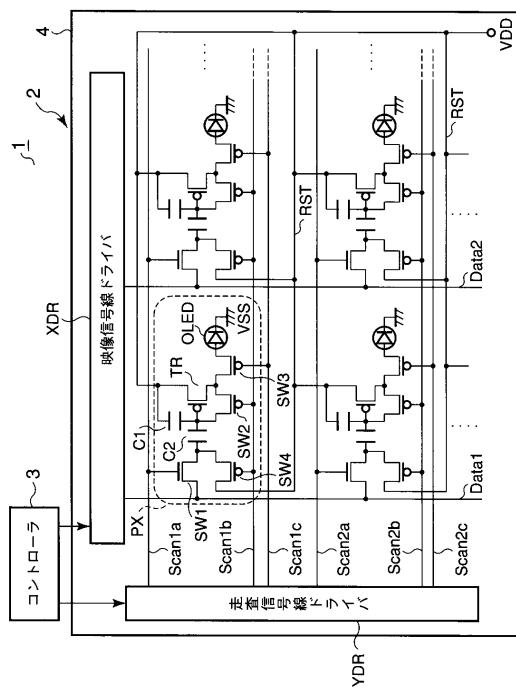

図 7 は、本態様の一変形例に係る表示装置を概略的に示す平面図である。なお、ここでは、一例として、有機 EL 表示装置を描いている。また、図 8 は、図 7 に示す表示装置 1 で利用可能な駆動方法の一例を示すタイミングチャートである。

#### 【0065】

図 7 に示す表示装置 1 は、第 2 走査信号線 ScanMb を備えておらず、各画素 P X において、選択用スイッチ SW1 として補正用スイッチ SW2 と導電型が同一の TFT, ここでは p チャネル TFT, を使用するとともに、補正用スイッチ SW2 の制御端子であるゲートが第 1 走査信号線 ScanMa に接続されていること以外は図 1 に示す表示装置 1 と同様の構造を有している。この表示装置 1 は、図 8 に示すように、第 2 走査信号を生成せず、第 1 走査信号の信号レベルを逆転させたこと以外は、図 4 を参照しながら説明したのと同様の方法により駆動することができる。

## 【0066】

図7に示す表示装置1では、補正用スイッチSW2の制御端子であるゲートを第1走査信号線ScanMaに接続することにより、第2走査信号線ScanMbを省略している。そのため、図1の表示装置1に比べ、より少ない配線数で、有効表示期間を十分に長く設定しつつ、特性補正動作と書き込動作との双方に十分な時間を割り当てることが可能となる。

## 【0067】

なお、本発明は、上述の態様に限定されず、その要旨を逸脱しない範囲でさらに変形可能である。例えば、先の態様では、画素に特定の回路構成を採用したが、画素には他の回路構成を採用してもよい。例えば、スイッチSW1乃至SW3としては、nチャネルTFTを使用してもよく或いはpチャネルTFTを使用してもよい。また、それらスイッチSW1乃至SW3としてトランスミッショングート等の他のスイッチング素子を使用してもよい。

## 【0068】

また、先の態様では、特性補正回路が駆動電流制御素子TRの閾値電圧Vthのばらつき補正を行うものである場合について説明したが、特性補正回路は、駆動電流制御回路の特性のばらつきを補正するものであれば、駆動電流制御素子TRの閾値電圧Vthのばらつき補正を行うものでなくてもよい。

## 【0069】

また、上述の態様では、映像信号の書き込みを1画素行ずつ行うものについて説明したが、これに限定されず、複数行ずつ同時に書き込みを行ってもよい。

## 【0070】

さらに、上述の態様では、映像信号のデジタル-アナログ変換を基板4上に形成した映像信号線ドライバXDRで行う場合について説明したが、この変換は有機ELパネル2の外部で行ってもよい。

## 【0071】

また、映像信号線ドライバXDRはアナログ映像信号を時分割で対応する映像信号線DataNに供給するものであってもよい。そして、更に、有機EL素子OLEDに供給する電源電圧は発光色毎に設定してもよい。

## 【0072】

また、上述の態様では画素を構成するトランジスタとしてその活性層に多結晶ポリシリコンを用いるものについて説明したが、アモルファスシリコンを用いるものであってもよい。特に、アモルファスシリコンを用いる場合には補正期間の確保が重要となってくるため、本発明を適用することが望ましい。

## 【0073】

さらに、上述の態様では表示素子として有機EL素子OLEDを使用した有機EL表示装置1について説明したが、流れる電流の大きさに応じて光学特性が変化するものであれば他の表示素子を使用してもよい。すなわち、先の技術は有機EL表示装置以外の表示装置、例えば発光ダイオード表示装置や電界放出表示装置などのように自己発光素子を備えた表示装置、にも適用可能である。

## 【0074】

各画素PXにおけるスイッチ数の増加や配線数の増加が許容される場合には、以下に説明する技術でも、有効表示期間を十分に長く設定しつつ、特性補正動作と書き込動作との双方に十分な時間を割り当てることができる。

## 【0075】

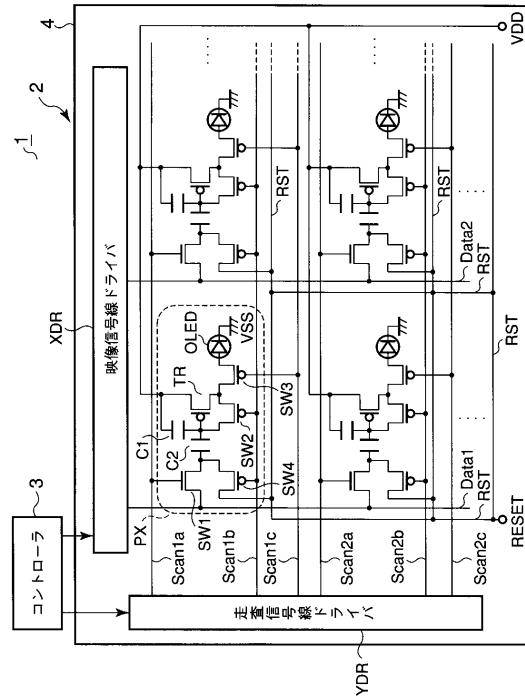

図9は、参考例に係る表示装置を概略的に示す平面図である。なお、ここでは、一例として、有機EL表示装置を描いている。

## 【0076】

この有機EL表示装置1は、有機ELパネル2と、有機ELパネル2の表示動作を制御するコントローラ3とを備えている。

10

20

30

40

50

## 【0077】

有機ELパネル2は、例えば17型XGAの表示領域を有しており、ガラス板等の光透過性絶縁基板4上でマトリクス状に配列した複数の画素PXと、これら画素PXの行に沿って延在した複数本の走査信号線ScanMa, ScanMb, ScanMcと、これら画素PXの行と略直交する方向に延在した複数本の映像信号線DataNと、走査信号線ScanMa, ScanMb, ScanMcのそれぞれを順次駆動する走査信号線ドライバYDRと、映像信号線DataNを駆動する映像信号線ドライバXDRとを備えている。また、この有機ELパネル2には、映像信号線DataNから独立したリセット信号線\_RSTが、画素列に沿った方向、すなわち映像信号線DataNと略平行な方向、に設けられている。

10

## 【0078】

各画素PXは、発光素子として自己発光素子である有機EL素子OLEDを備えるとともに、駆動電流制御回路と特性補正回路とを備えている。

## 【0079】

駆動電流制御回路は、駆動電流制御素子TRと、選択用スイッチSW1と、キャパシタC1とを備えている。ここでは、一例として、駆動電流制御素子TRにpチャネルTFTを使用するとともに、選択用スイッチSW1にnチャネルTFTを使用している。これらTFTは、例えば、その活性層に多結晶シリコン膜を用いたものであり、走査信号線ドライバYDR及び映像信号線ドライバXDRを構成するTFTと同一工程で形成され得る。

20

## 【0080】

駆動電流制御素子TRは、一对の電源端子VDD, VSS間で有機EL素子OLEDと直列に接続されている。駆動電流制御素子TRは、その制御端子と電源端子VDDとの間の電圧に対応した大きさの駆動電流を有機EL素子OLEDに対して出力する。

## 【0081】

選択用スイッチSW1は、映像信号線DataNと駆動電流制御素子TRの制御端子との間に接続されている。すなわち、選択用スイッチSW1は、そのソースが映像信号線DataNに接続され、ドレインが後述のキャパシタC2を介して駆動電流制御素子TRの制御端子に接続され、ゲートが対応する走査信号線ScanMaに接続されている。選択用スイッチSW1は、映像信号線DataNとキャパシタC2の選択用スイッチSW1側の端子との間の導通/非導通を走査信号線ScanMaを介して供給される第1走査信号に応じて切り替える。

30

## 【0082】

キャパシタC1は、電源端子VDDと駆動電流制御素子TRの制御端子との間に接続されている。キャパシタC1は、駆動電流制御素子TRの制御端子と電源端子VDDとの間の電圧を所定期間ほぼ一定に保持する役割を果たす。

## 【0083】

具体的には、選択用スイッチSW1は、書き動作に対応して走査信号線ドライバYDRから走査信号線ScanMaを介して供給される第1走査信号により映像信号線DataNと駆動電流制御素子TRの制御端子との間を導通状態とした際に、映像信号線ドライバXDRから映像信号線DataNを介して供給される信号、例えば映像信号Vsig(=0~4V), をノードAに出力する。駆動電流制御素子TRは、選択用スイッチSW1が出力する映像信号Vsigに対応した大きさの駆動電流Idを有機EL素子OLEDに供給する。なお、電源端子VDD, VSSは、例えば、+10V及び0Vの電位にそれぞれ設定される。

40

## 【0084】

特性補正回路は、ここでは閾値キャンセル回路であり、補正用スイッチSW2と、出力制御用スイッチSW3と、リセットスイッチSW4と、キャパシタC2とを備えている。なお、ここでは、一例として、補正用スイッチSW2、出力制御用スイッチSW3、リセットスイッチSW4に、pチャネルTFTを使用している。

## 【0085】

50

リセットスイッチ SW 4 は、リセット信号 V<sub>rst</sub> ( = 8 V ) を供給するリセット信号線 R<sub>S</sub>T と駆動電流制御素子 T<sub>R</sub> の制御端子との間に接続されている。すなわち、リセットスイッチ SW 4 は、そのソースがリセット信号線 R<sub>S</sub>T に接続され、ドレインがキャパシタ C<sub>2</sub> を介して駆動電流制御素子 T<sub>R</sub> の制御端子に接続され、ゲートが走査信号線 S<sub>c</sub>a<sub>n</sub>M<sub>b</sub> に接続されている。リセットスイッチ SW 4 は、リセット信号線 R<sub>S</sub>T とキャパシタ C<sub>2</sub> の選択用スイッチ SW<sub>1</sub> 側の端子との間の導通 / 非導通を走査信号線 S<sub>c</sub>a<sub>n</sub>M<sub>b</sub> を介して供給される第 2 走査信号に応じて切り替える。

#### 【 0 0 8 6 】

補正用スイッチ SW<sub>2</sub> は、駆動電流制御素子 T<sub>R</sub> の出力端子と制御端子との間に接続されている。補正用スイッチ SW<sub>2</sub> は、駆動電流制御素子 T<sub>R</sub> の出力端子と制御端子との間の導通 / 非導通を走査信号線 S<sub>c</sub>a<sub>n</sub>M<sub>b</sub> を介して供給される第 2 走査信号に応じて切り替える。

#### 【 0 0 8 7 】

出力制御用スイッチ SW<sub>3</sub> は、駆動電流制御素子 T<sub>R</sub> の出力端子と有機 E<sub>L</sub> 素子 O<sub>L</sub>E<sub>D</sub> との間に直列接続されている。出力制御用スイッチ SW<sub>3</sub> は、駆動電流制御素子 T<sub>R</sub> の出力端子と有機 E<sub>L</sub> 素子 O<sub>L</sub>E<sub>D</sub> との間の導通 / 非導通を走査信号線 S<sub>c</sub>a<sub>n</sub>M<sub>c</sub> を介して供給される第 3 走査信号に応じて切り替える。

#### 【 0 0 8 8 】

キャパシタ C<sub>2</sub> は、選択用スイッチ SW<sub>1</sub> と駆動電流制御素子 T<sub>R</sub> の制御端子との間に接続されている。キャパシタ C<sub>2</sub> は、ノード A, B 間での電荷の移動を防ぐとともにノード A の電位変化に対応したノード B の電位変化を可能としている。

#### 【 0 0 8 9 】

有機 E<sub>L</sub> 素子 O<sub>L</sub>E<sub>D</sub> は、赤、緑、または青のルミネセンス性有機化合物を含む薄膜である発光層を含んだ有機物層を陰極と陽極との間に介在させた構造を有している。有機 E<sub>L</sub> 素子 O<sub>L</sub>E<sub>D</sub> は、有機物層に電子及び正孔を注入しそれらを再結合させることにより励起子を生成させ、この励起子の失活時に生じる光放出により発光する。

#### 【 0 0 9 0 】

なお、有機薄膜層は、陽極バッファ層、発光層、陰極発光層の 3 層を積層した構造や、これらを機能的に複合した 2 層あるいは単層構造であってもよい。

#### 【 0 0 9 1 】

コントローラ 3 は、有機 E<sub>L</sub> パネル 2 の外部に配置されるプリント基板上に形成され、走査信号線ドライバ Y<sub>D</sub>R 及び映像信号線ドライバ X<sub>D</sub>R の動作を制御する。コントローラ 3 は、外部から供給されるデジタル映像信号及び同期信号を受け取り、垂直走査タイミングを制御する垂直走査制御信号及び水平走査タイミングを制御する水平走査制御信号を同期信号に基づいて発生し、これら垂直走査制御信号及び水平走査制御信号をそれぞれ走査信号線ドライバ Y<sub>D</sub>R 及び映像信号線駆動ドライバ X<sub>D</sub>R に供給するとともに、水平及び垂直走査タイミングに同期してデジタル映像信号を映像信号線ドライバ X<sub>D</sub>R に供給する。

#### 【 0 0 9 2 】

映像信号線ドライバ X<sub>D</sub>R は、各水平走査期間において、水平走査制御信号の制御のもとで、デジタル映像信号をアナログ形式に変換するとともに、それにより得られる映像信号 V<sub>sig</sub> を複数の映像信号線 D<sub>a</sub>t<sub>a</sub>N に対して並列的に供給する。

#### 【 0 0 9 3 】

走査信号線ドライバ Y<sub>D</sub>R は、垂直走査制御信号の制御のもとで、各表示期間 ( = 1 フレーム期間 + 垂直プランギング期間 = 補正期間 + 書込期間 + 有効表示期間 ) において、例えば、リセット期間 + 閾値キャンセル期間、書込期間、有効表示期間に対応して選択用スイッチ SW<sub>1</sub> をオフ状態 オン状態 オフ状態のように変化させる第 1 走査信号を複数本の走査信号線 S<sub>c</sub>a<sub>n</sub>M<sub>a</sub> に順次供給する。なお、この例では、補正期間は、リセット期間と閾値キャンセル期間との和に等しい。また、ここでは、走査信号線 S<sub>c</sub>a<sub>n</sub>M<sub>a</sub> に供給する第 1 走査信号が、第 1 接続期間に対応して選択用スイッチ SW<sub>1</sub> オン状態とするレ

10

20

30

40

50

ベルへと変化してから、再度、第1接続期間に対応して選択用スイッチ SW1 オン状態とするレベルへと変化するまでの期間を1水平走査期間(1H)と定める。

【0094】

各行の選択用スイッチ SW1 は、それに対応する走査信号線 Scan Ma から供給される第1走査信号により、1表示期間につき1回のみの書込期間に映像信号線 Data N とノードAとの間を導通させ、他の期間は非導通とする。駆動電流制御素子 TR は、選択用スイッチ SW1 の導通状態にある書込期間に映像信号線 Data N を介して供給される映像信号 Vsig に対応した駆動電流 Id を、書込期間に続く有効表示期間(発光期間)において有機EL素子 OLED に供給する。これら映像信号 Vsig は、映像信号の更新周期である1表示期間毎に更新される。

10

【0095】

また、走査信号線ドライバ YDR は、走査信号線 Scan Ma に対して説明したのと同様に、垂直走査制御信号の制御のもとで、各表示期間において、例えば、補正期間及び書込期間+有効表示期間に対応して補正用スイッチ SW2 及びリセットスイッチ SW4 をオン状態 オフ状態のように変化させる第2走査信号を、複数本の走査信号線 Scan Mb に順次供給する。各行の補正用スイッチ SW2 は、それに対応する走査信号線 Scan Mb から供給される第2走査信号により、1表示期間につき1回のみの補正期間に駆動電流制御素子 TR の出力端子と制御端子との間を導通させ、他の期間は非導通とする。同様に、各行のリセットスイッチ SW4 は、それに対応する走査信号線 Scan Mb から供給される第2走査信号により、1表示期間につき1回のみの補正期間にリセット信号線 RST とノードAとの間を導通させ、他の期間は非導通とする。

20

【0096】

さらに、走査信号線ドライバ YDR は、走査信号線 Scan Ma に対して説明したのと同様に、垂直走査制御信号の制御のもとで、各表示期間において、例えば、リセット期間、閾値キャセル期間+書込期間、有効表示期間に対応して出力制御用スイッチ SW3 をオン状態 オフ状態 オン状態のように変化させる第3走査信号を、複数本の走査信号線 Scan Mc に順次供給する。各行の出力制御用スイッチ SW3 は、それに対応する走査信号線 Scan Mc から供給される第3走査信号により、1表示期間につき1回のみのリセット期間及び有効表示期間に駆動電流制御素子 TR と有機EL素子 OLEDとの間を導通させ、他の期間は非導通とする。

30

【0097】

図10は、図9に示す表示装置1の画素PXの等価回路図である。

上述のように、各画素PXは、有機EL素子OLED及び駆動電流制御回路に加え、特性補正回路を備えている。また、駆動電流制御回路は、駆動電流制御素子TRと選択用スイッチ SW1 とキャパシタ C1 とを備えており、特性補正回路は、補正用スイッチ SW2 と出力制御用スイッチ SW3 とリセットスイッチ SW4 とキャパシタ C2 とを備えている。これらスイッチ SW2 乃至 SW4 は、書込期間に先立つ補正期間において、駆動電流制御素子 TR の制御電圧をこの駆動電流制御素子 TR の閾値電圧 Vth とほぼ等しいレベルに初期化するために図11に示す関係でオン/オフされる。

40

【0098】

図11は、図10に示す画素PXの駆動方法の一例を示す図である。

図11に示すように、補正期間はリセット期間と閾値キャセル期間とを含んでいる。

【0099】

リセット期間では、駆動電流制御素子 TR の入力端子と制御端子との間の電圧をその閾値電圧 Vth より大きくなるよう設定する。具体的には、選択用スイッチ SW1 をオフ状態とし、スイッチ SW2 乃至 SW4 をオン状態とする。この動作により、ノードAの電位はリセットスイッチ SW4 を介して供給されるリセット信号 Vrst により上昇し、ノードB及びCの電位は補正用スイッチ SW2 を介して流れる放電電流により低下する。

【0100】

これに続く閾値キャセル期間では、選択用スイッチ SW1 をオフ状態に維持したまま

50

、出力制御用スイッチ SW3 をオフ状態に設定する。これにより、ノード B の電位は、補正用スイッチ SW2 を介して流れる充電電流によって駆動電流制御素子 TR の閾値電圧 V<sub>th</sub> とほぼ等しいレベルにまで上昇する。なお、この際、キャパシタ C2 のノード A 側の電極には、リセット信号 V<sub>rst</sub> が供給されている。

#### 【0101】

書込期間では、選択用スイッチ SW1 をオン N 状態とし、スイッチ SW2 乃至 SW4 を OFF 状態とする。これにより、ノード A には、リセットスイッチ SW4 を介して供給されるリセット信号 V<sub>rst</sub> に代わり、映像信号 V<sub>sig</sub> が選択用スイッチ SW1 を介して供給される。その結果、ノード B の電位は、閾値電圧 V<sub>th</sub> と映像信号 V<sub>sig</sub> との和にほぼ等しくなる。

10

#### 【0102】

有効表示期間では、出力制御用スイッチ SW3 を ON 状態とし、スイッチ SW1, SW2, SW4 を OFF 状態とする。これにより、駆動電流 I<sub>d</sub> が出力制御用スイッチ SW3 を介して有機 EL 素子 OLE D に供給される。ここで、駆動電流 I<sub>d</sub> は、リセット信号 V<sub>rst</sub> と映像信号 V<sub>sig</sub> との電位差により決定されることになり、駆動電流制御素子 TR の閾値電圧 V<sub>th</sub> が画素 P X 間でばらついていたとしても、そのようなばらつきが駆動電流 I<sub>d</sub> に与える影響を排除することができる。

#### 【0103】

さて、本参考例では、この表示装置 1 を以下に説明するように駆動する。

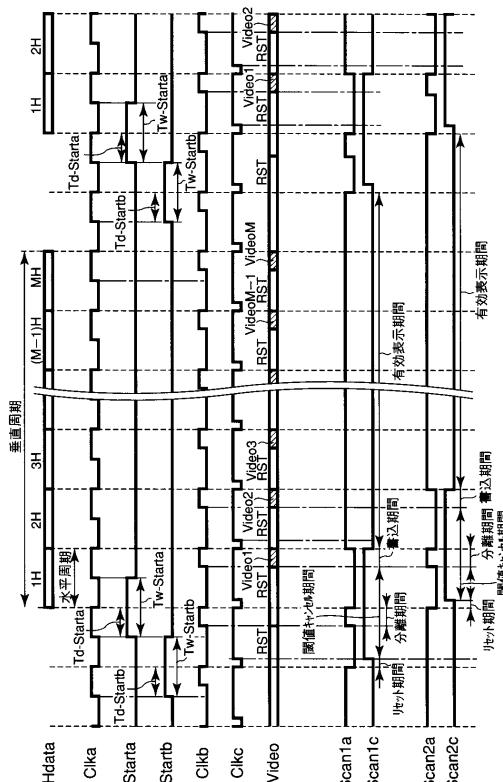

図 12 は、図 9 に示す表示装置 1 で利用可能な駆動方法の一例を示すタイミングチャートである。なお、図 12 に示す参照符号 C1ka, C1kb はクロック信号を示し、Starta, Startb はスタート信号を示し、Video は映像信号を示しており、これらは何れもコントローラ 3 が出力する信号である。また、図 12 に示す参照符号 ScanMa, ScanMb, ScanMc は、それぞれ、走査信号線ドライバ YDR が走査信号線 ScanMa, ScanMb, ScanMc に出力する走査信号を示している。

20

#### 【0104】

走査信号線ドライバ YDR は、スタート信号 Starta 及びクロック信号 C1ka から各水平走査期間に対応した 1 水平期間の幅 (Tw - Starta) の第 1 パルスを生成して順次次段に転送するとともに各段の第 1 パルスを第 1 走査信号として対応する走査信号線へ出力するシフトレジスタと、スタート信号 Startb 及びクロック信号 C1ka から各水平走査検査期間に対応した 1 水平走査期間の整数倍の幅 (Tw - Startb) の第 2 パルスを生成して順次次段に転送するとともに各段の第 2 パルスを第 2 走査信号として対応する走査信号線へ出力するシフトレジスタとを備えている。走査信号線ドライバ YDR は、第 1 パルスを第 1 走査信号として第 1 走査信号線 ScanMa に順次出力し、第 2 パルスを第 2 走査信号として第 2 走査信号線 ScanMb に順次出力する。さらに、走査信号線ドライバ YDR は、第 2 パルスとクロック信号 C1kb とから第 3 走査信号を生成し、これを第 3 走査信号線 ScanMc に順次出力する。

30

#### 【0105】

具体的には、走査信号線ドライバ YDR は、リセット期間では、走査信号線 ScanMa を非選択レベル (ここでは Low レベル), ScanMb, ScanMc を選択レベル (ここでは Low レベル) の走査信号を供給する。閾値キャセル期間では、走査信号線ドライバ YDR は、走査信号線 ScanMa, ScanMb に Low レベルの走査信号を供給し、走査信号線 ScanMc に非選択レベル (ここでは High レベル) の走査信号を供給する。書込期間では、走査信号線ドライバ YDR は、走査信号線 ScanMa を選択レベル (ここでは High レベル), ScanMb, ScanMc を非選択レベル (ここでは High レベル) の走査信号を供給する。有効表示 (発光) 期間では、走査信号線ドライバ YDR は、走査信号線 ScanMa, ScanMc に Low レベルの走査信号を供給し、走査信号線 ScanMb に High レベルの走査信号を供給する。

40

#### 【0106】

本参考例では、走査信号線ドライバ YDR は、或る行の画素 P X への特性補正動作 (=

50

リセット動作 + 閾値キャンセル動作) を開始してから 1 水平周期の  $n$  倍 ( $n$  は 1 以上の整数) だけ経過後に、次の行の画素  $P_X$  への特性補正動作を開始する。すなわち、或る行の画素  $P_X$  に対して書込動作を行う書込期間と次の行の画素に対して特性補正動作を行う補正期間とを少なくとも部分的に重ね合わせる。こうすると、或る行の画素  $P_X$  への特性補正動作と書込動作との双方を完了した後に次の行の画素  $P_X$  への特性補正動作を開始する場合に比べ、有効表示(発光)期間を十分に長く設定しつつ(有効表示期間が 1 表示期間に占める割合は 50% 以上であることが望ましい)、特性補正動作と書込動作との双方に十分な時間を割り当てることが可能となる。

#### 【0107】

また、本参考例では、映像信号  $V_{sig}$  を供給するための映像信号線  $Data_N$  とは別に、リセット信号  $V_{rst}$  を供給するためのリセット信号線  $RST$  を設けている。このようにリセット信号  $V_{rst}$  を供給するための配線を映像信号  $V_{sig}$  を供給するための配線から独立させると、発光動作から特性補正動作への移行の際に、配線容量に起因してリセット信号  $V_{rst}$  のノード A への供給が遅延するのを防止することができる。すなわち、本参考例によれば、リセット信号  $V_{rst}$  の供給に映像信号  $V_{sig}$  を供給するための映像信号線  $Data_N$  を併用した場合とは異なり、画素  $P_X$  の動作を発光動作から特性補正動作へと切り替えると、ノード A の電位は速やかにリセット信号  $V_{rst}$  と等しいレベルへと変化する。そのため、本参考例によれば、ノード A の電位が安定化するまでに比較的長い時間を要することに起因して駆動電流制御素子  $TR$  の制御電圧を完全に初期化できないという状況になり難い。

10

20

#### 【0108】

このように、本参考例によると、特性補正動作と書込動作との双方に十分な時間を割り当てることができる。加えて、本参考例によると、発光動作から特性補正動作への切り替えの際にノード A の電位は速やかにリセット信号  $V_{rst}$  と等しいレベルへと変化させることができる。したがって、本参考例によると、駆動電流制御回路の特性の画素  $P_X$  間でのばらつきに起因した表示ムラを十分に解消することができる。

30

#### 【0109】

なお、補正期間は、有機 EL パネルのサイズや精細度等により適宜設定されるが、本態様クラスの有機 EL パネルにおいては  $50 \mu sec$  以上とすることが望ましい。ここでは、書込期間(すなわち 1 水平周期)は  $21 \mu sec$  程度に設定するのに対し、補正期間は  $50 \mu sec$  程度であり、1 水平周期の長さよりも補正期間を長く設定する場合がある。したがって、本参考例では、図 12 に示すように、或る行の画素  $P_X$  に対して特性補正動作を行う補正期間と次の行の画素  $P_X$  に対して特性補正動作を行う補正期間とを部分的に重ね合わせることにより、複数の水平走査周期にわたって特性補正を行なうことができ、発光時間を削減することなく十分な補正期間を得ることができる。

30

#### 【0110】

また、本参考例においては、リセット信号線  $RST$  を画素列に沿った方向、つまり映像信号線  $Data_N$  に平行な方向に沿って設けている。このような構造によると、選択画素行に対する特性補正動作時に、その画素行に含まれる画素  $P_X$  に対して別々のリセット信号線  $RST$  からリセット信号  $V_{rst}$  を供給することができる。この場合、リセット信号の供給を画素行に沿った方向で供給する場合と比較して、1 配線に集中させることなく、リセット信号線  $RST$  の配線本数分で分割することができるので、リセット信号線  $RST$  内での電圧降下の発生を抑制することができる。そして、この電圧降下に起因して発生する画素間のクロストークを改善し、より均一な画像表示が可能となる。特に、画素数が増大し、走査線数が多くなった場合にも良好な表示動作を行うことが可能となる。

40

#### 【0111】

なお、先に参考例として説明した技術は、図 9 に示す表示装置 1 や図 12 に示す駆動方法に限定されず、様々に変形可能である。

#### 【0112】

例えば、図 9 に示す映像信号線ドライバ  $XDR$  からリセット信号  $V_{rst}$  を供給可能な構

50

造の代わりに、図13に示すようにリセット信号Vrstをリセット信号供給端子RESETから供給可能な構造を採用してもよい。リセット信号を供給する回路をPCB上に形成することにより、アレイ基板の製造歩留まりを向上させることができる。また、アレイ基板の非表示領域である額縁部の面積を低減し、狭額縁化を達成することができる。また、リセット信号の調整を容易に行うことが可能となる。

#### 【0113】

また、図14に示すように、リセット信号線RSTを画素行に沿った方向、つまり走査信号線DataNと平行に配置してもよい。このような構造を採用した表示装置1は、上述したのと同様の方法により駆動することができる。

#### 【0114】

さらに、図15に示すようにリセット信号線RSTを画素行に平行に配置するとともに、隣接する画素行間でリセット信号線RSTを共用させることも可能である。こうすると、画素行の配列方向に配列した配線の数を削減することができ、特に配線が形成された基板側を表示面とする有機EL表示装置においては、発光の取り出し効率をより向上させることができるとなる。

#### 【0115】

詳しく説明すると、リセット信号線RSTを画素行と平行に配置し、例えば、走査信号線ScanMb, ScanMcのうち偶数番目の行に位置したものを省略するとともに、偶数行目の行の画素PX2とその上の行の画素PX1との間で走査信号線ScanMb, ScanMc（ここではMは奇数）及びリセット信号線RSTを共用する。なお、画素PX1, PX2の回路構成は画素PXの回路構成と同様である。

#### 【0116】

この構造によると、リセット信号Vrst並びに第2及び第3走査信号を供給するために必要な配線数及び表示領域内で配線が占有する面積を低減することができる。したがって、表示装置1の大型化及び高精細化が容易になる。

#### 【0117】

なお、図15に示す構造を採用した場合、画素PX1, PX2への特性補正動作は2行毎に行われ、書込動作は1行毎に行われる。具体的には、図16に示すように、2n行目（nは自然数）の画素PX2と2n-1行目の画素PX1とに対して特性補正動作が同時に行われ、それらへの特性補正動作が完了した後に、2(n+1)行目の画素PX2と2(n+1)-1行目の画素PX1とに対して特性補正動作が同時に行われる。また、2n行目の画素PX2と2n-1行目の画素PX1とへの特性補正動作が完了後、2(n+1)行目の画素PX2と2(n+1)-1行目の画素PX1とに対する特性補正動作と並行して、2n行目の画素PX2と2n-1行目の画素PX1とに対して1行毎に書込動作が順次行われる。

#### 【0118】

このように、本参考例では、2n行目の画素PX2に対する特性補正動作と2n-1行目の画素PX1に対する特性補正動作とを同時に実行する。加えて、本参考例では、2n行目の画素PX2に対する補正期間と2n-1行目の画素PX1に対する書込期間とは重ね合わないが、2n行目の画素PX2に対する補正期間と2n+1行目の画素PX1に対する書込期間とは重ね合わせる。したがって、特性補正動作と書込動作との双方に十分な時間を割り当てることができる。また、本参考例では、図9、図13及び図14に示した例と同様に、映像信号Vsigを供給するための映像信号線DataNとは別にリセット信号Vrstを供給するためのリセット信号線RSTを設けているため、発光動作から特性補正動作への切り替えの際にノードAの電位を速やかにリセット信号Vrstと等しいレベルへと変化させることができる。したがって、本参考例でも、上述の参考例で説明したのとほぼ同等の効果が得られる。

#### 【0119】

また、図17に示すように、リセット信号線RSTは、電源端子VDDに接続した配線と共に通化してもよい。

10

20

30

40

50

## 【0120】

この構造によると、リセット信号線 RST を有機EL素子 OLED と電源端子 VDD とを接続する配線の一部と共に用いるため、表示領域内で配線が占有する面積を低減することができる。但し、この構造では、リセット信号 Vrst は電源電圧 VDD と等しくなるため、映像信号 Vsig の最大値が電源電圧 VDD にほぼ等しい必要がある。

## 【0121】

また、図 18 に示すように、リセット信号線 RST を格子状に配置し、互いに交差したリセット信号線 RST 同士をそれらの交差部で接続してもよい。

## 【0122】

このような構造によると、上述の参考例で説明したのと同様の効果を得ることができる。加えて、この構造によると、リセット信号の供給を表示面内に格子状に配置した配線から行うため、リセット信号線 RST における電圧降下をさらに抑制することができる。そのため、これらリセット信号線 RST 間で生じる電圧降下のばらつきが一層低減され、また、電圧降下が発生したとしても、クロストークとして視認されるのを抑制でき、さらに均一な表示が可能となる。

## 【0123】

以上説明したように、或る行の画素 PX に対して書き動作を行う書き期間と次の行の画素に対して特性補正動作を行う補正期間とを少なくとも部分的に重ね合わせると、特性補正動作と書き動作との双方に十分な時間を割り当てることが可能となる。また、画素への映像信号の供給とリセット信号の供給とをそれぞれ独立した配線で行うと、例えば、大型化により負荷が増大した場合或いは高精細化により水平走査期間を短縮せざるを得ない場合であっても、十分な補正期間を確保することができる。さらに、同時に特性補正動作を行う複数の画素に複数本の配線からリセット信号を供給した場合には、電圧降下を抑制できるため、より均一な表示が可能となる。

## 【0124】

なお、上記の参考例に係る技術は、さらに変形が可能である。例えば、先の参考例では、画素 PX に特定の回路構成を採用したが、画素 PX には他の回路構成を採用してもよい。例えば、スイッチ SW1 乃至 SW4 としては、n チャネル TFT を使用してもよく或いは p チャネル TFT を使用してもよい。また、それらスイッチ SW1 乃至 SW4 としてトランスマッシュゲート等の他のスイッチング素子を使用してもよい。例えば、リセットスイッチ SW4 としてトランスマッシュゲートを使用し、先に説明したのとは逆極性の第2走査信号によりリセットスイッチ SW4 のオン / オフを制御してもよい。

## 【0125】

また、先の参考例では、特性補正回路が駆動電流制御素子 TR の閾値電圧 Vth のばらつき補正を行うものである場合について説明したが、特性補正回路は、駆動電流制御回路の特性のばらつきを補正するものであれば、駆動電流制御素子 TR の閾値電圧 Vth に限定したばらつき補正するものでなくてもよい。

## 【0126】

また、図 15 に示す構造では、2 行の画素 PX1, PX2 で 1 本のリセット信号線 RST を共用しているが、3 行以上の画素で 1 本のリセット信号線 RST を共用してもよい。

## 【0127】

また、上述の参考例では、映像信号の書き込みを 1 画素行ずつ行うものについて説明したが、これに限定されず、複数行ずつ同時に書き込みを行ってもよい。

## 【0128】

さらに、上述の参考例では、補正用スイッチ SW2 及びリセットスイッチ SW4 を共通の走査信号線 ScanMb を用いて制御する場合について説明したが、それらのオン / オフは独立した走査信号線を用いて制御してもよい。このように制御することにより、さらに動作を安定させ、表示品位を向上させることが可能となる。

## 【0129】

また、上述の参考例では、映像信号のデジタル - アナログ変換をガラス基板上に形成さ

10

20

30

40

50

れた映像信号線ドライバXDRで行う場合について説明したが、この変換は有機ELパネル2の外部で行ってもよい。

【0130】

また、映像信号線ドライバXDRはアナログ映像信号を時分割で対応する映像信号線DataNに供給するものであってもよい。そして、更に、有機EL素子へ供給する電源電圧を発光色毎に設定してもよい。

【0131】

また、上述の参考例では画素を構成するトランジスタとしてその活性層に多結晶シリコンを用いるものについて説明したが、アモルファスシリコンを用いるものであってもよい。特に、アモルファスシリコンを用いる場合には補正期間の確保が重要となってくるため、上記の参考例に係る技術を適用することが望ましい。

【0132】

さらに、上述の参考例では表示素子として有機EL素子OLEDを使用した有機EL表示装置1について説明したが、流れる電流の大きさに応じて光学特性が変化するものであれば他の表示素子を使用してもよい。すなわち、先の技術は有機EL表示装置以外の表示装置、例えば発光ダイオード表示装置や電界放出表示装置などのように自己発光素子を備えた表示装置、にも適用可能である。

【図面の簡単な説明】

【0133】

【図1】本発明の一態様に係る表示装置を概略的に示す平面図。

20

【図2】図1に示す表示装置の画素の等価回路図。

【図3】図2に示す画素の駆動方法の一例を示す図。

【図4】図1に示す表示装置で利用可能な駆動方法の一例を示すタイミングチャート。

【図5】図1に示す表示装置で利用可能な駆動方法の例を示す図。

【図6】図1に示す表示装置で利用可能な駆動方法の他の例を示す図。

【図7】図1の形態の一変形例に係る表示装置を概略的に示す平面図。

【図8】図7に示す表示装置で利用可能な駆動方法の一例を示すタイミングチャート。

【図9】参考例に係る表示装置を概略的に示す平面図。

【図10】図9に示す表示装置の画素の等価回路図。

30

【図11】図10に示す画素の駆動方法の一例を示す図。

【図12】図9に示す表示装置で利用可能な駆動方法の一例を示すタイミングチャート。

【図13】図9に示す形態の一変形例に係る表示装置を概略的に示す平面図。

【図14】図9に示す形態の一変形例に係る表示装置を概略的に示す平面図。

【図15】図9に示す形態の一変形例に係る表示装置を概略的に示す平面図。

【図16】図15に示す表示装置で利用可能な駆動方法の一例を示すタイミングチャート。

。

【図17】図9に示す形態の一変形例に係る表示装置を概略的に示す平面図。

【図18】図9に示す形態の一変形例に係る表示装置を概略的に示す平面図。

【符号の説明】

【0134】

1...有機EL表示装置、2...有機ELパネル、3...コントローラ、4...光透過性絶縁基板、PX...画素、PX1...画素、PX2...画素、YDR...走査信号線ドライバ、XDR...映像信号線ドライバ、ScanMa...走査信号線、ScanMb...走査信号線、ScanMc...走査信号線、DataN...映像信号線、RST...リセット信号線、OLED...有機EL素子、TR...駆動電流制御素子、SW1...選択用スイッチ、SW2...補正用スイッチ、SW3...出力制御用スイッチ、SW4...リセットスイッチ、C1...キャパシタ、C2...キャパシタ、VDD...電源端子、VSS...電源端子、RESET...リセット信号供給端子、A...ノード、B...ノード、C...ノード。

40

【図1】

【図2】

【図3】

【図4】

【図5】

|               | 補正期間 |     |                      |     | 書込期間                 |     | 有効表示期間  |     |

|---------------|------|-----|----------------------|-----|----------------------|-----|---------|-----|

|               | 光外期間 |     | 閾値キャッシュ期間            |     | 書込期間                 |     | 有効表示期間  |     |

| M-1           | SW1  | ON  | OFF                  | ON  | ON                   | OFF | OFF     | OFF |

|               | SW2  | ON  | OFF                  | ON  | ON                   | OFF | OFF     | OFF |

|               | SW3  | ON  | OFF                  | ON  | ON                   | ON  | ON      | ON  |

| M             | SW1  | OFF | ON                   | OFF | ON                   | OFF | ON      | OFF |

|               | SW2  | OFF | ON                   | OFF | ON                   | OFF | OFF     | OFF |

|               | SW3  | ON  | OFF                  | ON  | OFF                  | ON  | ON      | ON  |

| 映像信号/<br>光外信号 |      | RST | Video M <sub>2</sub> | RST | Video M <sub>1</sub> | RST | Video M | RST |

【図6】

|               | 補正期間 |     |                      |     | 書込期間                 |     | 有効表示期間  |     |

|---------------|------|-----|----------------------|-----|----------------------|-----|---------|-----|

|               | 光外期間 |     | 閾値キャッシュ期間            |     | 書込期間                 |     | 有効表示期間  |     |

| M-1           | SW1  | ON  | OFF                  | ON  | ON                   | OFF | OFF     | OFF |

|               | SW2  | ON  | OFF                  | ON  | ON                   | OFF | OFF     | OFF |

|               | SW3  | ON  | OFF                  | ON  | OFF                  | ON  | ON      | ON  |

| M             | SW1  | OFF | ON                   | OFF | ON                   | OFF | ON      | OFF |

|               | SW2  | OFF | ON                   | OFF | ON                   | OFF | OFF     | OFF |

|               | SW3  | ON  | OFF                  | ON  | OFF                  | ON  | ON      | ON  |

| 映像信号/<br>光外信号 |      | RST | Video M <sub>2</sub> | RST | Video M <sub>1</sub> | RST | Video M | RST |

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

### 【図13】

【 図 1 4 】

【図15】

【図16】

【図17】

【図18】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 2 A |

| G 0 9 G | 3/20  | 6 8 0 G |

| H 0 5 B | 33/14 | A       |

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 青木 良郎

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

(72)発明者 仲戸川 博人

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 3K007 AB17 BA06 DB03 GA00 GA04

5C080 AA06 BB05 DD03 EE29 FF11 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2005258326A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2005-09-22 |

| 申请号            | JP2004073145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2004-03-15 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 青木良朗<br>仲戸川博人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 青木 良朗<br>仲戸川 博人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/30.K G09G3/20.611.H G09G3/20.621.A G09G3/20.624.B G09G3/20.641.D G09G3/20.642.A<br>G09G3/20.680.G H05B33/14.A G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 5C080/AA06 5C080/BB05 5C080<br>/DD03 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 3K107/AA01 3K107/BB01<br>3K107/CC33 3K107/EE03 3K107/HH00 3K107/HH02 3K107/HH04 3K107/HH05 5C380/AA01 5C380<br>/AA03 5C380/AB06 5C380/AB18 5C380/AB22 5C380/AB23 5C380/AB34 5C380/AB45 5C380/AB46<br>5C380/AC04 5C380/AC11 5C380/AC12 5C380/BA12 5C380/BA17 5C380/BA19 5C380/BA20 5C380<br>/BA29 5C380/BA31 5C380/BA34 5C380/BA38 5C380/BA39 5C380/BB08 5C380/CA04 5C380/CA08<br>5C380/CA12 5C380/CA32 5C380/CA53 5C380/CA54 5C380/CB01 5C380/CB02 5C380/CB16 5C380<br>/CB17 5C380/CB31 5C380/CC04 5C380/CC05 5C380/CC07 5C380/CC26 5C380/CC27 5C380/CC33<br>5C380/CC39 5C380/CC52 5C380/CC61 5C380/CC63 5C380/CC64 5C380/CC77 5C380/CD024 5C380<br>/CD025 5C380/CE20 5C380/CF07 5C380/DA02 5C380/DA06 5C380/DA32 5C380/DA47 5C380/HA02<br>5C380/HA11 |         |            |

| 代理人(译)         | 河野 哲<br>中村诚                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | <a href="#">JP4945063B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

### 摘要(译)

解决的问题：提供一种能够为特性校正操作和写入操作两者分配足够的时间的显示装置及其驱动方法。在本发明的显示装置1中，在显示期间，通过显示元件OLED对像素PX进行记录，并经由视频信号线DataN提供视频信号，并提供与之相对应的大小的驱动电流。在有效显示周期期间在显示元件OLED中流动的驱动电流控制电路与在写入周期之前的校正周期期间经由视频信号线DataN被提供有复位信号的驱动电流控制电路的像素PX之间。对像素PX的每一行依次执行校正像素PX的特性变化的特性校正电路以及特性校正操作和写入操作。对前一行的像素PX执行写入操作。[选型图]图1