(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-106993

(P2005-106993A)

(43) 公開日 平成17年4月21日(2005.4.21)

(51) Int.Cl.<sup>7</sup>

G09F 9/30

H05B 33/14

F 1

G09F 9/30

338

テーマコード(参考)

G09F 9/30

365Z

3K007

H05B 33/14

5C094

A

審査請求 未請求 請求項の数 5 O L (全 8 頁)

(21) 出願番号

特願2003-337933 (P2003-337933)

(22) 出願日

平成15年9月29日 (2003.9.29)

(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100075258

弁理士 吉田 研二

(74) 代理人 100096976

弁理士 石田 純

(72) 発明者 松本 昭一郎

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内F ターム(参考) 3K007 AB03 BA06 DB03 FA00 GA00

5C094 AA07 BA03 BA29 CA19 EA04

FA10

(54) 【発明の名称】有機ELパネル

## (57) 【要約】

【課題】有機ELパネルの開口率を上昇する。

【解決手段】駆動トランジスタ2は、ドライン領域2dが、コンタクトを介し電源ラインPLに接続され、ソース2s領域がコンタクトを介し、有機EL素子4の透明電極に接続されている。そして、チャネル領域2cは、略L字型に折れ曲がっている。そこで、ゲート電極2gは、電源ラインPLと平行な方向からチャネル領域2c上に真っすぐのばすことができ、その配置が単純化され、これによって開口率を上昇することができる。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

一対の電極間に少なくとも有機発光層を有する有機EL素子を行列配置した有機ELパネルであって、

前記有機EL素子に電源ラインからの電流を供給する駆動トランジスタは、略L字型に折れ曲がる形状の半導体層を有し、

この半導体層の両端部にはソース領域と、ドレイン領域が形成されており、

ソース領域とドレイン領域の中間部には、前記略L字型の半導体層の一辺上を直線状にのびるゲート電極によって覆われたチャネル領域が形成されていることを特徴とする有機ELパネル。

**【請求項 2】**

請求項1に記載の有機ELパネルにおいて、

前記電源ラインは、列方向に伸び、

前記半導体層は、前記電源ラインに沿って伸びる第1の部分と、ここからほぼ直角に折れ曲がる第2の部分とからなっていることを特徴とする有機ELパネル。

**【請求項 3】**

請求項2に記載の有機ELパネルにおいて、

前記ゲート電極は、前記第1の部分と同一方向に伸びることを特徴とする有機ELパネル。

**【請求項 4】**

請求項2または3に記載の有機ELパネルにおいて、

前記第1の部分の先端部は、前記電源ラインに接続され、前記第2の部分は前記有機EL素子に接続されることを特徴とする有機ELパネル。

**【請求項 5】**

請求項4に記載の有機ELパネルにおいて、

前記電源ラインは、前記駆動トランジスタ側に突出する突出部を有し、この突出部と前記第1の部分がコンタクトを介し接続されることを特徴とする有機ELパネル。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、一対の電極間に少なくとも有機発光層を有する有機EL素子を行列配置した有機ELパネルに関する。

**【背景技術】****【0002】**

従来より、液晶ディスプレイに代わる次世代のフラットディスプレイの一つとして有機エレクトロルミネッセンス(以下ELという)ディスプレイが注目されている。このディスプレイパネル(以下有機ELパネルという)では、各画素に用いる有機発光層の発光材料を変更することで、各画素の発光色を決定できる。そこで、各画素の発光色を異なさせて、RGB表示を行うことができる。

**【0003】**

このような有機ELパネルにおいて、明るい表示を行うためには、各有機EL素子に供給する電流量を多くすればよい。しかし、電流量を多くすれば、それだけ有機EL素子の寿命が短くなるという問題がある。そこで、各画素中における発光領域の面積(開口率)をできるだけ大きくしたいという要求がある。開口率を高くすることで、有機EL素子に流す電流を比較的小さく抑えつつ、明るい表示が行える。

**【0004】****【特許文献1】特開2001-290441公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

10

20

30

40

50

ここで、開口率を上げるということは、各画素における有機EL素子の発光領域の占める割合を上げることである。アクティプタイプの有機ELパネルでは、各画素に有機EL素子を駆動するために最低2つのTFTが設けられており、特に有機EL素子に対する駆動電流を制御する駆動TFTは、回路的に電源ラインと有機EL素子の中間に配置されるため、平面的な配置においても電源ラインおよび有機EL素子の両方に近い場所に配置される。一方、この駆動TFTは、ゲート電圧に応じて有機EL素子の駆動電流を制御するものであり、ゲート長が長い構成になっている。そこで、この駆動TFTの配置が難しいという問題がある。特に、この駆動TFTのゲートラインは、駆動TFTの両端にあるソース、ドレイン電極のコンタクトを迂回しなければならず、この配線が開口率の低下を招くという問題がある。

10

#### 【課題を解決するための手段】

##### 【0006】

本発明は、一対の電極間に少なくとも有機発光層を有する有機EL素子を行列配置した有機ELパネルであって、前記有機EL素子に電源ラインからの電流を供給する駆動トランジスタは、略L字型に折れ曲がる形状の半導体層を有し、この半導体層の両端部にはソース領域と、ドレイン領域が形成されており、ソース領域とドレイン領域の中間部には、前記略L字型の半導体層の一辺上を直線状にのびるゲート電極によって覆われたチャネル領域が形成されていることを特徴とする。

##### 【0007】

また、前記電源ラインは、列方向に伸び、前記半導体層は、前記電源ラインに沿って伸びる第1の部分と、ここからほぼ直角に折れ曲がる第2の部分とからなっていることが好適である。

20

##### 【0008】

また、前記ゲート電極は、前記第1の部分と同一方向に伸びることが好適である。

##### 【0009】

また、前記第1の部分の先端部は、前記電源ラインに接続され、前記第2の部分は前記有機EL素子に接続されることが好適である。

##### 【0010】

また、前記電源ラインは、前記駆動トランジスタ側に突出する突出部を有し、この突出部と前記第1の部分がコンタクトを介し接続されることが好適である。

30

#### 【発明の効果】

##### 【0011】

このように、本発明によれば、駆動トランジスタが略L字状（L字型又は逆L字型）に折れ曲がった形状の半導体層を有する。従って、この配置の自由度が上昇し、特にゲート電極を直線状に形成することができ、ゲート電極の配線パターンを単純化して、開口率を上昇することができる。

#### 【発明を実施するための最良の形態】

##### 【0012】

以下、本発明の実施形態について、図面に基づいて説明する。

##### 【0013】

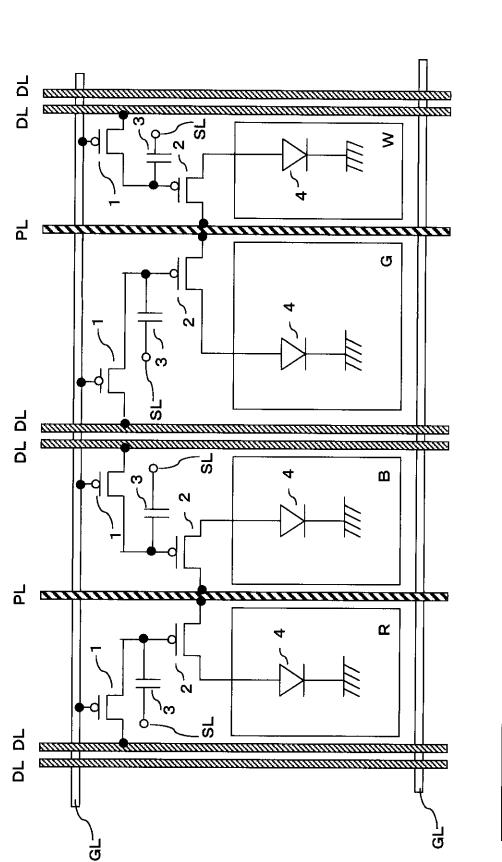

図1には、実施形態の構成が模式的に示してある。データラインDLは、画素1列に対応して1本設けられるが、1つおきの画素列間に2本ずつ配置されている。また、電源ラインPLは、データラインDLが設けられていない画素列間に設けられる。また、ゲートラインGLは、各画素行間に設けられている。

40

##### 【0014】

各画素には、選択TFT1、駆動TFT2、保持容量3、および有機EL素子4が設けられている。選択TFT1は、この例ではpチャネルTFTであり、ソースがデータラインDLに接続され、ドレインが駆動TFT2のゲートに接続され、ゲートがゲートラインGLに接続されている。駆動TFT2は、この例ではpチャネルTFTであり、ソースが電源ラインPLに接続され、ドレインが有機EL素子4のアノードに接続されている。有

50

機 E L 素子 4 のカソードはグランドに接続されている。また、駆動 T F T 2 のゲートには、保持容量 3 の一端が接続され、保持容量 3 の他端は保持容量ライン S L に接続されている。

#### 【 0 0 1 5 】

従って、ゲートライン G L を低レベル ( L ) にすることによって、その行の選択 T F T 1 がオンする。この状態で、各列のデータライン D L に順次該当列の画素データを供給することで、駆動 T F T 2 のゲートが画素データの電圧に設定され、この電圧が保持容量 3 に保持される。そこで、画素データに応じた電流が電源ライン P L から駆動 T F T 2 を介し、有機 E L 素子 4 に供給され、画素データに応じた発光が行われる。

#### 【 0 0 1 6 】

ここで、本実施形態では、各画素は R ( 赤 ) 、 G ( 緑 ) 、 B ( 青 ) 、 W ( 白 ) の 4 色でそれぞれ発光し、各列は同一色で発光するストライプタイプとなっている。この例では、 R 、 B 、 G 、 W の画素が行方向に並んでいる。特に、 R と B の画素はその大きさ ( 幅 ) はほぼ同一であるが、 G の画素は一番大きく、 W の画素は一番小さく設定されている。そして、電源ライン P L は、 R の画素列と、 B の画素列の間に配置されるものと、 G の画素列と W の画素列の間に配置されるものの 2 種類となっている。即ち、電源ライン P L は、 R の画素列と B の画素列で共用し、 G の画素列と W の画素列で共用している。

#### 【 0 0 1 7 】

画素の大きさは、有機 E L 素子 4 の電流効率に基づいて決定されている。ここで、電流効率とは、単位電流当たりの発光量であり、外部量子効率ともいう。本実施形態の場合、表示において利用される最大電流量に対応している。すなわち、必要最大電流が大きいほど電流効率が悪いという関係になる。この電流効率は有機 E L 素子 4 の有機発光材料などにより決定される。

#### 【 0 0 1 8 】

また、この例では、 W の有機 E L 素子 4 の電流効率が最も高く、 G の有機 E L 素子 4 の電流効率が最も低い。フルカラー表示における色バランスを維持するためには、電流効率の悪い色については電流量を大きくする必要がある。一方、有機 E L 素子 4 では、電流密度によってその寿命が決定されるため、各素子における電流密度を一定としたいという要求がある。そこで、電流効率の悪い色の有機 E L 素子 4 ほど面積を大きくし、各有機 E L 素子 4 の電流密度を一定に保っている。

#### 【 0 0 1 9 】

そして、電流効率の最も良い W と、最も悪い G の画素列で、 1 つの電源ライン P L を共用し、電流効率が中間の残りの R 、 B の画素列で 1 つの電源ライン P L を共用する。これによって、各電源ライン P L における電流量が比較的近くなる。電源ライン P L の線幅は、最大電流量によって決定されるが、線幅には上限があり、あまり大きくできない。本実施形態のように電流量のバランスをとることで、 2 種類の電源ライン P L の電流量を近づけて効果的な電流供給が行える。

#### 【 0 0 2 0 】

ここで、従来の場合は、各画素列に対し、 1 本の電源ライン P L と 1 本のデータライン D L が必要であり、これら 2 本のラインが各画素列間に配置されている。デザインルールにより、通常は各配線ライン間には、通常  $4 \mu m$  程度の間隙が設けられる。ここで、 1 つの画素列間に 2 本の電源ライン P L を配置し、 1 本の電源ライン P L の線幅が  $10 \mu m$  程度であった場合を考える。この場合、 2 本の電源ライン P L をあわせた幅は、  $24 \mu m$  になる。本実施形態では、これを 1 本の電源ライン P L にまとめており、この場合に線幅  $15 \mu m$  程度で良いことが分かっている。これは、 2 本の電源ライン P L を 1 本にまとめた場合、  $20 \mu m$  必要になるが、絶対的な値として必要な余裕が 1 本のラインについて決められているため、その分、線幅を小さくできるからであり、また 2 本のラインの間の間隙の  $4 \mu m$  分とあわせて、  $9 \mu m$  の線幅を減少できることになる。これによって、配線配置のための面積を減少して、開口率を大きくすることができます。

#### 【 0 0 2 1 】

10

20

30

40

50

なお、本実施形態では、電流効率をW、R、B、Gの順番としたが、発光材料によっては、異なった順番になる。また、R、G、Bの3色の場合には、発光効率のよいRについて、電源ラインを1本として、比較的発光効率の悪いG、Bとで、1本の電源ラインを共用すればよい。

#### 【0022】

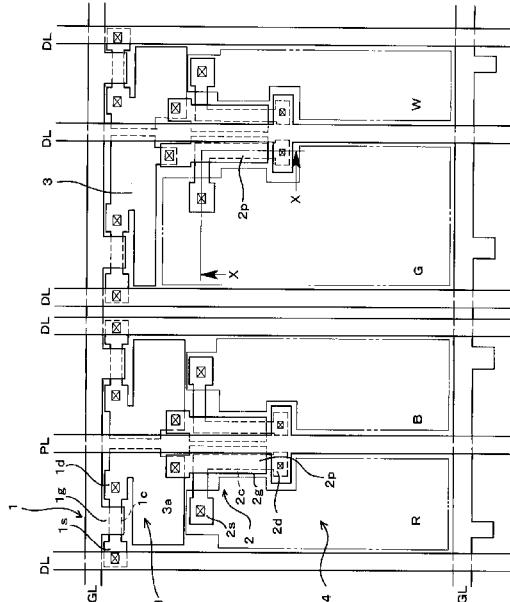

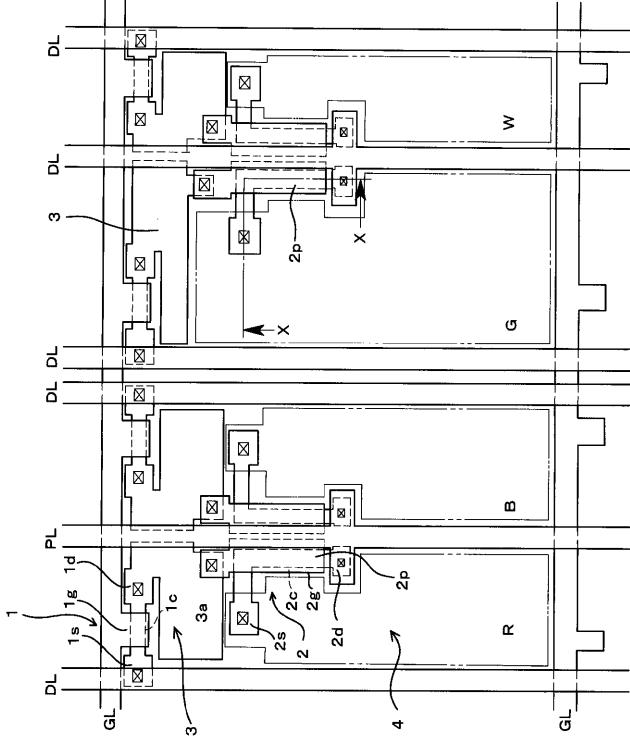

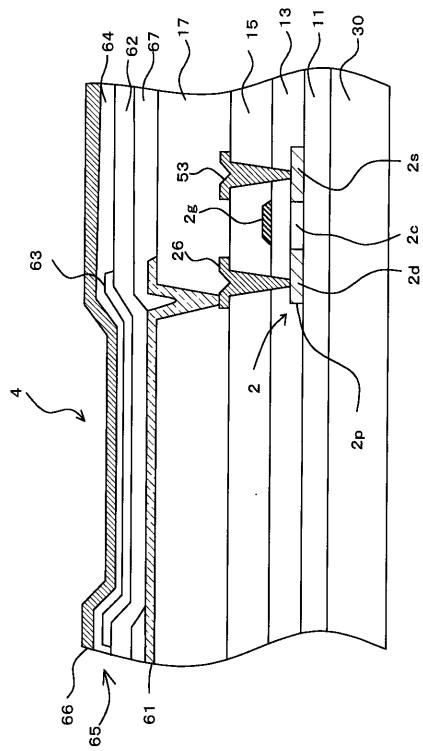

図2には、具体的配置構成を示してある。選択TFT1は半導体層で形成され、そのチャネル領域1c上には、ゲートラインGLの一部が突出されてゲート電極1gとなっている。また、選択TFT1のソース1sは、コンタクトによって、上方のデータラインDLに接続されている。また、ソース領域1sの半導体層はそのまま容量電極3aとなり、これに対向して保持容量ライン(図示省略)が配置されて保持容量3が形成されている。

10

#### 【0023】

容量電極3aには、コンタクトを介し、駆動TFT2のゲート電極2gが接続されている。このゲート電極2gは、電源ラインPLと平行で直線状にのびており、一部は電源ラインPLの下方に配置されている。

#### 【0024】

また、駆動TFT2を構成する半導体層(図中、2s, 2c, 2dの部分、即ち後述の符号2p)は、電源ラインPLから画素領域の内側に突出した部分に設けられたコンタクトから上方に沿ってのびた後、直角に曲がったL字型または逆L字型となっている。そして、他端がコンタクトを介し、上方に位置する有機EL素子4のアノードに接続されている。

20

#### 【0025】

この例では、駆動TFT2はpチャネルであり、電源ラインPLに接続している部分がソース、有機EL素子4のアノードに接続している部分がドレインである。また、ゲート電極は、半導体層のソース、ドレイン間の不純物ドープされていないチャネル領域を覆つて形成されている。

#### 【0026】

このように、駆動TFT2をL字型(または逆L字型)にすることによって、ゲート電極2gの少なくとも一部を電源ラインPLの下側に配置することができ、電源ラインPLの下側空間を利用して開口率を上昇することができる。

30

#### 【0027】

また、有機EL素子4とのコンタクト(図中2s近傍)が画素領域の内側に位置しているため、ゲート電極2gが直線状となり、コンタクト迂回のために、開口率が減少することを防止することができる。

#### 【0028】

さらに、本実施形態では、画素領域の高さを一定としたため、ゲートラインGLを直線とすることができます。また、画素領域の幅を変更したが、ストライプ型のため、電源ラインPLおよびデータラインDLを直線とすることも可能となっている。さらに、画素領域の内部の発光領域の形状を変更することで、発光領域の効率的な配置を達成している。例えば、Gの画素では、画素領域の幅が広いため、補助容量3を選択TFT1の側方にも設け、発光領域を上方にまで延ばし、画素領域を有效地に利用している。

40

#### 【0029】

また、駆動TFTの大きさはすべて同一とするとともに、電源ラインとの構成についても同一にしている。すなわち、図における駆動TFT2の電源ラインPLとの接続点(コンタクト)および有機EL素子4との接続点(コンタクト)はすべて上下方向同一の位置であり、また電源ラインPLからみて同一の位置にある。従って、各画素において、駆動TFT2による電流供給能力を容易に揃えることができる。

#### 【0030】

なお、図2において、有機EL素子4は、透明電極の部分について二点鎖線で示してあるが、図を見やすくするために、小さめに記載してある。

#### 【0031】

50

図3は、1画素の発光領域と駆動TFTの部分の構成を示す断面図(図2のX-X断面図)であり、L字型の駆動TFT2に沿って直角に曲がる線についての断面を示している。ガラス基板30上には、SiNとSiO<sub>2</sub>の積層からなるバッファ層11が全面に形成され、その上に所定のエリア(TFTを形成するエリア)にポリシリコンの半導体層(能動層)2pが形成される。

#### 【0032】

能動層2pおよびバッファ層11を覆って全面にゲート絶縁膜13が形成される。このゲート絶縁膜13は、例えばSiO<sub>2</sub>およびSiNを積層して形成される。このゲート絶縁膜13上方であって、チャネル領域2cの上に例えばCrのゲート電極2gが形成される。そして、ゲート電極2gをマスクとして、能動層2pへ不純物をドープすることで、この能動層2pには、中央部分のゲート電極の下方に不純物がドープされていないチャネル領域2c、その両側に不純物のドープされたソース領域2sおよびドレイン領域2dが形成される。

#### 【0033】

そして、ゲート絶縁膜13およびゲート電極2gを覆って全面に層間絶縁膜15が形成され、この層間絶縁膜15内部にソース領域2s、ドレイン領域2dの上部にコンタクトホールが形成され、このコンタクトホールを介し、層間絶縁膜15の上面に配置されるソース電極53、およびドレイン電極26が形成される。なお、ソース電極53には、電源ライン(図示せず)が接続される。ここで、このようにして形成された駆動TFTは、この例ではpチャネルTFTであるが、nチャネルTFTとすることもできる。

#### 【0034】

層間絶縁膜15を覆って、全面に平坦化膜17が形成され、この平坦化膜17の上に有機EL素子4の陽極として機能する透明電極61が設けられる。また、ドレイン電極26の上方の平坦化膜17には、これらを貫通するコンタクトホールが形成され、このコンタクトホールを介し、ドレイン電極26と透明電極61が接続される。

#### 【0035】

なお、層間絶縁膜15および平坦化膜17には、通常アクリル樹脂などの有機膜が利用されるが、TEOSなどの無機膜を利用することも可能である。また、ソース電極53、ドレイン電極26は、アルミなどの金属が利用され、透明電極61には通常ITOが利用される。

#### 【0036】

透明電極61の上には、全面に形成されたホール輸送層62、発光領域より若干大きめに形成された有機発光層63、全面に形成された電子輸送層64からなる有機層65と、全面に形成された金属製(例えば、アルミ(A1))の対向電極66が陰極として形成されている。

#### 【0037】

透明電極61の周辺部分上のホール輸送層62の下方には、平坦化膜67が形成されており、この平坦化膜67によって、各画素の発光領域が透明電極61上であって、ホール輸送層62が透明電極61と直接接している部分が限定され、ここが発光領域となる。なお、平坦化膜67にも、通常アクリル樹脂などの有機膜が利用されるがTEOSなどの無機膜を利用することも可能である。

#### 【0038】

なお、ホール輸送層62、有機発光層63、電子輸送層64には、有機EL素子に通常利用される材料が使用され、有機発光層63の材料(通常はドーパント)によって、発光色が決定される。例えば、ホール輸送層62にはNPB、赤色の有機発光層63にはTBA(DN+DCJT)B、緑色の有機発光層63にはAlq3+CFDMA、青色の有機発光層63にはTBA(DN+TB)P、電子輸送層64にはAlq3等が用いられる。

#### 【0039】

このような構成において、ゲート電極2gの設定電圧に応じて、駆動TFT2がオンすると、電源ラインからの電流が、透明電極61から対向電極66に流れ、この電流によっ

10

20

30

40

50

て有機発光層 63において、発光が起こり、この光が、透明電極 61、平坦化膜 17、層間絶縁膜 15、ゲート絶縁膜 13、およびガラス基板 30を通過し、図における下方に射出される。

**【図面の簡単な説明】**

**【0040】**

【図1】実施形態の平面構成を模式的に示す図である。

【図2】実施形態の平面構成を示す図である。

【図3】実施形態の要部の断面を示す図である。

**【符号の説明】**

**【0041】**

1 選択TFT、2 駆動TFT、3 保持容量、4 有機EL素子。

10

**【図1】**

**【図2】**

【図3】

|                |                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL面板                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2005106993A</a>                                                                                                                                                   | 公开(公告)日 | 2005-04-21 |

| 申请号            | JP2003337933                                                                                                                                                                    | 申请日     | 2003-09-29 |

| [标]申请(专利权)人(译) | 三洋电机株式会社                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社                                                                                                                                                                        |         |            |

| [标]发明人         | 松本昭一郎                                                                                                                                                                           |         |            |

| 发明人            | 松本 昭一郎                                                                                                                                                                          |         |            |

| IPC分类号         | H01L51/50 G09F9/30 G09G3/10 H01L21/77 H01L27/12 H01L27/32 H01L29/786 H05B33/00 H05B33/08 H05B33/12 H05B33/14                                                                    |         |            |

| CPC分类号         | H01L27/1214 G09G2300/0452 G09G2300/0842 H01L27/3213 H01L27/3244 H01L27/3262 H01L29/78696                                                                                        |         |            |

| FI分类号          | G09F9/30.338 G09F9/30.365.Z H05B33/14.A G09F9/30.365 H01L27/32                                                                                                                  |         |            |

| F-TERM分类号      | 3K007/AB03 3K007/BA06 3K007/DB03 3K007/FA00 3K007/GA00 5C094/AA07 5C094/BA03 5C094/BA29 5C094/CA19 5C094/EA04 5C094/FA10 3K107/AA01 3K107/BB01 3K107/CC36 3K107/DD02 3K107/EE04 |         |            |

| 代理人(译)         | 吉田健治<br>石田 纯                                                                                                                                                                    |         |            |

| 其他公开文献         | <a href="#">JP4443179B2</a>                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                       |         |            |

### 摘要(译)

要解决的问题：增加有机EL面板的数值孔径。在驱动晶体管2中，漏极区域2d经由接触连接到电源线PL，并且源极2s区域经由接触连接到有机EL元件4的透明电极。沟道区2c弯曲成大致L形。因此，栅电极2g可以从平行于电源线PL的方向直线延伸到沟道区域2c的上方，并且其布置被简化，从而增加了开口率。.The