(19) 日本国特許庁 (JP)

(12) 公 開 特 許 公 報(A)

(11) 特許出願公開番号

特開2006-284941

(P2006-284941A)

(43) 公開日 平成18年10月19日(2006. 10. 19)

| (51) Int.Cl.                 | F 1  |       |      | テーマコード (参考) |

|------------------------------|------|-------|------|-------------|

| <b>G09G</b> 3/30 (2006.01)   | GO9G | 3/30  | J    | 5C080       |

| <b>H01L</b> 29/786 (2006.01) | HO1L | 29/78 | 623A | 5C094       |

| <b>G09G</b> 3/20 (2006.01)   | HO1L | 29/78 | 614  | 5F110       |

| <b>G09F</b> 9/30 (2006.01)   | GO9G | 3/20  | 624B |             |

|                              | GO9F | 9/30  | 338  |             |

審査請求 未請求 請求項の数 5 O.L. (全 11 頁) 最終頁に続く

|           |                              |          |                      |

|-----------|------------------------------|----------|----------------------|

| (21) 出願番号 | 特願2005-105096 (P2005-105096) | (71) 出願人 | 302020207            |

| (22) 出願日  | 平成17年3月31日 (2005. 3. 31)     |          | 東芝松下ディスプレイテクノロジー株式会社 |

|           |                              |          | 東京都港区港南4-1-8         |

| (74) 代理人  | 100058479                    |          | 弁理士 鈴江 武彦            |

| (74) 代理人  | 100091351                    |          | 弁理士 河野 哲             |

| (74) 代理人  | 100088683                    |          | 弁理士 中村 誠             |

| (74) 代理人  | 100108855                    |          | 弁理士 蔡田 昌俊            |

| (74) 代理人  | 100075672                    |          | 弁理士 峰 隆司             |

最終頁に続く

(54) 【発明の名称】 表示装置及びアレイ基板

(57) 【要約】

【課題】直列に接続した複数のダイオード接続スイッチの静電破壊を抑制する。

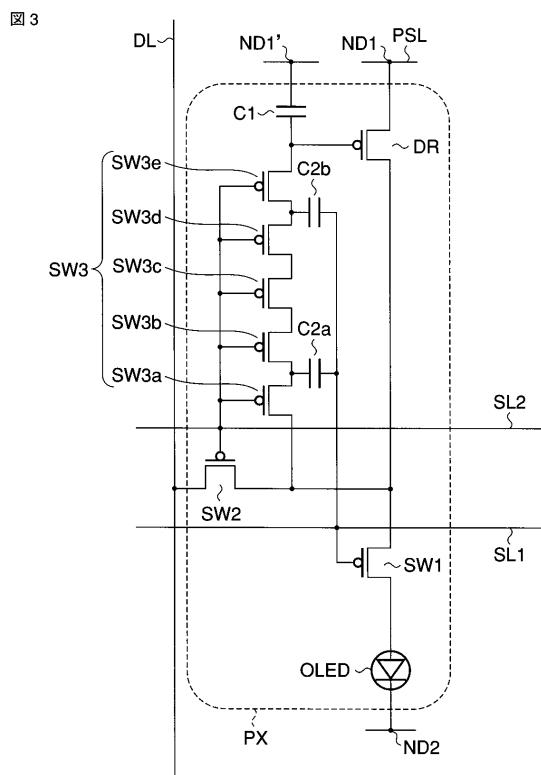

【解決手段】本発明の表示装置は、各画素P Xが、制御端子と電源端子N D 1に接続された第1端子とそれらの間に電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子D Rと、画素電極と電源端子N D 2に接続された対向電極とそれらの間に介在した活性層とを含んだ表示素子O L E Dと、第2端子と画素電極との間に接続された出力制御スイッチS W 1と、第2端子と映像信号線D Lとの間に接続された映像信号供給制御スイッチS W 2と、第2端子と制御端子との間で直列に接続された複数のダイオード接続スイッチS W 3 a乃至S W 3 eと、制御端子と定電位端子N D 1'との間に接続されたキャパシタC 1と、走査信号線S L 1とスイッチS W 3 a乃至S W 3 e同士を接続している接続点との間に接続されたキャパシタC 2 a及びC 2 bとを含んだことを特徴とする。

【選択図】 図 1

## 【特許請求の範囲】

## 【請求項 1】

絶縁基板と、その上で配列した複数の画素と、前記複数の画素が形成する行に沿って配列した複数の走査信号線と、前記複数の画素が形成する列に沿って配列した複数の映像信号線とを具備し、前記複数の画素のそれぞれは、

制御端子と、第1電源端子に接続された第1端子と、それらの間の電圧に対応した大きな駆動電流を出力する第2端子とを含んだ駆動制御素子と、

画素電極と、第2電源端子に接続された対向電極と、それらの間に介在した活性層とを含んだ表示素子と、

前記第2端子と前記画素電極との間に接続された出力制御スイッチと、

10

前記第2端子と前記映像信号線との間に接続された映像信号供給制御スイッチと、

前記第2端子と前記制御端子との間で直列に接続された複数のダイオード接続スイッチと、

前記制御端子と定電位端子との間に接続された第1キャパシタと、

前記複数の走査信号線のうち前記出力制御スイッチの制御端子が接続されたものと前記複数のダイオード接続スイッチ同士を接続している接続点との間に接続された第2キャパシタとを含んだことを特徴とする表示装置。

## 【請求項 2】

絶縁基板と、その上で配列した複数の画素と、前記複数の画素が形成する行に沿って配列した複数の走査信号線と、前記複数の画素が形成する列に沿って配列した複数の映像信号線とを具備し、前記複数の画素のそれぞれは、

20

制御端子と、第1電源端子に接続された第1端子と、それらの間の電圧に対応した大きな駆動電流を出力する第2端子とを含んだ駆動制御素子と、

画素電極と、第2電源端子に接続された対向電極と、それらの間に介在した活性層とを含んだ表示素子と、

前記第2端子と前記画素電極との間に接続された出力制御スイッチと、

30

前記第2端子と前記映像信号線との間に接続された映像信号供給制御スイッチと、

前記第2端子と前記制御端子との間で直列に接続された複数のダイオード接続スイッチと、

前記制御端子と定電位端子との間に接続されたキャパシタとを含み、

前記絶縁基板の正面に垂直な方向から見た場合に、前記複数の画素のそれぞれにおいて、前記第2端子と前記制御端子とを結ぶ導電路は、その画素が含む前記出力制御スイッチの制御端子が接続された前記走査信号線と部分的に重なり合っていることを特徴とする表示装置。

## 【請求項 3】

前記表示素子は有機EL素子であることを特徴とする請求項1又は2に記載の表示装置。

## 【請求項 4】

絶縁基板と、その上で配列した複数の画素回路と、前記複数の画素回路が形成する行に沿って配列した複数の走査信号線と、前記複数の画素回路が形成する列に沿って配列した複数の映像信号線とを具備し、前記複数の画素回路のそれぞれは、

40

制御端子と、電源端子に接続された第1端子と、それらの間の電圧に対応した大きな駆動電流を出力する第2端子とを含んだ駆動制御素子と、

画素電極と、

前記第2端子と前記画素電極との間に接続された出力制御スイッチと、

前記第2端子と前記映像信号線との間に接続された映像信号供給制御スイッチと、

前記第2端子と前記制御端子との間で直列に接続された複数のダイオード接続スイッチと、

前記制御端子と定電位端子との間に接続された第1キャパシタと、

前記複数の走査信号線のうち前記出力制御スイッチの制御端子が接続されたものと前記

50

複数のダイオード接続スイッチ同士を接続している接続点との間に接続された第2キャパシタとを含んだことを特徴とするアレイ基板。

#### 【請求項 5】

絶縁基板と、その上で配列した複数の画素回路と、前記複数の画素回路が形成する行に沿って配列した複数の走査信号線と、前記複数の画素回路が形成する列に沿って配列した複数の映像信号線とを具備し、前記複数の画素のそれぞれは、

制御端子と、電源端子に接続された第1端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子と、

画素電極と、

前記第2端子と前記画素電極との間に接続された出力制御スイッチと、

10

前記第2端子と前記映像信号線との間に接続された映像信号供給制御スイッチと、

前記第2端子と前記制御端子との間で直列に接続された複数のダイオード接続スイッチと、

前記制御端子と定電位端子との間に接続されたキャパシタとを含み、

前記絶縁基板の主面に垂直な方向から見た場合に、前記複数の画素回路のそれぞれにおいて、前記第2端子と前記制御端子とを結ぶ導電路は、その画素回路が含む前記出力制御スイッチの制御端子が接続された前記走査信号線と部分的に重なり合っていることを特徴とするアレイ基板。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は、アクティブマトリクス型表示装置及びそれに用いるアレイ基板に関する。

##### 【背景技術】

##### 【0002】

以下の特許文献1には、カレントコピー型の回路を画素回路に採用したアクティブマトリクス型有機エレクトロルミネッセンス(EL)表示装置が記載されている。このカレントコピー型の画素回路は、駆動制御素子であるnチャネル電界効果トランジスタと、有機EL素子と、キャパシタと、出力制御スイッチと、映像信号供給制御スイッチと、ダイオード接続スイッチとを含んでいる。

##### 【0003】

30

駆動制御素子のソースは低電位の第1電源線に接続されており、キャパシタは駆動制御素子のゲートと第1電源線との間に接続されている。出力制御スイッチは駆動制御素子のドレインと有機EL素子の陰極との間に接続されており、有機EL素子の陽極はより高電位の第2電源線に接続されている。映像信号供給制御スイッチは駆動制御素子のドレインと映像信号線との間に接続されており、ダイオード接続スイッチは駆動制御素子のドレインとゲートとの間に接続されている。なお、各スイッチには、通常、電界効果トランジスタを使用する。

##### 【0004】

このカレントコピー型回路では、駆動制御素子のドレインとゲートとの間に1つのダイオード接続スイッチを接続する代わりに、それらの間で複数のダイオード接続スイッチを直列に接続することができる。こうすると、書き期間において設定したキャパシタの電極間電圧が有効表示期間において変化するのを抑制することができる(特許文献2)。

40

##### 【0005】

しかしながら、本発明者は、本発明を為すに際し、そのような画素回路を含んだ有機EL表示装置の製造においては、有機EL素子を完成するまでの間に、ダイオード接続スイッチなどの静電破壊(electrostatic damage)が生じ易いことを見い出している。

##### 【特許文献1】米国特許第6373454号明細書

##### 【特許文献2】特開2004-246349号公報

##### 【発明の開示】

##### 【発明が解決しようとする課題】

50

## 【0006】

本発明の目的は、直列に接続した複数のダイオード接続スイッチの静電破壊を抑制することにある。

## 【課題を解決するための手段】

## 【0007】

本発明の第1側面によると、絶縁基板と、その上で配列した複数の画素と、前記複数の画素が形成する行に沿って配列した複数の走査信号線と、前記複数の画素が形成する列に沿って配列した複数の映像信号線とを具備し、前記複数の画素のそれぞれは、制御端子と、第1電源端子に接続された第1端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子と、画素電極と、第2電源端子に接続された対向電極と、それらの間に介在した活性層とを含んだ表示素子と、前記第2端子と前記画素電極との間に接続された出力制御スイッチと、前記第2端子と前記映像信号線との間に接続された映像信号供給制御スイッチと、前記第2端子と前記制御端子との間で直列に接続された複数のダイオード接続スイッチと、前記制御端子と定電位端子との間に接続された第1キャパシタと、前記複数の走査信号線のうち前記出力制御スイッチの制御端子が接続されたものと前記複数のダイオード接続スイッチ同士を接続している接続点との間に接続された第2キャパシタとを含んだことを特徴とする表示装置が提供される。

## 【0008】

本発明の第2側面によると、絶縁基板と、その上で配列した複数の画素と、前記複数の画素が形成する行に沿って配列した複数の走査信号線と、前記複数の画素が形成する列に沿って配列した複数の映像信号線とを具備し、前記複数の画素のそれぞれは、制御端子と、第1電源端子に接続された第1端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子と、画素電極と、第2電源端子に接続された対向電極と、それらの間に介在した活性層とを含んだ表示素子と、前記第2端子と前記画素電極との間に接続された出力制御スイッチと、前記第2端子と前記映像信号線との間に接続された映像信号供給制御スイッチと、前記第2端子と前記制御端子との間で直列に接続された複数のダイオード接続スイッチと、前記制御端子と定電位端子との間に接続されたキャパシタとを含み、前記絶縁基板の主面に垂直な方向から見た場合に、前記複数の画素のそれれにおいて、前記第2端子と前記制御端子とを結ぶ導電路は、その画素が含む前記出力制御スイッチの制御端子が接続された前記走査信号線と部分的に重なり合っていることを特徴とする表示装置が提供される。

## 【0009】

本発明の第3側面によると、絶縁基板と、その上で配列した複数の画素回路と、前記複数の画素回路が形成する行に沿って配列した複数の走査信号線と、前記複数の画素回路が形成する列に沿って配列した複数の映像信号線とを具備し、前記複数の画素回路のそれぞれは、制御端子と、電源端子に接続された第1端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子と、画素電極と、前記第2端子と前記画素電極との間に接続された出力制御スイッチと、前記第2端子と前記映像信号線との間に接続された映像信号供給制御スイッチと、前記第2端子と前記制御端子との間で直列に接続された複数のダイオード接続スイッチと、前記制御端子と定電位端子との間に接続された第1キャパシタと、前記複数の走査信号線のうち前記出力制御スイッチの制御端子が接続されたものと前記複数のダイオード接続スイッチ同士を接続している接続点との間に接続された第2キャパシタとを含んだことを特徴とするアレイ基板が提供される。

## 【0010】

本発明の第4側面によると、絶縁基板と、その上で配列した複数の画素回路と、前記複数の画素回路が形成する行に沿って配列した複数の走査信号線と、前記複数の画素回路が形成する列に沿って配列した複数の映像信号線とを具備し、前記複数の画素のそれぞれは、制御端子と、電源端子に接続された第1端子と、それらの間の電圧に対応した大きさの駆動電流を出力する第2端子とを含んだ駆動制御素子と、画素電極と、前記第2端子と前記画素電極との間に接続された出力制御スイッチと、前記第2端子と前記映像信号線との

10

20

30

40

50

間に接続された映像信号供給制御スイッチと、前記第2端子と前記制御端子との間に直列に接続された複数のダイオード接続スイッチと、前記制御端子と定電位端子との間に接続されたキャパシタとを含み、前記絶縁基板の主面に垂直な方向から見た場合に、前記複数の画素回路のそれぞれにおいて、前記第2端子と前記制御端子とを結ぶ導電路は、その画素回路が含む前記出力制御スイッチの制御端子が接続された前記走査信号線と部分的に重なり合っていることを特徴とするアレイ基板が提供される。

【発明の効果】

【0011】

本発明によると、直列に接続した複数のダイオード接続スイッチの静電破壊を抑制することが可能となる。

10

【発明を実施するための最良の形態】

【0012】

以下、本発明の態様について、図面を参照しながら詳細に説明する。なお、各図において、同様又は類似した機能を発揮する構成要素には同一の参照符号を付し、重複する説明は省略する。

20

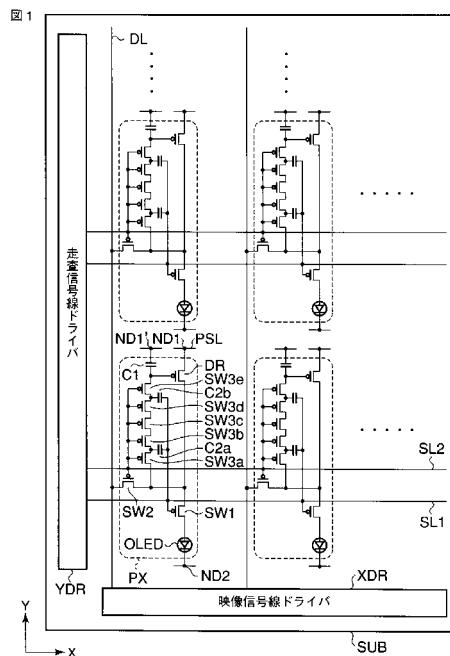

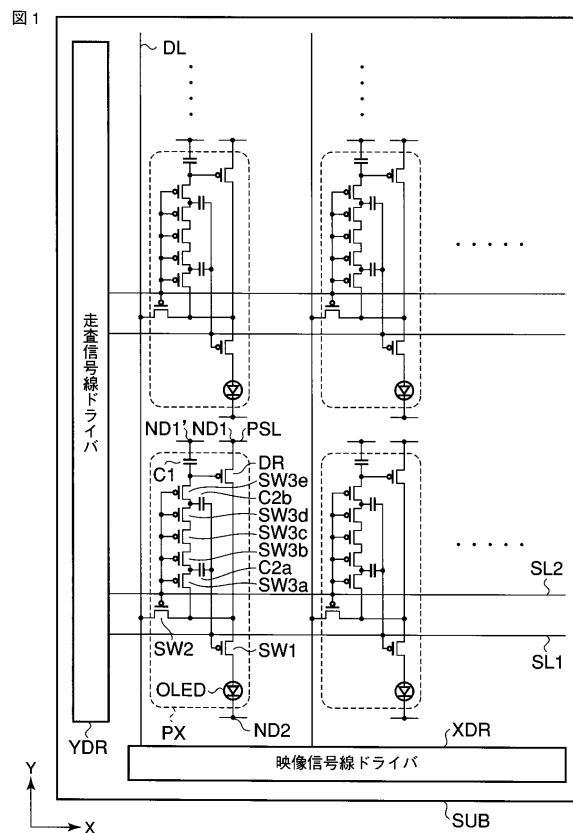

【0013】

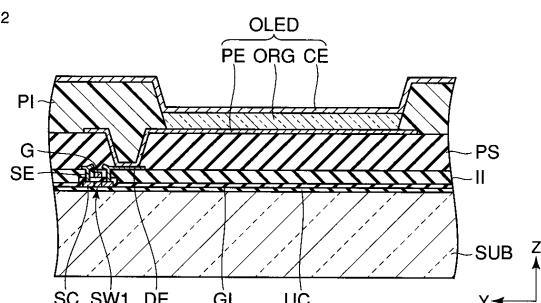

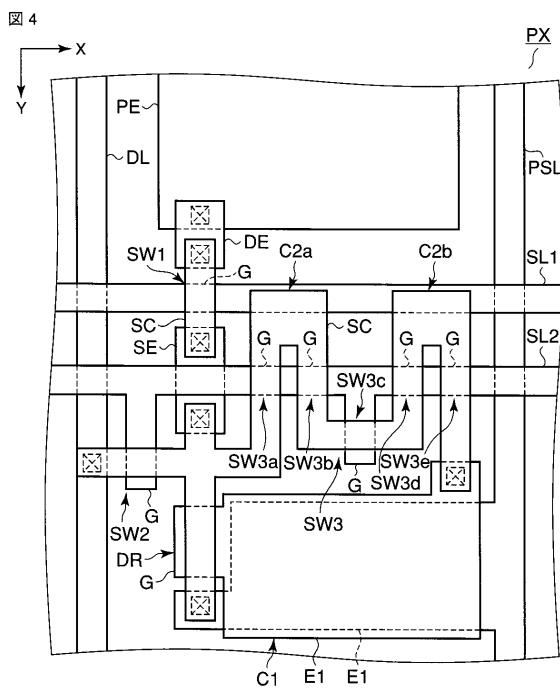

図1は、本発明の一態様に係る表示装置を概略的に示す平面図である。図2は、図1の表示装置に採用可能な構造の一例を概略的に示す断面図である。図3は、図1の表示装置が含む画素の等価回路図である。図4は、図1の表示装置が含む画素に採用可能な構造の一例を概略的に示す平面図である。

20

【0014】

なお、図2では、表示装置を、その表示面、すなわち前面又は光出射面、が下方を向き、背面が上方を向くように描いている。また、図4には、表示面側から見た画素の構造を描いている。

【0015】

この表示装置は、アクティブマトリクス型駆動方式を採用した下面発光型の有機EL表示装置である。この有機EL表示装置は、例えば、ガラス基板などの絶縁基板SUBを含んでいる。

【0016】

基板SUB上には、図2に示すように、アンダーコート層UCとして、例えば、SiN<sub>x</sub>層とSiO<sub>x</sub>層とが順次積層されている。

30

【0017】

アンダーコート層UC上には、例えばチャネル及びソース・ドレインが形成されたポリシリコン層である半導体層SC、例えばTEOS (TetraEthyl OrthoSilicate)などを用いて形成され得るゲート絶縁膜GI、及び例えばMoWなどからなるゲートGが順次積層されており、それらはトップゲート型の薄膜トランジスタを構成している。この例では、これら薄膜トランジスタは、pチャネル薄膜トランジスタであり、図1、図3及び図4の画素PXが含む駆動制御素子DR及びスイッチSW1、SW2及びSW3a乃至SW3eとして利用している。

40

【0018】

半導体層SCのうちスイッチSW3a及びSW3dのドレインに対応した部分は、それぞれ、後述するキャパシタC2aの一方の電極及びキャパシタC2bの一方の電極として利用する。また、それらの上に位置したゲート絶縁膜GIは、キャパシタC2a及びC2bの誘電体層として利用する。

【0019】

ゲート絶縁膜GI上には、図1、図3及び図4に示す走査信号線SL1及びSL2並びに図4に示す電極E1がさらに配置されている。走査信号線SL1及びSL2並びに電極E1は、ゲートGと同一の工程で形成可能である。

【0020】

走査信号線SL1及びSL2は、図1に示すように、各々が画素PXの行方向(X方向

50

)に延びており、画素P Xの列方向(Y方向)に交互に配列している。これら走査信号線S L 1及びS L 2は、走査信号線ドライバY D Rに接続されている。走査信号線S L 1の一部は、キャパシタC 2 a及びC 2 bの各々の他方の電極として利用する。

【0021】

電極E 1は、駆動制御素子D RのゲートGに接続されている。電極E 1は、後述するキャパシタC 1の一方の電極として利用する。

【0022】

ゲート絶縁膜G I、ゲートG、走査信号線S L 1及びS L 2、並びに電極E 1は、図2に示す層間絶縁膜I Iで被覆されている。層間絶縁膜I Iは、例えばプラズマC V D法などにより成膜されたS i O<sub>x</sub>などからなる。この層間絶縁膜I Iのうち電極E 1上の部分は、キャパシタC 1の誘電体層として利用する。

【0023】

層間絶縁膜I I上には、図2と図4とに示すソース電極S E及びドレイン電極D E、図1と図3と図4とに示す映像信号線D L及び電源線P S L、並びに図4に示す電極E 2が配置されている。これらは、同一工程で形成可能であり、例えば、M o / A l / M oの三層構造を有している。

【0024】

ソース電極S E及びドレイン電極D Eは、層間絶縁膜I Iに設けられたコンタクトホールを介して薄膜トランジスタのソース及びドレインに電気的に接続されている。

【0025】

映像信号線D Lは、図1に示すように、各々がY方向に延びており、X方向に配列している。これら映像信号線D Lは、映像信号線ドライバX D Rに接続されている。

【0026】

電源線P S Lは、この例では、図4に示すように、各々がY方向に延びており、X方向に配列している。

【0027】

電極E 2は、電源線P S Lに接続されている。電極E 2は、キャパシタC 1の他方の電極として利用する。

【0028】

ソース電極S E、ドレイン電極D E、映像信号線D L、電源線P S L、及び電極E 2は、図2に示すパッシベーション膜P Sで被覆されている。パッシベーション膜P Sは、例えばS i N<sub>x</sub>などからなる。

【0029】

パッシベーション膜P S上には、図2に示すように、前面電極として、光透過性の第1電極P Eが互いから離間して並置されている。各第1電極P Eは、画素電極であり、図2及び図3に示すように、パッシベーション膜P Sに設けた貫通孔を介して、スイッチS W 1のドレイン電極D Eに接続されている。

【0030】

第1電極P Eは、この例では陽極である。第1電極P Eの材料としては、例えば、I T O(Indium Tin Oxide)のような透明導電性酸化物を使用することができる。

【0031】

パッシベーション膜P S上には、さらに、図2に示す隔壁絶縁層P Iが配置されている。隔壁絶縁層P Iには、第1電極P Eに対応した位置に貫通孔が設けられているか、或いは、第1電極P Eが形成する列又は行に対応した位置にスリットが設けられている。ここでは、一例として、隔壁絶縁層P Iには、第1電極P Eに対応した位置に貫通孔が設けられていることとする。

【0032】

隔壁絶縁層P Iは、例えば、有機絶縁層である。隔壁絶縁層P Iは、例えば、フォトリソグラフィ技術を用いて形成することができる。

【0033】

10

20

30

40

50

第1電極P E上には、活性層として、発光層を含んだ有機物層O R Gが配置されている。発光層は、例えば、発光色が赤色、緑色、又は青色のルミネセンス性有機化合物を含んだ薄膜である。この有機物層O R Gは、発光層に加え、正孔注入層、正孔輸送層、正孔ブロッキング層、電子輸送層、電子注入層などもさらに含むことができる。

【0034】

隔壁絶縁層P I及び有機物層O R Gは、背面電極である第2電極C Eで被覆されている。第2電極C Eは、画素P X間で互いに接続された対向電極、すなわち共通電極、であり、この例では光反射性の陰極である。第2電極C Eは、例えば、パッシベーション膜P Sと隔壁絶縁層P Iとに設けられたコンタクトホールを介して、映像信号線D Lと同一の層上に形成された電極配線(図示せず)に電気的に接続されている。各々の有機EL素子O L E Dは、第1電極P E、有機物層O R G及び第2電極C Eで構成されている。

10

【0035】

各画素P Xを構成している画素回路は、この例では、図1、図3及び図4に示すように、有機EL素子O L E Dと、駆動制御素子D Rと、出力制御スイッチS W 1と、映像信号供給制御スイッチS W 2と、ダイオード接続スイッチS W 3 a乃至S W 3 eと、キャパシタC 1と、キャパシタC 2 a及びC 2 bとを含んでいる。上記の通り、この例では、駆動制御素子D R及びスイッチS W 1、S W 2及びS W 3 a乃至S W 3 eはpチャネル薄膜トランジスタである。また、この例では、ダイオード接続スイッチS W 3 a乃至S W 3 eは第1スイッチ群S W 3を構成しており、映像信号供給制御スイッチS W 2と第1スイッチ群S W 3とは、駆動制御素子D Rのドレインと映像信号線D L、駆動制御素子D Rのドレインと駆動制御素子D Rのゲートとの接続状態を、それらが互いに接続された第1状態と、それらが互いから遮断された第2状態との間で切り替える第2スイッチ群を構成している。

20

【0036】

駆動制御素子D Rと出力制御スイッチS W 1と有機EL素子O L E Dとは、第1電源端子N D 1と第2電源端子N D 2との間で、この順に直列に接続されている。この例では、第1電源端子N D 1は高電位電源端子であり、第2電源端子N D 2は低電位電源端子である。

20

【0037】

出力制御スイッチS W 1のゲートは、走査信号線S L 1に接続されている。映像信号供給制御スイッチS W 2は駆動制御素子D Rのドレインと映像信号線D Lとの間に接続されており、そのゲートは走査信号線S L 2に接続されている。ダイオード接続スイッチS W 3 a乃至S W 3 eは、駆動制御素子D Rのドレインとゲートとの間で、この順に直列に接続されている。ダイオード接続スイッチS W 3 a乃至S W 3 eのゲートは、走査信号線S L 2に接続されている。

30

【0038】

キャパシタC 1は、駆動制御素子D Rのゲートと定電位端子N D 1との間に接続されている。キャパシタC 2 aは、走査信号線S L 1とダイオード接続スイッチS W 3 aのドレインとの間に接続されている。キャパシタC 2 bは、走査信号線S L 1とダイオード接続スイッチS W 3 dのドレインとの間に接続されている。

40

【0039】

なお、この有機EL表示装置から第2電極C Eや有機物層O R Gを除いた構造がアレイ基板に相当している。

【0040】

この有機EL表示装置で画像を表示する場合、例えば、走査信号線S L 1及びS L 2の各々を線順次駆動する。そして、或る画素P Xに映像信号を書き込む書込期間では、まず、走査信号線ドライバY D Rから、先の画素P Xが接続された走査信号線S L 1にスイッチS W 1を開く(O F F)走査信号を電圧信号として出力し、続いて、先の画素P Xが接続された走査信号線S L 2にスイッチS W 2及びS W 3 a乃至S W 3 eを閉じる(O N)走査信号を電圧信号として出力する。この状態で、映像信号線ドライバX D Rから、先の

50

画素 P X が接続された映像信号線 D L に映像信号を電流信号として出力し、駆動制御素子 D R のゲート - ソース間電圧を、先の映像信号に対応した大きさに設定する。その後、走査信号線ドライバ Y D R から、先の画素 P X が接続された走査信号線 S L 2 にスイッチ S W 2 及び S W 3 a 乃至 S W 3 e を開く (OFF) 走査信号を電圧信号として出力し、続いて、先の画素 P X が接続された走査信号線 S L 1 にスイッチ S W 1 を閉じる (ON) 走査信号を電圧信号として出力する。

#### 【0041】

スイッチ S W 1 を閉じている (ON) 有効表示期間では、有機 E L 素子 O L E D には、駆動制御素子 D R のゲート - ソース間電圧に対応した大きさの駆動電流が流れる。有機 E L 素子 O L E D は、駆動電流の大きさに対応した輝度で発光する。

10

#### 【0042】

さて、上記の通り、従来のカレントコピー型回路で複数のダイオード接続スイッチを直列に接続した構造を採用した場合、有機 E L 素子を完成するまでの間に、ダイオード接続スイッチなどの静電破壊が生じ易い。ダイオード接続スイッチなどの静電気破壊を生じた画素は、輝点又は滅点として視認される可能性がある。

本発明者は、この現象について詳細に調べた。その結果、以下の事実を見い出した。

#### 【0043】

画素電極を形成してから有機 E L 素子を完成するまでの間、薄膜トランジスタの半導体層は対向電極で覆われていない。そのため、半導体層は、例えば、蒸着用の金属マスクをアレイ基板に近づけた場合などにキャパシタを形成し、薄膜トランジスタのソース及びドレインに電位変化を生じさせる。

20

#### 【0044】

この電位変化は、半導体層のうち、配線などとキャパシタンスが十分に大きなキャパシタを形成しているか或いはキャパシタンスが十分に大きなキャパシタに接続されている部分又はその近傍では大きくはない。電位変化が小さければ、薄膜トランジスタのソース又はドレインとゲートとの間に大きな電圧が加わることはないため、それらの短絡は生じ難い。

#### 【0045】

しかしながら、従来のカレントコピー型回路で複数のダイオード接続スイッチを直列に接続しただけでは、これらダイオード接続スイッチの半導体層は、配線などとキャパシタンスが十分に大きなキャパシタを形成せず、また、キャパシタンスが十分に大きなキャパシタに接続されもしない。このため、ダイオード接続スイッチのソース又はドレインとゲートとの間には大きな電圧が加わり、それらの短絡が生じ易かった。

30

#### 【0046】

本態様では、ダイオード接続スイッチ S W 3 a のドレインと走査信号線 S L 1 との間にキャパシタ C 2 a を接続し、ダイオード接続スイッチ S W 3 d のドレインと走査信号線 S L 1 との間にキャパシタ C 2 b を接続する。そのため、上述した電位変化を十分に小さくすることができる。したがって、本態様によると、ダイオード接続スイッチ S W 3 a 乃至 S W 3 e のソース又はドレインとゲートとの間に大きな電圧が加わるのを防止することができる。すなわち、ダイオード接続スイッチ S W 3 a 乃至 S W 3 e の静電破壊を生じ難くすることが可能となる。

40

#### 【0047】

キャパシタ C 2 a 及び C 2 b のキャパシタンスは、例えば、0.01 pF 乃至 0.1 pF の範囲内とする。キャパシタ C 2 a 及び C 2 b のキャパシタンスが小さい場合、上述した効果が十分に得られないことがある。キャパシタ C 2 a 及び C 2 b のキャパシタンスが大きい場合、走査信号の鈍りを生じることがある。

#### 【0048】

本態様では、第 1 スイッチ群 S W 3 を 5 つのダイオード接続スイッチ S W 3 a 乃至 S W 3 e で構成しているが、第 1 スイッチ群 S W 3 を構成しているダイオード接続スイッチの数は 2 以上であれば特に制限はない。また、本態様では、有機 E L 表示装置を下面発光型

50

としたが、上面発光型としてもよい。

【図面の簡単な説明】

【0049】

【図1】本発明の一態様に係る表示装置を概略的に示す平面図。

【図2】図1の表示装置に採用可能な構造の一例を概略的に示す断面図。

【図3】図1の表示装置が含む画素の等価回路図。

【図4】図1の表示装置が含む画素に採用可能な構造の一例を概略的に示す平面図。

【符号の説明】

【0050】

C1...キャパシタ、C2a...キャパシタ、C2b...キャパシタ、CE...第2電極、DE...ドレイン電極、DL...映像信号線、DR...駆動制御素子、E1...電極、E2...電極、G...ゲート、GI...ゲート絶縁膜、II...層間絶縁膜、ND1...第1電源端子、ND1'...定電位端子、ND2...第2電源端子、OLED...有機EL素子、ORG...有機物層、PE...第1電極、PI...隔壁絶縁層、PS...パッシベーション膜、PSL...電源線、PX...画素、SC...半導体層、SE...ソース電極、SL1...走査信号線、SL2...走査信号線、SUB...絶縁基板、SW1...出力制御スイッチ、SW2...映像信号供給制御スイッチ、SW3...スイッチ群、SW3a...ダイオード接続スイッチ、SW3b...ダイオード接続スイッチ、SW3c...ダイオード接続スイッチ、SW3d...ダイオード接続スイッチ、SW3e...ダイオード接続スイッチ、UC...アンダーコート層、XDR...映像信号線ドライバ、YDR...走査信号線ドライバ。

10

20

【図1】

【図2】

【図3】

【図4】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 7 0 Z

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 小俣 一由

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

(72)発明者 濵沢 誠

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 5C080 AA06 BB05 DD19 FF11 HH09 JJ03 JJ06

5C094 AA31 BA03 BA29 CA19

5F110 AA22 BB02 CC01 DD02 DD13 DD14 EE06 FF02 GG02 GG13

NN02 NN23 NN35 NN72 NN73

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置和阵列基板                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP2006284941A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2006-10-19 |

| 申请号            | JP2005105096                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2005-03-31 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 小俣一由<br>瀧沢誠                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 小俣一由<br>瀧沢誠                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G09G3/30 H01L29/786 G09G3/20 G09F9/30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G09G3/30.J H01L29/78.623.A H01L29/78.614 G09G3/20.624.B G09F9/30.338 G09G3/20.670.Z<br>G09G3/325 G09G3/3266 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 5C080/AA06 5C080/BB05 5C080/DD19 5C080/FF11 5C080/HH09 5C080/JJ03 5C080/JJ06 5C094<br>/AA31 5C094/BA03 5C094/BA29 5C094/CA19 5F110/AA22 5F110/BB02 5F110/CC01 5F110/DD02<br>5F110/DD13 5F110/DD14 5F110/EE06 5F110/FF02 5F110/GG02 5F110/GG13 5F110/NN02 5F110<br>/NN23 5F110/NN35 5F110/NN72 5F110/NN73 5C380/AA01 5C380/AB06 5C380/AB11 5C380/AB12<br>5C380/AB23 5C380/AB34 5C380/BD10 5C380/CA13 5C380/CB17 5C380/CC13 5C380/CC33 5C380<br>/CC39 5C380/CC52 5C380/CC63 5C380/CC77 5C380/CD038 5C380/DA02 5C380/DA06 5C380/GA14 |         |            |

| 代理人(译)         | 河野哲<br>中村诚                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 其他公开文献         | JP4945087B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

### 摘要(译)

要解决的问题：抑制串联连接的多个二极管开关的静电击穿。根据本发明的显示装置，每个像素PX具有连接到控制端子和电源端子ND1的第一端子，以及用于输出具有与它们之间的电压相对应的大小的驱动电流的第二端子。驱动控制元件DR包括：显示元件OLED，其包括像素电极；对电极，其连接到电源端子ND2；以及有源层，介于它们之间；以及显示元件OLED，其连接在第二端子和像素电极之间。输出控制开关SW1，连接在第二端子和视频信号线DL之间的视频信号提供控制开关SW2以及串联在第二端子和控制端子之间的多个二极管连接开关SW3a至SW3e，连接在控制端子和恒定电位端子ND1#39;之间的电容器C1，以及连接在扫描信号线SL1和连接开关SW3a至SW3e的连接点之间的电容器。其特征在于含有C2a和C2b。[选型图]图1