(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-130469

(P2005-130469A)

(43) 公開日 平成17年5月19日(2005.5.19)

(51) Int.Cl.<sup>7</sup>

H03M 1/74

H03K 17/00

H03K 17/687

H05B 33/14

F 1

H03M 1/74

H03K 17/00

H05B 33/14

H03K 17/687

テーマコード(参考)

3K007

5J022

5J055

A

審査請求 未請求 請求項の数 9 O L (全 12 頁)

(21) 出願番号 特願2004-268119 (P2004-268119)

(22) 出願日 平成16年9月15日 (2004.9.15)

(31) 優先権主張番号 特願2003-339531 (P2003-339531)

(32) 優先日 平成15年9月30日 (2003.9.30)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000116024

ローム株式会社

京都府京都市右京区西院溝崎町21番地

(74) 代理人 100079555

弁理士 梶山 信是

(74) 代理人 100079957

弁理士 山本 富士男

(72) 発明者 前出 淳

京都市右京区西院溝崎町21番地 ローム

株式会社内

(72) 発明者 阿部 真一

京都市右京区西院溝崎町21番地 ローム

株式会社内

最終頁に続く

(54) 【発明の名称】 D/A変換回路、有機EL駆動回路および有機EL表示装置

## (57) 【要約】

## 【課題】

トランジスタセルを多数用いてカレントミラー回路を構成し、このカレントミラー回路を要素とするD/Aを多数設けた回路において、D/Aの変換特性のばらつきによるD/A相互の出力電流のばらつきを低減できるD/A変換回路、有機EL駆動回路および有機EL表示装置を提供することにある。

## 【解決手段】

この発明は、ゲート領域が平面からみて折れ曲げられたストライプ状になっているMOSトランジスタあるいはゲート領域に流れる電流の方向が平面からみて折り返されるストライプ状のチャネルを有するMOSトランジスタを持つ多数のトランジスタセルを形成して、これらのトランジスタセルを用いてカレントミラー回路形のD/Aを構成するものである。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

カレントミラー回路を要素とする D / A 変換回路において、

前記カレントミラー回路は、複数のトランジスタセルを含み、それぞれの前記トランジスタセルは、そのゲート領域が平面からみて折れ曲げられたストライプ状になっている M OS トランジスタあるいは前記ゲート領域に流れる電流の方向が平面からみて折り返されるストライプ状のチャネルが形成された M OS トランジスタを有している D / A 変換回路。

。

## 【請求項 2】

前記トランジスタセルは、前記 M OS トランジスタとこれに直列に接続されたスイッチ動作のトランジスタとからなる直列回路からなる請求項 1 記載の D / A 変換回路。

10

## 【請求項 3】

前記 M OS トランジスタは、サーベンテイン型 M OS トランジスタであり、前記スイッチ動作のトランジスタも M OS トランジスタであって、これら M OS トランジスタが平面からみて矩形の領域に形成されている請求項 2 記載の D / A 変換回路。

。

## 【請求項 4】

前記トランジスタセルは、前記カレントミラー回路の入力側トランジスタおよび複数の出力側トランジスタとしてそれぞれに割当られ、前記複数の出力側トランジスタセルのそれぞれの前記スイッチ動作のトランジスタは、ゲートに表示データの 1 ビットをそれぞれに受けて ON / OFF し、前記表示データを D / A 変換したアナログ電流を前記複数の出力側トランジスタセルの合計出力として発生する請求項 3 記載の D / A 変換回路。

20

## 【請求項 5】

前記アナログ電流は、有機 E L パネルの端子ピンに送出する電流あるいはその基礎となる電流として生成される請求項 4 記載の D / A 変換回路。

。

## 【請求項 6】

前記トランジスタセルは、平面からみて矩形のトランジスタ配列ブロックに縦横に多数配列されたトランジスタセルの中から選択されたセルである請求項 5 記載の D / A 変換回路。

。

## 【請求項 7】

請求項 1 ~ 6 のいずれか 1 項記載の D / A 変換回路を有する有機 E L 駆動回路。

30

## 【請求項 8】

請求項 6 記載の D / A 変換回路において、前記矩形のトランジスタ配列ブロックは、前記パッドの配列方向のパッドピッチの  $3n$  倍 ( $n$  は正の整数) に実質的に対応したパッド配列方向の幅を有しこの幅に対して 4 個以上の前記トランジスタセルが配列されかつ前記パッド配列方向に直交する方向に多数の前記トランジスタセルが配列されて形成され、前記トランジスタ配列ブロック内において R , G , B のそれぞれの前記 D / A 変換回路が前記パッド配列方向に対して直角な方向に順次形成されるように前記トランジスタセルが選択されて I C 化されている請求項 6 記載の D / A 変換回路を有するの有機 E L 駆動回路。

。

## 【請求項 9】

請求項 7 あるいは請求項 8 記載の有機 E L 駆動回路と、この有機 E L 駆動回路から駆動電流を端子ピンに受ける有機 E L パネルとを有する有機 E L 表示装置。

40

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

この発明は、D / A 変換回路、有機 E L 駆動回路および有機 E L 表示装置に関し、詳しくは、有機 E L パネルのカラムピン対応に表示データを D / A 変換してカラム方向の駆動電流あるいはこの駆動電流の元となる電流を生成する電流駆動回路において、D / A 変換回路の変換特性のばらつきによる表示画面の輝度むら、輝度ばらつきを抑えることができるような有機 E L 駆動回路および有機 E L 表示装置の改良に関する。

## 【背景技術】

50

## 【0002】

携帯電話機、P H S、D V D プレーヤ、P D A（携帯端末装置）等に搭載される有機 E L 表示装置の有機 E L 表示パネルでは、カラムラインの数が 396 個（132 × 3）の端子ピン（カラムピン）、ローラインが 162 個の端子ピンを持つものが提案され、カラムライン、ローラインの端子ピンはこれ以上に増加する傾向にある。

このような有機 E L 表示パネルの駆動回路として、カラムピン対応に D / A 変換回路を設けたこの出願人の出願特開 2003-234655 号（特許文献 1）と特開 2003-308043 号（特許文献 2）とがある。後者は、カラムピン対応に設けた D / A 変換回路が表示データと基準電流とを受けて、基準電流に従って表示データを有機 E L パネルのカラムピン対応に D / A 変換してカラム方向の駆動電流あるいはこの駆動電流の元となる電流を生成する。この場合、特に、パッシブマトリックス型の有機 E L パネルでは、容量性負荷となる特性を持つ有機 E L 素子を初期充電して駆動するためにピーク電流が生成される。

【特許文献 1】特開 2003-234655 号公報

【特許文献 2】特開 2003-308043 号公報

## 【0003】

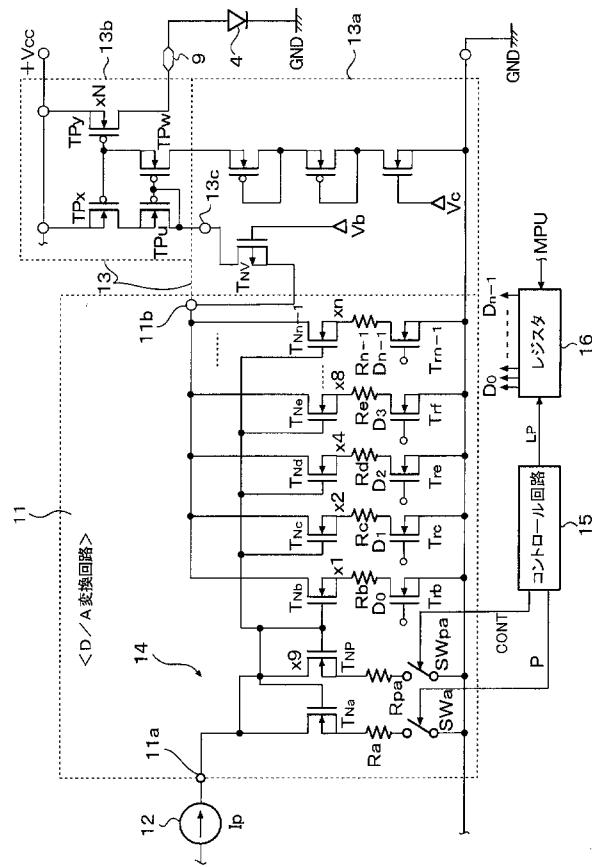

図 6 は、有機 E L 表示パネルの駆動回路のカラムピン対応に設けられる、M O S F E T ランジスタ（M O S ランジスタ）を主体とした D / A 変換回路の一例（特開 2003-308043 号）である。

11 は、電流駆動回路の D / A 変換回路（D / A）である。D / A 11 は、いわゆる電流スイッチング D / A であって、カレントミラー回路により構成されている。この D / A 11 は、入力側トランジスタ T N a に定電流源 12 から入力端子 11 a を介して基準電流 I p を受け、さらに表示データ D 0 ~ D n-1 をレジスタ 16 から受けて基準電流 I p を表示データ倍にして出力する回路である。この D / A 11 は、N チャネルの入力側トランジスタ T N a と、N チャネルの出力側トランジスタ T N b ~ T N n-1 のカレントミラー回路で構成され、さらにピーク電流を生成するために、入力側トランジスタ T N a と並列に N チャネルの M O S ランジスタ T N p を入力側トランジスタとして有している。

## 【0004】

トランジスタ T N p のゲートとドレインは入力端子 11 a に接続されている。トランジスタ T N a とトランジスタ T N p のソースは、抵抗 R a, R P a とスイッチ回路 S W a, S W P a を介してそれぞれ接地されている。スイッチ回路 S W a, S W P a は、コントロール回路 15 からのパルス信号 P, C O N T により O N / O F F が制御される。スイッチ回路 S W a が O N してスイッチ回路 S W P a が O F F 状態で基準電流 I p を受けてピーク電流を D / A 11 が output する。スイッチ回路 S W a, S W P a がともに O N になって、D / A 11 は、基準電流に応じた定常電流を出力する。

なお、出力側トランジスタ T N b ~ T N n-1 の下流に設けられた抵抗 R b ~ R n-1 は、カレントミラー回路の動作電流をバランスさせる抵抗であり、抵抗 R a ~ R n-1 の下流に設けられた N チャネルのトランジスタ T r b ~ T r n-1 は、表示データ D 0 ~ D n-1 により O N / O F F されるスイッチングトランジスタである。

## 【0005】

ここで、出力側トランジスタ T N b ~ T N n-1 は、それぞれのドレインが D / A 11 の出力端子 11 b に接続され、トランジスタ T N a のゲート幅（チャネル幅）に対してそれぞれのトランジスタは、例えば、×1, ×2, ×4, … ×n の倍数の各桁の重みに対応するのゲート幅（チャネル幅）を持っている。各桁の重みに対応するゲート幅（チャネル幅）は、通常、トランジスタセルとして形成された単位トランジスタを複数個パラレルに接続することで形成される。

13 は、出力段電流源であり、駆動レベルシフト回路 13 a と出力段カレントミラー回路 13 b とで構成されている。

駆動レベルシフト回路 13 a は、D / A 11 の出力電流を出力段カレントミラー回路 13 b に伝達するための回路であって、N チャネルの M O S ランジスタ T N v からなる。ト

ランジスタ  $T_{Nv}$  のゲートは、バイアスライン  $V_b$  に接続され、ソース側が出力端子  $11b$  に接続され、ドレインが出力段カレントミラー回路  $13b$  の入力端子  $13c$  に接続されている。

出力段カレントミラー回路  $13b$  は、P チャネル MOS トランジスタ  $T_{Pu}$ ,  $T_{Pw}$  と、出力段カレントミラー回路を構成する P チャネル MOS トランジスタ  $T_{Px}$ ,  $T_{Py}$  とを有している。トランジスタ  $T_{Py}$  は、そのドレインから出力ピン  $9$  を介して有機 EL 素子  $4$  に駆動電流を出力する。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0006】

このような電流駆動回路は、基準電流  $I_p$  に従って D / A 変換してカラム方向の駆動電流あるいはこの駆動電流の元となる電流をカラムピン対応に生成する。しかも、トランジスタセルを多数用いるカレントミラー回路で D / A を構成する。そのため、D / A の変換特性のばらつきがカラムピン相互の出力電流のばらつきとなり、それが表示画面の輝度むら、輝度ばらつきとなって現れてくる。

この輝度むら、輝度ばらつきは、基準電流の電流値を調整しても吸収できないため、D / A 変換回路に変換電流値を調整する調整回路を設けることが必要になる。しかし、この調整回路は、カラムピン対応に設けなければならないために、調整回路の素子数が多くなると回路規模が大きくなつて、IC として電流駆動回路をワンチップ化することが難しくなる。

この発明の目的は、このような従来技術の問題点を解決するものであつて、トランジスタセルを多数用いてカレントミラー回路を構成し、このカレントミラー回路を要素とする D / A を多数設けた回路において、D / A の変換特性のばらつきによる D / A 相互の出力電流のばらつきを低減できる D / A 変換回路を提供することにある。

また、この発明の他の目的は、前記のようなトランジスタセルを多数用いるカレントミラー回路を要素とする D / A を用いる有機 EL 駆動回路および有機 EL 表示装置において、表示画面の輝度むら、輝度ばらつきを抑えることができる有機 EL 駆動回路または有機 EL 表示装置を提供することにある。

##### 【課題を解決するための手段】

##### 【0007】

このような目的を達成するためのこの発明の D / A 変換回路、有機 EL 駆動回路または有機 EL 表示装置の特徴は、カレントミラー回路を要素とする D / A 変換回路において、前記カレントミラー回路が複数のトランジスタセルを含み、それぞれのトランジスタセル（単位トランジスタ）がそのゲート領域が平面からみて折れ曲げられたストライプ状になっている MOS トランジスタあるいはゲート領域に流れる電流の方向が平面からみて折り返されるストライプ状のチャネルが形成された MOS トランジスタを有しているものである。

#### 【発明の効果】

##### 【0008】

ところで、MOS トランジスタによるカレントミラー回路において、所定の入力駆動電流値  $I$  に対する出力側電流値のばらつき  $I$  は、次のような式で表すことができる。

$$I = I - 2 \cdot V_{th} / (V_{GS} - V_{th}) \dots \dots (1)$$

ただし、 $V_{GS}$  は、ゲート - ソース間電圧、 $V_{th}$  は閾値電圧、 $V_{th}$  は、そのトランジスタの設計基準となる閾値電圧に対する差電圧である。

前記の(1)式の  $(V_{GS} - V_{th})$  は、次の式で表すことができる。

$$V_{GS} - V_{th} = \{(2 / \mu_n C_{ox}) \cdot (L / W) \cdot I_D\} \dots \dots (2)$$

ただし、 $\mu_n$  は電子移動度、 $C_{ox}$  はゲート酸化膜の単位面積あたりの容量、 $I_D$  はドレン電流、 $L$  はチャネル長、 $W$  はチャネル幅である。

ところで、駆動ピン数は高解像度化の要請により増加する傾向にある。これにより消費電力が増加するので、その低減がいっそう要求される。そのため、D / A 変換回路の動作

10

20

30

40

50

電源電圧は、例えば、3V程度か、それ以下に抑える必要がある。したがって、V<sub>GS</sub>を大きくすることはできない。

【0009】

そこで、IDを一定値と考えた場合に、(V<sub>GS</sub> - V<sub>th</sub>)を大きくすれば、ばらつき I は小さくなる。(V<sub>GS</sub> - V<sub>th</sub>)を大きくするには、L / Wを大きくすることが必要となる。言い換えれば、その逆数のW / Lを小さくすればよい。

そこで、この発明は、ゲート領域が平面からみて折れ曲げられたストライプ状になっているMOSトランジスタあるいはゲート領域に流れる電流の方向が平面からみて折り返されるストライプ状のチャネルを有するMOSトランジスタを持つトランジスタセルを多数形成して、これらのトランジスタセルを用いてカレントミラー回路形のD/Aを構成する。これによりチャネル長Lの長いトランジスタによりカレントミラー回路を構成することができる。また、これによりW / Lを小さくすることができる。

さらに、チャネルを折れ曲げることでトランジスタセル(単位トランジスタ)の形態は、長方形形状とならず、正方形に近い四角形にすることができる。このことからトランジスタセル間の距離が短くなる上に、集積効率を向上させることができる。また、これによりカレントミラー回路を構成するそれぞれのトランジスタの距離を短くレイアウトすることができる。その結果、カレントミラー回路を構成する各トランジスタの特性上からみたペア性を向上させることができ、D/A変換の電流精度を向上させることができる。

このようなことから、この発明は、カレントミラー回路を用いる多数のD/Aを設けた回路において、D/Aの変換特性のばらつきによるD/A相互の出力電流のばらつきを低減できる。さらに、この発明のD/Aを有機ELパネルの端子ピンに対応に設ける有機EL駆動回路および有機EL表示装置は、カレントミラー回路の変換電流のばらつきが抑制され、D/A変換回路の変換特性のばらつきによる表示画面の輝度むら、輝度ばらつきを抑えることができる。

【発明を実施するための最良の形態】

【0010】

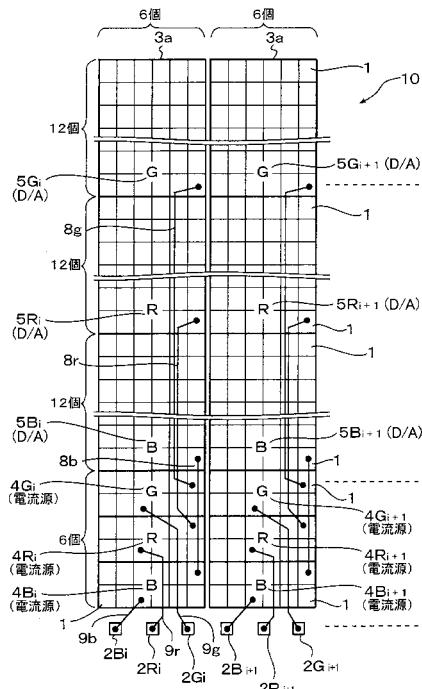

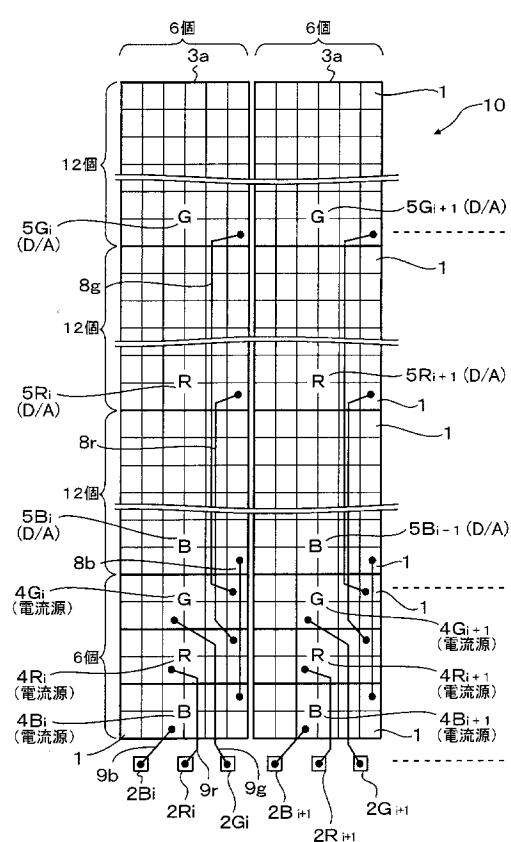

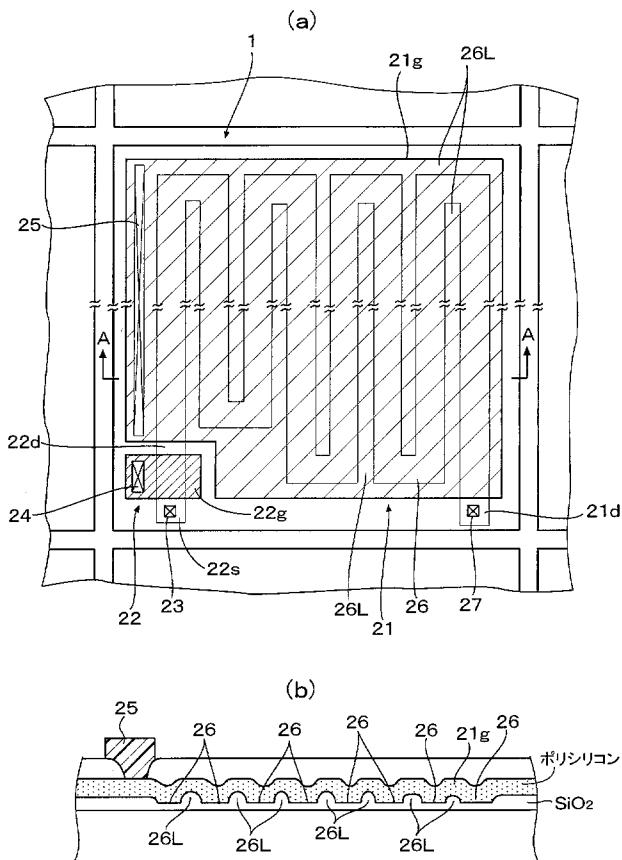

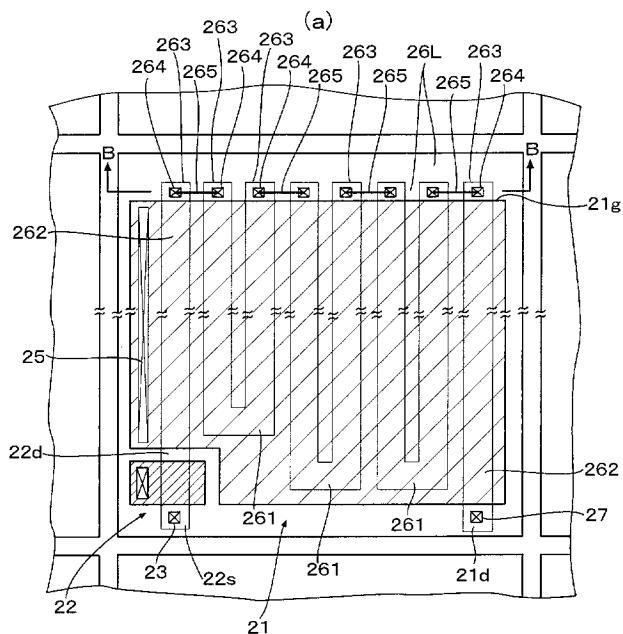

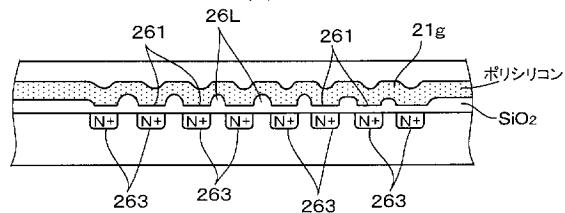

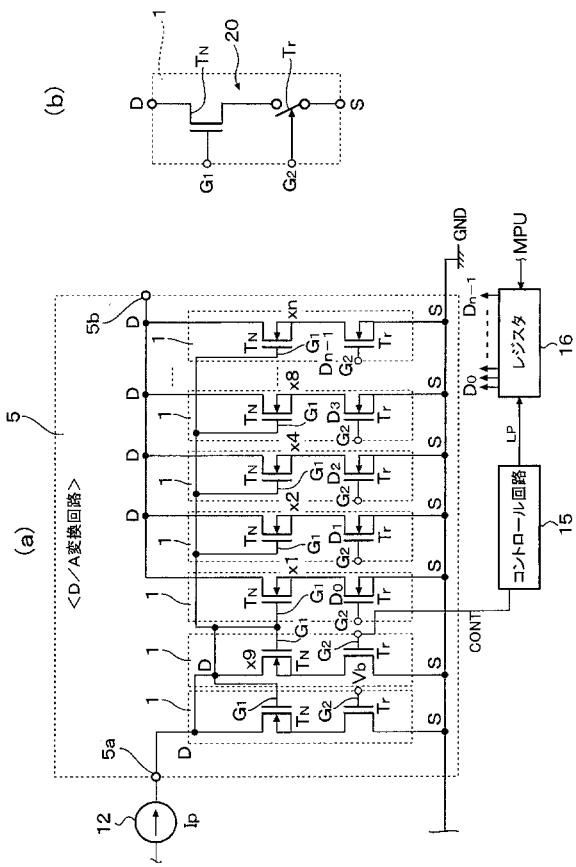

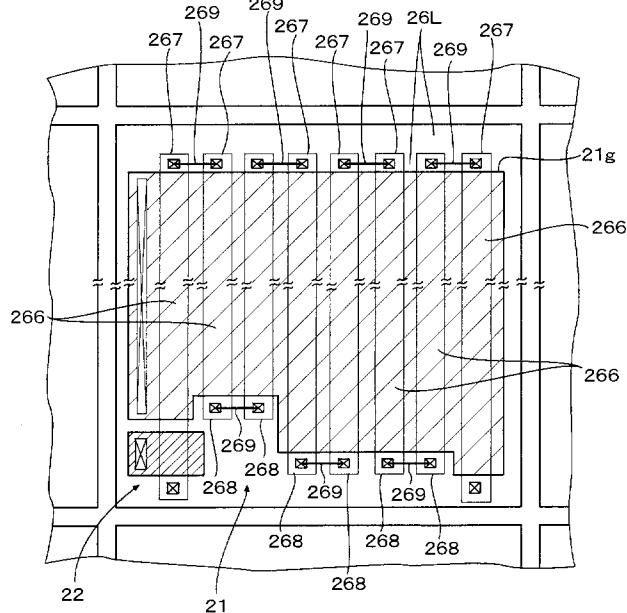

図1は、この発明の有機EL駆動回路を適用した一実施例の電流駆動回路のD/Aと出力段電流源のカレントミラー回路を構成するトランジスタセルについてのレイアウトの説明図、図2(a)は、カレントミラー形のD/Aにおけるトランジスタセルの半導体構造の平面説明図、図2(b)は、そのA-A断面説明図、図3(a)は、カレントミラー形のD/Aにおけるトランジスタセルの他の半導体構造の平面説明図、図3(b)は、そのB-B断面説明図、図4は、カレントミラー形のD/Aにおけるトランジスタセルのさらに他の半導体構造の平面説明図、図5(a)は、前記トランジスタセルを使用したカレントミラー形のD/Aの説明図、そして、図5(b)は、前記トランジスタセルの等価回路である。

図1において、10は、カレントミラーを構成するトランジスタセル(トランジスタ単位回路)1のレイアウトである。このレイアウト10は、有機EL駆動回路のカラムドライバICにおいて、カラムピンに対応に設けられるD/Aと出力段電流源を形成する領域に対応している。

図6に示すD/A11と出力段電流源13のカレントミラーを構成するするために、図1に示すようなレイアウト10で示す配列のトランジスタセル1を使用する。そのため、図6のD/A11は、図5(a)に示すように抵抗R<sub>a</sub>~R<sub>n-1</sub>を使用しない回路構成のD/A5とし、トランジスタセル1を図5(b)に示すように、電流出力用のNチャネルMOSトランジスタT<sub>N</sub>とスイッチ回路となるNチャネルMOSトランジスタT<sub>r</sub>の直列回路20からなる、2個のトランジスタを単位として構成する。さらに、D/A5については、トランジスタセル1のトランジスタT<sub>N</sub>を図2(a), (b)に示すような平面からみて折り返されるストライプ状のチャネルを有するサーペンテイン型トランジスタ21とする。

【0011】

図5(a)に示すD/A5は、トランジスタセル1をカレントミラー回路の2つの入力

10

20

30

40

50

側トランジスタおよび多数の出力側トランジスタとして使用している。出力側トランジスタセル1のトランジスタTrは、そのゲートG2が表示データのうちの1ビットを受け、その“1”、“0”に応じてON/OFFする。そして、2つの入力側トランジスタセル1のドレインDは、共にD/A5の入力端子5aに接続され、多数の出力側トランジスタセル1のドレインDは、D/A5の出力端子5bに接続されている。表示データに対するアナログ変換電流は出力端子5bに発生する。トランジスタTNのゲートG1は、共通に接続され、さらに入力端子5aに接続されている。各トランジスタセル1のソースS(トランジスタTrのソースS)はグランドGNDに接続されている。

トランジスタセル1は、図1のレイアウト10に示すように、ここでは、有機EL駆動回路のカラムピンに接続されるパッド配列方向(口ウ方向に対応)に対して直交する方向(縦方向=カラム方向)が長手方向となる長方形のトランジスタ配列ブロック3aにおいて縦横に配列されている。10

#### 【0012】

トランジスタ配列ブロック3aにおけるトランジスタセル1の総個数は、252個、42個×6個である。このトランジスタ配列ブロック3aは、所定の間隙を挟んでパッド配列方向(横方向=口ウ方向)に3パッドピッチおきに繰り返して形成されている。そして、口ウ方向の2個のトランジスタセル1からなる各列が各パッドにそれぞれ対応している。20

3×パッドピッチ幅の単位の各トランジスタ配列ブロック3aにおいてそれぞれにカレントミラーを構成するトランジスタセル1が選択されて、R, G, BのD/Aのそれぞれのカレントミラー回路が形成される。20

この実施例では、図6のD/A11に対応するものとして図5(a)に示すD/A5の回路をD/A11の回路に換えて使用する。D/A5は、図1のレイアウト10において、R, G, Bに対応してD/A5Biと、D/A5Ri、D/A5Giの各領域におけるそれぞれのトランジスタセル1によりそれぞれに形成される。D/A5Biと、D/A5Ri、D/A5Giのトランジスタセル1によりそれぞれ形成されるD/A5は、図5(a)に示すように、図6のD/A11の抵抗Ra, RPaが削除されて上流側の入力側トランジスタTNa, トランジスタTNpとスイッチ回路SWa, SWPaとがそれぞれ直接接続された回路となっている。また、抵抗Ra～Rn-1が削除されて上流の出力側トランジスタTNa～TNn-1と下流のスイッチ回路であるトランジスタTRA～TRn-1とが直接接続されている。30

#### 【0013】

その結果、カレントミラー回路を構成する入力側と出力側の各回路のトランジスタ構成は、図5(b)に示すようなソースとドレインが接続された電流出力用のNチャネルMOSトランジスタTNとスイッチ回路となるNチャネルMOSトランジスタTrの直列回路を単位回路とすることができます。

トランジスタ配列ブロック3aのパッド2側に出力段電流源13を構成するカレントミラー回路の領域として各電流源4Bi, 4Ri, 4Giのブロックが設けられる。B(青)のトランジスタセル領域が図示するように、2個×6個の領域の電流源4Biとして割り当たられる。この領域の10個のトランジスタセルにより上の配線層でカレントミラー回路を構成する。そして、このカレントミラー回路の出力を上層の配線ライン9bを介してパッド2Biに接続する。電流源4Biでは、10個のトランジスタセルが使用され、残りの2個は予備あるいはダミーのトランジスタセルとされる。40

#### 【0014】

パッド2Bi側を前とすると、これに対してその後ろには、R(赤)のカレントミラーの電流源を構成するトランジスタセル領域が図示するように、2個×6個の領域として割り当たられる。ここを電流源4Riとする。同様に各10個のトランジスタセルでカレントミラー回路を構成して、そのカレントミラー回路の出力を上層の配線ライン9rを介してパッド2Riに接続する。

さらに、その後ろには、G(緑)のカレントミラーの電流源を構成するトランジスタセル領域が図示するように、2個×6個の領域として割り当たられる。ここを電流源4Giと50

する。同様に各 10 個のトランジスタセルでカレントミラー回路を構成して、そのカレントミラー回路の出力を上層の配線ライン 9 g を介してパッド 2 Gi に接続する。

これらの後ろには、カレントミラー構成の電流スイッチング D / A を形成する 12 個 × 6 個の領域が 3 個設けられ、これら領域が同様に B, R, G に対応してこれの順で D / A 5 Bi と、D / A 5 Ri、そして D / A 5 Gi としてそれぞれ割り当てられている。それぞれの D / A は、70 個のトランジスタセルとからなり、2 個のトランジスタセルが予備あるいはダミートランジスタとされる。

#### 【0015】

なお、前記のトランジスタセル（単位トランジスタ）252 個の個数は、カレントミラー回路を構成するものとしては、内部に単位トランジスタの面積の実質的に 2 倍あるいは  $n$  倍のトランジスタあるいはトランジスタセルを部分的に 1 個形成した場合には、それを 2 個あるいは  $n$  個として換算した数値になる。逆に、単位トランジスタの整数分の 1 のトランジスタあるいはトランジスタセルを部分的に 2 個あるいは  $n$  個形成した場合にはカレントミラー回路を構成するものとしては、逆にそれら全体を 1 個と換算した値である。

D / A 5 Bi の出力端子は、電流源 4 Bi の入力端子と上層の配線ライン 8 b を介して接続されている。D / A 5 Ri と D / A 5 Gi もそれぞれ電流源 4 Ri, 電流源 4 Gi と配線ライン 8 r, 8 g を介してそれぞれの出力端子が電流源の対応する入力端子と接続されている。

このようなトランジスタ配列ブロック 3 a が B, R, G のそれぞれ 3 個のパッドごとにレイアウトされる。

なお、図 1 における B, R, G の各電流源 4 Bi, 4 Ri, 4 Gi のブロックについては、これらのブロックをパッド 2 Bi, 2 Ri, 2 Gi に対応して横方向に配列して、D / A 5 Bi, 5 Ri, 5 Gi のみを縦方向に B, R, G の順で配列してもよい。

#### 【0016】

ところで、図 6 における出力段電流源 13 は P チャネル MOS トランジスタであり、D / A 11 は N チャネル MOS トランジスタである。前記の配線ラインによる接続は、D / A 5 Bi と、D / A 5 Ri, D / A 5 Gi を N チャネル MOS トランジスタのトランジスタセル 1 とし、電流源 4 Bi と、電流源 4 Ri, 電流源 4 Gi を P チャネル MOS トランジスタのトランジスタセル 1 とした場合である。したがって、電流源 4 Bi と、電流源 4 Ri, 電流源 4 Gi については、図 5 (b) の等価回路は、図示しないが、N チャネルから P チャネル MOS トランジスタに変わる。

なお、ここでは、各電流源のブロックのトランジスタセル数が D / A のブロックのトランジスタセル数に比べてはるかに少ないので、トランジスタセル 1 の P チャネル, N チャネルの形態は別にして同じトランジスタセル 1 としているが、電流源 4 Bi と、電流源 4 Ri、電流源 4 Gi を D / A 5 Bi と、D / A 5 Ri, D / A 5 Gi とを、例えば、同じ N チャネル MOS トランジスタのトランジスタセル 1 とした場合には、別領域に形成した P チャネル MOS トランジスタのカレントミラー回路を介して D / A 5 Bi と、D / A 5 Ri, D / A 5 Gi の各出力端子と電流源 4 Bi と、電流源 4 Ri, 電流源 4 Gi の各入力端子とをそれぞれ接続することになる。この場合には、N チャネル MOS トランジスタで形成される電流源 4 Bi と、電流源 4 Ri, 電流源 4 Gi とは、図 6 の出力段電流源 13 の場合と異なり、電流シンク型になる。

また、電流源 4 Bi と、電流源 4 Ri, 電流源 4 Gi を構成するトランジスタにはスイッチ動作のトランジスタは不要である。図 5 (b) の等価回路のトランジスタセル 1 の場合には、直列回路 20 のうち電流出力用の MOS トランジスタ TN が使用される。そこで、スイッチ回路となる N チャネル MOS トランジスタ Tr は、ON 状態に設定されて実質的に電流出力用のトランジスタが 1 つ形成されているトランジスタセル 1 として使用される。

#### 【0017】

図 2、図 3 は、このような場合の図 5 (a) に示す D / A 5 の回路を形成する D / A 5 Bi, 5 Ri, 5 Gi の各領域に形成されるトランジスタセル 1 の半導体構造説明図である。

D / A 5 Bi, 5 Ri, 5 Gi のトランジスタセル 1 は、特に、図 5 (b) に示すように、トランジスタ TN とスイッチ回路となるトランジスタ Tr の直列回路 20 で形成される。D /

10

20

30

40

50

A 5 Bi, 5 Ri, 5 Giは、図6のD/A 11に対して抵抗が削除された回路である。そこで、カレントミラー回路の入力側も出力側も直列回路20が単位回路となっている。

具体的には、カレントミラー回路の入力トランジスタ側では直列回路20のトランジスタTNのドレインDが基準電流を受ける入力端子11aに接続され、トランジスタTrのソースSがグランドGNDに接続される。なお、図5(a)の図面一番左側にあるトランジスタセル1に示すように、トランジスタTrのゲートが所定のバイアス電圧Vbに設定されると、これがスイッチ回路ではなく、抵抗になる。実際の回路では、図5(a)の図面一番左側にあるトランジスタセル1のトランジスタTrあるいは図6のスイッチ回路SWaは抵抗に置き換えられる。

前記したように、カレントミラー回路の出力側トランジスタではトランジスタTNのドレインDが出力端子5aに接続され、トランジスタTrのソースSがグランドGNDに接続される。そして、出力側トランジスタの各桁の重み付けに応じて直列回路20のトランジスタセル1が複数個パラレルに接続される。

#### 【0018】

図2(a)は、D/A 5 Bi, 5 Ri, 5 Giのトランジスタセル1のうち上流側のトランジスタTNをサーペンティン型トランジスタとしたものの平面図である。なお、電流源4Biと、電流源4Ri、電流源4Giを構成するトランジスタセル1は、必ずしもサーペンティン型トランジスタの構成を探る必要はない。

21は、トランジスタTNが形成された領域であり、22がトランジスタTrが形成された領域である。22sは、トランジスタTrのソース領域であり、23は、ソースコンタクト領域である。22gは、トランジスタTrのゲート領域であり、24はそのゲートコンタクト領域である。22dは、トランジスタTrのドレイン領域であるとともに、トランジスタTNのソース領域になっている。

21gは、トランジスタTNのゲート領域であり、25は、そのゲートコンタクト領域である。26は、ゲート領域21gのゲート電極の下側にチャネルを形成するためのチャネル形成領域であり、これによりゲートに所定の電圧が加わったときに、ゲート領域は、平面からみて折れ曲げられたストライプ形状のチャネル(反転層)をチャネル形成領域26の直下に形成する。この領域の周囲にはLOCOS(SiO<sub>2</sub>)領域26Lが各ストライプチャネルを分離するために設けられている。21dは、トランジスタTNのドレイン領域であり、27はそのドレインコンタクト領域である。

ここで、チャネル形成領域26は、図2(b)のA-A断面図に示すように、LOCOS領域26Lと交互に配置され、ゲート領域に形成されるチャネルがチャネル形成領域26の範囲で制限される。その結果、平面からみてゲート領域にストライプ状にくねったチャネルを形成できる。これによりゲート領域に形成されるチャネルは、電流の流れる方向が折り返される形状になる。また、これによりトランジスタTNのW/Lを小さくすることがきる。

#### 【0019】

図3(a)は、他のチャネル形成領域の形状であって、チャネル形成領域26をUの字形の折り曲げチャネル形成領域261を1単位として複数個並列に設けて、さらに両側に直線状のストライプ262を設けて、図2(a)のチャネル形成領域26を複数の部分に分割したものである。

ゲート領域21gの外側には、チャネル電流を取り出すチャネルコンタクト領域263が折り曲げ部261, 262の端部にそれぞれ設けられている。この端部同士を上層のコンタクト領域配線層においてコンタクト領域264を介して配線ライン265によりそれぞれ接続して1本の折り曲げチャネルとして形成する。

図3(b)は、そのB-B断面説明図である。チャネルコンタクト領域263は、N<sup>+</sup>の島領域として折り曲げ部261, 262の端部の直下にそれぞれ形成されている。

なお、A-A断面は、図2(b)と同じである。

#### 【0020】

図4は、他のチャネル形成領域であって、単にストライプのチャネル形成領域266を

10

20

30

40

50

複数個並設して、チャネル形成領域 266において図面上下方向に設けたチャネルコンタクト領域 267, 268を設けて、それを配線ライン 269でそれぞれ接続したものである。これによりゲート領域に形成されるチャネルは、平面からみて電流の流れる方向が折り返される形状になる。なお、これについての断面説明図は省略する。

#### 【0021】

以上説明してきたが、図 5 (b) の直列回路 20 は、トランジスタ TN 側が下流でトランジスタ Tr 側が上流となる直列回路であってもよい。さらに、カレントミラー回路を構成するトランジスタ TN 側だけをトランジスタセル 1 として D/A 5Bi, 5Ri, 5Gi のそれぞれの領域に設け、スイッチ動作のトランジスタ Tr は、別の領域に設けられていてよい。したがって、トランジスタセル 1 は、サーペンティン型 MOS トランジスタセルの電流出力用の MOS トランジスタ 1 個だけであってもよい。

また、実施例のトランジスタセル 1 の電流出力用の MOS トランジスタ TN は、ゲート領域が実質的に矩形とされ、ゲート領域に形成されるチャネルをそこに流れる電流の方向が折り返される形状になるようにしている。しかし、MOS トランジスタ TN のゲート領域そのものを平面からみて折れ曲げられたストライプ状にしても同様なチャネルが形成できる。

#### 【産業上の利用可能性】

#### 【0022】

実施例では、D/A のカレントミラー回路についてサーペンティン型 MOS トランジスタセルを用いているが、出力段電流源のカレントミラー回路の単位トランジスタもサーペンティン型 MOS トランジスタセルで構成してもよいことはもちろんである。

また、実施例の図 1 のレイアウトでは、D/A と出力段電流源のカレントミラー回路を構成するそれぞれの領域は、それぞれ 2 個のトランジスタを単位とするトランジスタセル 1 で構成されている。しかし、このトランジスタセル 1 は、2 個以上のトランジスタを単位として構成されていてよい。また、D/A に対して出力段電流源のトランジスタセル数は少なく、また、出力段電流源のカレントミラー回路の単位トランジスタは、スイッチ回路を必要としていないので、N チャネル MOS トランジスタ Tr がない電流出力用の MOS トランジスタ TN が 1 つだけのトランジスタセルとしてもよい。

さらに、実施例のトランジスタセル 1 は、N チャネル MOS トランジスタで構成されているが、これは、P チャネル MOS トランジスタで構成されてもよい。

#### 【図面の簡単な説明】

#### 【0023】

【図 1】図 1 は、この発明の有機 EL 駆動回路を適用した一実施例の電流駆動回路の D/A と出力段電流源のカレントミラー回路を構成するトランジスタセルについてのレイアウトの説明図である。

【図 2】図 2 (a) は、カレントミラー形の D/A におけるトランジスタセルの半導体構造の平面説明図、図 2 (b) は、その A-A 断面説明である。

【図 3】図 3 (a) は、カレントミラー形の D/A におけるトランジスタセルの他の半導体構造の平面説明図、図 3 (b) は、その B-B 断面説明図である。

【図 4】図 4 は、カレントミラー形の D/A におけるトランジスタセルのさらに他の半導体構造の平面説明図である。

【図 5】図 5 (a) は、前記トランジスタセルを使用したカレントミラー形の D/A の説明図、図 5 (b) は、前記トランジスタセルの等価回路である。

【図 6】図 6 は、有機 EL 表示パネルの駆動回路のカラムピン対応に設けられる D/A の一例の説明図である。

#### 【符号の説明】

#### 【0024】

1 ... トランジスタセル (単位トランジスタ)、2 ... パッド、

3, 3a ... 単位トランジスタの配列ブロック、

4Bi, 4Ri, 4Gi ... 電流駆動回路、

5 Bi , 5 Ri , 5 Gi ... D / A、

6 bi ... 出力端子、 7 bi ... 入力端子、

8 b , 8 r , 8 g , 9 b , 9 r , 9 g ... 配線ライン、

10 ...

21 ... トランジスタ TN が形成された領域、

21g ... トランジスタ TN のゲート領域、

21d ... トランジスタ TN のドレイン領域、

22 ... トランジスタ Tr が形成された領域、

22g ... トランジスタ Tr のゲート領域、

22s ... トランジスタ Tr のソース領域、

22d ... トランジスタ Tr のドレイン領域、

23 ... ソースコンタクト領域、

24 , 25 ... ゲートコンタクト領域、

26 ... チャネル形成溝、

26L ... LOCOS 領域、

27 ... ドレインコンタクト領域。

10

【 図 1 】

【 図 2 】

【 図 3 】

(b)

【 図 5 】

【 図 4 】

【図6】

---

フロントページの続き

(72)発明者 藤川 昭夫

京都市右京区西院溝崎町21番地 ローム株式会社内

F ターム(参考) 3K007 AB17 BA06 DB03 GA00 GA04

5J022 AB06 BA01 BA06 CE08 CG01

5J055 AX48 BX09 BX16 CX29 DX22 DX48 EX07 EY21 EZ03 EZ04

EZ24 EZ33 EZ68 FX04 FX12 GX01 GX07

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | D / A转换电路，有机EL驱动电路和有机EL显示装置                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | JP2005130469A                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2005-05-19 |

| 申请号            | JP2004268119                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2004-09-15 |

| [标]申请(专利权)人(译) | 罗姆股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | ROHM株式会社                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 前出淳<br>阿部真一<br>藤川昭夫                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 前出淳<br>阿部真一<br>藤川昭夫                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| IPC分类号         | H01L51/50 H03K17/00 H03K17/687 H03M1/74 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | H03M1/74 H03K17/00.M H05B33/14.A H03K17/687.A H01L27/04 H05B33/14                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 5J022/AB06 5J022/BA01 5J022 /BA06 5J022/CE08 5J022/CG01 5J055/AX48 5J055/BX09 5J055/BX16 5J055/CX29 5J055/DX22 5J055 /DX48 5J055/EX07 5J055/EY21 5J055/EZ03 5J055/EZ04 5J055/EZ24 5J055/EZ33 5J055/EZ68 5J055 /FX04 5J055/FX12 5J055/GX01 5J055/GX07 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH05 5F038/CA02 5F038/CA03 5F038/CA10 5F038/CD16 5F038/DF03 5F038/EZ20 |         |            |

| 代理人(译)         | 梶山 信是<br>山本富士雄                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 优先权            | 2003339531 2003-09-30 JP                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 其他公开文献         | JP4526338B2                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

[问题] 使用大量的晶体管单元构成电流镜电路，并且在具有大量D/A的电路中，由于使用该电流镜电路作为元件，所以由于D/A转换特性的变化，导致D/A之间的输出电流发生变化。一个目的是提供可以减少的D/A转换电路，有机EL驱动电路和有机EL显示装置。[解决方案] 晶体管技术领域本发明涉及大量的晶体管，其具有在俯视图中栅极区域弯曲的MOS晶体管，或者具有在沟道图中流向栅极区域的电流的方向折返的条纹状的沟道的MOS晶体管。形成一个单元，并使用这些晶体管单元形成D/A型电流镜电路。[选型图]图1