(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-37916

(P2005-37916A)

(43) 公開日 平成17年2月10日(2005.2.10)

(51) Int.Cl.<sup>7</sup>

G09G 3/30

G09G 3/20

H03M 1/74

H05B 33/14

F 1

G09G 3/30

K

テーマコード(参考)

3K007

G09G 3/30

H

5C080

G09G 3/20

5J022

G09G 3/20

623B

G09G 3/20

623F

審査請求 未請求 請求項の数 19 O L (全 13 頁) 最終頁に続く

(21) 出願番号

特願2004-181124 (P2004-181124)

(22) 出願日

平成16年6月18日 (2004.6.18)

(31) 優先権主張番号

特願2003-184339 (P2003-184339)

(32) 優先日

平成15年6月27日 (2003.6.27)

(33) 優先権主張国

日本国 (JP)

(71) 出願人 000116024

ローム株式会社

京都府京都市右京区西院溝崎町21番地

(74) 代理人 100079555

弁理士 梶山 信是

(74) 代理人 100079957

弁理士 山本 富士男

(72) 発明者 前出 淳

京都市右京区西院溝崎町21番地 ローム

株式会社内

(72) 発明者 阿部 真一

京都市右京区西院溝崎町21番地 ローム

株式会社内

最終頁に続く

(54) 【発明の名称】有機EL駆動回路および有機EL表示装置

## (57) 【要約】

## 【課題】

輝度むらを低減でき、かつ、製品ごとの輝度ばらつきに与える影響を低減できる有機EL駆動回路および有機EL表示装置を提供することにある。

## 【解決手段】

この発明は、ICチップの回路形成領域において両端に位置するトランジスタブロックが動作対象とされないダミー回路となっているので、このダミー回路より内側に位置するトランジスタブロックに形成されたD/A変換回路あるいはD/A変換回路と出力段の電流源とは、これら回路を形成するトランジスタの物的なストレスの偏りが減少して、D/A変換回路のカレントミラー回路は、ペア性の高いトランジスタで構成することができる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

有機 E L パネルの端子ピンを介して有機 E L 素子を電流駆動する I C 化された有機 E L 駆動回路において、

前記端子ピンに対応して設けられた複数のパッドと、

前記複数のパッドに対応してそれぞれ設けられ前記有機 E L 素子による輝度表示のための表示データを受けてこれに対応するアナログ電流を発生するカレントミラー構成の複数の D / A 変換回路とを備え、

前記パッドの配列方向のパッドピッチの  $n$  倍 ( $n$  は正の整数) に実質的に対応したパッド配列方向の幅を有しこの幅に対して少なくとも 2 個以上のトランジスタが形成された多数のトランジスタを有する矩形のトランジスタブロックが複数個設けられ、

前記 D / A 変換回路を構成するトランジスタが前記トランジスタブロック内において選択され、複数の前記トランジスタブロックを形成したエリアの両端に位置する前記トランジスタブロックの前記 D / A 変換回路がマトリックス状に配列された前記有機 E L 素子を駆動するためには使用されないダミー回路となっている有機 E L 駆動回路。

**【請求項 2】**

複数の前記トランジスタブロックは、1 以上のパッドに対応して配列され、前記多数のトランジスタが単位トランジスタとして前記パッド配列方向に対して直角な方向に配列された少なくとも 2 列を有し、この 2 列に前記パッド配列方向に配列された前記 2 個以上のトランジスタを含み、前記ダミー回路は、複数の前記トランジスタブロックが形成されたエリアの最も外側に位置している請求項 1 記載の有機 E L 駆動回路。

**【請求項 3】**

有機 E L パネルの端子ピンを介して有機 E L 素子を電流駆動する I C 化された有機 E L 駆動回路において、

前記端子ピンに対応して設けられた複数のパッドと、

前記複数のパッドに対応してそれぞれ設けられ前記有機 E L 素子による輝度表示のための表示データを受けてこれに対応するアナログ電流を発生するカレントミラー構成の複数の D / A 変換回路とを備え、

前記パッドの配列方向のパッドピッチの  $n$  倍 ( $n$  は正の整数) に実質的に対応したパッド配列方向の幅を有しこの幅に対して少なくとも 2 個のトランジスタが形成された多数のトランジスタを有する少なくとも 2 列の矩形のトランジスタブロックを複数個有するトランジスタ配列ブロックが設けられ、

前記 D / A 変換回路を構成するトランジスタが前記トランジスタ配列ブロックの内側のエリアにおいて選択され、前記トランジスタ配列ブロックの両端のエリアに位置する前記トランジスタブロックの前記 D / A 変換回路がマトリックス状に配列された前記有機 E L 素子を駆動するためには使用されないダミー回路となっている有機 E L 駆動回路。

**【請求項 4】**

前記 D / A 変換回路は電流スイッチング D / A である請求項 3 記載の有機 E L 駆動回路。

**【請求項 5】**

さらに、前記有機 E L 素子を電流駆動する前記パッドに対応して設けられた複数の電流源を有し、前記複数の電流源は、それぞれ前記パッドに対応して設けられた前記 D / A 変換回路からの出力電流でそれぞれ駆動され、前記電流源を構成するトランジスタが前記トランジスタブロック内において選択されて、前記ダミー回路は、前記両端のエリアに位置するトランジスタブロックにおける前記電流源を含む請求項 4 記載の有機 E L 駆動回路。

**【請求項 6】**

前記電流源はカレントミラー回路で構成される請求項 5 記載の有機 E L 駆動回路。

**【請求項 7】**

前記ダミー回路の前記トランジスタブロックは複数であり、これら複数の前記トランジスタブロックに対応して設けられる前記パッドは存在しないか、そのパッドへの回路接

10

20

30

40

50

続がされないか、およびそのパッドから前記有機EL素子を駆動する前記端子ピンへの接続がされないかのいずれかである請求項5記載の有機EL駆動回路。

【請求項8】

前記D/A変換回路と前記電流源とは、R,G,Bの表示色のそれぞれに対応して設けられ、前記トランジスタブロックがR,G,Bに対応し、かつ、R,G,Bの前記トランジスタブロックが順次繰り返されて配列されて設けられ、前記ダミー回路の前記トランジスタブロックは複数個設けられ、前記電流源は、カレントミラー回路を有する出力段電流源である請求項5記載の有機EL駆動回路。

【請求項9】

nは3であり、前記トランジスタブロックは、少なくとも6個のトランジスタがパッドピッチの3倍の幅においてパッド配列方向に配置され、前記D/A変換回路と前記電流源とがR,G,Bの表示色のそれぞれに対応してそれぞれ形成されている請求項5記載の有機EL駆動回路。 10

【請求項10】

前記ダミー回路の前記電流源は、アイコン表示のための有機ELパネルの端子ピンに接続される請求項5記載の有機EL駆動回路。

【請求項11】

前記ダミー回路の前記トランジスタブロックは複数であり、前記ダミー回路の複数の前記電流源が前記アイコン表示のための有機ELパネルの端子ピンにパラレルに接続される請求項10記載の有機EL駆動回路。 20

【請求項12】

前記ダミー回路のR,G,Bの表示色のそれぞれに対応する前記電流源のうちの複数がアイコン表示のための有機ELパネルの端子ピンにパラレルに接続される請求項8記載の有機EL駆動回路。

【請求項13】

有機ELパネルと、この有機ELパネルの端子ピンを介して有機EL素子を電流駆動する有機EL駆動回路のICとを有する有機EL表装置において、

前記ICは、前記端子ピンに対応して設けられた複数のパッドと、

前記複数のパッドに対応してそれぞれ設けられ前記有機EL素子による輝度表示のための表示データを受けてこれに対応するアナログ電流を発生するカレントミラー構成の複数のD/A変換回路とを備え、 30

前記パッドの配列方向のパッドピッチのn倍(nは正の整数)に実質的に対応したパッド配列方向の幅を有しこの幅に対して2個以上のトランジスタが形成された多数のトランジスタを有する矩形のトランジスタブロックが複数個設けられ、

前記D/A変換回路を構成するトランジスタが前記トランジスタブロック内において選択され、複数の前記トランジスタブロックを形成したエリアの両端に位置する前記トランジスタブロックの前記D/A変換回路がマトリックス状に配列された前記有機EL素子を駆動するためには使用されないダミー回路となっている有機EL表示装置。

【請求項14】

有機ELパネルと、この有機ELパネルの端子ピンを介して有機EL素子を電流駆動する有機EL駆動回路のICとを有する有機EL表装置において、 40

前記ICは、前記端子ピンに対応して設けられた複数のパッドと、

前記複数のパッドに対応してそれぞれ設けられ前記有機EL素子による輝度表示のための表示データを受けてこれに対応するアナログ電流を発生するカレントミラー構成の複数のD/A変換回路とを備え、

前記パッドの配列方向のパッドピッチのn倍(nは正の整数)に実質的に対応したパッド配列方向の幅を有しこの幅に対して少なくとも2個のトランジスタが形成された多数のトランジスタを有する少なくとも2列の矩形のトランジスタブロックを複数個有するトランジスタ配列ブロックが設けられ、

前記D/A変換回路を構成するトランジスタが前記トランジスタ配列ブロックの内側の 50

エリアにおいて選択され、前記トランジスタ配列ブロックの両端のエリアに位置する前記トランジスタブロックの前記D/A変換回路がマトリックス状に配列された前記有機EL素子を駆動するためには使用されないダミー回路となっている有機EL表示装置。

**【請求項15】**

前記D/A変換回路は電流スイッチングD/Aである請求項14記載の有機EL表示装置。

**【請求項16】**

さらに、前記有機EL素子を電流駆動する前記パッドに対応して設けられた複数の電流源を有し、前記複数の電流源は、それぞれ前記パッドに対応して設けられた前記D/A変換回路からの出力電流でそれぞれ駆動され、前記電流源を構成するトランジスタが前記トランジスタブロック内において選択されて、前記ダミー回路は、前記両端のエリアに位置するトランジスタブロックにおける前記電流源を含む請求項15記載の有機EL表示装置。

10

**【請求項17】**

前記電流源はカレントミラー回路で構成される請求項16記載の有機EL表示装置。

**【請求項18】**

前記ダミー回路の前記トランジスタ配列ブロックは複数であり、これら複数の前記トランジスタ配列ブロックに対応して設けられる前記パッドは存在しないか、そのパッドへの回路接続がされないか、およびそのパッドから前記有機EL素子を駆動する前記端子ピンへの接続がされないかのいずれかである請求項16記載の有機EL表示装置。

20

**【請求項19】**

前記D/A変換回路と前記電流源とは、R, G, Bの表示色のそれぞれに対応して設けられ、前記トランジスタブロックがR, G, Bに対応し、かつ、R, G, Bの前記トランジスタブロックが順次繰り返されて配列されて設けられ、前記ダミー回路の前記トランジスタ配列ブロックは複数個設けられ、前記電流源は、カレントミラー回路を有する出力段電流源である請求項16記載の有機EL表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

この発明は、有機EL駆動回路および有機EL表示装置に関し、詳しくは、カレントミラー回路を利用したD/A変換回路により表示データに対応する電流値を生成して有機ELパネルの端子ピンを介して有機ELパネルを電流駆動するカラムライン（陽極側ドライブライン、以下同じ）の電流駆動回路において、輝度むらを低減でき、かつ、製品ごとの輝度ばらつきに与える影響を低減できるような有機EL駆動回路の回路レイアウトに関する。

30

**【背景技術】**

**【0002】**

携帯電話機、PHS、DVDプレーヤ、PDA（携帯端末装置）等に搭載される有機EL表示装置の有機EL表示パネルでは、カラムラインの数が396個（132×3）の端子ピン、ローラインが162個の端子ピンを持つものが提案され、カラムライン、ローラインの端子ピンはこれ以上に増加する傾向にある。

40

このような有機EL表示パネルの電流駆動回路の出力段は、アクティブマトリックス型でも単純マトリックス型のものでも端子ピン対応に電流源の駆動回路、例えば、カレントミラー回路による出力回路が設けられている。

**【0003】**

カレントミラー回路による出力回路は、端子ピン対応に配置され、そのドライブ段は、例えば、特開2003-255898号のように、端子ピン対応に多数の出力側トランジスタを有するパラレル駆動のカレントミラー回路（基準電流分配回路）を有している。そして、入力段となるその手前の基準電流発生回路から基準電流を受けて端子ピン対応にミラー電流を発生することで基準電流を端子ピン対応に分配して出力回路を駆動する（特許

50

文献 1 )。さらに、出力回路の手前に端子ピン対応にカレントミラーで構成される D / A 変換回路 ( D / A ) を設けて、それぞれの D / A が基準駆動電流として前記のミラー電流を受けてこの電流を基準として D / A 変換をする。その D / A 変換は、受けたこの電流を基準にして、受けた輝度の表示データを D / A 変換して端子ピン対応に表示データに応じたアナログ変換電流を生成するものである。このアナログ変換電流により前記のカレントミラーの出力回路が駆動され、端子ピン対応に有機 E L 素子の駆動電流が発生する。

このようなカレントミラー構成で有機 E L 素子に対する駆動電流を生成することにより、例えば、パッシブマトリックスの場合には、数  $\mu$  A 程度の微小な基準電流から m A あるいは 1 A 程度の大きな電流を電力ロスを抑えて電流増幅することができる。これにより低消費電力の駆動回路を実現することができる。また、アクティブマトリックスの場合には、同様にして低消費電力で 1 n A ~ 10  $\mu$  A の駆動電流を得ることが可能。

#### 【 0 0 0 4 】

このような有機 E L 表示パネルの電流駆動回路は、カレントミラーを構成する単位トランジスタが多数、パッドに対応して配列されることになる。

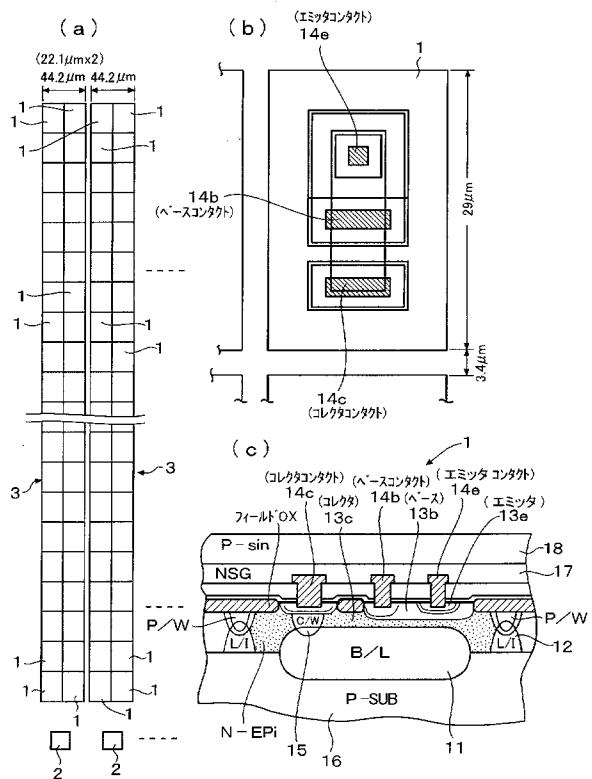

図 4 は、その説明図であって、電流駆動回路の D / A と出力段電流源を形成する先行技術における単位トランジスタの配列ブロック (トランジスタブロック) のレイアウトとこれに形成されるトランジスタを示している。

図 4 ( a ) は、電流駆動回路の D / A と出力段電流源を形成するトランジスタブロック、図 ( b ) は、カレントミラーを構成する単位トランジスタの平面図、図 4 ( c ) はその断面図である。

単位トランジスタ 1 は、図 4 ( c ) に示されるように、埋め込み層 ( B / L ) 1 1 と素子分離領域 1 2 とで形成される矩形領域においてトランジスタ 1 が素子分離されてそのベース領域 1 3 b とエミッタ領域 1 3 e とコレクタ領域 1 3 c とが矩形形状にサブストレート 1 6 の表面側に形成される。なお、1 4 b , 1 4 e , 1 4 c は、それぞれ、ベースコンタクト、エミッタコンタクト、コレクタコンタクトであり、コレクタコンタクト 1 4 c は、コレクタウォール 1 5 と埋め込み層 1 1 を介してコレクタ領域 1 3 c と接続されている。

1 7 は、N SG の層間分離膜であり、1 8 は、上の層のポリシリコン絶縁層 ( P - S i N ) である。

そして、このような単位トランジスタ 1 が、図 4 ( a ) に示すように、トランジスタブロック 3 において、パッド 2 の配列方向 ( 図面横方向、ロー方向 ) に 2 個配置されてパッド配列方向に直角な方向 ( 縦方向、カラム方向 ) に 2 列で、多数設けられている。このような 2 列配置のトランジスタブロック 3 がパッド配列方向に繰り返して形成されて有機 E L 表示パネルの端子ピン対応の電流駆動回路が I C 化される。

#### 【 0 0 0 5 】

この 2 列配置のトランジスタブロック 3 は、有機 E L 表示パネルの各端子ピンが G , R , B の繰り返しで配列されることからそれに応じてその配列が G , R , B 対応に割当られる。また、端子ピン配列に対応させて、各端子ピンに接続されるパッド ( 出力端子 ) 2 も配列される。

例えば、パッドピッチが 50  $\mu$  m のときには、素子形成幅を 44  $\mu$  m とし、横方向の間隔が 6  $\mu$  m として、50  $\mu$  m の間隔で、素子形成幅を 44  $\mu$  m の中に 2 個のトランジスタを形成し、各端子ピンを駆動する回路に必要な数のトランジスタを縦方向に多数形成する。

その結果、2 列配列の単位トランジスタ 1 が各出力端子ピンに対応するパッド 2 の位置に一致して、縦方向には、例えば、数十個 ~ 百個程度 ( その長さは 1.0 mm ~ 3.0 mm 程度 ) の長さでトランジスタ 1 が配置される。そして、これらトランジスタ 1 のほとんどは、上の配線層でカレントミラー接続される。

このとき、カレントミラー出力回路 ( 出力段電流源 ) とカレントミラー構成の電流スイッチング D / A とは、2 列の多数のトランジスタからできるだけペア特性が揃った位置にあるものが選択される。

10

20

30

40

50

## 【0006】

なお、この明細書および特許請求の範囲における電流スイッチングD/Aとは、複数の電流源の電流に対して電流源の電流をビットデータに応じてON/OFFスイッチングすることでD/A変換の電流値を得る回路である。

また、図4(a)は、2列であるが、集積率をよくするために、G, R, Bの3端子ピンを1単位(G, R, Bのカラム方向の画素ピッチに相当)として単位トランジスタ1を6列としたトランジスタブロックがロー方向に繰り返し配列されるものもある。このときには、端子ピン方向(ロー方向)の幅が150μmとなるが、この場合にはG, R, Bそれぞれの2列を単位として各パッド2に対応して各端子ピンを電流駆動する駆動回路が縦方向に割当てられることは変わらない。

ところで、マトリックス状に配置した有機EL素子を電流駆動し、かつ、有機EL素子の陽極と陰極をグランドに落としてリセットする有機EL素子の駆動回路が公知である(特許文献2)。また、DC-DCコンバータを用いて有機EL素子を低消費電力で電流駆動する技術が公知である(特許文献3)。

【特許文献1】特開2003-255898号公報

【特許文献2】特開平9-232074号公報

【特許文献3】特開2001-143867号公報

【発明の開示】

【発明が解決しようとする課題】

## 【0007】

前記したカレントミラー回路構成のD/Aを用いて駆動電流を生成する有機EL駆動回路にあって、数μA程度の微小な基準電流からmAあるいは1A程度の大きな電流を生成する場合にはD/Aの変換精度のばらつきが出力段電流源の出力電流のばらつきを生じ、それが輝度むらとなる問題がある。

特に、カレントミラー構成の電流スイッチングD/Aでは、電流源からの電流をスイッチングすることで、基準電流を2倍、4倍、8倍、16倍、…と重みを付けて増幅した電流をカレントミラー接続の出力側トランジスタに得るので、カレントミラー接続されるトランジスタの数が数十から100個程度は必要になる。そのために、カレントミラー構成のトランジスタの入力側トランジスタに対するペア特性の確保が重要になる。このペア特性は、IC化されているトランジスタの間の距離とトランジスタが選択される位置とが影響する。

## 【0008】

しかも、カレントミラーで構成されるD/A変回路は、有機EL素子の発光輝度を示す表示データに応じた駆動電流を発生するために高い変換精度が要求される。前記のような縦に長いトランジスタブロック3をパッドに対応して配列すると、トランジスタブロック3の形成エリアの両端に位置するトランジスタブロック3のトランジスタはペア性が悪くなる。

その理由は、内側に位置するトランジスタブロック3は、両端(両側)に同じようなトランジスタブロック3があるのに対して、両端では片側にしかトランジスタブロック3がないからである。それにより両端のトランジスタブロック3に形成されたトランジスタは、内側のトランジスタブロック3に形成されたトランジスタに比べて物性的にみた形成環境が均等でなくなり、物性的なストレスの偏りがあるために特性に差が出てくる。そのためカレントミラー回路としてのトランジスタのペア特性が落ちる。

その結果、端子ピン間の出力電流値の差が大きくなり、それが輝度むらとなって現れてくる。特に、ドライブICを複数個使用した場合には、IC間の境目での輝度むらが目立ってくる。

前記した特開2003-255898号(特許文献1)では、IC間の境目での輝度むらを防止するために、基準電流を分配するカレントミラー回路において、その入力側トランジスタを数十の多数の出力側トランジスタの中央に配置している。

## 【0009】

10

20

30

40

50

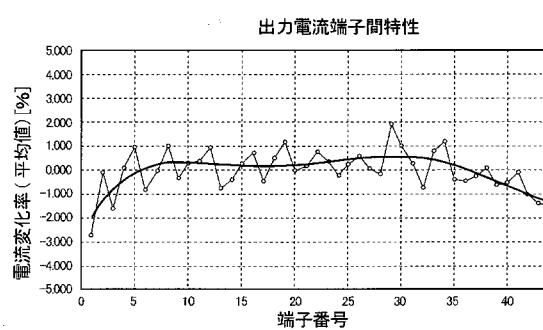

図5は、この特開2003-255898号の回路における端子ピンに対する出力電流特性を示すものである。G, R, Bの端子ピン数を各45ピンとして電流駆動回路の出力電流の端子間特性を示している。点を結ぶ線が実際の測定値であり、この線の間の実線は回帰曲線である。縦軸は電流変化率であり、単位は[%]である。横軸は、端子ピン番号(端子の位置)である。

この特性にみると、両端にある端子ピンに近づくにつれて出力電流が落ちてくる。両端にある端子ピンは、サブストレートにおけるトランジスタブロック3の形成エリアの両端のトランジスタブロック3に対応している。

特開2003-255898号のように、入力側トランジスタを多数の出力側トランジスタの中央に配置して基準電流を分配したとしても有機ELパネルの表示画面の輝度むらを十分には抑えることができない。そして、両端の端子ピンの出力電流の落込みは、製品ごとの輝度ばらつきに与える影響が大きい。

10

この発明の目的は、このような従来技術の問題点を解決するものであって、輝度むらを低減でき、かつ、製品ごとの輝度ばらつきに与える影響を低減できる有機EL駆動回路および有機EL表示装置を提供することにある。

20

20

#### 【課題を解決するための手段】

#### 【0010】

このような目的を達成するための第1の発明の有機EL駆動回路あるいは有機EL表示装置の特徴は、端子ピンに対応して設けられた複数のパッドと、この複数のパッドに対応してそれぞれ設けられ有機EL素子による輝度表示のための表示データを受けてこれに対応するアナログ電流を発生するカレントミラー構成のD/Aを備えていて、パッドの配列方向のパッドピッチのn倍(nは正の整数)に実質的に対応したパッド配列方向の幅を有しこの幅に対して2個以上のトランジスタが形成された多数のトランジスタを有する矩形のトランジスタブロックが複数個設けられ、D/Aを構成するトランジスタがトランジスタブロック内において選択され、複数のトランジスタブロックを形成したエリアの両端に位置するトランジスタブロックのD/Aがマトリックス状に配列された前記有機EL素子を駆動するためには使用されないダミー回路となっているものである。

20

20

#### 【0011】

また、第2の発明は、さらに、パッドに対応して設けられ前記のD/Aからの出力電流で駆動され前記パッドを介して駆動電流を前記の端子ピンに出力する複数の電流源を有していて、D/Aと電流源とを構成するトランジスタがトランジスタブロック内において選択されてこれらの回路が形成され、トランジスタブロックを形成したエリアの両端に位置するトランジスタブロックのD/Aと電流源とがマトリックス状に配列された前記有機EL素子を駆動するためには使用されないダミー回路となっているものである。

30

30

#### 【発明の効果】

#### 【0012】

このように、この発明にあっては、ICチップの駆動回路形成領域において両端に位置するトランジスタブロックが動作対象とされないダミー回路となっているので、このダミー回路より内側に位置するトランジスタブロックに形成されたD/AあるいはD/Aと出力段の電流源とは、これら回路を形成するトランジスタの物性的なストレスの偏りが減少して、D/Aのカレントミラー回路は、ペア性の高いトランジスタで構成することができる。

40

これにより、両端の端子ピンの出力電流の落込みが低減されるので、輝度むらが低減でき、さらに製品ごとの輝度ばらつきに与える影響を抑えることができる。

#### 【発明を実施するための最良の形態】

#### 【0013】

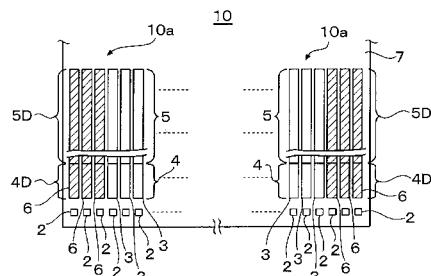

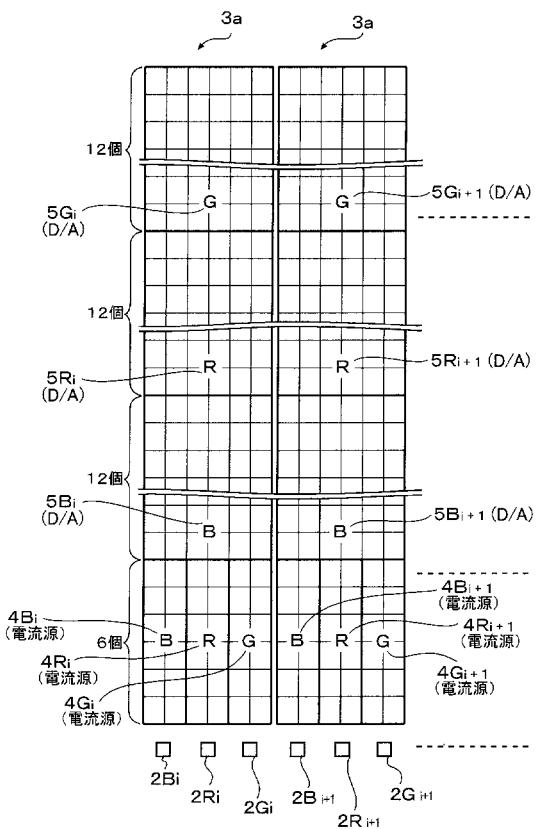

図1は、この発明の有機EL駆動回路を適用した一実施例の電流駆動回路のD/Aと出力段電流源のカレントミラーを構成する単位トランジスタのレイアウトの説明図、

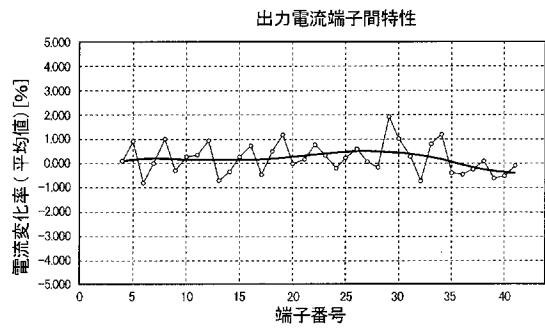

図2は、出力電流の端子間特性の説明図、

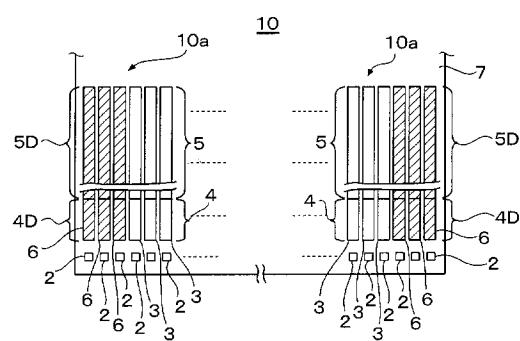

図3は、R, G, Bを1つのトランジスタブロックに割当てた場合の詳細説明図、

50

図4は、電流駆動回路のD/Aと出力段電流源を形成する先行技術におけるトランジスタブロックのレイアウトとこれに形成されるトランジスタの説明図、そして、

図5は、図4における出力電流の端子間特性の説明図である。

なお、図1～図3においては、図4、5と同一の構成要素は同一の符号で示す。

#### 【実施例1】

##### 【0014】

図1において、10は、有機EL駆動回路のカラムドライバICであって、10aは、有機ELパネルの端子ピンに対応に設けられるD/Aと出力段電流源のカレントミラーを構成する単位トランジスタのICチップにおけるレイアウトである。

3は、2列単位(2カラム)で $2 \times 4$ 2個のトランジスタを単位とするトランジスタブロックであり、図4(a)に示す配列ブロックである。6は、トランジスタブロック3と同じものであるが、マトリックス状に配列された有機EL素子を駆動するためには使用されない配列ブロック(ダミー回路)である。

トランジスタブロック3は、所定の間隙を挟んでパッド配列方向(横方向)にパッドピッチおきに各パッド2に対してB, G, Rの順に繰り返して形成される。ICチップの駆動回路形成領域においてその両端(両側)にあるそれぞれ3個のトランジスタブロック3は、使用されないトランジスタブロック6として形成される。内側の配列ブロック3と同じ回路がここにも形成されるが、パッド2に対する接続は行われない。したがって、駆動電流は出力されない。

##### 【0015】

有機ELパネルの電流駆動回路は、入力段に基準電流発生回路を有し、ドライブ段と出力段が有機ELパネルの各端子ピンに対応に設けられる。これらは、トランジスタブロック3, 6にそれぞれ形成される。ドライブ段には、各端子ピンに対応に基準電流を分配する基準電流分配回路と各端子ピンに対応に設けられたカレントミラー構成の電流スイッチングD/Aが設けられる。このD/Aが表示データを受けて、各端子ピンに対応に設けられた出力段電流源を駆動する。

4は、トランジスタブロック3におけるその出力段電流源が形成されたブロックであり、 $2 \times 6$ 個のトランジスタからなる。5は、トランジスタブロック3においてD/Aが形成されたブロックであり、ブロック4の後ろに設けられた $2 \times 3$ 6のトランジスタからなる。

これら配列ブロック4, 5に対して隣接する有機EL素子を駆動するものとして動作させない出力段電流源の回路とD/Aとがダミーのブロック4D, 5Dとしてトランジスタブロック3に形成される。それがトランジスタブロックの形成エリア7の左右側にそれぞれ3個ずつ設けられたトランジスタブロック6となる。ダミーのブロック4D, 5Dは、配列された隣接する有機EL素子を駆動するための駆動回路にはならない。そのため、ダミーのブロック4D, 5Dの各パッド2への接続あるいはこれの端子ピンへの接続配線はされない。

##### 【0016】

ここでは、出力段電流源のカレントミラー回路のトランジスタの個数を10個、D/Aのカレントミラー回路のトランジスタの個数を70個としてカレントミラー構成の電流スイッチングD/Aを構成し、それぞれに予備あるいはダミートランジスタ2個設けて、前記した特開2003-255898号の実施例の回路を実現する。図2は、その場合の端子ピンに対する出力電流特性である。

なお、トランジスタブロック3, 6に形成されるD/Aと出力段電流源の回路の詳細は、この出願人が出願し、すでに公開された特開平2003-308043号に記載されている。

図2に示すように、端子ピンの数は、B, G, Rともに2本少なくなるが、その特性は、図5の場合よりも平坦となり、端子ピン間の出力電流のばらつきは少なくなる。縦軸は、電流変化率であり、単位は[%]である。横軸は、端子ピン番号(端子の位置)である。

10

20

30

40

50

## 【実施例 2】

## 【0017】

図3は、R, G, Bを独立のトランジスタブロック3とせずに、1つのトランジスタブロック3aとして、その中にD/Aと出力段電流源を割当てた場合の実施例の詳細説明図である。各トランジスタブロック3aにおいては、B, R, Gの各出力段電流源のブロックをパッドに対応して横方向に配置した構成とし、D/Aのみを縦方向にB, R, Gの順で配列したものである。

トランジスタの配列ブロック3aは、トランジスタの配列ブロック3を3個並べて1個にしたものである。トランジスタブロックの形成エリア7(図1参照)の両端に位置するトランジスタブロック6に対応するダミー回路のトランジスタブロックも同様な構成であるが、図では省略してある。この場合のダミー回路のトランジスタブロック3aは、ICチップにおいてその両端にそれぞれ1個ずつとなる。

図3において、4Ri, 4Gi, 4Bi, …は、それぞれのトランジスタブロック3aにおける出力段を構成する電流源であり、パッド2の配列方向に沿って割当てられる。5Ri, 5Gi, 5Bi, …は、それぞれの配列ブロック7におけるD/Aである。これは、パッド2の配列方向に対して直角方向に割当てられている。

なお、ダミーの回路4D, 5Dを持つトランジスタブロックも出力段電流源4Ri, 4Gi, 4BiとD/A5Ri, 5Gi, 5Biとが同様な割当てでトランジスタブロック形成エリア7の両端に設けられる。

前記と同様に、トランジスタブロック3aのトランジスタ数を84個×3として、R, G, Bに対応に出力段電流源とD/Aとを設けている。そこで、トランジスタブロック3aの単位トランジスタの総数は、84×3=252個になる。

## 【0018】

この図3の実施例では、各トランジスタブロック3aにおいて3×パッドピッチ幅の単位でそれぞれにカレントミラーを構成する単位トランジスタ1を選択して、R, G, Bの出力段電流源とD/A(D/A)を割当ててそれぞれのカレントミラー回路を形成する。

また、図3の実施例では、D/Aを形成するトランジスタの配列ブロックを横方向に幅のある長方形としている。このようにすることで、カレントミラー回路を構成するペア特性を探るトランジスタの選択範囲が横方向に広げられる。図4ではペア特性を探るトランジスタは、縦方向のトランジスタを選択することになるが、この場合よりも特性が揃う確率が高くなる。

## 【0019】

ところで、携帯電話等では、表示画面の上部に電波の受信状態や電池の残量を示すアイコンがそれぞれ設けられている。さらに、表示画面の下側には、特定の操作に対応したアイコンが設けられているものも多くある。

このようなアイコンは、マトリックス状に配列され隣接したものが駆動されてそのときの表示データに応じて輝度を表示するメインの有機EL素子ではないので、表示輝度に多少のばらつきがあっても問題ない。これらアイコンは、表示画素が大きくなるので、その分大きな駆動電流が要求される。

そこで、図1に示すダミー回路のトランジスタブロック6のブロック4Dの出力段電流源は、パッド2を介してこれらアイコンに対応する有機EL素子を駆動するものとして割当てる。有機ELパネルのアイコン駆動用の端子ピンにダミー回路の出力段電流源を接続してアイコン表示のための有機EL素子を駆動する。アイコン表示の場合には、駆動電流値のばらつきは問題にならないので、これによりダミー回路を有効に使用することができる。

## 【0020】

このように、ダミー回路6は、電源からは電力が供給された状態にあるので、動作させなくてもあるいはアイコン駆動用として動作させても、メインの有機EL素子に対応する端子ピンに送出する駆動電流のばらつきに対する作用においては影響しない。要するに、この発明では、このダミー回路が配列された隣接する有機EL素子を駆動する回路として

10

20

30

40

50

動作しなければよい。

なお、このアイコン用の有機EL素子を駆動する場合には、駆動電流量が大きくなるので、パッド2に接続されたトランジスタブロック6のブロック4Dの電流源複数を1つのアイコンの有機EL素子に対応させて電流源のパラレル接続で駆動するようになるとよい。これにより、大きな駆動電流を容易に生成することができる。

【産業上の利用可能性】

【0021】

以上説明してきたが、実施例では、トランジスタブロック3, 6にD/Aと電流源とを設けて構成しているが、アクティブマトリックスの有機ELパネルでは、駆動電流値が小さくなるので、D/Aの出力そのものを駆動電流として使用することができる。この場合にはD/Aが出力段電流源となる。そのレイアウトは、図1, 図3における出力段電流源が形成されたブロック4あるいは4Dがなくなり、D/Aが形成されたブロック5あるいは5Dがトランジスタブロック3, 6の先頭にきてパット2に対応することになる。

したがって、この発明では、トランジスタブロック3, 6に設けられる回路は、D/Aだけであってもよい。

【0022】

また、実施例では、ダミー回路を持つトランジスタブロック6についてもパッド2を設けている。しかし、アイコン表示の有機EL素子等の駆動としてダミー回路を割当てない場合には、この発明では、パッド2に対する配線が必要ではないので、トランジスタブロック6に対してはパッド2を設ける必要はない。

さらに、実施例では、ICチップの駆動回路形成領域においてその両端（両側）にあるトランジスタブロックをダミー回路として割り当てている。そこで、ICチップの駆動回路形成領域の両端に有機EL素子の駆動回路とは異なる回路が形成されていてもよいことはもちろんである。このようなダミー回路のトランジスタブロックは、1個であっても、2以上であってもよい。

さらに、この発明は、直接カラムラインに接続された有機EL素子を電流駆動するパッシブ型の有機ELパネルに限らず、ピクセル回路のコンデンサを介してピクセル回路の有機EL素子を駆動するアクティブマトリックス型の有機ELパネルにあっても適用できる。

ところで、実施例では、バイポーラトランジスタを例としているが、バイポーラトランジスタに換えてMOSFETトランジスタを使用してもこの発明が適用できることはもちろんである。

【図面の簡単な説明】

【0023】

【図1】図1は、この発明の有機EL駆動回路を適用した一実施例の電流駆動回路のD/Aと出力段電流源のカレントミラーを構成する単位トランジスタのレイアウトの説明図である。

【図2】図2は、出力電流の端子間特性の説明図である。

【図3】図3は、R, G, Bを1つのトランジスタブロックに割当てた場合の詳細説明図である。

【図4】図4は、電流駆動回路のD/Aと出力段電流源を形成する先行技術におけるトランジスタブロックのレイアウトとこれに形成されるトランジスタの説明図である。

【図5】図5は、図4における出力電流の端子間特性の説明図である。

【符号の説明】

【0024】

- 1 ... 単位トランジスタ、2 ... パッド、

- 3, 3a ... トランジスタブロック、

- 6 ... ダミー回路のトランジスタブロック、

- 4Bi, 4Ri, 4Gi ... 電流駆動回路、

- 5Bi, 5Ri, 5Gi ... D/A、

10

20

30

40

50

7 ... パッケージの形成エリア、

10 ... カラムドライバ I C。

【図 1】

【図 2】

【図 3】

【図4】

【図5】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 4 2 B |

| G 0 9 G | 3/20  | 6 8 0 G |

| H 0 3 M | 1/74  |         |

| H 0 5 B | 33/14 | A       |

(72)発明者 藤川 昭夫

京都市右京区西院溝崎町21番地 ローム株式会社内

(72)発明者 藤沢 雅憲

京都市右京区西院溝崎町21番地 ローム株式会社内

F ターム(参考) 3K007 AB17 BA06 BB07 DB03 GA00

|       |      |      |      |      |      |      |      |      |      |      |

|-------|------|------|------|------|------|------|------|------|------|------|

| 5C080 | AA06 | BB05 | CC03 | DD05 | EE29 | EE30 | FF01 | FF11 | FF12 | JJ05 |

| JJ06  | KK47 |      |      |      |      |      |      |      |      |      |

| 5J022 | AB06 | BA01 | CF04 | CF09 | CG01 |      |      |      |      |      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL驱动电路和有机EL显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2005037916A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2005-02-10 |

| 申请号            | JP2004181124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2004-06-18 |

| [标]申请(专利权)人(译) | 罗姆股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | ROHM株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 前出淳<br>阿部真一<br>藤川昭夫<br>藤沢雅憲                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 前出淳<br>阿部真一<br>藤川昭夫<br>藤沢雅憲                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 H03M1/74 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/30.K G09G3/30.H G09G3/20.621.M G09G3/20.623.B G09G3/20.623.F G09G3/20.642.B G09G3/20.680.G H03M1/74 H05B33/14.A G09G3/3216 G09G3/3233 G09G3/3275 G09G3/3283                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/BB07 3K007/DB03 3K007/GA00 5C080/AA06 5C080/BB05 5C080/CC03 5C080/DD05 5C080/EE29 5C080/EE30 5C080/FF01 5C080/FF11 5C080/FF12 5C080/JJ05 5C080/JJ06 5C080/KK47 5J022/AB06 5J022/BA01 5J022/CF04 5J022/CF09 5J022/CG01 3K107 /AA01 3K107/BB01 3K107/CC33 3K107/EE04 3K107/HH00 3K107/HH04 3K107/HH05 5C380/AA01 5C380/AB05 5C380/AB06 5C380/AB19 5C380/AB34 5C380/AC05 5C380/AC11 5C380/AC12 5C380 /BA27 5C380/BA37 5C380/BA47 5C380/BB02 5C380/BB05 5C380/CA13 5C380/CA34 5C380/CA35 5C380/CA46 5C380/CF26 5C380/CF48 5C380/CF51 5C380/DA02 |         |            |

| 代理人(译)         | 梶山信是<br>山本富士雄                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 优先权            | 2003184339 2003-06-27 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | JP4841812B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

## 摘要(译)

[问题] 本发明的目的是提供一种有机EL驱动电路和有机EL显示装置，其可以减少亮度的不均匀性以及对每种产品的亮度变化的影响。[解决方案] 根据本发明，由于位于IC芯片的电路形成区域中的两端的晶体管块是不工作的伪电路，因此，形成在位于伪电路内部的晶体管块中的D/A转换电路或D/A转换电路为D/A转换电路和输出级的电流源减小了形成这些电路的晶体管的物理应力的偏置，并且D/A转换电路的电流镜电路由高度配对的晶体管组成。可以的 [选型图]图1