(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-341368

(P2004-341368A)

(43) 公開日 平成16年12月2日(2004.12.2)

(51) Int.Cl.<sup>7</sup>

**G09G** 3/30

**G09F** 9/30

**G09F** 9/33

**G09G** 3/20

**H05B** 33/14

F 1

G09G 3/30 J 3K007

G09F 9/30 338 5C080

G09F 9/33 365Z 5C094

G09F 9/33 Z

G09G 3/20 611H

テーマコード(参考)

審査請求 未請求 請求項の数 9 O L (全 20 頁) 最終頁に続く

(21) 出願番号

特願2003-139665 (P2003-139665)

(22) 出願日

平成15年5月16日 (2003.5.16)

(71) 出願人

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者

宮川 恵介

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 3K007 AB03 AB06 AB11 AB17 BA06

DB03 GA00 GA04

5C080 AA06 BB05 DD03 DD29 EE29

FF11 JJ02 JJ03 JJ05 KK01

KK07 KK43 KK47

5C094 AA04 AA24 AA31 AA53 AA55

BA03 BA26 BA29 CA19 DB04

EA04 FB14 HA06 HA08

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】駆動TFTを飽和領域で動作させることによってEL素子が劣化しても輝度が低下しにくくする。しかし高電圧となり、消費電力が高くなる、発熱が多くなる、などの問題が生ずる。また、駆動TFTを飽和領域で動作させた場合、駆動TFTのばらつきによって輝度むらが生ずる。

【解決方法】駆動TFTとして、高階調では電流能力の高いTFTを使い、低階調では電流能力の低いTFTを使う。電流能力の高いTFTはより低いV<sub>gs</sub>でも大きな電流を供給できるため、V<sub>ds</sub>が低くなても線形領域になりにくい。このためEL素子が劣化しても輝度低下を発生しにくく、低電圧で駆動できる。電流能力の低いTFTはより高いV<sub>gs</sub>を印加することで電流を供給する。V<sub>gs</sub>が高いことでTFTの特性ばらつき、特にV<sub>th</sub>のばらつきの影響を少なくすることができる。

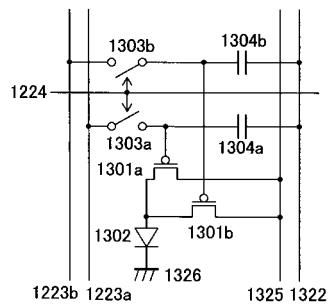

【選択図】 図13

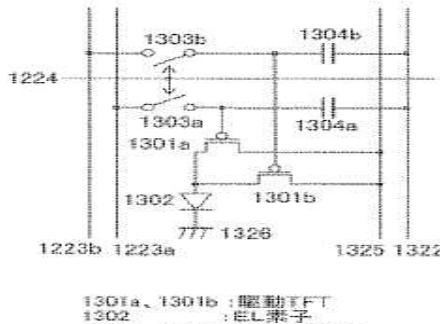

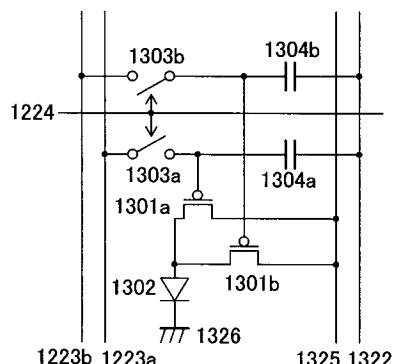

1301a, 1301b : 駆動TFT

1302 : EL素子

1303a, 1303b : 書込スイッチ

1304a, 1304b : 画素容量

1322 : 画素容量線

1223a, 1223b : 信号線

1224 : 行選択線

1325 : アノード

1326 : カソード

**【特許請求の範囲】****【請求項 1】**

アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、

前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、

前記発光素子に接続される第1の駆動用トランジスタと、

前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、

前記発光素子に接続される第2の駆動用トランジスタと、

を有することを特徴とする表示装置。

**【請求項 2】**

アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、

前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、

前記第1のトランジスタと電源線とに接続される第1の容量素子と、

前記第1の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第1の駆動用トランジスタと、

前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、

前記第2のトランジスタと電源線とに接続される第2の容量素子と、

前記第2の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第2の駆動用トランジスタと、

を有することを特徴とする表示装置。

**【請求項 3】**

アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、

前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、

前記発光素子に接続される第1の駆動用トランジスタと、

前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、

前記発光素子に接続される第2の駆動用トランジスタと、

を有し、

前記第1の駆動用トランジスタ電流能力と、前記第2の駆動用トランジスタとの電流能力とは異なることを特徴とする表示装置。

**【請求項 4】**

アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、

前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、

前記第1のトランジスタと電源線とに接続される第1の容量素子と、

前記第1の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第1の駆動用トランジスタと、

前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、

前記第2のトランジスタと電源線とに接続される第2の容量素子と、

前記第2の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第2の駆動用トランジスタと、

を有し、

前記第1の駆動用トランジスタ電流能力と、前記第2の駆動用トランジスタとの電流能力とは異なることを特徴とする表示装置。

**【請求項 5】**

請求項3又は4において、前記第1の駆動用トランジスタ電流能力は、前記第2の駆動用トランジスタとの電流能力より高く、高階調表示を行うことを特徴とする表示装置。

**【請求項 6】**

請求項3又は4において、前記第2の駆動用トランジスタ電流能力は、前記第1の駆動用

10

20

30

40

50

トランジスタとの電流能力より低く、低階調表示を行うことを特徴とする表示装置。

【請求項 7】

アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、

前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、

前記発光素子に接続される第1の駆動用トランジスタと、

前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、

前記発光素子に接続される第2の駆動用トランジスタと、

を有し、

前記第1の駆動用トランジスタのゲートドレイン間電圧と、前記第2の駆動用トランジスタのゲートドレイン間電圧とは異なることを特徴とする表示装置。 10

【請求項 8】

アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、

前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、

前記第1のトランジスタと電源線とに接続される第1の容量素子と、

前記第1の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第1の駆動用トランジスタと、

前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、

前記第2のトランジスタと電源線とに接続される第2の容量素子と、 20

前記第2の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第2の駆動用トランジスタと、

を有し、

前記第1の駆動用トランジスタのゲートドレイン間電圧と、前記第2の駆動用トランジスタのゲートドレイン間電圧とは異なることを特徴とする表示装置。

【請求項 9】

請求項1乃至8のいずれか一に記載の表示装置であって、前記発光素子の輝度に応じて、前記発光素子に接続される複数の駆動用トランジスタを選択する手段を有することを特徴とする表示装置。

【発明の詳細な説明】 30

【0001】

【発明の属する技術分野】

本発明はトランジスタを有する表示装置に関する。本発明は特に、絶縁体上に作製した薄膜トランジスタ（以後、TFTと表記する）等とEL素子を有する表示装置に関する。また、このような構成の表示装置を用いた電子機器に関する。

【0002】

【従来の技術】

近年、エレクトロルミネッセンス（Electro Luminescence：EL）素子等を始めとした発光素子を用いた表示装置の開発が活発化している。発光素子は、自らが発光するために視認性が高く、液晶表示装置（LCD）等において必要なバックライトを必要としないために薄型化に適しているとともに、視野角にほとんど制限がない。

【0003】

一般に、EL素子に電流を流すことでEL素子は発光する。そのためLCDとは異なる画素構成が提案されている（非特許文献1参照）。

【0004】

【非特許文献1】

「有機ELディスプレイにおける材料技術と素子の作製」技術情報協会、2002年1月、p.179-195

【0005】

## 【発明が解決しようとする課題】

上記非特許文献1では、駆動TFTを飽和領域で動作させることによってEL素子が劣化しても輝度が低下しにくい。しかし劣化分を見越した電圧をあらかじめ印加する必要があるため高電圧となり、消費電力が高くなる、発熱が多くなる、などの問題が生ずる。また、駆動TFTを飽和領域で動作させた場合、駆動TFTのばらつきが生じ、その結果輝度むらが生ずる。本発明は上記欠点に鑑み、EL素子の劣化の影響が少なく、低電圧で動作可能であり、しかも駆動TFTのばらつきの影響を少なくする回路構成を用いた表示装置を提供することを目的とする。

## 【0006】

## 【課題を解決するための手段】

TFTはソースとドレインが同じ構造で示せるため、本文では一方を第1の電極他方を第2の電極と呼ぶ。また本文ではTFTのゲート-ソース間に閾値を超える電圧が印加され、ソース-ドレイン間に電流が流れる状態になることをONすると呼ぶ。またTFTのゲート-ソース間に閾値以下の電圧が印加され、ソース-ドレイン間に電流が流れない状態になることをOFFすると呼ぶ。なお、本明細書においては表示装置を構成する素子の例としてTFTを挙げているが、これに限定するものではない。例えば、MOSトランジスタ、有機トランジスタ、バイポーラトランジスタ、分子トランジスタ等を用いても良い。また、機械的スイッチを用いてもよい。

## 【0007】

本明細書においては発光素子の例としてEL素子を挙げているが、これに限定するものではない。例えば、発光ダイオード等を用いても良い。

## 【0008】

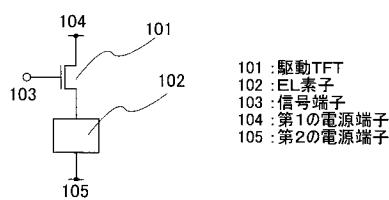

図1に示す駆動TFT101とEL素子102が接続された表示装置において、駆動TFT101のゲートは信号端子103と接続し、第1の端子は第1の電源端子104と接続し、第2の端子はEL素子102の第1の端子と接続し、EL素子102の第2の端子は第2の電源端子105と接続している。上記表示装置は駆動TFT101がEL素子102に流れる電流を調節し、EL素子102の発光輝度を決定する。駆動TFT101を飽和領域で動作させると、駆動TFT101のゲートソース間電圧 $V_{gs}$ によってソースドレイン間電流 $I_{ds}$ を調節することができる。図1において、駆動TFT101はNchTFTでもよいしPchTFTでもよい。

## 【0009】

なお本明細書において便宜上端子と表記するが、実際に端子が設けられている必要はなく、配線と電気的に接続していればよい。また本明細書においては、TFTのゲートソース間電圧を $V_{gs}$ 、TFTのソースドレイン間電圧を $V_{ds}$ 、TFTのドレインソース間電流を $I_{ds}$ 、TFTの閾値電圧を $V_{th}$ と呼ぶ。

## 【0010】

ここで、駆動TFT101を飽和領域で動作させる場合は下記の第1の問題と第2の問題が生ずる。またソース端子とドレイン端子は、駆動TFT101に印加される電位に応じて決定されるため、図1において駆動TFT101の第1の電源端子104側がソース端子でもドレイン端子でもよい。また、ソース端子とドレイン端子は、駆動TFT101の第1の電極と第2の電極に印加される電圧と、駆動TFT101がNchTFTかPchTFTかによって決定される。

## 【0011】

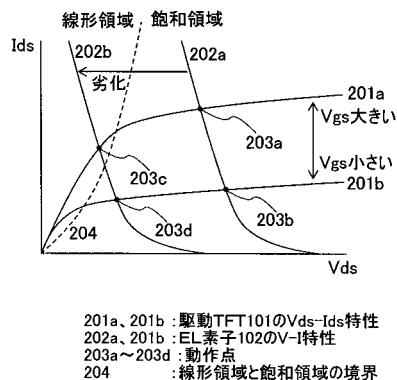

第1の問題は、特にEL素子102に流れる電流値の多い高階調では線形領域での動作となりやすいことである。図2では駆動TFT101の $V_{ds}$ - $I_{ds}$ 特性201a~bとEL素子102の $V$ - $I$ 特性202a~bについて負荷曲線で示している。特性201aは $V_{gs}$ が高く $I_{ds}$ の多い高階調表示の場合、特性201bは $V_{gs}$ が低く $I_{ds}$ の少ない低階調表示の場合を示している。また、特性202aはEL素子102が劣化する前、特性202bはEL素子102が劣化した場合を示している。特性201a~bと特性202a~bの交差点が動作点203a~dとなる。EL素子102の劣化により特性2

10

20

30

40

50

02a から特性 202b に変化すると、動作点 203a、b から動作点 203c、d に変化する。このとき駆動 TFT101 の  $V_{ds}$  は低くなる。特に高階調での特性 201a では  $V_{ds}$  の低下によって、図 2 に示すように飽和領域である動作点 203a から線形領域である動作点 203c に駆動状態が変化してしまう。これは  $V_{gs}$  が高いため、より低い  $V_{ds}$  から線形領域での動作となるためである。なお、 $V_{gs} = V_{ds}$  が線形領域と飽和領域の境界であり、図 2 では破線 204 で示している。線形領域では  $V_{ds}$  の変化によって  $I_{ds}$  が著しく変化するため、EL 素子 102 に流れる電流が変動して輝度が変化し、焼き付きなどの表示品位の低下原因となる。また、線形領域では  $V_{gs}$  を変えても  $I_{ds}$  がほとんど変化しないため、 $V_{gs}$  の制御による輝度調節が難しくなる。この問題を避けるためには、あらかじめ劣化を見越した充分な電圧を印加することで線形領域での動作になりにくくすればよいが、消費電力が高くなる、発熱が多くなる、TFT 素子の劣化が早まる、などの問題が生ずる。

10

## 【0012】

$I_{ds}$  が小さい低階調での特性 201b では  $V_{ds}$  の低下によって、図 2 に示すように動作点 203b から動作点 203d に変化しても、駆動状態は飽和領域のままである。これは  $V_{gs}$  が低いため、より低い  $V_{ds}$  まで飽和領域となるためである。

## 【0013】

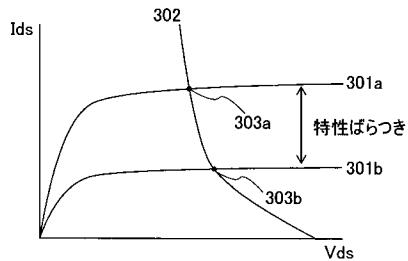

第 2 の問題は、特に EL 素子 102 に流れる電流値の少ない低階調では TFT の特性ばらつきの影響を受けやすいことである。図 3 では駆動 TFT101 の  $V_{ds}$  -  $I_{ds}$  特性 301a ~ b と EL 素子 102 の  $V$  -  $I$  特性 302 について負荷曲線で示している。特性 301a と特性 301b は駆動 TFT101 の特性がばらついた場合を示している。特性 301a ~ b と特性 302 の交差点が動作点 303a ~ b となる。TFT の特性は一定ではなく、 $V_{th}$  のばらつきなどの特性ばらつきを持つ。駆動 TFT101 の特性ばらつきにより特性 301a から特性 301b に変化すると、動作点 303a から動作点 303b に変化し、 $I_{ds}$  が変化する。 $I_{ds}$  は  $(V_{gs} - V_{th})^2$  に比例するが、特に  $I_{ds}$  が少ない低階調では  $V_{gs}$  が小さいため  $V_{th}$  のばらつきの影響が大きい。この影響は表示装置での輝度むらとして表われ、表示品位の低下原因となる。

20

## 【0014】

$I_{ds}$  が大きい高階調では、 $V_{gs}$  が大きいため  $V_{th}$  のばらつきの影響は小さくなる。

30

## 【0015】

本発明では駆動 TFT として、高階調（表示）では電流能力の高い TFT を使い、低階調（表示）では電流能力の低い TFT を使うことを特徴とする。

## 【0016】

高階調では駆動 TFT として電流能力の高い TFT を使う理由は、電流能力の高い TFT はより低い  $V_{gs}$  でも大きな電流を供給できるため、 $V_{ds}$  が低くなっても線形領域になりにくい。このため EL 素子が劣化しても輝度低下を発生しにくく、またより低い電圧で駆動できるため低消費電力で低発熱であり、また TFT 素子の劣化を防ぐことができる。

## 【0017】

低階調では駆動 TFT として電流能力の低い TFT を使う理由は、電流能力の低い TFT はより高い  $V_{gs}$  を印加することで電流を供給する。 $V_{gs}$  が高いことで TFT の特性ばらつき、特に  $V_{th}$  のばらつきの影響を少なくすることができる。特に  $V_{gs}$  が低くなる低階調において効果が大きく、表示品位を高めることができる。また、電流能力を低くするために TFT の L 長を長くすることで、特性ばらつきを少なくすることができる。

40

## 【0018】

本発明の構成を以下に記す。

## 【0019】

本発明の表示装置は、アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、前記第 1 の信号線と、前記走査線とに接続される第 1 のトランジスタと、前記発光素子に接続される第 1 の駆動用トランジスタと、前記第 2 の信号線と、前記走査線とに接続される第 2 のトランジスタと、前

50

記発光素子に接続される第2の駆動用トランジスタと、を有することを特徴としている。

【0020】

本発明の表示装置は、アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、前記第1のトランジスタと電源線とに接続される第1の容量素子と、前記第1の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第1の駆動用トランジスタと、前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、前記第2のトランジスタと電源線とに接続される第2の容量素子と、前記第2の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第2の駆動用トランジスタと、を有することを特徴としている。

10

【0021】

本発明の表示装置は、アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、前記発光素子に接続される第1の駆動用トランジスタと、前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、前記発光素子に接続される第2の駆動用トランジスタと、を有し、前記第1の駆動用トランジスタ電流能力と、前記第2の駆動用トランジスタとの電流能力とは異なることを特徴としている。

【0022】

本発明の表示装置は、アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、前記第1のトランジスタと電源線とに接続される第1の容量素子と、前記第1の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第1の駆動用トランジスタと、前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、前記第2のトランジスタと電源線とに接続される第2の容量素子と、前記第2の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第2の駆動用トランジスタと、を有し、前記第1の駆動用トランジスタ電流能力と、前記第2の駆動用トランジスタとの電流能力とは異なることを特徴としている。

20

【0023】

本発明の表示装置は、第1の駆動用トランジスタ電流能力は、第2の駆動用トランジスタとの電流能力より高く、高階調表示を行うことを特徴としている。

30

【0024】

本発明の表示装置は、前記第2の駆動用トランジスタ電流能力は、前記第1の駆動用トランジスタとの電流能力より低く、低階調表示を行うことを特徴としている。

【0025】

本発明の表示装置は、アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、前記発光素子に接続される第1の駆動用トランジスタと、前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、前記発光素子に接続される第2の駆動用トランジスタと、を有し、前記第1の駆動用トランジスタのゲートドレイン間電圧と、前記第2の駆動用トランジスタのゲートドレイン間電圧とは異なることを特徴としている。

40

【0026】

本発明の表示装置は、アナログ信号が入力される信号線と、走査線と、複数のトランジスタと、発光素子と、を少なくとも有する表示装置において、前記第1の信号線と、前記走査線とに接続される第1のトランジスタと、前記第1のトランジスタと電源線とに接続される第1の容量素子と、前記第1の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第1の駆動用トランジスタと、前記第2の信号線と、前記走査線とに接続される第2のトランジスタと、前記第2のトランジスタと電源線とに接続される第2の容量素子と、前記第2の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第2の駆動用トランジスタと、を有することを特徴としている。

50

2の容量素子と、前記第2の容量素子にゲート電極が接続され、一方の電極が前記発光素子に接続される第2の駆動用トランジスタと、を有し、前記第1の駆動用トランジスタのゲートドレイン間電圧と、前記第2の駆動用トランジスタのゲートドレイン間電圧とは異なることを特徴としている。

【0027】

本発明の表示装置は、前記発光素子の輝度に応じて、前記発光素子に接続される複数の駆動用トランジスタを選択する手段を有することを特徴としている。

【0028】

【発明の実施の形態】

(実施の形態1)

10

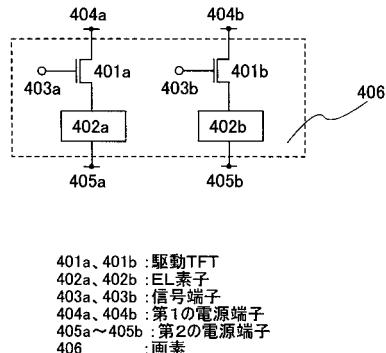

図4に、本発明の一実施形態を示す。一以上の画素406により構成された表示装置で、画素406はEL素子402a、402bと、EL素子402a、402bを駆動する駆動TFT401a、401bと、駆動TFT401a、401bのゲートと接続した信号端子403a、403bと、駆動TFT401a、401bの第1の端子と接続した第1の電源端子404a、404bと、EL素子402a、402bの第2の端子と接続した第2の電源端子405a、405bとを有する。駆動TFT401a、401bの第2の端子はEL素子402a、402bの第1の端子と接続している。

【0029】

駆動TFT401aと駆動TFT401bは異なる特性とする。異なる特性のTFTを用いることで、高階調表示と低階調表示の両方に適した駆動が可能となる。TFTを異なる特性とする方法は、TFTのサイズや形状を異なるものとする、TFTのドーパントやドーピング量を異なるものとする、TFTの並列数や直列数を異なるものとする、などがある。

【0030】

なお、駆動TFT401a、401bのゲートと信号端子403a、403bとの間、駆動TFT401a、401bの第1の端子と第1の電源端子404a、404bとの間、EL素子402a、402bの第2の端子と第2の電源端子405a、405bとの間、駆動TFT401a、401bの第2の端子とEL素子402a、402bの第1の端子との間に、別の素子を挿入しても良い。例えば、駆動TFT401a、401bの第1の端子と第1の電源端子404a、404bとの間にスイッチを挿入すれば、信号端子403a、403bの状態に関わりなくEL素子402a、402bの表示と非表示を制御できる。

【0031】

また、駆動TFT401a、401bはNchTFTでもPchTFTでも良い。

【0032】

また、EL素子402a、402bと、第1の電源端子404a、404bと、第2の電源端子405a、405bは、通常それぞれ共通とすることができますが、分けても良い。分けることで、高階調と低階調でのTFTの動作状態を別に制御することができる。例えばEL素子402aとEL素子402bを、高階調用と低階調用として別にして、例えば素子面積をEL素子402aは広く、EL素子402bは狭く作成する。素子面積が狭いほど一般に抵抗値は高くなり、また低階調ほどEL素子に流れる電流値は小さくなるため、EL素子での電圧降下が高階調と低階調で近くなる。駆動TFT401a、401bのV<sub>ds</sub>は、第1の電源端子404a、404bと第2の電源端子405a、405bの差からEL素子402a、402bでの電圧降下分を引いた値となる。ここでEL素子での電圧降下が高階調と低階調で近ければ、駆動TFT401a、401bのV<sub>ds</sub>は高階調と低階調で近い値となる。一般にTFTは飽和領域においてもV<sub>ds</sub>の上昇によってI<sub>ds</sub>が多少上昇する傾向にあり、正確な輝度調整の妨げとなる。ここでV<sub>ds</sub>を高階調と低階調で近い値とすることで、より正確な輝度調整ができるようになる。

【0033】

また、信号端子403a、403bは、別に分ける。しかし共通にしても良い。

20

30

40

50

## 【0034】

図5を用いて、動作について説明する。

## 【0035】

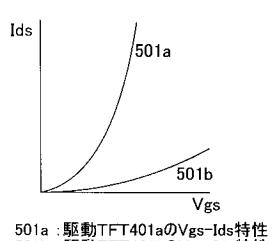

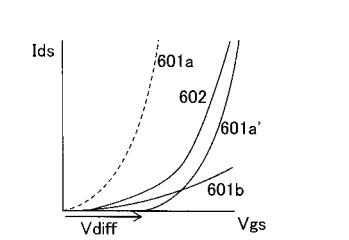

図5(A)は、駆動TFT401a～bのVgsとIdsとの関係を示している。ここでは例として駆動TFT401aに電流能力の高いTFTを使用し、駆動401bに電流能力の低いTFTを使用する。特性501aが駆動TFT401aのVgs-Ids特性、特性501bが駆動TFT401bのVgs-Ids特性である。なお、図4でIdsはEL素子402a、402bに流れる。

## 【0036】

EL素子は一般に電流値と輝度が比例関係にある。そのためIdsを制御することで輝度を制御することができる。表示装置の輝度はEL素子402a～bに流れる電流値の和となる。 10

## 【0037】

ここで駆動TFT401aと駆動TFT401bのVgsをそれぞれ個別に制御する。ここで駆動TFT401aのVgsをVgsa、駆動TFT401bのVgsをVgbsとする。個別に制御された駆動TFT401a、401bはそれぞれVgsa、Vgbsに応じた電流Idsa、IdsbをEL素子402a、402bに供給し、電流Idsa+Idsbが表示装置の輝度を決定する。

## 【0038】

輝度の高い高階調では駆動TFT401aのVgsをより高くし、輝度の低い低階調では駆動TFT401bのVgsをより高くする。 20

## 【0039】

図6に、駆動TFT401aと駆動TFT401bのゲートを異なる電圧にする例を示す。VgsaとVgbsは以下の関係になるよう決定する。

## 【0040】

## 【数1】

$$Vgsa = Vgbs - Vdiff \quad \dots \quad (\text{式1})$$

30

## 【0041】

特性601a'は駆動TFT401aのゲートにVgsaを印加した場合を示し、特性601bは駆動TFT401bのゲートにVgbsを印加した場合を示す。なお特性601a'は駆動TFT401aのゲートにVgbsを印加した特性特性601aをVdiffだけ電圧シフトした特性となる。

## 【0042】

飽和領域での電流値Idsは、駆動TFT401aのドレイン電流をIdsa'、駆動TFT401bのドレイン電流をIdsbとしたとき、以下の式であらわされる。 40

## 【0043】

## 【数2】

$$\begin{aligned}

Idsa' &= \frac{Wa}{La} \mu a Ca \frac{(Vgsa - Vtha)^2}{2} \\

&= \frac{Wa}{La} \mu a Ca \frac{(Vgsb - Vdiff - Vtha)^2}{2} \quad \dots \quad (\text{式 2}) \\

Idsb &= \frac{Wb}{Lb} \mu b Cb \frac{(Vgsb - Vthb)^2}{2}

\end{aligned}$$

10

## 【 0 0 4 4 】

ここで  $W_a$ 、 $W_b$ 、 $L_a$ 、 $L_b$ 、 $\mu_a$ 、 $\mu_b$ 、 $C_a$ 、 $C_b$ 、 $V_{tha}$ 、 $V_{thb}$ 、はそれぞれ駆動 TFT 401a と駆動 TFT 401b のゲート幅、ゲート長、移動度、酸化膜の単位面積当たり容量、閾値電圧である。

## 【 0 0 4 5 】

EL 素子 402a と 402b に流れる電流値の和  $I_{el}$  は、以下の式であらわされる。

## 【 0 0 4 6 】

## 【 数 3 】

20

$$\begin{aligned}

I_{el} &= Idsa' + Idsb \\

&= \frac{Wa}{La} \mu a Ca \frac{(Vgsb - Vdiff - Vtha)^2}{2} \quad \dots \quad (\text{式 3}) \\

&\quad + \frac{Wb}{Lb} \mu b Cb \frac{(Vgsb - Vthb)^2}{2}

\end{aligned}$$

## 【 0 0 4 7 】

また  $I_{el}$  は図 6 で特性 602 のように示すことができる。この  $I_{el}$  が表示装置の輝度 30 を決定する。

## 【 0 0 4 8 】

駆動 TFT 401b よりも駆動 TFT 401a の方が電流能力が高い。また消費電流の多い高階調表示では  $Idsa'$  の比率が高く、消費電流が少なくばらつきの影響を小さくしたい低階調表示では  $Idsb$  の比率が高くなる。駆動 TFT を階調に応じて使い分けることで、EL 素子 402a ~ b の劣化の影響が少なく、消費電力が少なく、ばらつきの影響の小さい表示装置となる。

## 【 0 0 4 9 】

$|Vgsb - Vdiff - Vtha| = 0$  では  $Idsa'$  はほぼ 0 となるため、表示装置の輝度はほとんど駆動 TFT 401b の供給する電流によって発生する。また、 $Vgsa$  と  $Vgsb$  が高くなるほど駆動 TFT 401a の供給する電流の  $I_{el}$  に占める割合は多くなる。以上のように、低階調では駆動 TFT 401b の供給する電流が多く、高階調では駆動 TFT 401a の供給する電流を多くする。

## 【 0 0 5 0 】

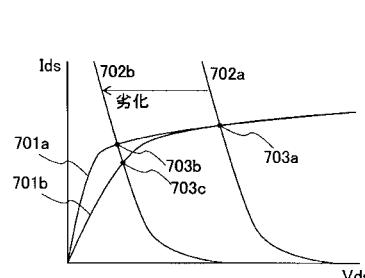

高階調で電流能力の高い TFT を用いた場合の利点を図 7 (A) で負荷曲線で示す。駆動 TFT 401a として、電流能力の高い TFT を用いた場合の  $Vds - Ids$  特性を特性 701a とすると、電流能力の低い TFT を用いた場合の  $Vds - Ids$  特性は特性 701b のようになる。また EL 素子 402a の劣化前の  $V - I$  特性を特性 702a、劣化後の  $V - I$  特性を特性 702b とする。特性 701a ~ b と特性 702a ~ b の交点が動作点 703a ~ c となる。このとき、特性 701a と特性 701b で、動作点 703a での 40

40

50

$I_{ds}$  が同じになるように駆動 TFT の  $V_{gs}$  を調整する。電流能力の高い TFT では、線形領域での電流値の立上り特性が急峻になる。同時に低い  $V_{ds}$  から飽和領域となっているため、EL 素子 402a が劣化して  $V_{ds}$  が低下しても線形領域での動作となりにくい。図 7 (A) では EL 素子 402a が劣化した場合の動作点の例として、電流能力の高い TFT を用いた場合の動作点を動作点 703b、電流能力の低い TFT を使った場合の動作点を動作点 703c として示す。

#### 【0051】

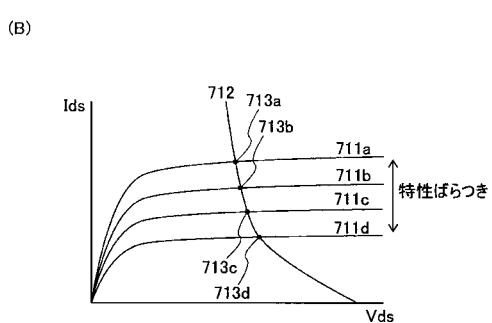

低階調で電流能力の低い TFT を用いた場合の利点を図 7 (B) で負荷曲線で示す。駆動 TFT 401b として、電流能力の高い TFT を用いた場合の  $V_{ds}$  -  $I_{ds}$  特性が特性 711a から特性 711d までの範囲でばらついたとすると、電流能力の低い TFT を用いた場合の  $V_{ds}$  -  $I_{ds}$  特性は特性 711b から特性 711c までの範囲のばらつきとなり、ばらつきの範囲は狭くなる。また EL 素子 402b の  $V$  -  $I$  特性を特性 712 とする。特性 711a ~ d と特性 712 の交点が動作点 713a ~ d となる。動作点は電流能力の高い TFT を用いた場合は 713a から 713d の範囲でばらつくが、電流能力の低い TFT を用いた場合は 713b から 713c の範囲でのばらつきとなり、ばらつきの範囲は狭くなる。

#### 【0052】

電流能力の低い TFT を用いることで、ばらつきの範囲が狭くなる理由を説明する。飽和領域での TFT の  $I_{ds}$  は以下の式で示すことができる。

#### 【0053】

#### 【数4】

$$I_{ds} = \frac{W}{L} \mu C \frac{(V_{gs} - V_{th})^2}{2} \quad \dots \quad (\text{式4})$$

#### 【0054】

ここで  $W$ 、 $L$ 、 $\mu$ 、 $C$ 、 $V_{th}$  はそれぞれ TFT のゲート幅、ゲート長、移動度、酸化膜の単位面積当たり容量、閾値電圧である。ここで例えば  $W/L$  を小さくすることで、電流能力が低くなる。上記式より駆動 TFT 401b の電流能力が低いほど、同じ  $I_{ds}$  でもより高い  $V_{gs}$  を印加することとなる。より高い  $V_{gs}$  を印加することで  $V_{th}$  のばらつきの  $I_{ds}$  への影響を小さくすることが出来、 $I_{ds}$  のばらつきを小さくすることができる。

#### 【0055】

高階調ではもともと  $V_{gs}$  が高くなるため  $V_{th}$  の影響は小さいため、駆動 TFT 401a に電流能力の高い TFT を用いても問題になることはない。また低階調では  $V_{gs}$  が低いため飽和領域となりやすく、駆動 TFT 401b に電流能力の低い TFT を用いても問題になることはない。

#### 【0056】

本実施形態では、高階調では電流能力の高い駆動 TFT 401a を電流源として主に用い、低階調では電流能力の低い駆動 TFT 401b を電流源として主に用いる。階調に応じて TFT を使い分けることで、EL 素子 402a ~ b が劣化しても輝度が低下しにくく、また TFT のばらつきの影響が少ない表示装置とすることができる。

#### 【0057】

第 1 の電源端子 404a、404b と第 2 の電源端子 405a、405b との間には、EL 素子 402a、402b の駆動電圧と駆動 TFT 401a、401b の飽和領域までの電圧の他に、EL 素子 402a、402b が劣化した場合の EL 素子 402a、402b

10

20

30

40

50

の抵抗増による電圧降下分をあらかじめ印加している。こうすることでEL素子402a、402bでの電圧降下が増加して駆動TFT401a、401bのVdsが低くなつても、駆動TFT401a、401bが線形領域での動作とならず、輝度低下の原因となつないようにしている。しかしEL素子402a、402bの抵抗増による電圧降下分をあらかじめ印加することは、電源電圧を高くすることであり、消費電力が増加する原因となる。本実施形態では高階調で電流能力の高い駆動TFTを主に用いることで、より低いVdsまで飽和領域としている。より低いVdsまで飽和領域となつてゐるため、電源端子404a、404bと電源端子405a、405bとの間をより低い電圧に設定しても、EL素子402a、402bの劣化の影響が発生しにくくなる。以上により消費電力が低く、また発熱が少なく、TFTの劣化が生じにくくできる。

10

## 【0058】

VgsaとVgsbに電位差Vdfffを与える方法の一例を示す。両端に電位差を持った容量素子を、駆動TFT401a、401bのどちらか一方または両方の、ゲートと信号端子403a、403bの間に挿入する。結果として容量素子を挿入した駆動TFT401a、401bのゲートには、信号端子403a、403bの電圧と容量素子の両端の電位差の和が印加される。この例では、信号端子403a、403bを共通にしても、容量素子を使うことで駆動TFT401a、401bのゲートに電位差Vdfffを与えることが可能である。信号端子403a、403bを共通に出来れば、駆動TFT401a、401bの制御が容易になる。

20

## 【0059】

## (実施の形態2)

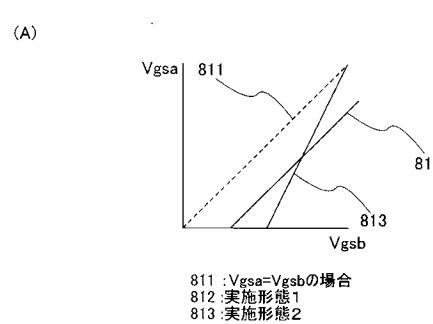

図8にて、本発明の一実施形態を説明する。駆動TFT401aと駆動TFT401bのVgsを異なる電圧に設定するする方法として、実施形態1では駆動TFT401aのVgsを電圧シフトさせた。図8(A)に駆動TFT401aのVgsと、駆動TFT401bのVgsとの関係を示す。ここで駆動TFT401aのVgsをVgsa、駆動TFT401bのVgsをVgsbとする。VgsaとVgsbとして等しい電圧を印加する場合を特性811とすると、実施形態1では特性812となる。本実施形態では実施形態1と異なる電圧設定方法を示す。

## 【0060】

Vgsbに対してVgsaが低階調では低くなるように設定し、高階調になるほどVgsaに対してVgsbが近い電圧となるよう設定する。特性813で本実施形態での電圧設定を示す。

30

## 【0061】

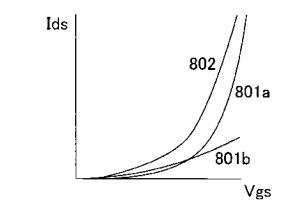

図8(B)に上記Vgsを印加した駆動TFT401aのVgs-Ids特性801aと、駆動TFT401bのVgs-Ids特性801bと、駆動TFT401aと駆動TFT401bの合計電流の特性802を示す。低階調では駆動TFT401bのIdsの比率が高く、また高階調では駆動TFT401aのIdsの比率が高くなる。EL素子401a、401bが劣化しても輝度が低下しにくく、また駆動TFT401a、401bのばらつきの影響が少ない表示装置を作ることができる。

40

## 【0062】

EL素子401a、401bの劣化によって輝度が変化しないためには、駆動TFT402a、402bの飽和領域がより低いVdsから始まるようにする。このとき飽和領域はVds=VgsとなるVdsから始まるため、EL素子401a、401bの劣化の影響を避けるにはVgsが低いほどよい。Vgsは階調によって変化し、最高階調でVgsが最大値となる。つまり最高階調での駆動TFT402aと駆動TFT402bのVgsを極力低くすることが有効となる。最高階調では駆動TFT402aと駆動TFT402bの電流値を最大にしつつVgsを最も低くするためには、最高階調でのVgsを等しくすればよい。

## 【0063】

本実施形態により、低階調でTFTのばらつきの影響が少なく、高階調でEL素子の劣化

50

の影響が少なくできる。さらに劣化の影響を最も受ける階調でのV<sub>g</sub>sをできるだけ低くすることが可能となるため、より劣化の影響を受けにくくなる。

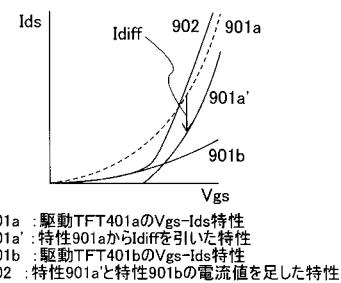

【0064】

(実施の形態3)

図9にて、本発明の一実施形態を説明する。実施形態1と2では駆動TFT401aと駆動TFT401bのV<sub>g</sub>sを異なる電圧に設定した。本実施形態では駆動TFT401aと駆動TFT401bのV<sub>g</sub>sを等しくした場合でも、高階調で駆動TFT401aを主に使い、低階調で駆動TFT401bを主に使う動作とできる。

【0065】

駆動TFT401aの供給する電流をI<sub>ds</sub>a、駆動TFT401bの供給する電流をI<sub>ds</sub>bとする。本実施形態ではI<sub>ds</sub>aから一定電流I<sub>diff</sub>を引いた電流をEL素子402aに供給する。EL素子102a～bに供給される電流I<sub>el</sub>は、以下の式であらわされる。

【0066】

【数5】

$$I_{el} = I_{ds}a - I_{diff} + I_{ds}b \cdots (I_{ds}a > I_{diff}) \quad \dots \quad (式5)$$

$$I_{el} = I_{ds}b \cdots (I_{ds}a \leq I_{diff})$$

10

20

【0067】

図9でV<sub>g</sub>sを印加した駆動TFT401aのV<sub>g</sub>s-I<sub>ds</sub>特性901aと、特性901aからI<sub>diff</sub>を引いた特性901a'、駆動TFT401bのV<sub>g</sub>s-I<sub>ds</sub>特性901bと、特性901a'、特性901bの和の特性902を示す。ここで特性901aがI<sub>ds</sub>aで、特性901bがI<sub>ds</sub>bで、特性902がI<sub>el</sub>である。低階調では駆動TFT401bのI<sub>ds</sub>の比率が高く、また高階調では駆動TFT401aのI<sub>ds</sub>の比率が高くなる。これによりEL素子401a～bが劣化しても輝度が低下しにくく、また駆動TFT401a、401bのばらつきの影響が少ない表示装置を作ることができる。

【0068】

駆動TFT401aのV<sub>g</sub>sを電圧シフトさせる実施形態1の方法や、駆動TFT401aと駆動TFT401bのV<sub>g</sub>sをそれぞれ個別に制御する実施形態2の方法と異なり、本実施形態では駆動TFT401aと駆動TFT401bのV<sub>g</sub>sが等しい。V<sub>g</sub>sが等しければ信号端子403a、403bを共通化でき、階調の制御が簡略化できる。

【0069】

(実施の形態4)

実施形態1から3において、駆動TFTを三つ以上使ってもよい。例えば駆動TFTを三つ使う場合は、低階調、中階調、高階調と階調を三領域に分け、それぞれに適した特性の駆動TFTを配置する。駆動TFTを三つ以上使うことにより、微小輝度発光でも高輝度発光でも劣化とばらつきの影響を抑えることができる。

【0070】

特に携帯機器のように暗環境でも明環境でも利用する表示装置の場合、暗環境では微小輝度領域での発光、明環境では高輝度領域での発光が要求される。例えば駆動TFTを三つ使う場合は、微小輝度領域と高輝度領域でそれぞれ二つの駆動TFTを使う。微小輝度領域での発光の場合、電流能力の弱い第1の駆動TFTと電流能力が中程度の第2の駆動TFTを使い、微小輝度領域の中でも低階調は第1の駆動TFTを、微小輝度領域の高階調は第2の駆動TFTを使う。また高輝度領域での発光の場合、電流能力が中程度の第2の

30

40

50

駆動 TFT と電流能力の強い第 3 の駆動 TFT を使い、高輝度領域の中でも低階調は第 2 の駆動 TFT を、高輝度領域の高階調は第 3 の駆動 TFT を使う。また微小輝度領域では  $V_{ds}$  が低くても飽和領域を維持するため電源電圧を低くすることができ、消費電力の低減が可能である。以上により三つ以上の駆動 TFT を使うことで、輝度領域に関わらず最適な駆動が可能となる。もちろん三つ以上の駆動 TFT を単一の輝度領域で同時に使ってもよい。

#### 【0071】

##### 【実施例】

以下に、本発明の実施例について記載する。

#### 【0072】

##### 【実施例 1】

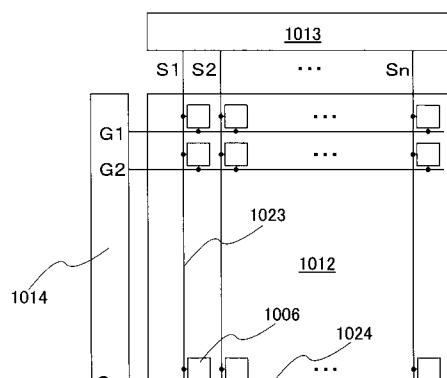

本実施例においては、実施形態 1 で示した表示装置の構成例について説明する。図 10 に表示装置の構成例を示す。複数の画素 1006 が  $m$  行  $n$  列のマトリクス状に配置された画素部 1012 を有し、画素部 1012 周辺には、信号線駆動回路 1013、行選択線駆動回路 1014 を有している。S1 ~ Sn で表記された信号線 1023 は画素 1006 と列に対応して接続しており、また信号線駆動回路 1013 に接続している。G1 ~ Gm で表記された行選択線 1024 は画素 1006 と行に対応して接続しており、また行選択線駆動回路 1014 に接続している。その他に電源線などを有するが図 10 では省略する。

#### 【0073】

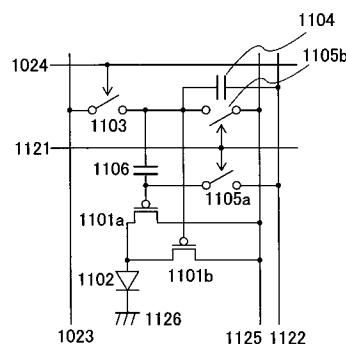

図 11 に画素 1006 の構成例を示す。駆動 TFT 1101a、1101b と、EL 素子 1102 と、書込用スイッチ 1103 と、第 1 の容量素子（画素容量）1104 と、電圧シフト容量用スイッチ 1105a ~ b と、第 2 の容量素子（電圧シフト容量）1106 を有する。EL 素子 1102 の第 2 の端子はカソード 1126 と接続し、駆動 TFT 1101a、1101b のドレインは EL 素子 1102 の第 1 の端子と接続し、ソースはアノード 1125 と接続する。駆動 TFT 1101a のゲートは電圧シフト容量 1106 の第 2 の端子と接続し、かつ電圧シフト容量用スイッチ 1105a を介して配線（画素容量線）1122 と接続する。駆動 TFT 1101b のゲートと電圧シフト容量 1106 の第 1 の端子は書込用スイッチ 1103 を介して信号線 1023 と接続し、かつ電圧シフト容量用スイッチ 1105b を介してアノード 1125 と接続し、かつ画素容量 1104 の第 1 の端子と接続している。画素容量 1104 の第 2 の端子は画素容量線 1122 と接続している。書込用スイッチ 1103 は走査線（行選択線）1024 で制御し、電圧シフト容量用スイッチ 1105a ~ b は配線（電圧シフト容量制御信号線）1121 で制御する。

#### 【0074】

本実施例における画素 1006 の動作について説明する。

#### 【0075】

まず電圧シフト容量 1106 に任意の電圧  $V_{diff}$  を印加する。なお電圧  $V_{diff}$  は駆動 TFT 1101a、1101b の  $V_{gs}$  の差となる。アノード 1125 と画素容量線 1122 に  $V_{diff}$  の電位差を与え、電圧シフト容量制御信号線 1121 により電圧シフト容量用スイッチ 1105a ~ b を ON する。電圧シフト容量 1106 に電圧  $V_{diff}$  分の電荷が充電された後、電圧シフト容量制御信号線 1121 により電圧シフト容量用スイッチ 1105a ~ b を OFF する。以上の動作により電圧シフト容量 1106 の両端に電位差  $V_{diff}$  が印加できる。なお、これらの動作時には書込用スイッチ 1103 は OFF することが望ましいがこれに限らない。

#### 【0076】

次に電圧シフト容量 1106 の両端に電位差  $V_{diff}$  が印加された状態で、行選択線 1024 により書込用スイッチ 1103 を ON する。このとき信号線 1023 に EL 素子 1102 の発光輝度に見合う電圧  $V_{signal}$  を印加する。画素容量 1104 の第 1 の端子が  $V_{signal}$  に達した後、行選択線 1024 により書込用スイッチ 1103 を OFF する。以上の動作により駆動 TFT 1101b のゲートには  $V_{signal}$  が印加され、駆動 TFT 1101a のゲートには  $V_{signal} - V_{diff}$  が印加される。

10

20

30

40

50

## 【0077】

以上の動作により、EL素子1102は発光する。ここで駆動TFT1101aと駆動TFT1101bの特性が異なり、かつ駆動TFT1101aと駆動TFT1101bのVgsが異なるため、実施形態1で示した特徴を持つ表示装置とすることができます。

## 【0078】

また、比較的単純な方法で駆動TFT1101aと駆動TFT1101bに異なるVgsを与えることができる。

## 【0079】

電圧シフト容量1106に電位差を与えるために、アノード1125と画素容量線1122の電位差を用いた理由を示す。アノード1125はEL素子1102の特性によって調整する必要がある。またVdiffも駆動TFT1101a～bとEL素子1102の特性によって調整する必要がある。しかし画素容量線1122の電位は一般に任意であり、適当な電位に設定してもよく、アノード1125とVdiffに応じて決めることが可能でだからである。

## 【0080】

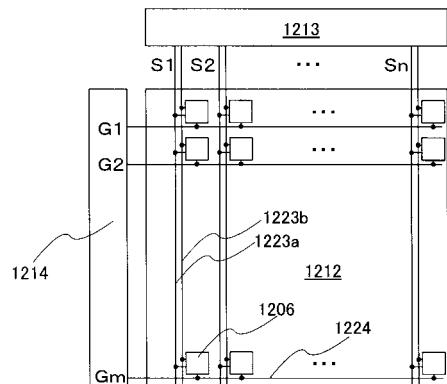

## [実施例2]

本実施例においては、実施形態2で示した表示装置の構成例について説明する。図12に表示装置の構成例を示す。複数の画素1206がm行n列のマトリクス状に配置された画素部1212を有し、画素部1212周辺には、信号線駆動回路1213、行選択線駆動回路1214を有している。S1～Snで表記された信号線1223a～bは画素1206と列に対応して接続しており、また信号線駆動回路1213に接続している。G1～Gmで表記された行選択線1224は画素1206と行に対応して接続しており、また行選択線駆動回路1214に接続している。その他に電源線などを有するが図12では省略する。

## 【0081】

図13に画素1206の構成例を示す。駆動TFT1301a、1301bと、EL素子1302と、書込用スイッチ1303a、1303bと、画素容量1304a～bとを有する。EL素子1302の第2の端子はカソード1326と接続し、駆動TFT1301a、1301bのドレインはEL素子1302の第1の端子と接続し、ソースはアノード1325と接続する。駆動TFT1301a、1301bのゲートはそれぞれ画素容量1304a、1304bの第1の端子と接続し、かつそれぞれ書込用スイッチ1303a、1303bを介してそれぞれ信号線1023a、1023bと接続している。画素容量1304a、1304bの第2の端子は画素容量線1322と接続している。書込用スイッチ1303a、1303bは行選択線1224で制御する。

## 【0082】

画素1206の動作について説明する。

## 【0083】

行選択線1224により書込用スイッチ1303a、1303bをONする。このとき信号線1223a、1223bにEL素子1302の発光輝度に見合う電圧Vsignal a、Vsignal bを印加する。このときVsignal aとVsignal bは異なる電圧に設定する。画素容量1304a、1304bの第1の端子がVsignal a、Vsignal bに達した後、行選択線1224により書込用スイッチ1303a、1303bをOFFする。以上の動作により駆動TFT1301a、1301bのゲートにはVsignal a、Vsignal bが印加される。

## 【0084】

以上の動作により、EL素子1302は発光する。ここで駆動TFT1301aと駆動TFT1301bの特性が異なり、かつ駆動TFT1301aと駆動TFT1301bのVgsが異なるため、実施形態2で示した特徴を持つ表示装置とすることができます。

## 【0085】

また、駆動TFT1301aと駆動TFT1301bのVgsを、階調に応じて個別に設

10

20

30

40

50

定できるため、制御の自由度が高い。また構造が単純であるため信頼性が高い。

【0086】

[実施例3]

本実施例においては、実施形態3で示した表示装置の構成について説明する。表示装置の構成例については図10と実施例1で示した。ただし実施例1とは画素1006の構成が異なる。

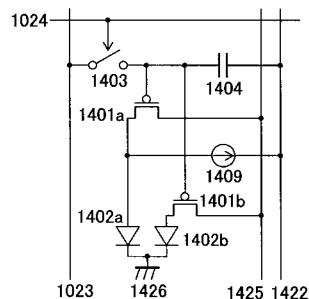

【0087】

図14に画素1006の構成例を示す。駆動TFT1401a、1401bと、EL素子1402a、1402bと、書込用スイッチ1403と、画素容量1404とを有する。EL素子1402a、1402bの第2の端子はカソード1426と接続し、駆動TFT1401a、1401bのドレインはそれぞれEL素子1402a、1402bの第1の端子と接続し、ソースはアノード1425と接続する。EL素子1402aの第1の端子はさらに電流源1409と接続している。電流源は画素容量線1422と接続しているが、これに限らない。駆動TFT1401a、1401bのゲートは画素容量1404の第1の端子と接続し、かつ書込用スイッチ1403を介して信号線1023と接続している。画素容量1404の第2の端子は画素容量線1422と接続している。書込用スイッチ1403は行選択線1024で制御する。

【0088】

本実施例における画素1006の動作について説明する。

【0089】

行選択線1024により書込用スイッチ1403をONする。このとき信号線1023にEL素子1402a、1402bの発光輝度に見合う電圧Vsingnalを印加する。画素容量1404の第1の端子がVsingnalに達した後、行選択線1024により書込用スイッチ1403をOFFする。以上の動作により駆動TFT1401a、1401bのゲートにはVsingnalが印加される。

【0090】

以上の動作により、EL素子1402a、1402bは発光する。ここで駆動TFT1401aと駆動TFT1401bの特性が異なり、かつ駆動TFT1401aのドレインに接続した電流源1409によりEL素子1402aへの電流供給が減るため、実施形態3で示した特徴を持つ表示装置とすることができます。

【0091】

また、比較的単純な方法で駆動TFT1401aと駆動TFT1401bを高階調と低階調で使い分けることができる。

【0092】

電流源1409はTFTを使うことで容易に実現できる。TFTのVgsを飽和領域で動作するように設定することで、駆動TFT1401aのドレイン電圧に関わりなく電流を減らすことができる。また、駆動TFT1401aの供給電流が少ないとドレイン電圧が低下し、電流源1409のTFTは線形領域で動作するようになり減らす電流値も少なくなる。

【0093】

実施例2から3において、容量線とアノードは共通にしてもよい。また実施例1から3において、駆動TFTを3つ以上使ってもよい。

【0094】

[実施例4]

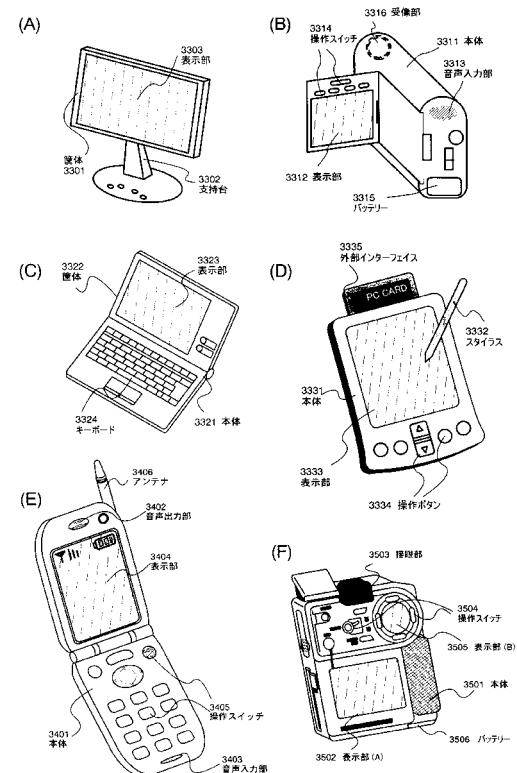

本発明の表示装置には様々な用途がある。本実施例では、本発明の適用が可能な電子機器の例について説明する。

【0095】

このような電子機器には、携帯情報端末（電子手帳、モバイルコンピュータ、携帯電話等）、ビデオカメラ、デジタルカメラ、パーソナルコンピュータ、テレビ等が挙げられる。それらの一例を図7に示す。

10

20

30

40

50

## 【0096】

図15(A)はELディスプレイであり、筐体3301、支持台3302、表示部3303等を含む。本発明の表示装置は表示部3303にて用いることが出来る。

## 【0097】

図15(B)はビデオカメラであり、本体3311、表示部3312、音声入力部3313、操作スイッチ3314、バッテリー3315、受像部3316等を含む。本発明の表示装置は表示部3312にて用いることが出来る。

## 【0098】

図15(C)はパーソナルコンピュータであり、本体3321、筐体3322、表示部3323、キーボード3324等を含む。本発明の表示装置は表示部3323にて用いることが出来る。

## 【0099】

図15(D)は携帯情報端末であり、本体3331、スタイルス3332、表示部3333、操作ボタン3334、外部インターフェイス3335等を含む。本発明の表示装置は表示部3333にて用いることが出来る。

## 【0100】

図15(E)は携帯電話であり、本体3401、音声出力部3402、音声入力部3403、表示部3404、操作スイッチ3405、アンテナ3406を含む。本発明の表示装置は表示部3404にて用いることが出来る。

## 【0101】

図15(F)はデジタルカメラであり、本体3501、表示部(A)3502、接眼部3503、操作スイッチ3504、表示部(B)3505、バッテリー3506を含む。本発明の表示装置は、表示部(A)3502、表示部(B)3505にて用いることが出来る。

## 【0102】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。

## 【発明の効果】

本発明によると、特性の異なる駆動TFTを複数使うことで、EL素子の劣化の影響が少なく、低電圧で動作可能であり、しかも駆動TFTのばらつきの影響を少なくすることができる。

## 【図面の簡単な説明】

【図1】EL素子の発光方法を示す図。

【図2】図1の特性を示す負荷曲線図。

【図3】図1の特性を示す負荷曲線図。

【図4】本発明の表示装置の構成を示す図。

【図5】駆動TFTの特性を示す図。

【図6】本発明の表示装置の動作を示す図。

【図7】本発明の表示装置の動作を示す負荷曲線図。

【図8】本発明の表示装置の動作を示す図。

【図9】本発明の表示装置の動作を示す図。

【図10】本発明の実施例を示す図。

【図11】本発明の実施例を示す図。

【図12】本発明の実施例を示す図。

【図13】本発明の実施例を示す図。

【図14】本発明の実施例を示す図。

【図15】本発明が適用可能な電子機器の例を示す図。

10

20

30

40

【図1】

【図2】

【図3】

301a, 301b : 駆動TFT101のVds-Ids特性

302 : EL素子102のV-I特性

303a, 303b : 動作点

【図4】

【図5】

501a : 駆動TFT401aのVgs-Ids特性

501b : 駆動TFT401bのVgs-Ids特性

【図7】

701a, 701b : 駆動TFT401aのVds-Ids特性

702a, 702b : EL素子402aのV-I特性

703a~703c : 動作点

【図6】

601a : 駆動TFT401aのVgs-Ids特性

601a' : 特性601aをVdiff電圧シフトさせた特性

601b : 駆動TFT401bのVgs-Ids特性

602 : 特性601a'と特性601bの電流値を足した特性

711a~711d : 駆動TFT401bのVds-Ids特性

712 : EL素子402bのV-I特性

713a~713d : 動作点

【図8】

(B)

801a : 駆動TFT401aの供給する電流 $Id_{sa}$

801b : 駆動TFT401bの供給する電流 $Id_{sb}$

802 :  $Id_{sa} + Id_{sb}$

【図10】

1006 : 画素

1012 : 画素部

1013 : 信号線駆動回路

1014 : 行選択線駆動回路

1023 : 信号線

1024 : 行選択線

【図9】

【図11】

1101a, 1101b : 駆動TFT

1102 : EL素子

1103 : 書込用スイッチ

1104 : 画素容量

1105a, 1105b : 電圧シフト容量用スイッチ

1106 : 電圧シフト容量

1121 : 電圧シフト容量制御信号線

1122 : 画素容量線

1123 : 信号線

1124 : 行選択線

1125 : アーノード

1126 : カソード

【図12】

1206 : 画素

1212 : 画素部

1213 : 信号線駆動回路

1214 : 行選択線駆動回路

1223a~b : 信号線

1224 : 行選択線

【図13】

1301a, 1301b : 駆動TFT

1302 : EL素子

1303a, 1303b : 書込スイッチ

1304a, 1304b : 画素容量

1322 : 画素容量線

1223a, 1223b : 信号線

1224 : 行選択線

1325 : アノード

1326 : カソード

【図14】

1401a, 1401b : 駆動TFT

1402 : EL素子

1403 : 書込用スイッチ

1404 : 画素容量

1409 : 電流源

1422 : 画素容量線

1023 : 信号線

1024 : 行選択線

1425 : アノード

1426 : カソード

【図15】

## フロントページの続き

---

| (51) Int.Cl. <sup>7</sup> | F I    | テーマコード(参考) |

|---------------------------|--------|------------|

|                           | G 09 G | 3/20 624B  |

|                           | G 09 G | 3/20 641D  |

|                           | G 09 G | 3/20 642C  |

|                           | G 09 G | 3/20 670J  |

|                           | H 05 B | 33/14 A    |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2004341368A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2004-12-02 |

| 申请号            | JP2003139665                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2003-05-16 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 半导体能源研究所有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 宮川惠介                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 宮川 惠介                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | H01L51/50 G09F9/30 G09F9/33 G09G3/20 G09G3/30 H01L27/32 H05B33/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G09G3/3233 G09G3/3258 G09G2300/0819 G09G2300/0852 G09G2300/0876 G09G2310/0262 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| FI分类号          | G09G3/30.J G09F9/30.338 G09F9/30.365.Z G09F9/33.Z G09G3/20.611.H G09G3/20.624.B G09G3/20.641.D G09G3/20.642.C G09G3/20.670.J H05B33/14.A G09F9/30.365 G09F9/33 G09G3/20.641.K G09G3/3233 G09G3/3266 G09G3/3291 H01L27/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 3K007/AB03 3K007/AB06 3K007/AB11 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 5C080/AA06 5C080/BB05 5C080/DD03 5C080/DD29 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ05 5C080/KK01 5C080/KK07 5C080/KK43 5C080/KK47 5C094/AA04 5C094/AA24 5C094/AA31 5C094/AA53 5C094/AA55 5C094/BA03 5C094/BA26 5C094/BA29 5C094/CA19 5C094/DB04 5C094/EA04 5C094/FB14 5C094/HA06 5C094/HA08 3K107/AA01 3K107/BB01 3K107/CC12 3K107/CC21 3K107/CC33 3K107/EE03 3K107/HH04 3K107/HH05 5C094/AA13 5C380/AA01 5C380/AA03 5C380/AB06 5C380/AB15 5C380/AB21 5C380/AB25 5C380/AC07 5C380/AC08 5C380/AC09 5C380/AC11 5C380/AC12 5C380/BA01 5C380/BA05 5C380/BA38 5C380/BA39 5C380/BA46 5C380/BB02 5C380/BD02 5C380/BD10 5C380/CA12 5C380/CB17 5C380/CB31 5C380/CC01 5C380/CC26 5C380/CC27 5C380/CC30 5C380/CC33 5C380/CC38 5C380/CC42 5C380/CC45 5C380/CC46 5C380/CC52 5C380/CC62 5C380/CC63 5C380/CD013 5C380/CD024 5C380/CD025 5C380/CE02 5C380/DA02 5C380/DA06 5C380/HA12 5C380/HA13 |         |            |

| 其他公开文献         | <a href="#">JP2004341368A5</a><br><a href="#">JP4623939B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

### 摘要(译)

驱动TFT在饱和区域中操作，使得即使EL元件劣化，亮度也不太可能降低。然而，出现诸如高电压，高功耗和大量发热的问题。此外，当驱动TFT在饱和区域中操作时，由于驱动TFT的变化而导致亮度不均匀。[解决方案]作为驱动用TFT，高灰度级使用高电流能力的TFT，低灰度级使用电流能力低的TFT。具有高电流能力的TFT即使在较低的Vgs下也可以提供大电流，因此即使当Vds较低时也不大可能处于线性区域。因此，即使EL元件劣化，亮度也不可能降低，并且可以以低电压驱动EL元件。具有低电流能力的TFT通过施加更高的Vgs来提供电流。高Vgs可以减少TFT特性变化（尤其是Vth变化）的影响。[选择图]图13