(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4855648号

(P4855648)

(45) 発行日 平成24年1月18日(2012.1.18)

(24) 登録日 平成23年11月4日(2011.11.4)

|                      |                     |

|----------------------|---------------------|

| (51) Int.Cl.         | F 1                 |

| G09G 3/30 (2006.01)  | G09G 3/30   H       |

| G09G 3/20 (2006.01)  | G09G 3/30   K       |

| H01L 51/50 (2006.01) | G09G 3/20   6 1 1 H |

|                      | G09G 3/20   6 3 1 V |

|                      | G09G 3/20   6 4 1 D |

請求項の数 5 (全 11 頁) 最終頁に続く

|           |                               |           |                                                                                                                                                                                                                                   |

|-----------|-------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2004-101143 (P2004-101143)  | (73) 特許権者 | 510048417<br>グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー<br>GLOBAL OLED TECHNOLOGY LLC.<br>アメリカ合衆国、バージニア州、ハーベンドン、パーク・センター・ロード 1387<br>3、スイート 330<br>13873 Park Center Road, Suite 330, Herndon, VA 20171, United States of America |

| (22) 出願日  | 平成16年3月30日 (2004.3.30)        |           |                                                                                                                                                                                                                                   |

| (65) 公開番号 | 特開2005-284172 (P2005-284172A) |           |                                                                                                                                                                                                                                   |

| (43) 公開日  | 平成17年10月13日 (2005.10.13)      |           |                                                                                                                                                                                                                                   |

| 審査請求日     | 平成19年3月26日 (2007.3.26)        |           |                                                                                                                                                                                                                                   |

最終頁に続く

(54) 【発明の名称】有機EL表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

有機EL素子および輝度データに応じた駆動電流を前記有機EL素子に供給する駆動トランジスタを各表示画素に含み、この表示画素をマトリクス配置する有機EL表示装置において、

表示画素の位置と、その表示画素における駆動トランジスタの輝度データに対する駆動電流の傾きを補正する補正用ゲインを記憶する補正用ゲイン記憶部と、

表示画素の位置と、その表示画素における駆動トランジスタの輝度データに対するオフセットを補正するための補正用オフセットを所定の複数の表示画素からなるエリア毎に記憶する補正用オフセット記憶部と、

画素毎の輝度データを画素位置に応じて、前記補正用ゲイン記憶部に記憶されている補正用ゲインおよび前記補正用オフセット記憶部に記憶されている補正用オフセットを得て、これを用いて該当画素の輝度データに補正して補正輝度データを生成する補正部と、

表示画素がマトリクス配置された表示エリア内の全部の表示画素について、互いに異なる2以上の輝度データに基づいて発光させる全体発光制御手段と、

前記エリア内の複数の表示画素の有機EL素子について、異なる2以上の輝度データに基づいて選択的に発光させる選択発光制御手段と、

全体および選択発光させた際の駆動電流をそれぞれ検出する電流検出手段と、

検出した駆動電流に基づき選択された表示画素における輝度データに対する駆動電流を選択された画素の数で割った平均電流の傾きについて、全体の表示画素における輝度データ

10

20

タに対する駆動電流を全画素数で割った平均電流の傾きとの関係を算出する傾き特性算出手段と

を有し、

前記傾き特性算出手段において算出された傾き特性に対応する補正用ゲインを前記補正用ゲイン記憶部に記憶させるとともに、前記補正部において生成された補正輝度データに基づいて、前記駆動トランジスタを駆動して対応する有機EL素子に駆動電流を供給して各表示画素の表示を行うことを特徴とする有機EL表示装置。

【請求項2】

請求項1に記載の装置において、

前記補正部は、輝度データに対し、補正用ゲインを乗算することを特徴とする有機EL表示装置。 10

【請求項3】

請求項1に記載の装置において、

前記補正部は、前記補正用オフセットを前記輝度データに加算または減算することを特徴とする有機EL表示装置。

【請求項4】

請求項1～3のいずれか1つに記載の装置において、

前記補正用ゲイン記憶部は、水平または垂直方向の1ライン毎に補正值を記憶することを特徴とする有機EL表示装置。

【請求項5】

請求項1に記載の装置において、

検出した駆動電流に基づき選択された表示画素における輝度データに対する駆動電流を選択された画素の数で割った平均電流のオフセットについて、全体の表示画素における輝度データに対する駆動電流を全画素数で割った平均電流のオフセットとの関係を算出するオフセット特性算出手段と、

をさらに有し、

前記オフセット特性算出手段において算出されたオフセット特性に対応する補正用オフセットを前記補正用オフセット記憶部に記憶させる有機EL表示装置。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は、有機EL素子を含む表示画素をマトリクス配置する有機EL表示装置、特に表示画素における輝度不均一性の補正に関する。

【背景技術】

【0002】

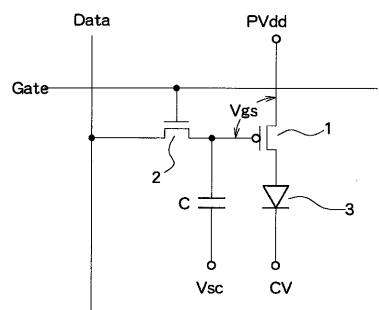

図1に、アクティブ型の有機EL表示装置における1画素分の回路(画素回路)の構成例を示す。ソースが電源ラインP V d dに接続されたPチャンネルの駆動TFT1のドレインが有機EL素子3のアノードに接続され、有機EL素子3のカソードが陰極電源C Vに接続されている。駆動TFT1のゲートには、Nチャンネルの選択TFT2のソースが接続されており、この選択TFT2のドレインはデータラインD a t aに接続され、ゲートはゲートラインG a t eに接続されている。また、駆動TFT1のゲートには、保持容量Cの一端が接続されており、他端は容量電源ラインV s cに接続されている。 40

【0003】

従って、水平方向に伸びるゲートラインをHレベルにして、選択TFT2をオンし、その状態で垂直方向に伸びるデータラインD a t aに表示輝度に応じた電圧を有するデータ信号をのせることで、データ信号が保持容量Cに蓄積される。これによって、駆動TFT1がデータ信号に応じた駆動電流を有機EL素子3に供給して、有機EL素子3が発光する。

【0004】

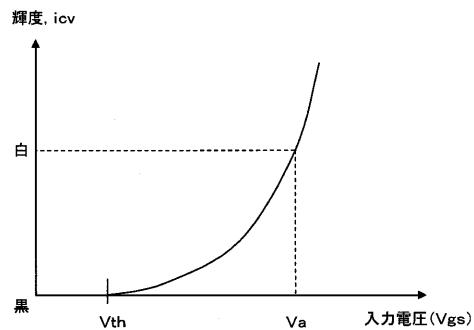

ここで、有機EL素子の発光量と電流はほぼ比例関係にある。通常、駆動TFT1のゲ

50

ート -  $P_{Vdd}$  には画像の黒レベル付近でドレイン電流が流れ始めるような電圧 ( $V_{th}$ ) を与える。また、画像信号の振幅としては、白レベル付近で所定の輝度となるような振幅を与える。

**【0005】**

図2は駆動TFT1の入力信号電圧(ゲートソース間電圧  $V_{gs}$  = データライン  $D_{at}$  aの電圧と電源  $P_{Vdd}$  の差)に対する有機EL素子3に流れる電流  $i_{cv}$  (輝度に対応する)の関係を示している。そして、黒レベル電圧として、 $V_{th}$  を与え、白レベル電圧として、 $V_a$  を与えるように、データ信号を決定することで、有機EL素子3における適切な階調制御を行うことができる。

**【0006】**

ここで、有機EL表示装置は、マトリクス状の多数の画素を配列した表示パネルで構成される。このため、製造上の問題で画素ごとに  $V_{th}$  がばらつき、1枚の表示パネル上でも最適な黒レベルが画素ごとにばらつくことがある。その結果、データ信号(入力電圧)に対する発光量が画素ごとに不均一となり、輝度ムラが発生する。

**【0007】**

そこで、各画素の輝度を測定し、メモリに記憶した補正データに従ってすべての画素について黒レベル電圧を補正することも提案されている(特許文献1)。

**【0008】**

**【特許文献1】特開平11-282420号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0009】**

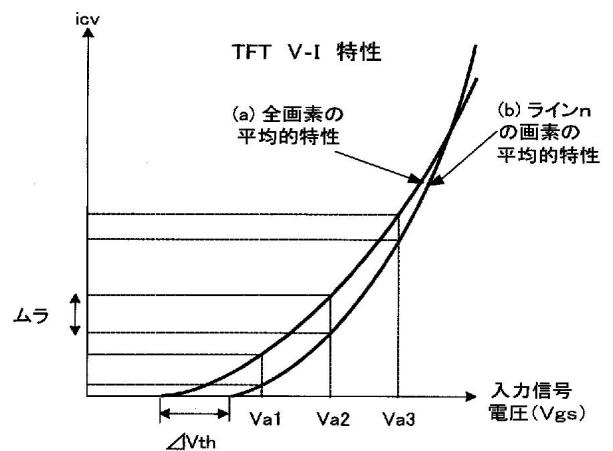

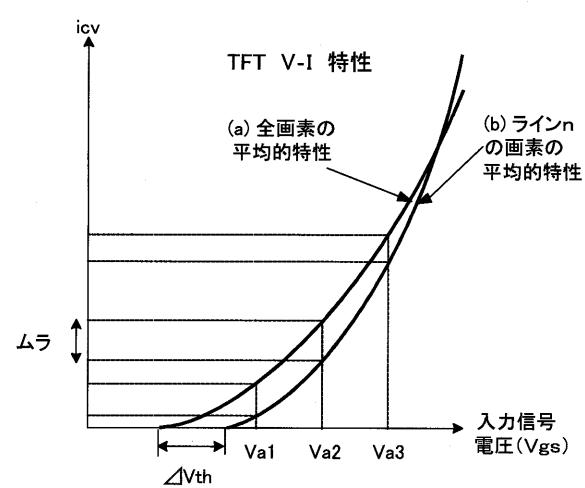

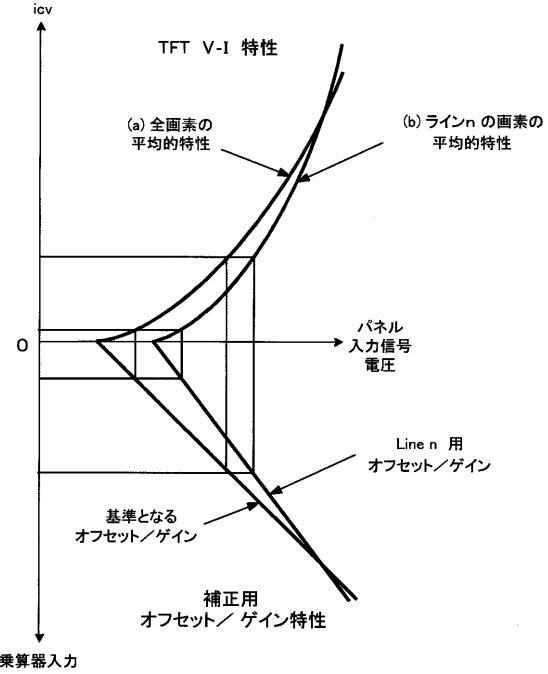

しかし、図3に示すように、画素駆動用TFTの  $V_{th}$  のバラツキ ( $V_{th}$ ) だけでなく、 $V$ - $I$  特性の傾き ( $gm$ ) がばらついている場合もある。すなわち、全画素の平均的特性 (a) に対し、ラインnの画素の平均的特性 (b) は、 $V_{th}$  が  $V_{th}$  だけ異なるだけでなく、入力電圧に対する駆動電流  $i_{cv}$  の傾きが異なっており、入力電圧  $V_{a1}$  、 $V_{a2}$  、 $V_{a3}$  における特性 (a) と特性 (b) の差が均一でない。このような場合には  $V_{th}$  の補正だけでは十分な補正ができない。

**【0010】**

本発明は、輝度データに対する駆動トランジスタの電流特性についての補償を行うことを目的とする。

**【課題を解決するための手段】**

**【0011】**

本発明は、有機EL素子および輝度データに応じた駆動電流を前記有機EL素子に供給する駆動トランジスタを各表示画素に含み、この表示画素をマトリクス配置する有機EL表示装置において、表示画素の位置と、その表示画素における駆動トランジスタの輝度データに対する駆動電流の傾きを補正する補正用ゲインを記憶する補正用ゲイン記憶部と、表示画素の位置と、その表示画素における駆動トランジスタの輝度データに対するオフセットを補正するための補正用オフセットを所定の複数の表示画素からなるエリア毎に記憶する補正用オフセット記憶部と、画素毎の輝度データを画素位置に応じて、前記補正用ゲイン記憶部に記憶されている補正用ゲインおよび前記補正用オフセット記憶部に記憶されている補正用オフセットを得て、これを用いて該当画素の輝度データに補正して補正輝度データを生成する補正部と、表示画素がマトリクス配置された表示エリア内の全部の表示画素について、互いに異なる2以上の輝度データに基づいて発光させる全体発光制御手段と、前記エリア内の複数の表示画素の有機EL素子について、異なる2以上の輝度データに基づいて選択的に発光させる選択発光制御手段と、全体および選択発光させた際の駆動電流をそれぞれ検出する電流検出手段と、検出した駆動電流に基づき選択された表示画素における輝度データに対する駆動電流を選択された画素の数で割った平均電流の傾きについて、全体の表示画素における輝度データに対する駆動電流を全画素数で割った平均電流の傾きとの関係を算出する傾き特性算出手段とを有し、前記傾き特性算出手段において算

10

20

40

50

出された傾き特性に対応する補正用ゲインを前記補正用ゲイン記憶部に記憶させるとともに、前記補正部において生成された補正輝度データに基づいて、前記駆動トランジスタを駆動して対応する有機EL素子に駆動電流を供給して各表示画素の表示を行うことを特徴とする。

**【発明の効果】**

**【0018】**

本発明によれば、画素駆動用TFTのV-I特性の傾き( $g_m$ )がばらついている場合に、これを補償してムラのない適切な発光を維持することができる。

**【発明を実施するための最良の形態】**

10

**【0019】**

以下、本発明の実施形態について、図面に基づいて説明する。

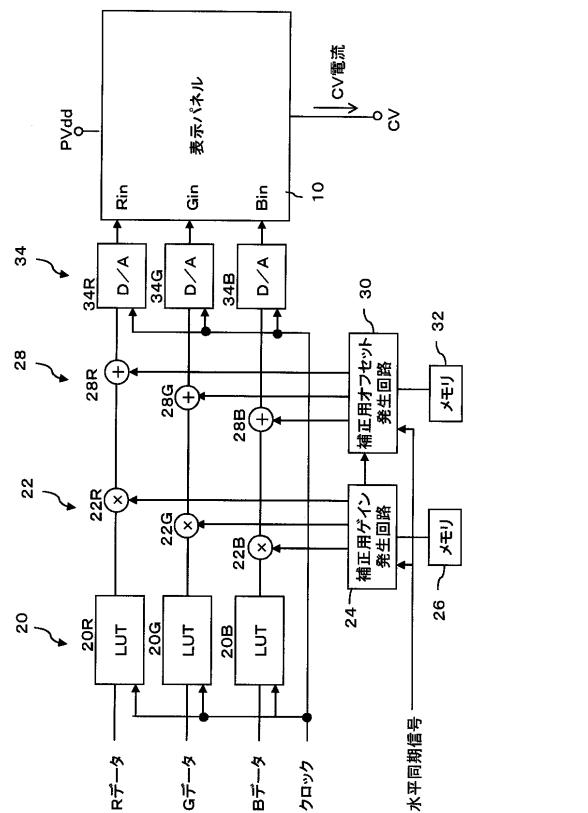

**【0020】**

図4には、本発明の有機EL表示装置における、輝度データから表示パネルに供給される補正された輝度データ(アナログ信号)を作成するための構成を示してある。

**【0021】**

表示パネル10は、RGBの各色ごとの画素を有しており、表示用の輝度データは、RGBの各色ごとに別に入力されてくる。例えば、画素は垂直方向に同一色のものを配置することで、各データラインにはRGBのいずれかのデータが供給され、各色ごとの表示が行える。なお、この例において、RGBの各データは、それぞれ8ビットの輝度データである。

20

**【0022】**

RデータはルックアップテーブルLUT20R、GデータはルックアップテーブルLUT20G、BデータはルックアップテーブルLUT20Bに供給される。このルックアップテーブルLUT20(20R、20G、20B)には、輝度データに対する発光輝度(駆動電流)の関係が所望のカーブとなるようにガンマ補正するとともに、表示パネル10において、平均的なオフセット、ゲインを考慮したテーブルデータが記憶されている。すなわち、図3における特性(a)を補償するデータが記憶されている。従って、このルックアップテーブルLUT20を利用して輝度データを変換することで、平均的な特性の駆動TFTを駆動した場合において、有機EL素子の発光量が輝度データに対応したものとなる。

30

**【0023】**

なお、ルックアップテーブルLUT20に代えて、特性式を記憶しておき、演算によって輝度データを変換してもよい。なお、この例では、ルックアップテーブルLUT20R、20G、20Bの出力は、それぞれ10ビットのビット幅に広げられている。また、ルックアップテーブルLUT20R、20G、20Bには、画素毎の入力データに同期したクロックが供給されており、ルックアップテーブルLUT20R、20G、20Bからの出力も、このクロックに同期したものになっている。

**【0024】**

ルックアップテーブルLUT20R、20G、20Bの出力は、乗算器22R、22G、22Bに供給される。この乗算器22R、22G、22Bには、補正用ゲイン発生回路24からの乗算補正值がそれぞれ供給されている。また、補正用ゲイン発生回路24には、メモリ26が接続されており、補正用ゲイン発生回路24は、入力されてくる輝度データがどの水平ラインに対応するかを入力されてくる水平同期信号から判定し、その水平ラインについての乗算補正值をメモリ26から読み出し、乗算補正值を発生する。

40

**【0025】**

乗算器22R、22G、22Bの出力は、加算器28R、28G、28Bにそれぞれ供給される。この加算器28R、28G、28Bには、補正用オフセット発生回路30からのオフセット補正值がそれぞれ供給されている。また、補正用オフセット発生回路30には、メモリ32が接続されており、補正用オフセット発生回路30は、該当水平ラインに

50

についてのオフセット補正值をメモリ 32 から読み出し、オフセット補正值を発生する。

【0026】

加算器 28R、28G、28B の出力は、D/A 変換器 34R、34G、34B に供給され、ここでアナログ信号に変換され、表示パネル 10 の各色ごとの入力端子 R<sub>in</sub>、G<sub>in</sub>、B<sub>in</sub> に供給される。そこで、これら各色ごとに画素位置に応じて補正されたデータ信号がデータラインに供給され、各画素において、EL 素子がデータ信号に応じた電流で駆動される。

【0027】

このように、本実施形態によれば、ルックアップテーブル LUT 20 によって、平均的な駆動 TFT を対象としたオフセット、V-I 特性の補償と、ガンマ補正を行う。そして、補正用ゲイン発生回路 24、補正用オフセット発生回路 30 が、メモリ 26、32 を利用して、各画素の位置における補正用ゲイン、補正用オフセットを出力する。従って、各画素における駆動トランジスタ（駆動 TFT）のしきい値電圧 V<sub>th</sub> のバラツキ V<sub>th</sub> を補償するだけでなく、ゲートソース間電圧 V<sub>gs</sub> に対するドレイン電流（有機 EL の駆動電流）の V-I 特性を補償して、輝度データに応じた適切な駆動電流を有機 EL 素子に供給することができる。

【0028】

本実施形態では、この補正用ゲイン発生回路 24、補正用オフセット発生回路 30 は、ライン毎に一定の補正值を発生しているが、これに限定されることなく、表示パネル 10 を面と考え、各画素についての補正值を規定する式を記憶するようにしてもよい。すなわち、補正值 = a<sub>x</sub> + b<sub>y</sub> + c（または係数 a, b, c）を記憶する。そして、画素に同期したクロックに応じて、データ信号の画素位置 x、y を認識し、これに対応した補正值を発生する。

【0029】

また、補正值は、この例のように、RGB ごとに別に発生できるようにしてもよいし、RGB について共通にしてもよい。

【0030】

なお、本実施形態では、補正用ゲイン発生回路 24、補正用オフセット発生回路 30 からの出力補正值は 10 ビットであり、乗算器 22R、22G、22B、加算器 28R、28G、28B ビット幅は 10 ビットになっている。

【0031】

「補正用ゲインおよび補正用オフセット」

上述のように、本実施形態では、補正用ゲインがメモリ 26、補正用オフセットがメモリ 32 に記憶されている。そこで、これらの補正用ゲイン、および補正用オフセットについて、以下に説明する。

【0032】

一例として、水平ライン毎のムラが発生している場合を考える。駆動 TFT の V<sub>th</sub> と g<sub>m</sub> がラインによって違っているパネルの全画素に、ある入力電圧 V<sub>a2</sub> を印加すると、CV 電流はライン毎にばらつき、筋状のムラが発生する。このような、製造上の問題により有機 EL 表示パネルに発生する輝度不均一性を、補正用ゲインおよび補正用オフセットで補償する。

【0033】

これらの補正用ゲインおよび補正用オフセットの発生および補正は、次のようにして行う。

【0034】

i) 表示パネル 10 の全画素を 2 つ以上の入力電圧（この例では、図 3 における 3 点 V<sub>a1</sub>、V<sub>a2</sub>、V<sub>a3</sub>）で点灯し、各入力電圧における CV 電流を測定する。表示パネル 10 に流れる全電流を測定できれば、P<sub>Vdd</sub> 側で測定しても CV 側で測定してもよい。

【0035】

各画素の平均電流（i<sub>cV</sub>）はこの CV 電流を全画素数で割った値となるので、入力電

10

20

30

40

50

圧対  $i_c v$  の関係をプロットする。この結果により、このパネルの平均的な TFT の V - I 特性を予想し、プロットする（図 3 の（a））。

【0036】

i i ) パネルの中の任意の一水平ライン（ライン n）のみを 2 つ以上の入力電圧（この例では 3 点  $V_{a1}$ ,  $V_{a2}$ ,  $V_{a3}$ ）で点灯し、各入力電圧における CV 電流を測定する。このラインの各画素の平均電流（ $i_c v$ ）はこの CV 電流を 1 ラインの画素数で割った値となるので、このラインの一画素の TFT の V - I 特性を予想し、プロットする（図 3 の（b））。同様にして、全てのラインの TFT の V - I 特性を予想し、プロットする。これら各ラインの V - I 特性も上述の全画素の V - I 特性と同様に、近似式などを決定することができる。

10

【0037】

i i i ) 図 3 により、平均的特性に対するライン n の  $V_{th}$  及び  $gm$  のずれを求める。CV 電流または輝度の差が最小となるように補正ゲインと補正オフセットを求める。すなわち、図 5 に示すように、図 3 の特性を補償する補正ゲインを求める。この例では、補正オフセット / ゲイン特性を、直線で近似している。従って、補正用オフセットは、基準となるオフセット / ゲインの  $i_c v = 0$  のパネル入力信号電圧と、特定のラインのオフセット / ゲインの  $i_c v = 0$  のパネル入力信号電圧との差となる。また、補正用ゲインは、基準となるオフセット / ゲインの傾きで、特定のラインのオフセット / ゲインの傾きを除算した値となる。

【0038】

20

i v ) このようにして得られた補正用ゲイン及び補正用オフセットの値をメモリ 26、32 に記憶させる。これによって、入力されてくる輝度データ（R データ、G データ、B データ）に対し、乗算器 22（22R、22G、22B）において、補正用ゲインが乗算され、加算器 28（28R、28G、28B）において補正用オフセットが加算され、輝度データが補正される。従って、各輝度データが駆動する TFT の特性（オフセット、V - I 特性）に応じて適切に補正され、これが D / A 変換されて表示パネル 10 に供給される。従って、輝度データに応じた電流が対応する有機 EL 素子に供給され、輝度データに応じた発光が確保される。

【0039】

30

このようにして、製造上の問題により駆動 TFT の特性が変化し、有機 EL 表示素子に発生する輝度不均一性を、簡単な測定と、比較的簡単な外部回路により補正することができる。

【0040】

ここで、表示パネル 10 は、通常ガラス基板上に形成され、表示エリアには画素回路がマトリクス状に配置され、その周辺に駆動回路が配置される。画素回路は、例えばガラス基板上に TFT や配線などを通常の半導体集積回路を構成する手法で構成し、その後 ITO などの画素電極を形成し、その上に有機層、陰極を積層形成することで製作する。

【0041】

このようにして、表示パネルが製作された場合には、電源を接続するとともに有機 EL 素子に流れるトータルの電流  $I_c v$  を計測する。すなわち、表示パネル 10 の各電源ライン  $PVdd$  に電源電圧  $PVdd$  を供給し、全有機 EL 素子に共通のカソードから電源 CV に流れる合計電流  $I_c v$  を電流検出器によって検出し、得られた検出結果により、上述のようにして、補正值を作成する。

40

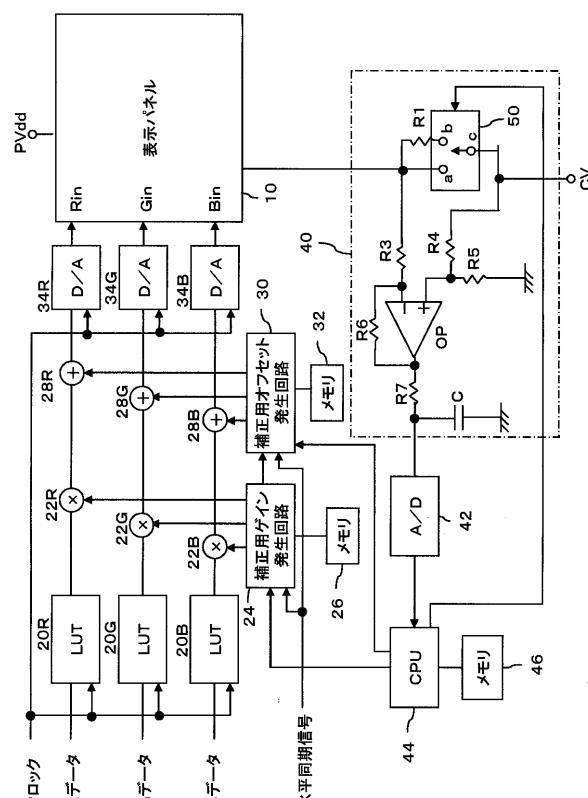

【0042】

図 6 には、上述のような補正を行う回路を製品自体に組み込んだ構成例を示してある。この構成において、表示パネル 10 は、図 4 と同様に、正側が電源  $PVdd$  に接続され、負側が低電圧電源 CV に接続され、表示パネル 10 と低電圧電源 CV との間に電流検出器 40 が配置されている。

【0043】

そして、電流検出器 40 の検出値は、A / D 変換器 42 によりデジタルデータに変換さ

50

れた後、C P U 4 4 に供給される。このC P U 4 4 は、有機E L表示装置の各種動作を制御するマイコンであり、必要なデータを適宜記憶するメモリ4 6 が接続され、上述の実施形態において説明した電流検出器4 0 の検出値に応じたオフセット制御のための処理も行う。

#### 【0 0 4 4】

次に、図における電流検出器4 0 の構成について説明する。表示パネル1 0 の負側は、スイッチ5 0 に入力される。このスイッチ5 0 は、1 つの出力側端子c が低電圧電源C V に接続されており、他の2 つの入力側端子a , b の内の1 つが選択的に電源C V に接続される。このスイッチ5 0 の切り替えはC P U 4 4 によって制御される。表示パネル1 0 の負側は、2 つの入力端子a , b に接続されるが、a はそのまま、b は抵抗R 1 を介し、スイッチ5 0 の入力端子に接続されている。10

#### 【0 0 4 5】

そして、C P U 4 4 は、通常時は入力端子a 、補正のための処理を行う場合は入力端子b を選択する。これによって、通常時には、電流検出器4 0 における電圧降下をほぼ0 とすることができる。また、入力端子b が選択された際には、C V 電流に応じた電圧降下が抵抗R 1 において生じ、R 1 の上側の電圧がC V 電流に応じたものになる。

#### 【0 0 4 6】

抵抗R 1 の上側（表示パネル1 0 との接続側）は、抵抗R 3 を介しオペアンプO P の負入力端に接続されている。また、このオペアンプO P の正入力端は、抵抗R 4 を介し低電圧電源C V に接続されると共に、抵抗R 5 を介しグランドに接続されている。従って、オペアンプO P の正入力端子は、グランドと、C V 電圧および抵抗R 4 、R 5 によって決定される電圧に維持される。また、オペアンプO P の負入力端子、出力端子間は、帰還抵抗R 6 によって接続されている。このため、オペアンプO P は、正入力端の電圧を基準として、抵抗R 1 の上側電圧を抵抗R 3 、R 6 によって決定される増幅率で増幅した出力をする。20

#### 【0 0 4 7】

オペアンプO P の出力端は抵抗R 7 の一端に接続され、この抵抗R 7 の他端はA / D 変換器4 2 に接続されるとともに、コンデンサC を介しグランドに接続されている。従って、オペアンプO P の出力は、抵抗R 7 およびコンデンサC よりなる積分回路によって、平滑化され、平滑された電圧がA / D 変換器4 2 に入力される。30

#### 【0 0 4 8】

このようにして、本実施形態では、スイッチ5 0 を操作して、入力端子b を選択することで、表示パネル1 0 における電流値がC P U 4 4 に取り込まれる。

#### 【0 0 4 9】

C P U 4 4 は、適宜のタイミングでスイッチ5 0 を操作して、表示パネル1 0 に流れる電流量を検出する。例えば、電源投入時や、製品の使用開始時、リセット時などに、C P U 4 4 は電流検出動作を行う。すなわち、スイッチ5 0 により入力端子b を選択し、この状態で全体についての2 回以上の発光を行い、次にライン毎の2 回以上の発光を順次行い、表示パネル1 0 全体における平均的な画素毎の電流量と、各ラインの平均的な画素毎の電流量を検出する。この際、パネル全体を発光させる時と、1 ラインを発光させる時とで電流検出用抵抗値を変更し、より精度の高い測定を行うことが好適である。そして、検出した電流量に応じて、ライン毎の補正用ゲインおよび補正用オフセットを算出し、これをメモリ2 6 、3 2 に記憶させる。40

#### 【0 0 5 0】

なお、補正值は上述のようなライン毎のゲイン、オフセットの補正值のみでなく、上述のような表示パネル1 0 の全体的な傾向についての補正式でもよい。このような補正式は、表示エリア内の所定の小エリア（表示エリアを複数に分割したエリアであって、その一部でもよい）におけるC V 電流を検出し、検出電流に基づき表示エリア全体の補正值を規定する面の式を計算ことで得られる。このような補正式またはその係数をメモリ2 6 、3 2 に記憶させることでも、上述の実施形態と同様に、適切な補正を行うことができる。な50

お、通常使用時には、上述のように、スイッチ 50 において、入力端子 a を選択しておくことで、何ら問題は生じない。

#### 【0051】

このように、図 6 の実施形態によれば、補正用ゲイン、補正用オフセット量検出のための構成が製品中に設けられている。そこで、製品の実際の使用時において、補正值算出式や補正值などを適宜決定し、記憶することができる。このような設定を適宜行うことで使用状況の変化や、経年的な変化に対応することも可能である。

#### 【0052】

##### 「その他」

i ) 全画素の平均的 V - I 特性を求める代わりに、代表的な TFT の V - I 特性を求めて用いることもできる。すなわち、あるエリアまたはラインなどを点灯し、CV 電流を点灯した画素数で割り基準となる V - I 特性を求める。 10

ii ) 上記実施形態では乗算器を用いたが、乗算器の変わりにルックアップテーブルを用いてもよい。

すなわち、乗算器による演算（リニア演算）だけでは補正が不十分な場合は、非直線な入出力特性をもったルックアップテーブルを多数用意し、ライン毎に最適なルックアップテーブルを選択することもできる。この場合メモリには、ラインに対応させた、選択すべきルックアップテーブルの番号などを格納しておく。

iii ) 図 4 の乗算器 22 、加算器 28 等は、LUT の前に置いても良いし、D/A 変換器 34 の出力の後でアナログ的に処理することも可能である。 20

iv ) CV 電流を測定して輝度不均一性を予測するかわりに実際に輝度を測定しても良い。

v ) パネル出荷時に、補正のためのゲインとオフセットを、有機 EL パネルのガラス基板上またはパネルから引き出されているフレキシブルケーブル上におかれた不揮発性メモリに予め書き込んでおくとよい。これによって、表示パネル 10 に輝度信号を供給する装置側の回路は、このデータを基に入力信号（輝度データ）の補正を行うことができる。こうすることにより、装置側は表示パネル 10 が変更されたときも、パネルモジュールの不揮発性メモリからデータを読み取り、輝度データの補正を行うことが可能になる。

vi ) 不揮発性メモリには、ガンマデータ、輝点、滅点、明点、暗点の位置情報や、明るさなど、その他の表示パネル 10 に特有なデータを書き込んでおくこともできる。これによって、装置側において、これらデータを利用して表示を制御することもできる。 30

vii ) 補正值について、画素位置と補正值の関係を示す式を記憶する場合において、平面の式を用いることが好適であるが、曲面の式を用いてもよい。例えば、x 、 y を変数とする高次の多項式とすることができる。

viii ) Vth に関しては、CV 電流が流れ始める点の入力電圧を Vth とみなして測定することもできる。さらに、CV 電流を測定して輝度不均一性を予測するかわりに実際に輝度を測定しても良い。

#### 【図面の簡単な説明】

#### 【0053】

【図 1】アクティブ型の有機 EL 表示装置における画素回路の構成例を示す図である。 40

【図 2】駆動 TFT のゲートソース間電圧 Vgs に対する輝度及び有機 EL 素子に流れる電流  $i_{cv}$  の関係を示す図である。

【図 3】全体および 1 ラインの平均的な駆動 TFT のゲートソース間電圧 Vgs に対する輝度及び有機 EL 素子に流れる電流  $i_{cv}$  の関係を示す図である。

【図 4】補正用ゲイン、補正用オフセットによる補正を行う EL 表示装置の構成を示すブロック図である。

【図 5】駆動 TFT のゲートソース間電圧 Vgs に対する有機 EL 素子に流れる電流  $i_{cv}$  の補正を示す図である。

【図 6】補正算出式や補正值などを算出するための構成を含む EL 表示装置の構成を示すブロック図である。 50

## 【符号の説明】

## 【0054】

10 表示パネル、20 (20R, 20G, 20B) ルックアップテーブル LUT、

22 (22R, 22G, 22B) 乗算器、24 補正用ゲイン発生回路、26, 32

メモリ、28 (28R, 28G, 28B) 加算器、30 補正用オフセット発生回路、

34 (34R, 34G, 34B) D/A 変換器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| G 09 G | 3/20  | 6 4 1 P |

| G 09 G | 3/20  | 6 4 2 A |

| H 05 B | 33/14 | A       |

(74)代理人 100110423

弁理士 曾我 道治

(74)代理人 100084010

弁理士 古川 秀利

(74)代理人 100094695

弁理士 鈴木 憲七

(74)代理人 100111648

弁理士 梶並 順

(74)代理人 100122437

弁理士 大宅 一宏

(74)代理人 100147566

弁理士 上田 俊一

(72)発明者 水越 誠一

東京都中央区日本橋小綱町6番1号 コダック株式会社内

(72)発明者 森 信幸

東京都中央区日本橋小綱町6番1号 コダック株式会社内

(72)発明者 小野村 高一

東京都中央区日本橋小綱町6番1号 コダック株式会社内

(72)発明者 河野 誠

東京都中央区日本橋小綱町6番1号 コダック株式会社内

審査官 福村 拓

(56)参考文献 特開平11-219146 (JP, A)

特開2003-195813 (JP, A)

特開2003-150099 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 3 0

G 09 G 3 / 2 0

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP4855648B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2012-01-18 |

| 申请号            | JP2004101143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2004-03-30 |

| [标]申请(专利权)人(译) | 伊斯曼柯达公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 伊士曼柯达公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 全球豪迪E.科技有限责任公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 水越誠一<br>森信幸<br>小野村高一<br>河野誠                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 水越 誠一<br>森 信幸<br>小野村 高一<br>河野 誠                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50 G09G3/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0842 G09G2320/0285 G09G2320/029 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G09G3/30.H G09G3/30.K G09G3/20.611.H G09G3/20.631.V G09G3/20.641.D G09G3/20.641.P G09G3/20.642.A H05B33/14.A G09G3/20.642.P G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH00 3K107/HH04 5C080/AA06 5C080/BB05 5C080/DD05 5C080/EE28 5C080/FF11 5C080/GG12 5C080/JJ02 5C080/JJ03 5C080/JJ05 5C380/AA01 5C380/AB06 5C380/AB34 5C380/BA22 5C380/BA38 5C380/BA39 5C380/BB03 5C380/BB13 5C380/CA08 5C380/CA12 5C380/CB01 5C380/CC02 5C380/CC26 5C380/CC33 5C380/CC62 5C380/CD012 5C380/CF01 5C380/CF05 5C380/CF13 5C380/CF18 5C380/CF19 5C380/CF20 5C380/CF27 5C380/CF41 5C380/CF43 5C380/CF48 5C380/CF49 5C380/CF62 5C380/DA06 5C380/DA32 5C380/DA39 5C380/EA02 5C380/EA05 5C380/FA03 5C380/FA22 5C380/FA28 |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序<br>上田俊一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 审查员(译)         | 福村 拓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 其他公开文献         | JP2005284172A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

**摘要(译)**

要解决的问题：补偿驱动晶体管相对于亮度数据的电流特性。ŽSOLUTION：在用于补偿产生电路24的增益和用于补偿产生电路30的偏移中，产生对应于驱动TFT的VI特性的增益的补偿值到像素位置（例如，每个水平线）和对应于阈值的偏移。水平。然后，补偿图像数据，并且通过将用于补偿的增益乘以乘法器22并根据输入图像数据的像素位置添加用于补偿的补偿来防止屏幕上显示的变化的产生。Ž

【図3】