(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-130466

(P2017-130466A)

(43) 公開日 平成29年7月27日(2017.7.27)

| (51) Int.CI.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H05B 33/02</b> (2006.01) | H05B 33/02 | 3K107       |

| <b>H01L 27/32</b> (2006.01) | H01L 27/32 | 5C094       |

| <b>H01L 51/50</b> (2006.01) | H05B 33/14 | A           |

| <b>H05B 33/14</b> (2006.01) | H05B 33/14 | Z           |

| <b>G09F 9/30</b> (2006.01)  | G09F 9/30  | 365         |

審査請求 有 請求項の数 5 O L (全 57 頁) 最終頁に続く

|              |                            |            |                                                                                                                                                              |

|--------------|----------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2017-79533 (P2017-79533) | (71) 出願人   | 000153878                                                                                                                                                    |

| (22) 出願日     | 平成29年4月13日 (2017.4.13)     |            | 株式会社半導体エネルギー研究所                                                                                                                                              |

| (62) 分割の表示   | 特願2016-95817 (P2016-95817) |            | 神奈川県厚木市長谷398番地                                                                                                                                               |

| 原出願日         | 平成18年1月24日 (2006.1.24)     | (72) 発明者   | 木村 肇                                                                                                                                                         |

| (31) 優先権主張番号 | 特願2005-24631 (P2005-24631) |            | 神奈川県厚木市長谷398番地 株式会社                                                                                                                                          |

| (32) 優先日     | 平成17年1月31日 (2005.1.31)     |            | 半導体エネルギー研究所内                                                                                                                                                 |

| (33) 優先権主張国  | 日本国 (JP)                   | F ターム (参考) | 3K107 AA01 AA05 BB01 CC14 CC29<br>CC33 CC45 DD39 EE03 FF15<br>GG57<br>5C094 AA25 AA43 BA03 BA27 CA19<br>DA13 DB04 EA07 FB12 FB14<br>HA05 HA06 HA07 HA08 JA08 |

(54) 【発明の名称】表示装置、電子機器、及び携帯情報端末

## (57) 【要約】

【課題】E-Lの膜厚が薄いことにより陽極-陰極間がショートしたり、トランジスタ不良が起きたりする。

【解決手段】電極及び電界発光層を有する発光素子と、前記発光素子の電極に電気的に接続された配線と、ソース、ドレイン、及びチャネル形成領域を含む活性層を有するトランジスタと、前記トランジスタのソースまたはドレインの一方に電気的に接続された電源線とを有し、前記配線は、前記トランジスタのソースまたはドレインの他方に電気的に接続され、前記電極と前記配線とが電気的に接続される領域の近傍に、前記電極と前記配線とが電気的に接続される領域に比較して前記電極の幅が細い領域を有することを特徴とする。

【選択図】図5

## 【特許請求の範囲】

## 【請求項 1】

電極及び電界発光層を有する発光素子と、

前記発光素子の電極に電気的に接続された配線と、

ソース、ドレイン、及びチャネル形成領域を含む活性層を有するトランジスタと、

前記トランジスタのソースまたはドレインの一方に電気的に接続された電源線とを有し

、

前記配線は、前記トランジスタのソースまたはドレインの他方に電気的に接続され、

前記電極と前記配線とが電気的に接続される領域の近傍に、前記電極と前記配線とが電気的に接続される領域に比較して前記電極の幅が細い領域を有することを特徴とする表示装置。

10

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、自発光素子を有する表示装置における欠陥画素の修正方法に関する。特に、EL (Electro Luminescence) 素子を有するアクティブマトリクス型の表示装置における欠陥画素の修正方法に関する。また、欠陥画素が形成された場合に簡便に修正対応することができる構造を有する表示装置に関する。

## 【背景技術】

## 【0002】

近年、EL素子を代表とする発光素子を含む発光装置の開発が進められ、自発光型ゆえの高画質、広視野角、薄型、軽量等の利点を活かして、幅広い利用が期待されている。このような自発光型の表示装置に用いられる発光素子としては、有機発光ダイオード（「OLED (Organic Light Emitting Diode)」、「有機EL素子」などとも言う）、エレクトロルミネッセンス（Electro Luminescence : EL）素子などが注目を集めしており、ELディスプレイなどに用いられるようになってきている。OLEDなどの発光素子は自発光型であるため、液晶ディスプレイに比べて画素の視認性が高く、バックライトが不要で応答速度が速い等の利点がある。また、発光素子の輝度は、当該発光素子を流れる電流値によって制御される。

20

## 【0003】

EL素子は、陰極と陽極との間に電界発光層（有機化合物を含む層）を有している。電界発光層（有機化合物を含む層）は、単数の層（発光層のみ）で構成しても良いし、複数の層を積層させて構成しても良い。複数の層で構成する場合、半導体素子側（画素電極側）から見て、（1）陽極、ホール（正孔）注入層、ホール輸送層、発光層、電子輸送層、陰極、（2）陽極、ホール注入層、発光層、電子輸送層、陰極、（3）陽極、ホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層、陰極、（4）陽極、ホール注入層、ホール輸送層、発光層、ホールブロッキング層、電子輸送層、陰極、（5）陽極、ホール注入層、ホール輸送層、発光層、ホールブロッキング層、電子輸送層、電子注入層、陰極、等の素子構造とすればよい。これは、所謂順積みと呼ばれる構造で、画素電極は、陽極として機能する。一方、半導体素子側（画素電極側）から見て、陰極が先に来る場合には、逆積みと呼ばれ、画素電極は陰極として機能する。

30

## 【0004】

また、電界発光層に求められる性質としては、発光すること、電流を流すことの2点が挙げられる。電流は、膜厚の3乗に反比例して流れなくなる特性を示すため、電界発光層の膜厚は非常に薄いことが要求される（例えば、特許文献1参照）。

## 【先行技術文献】

## 【特許文献】

## 【0005】

## 【特許文献1】国際公開第04/043937号パンフレット

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

しかしながら、電界発光層の膜厚を極端に薄くすると、以下の問題が発生する。すなわち、電界発光層の膜厚が薄いことにより、陽極-陰極間が非常にショートしやすくなる(以下、本明細書において、「両極間ショート」と呼ぶ。)。また、その他に、電極の多層の凹凸が原因の場合もあるし、小さなゴミが原因の場合もある。また、EL素子に接続されたトランジスタの動作不良により、本来EL素子に電荷を供給しない期間においてもEL素子に電荷を供給してしまいEL素子が発光してしまうことがある。また、その逆に、EL素子に接続されたトランジスタの動作不良により、EL素子に電荷を供給することができず、常にEL素子が発光しなくなってしまうこともある。このように、EL素子の電界発光層に過剰の電流が流れてしまったり、本来光るべきではないところでEL素子が光ってしまうことがあり、表示装置の品位を著しく損なっている。なお、本明細書においては、発光素子が設けられている複数の画素のうち、発光素子の両極間ショート、配線間のショート、発光素子の電極と配線間のショート、または発光素子に接続されたトランジスタの動作不良により、常に発光または非発光の状態となっていたり、発光素子を正常に制御することができないような状態の画素を欠陥画素と呼ぶ。

## 【0007】

また、欠陥画素があると、ショートにより電圧降下して各画素に電位を与えるべく接続されている電源線から他の画素に十分な電位を与えることが困難になることがある。すなわち、常時発光素子があると、その画素だけでなく他の画素の発光素子にも影響を及ぼすことになる。

## 【0008】

ここで、昨今表示装置の市場を賑わしている液晶表示装置の場合について考える。液晶表示装置の場合、液晶素子は、キャパシタとして動作し、電圧を加えると、その電圧をそのまま保持し、加えられた電圧によって生じる電界によって、液晶分子が制御される。つまり、液晶素子に電流が流れ続けることはない。したがって、仮に、ある画素の画素電極が別の配線とショートしたとしても、電流が流れ続けるわけではないので、別の画素に影響を与えることはない。

## 【0009】

また、液晶素子の場合、電流が流れ続けるわけではないので、消費電力が大きくなってしまうこともない。また、通常、1画素に1つのトランジスタが配置されているだけであるため、修復の対象は、1つのトランジスタと1つの画素電極のみを考えればよい。

## 【0010】

一方、EL素子は、電流駆動型のデバイスであり、発光している間、電源線から電流が流れ続ける。このような性質を有するEL素子が設けられた画素に欠陥が生じると、他の正常な画素にまで悪影響を与えたり、消費電力が多くなってしまったりする。また、画素には最低2つのトランジスタが配置されており、信号を保持する部分や電流量を制御する部分など複雑な回路構成をしているため、どの部分をどのようにすればよいかは自明ではない。

## 【0011】

このような問題は、電源線を必要としたり、電流が流れ続けたりするという、エレクトロルミネッセンス表示装置に特有の問題であって、液晶表示装置にはない問題である。

## 【0012】

本発明は、発光素子の両極間ショート、配線間のショート、発光素子の電極と配線間のショート、または発光素子に接続されたトランジスタの動作不良などにより、欠陥画素、特に常時発光していたり、正常に制御することができず発光素子が発光してしまうような状態の画素における欠陥を修正し、画像の品位が損なわれることのない表示装置を提供することを目的とする。また、欠陥画素が形成された場合に容易に修正することができる構造を有する表示装置を提供することを目的とする。

## 【課題を解決するための手段】

10

20

30

40

50

## 【0013】

欠陥画素、特に常時発光していたり、正常に制御することができず発光素子が発光してしまうような状態の画素において、前記発光素子の一方の電極に、電位が常に与えられないうようにする。例えば、発光素子の一方の電極をフローティング状態となるようにする。

## 【0014】

本明細書で開示する発明の構成は、発光素子の一方の電極に電位を与える配線（電源線）と前記発光素子の一方の電極との間ににおいて、少なくとも1箇所配線をカット（切断）することを特徴とする。つまり、物理的に配線の接続を切断し、電流が流れなくなるようにする。

## 【0015】

また、上記発明の構成において、レーザー光を照射することにより、配線をカットすることを特徴とする。その結果、電源線から発光素子を通って電流が流れる経路を遮断することができるため、発光素子が発光すること（輝点の発生）を防止することができる。

## 【0016】

また、本明細書で開示する別の発明の構成は、発光素子と、当該発光素子に電位を与える電源線との間ににおいて、前記発光素子に接続されたトランジスタが常時オフになるようになる。例えば、ノーマリーオフのトランジスタ（エンハンスマント型のトランジスタ）において、ゲートとソースが同電位になるようにする。つまり、電気的に配線の接続を切断し、表示期間中にはEL素子に電流が流れなくなるようにする。

## 【0017】

また、本明細書で開示する別の発明の構成は、発光素子と、当該発光素子に電位を与える電源線との間に設けられた配線において、前記配線の一部の幅が狭くなっていることを特徴とする。なお、本明細書において、「配線の幅」と単に記載するとき、当該配線を流れる電流の向きに対して垂直の方向をさすものとする。また、本明細書において「電源線の幅」または「電極の幅」と記載するときも同様に、電源線（または電極）を流れる電流の向きに対して垂直の方向をさすものとする。

## 【0018】

また、上記発明の構成において、前記狭くなっている配線の一部の幅は、3 μm以下であることを特徴とする。

## 【0019】

また、本明細書で開示する別の発明の構成は、

電極及び電界発光層を有する発光素子が設けられた画素を複数有し、前記複数の画素のうち少なくとも一つ以上の画素が欠陥画素である表示装置の欠陥修正方法であって、

前記欠陥画素に設けられた発光素子の電極に接続された配線を切断することを特徴とする。

## 【0020】

また、本明細書で開示する別の発明の構成は、

電極及び電界発光層を有する発光素子と、トランジスタとが設けられた画素を複数有し、前記複数の画素のうち少なくとも一つ以上の画素が欠陥画素である表示装置の欠陥修正方法であって、

前記トランジスタのソースまたはドレインのいずれか一方と前記発光素子の電極とが配線を介して接続されており、

前記欠陥画素に設けられた発光素子の電極に接続された配線を切断することを特徴とする。

## 【0021】

また、本明細書で開示する別の発明の構成は、

電極及び電界発光層を有する発光素子と、トランジスタとが設けられた画素を複数有し、前記複数の画素のうち少なくとも一つ以上の画素が欠陥画素である表示装置の欠陥修正方法であって、

前記欠陥画素に設けられたトランジスタを常時オフにすることを特徴とする。

10

20

30

40

50

## 【0022】

また、本明細書で開示する別の発明の構成は、

電極及び電界発光層を有する発光素子と、Pチャネル型のトランジスタとが設けられた画素を複数有し、前記複数の画素のうち少なくとも一つ以上の画素が欠陥画素である表示装置の欠陥修正方法であって、

前記トランジスタにおいて、ソースまたはドレインのいずれか一方が電源線と接続され、他方が配線を介して前記発光素子の電極と接続され、ゲートが前記電源線よりも高い電位を有する配線と接続されていることを特徴とする。

## 【0023】

また、上記発明の構成において、前記欠陥画素に設けられた発光素子の電極に接続された配線をレーザー照射により切断することを特徴とする。また、上記発明の構成において、前記トランジスタにより発光素子を駆動することを特徴とする。

10

## 【0024】

また、本明細書で開示する別の発明の構成は、

電極及び電界発光層を有する発光素子と、

前記発光素子の電極に電気的に接続された配線と、

ソース、ドレイン、及びチャネル形成領域を含む活性層を有するトランジスタと、

前記トランジスタのソースまたはドレインの一方に電気的に接続された電源線とを有し、

20

前記配線は、前記トランジスタのソースまたはドレインの他方に電気的に接続され、

前記電極と前記配線とが電気的に接続される領域の近傍に、前記電極と前記配線とが電気的に接続される領域に比較して前記電極の幅が細い領域を有することを特徴とする。

## 【0025】

また、上記発明の構成において、前記電極の幅が細い領域の幅は  $3 \mu m$  以下であることを特徴とする。また、前記電極の幅が細い領域は、当該電極において最も幅が細いことを特徴とする。また、前記電極の幅が細い領域の幅は、それ以外の領域の幅に比較して半分以下であることを特徴とする。また、前記電極の幅が細い領域の幅は、信号線駆動回路及び走査線駆動回路に用いられている配線のうち、最も細い幅を有する配線の幅よりも細い狭いことを特徴とする。

30

## 【0026】

また、本明細書で開示する別の発明の構成は、

電極及び電界発光層を有する発光素子と、

前記発光素子の電極に電気的に接続された配線と、

ソース、ドレイン、及びチャネル形成領域を含む活性層を有するトランジスタと、

前記トランジスタのソースまたはドレインの一方に電気的に接続された電源線とを有し、

40

前記配線は、前記トランジスタのソースまたはドレインの他方に電気的に接続され、

前記電極と前記配線とが電気的に接続される領域と、前記配線と前記トランジスタのソースまたはドレインの他方とが電気的に接続される領域との間に、前記配線の幅が細い領域を有することを特徴とする。

## 【0027】

また、上記発明の構成において、前記配線の幅が細い領域の幅は  $3 \mu m$  以下であることを特徴とする。また、前記配線の幅が細い領域は、当該配線において最も幅が細いことを特徴とする。また、前記配線の幅が細い領域の幅は、それ以外の領域の幅に比較して半分以下であることを特徴とする。また、前記配線の幅が細い領域の幅は、信号線駆動回路及び走査線駆動回路に用いられている配線のうち、最も細い幅を有する配線の幅よりも細いことを特徴とする。

## 【0028】

また、本明細書で開示する別の発明の構成は、

電極及び電界発光層を有する発光素子と、

50

前記発光素子の電極に電気的に接続された配線と、

ソース、ドレイン、及びチャネル形成領域を含む活性層を有するトランジスタと、

前記トランジスタのソースまたはドレインの一方に電気的に接続された電源線と、

ゲート配線とを有し、

前記配線は、前記トランジスタのソースまたはドレインの他方に電気的に接続され、

前記活性層は、前記配線、前記ゲート配線、及び前記電源線とそれ一部重なっており、

前記活性層のうち、前記配線、前記ゲート配線、及び前記電源線に重ならない領域の幅が細いことを特徴とする。

【0029】

10

また、上記発明の構成において、前記活性層のうち、前記配線、前記ゲート配線、及び前記電源線に重ならない領域の幅は  $3 \mu m$  以下であることを特徴とする。また、前記活性層のうち、前記配線、前記ゲート配線、及び前記電源線に重ならない領域の幅は、それ以外の領域の幅に比較して半分以下であることを特徴とする。また、前記活性層のうち、前記配線、前記ゲート配線、及び前記電源線に重ならない領域の幅は、信号線駆動回路及び走査線駆動回路に用いられている配線のうち、最も細い幅を有する配線の幅よりも細いことを特徴とする。

【0030】

20

また、本明細書で開示する別の発明の構成は、

電極及び電界発光層を有する発光素子と、

前記発光素子の電極に電気的に接続された配線と、

ソース、ドレイン、及びチャネル形成領域を含む活性層を有するトランジスタと、

前記トランジスタのソースまたはドレインの一方に電気的に接続された電源線とを有し、

前記配線は、前記トランジスタのソースまたはドレインの他方に電気的に接続され、

前記トランジスタのソースまたはドレインの一方と前記電源線とが電気的に接続される領域の近傍に、前記トランジスタのソースまたはドレインの一方と前記電源線とが電気的に接続される領域に比較して前記電源線の幅が細い領域を有することを特徴とする。

【0031】

30

また、上記発明の構成において、前記電源線の幅が細い領域の幅は  $3 \mu m$  以下であることを特徴とする。また、前記電源線の幅が細い領域は、当該電源線において最も幅が細いことを特徴とする。また、前記電源線の幅が細い領域の幅は、それ以外の領域の幅に比較して半分以下であることを特徴とする。また、前記電源線の幅が細い領域の幅は、信号線駆動回路及び走査線駆動回路に用いられている配線のうち、最も細い幅を有する配線の幅よりも細い狭いことを特徴とする。

【0032】

また、上記発明の構成において、前記トランジスタの活性層は、非晶質半導体膜または結晶性半導体膜であることを特徴とする。また、前記トランジスタはトップゲート型またはボトムゲート型であることを特徴とする。

【0033】

40

本明細書において、発光素子は、有機EL、無機EL、有機ELと無機ELとが混合された素子のいずれでもよい。また、電子放出素子、など、電気磁気的作用によりコントラストが変化する表示媒体を適用することもできる。電子放出素子を用いた表示装置としてはフィールドエミッショングラスディスプレイ (FED)、SED方式平面型ディスプレイ (S E D : Surface-conduction Electron-emitter Display) などが挙げられる。

【0034】

また、本明細書において、「接続されている」とは、電気的に接続されている場合も含むものとする。したがって、間に別の素子やスイッチなどが配置されていてもよい。

【0035】

50

また、本発明におけるトランジスタは、どのようなタイプのトランジスタでもよい。例えば、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ（以下、「TFT」と記載する。）、半導体基板やSOI基板を用いて形成されるMOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。また、トランジスタが配置されている基板の種類に限定はなく、単結晶基板、SOI基板、ガラス基板、プラスチック基板などに配置することができる。

#### 【0036】

また、本明細書中において、「スイッチ」は、電気的なスイッチでもよいし、機械的なスイッチでもよい。すなわち、電流の流れを制御できるものなら、何でも良い。例えば、トランジスタでもよいし、ダイオードでもよいし、それらを組み合わせた論理回路でもよい。なお、スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性（導電型）は特に限定されない。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域が設けられているものや、マルチゲート構造のもの等がある。また、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源（V<sub>ss</sub>、V<sub>gnd</sub>、0Vなど）に近い状態で動作する場合はnチャネル型を、反対に、ソース端子の電位が、高電位側電源（V<sub>dd</sub>など）に近い状態で動作する場合はpチャネル型を用いることが望ましい。なぜなら、ゲート・ソース間電圧の絶対値を大きくできるため、スイッチとして、動作しやすいからである。また、nチャネル型とpチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。

10

20

30

40

50

#### 【0037】

なお、すでに述べたように、本発明におけるトランジスタは、どのようなタイプのトランジスタでもよいし、どのような基板上に形成されていてもよい。したがって、画素を駆動する回路が全てガラス基板上に形成されていてもよいし、プラスチック基板上に形成されていてもよいし、単結晶基板上に形成されていてもよいし、SOI基板上に形成されていてもよいし、他のどのような基板上に形成されていてもよい。また、画素を駆動する回路の一部が、第1の基板上に形成されており、画素を駆動する回路の他の一部が、前記第1の基板とは別の第2の基板上に形成されていてもよい。すなわち、画素を駆動する回路の全てが同じ基板上に形成されていなくてもよい。例えば、画素配列及びゲート線駆動回路は、TFTを用いてガラス基板上に形成し、信号線駆動回路（もしくはその一部）は単結晶基板上に形成してもよい。さらに、単結晶基板上に形成した前記信号線駆動回路を（ICチップ）をCOG（Chip On Glass）で接続して前記ガラス基板上に配置してもよいし、ICチップをTAB（Tape Auto Bonding）やプリント基板を用いて前記ガラス基板と接続するようにしてもよい。

#### 【0038】

また、本明細書において「半導体装置」とは、トランジスタやダイオードなどの半導体素子を有する装置のことをいう。なお、表示装置とは、液晶素子やEL素子などの表示素子を有する装置のことを言う。なお、液晶表示装置とは、液晶素子を有する表示装置のことをいう。発光装置とは、EL素子などの発光素子を有する装置のことをいう。

#### 【0039】

また、本発明は、パッシブマトリックス駆動方式、アクティブマトリックス駆動方式のいずれの駆動方式を用いた表示装置にも適用することができる。

#### 【発明の効果】

#### 【0040】

本発明を適用することにより、簡単なプロセスを追加するのみで欠陥画素を確実に修正することができ、輝点がなく、画面全体の画質不良が低減された、表示品位に優れた表示装置が得られる。また、同時に表示装置の作製歩留まりの向上、大幅なコストダウンを図ることができる。

## 【0041】

また、発光素子が設けられている複数の画素のうち、常に発光素子が発光している画素に対して本発明を適用すると、常時黒の表示となる。したがって、例えば点欠（ドット抜け）の状態であるという点においては、本発明を適用する場合としない場合においても同じである。しかしながら、全画素の発光素子を発光させようとしているときに消灯している画素がある状態の方が、全画素の発光素子を消灯させようとしているときに点灯している画素がある状態に比べて、画素の欠陥が目立ちにくい。したがって、本発明により、表示品位に優れ、かつ消費電力の点でも格段に優れた表示装置を提供することができる。また、正常な発光素子が設けられた画素に対して不良画素が悪影響を与えることもない。

## 【0042】

10

また、上述のような構成を有する表示装置は、欠陥画素が形成された場合に容易に画素の欠陥を修正することができる。

## 【図面の簡単な説明】

## 【0043】

【図1】本発明の実施の形態1を示す図。

【図2】本発明の実施の形態3を示す図。

【図3】本発明の実施の形態3を示す図。

【図4】本発明の実施の形態5を示す図。

【図5】本発明の実施の形態6を示す図。

【図6】本発明の実施の形態7を示す図。

【図7】本発明の実施の形態8を示す図。

【図8】本発明の実施例2を示す図。

【図9】本発明の実施の形態6を示す図。

【図10】本発明の実施例2を示す図。

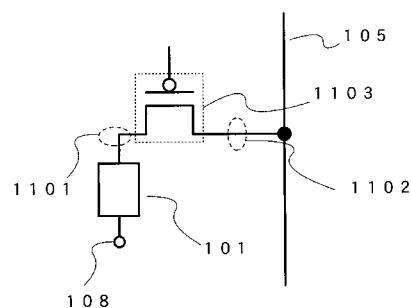

【図11】本発明の実施の形態1、4を示す図。

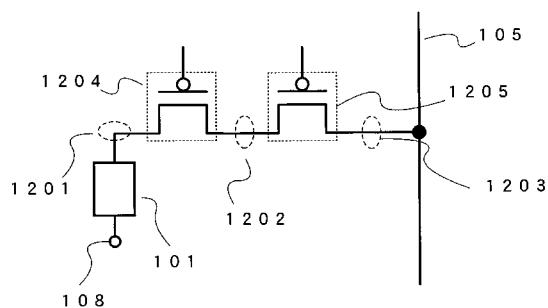

【図12】本発明の実施の形態1、4を示す図。

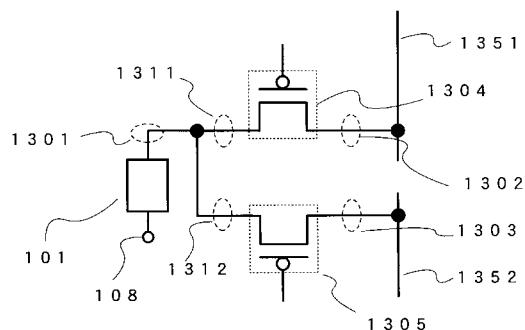

【図13】本発明の実施の形態1、4を示す図。

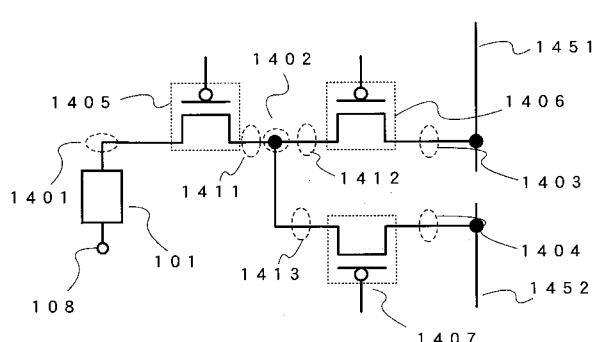

【図14】本発明の実施の形態1、4を示す図。

【図15】本発明の実施の形態1、4を示す図。

【図16】本発明の実施の形態5を示す図。

20

【図17】本発明の実施の形態5を示す図。

【図18】本発明の実施の形態9を示す図。

【図19】本発明の実施の形態6を示す図。

【図20】本発明の実施の形態6を示す図。

【図21】本発明の実施例1を示す図。

【図22】本発明の実施例1を示す図。

【図23】本発明の実施例1を示す図。

【図24】本発明の実施例1を示す図。

【図25】本発明の実施例1を示す図。

【図26】本発明の実施例1を示す図。

30

【図27】本発明の実施例1を示す図。

【図28】本発明の実施例1を示す図。

【図29】本発明の実施例1を示す図。

【図30】本発明の実施例1を示す図。

【図31】本発明の実施例1を示す図。

【図32】本発明の実施例1を示す図。

【図33】本発明の実施例1を示す図。

【図34】本発明の実施例1を示す図。

【図35】本発明の実施の形態9を示す図。

【図36】本発明の実施の形態10を示す図。

40

50

【図37】本発明の実施の形態11を示す図。

【図38】本発明の実施の形態12を示す図。

【図39】本発明の実施の形態13を示す図。

【図40】本発明の実施の形態14を示す図。

【図41】本発明の実施の形態15を示す図。

【図42】本発明の実施の形態16を示す図。

【図43】本発明の実施の形態17を示す図。

【発明を実施するための形態】

【0044】

本発明を実施するための最良の形態を、図面を用いながら説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

10

【0045】

(実施の形態1)

本実施の形態では、発光素子の一方の電極に電位を与える電源線と前記発光素子の一方の電極との間において、少なくとも1箇所配線をカット(切断)する方法について図を用いながら説明する。

20

【0046】

図11を用いて説明する。各画素には、発光素子101、トランジスタ1103が設けられており、トランジスタ1103のソースとドレインは、一方が電源線105に、もう一方が発光素子101の一方の電極にそれぞれ接続されている。

30

【0047】

次に、欠陥画素の修正方法について説明する。電源線105がトランジスタ1103を介して発光素子101の一方の電極に接続されている場合、電源線105とトランジスタ1103のソース、ドレインのいずれか一方とが接続されている間、またはトランジスタのソース、ドレインの他方と発光素子101の一方の電極とが接続されている間の配線をカットするようにする。例えば、図11の橢円形状で示した領域1101、1102をカットする。なお、カットする箇所は少なくとも1箇所あればよいが、信頼性向上のために2箇所以上カットするようにしてもよい。

30

【0048】

このように、発光素子の両極間ショート、配線間のショート、発光素子の電極と配線間のショート、または発光素子に接続されたトランジスタの動作不良が生じていても領域1101や領域1102をカットすることにより、電源線105からトランジスタ1103や発光素子101を通って発光素子の他方の電極108に電流が流れる経路を遮断することができるため、発光素子101が発光すること(輝点の発生)を防止することができる。

40

【0049】

なお、図11におけるトランジスタ1103は、Pチャネル型を示しているが、これに限定されない。トランジスタ1103がNチャネル型の場合でも、領域1101や領域1102をカットすることにより、電源線105からトランジスタ1103や発光素子101を通って発光素子の他方の電極108に電流が流れる経路を遮断するため、発光素子101が発光すること(輝点の発生)を防止することができる。また、図11においては電源線105と発光素子101との間にトランジスタ1103を有する構成を示しているが、トランジスタ1103の代わりに別の素子を設ける構成としてもよい。また、電源線105と発光素子101との間にトランジスタ1103に加え、当該トランジスタ1103以外の素子を有する構成としても本発明を実施することが可能である。

50

【0050】

次に、図12を用いて説明する。各画素には、発光素子101、第1のトランジスタ1204、第2のトランジスタ1205が設けられており、第2のトランジスタ1205のソースとドレインは、一方が電源線105に、他方が第1のトランジスタ1204のソースとドレインの一方に接続され、第1のトランジスタ1204のソースとドレインの他方が発光素子101の一方の電極に接続されている。すなわち、電源線105は、互いに直列に接続された第1のトランジスタ1204及び第2のトランジスタ1205を介して発光素子101の一方の電極に接続されている。

#### 【0051】

次に、欠陥画素の修正方法について説明する。電源線105と第2のトランジスタ1205のソース、ドレインの一方とが接続されている間、第2のトランジスタ1205のソース、ドレインの他方と第1のトランジスタ1204のソース、ドレインの一方とが接続されている間、または第1のトランジスタのソース、ドレインの他方と発光素子101の一方の電極とが接続されている間のどこかで配線をカットする。例えば、電源線105と発光素子101の一方の電極との間ににおいて、図12の橢円形状で示した領域1201、1202、1203を切断する。なお、カットする箇所は少なくとも1箇所あればよいが、信頼性向上のために2箇所以上カットするようにしてもよい。

10

#### 【0052】

このように、発光素子の両極間ショート、配線間のショート、発光素子の電極と配線間のショート、または発光素子に接続されたトランジスタの動作不良が生じていても領域1201、領域1202、領域1203をカットすることにより、電源線105から第1のトランジスタ1204及び第2のトランジスタ1205や発光素子101を通じて発光素子の他方の電極108に電流が流れる経路を遮断することができるため、発光素子101が発光すること（輝点の発生）を防止することができる。

20

#### 【0053】

なお、図12における第1のトランジスタ1204、第2のトランジスタ1205は、それぞれPチャネル型を示しているが、これに限定されない。第1のトランジスタ1204、第2のトランジスタ1205のいずれか一つがNチャネル型であったり、共にNチャネル型の場合でも、領域1201や領域1202、領域1203をカットすることにより、電源線105から第1のトランジスタ1204及び第2のトランジスタ1205や発光素子101を通じて発光素子の他方の電極108に電流が流れる経路を遮断することができるため、発光素子101が発光すること（輝点の発生）を防止することができる。すなわち、第1のトランジスタ1204、第2のトランジスタ1205は共にPチャネル型である場合、共にNチャネル型である場合、2つのトランジスタのうち一方がPチャネル型で他方がNチャネル型である場合のいずれの場合でもよい。なお、図12では、トランジスタが2つ直列になっているものを示したが、これに限定されない。3個以上のトランジスタが接続されていてもよい。その場合も、図12と同様に配線をカットすればよい。また、電源線105と発光素子101との間に、第1のトランジスタ1204及び第2のトランジスタ1205以外の素子も有する構成としても本発明を実施することができる。

30

#### 【0054】

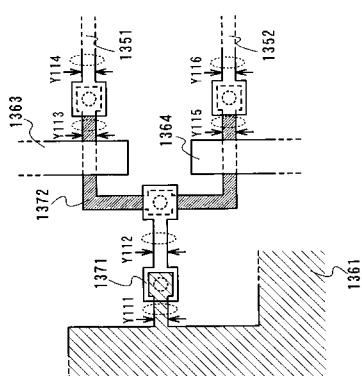

次に、図13を用いて説明する。各画素には、発光素子101、第1のトランジスタ1304、第2のトランジスタ1305が設けられている。また、第1のトランジスタ1304のソースとドレインは、一方が配線1351に、もう一方が発光素子101の一方の電極に接続されている。また、第2のトランジスタ1305のソースとドレインは、一方が配線1352に、もう一方が発光素子101の一方の電極に接続されている。なお、配線1351と配線1352は、同じ電源に接続されていてもよいし、互いに異なる電源に接続されていてもよい。

40

#### 【0055】

次に、欠陥画素の修正方法について説明する。配線1351と第1のトランジスタ1304のソース、ドレインの一方とが接続されている間、配線1352と第2のトランジス

50

タ1305のソース、ドレインの一方とが接続されている間の配線をともにカットする。または、第1のトランジスタ1304のソース、ドレインの他方と第2のトランジスタ1305のソース、ドレインの他方とが接続されている箇所と発光素子101の一方の電極とが接続されている間のどこかで配線をカットする。例えば、図13の橢円形状で示した領域1301をカットするか、領域1302及び領域1311のいずれか一方と領域1303及び領域1312のいずれか一方とを共にカットする。

#### 【0056】

このように、発光素子の両極間ショート、配線間のショート、発光素子の電極と配線間のショート、または発光素子に接続されたトランジスタの動作不良が生じていても領域1301をカットするか、領域1302及び領域1303を共にカットすることにより、配線1351及び配線1352から各トランジスタや発光素子101を通って発光素子の他方の電極108に電流が流れる経路を遮断することができるため、発光素子101が発光すること（輝点の発生）を防止することができる。

10

#### 【0057】

なお、図13における第1のトランジスタ1304、第2のトランジスタ1305は、それぞれPチャネル型を示しているが、これに限定されない。第1のトランジスタ1304、第2のトランジスタ1305がNチャネル型の場合でも、領域1301をカットするか、領域1302、領域1303をカットすることにより、電源線105から各トランジスタや発光素子101を通って発光素子の他方の電極108に電流が流れる経路を遮断することができるため、発光素子101が発光すること（輝点の発生）を防止することができる。すなわち、第1のトランジスタ1304、第2のトランジスタ1305は共にPチャネル型である場合、共にNチャネル型である場合、2つのトランジスタのうち一方がPチャネル型で他方がNチャネル型である場合のいずれの場合でもよい。なお、図13では、トランジスタが2つ並列になっているものを示したが、これに限定されない。3個以上のトランジスタが並列接続されていてもよい。その場合も、図13と同様に配線をカットすればよい。

20

#### 【0058】

配線1351及び配線1352は、何と接続されていてもよい。電源線に接続されていてもよいし、回路やトランジスタ、容量素子に接続されていてもよい。また、配線1351及び配線1352は、各々別のものに接続されていてもよいし、同じものに接続されていてもよい。また、配線1351及び配線1352が同一のものであり、配線1351及び配線1352それ自体が電源線として機能する配線でもよい。

30

#### 【0059】

第1のトランジスタ1304は、一つだけ配置されているが、これに限定されない。例えば、図15に示すように、さらに別のトランジスタなどの素子が直列に接続されていてもよい。また、第2のトランジスタ1305も同様に、さらにトランジスタなどの素子が直列に接続されていてもよい。

#### 【0060】

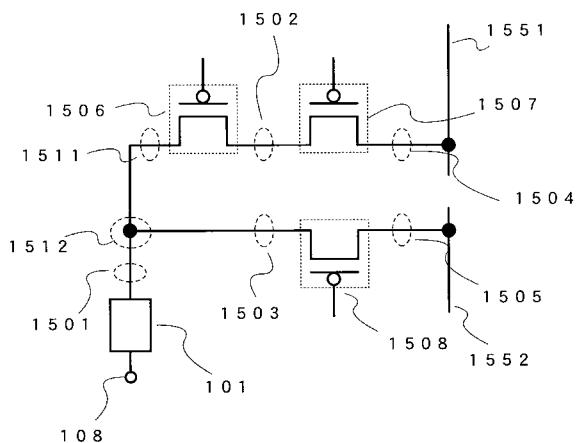

次に、図15を用いて説明する。各画素には、発光素子101、第1のトランジスタ1506、第2のトランジスタ1507、第3のトランジスタ1508が設けられている。また、第2のトランジスタ1507のソースとドレインは、一方が配線1551に、他方が第1のトランジスタ1506のソースとドレインの一方に接続されている。また、第3のトランジスタ1508のソースとドレインは、一方が配線1552に、他方が発光素子101の一方の電極に接続されている。また、第1のトランジスタ1506のソースとドレインの他方は、発光素子101の一方の電極に接続されている。なお、配線1551と配線1552は、同じ電源に接続されていてもよいし、互いに異なる電源に接続されていてもよい。

40

#### 【0061】

次に、欠陥画素の修正方法について説明する。配線1551と第2のトランジスタ1507のソース、ドレインの一方とが接続されている箇所から第2のトランジスタ1507

50

のソース、ドレインの一方までの間の配線、第2のトランジスタ1507のソース、ドレインの他方と第1のトランジスタ1506のソース、ドレインの一方とが接続されている間の配線、第1のトランジスタ1506のソース、ドレインの他方と発光素子101の一方の電極が接続されている箇所から第1のトランジスタ1506のソース、ドレインの他方までの間の配線のいずれか一を少なくともカットすることにより、配線1551から発光素子101の他方の電極までの電流が流れる経路を遮断することができる。さらに、配線1552と第3のトランジスタ1508のソース、ドレインの一方とが接続されている箇所から第3のトランジスタ1508のソース、ドレインの一方までの間の配線、第3のトランジスタ1508のソース、ドレインの他方と発光素子101の一方の電極が接続されている箇所から第3のトランジスタ1508のソース、ドレインの他方までの間の配線のいずれか一を少なくともカットすることにより、配線1552から発光素子101の他方の電極までの電流が流れる経路を遮断することができる。例えば、配線1551及び配線1552と発光素子101の一方の電極との間ににおいて、図15の橜円形状で示した領域1501または領域1512をカットするか、領域1502、領域1504、領域1511のいずれか一方と領域1503及び領域1505のいずれか一方とを共にカットする。

10

#### 【0062】

このように、発光素子の両極間ショート、配線間のショート、発光素子の電極と配線間のショート、または発光素子に接続されたトランジスタの動作不良が生じていても、領域1501をカットするか、領域1502、領域1504の一方、及び領域1503、領域1505の一方を共にカットすることにより、配線1551及び配線1552から各トランジスタや発光素子101を通って発光素子の他方の電極108に電流が流れる経路を遮断することができるため、発光素子101が発光すること（輝点の発生）を防止することができる。

20

#### 【0063】

なお、図15における第1～3のトランジスタ1506～1508は、それぞれPチャネル型を示しているが、これに限定されるものでない。すなわち、第1～3のトランジスタ1506～1508の導電型に依存するものではなく、領域1501をカットするか、領域1502、領域1504の一方、及び領域1503、領域1505の一方を共にカットすることにより、配線1551及び配線1552から各トランジスタや発光素子101を通って発光素子の他方の電極108に電流が流れる経路を遮断することができるため、発光素子101が発光すること（輝点の発生）を防止することができる。

30

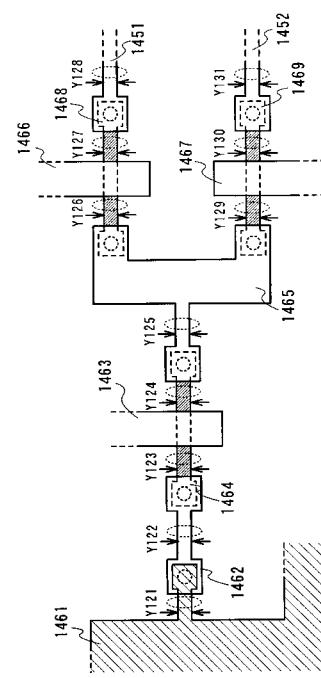

#### 【0064】

次に、図14を用いて説明する。各画素には、発光素子101、第1のトランジスタ1405、第2のトランジスタ1406、第3のトランジスタ1407が設けられている。また、第2のトランジスタ1406のソースとドレインは、いずれか一方が配線1451に、他方が第1のトランジスタ1405のソースとドレインのいずれか一方に接続されている。また、第3のトランジスタ1407のソースとドレインは、いずれか一方が配線1452に、他方が第1のトランジスタ1405のソースとドレインのいずれか一方に接続されている。また、第1のトランジスタ1405のソースとドレインの他方は、発光素子101の一方の電極に接続されている。なお、配線1451と配線1452は、同じ電源に接続されていてもよいし、互いに異なる電源に接続されていてもよい。また、配線1451及び配線1452が同一のものであり、配線1451及び配線1452それ自体が電源線として機能する配線でもよい。

40

#### 【0065】

次に、欠陥画素の修正方法について説明する。発光素子101の一方の電極と第1のトランジスタ1405のソース、ドレインの他方とが接続されている間の配線をカットする。または、第1のトランジスタ1405のソース、ドレインの一方と、第2のトランジスタ1406のソース、ドレインの他方及び第3のトランジスタ1407のソース、ドレインの他方とが接続されている箇所の配線をカットする。または、第2のトランジスタ14

50

06のソース、ドレインの一方と配線1451とが接続されている間、第3のトランジスタ1407のソース、ドレインの一方と配線1452とが接続されている間の配線をともにカットする。例えば、配線1451及び配線1452と発光素子101の一方の電極との間ににおいて、図14の機能円形状で示した領域1401、領域1402または領域1411をカットするか、領域1403及び領域1412のいずれか一方と領域1404及び領域1413のいずれか一方とを共にカットする。

【0066】

このように、発光素子の両極間ショート、配線間のショート、発光素子の電極と配線間のショート、または発光素子に接続されたトランジスタの動作不良が生じても領域1401または領域1402をカットするか、領域1403及び領域1404を共にカットすることにより、配線1451及び配線1452から各トランジスタや発光素子101を通って発光素子の他方の電極108に電流が流れる経路を遮断することができるため、発光素子101が発光すること（輝点の発生）を防止することができる。

10

【0067】

なお、図14における第1～3のトランジスタ1405～1407は、それぞれPチャネル型を示しているが、これに限定されるものでない。すなわち、第1～3のトランジスタ1405～1407の導電型に依存するものではなく、領域1401または領域1402をカットするか、領域1403及び領域1404を共にカットすることにより、配線1451及び配線1452から各トランジスタや発光素子101を通って発光素子の他方の電極108に電流が流れる経路を遮断することができるため、発光素子101が発光すること（輝点の発生）を防止することができる。なお、配線1451と第1のトランジスタ1405との間に、第2のトランジスタ1406以外のトランジスタなどの素子がさらに直列にあってもよいし、配線1452と第1のトランジスタ1405との間に、第3のトランジスタ1407以外のトランジスタなどの素子がさらに直列にあってもよい。また、第2のトランジスタ1406、第3のトランジスタ1407と並列関係にあるトランジスタなどの素子がさらにあってもよい。

20

【0068】

（実施の形態2）

本実施の形態では、発光素子の一方の電極に電位を与える電源線と前記発光素子の一方の電極との間ににおいて、少なくとも1箇所配線をカット（切断）する方法について説明する。

30

【0069】

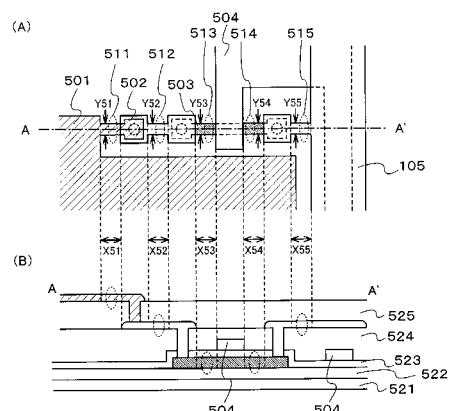

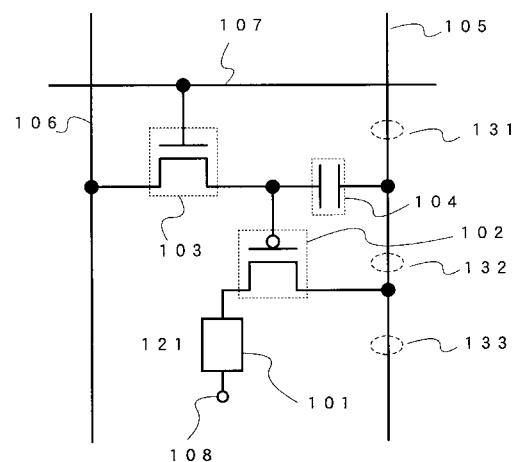

図1に、EL素子を有する画素がマトリクス状に設けられている画素部における1画素の構成の一例を示す。

【0070】

各画素には、発光素子101、駆動用のトランジスタ102、スイッチング用トランジスタ103、コンデンサ104が設けられている。スイッチング用トランジスタ103のゲート電極は、ゲート信号線107（走査線）に接続され、ソース領域とドレイン領域は、一方がソース信号線106（データ線）に、もう一方が駆動用のトランジスタ102のゲート電極及びコンデンサ104の一方の電極にそれぞれ接続されている。

40

【0071】

コンデンサ104はスイッチング用トランジスタ103が非選択状態（オフ状態）にあるとき、駆動用のトランジスタ102のゲート電圧（ゲート電極とソース領域間の電位差）を保持するために設けられている。なお、本実施の形態ではコンデンサ104を設ける構成を示したが、本発明はこの構成に限定されず、コンデンサ104を設けない構成にしてもよい。つまり、駆動用のトランジスタ102のゲート容量で代用することが可能である。トランジスタ102のゲート容量については、ソース領域、ドレイン領域、LDD領域などとゲート電極とが重なってオーバーラップしているような領域で容量が形成されていてもよいし、チャネル形成領域とゲート電極との間で容量が形成されていてもよいし、それらの組み合わせでもよい。

50

## 【0072】

また、駆動用のトランジスタ102のソース領域とドレイン領域は、一方が電源線105に接続され、もう一方は発光素子101の一方の電極に接続される。本実施の形態では、スイッチング用トランジスタ103はPチャネル型であり、電源線105の方が発光素子の他方の電極108よりも電位が高いとしているので、電源線105に接続されているのがソースであり、発光素子101の一方の電極に接続されているのがドレインである。

## 【0073】

電源線105はコンデンサ104の他方の電極に接続されている。しかし、この構成に限定されるものではなく、例えば、コンデンサ104の他方の電極に専用配線が接続されていてもよいし、他の画素のゲート信号線が接続されている構成でもよい。

10

## 【0074】

発光素子101は、陽極と陰極との間に設けられた有機化合物を含む層とからなる。陽極が駆動用のトランジスタ102のソース領域またはドレイン領域と接続している場合、陽極が画素電極、陰極が対向電極となる。逆に陰極が駆動用のトランジスタ102のソース領域またはドレイン領域と接続している場合、陰極が画素電極、陽極が対向電極となる。なお、本実施の形態では、画素電極を陽極として説明する。

## 【0075】

なお、有機化合物を含む層は、蒸着マスクを用いた蒸着法、またはインクジェット法によって形成される。有機化合物を含む層には、元素周期律第4族金属錯体をその一部に用いることとする。また、その他、組み合わせて用いることのできる材料としては、低分子系材料であっても高分子系材料であっても良い。また、有機化合物を含む層に用いる材料としては、通常、有機化合物を単層もしくは積層で用いる場合が多いが、有機化合物からなる膜の一部に無機化合物を用いる構成であってもよい。さらに、一重項材料だけでなく公知の三重項材料を用いることも可能である。

20

## 【0076】

発光素子101の発光素子の他方の電極108（対向電極（陰極））には低電源電位（VSS）が与えられている。また電源線は高電源電位（VDD）が与えられている。ここで、本明細書においては、高電源電位（VDD）は低電源電位（VSS）よりも相対的に高い電位を有しているものとする。また、高電源電位と低電源電位は、外付けのIC等により表示装置に設けられた電源によって与えられる。

30

## 【0077】

次に、欠陥画素の修正方法について説明する。

## 【0078】

電源線105と発光素子101の陽極との間において、少なくとも1箇所配線をカット（切断）する。例えば、図1の橢円形状で示した箇所121、122の少なくともいずれか一方（配線部）を切断する。例えば、駆動用のトランジスタ102の有する活性層を、チャネル幅方向に切断する。したがって、発光素子の両極間ショート、配線間のショート、発光素子の電極と配線間のショート、または発光素子に接続されたトランジスタの動作不良が生じていても、このように領域121や領域122をカットすることにより、電源線105から駆動用のトランジスタ102や発光素子101を通って発光素子の他方の電極108（陰極）に電流が流れる経路を遮断することができるため、発光素子101が発光すること（輝点の発生）を防止することができる。

40

## 【0079】

配線または活性層の切断方法については、公知の方法を用いればよい。例えば、任意の波長のレーザー光を、配線または活性層上の層間絶縁膜に照射して除去する。次に、任意の波長のレーザー光を露出された配線または活性層に照射して切断する。なお、レーザーの種類や、周波数、ビームプロファイル、エネルギー密度（またはパワー密度、）、パルス幅といったレーザーの照射条件についても特に限定されるものではない。また、レーザー光の発振方式は、パルス発振方式でもよいし、連続発振方式でもよい。また、レーザー光は、発光素子が設けられている側（基板上面側）から照射してもよいし、その逆側（基

50

板下面側)から照射してもよい。ただし、レーザー光を上面側から照射するときは、発光素子の他方の電極108(陰極)を透過させる必要があるので、下面側から照射することが望ましい。

#### 【0080】

本実施の形態では紫外(UV)レーザーを用いるが、本発明に用いるレーザーの種類に制約はない。レーザーは、レーザー媒質、励起起源、共振器により構成されている。レーザーは、媒質により分類すると、気体レーザー、液体レーザー、固体レーザーがあり、発振の特徴により分類すると、自由電子レーザー、半導体レーザー、X線レーザーがあるが、本発明では、いずれのレーザーを用いてもよい。なお、好ましくは、気体レーザー又は固体レーザーを用いるとよく、さらに好ましくは固体レーザーを用いるとよい。

10

#### 【0081】

気体レーザーは、ヘリウムネオンレーザー、炭酸ガスレーザー、エキシマレーザー、アルゴンイオンレーザーがある。エキシマレーザーは、希ガスエキシマレーザー、希ガスハライドエキシマレーザーがある。希ガスエキシマレーザーは、アルゴン、クリプトン、キセノンの3種類の励起分子による発振がある。アルゴンイオンレーザーは、希ガスイオンレーザー、金属蒸気イオンレーザーがある。

#### 【0082】

液体レーザーは、無機液体レーザー、有機キレートレーザー、色素レーザーがある。無機液体レーザーと有機キレートレーザーは、固体レーザーに利用されているネオジムなどの希土類イオンをレーザー媒質として利用する。

20

#### 【0083】

固体レーザーが用いるレーザー媒質は、固体の母体に、レーザー作用をする活性種がドープされたものである。固体の母体とは、結晶又はガラスである。結晶とは、YAG(イットリウム・アルミニウム・ガーネット結晶)、YLF、YVO<sub>4</sub>、YAlO<sub>3</sub>、サファイア、ルビー、アレキサンドライトである。また、レーザー作用をする活性種とは、例えば、3価のイオン(Cr<sup>3+</sup>、Nd<sup>3+</sup>、Yb<sup>3+</sup>、Tm<sup>3+</sup>、Ho<sup>3+</sup>、Er<sup>3+</sup>、Ti<sup>3+</sup>)である。

#### 【0084】

なお、媒質としてセラミック(多結晶)を用いると、短時間かつ低コストで自由な形状に媒質を形成することが可能である。媒質として単結晶を用いる場合、通常、直径数mm、長さ数十mmの円柱状のものが用いられているが、媒質としてセラミック(多結晶)を用いる場合はさらに大きいものを作ることが可能である。また、発光に直接寄与する媒質中のNd、Ybなどのドーパントの濃度は、単結晶中でも多結晶中でも大きくは変えられないため、濃度を増加させることによるレーザーの出力向上にはある程度限界がある。しかしながら、媒質としてセラミックを用いると、単結晶と比較して媒質の大きさを著しく大きくすることができるため大幅な出力向上が期待できる。さらに、媒質としてセラミックを用いると、平行六面体形状や直方体形状の媒質を容易に形成することが可能である。このような形状の媒質を用いて、発振光を媒質の内部でジグザグに進行させると、発振光路を長くとることができる。そのため、增幅が大きくなり、大出力で発振させることが可能になる。

30

#### 【0085】

また、本実施の形態では、駆動用のトランジスタ102をPチャネル型、スイッチング用トランジスタ103をNチャネル型としたが、本発明はこの構成に限定されず、それぞれNチャネル型、Pチャネル型のどちらでも用いることができる。ただし、本実施の形態のように、画素電極が発光素子101の陽極である場合、駆動用のトランジスタ102はPチャネル型であることが望ましい。また、画素電極が発光素子101の陰極である場合、駆動用のトランジスタ102はNチャネル型を用いると、駆動用のトランジスタ102のソース電位が変化せず、動作させやすいため、好ましい。

40

#### 【0086】

また、駆動用のトランジスタ102、スイッチング用トランジスタ103は、それぞ

50

非晶質半導体膜（代表的には、アモルファスシリコン）からなる活性層を有していてもよいし、多結晶半導体膜（代表的には、ポリシリコン）からなる活性層を有していてもよいし、単結晶でもよい。ただし、本実施の形態のように、駆動用のトランジスタ102としてPチャネル型を用いるときは、移動度の特性を考慮して多結晶半導体膜からなる活性層を有していることが望ましい。また、駆動用のトランジスタ102としてNチャネル型を用いるときは、非晶質半導体膜からなる活性層を有していることが望ましい。

【0087】

また、駆動用のトランジスタ102、スイッチング用トランジスタ103は、順スタガ型でもよいし、逆スタガ型であってもよい。また、トップゲート型でもよいし、ボトムゲート型でもよい。また、チャネル形成領域の上にゲート電極があってもよいし、下にゲート電極があってもよい。

10

【0088】

また、駆動用のトランジスタ102、スイッチング用トランジスタ103は、シングルゲート構造でもよいし、マルチゲート構造であってもよい。また、駆動用のトランジスタ102、スイッチング用トランジスタ103は、LDD構造を有していてもよいし、GOLD構造を有していてもよい。

20

【0089】

なお、本実施の形態では、駆動用のトランジスタ102と電源線105の間に、他のトランジスタや素子が配置されていない構成について説明したが、実施の形態1で説明した図12～15の構造のように、電源線と陽極との間に駆動用のトランジスタ102以外のトランジスタが配置されているような画素構成についても本発明を適用することができる。すなわち、画素内部に引き込まれた電源線と陽極との間ににおいて、電流の経路を断線させることにより、発光素子に電流が流れず発光しないようにしたり、他の画素に所定の電位を与えることができる。

20

【0090】

（実施の形態3）

本実施の形態では、発光素子の一方の電極に電位を与える電源線と前記発光素子の一方の電極との間ににおいて、少なくとも1箇所配線をカット（切断）する別の方法について説明する。

30

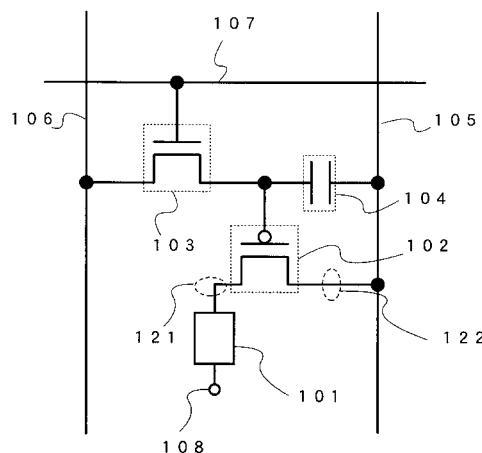

【0091】

図2に、表示装置の一例を示す。201は画素部、202は走査線駆動回路（ゲートドライバー）、203は信号線駆動回路（ソースドライバー）、を示している。また、走査線駆動回路202は、走査線G1～Gn（n：正の整数）を介して画素部201の各行を順に走査する。信号線駆動回路203は、信号線S1～Sm（m：正の整数）を介して画素部201の各列にデータ信号を伝達する。各画素の発光素子の一方の電極に電位を与えるための電源線V1～Vnは、各画素毎に上下の両方向から電位を与えることができるような構造になっている。なお、図2には、画素構成の一例を示しているが、本発明はこの画素構成に限定されるものではなく、他の実施の形態で説明するような構成を有する画素でも勿論構わない。

30

【0092】

次に、欠陥画素の修復方法について図3を用いながら説明する。なお、図3は、画素の構成に関して図1と全く同じであるので、ここでは接続関係などについての説明を省略する。

40

【0093】

欠陥画素に電源線から電位が与えられないようにするために、画素に電位を与える経路（図3における131、132の少なくともいずれか一と133）を2カ所（または3箇所）切断する。

【0094】

なお、欠陥画素を修正した後は、当該画素が設けられた画素の行よりも下の行には、下から電源線を介して電位を与え、当該画素が設けられた画素の行よりも上の行には、上か

50

ら電源線を介して電位を与えることが可能であり、その他の画素についても正常に動作させることができる。

【0095】

本実施の形態においては、図2のような画素構成の場合について説明したが、本発明は画素内部の構成には依存せず、あらゆる画素構成に対して本発明を適用することができる。すなわち、各画素に対して電源線105を介して上下の両方向から電位を与えることができるよう構造を有してさえいれば、あらゆる画素構成に対して本発明を適用することができる。

【0096】

(実施の形態4)

10

本実施の形態では、発光素子と、当該発光素子に電位を与える電源線との間において、前記発光素子に接続されたトランジスタが常時オフになるようにする方法について説明する。

【0097】

発光素子に接続されているトランジスタを常時オフにする方法として、トランジスタのゲート・ソース間電圧 $V_{gs}$ を制御して、Nチャネル型のときは $V_{gs} < V_{th}$ 、Pチャネル型のときは $V_{gs} > V_{th}$ となるようにする。例えば、Nチャネル型で、 $V_{th} > 0$ 、Pチャネル型で、 $V_{th} < 0$ のときは、トランジスタのゲートとソースとを同電位にする。

【0098】

20

まず、図11に示すような発光素子101と電源線105との接続関係の場合について説明する。1103は、Pチャネル型トランジスタを示している。

【0099】

発光素子に接続されているPチャネル型トランジスタ1103を常時オフにする方法として、Pチャネル型トランジスタ1103のゲート・ソース間電圧 $V_{gs}$ を制御して、 $V_{gs} > V_{th}$ となるようにする。例えば、 $V_{th} < 0$ のときは、トランジスタのゲートとソースとを同電位にする。

【0100】

30

したがって、電源線に接続されている発光素子の一方の電極が陽極の場合、電源線に接続されている側がソースであり、陽極に接続されている側がドレインとなるため、電源線105とPチャネル型トランジスタ1103のゲート配線とを短絡(ショート)させることにより、Pチャネル型トランジスタ1103のゲートとソースを同電位とすることができます。この結果、発光素子101の両端がショートしても発光素子に電流が流れ発光しないようにし、他の画素に所定の電位を与えることができる。

【0101】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、Pチャネル型トランジスタ1103のゲートに、ソースよりも高い電位を与えるようにしてもよい。すなわち、Pチャネル型トランジスタ1103のゲート配線と、高電位電源に接続された電源線105の電位よりも高い電位を与える配線とを短絡させるようにしてもよい。

【0102】

40

また、電源線に接続されている発光素子の一方の電極が陰極の場合、電源線に接続されている側がドレインであり、陰極に接続されている側がソースとなるため、発光素子の陰極とPチャネル型トランジスタ1103のゲート配線とを短絡(ショート)させることにより、Pチャネル型トランジスタ1103のゲートとソースを同電位とすることができます。この結果、発光素子101の両端がショートしても発光素子に電流が流れ発光しないようにし、他の画素に所定の電位を与えることができる。

【0103】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、Pチャネル型トランジスタ1103のゲートに、ソースよりも高い電位を与えるようにしてもよい。すなわち、Pチャネル型トランジスタ1103のゲート配線と、高電位電源に接続さ

50

れた発光素子の陽極の電位よりも高い電位を与える配線とを短絡させるようにしてもよい。

【0104】

なお、図11を用いて、トランジスタ1103がPチャネル型のときについて説明したが、トランジスタ1103がNチャネル型のときにも本発明は適用することができる。以下、具体的に説明する。

【0105】

電源線に接続されている発光素子の一方の電極が陽極の場合、発光素子の一方の電極に接続されている側がソースであり、電源線に接続されている側がドレインとなるため、発光素子の一方の電極とNチャネル型のトランジスタ1103のゲート配線とを短絡（ショート）させることにより、Nチャネル型のトランジスタ1103のゲートとソースを同電位とすることができる。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

10

【0106】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、Nチャネル型のトランジスタ1103のゲートに、ソースよりも低い電位を与えるようにしてもよい。すなわち、Nチャネル型のトランジスタ1103のゲート配線と、発光素子の陽極の電位よりも低い電位を与える配線とを短絡させることとしてもよい。

20

【0107】

また、電源線に接続されている発光素子の一方の電極が陰極の場合、陰極に接続されている側がドレインであり、電源線に接続されている側がソースとなるため、電源線105とNチャネル型のトランジスタ1103のゲート配線とを短絡（ショート）させることにより、Nチャネル型のトランジスタ1103のゲートとソースを同電位とすることができる。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

20

【0108】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、Nチャネル型のトランジスタ1103のゲートに、ソースよりも低い電位を与えるようにしてもよい。すなわち、Nチャネル型のトランジスタ1103のゲート配線と、低電位電源に接続された電源線の電位よりも低い電位を与える配線とを短絡させることとしてもよい。

30

【0109】

次に、図12に示すような発光素子101と電源線105との接続関係の場合について説明する。1204、1205は、共にPチャネル型トランジスタを示している。Pチャネル型トランジスタ1204、1205は直列接続されているので、少なくとも一つをオフにすればよいが、信頼性向上のために両方をオフにしてもよい。

【0110】

電源線に接続されている発光素子の一方の電極が陽極の場合、電源線に接続されている側がソースであり、陽極に接続されている側がドレインとなるため、電源線105と第1のPチャネル型トランジスタ1204のゲート配線、または電源線105と第2のPチャネル型トランジスタ1205のゲート配線とを短絡（ショート）させることにより、第1のPチャネル型トランジスタ1204または第2のPチャネル型トランジスタ1205をオフにすることができる。また、第1のPチャネル型トランジスタ1204のゲートとソースとを短絡（ショート）させることにより、第1のPチャネル型トランジスタ1204をオフにしてもよい。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

40

【0111】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、第1のPチャネル型トランジスタ1204または第2のPチャネル型トランジスタ1205のゲートに、ソースよりも高い電位を与えるようにしてもよい。すなわち、第1のPチャネル型トランジスタ1204または第2のPチャネル型トランジスタ1205のゲート配線と

50

、高電位電源に接続された電源線 105 の電位よりも高い電位を与える配線とを短絡させるようにしてもよい。

【0112】

また、電源線に接続されている発光素子の一方の電極が陰極の場合、電源線に接続されている側がドレインであり、陰極に接続されている側がソースとなるため、発光素子の陰極と、第1のPチャネル型トランジスタ1204または第2のPチャネル型トランジスタ1205のゲート配線とを短絡(ショート)させることにより、第1のPチャネル型トランジスタ1204または第2のPチャネル型トランジスタ1205をオフにすることができる。また、第2のPチャネル型トランジスタ1205のゲートとソースとを短絡(ショート)させることにより、第2のPチャネル型トランジスタ1205をオフにしてもよい。

10

この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

【0113】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、Pチャネル型のトランジスタのゲートに、ソースよりも高い電位を与えるようにしてもよい。すなわち、第1のPチャネル型トランジスタ1204または第2のPチャネル型トランジスタ1205のゲート配線と、高電位電源に接続された発光素子の陽極の電位よりも高い電位を与える配線とを短絡させるようにしてもよい。

20

【0114】

なお、図12を用いて、第1のトランジスタ1204及び第2のトランジスタ1205が共にPチャネル型のときについて説明したが、これに限定されない。第1のトランジスタ1204及び第2のトランジスタ1205が共にNチャネル型でもよいし、いずれか一方のみがNチャネル型のときにも本発明は適用することができる。以下、具体的に説明する。

30

【0115】

第1のトランジスタ1204及び第2のトランジスタ1205が共にNチャネル型の場合について説明する。Nチャネル型のトランジスタ1204、1205は直列接続されているので、少なくとも一つをオフにすればよいが、信頼性向上のために両方をオフにしてもよい。

30

【0116】

電源線に接続されている発光素子の一方の電極が陽極の場合、陽極に接続されている側がソースであり、電源線に接続されている側がドレインとなるため、陽極と第1のNチャネル型のトランジスタ1204のゲート配線、または陽極と第2のNチャネル型のトランジスタ1205のゲート配線とを短絡(ショート)させることにより、第1のNチャネル型のトランジスタ1204または第2のNチャネル型のトランジスタ1205をオフにすることができる。また、第2のNチャネル型のトランジスタ1205のゲートとソースとを短絡(ショート)させることにより、第2のNチャネル型のトランジスタ1205をオフにしてもよい。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

40

【0117】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、第1のNチャネル型のトランジスタ1204または第2のNチャネル型のトランジスタ1205のゲートに、ソースよりも低い電位を与えるようにしてもよい。すなわち、第1のNチャネル型のトランジスタ1204または第2のNチャネル型のトランジスタ1205のゲート配線と、陽極の電位よりも低い電位を与える配線とを短絡させるようにしてもよい。

【0118】

また、電源線に接続されている発光素子の一方の電極が陰極の場合、陰極に接続されている側がドレインであり、電源線に接続されている側がソースとなるため、電源線と、第1のNチャネル型のトランジスタ1204または第2のNチャネル型のトランジスタ12

50

05のゲート配線とを短絡(ショート)させることにより、第1のNチャネル型のトランジスタ1204または第2のNチャネル型のトランジスタ1205をオフにすることができる。また、第1のNチャネル型のトランジスタ1205のゲートとソースとを短絡(ショート)させることにより、第1のNチャネル型のトランジスタ1205をオフにしてもよい。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

【0119】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、Nチャネル型のトランジスタのゲートに、ソースよりも低い電位を与えるようにしてもよい。すなわち、第1のNチャネル型のトランジスタ1204または第2のNチャネル型のトランジスタ1205のゲート配線と、低電位電源に接続された電源線よりも低い電位を与える配線とを短絡させるようにしてもよい。

10

【0120】

次に、第1のトランジスタ1204及び第2のトランジスタ1205のうち、いずれか一方のみがNチャネル型のときについて説明する。

【0121】

上述したように、発光素子に接続されているトランジスタを常時オフにすればよいので、図12においては、第1のトランジスタ1204及び第2のトランジスタ1205の少なくとも一方を常時オフになるようにすればよい。そして、第1のトランジスタ1204がPチャネル型、Nチャネル型のそれぞれの場合につき、常時オフにさせる方法はすでに説明したので省略する。同様に、第2のトランジスタ1205がPチャネル型、Nチャネル型のそれぞれの場合のつき、常時オフにさせる方法はすでに説明したので省略する。

20

【0122】

次に、図13に示すような発光素子101と電源線との接続関係の場合について説明する。1304、1305は、共にPチャネル型トランジスタを示している。

【0123】

発光素子の他方の電極108よりも配線1351、配線1352の方が電位が高く、電源線に接続されている発光素子の一方の電極が陽極の場合、電源線に接続されている側がソースであり、陽極に接続されている側がドレインとなるため、配線1351と第1のPチャネル型トランジスタ1304のゲート配線、及び配線1352と第2のPチャネル型トランジスタ1305のゲート配線とを短絡(ショート)させることにより、第1のPチャネル型トランジスタ1304のゲートとソース、及び第2のPチャネル型トランジスタ1305のゲートとソースを同電位とすることができます。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

30

【0124】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、第1のPチャネル型トランジスタ1304及び第2のPチャネル型トランジスタ1305のゲートに、ソースよりも高い電位を与えるようにしてもよい。すなわち、第1のPチャネル型トランジスタ1304のゲート配線と、高電位電源に接続された配線1351の電位よりも高い電位を与える配線とを短絡させ、且つ、第2のPチャネル型トランジスタ1305のゲート配線と、高電位電源に接続された配線1352の電位よりも高い電位を与える配線とを短絡させるようにしてもよい。

40

【0125】

また、電源線に接続されている発光素子の一方の電極が陰極の場合、電源線に接続されている側がドレインとなり、陰極に接続されている側がソースとなるため、発光素子の陰極と、第1のPチャネル型トランジスタ1304及び第2のPチャネル型トランジスタ1305のゲート配線とを短絡(ショート)させることにより、第1及び第2のPチャネル型トランジスタのゲートとソースを同電位とすることができます。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定

50

の電位を与えることができる。

【0126】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、第1のPチャネル型トランジスタ1304及び第2のPチャネル型トランジスタ1305のゲートに、ソースよりも高い電位をそれぞれ与えるようにしてもよい。すなわち、第1のPチャネル型トランジスタ1304及び第2のPチャネル型トランジスタ1305のゲート配線と、高電位電源に接続された発光素子の陽極の電位よりも高い電位を与える配線とを短絡させるようにしてもよい。

【0127】

なお、図13を用いて、第1のトランジスタ1304及び第2のトランジスタ1305が共にPチャネル型のときについて説明したが、これに限定されない。第1のトランジスタ1304及び第2のトランジスタ1305が共にNチャネル型でもよいし、いずれか一方のみがNチャネル型のときにも本発明は適用することができる。

10

【0128】

次に、図14に示すような発光素子101と電源線との接続関係の場合について説明する。1405、1406、1407は、全てPチャネル型トランジスタを示している。

【0129】

発光素子の他方の電極108よりも配線1451、配線1452の方が電位が高く、電源線に接続されている発光素子の一方の電極が陽極の場合、電源線に接続されている側がソースであり、陽極に接続されている側がドレインとなるため、配線1451と第2のPチャネル型トランジスタ1406のゲート配線、及び配線1452と第3のPチャネル型トランジスタ1407のゲート配線とを短絡(ショート)させることにより、第2のPチャネル型トランジスタ1406のゲートとソース、及び第3のPチャネル型トランジスタ1407のゲートとソースを同電位とすることができます。また、第1のPチャネル型トランジスタ1405と第2のPチャネル型トランジスタ1406及び第3のPチャネル型トランジスタ1407とを接続している配線と、第1のPチャネル型トランジスタ1405のゲート配線とを短絡(ショート)させることにより、第1のPチャネル型トランジスタ1405のゲートとソースを同電位とすることができます。また、第1のPチャネル型トランジスタ1405のゲート配線と、配線1451または配線1452とをショートさせるようにしてもよい。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

20

【0130】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、第2のPチャネル型トランジスタ1406及び第3のPチャネル型トランジスタ1407のゲートに、ソースよりも高い電位を与えるようにしてもよい。すなわち、第2のPチャネル型トランジスタ1406のゲート配線と、高電位電源に接続された配線1451の電位よりも高い電位を与える配線とを短絡させ、且つ、第3のPチャネル型トランジスタ1407のゲート配線と、高電位電源に接続された配線1452の電位よりも高い電位を与える配線とを短絡させることにより、第1のPチャネル型トランジスタ1405のゲート配線と配線1451よりも配線1452の方が電位が高い場合、第2のPチャネル型トランジスタ1406のゲート配線と配線1452とをショートさせてもよい。また、第1のPチャネル型トランジスタ1405のゲートに、ソースよりも高い電位を与えるようにしてもよい。

30

【0131】

また、電源線に接続されている発光素子の一方の電極が陰極の場合、電源線に接続されている側がドレインであり、陰極に接続されている側がソースとなる。このため、発光素子の陰極と、第1のPチャネル型トランジスタ1405のゲート配線とを短絡(ショート)させることにより、第1のPチャネル型トランジスタ1405のゲートとソースを同電位とすることができます。また、第1のPチャネル型トランジスタ1405と第2のPチャネル型トランジスタ1406及び第3のPチャネル型トランジスタ1407とを接続している配線と、第2のPチャネル型トランジスタ1406のゲート配線及び第3のPチャネ

40

50

ル型トランジスタ1407のゲート配線を共に短絡(ショート)させることにより、第2のPチャネル型トランジスタ1406のゲートとソース及び第3のPチャネル型トランジスタ1407のゲートとソースを同電位とすることができる。また、第1のPチャネル型トランジスタ1405のゲートと、配線1451または配線1452とを短絡(ショート)させることにより、第1のPチャネル型トランジスタ1405をオフにしてもよい。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

【0132】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、第2のPチャネル型トランジスタ1406及び第3のPチャネル型トランジスタ1407のゲートに、ソースよりも高い電位を与えるようにしてもよい。また、第1のPチャネル型トランジスタ1405のゲートに、ソースよりも高い電位を与えるようにしてもよい。

10

【0133】

なお、図14を用いて、第1～3のトランジスタ1405～1407が全てPチャネル型のときについて説明したが、これに限定されない。第1～3のトランジスタ1405～1407が全てNチャネル型でもよいし、これらのうち1個または2個のトランジスタがNチャネル型のときにも本発明は適用することができる。

【0134】

次に、図15に示すような発光素子101と電源線との接続関係の場合について説明する。1506、1507、1508は、全てPチャネル型トランジスタを示している。

20

【0135】

発光素子の他方の電極108よりも配線1551、配線1552の方が電位が高く、電源線に接続されている発光素子の一方の電極が陽極の場合、電源線に接続されている側がソースであり、陽極に接続されている側がドレインとなるため、配線1551と第2のPチャネル型トランジスタ1507のゲート配線、及び配線1552と第3のPチャネル型トランジスタ1508のゲート配線とを短絡(ショート)させることにより、第2のPチャネル型トランジスタ1507のゲートとソース、及び第3のPチャネル型トランジスタ1508のゲートとソースを同電位とすることができます。また、第1のPチャネル型トランジスタ1506と第2のPチャネル型トランジスタ1507とを接続している配線または配線1551と、第1のPチャネル型トランジスタ1506のゲート配線とを短絡(ショート)させることにより、第1のPチャネル型トランジスタ1506のゲートとソースを同電位とすることができます。この結果、発光素子101の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

30

【0136】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、第1のPチャネル型トランジスタ1506または第2のPチャネル型トランジスタ1507、及び第3のPチャネル型トランジスタ1508のゲートに、ソースよりも高い電位を与えるようにしてもよい。すなわち、第1のPチャネル型トランジスタ1506または第2のPチャネル型トランジスタ1507のゲート配線と、高電位電源に接続された配線1551の電位よりも高い電位を与える配線とを短絡させ、且つ、第3のPチャネル型トランジスタ1508のゲート配線と、高電位電源に接続された配線1552の電位よりも高い電位を与える配線とを短絡させるようにしてもよい。

40

【0137】

また、電源線に接続されている発光素子の一方の電極が陰極の場合、電源線に接続されている側がドレインであり、陰極に接続されている側がソースとなる。このため、発光素子の陰極と第1のPチャネル型トランジスタ1506のゲート配線とを短絡(ショート)させることにより、第2のPチャネル型トランジスタ1507のゲート配線と、第1のPチャネル型トランジスタ1506及び第2のPチャネル型トランジスタ1507とを接続している配線とを短絡(ショート)させることにより、配線1551と発光素子101の陽極との間で電流が流れる経路を断つことができる。さらに、発光素子の陰極と第3のPチャネル

50

型トランジスタ 1508 のゲート配線とを短絡（ショート）させることにより、配線 1552 と発光素子 101 の陽極との間で電流が流れる経路を断つことができる。この結果、発光素子 101 の両端がショートしても発光素子に電流が流れて発光しないようにし、他の画素に所定の電位を与えることができる。

【0138】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、第 1 の P チャネル型トランジスタ 1506 または第 2 の P チャネル型トランジスタ 1507 のゲートに、ソースよりも高い電位を与えるようにし、且つ、第 3 の P チャネル型トランジスタ 1508 のゲートに、ソースよりも高い電位を与えるようにしてもよい。

【0139】

なお、図 15 を用いて、第 1 ~ 3 のトランジスタ 1506 ~ 1508 が全て P チャネル型のときについて説明したが、これに限定されない。第 1 ~ 3 のトランジスタ 1506 ~ 1508 が全て N チャネル型でもよいし、これらのうち 1 個または 2 個のトランジスタが N チャネル型のときにも本発明は適用することができる。

【0140】

以上、本実施の形態では、発光素子に接続されたトランジスタを常時オフにするようにする方法について説明したが、発光素子に電位を与える電流の経路が図 13 ~ 15 のように複数有る場合は、実施の形態 1、2 で述べた方法と本実施の形態で述べた方法を組み合わせて使用することが可能である。例えば、図 15 において、配線 1551 に接続されている電流の経路については領域 1502 または領域 1504 にレーザーを照射して配線をカットし、配線 1552 に接続されている電流の経路については、第 3 のトランジスタ 1508 のゲートとソースの電位を同電位にするようにし、第 3 のトランジスタ 1508 が常時オフになるようにすることもできる。

【0141】

（実施の形態 5）

本実施の形態では、発光素子と、当該発光素子に電位を与える電源線との間において、前記発光素子に接続されたトランジスタが常時オフになるようにする方法について図 4 を用いながら説明する。なお、図 4 は、図 1 におけるスイッチング用トランジスタ 103 が P チャネル型に置き換わっていること以外、図 1 と全く同じであるため、ここでは接続関係などについての説明を省略する。

【0142】

実施の形態 1 で説明したように、駆動用のトランジスタ 102 は P チャネル型であり、電源線に接続されている発光素子の一方の電極は陽極である。つまり、電源線に接続されている側がソースであり、陽極に接続されている側がドレインとなる。したがって、より具体的には、電源線 105 と駆動用のトランジスタ 102 のゲート配線とを短絡（ショート）させることにより、駆動用のトランジスタ 102 のゲートとソースを同電位とすることができます。この結果、発光素子 101 の両端がショートしても、発光素子に電流が流れて発光しないようにしたり、他の画素に所定の電位を与えることができる。なお、ゲートとソースとを同電位とする駆動用のトランジスタ 102 は、エンハンスマント型であることが望ましい。

【0143】

また、発光素子に接続されているトランジスタを常時オフにする別の例として、P チャネル型の駆動用のトランジスタ 102 のゲートに、ソースよりも高い電位を与えるようにしてもよい。すなわち、駆動用のトランジスタ 102 のゲート配線と、高電位電源に接続された電源線 105 の電位よりも高い電位を与える配線とを短絡させることによってもよい。この方法に関する具体例を説明する。

【0144】

本実施の形態ではスイッチング用トランジスタ 103 が P チャネル型であるため、スイッチング用トランジスタ 103 のゲートに接続されているゲート信号線 107 には、通常スイッチング用トランジスタ 103 をオフにすべく H i の信号が与えられている。したが

10

20

30

40

50

って、ゲート信号線 107 に通常与えられている電位を、電源線 105 の電位よりも高い電位に設定し、ゲート信号線 107 と駆動用のトランジスタ 102 のゲート配線とを短絡させることにより、駆動用のトランジスタ 102 を強制的にオフにさせることができる。

#### 【0145】

なお、短絡させる方法については、公知の方法を用いればよい。例えば、ゲート信号線 107 と駆動用のトランジスタ 102 のゲート配線とが絶縁膜を介して上下に重なっている箇所に対して任意の波長のレーザー光を照射する。レーザー光の照射により、当該照射領域における絶縁膜は破壊され、照射領域周辺においてゲート信号線 107 と駆動用のトランジスタ 102 のゲート配線とを接続することができる。なお、レーザーの種類や、エネルギー密度、パルス幅といった照射条件についても特に限定されるものではない。また、レーザー光の発振方式は、パルス発振方式でもよいし、連続発振方式でもよい。また、レーザー光は、発光素子が設けられている側（基板上面側）から照射してもよいし、その逆側（基板下面側）から照射してもよい。ただし、レーザー光を上面側から照射するときは、陰極 108 を透過させる必要があるので、下面側から照射することが望ましい。

10

#### 【0146】

なお、実施の形態 1 で説明した図 12～15 のように、電源線と陽極との間に駆動用のトランジスタ 102 以外のトランジスタが配置されている場合もある。この場合も、本実施の形態で説明した方法を用い、電源線と陽極との間に接続されたトランジスタの少なくとも一つが常にオフするようにし、発光素子の一方の電極に電流が流れ込まないようにすればよい。

20

#### 【0147】

また、本実施の形態では駆動用のトランジスタ 102 が P チャネル型の場合について説明したが、本方法は駆動用のトランジスタ 102 が N チャネル型の場合にも適用することが可能である。

#### 【0148】

また、本実施の形態ではスイッチング用トランジスタ 103 が P チャネル型の場合について説明したが、本方法はスイッチング用トランジスタ 103 が N チャネル型の場合にも適用することが可能である。

#### 【0149】

#### （実施の形態 6）

30

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の構成について説明する。

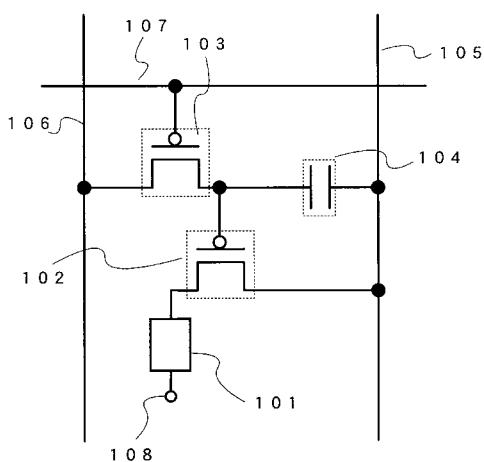

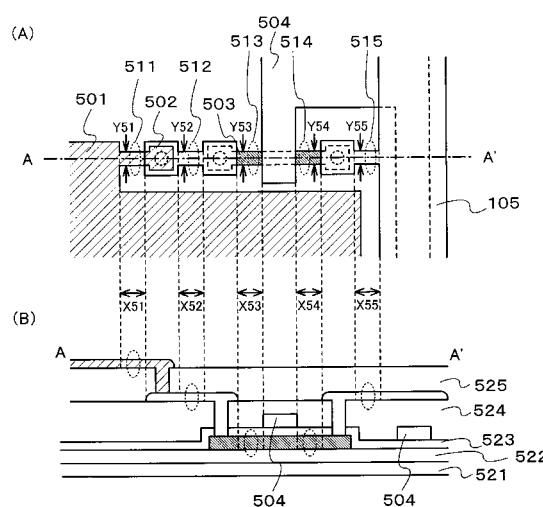

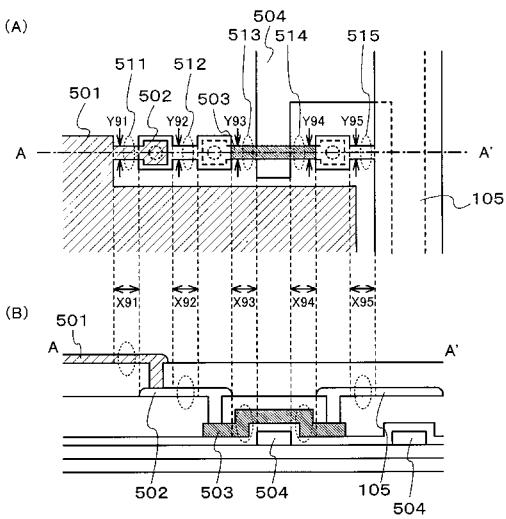

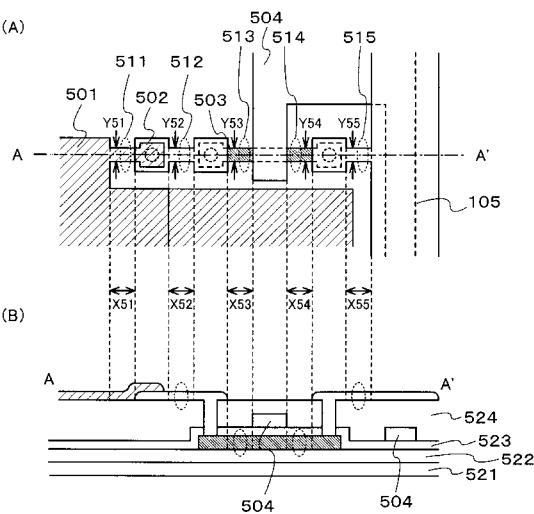

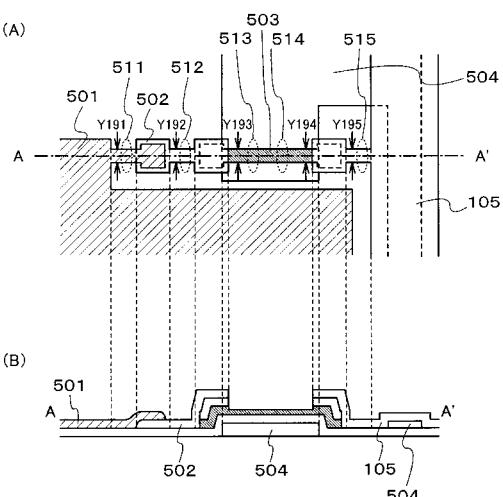

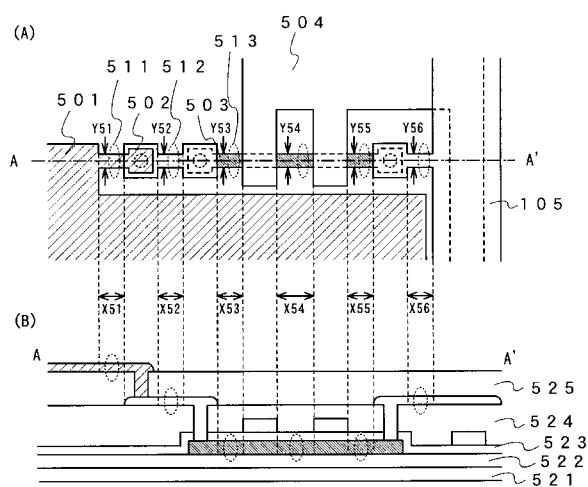

#### 【0150】

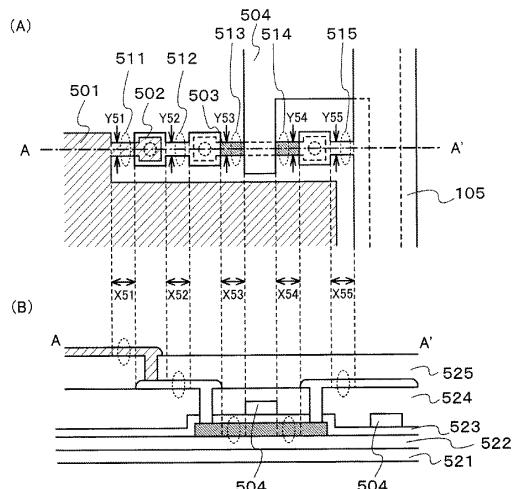

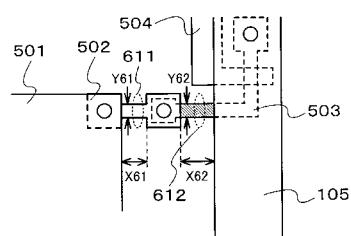

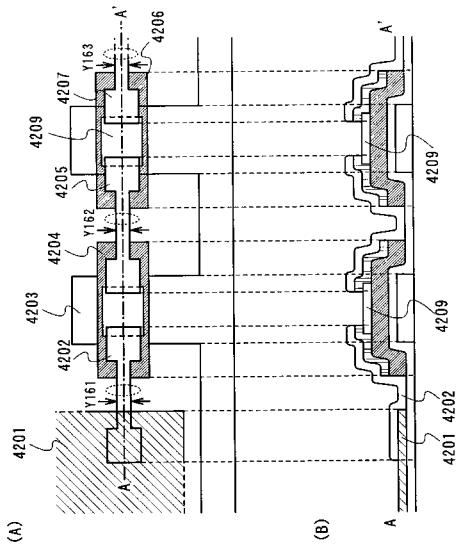

図 17 に、1 画素分のレイアウトの一例を示す。また、図 17 において波線で示した部分の拡大図を図 5 (A) に示す。また、図 5 (B) は、図 5 (A) において、A-A' 方向に切断したときの断面図である。なお、本画素構成の等価回路は、図 1 に対応している。

40

#### 【0151】

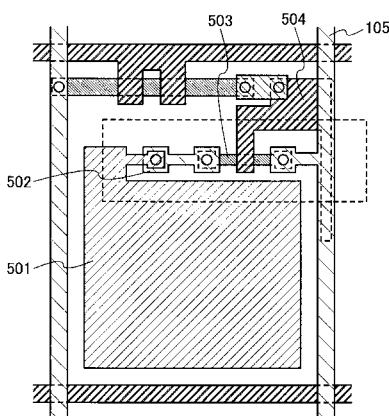

図 5 (A)、図 5 (B) において、501 は発光素子の一方の電極（陽極）、502 は配線、503 は駆動用のトランジスタ 102 の活性層、504 は駆動用のトランジスタ 102 のゲート電極も兼ねるゲート配線、521 は基板、522 は下地膜、523 は駆動用のトランジスタ 102 のゲート絶縁膜、524 は層間絶縁膜、525 は層間絶縁膜を示している。なお、これらを構成する材料は公知のものを用いればよく、具体例を以下に説明するが、以下に説明する具体例に限定されるものではない。

#### 【0152】

基板 521 は、バリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板、プラスチック等の可撓性を有する合成樹脂からなる基板等を用いることができる。

#### 【0153】

下地膜 522 は、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜のいずれ

50

かーを用いる単層構造としてもよいし、これらを適宜積層する構造としてもよい。例えば、下地膜として、基板 521 上に窒化酸化珪素膜、酸化窒化珪素膜を順に積層する構成とすればよい。この場合、下地膜が透明となり、レーザー光を透過させることが出来る。したがって、下地膜上に形成される配線または半導体層のみカットしたり配線間などをショートさせることができる。なお、本明細書中において、酸化窒化珪素とは酸素の組成比が窒素の組成比より大きい物質のことを指し、窒素を含む酸化珪素ということもできる。また、本明細書中において、窒化酸化珪素とは窒素の組成比が酸素の組成比より大きい物質のことを指し、酸素を含む窒化珪素ということもできる。

#### 【0154】

活性層 503 は、非晶質半導体膜、微結晶半導体膜、結晶性半導体膜などを用いることができる。また、半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム (SiGe) を用いるとよい。また、駆動用のトランジスタ 102 の活性層 503 は、ソース領域、ドレイン領域、及びチャネル形成領域を少なくとも有し、ソース領域、ドレイン領域には、p 型の導電型を付与する不純物が含まれている。また、活性層 503 はゲート電極に LDD 領域がオーバーラップしている構造や、ゲート電極に LDD 領域が重ならない構造、またはオフセット構造を有していてもよい。例えば、駆動用のトランジスタ 102 は N チャネル型、P チャネル型のいずれの場合でもゲート電極に LDD 領域がオーバーラップしている構造が好ましい。また、スイッチング用トランジスタ 103 は、N チャネル型、P チャネル型のいずれの場合でもゲート電極に LDD 領域が重ならない構造であることが好ましい。

10

20

#### 【0155】

ゲート絶縁膜 523 は、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜のいずれかーを用いる単層構造としてもよいし、これらを適宜積層する構造としてもよい。例えば、単層構造とする場合は酸化珪素膜を用い、積層構造とする場合は酸化窒化珪素膜窒化酸化珪素膜を順に積層する構成とすればよい。

#### 【0156】

ゲート配線 504 は、Al、Mo、Ti、Nd または W 等の金属若しくはその合金、またはその金属窒化物を使用することができ、これらの金属の単層構造としてもよいし、積層構造としてもよい。また、導電膜としてポリシリコン膜を用いてもよい。

30

#### 【0157】

層間絶縁膜 524 は、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜のいずれかーを用いる単層構造としてもよいし、これらを適宜積層する構造としてもよい。なお、ゲート配線 504 としてモリブデン (Mo) を用いているときは、ゲート配線 504 に接して層間絶縁膜 524 として窒化珪素膜を用いることが好ましい。

#### 【0158】

配線 502、電源線 105 は、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Zr、Ba、Nd 等の金属若しくはその合金、またはその金属窒化物を用いて形成する。また、Si、Ge などの半導体材料を用いることもできる。また、これらの積層構造としてもよい。なお、配線 502 や電源線 105 として低融点の金属材料を用いることは、配線 502 や電源線 105 を後にレーザー照射によってカットすることが容易になるため、本発明に最適である。

40

#### 【0159】

層間絶縁膜 525 は、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド (polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール (polybenzimidazole) などの耐熱性高分子、又はシロキサン系材料を出発材料として形成された珪素、酸素、水素からなる化合物のうち Si-O-Si 結合を含む無機シロキサン、珪素と結合された水素がメチル基やフェニル基のような有機基によって置換された有機シロキサン系の絶縁性材料を用いることができる。アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成してもよい。また、

50

これらの材料からなる層を積層させてもよい。また、図16に示すように、層間絶縁膜525を設けず、コンタクトホールを介さずに発光素子の一方の電極501と配線502とを直接接続する構成としてもよい。

【0160】

次に、本実施の形態における表示装置の構造について説明する。

【0161】

電源線105は、駆動用のトランジスタ102とコンタクトホールを介して接続するために、電源線は各画素（行）ごとに一部突出した形状を有している。また、電源線が一部突出している領域において、一部の幅が狭くなつた形状（図5における領域515の部分）を有している。この場合、領域515における電源線105の縦幅（Y55）を3μm以下にすることが好ましい。また、領域515における電源線105の横幅（X55）を4μm以上にすることが好ましい。このようにすることで、レーザーショットの断面（スポット）の形状や大きさとの関係から、欠陥を修復するのに必要な箇所のみカットすることができるため、電源線105自体が断線して他の画素に影響を与えることがない。また、他の配線がショートして他の回路に影響を与えることを防止することができる。

10

【0162】

このような形状の電源線105を有することにより、領域515にレーザーを照射して電源線105を容易に切断することができる。すなわち、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥のみを容易に修正することができる。

20

【0163】

また、駆動用のトランジスタ102の活性層503は、配線502やゲート配線504、電源線105に覆われていない領域513、514を有する。この領域513、514を、駆動用のトランジスタ102のチャネル幅方向に対して平行な方向の長さを小さくするようにしておき、領域513または領域514にレーザーを照射することによって、活性層503を切断するようにしてもよい。この場合、駆動用のトランジスタ102のチャネル幅方向に対して平行な方向の長さ（Y53、Y54）を3μm以下にすることが好ましい。また、駆動用のトランジスタ102のチャネル長方向に対して平行な方向の長さ（X53、X54）を4μm以上にすることが好ましい。

【0164】

また、活性層503と発光素子の一方の電極（陽極）501とを接続するための配線502において、配線502と活性層503とが接続されるコンタクトホールと、配線502と発光素子の一方の電極（陽極）501とが接続されるコンタクトホールとの間の配線502の一部の幅が狭くなるようにしてもよい。この場合、配線502の一部の縦幅（Y52）を3μm以下にすることが好ましい。また、配線502の一部の横幅（X52）を4μm以上にすることが好ましい。

30

【0165】

このような形状の配線502を有することにより、領域512にレーザーを照射して配線502を容易に切断することができる。すなわち、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥のみを容易に修正することができる。

40

【0166】

また、発光素子の一方の電極（陽極）501において、配線502と重なっている箇所に隣接する領域の幅を一部狭くなるようにしてもよい。この場合、発光素子の一方の電極（陽極）501の一部の縦幅（Y51）を3μm以下にすることが好ましい。また、発光素子の一方の電極（陽極）501の一部の横幅（X51）を4μm以上にすることが好ましい。

【0167】

このような形状の発光素子の一方の電極（陽極）501を有することにより、領域511にレーザーを照射して発光素子の一方の電極（陽極）501を容易に切断することができる。すなわち、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥のみを容易に修正することができる。

50

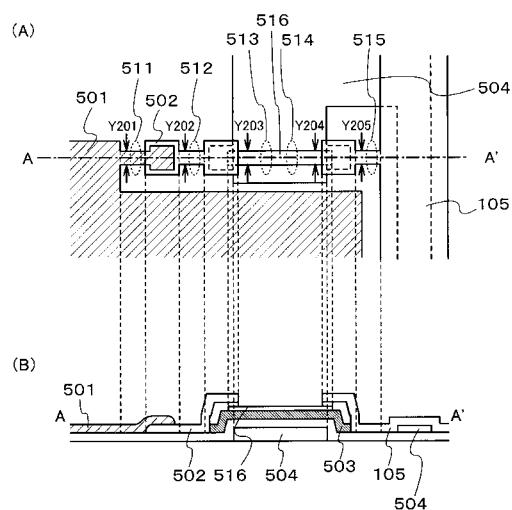

## 【0168】

また、図5ではゲート電極が半導体活性層に対して上部にある構成（トップゲート型）を示したが、図9に示すようなゲート電極が半導体活性層に対して下部にある構成の場合においても、レーザー照射により領域511～515の少なくともいずれか一を容易に切断することができる。

## 【0169】

また、アモルファスシリコンを半導体層に用いたボトムゲート構造のトランジスタを用いた構成の場合においても、本発明は適用することができる。例えば、図19に示すような逆スタガ型のチャネルエッチ構造のトランジスタ、図20に示すようなチャネル保護構造のトランジスタにおいても、レーザー照射により領域511～515の少なくともいずれか一を容易に切断することができる。なお、図20において、絶縁膜516がチャネルを保護する膜として機能している。

10

## 【0170】

## (実施の形態7)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

## 【0171】

図6に、1画素のレイアウトの上面図を示す。なお、本画素構成の等価回路は、図1に対応している。

20

## 【0172】

駆動用のトランジスタ102の活性層503は、配線502や電源線105に覆われていない領域612を有する。この領域612を、電源線105に対して平行な方向の長さを小さくするようにしておき、領域612にレーザーを照射することによって、活性層503を切断するようにしてもよい。この場合、電源線105に対して平行な方向の長さ(Y62)を3μm以下にすることが好ましい。また、電源線105に対して垂直な方向の長さ(X62)を4μm以上にすることが好ましい。このようにすることで、レーザーショットの断面(スポット)の形状や大きさとの関係から、欠陥を修復するのに必要な箇所のみカットすることができるため、領域612に隣接している電源線105自体が断線して他の画素に影響を与えることがない。また、他の配線がショートして他の回路に影響を与えることを防止することもできる。

30

## 【0173】

また、活性層503と発光素子の一方の電極(陽極)501とを接続するための配線502において、配線502と活性層503とが接続されるコンタクトホールと、配線502と発光素子の一方の電極(陽極)501とが接続されるコンタクトホールとの間の配線502の一部の幅が狭くなるようにしてもよい。この場合、配線502の一部の縦幅(Y61)を3μm以下にすることが好ましい。また、配線502の一部の横幅(X61)を4μm以上にすることが好ましい。

## 【0174】

このような形状の配線502を有することにより、領域611にレーザーを照射して配線502を容易に切断することができる。すなわち、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥のみを容易に修正することができる。

40

## 【0175】

## (実施の形態8)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

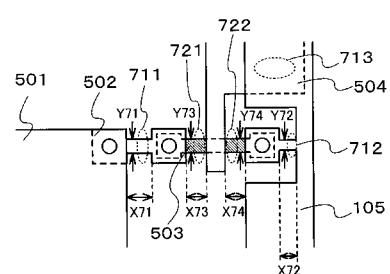

## 【0176】

図7に、1画素のレイアウトの上面図を示す。なお、本画素構成の等価回路は、図1に対応しており、駆動用のトランジスタ102はPチャネル型であるものとする。また、駆動用のトランジスタ102は、電源線105と接続されている側がソースであり、発光素子の一方の電極(陽極)501に接続されている側がドレインであるものとする。

50

## 【0177】

電源線 105 は、概略直線形状であるが、各画素（行）ごとに対応して、凹部を有している。さらに、この凹部の箇所には、活性層 503 に接続するために一部突出した領域を有し、且つ、前記突出した領域の一部の幅が狭くなつた形状を有している。この場合、領域 712 における電源線 105 の縦幅 (Y72) を 3 μm 以下にすることが好ましい。また、領域 712 における電源線 105 の横幅 (X72) を 4 μm 以上にすることが好ましい。

## 【0178】

このような形状の電源線 105 を有することにより、領域 712 にレーザーを照射して電源線 105 を容易に切断することができる。すなわち、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥のみを容易に修正することができる。なお、図 5 に示した構造では、電源線 105 の一部が突出しているためにレイアウト面積が大きくなり開口率が犠牲になつてしまつが、図 7 に示した構造のように電源線に凸部が設けられていることにより、開口率を犠牲にせずに配線 502 を容易に切断する構成を得ることができる。

10

## 【0179】

また、ゲート配線 504 は、層間絶縁膜を介して電源線 105 と重なつてゐる。この重なつてゐる領域の一部、例えば領域 713 に対してレーザーを照射することにより、ゲート配線 504 と電源線 105 とを短絡させてもよい。すなわち、ゲート配線 504 と、電源線 105 とを短絡させることによって駆動用のトランジスタ 102 のゲートとソースが同電位になるため、駆動用のトランジスタ 102 はオフになり、発光素子がショートしても電流が流れず、画素不良の欠陥を容易に修正することができる。

20

## 【0180】

また、駆動用のトランジスタ 102 の活性層 503 は、配線 502 やゲート配線 504 、電源線 105 に覆われてない領域 721、722 を有する。この領域 721、722 を、駆動用のトランジスタ 102 のチャネル幅方向に対して平行な方向の長さを小さくするようにしておき、領域 721 または領域 722 にレーザーを照射することによって、活性層 503 を切断するようにしてもよい。この場合、駆動用のトランジスタ 102 のチャネル幅方向に対して平行な方向の長さ (Y73、Y74) を 3 μm 以下にすることが好ましい。また、駆動用のトランジスタ 102 のチャネル長方向に対して平行な方向の長さ (X73、X74) を 4 μm 以上にすることが好ましい。

30

## 【0181】

また、活性層 503 と発光素子の一方の電極（陽極）501 とを接続するための配線 502 において、配線 502 と活性層 503 とが接続されるコンタクトホールと、配線 502 と発光素子の一方の電極（陽極）501 とが接続されるコンタクトホールとの間の配線 502 の一部の幅が狭くなるようにしてもよい。この場合、配線 502 の一部の縦幅 (Y71) を 3 μm 以下にすることが好ましい。また、配線 502 の一部の横幅 (X71) を 4 μm 以上にすることが好ましい。

## 【0182】

このような形状の配線 502 を有することにより、領域 711 にレーザーを照射して配線 502 を容易に切断することができる。すなわち、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥のみを容易に修正することができる。

40

## 【0183】

## (実施の形態 9)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

## 【0184】

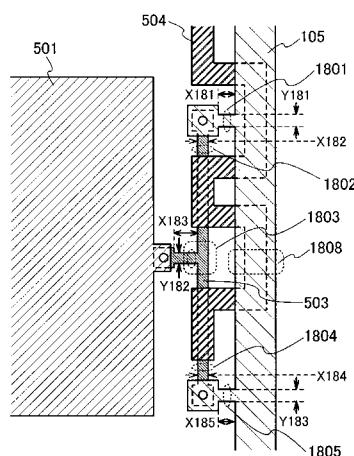

図 18 に、1 画素のレイアウトの上面図を示す。なお、本画素構成の等価回路は、図 13 において配線 1351 と配線 1352 とが同じ電源に接続されている場合に対応しており、発光素子の一方の電極 501 は、互いに並列に接続された第 1 のトランジスタと第 2

50

のトランジスタを介して電源線 105 に接続されている。

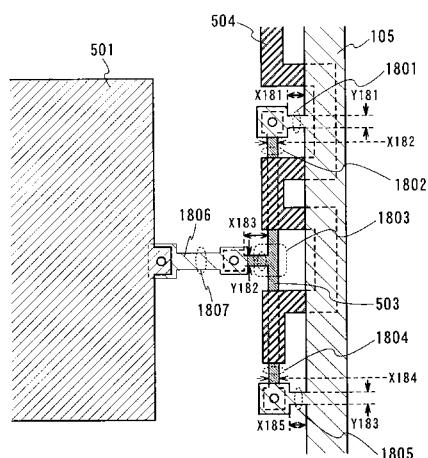

【0185】

電源線 105 は、概略直線形状であるが、各画素（行）ごとに対応して、凸部を 2箇所所有している。この凸部は、一部の幅が狭くなつた形状を有している。この場合、領域 1801 及び領域 1805 における電源線 105 の縦幅（Y）を  $3 \mu m$  以下にすることが好ましい。また、領域 712 における電源線 105 の横幅（X）を  $4 \mu m$  以上にすることが好ましい。

【0186】

このような形状の電源線 105 を有することにより、領域 1801 及び領域 1805 にレーザーを照射して電源線 105 を容易に切断することができる。すなわち、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥のみを容易に修正することができる。

10

【0187】

また、ゲート配線 504 は、層間絶縁膜を介して電源線 105 と重なつてはいる。このため、第 1 のトランジスタ及び第 2 のトランジスタが P チャネル型で、且つ、発光素子の一方の電極 501 が陽極の場合、または、第 1 のトランジスタ及び第 2 のトランジスタが N チャネル型で、且つ、発光素子の一方の電極 501 が陰極の場合、ゲート配線 504 と電源線 105 とが重なつてはいる領域の一部、例えば領域 1808 に対してレーザーを照射することにより、ゲート配線 504 と電源線 105 とを短絡させてもよい。すなわち、ゲート配線 504 と、電源線 105 とを短絡させることによって第 1 のトランジスタ及び第 2 のトランジスタのゲートとソースが同電位になるため、各トランジスタはオフになり、発光素子がショートしても電流が流れず、画素不良の欠陥を容易に修正することができる。

20

【0188】

また、第 1 及び第 2 のトランジスタの活性層 503 に対して、領域 1802 及び領域 1804 の双方に対してレーザー照射を行い、活性層をカットするようにしてよい。また、領域 1803 に対してレーザー照射を行えば、照射箇所が 1 箇所でよいため、歩留まり向上の点で好ましい。なお、領域 1802 及び領域 1804 の横幅（X）は  $3 \mu m$  以下にし、

30

縦幅（Y）を  $4 \mu m$  以上にすることが好ましい。

【0189】

このような形状の活性層 503 を有することにより、領域 1802 及び領域 1804 の双方、または領域 1803 にレーザーを照射して活性層 503 を容易に切断することができる。すなわち、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥のみを容易に修正することができる。

40

【0190】

なお、図 18 においては、発光素子の一方の電極 501 と第 1 及び第 2 のトランジスタの活性層 503 とが直接接続されているが、図 35 に示すように、発光素子の一方の電極 501 と第 1 及び第 2 のトランジスタの活性層 503 との間に配線 1806 が設けられていてよい。このとき、配線 1806 は、電源線 105 を形成する際に同時に作製することができる。また、配線 1806 は、欠陥画素が生じたときに簡便に修正することができる構造とする。すなわち、配線 1806 は、発光素子の一方の電極 501 と配線 1806 とが接続される領域と、配線 1806 と第 1 及び第 2 のトランジスタの活性層 503 とが接続される領域との間における配線 1806 の一部の幅が細くなつた構造としている。配線 1806 が一部細くなつてはいる領域 1807 の幅は  $3 \mu m$  以下にすることが好ましい。

【0191】

（実施の形態 10）

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

【0192】

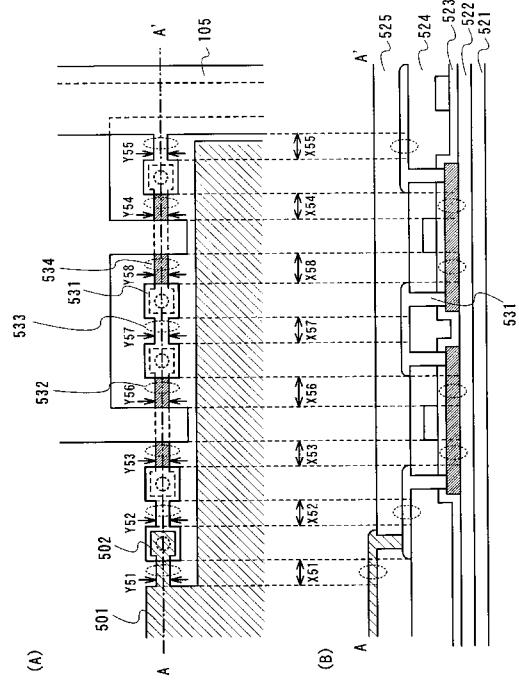

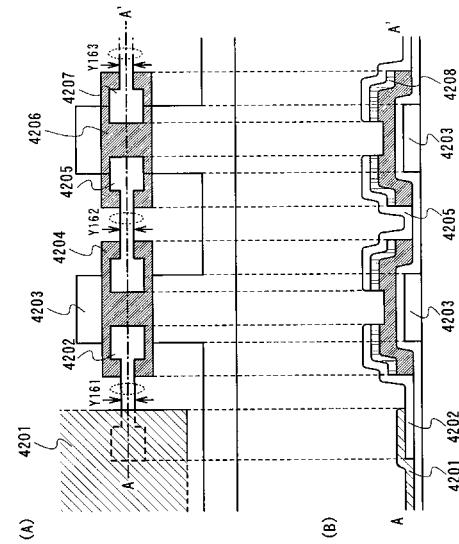

図 36（A）に表示装置の画素部における 1 画素の一部に相当するレイアウトを示す。

50

図36(A)は、画素電極(発光素子の有する一対の電極のうちの一方の電極)と電源線との接続関係を示す上面図であり、図36(B)は、図36(A)においてA-A'方向に切断したときの断面図である。また、図36(A)に示す上面図を等価回路に表すと、図12に相当する。すなわち、図36(A)、図36(B)は、画素電極(発光素子の有する一対の電極のうちの一方の電極)と電源線との間に、直列に接続された2つのトランジスタを有する構成を示している。

【0193】

図36(A)は、実施の形態6で説明した図5(A)におけるゲート配線504と駆動用のトランジスタの活性層503との重なりが1つであるのに対し、2つである点で異なるが、それ以外の構成については同じである。このため、本実施の形態では図5との違いに関してのみ説明する。本実施の形態では、上面から見て2つのゲート配線との間に挟まれた活性層503の領域の幅Y54を狭く(細く)した形状としている。この活性層503の領域の幅は、3μm以下とすることが好ましい。

10

【0194】

このような形状の活性層503を有する表示装置は、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥を容易に修正することができる。

【0195】

(実施の形態11)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

20

【0196】

図37(A)に表示装置の画素部における1画素の一部に相当するレイアウトを示す。図37(A)は、画素電極(発光素子の有する一対の電極のうちの一方の電極)と電源線との接続関係を示す上面図であり、図37(B)は、図37(A)においてA-A'方向に切断したときの断面図である。また、図37(A)に示す上面図を等価回路に表すと、図12に相当し、図36(A)と同様に、画素電極(発光素子の有する一対の電極のうちの一方の電極)と電源線との間に、直列に接続された2つのトランジスタを有する構成を示している。

【0197】

図37(A)は、実施の形態10で説明した図36(A)における活性層503が2つに分割され、当該二つの活性層が配線531を介して接続された構成となっている点で図36(A)と異なるが、それ以外の構成については同じである。このため、本実施の形態では図36(A)との違いに関してのみ説明する。本実施の形態では、上面から見て2つのゲート配線との間に挟まれ、且つ配線531と重ならない活性層503の領域の幅Y56、Y58を狭く(細く)した形状としている。この活性層503の領域の幅は、3μm以下とすることが好ましい。また、この活性層503の領域の幅Y56、Y58は、共に狭くした形状としてもよいし、どちらか一方でもよい。

30

【0198】

また、活性層503の領域の幅の少なくとも一部を狭く(細く)する形状とする代わりに、上面から見て2つの活性層と重ならない配線531の領域の幅を狭く(細く)した形状としてもよい。この配線531の領域の幅Y57は、3μm以下とすることが好ましい。

40

【0199】

上述したような形状の活性層503または配線531を有する表示装置は、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥を容易に修正することができる。

【0200】

(実施の形態12)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

50

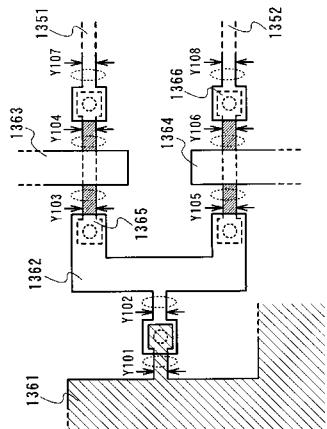

## 【0201】

図38に表示装置の画素部における1画素の一部に相当するレイアウトを示す。図38は、画素電極と電源線との接続関係を示す上面図である。また、図38(A)に示す上面図を等価回路に表すと、図13に相当し、画素電極(発光素子の有する一対の電極のうちの一方の電極)と電源線との間において、発光素子の一方の電極に接続された2つのトランジスタを少なくとも有する構成を示している。

## 【0202】

活性層1365を有するトランジスタ1304のソースまたはドレインの一方及び活性層1366を有するトランジスタ1305のソースまたはドレインの一方は、配線1362を介して互いに接続されている。また、配線1362は発光素子101の一方の電極1361(画素電極)に接続されている。また、トランジスタ1304のソースまたはドレインの他方は、配線1351に接続され、トランジスタ1305のソースまたはドレインの他方は、配線1352に接続されている。

10

## 【0203】

本実施の形態では、上面から見て配線1362、ゲート配線1363、及び配線1351と重ならない活性層1365の領域の幅Y103、Y104、または活性層1365と重ならない配線1351の幅Y107を狭く(細く)した形状としている。このとき、活性層1365の領域の幅Y103、Y104、または配線1351の幅Y107は、3μm以下とすることが好ましい。また、この幅Y103、Y104、Y107は、これら全ての幅を狭くした形状としてもよいが、少なくとも一つが上記形状となつていればよい。

20

## 【0204】

また、本実施の形態では、上面から見て配線1362、ゲート配線1364、及び配線1352と重ならない活性層1366の領域の幅Y105、Y106、または活性層1366と重ならない配線1352の幅Y108を狭く(細く)した形状としている。このとき、活性層503の領域の幅Y105、Y106、または活性層1366と重ならない配線1352の幅Y108は、3μm以下とすることが好ましい。また、この幅Y105、Y106、Y108は、これら全ての幅を狭くした形状としてもよいが、少なくとも一つが上記形状となつていればよい。

20

## 【0205】

また、幅Y103、Y104、Y107、及び幅Y105、Y106、Y108と共に狭く(細く)する形状とする代わりに、上面から見て発光素子101の一方の電極1361と配線1362とが重ならない領域の近傍における配線1362の幅Y102または発光素子101の一方の電極1361の幅Y101を狭く(細く)した形状としてもよい。欠陥画素を修復する際に、前者の構成より後者の構成を採用することにより、配線などを切断する箇所が1箇所でよいため好ましい。また、この配線1362の幅Y102または発光素子101の一方の電極1361の幅Y101は、3μm以下とすることが好ましい。

30

## 【0206】

上述したような形態の発光素子101の一方の電極1361、配線1362、活性層1365、活性層1366、配線1351、配線1352を有する表示装置は、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥を容易に修正することができる。

40

## 【0207】

## (実施の形態13)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

## 【0208】

図39に表示装置の画素部における1画素の一部に相当するレイアウトを示す。図39は、画素電極(発光素子の有する一対の電極のうちの一方の電極)と電源線との接続関係を示す上面図である。また、図39に示す上面図を等価回路に表すと、図13に相当し、

50

図38と同様に、発光素子の一方の電極に接続された2つのトランジスタを有する構成を示している。

【0209】

図39は、実施の形態10で説明した図38における2つの活性層1365、1366が一つの活性層1372に置換された構成となっている点で図38と異なるが、それ以外の構成については同じである。このため、本実施の形態では図38との違いに関してのみ説明する。本実施の形態では、幅Y113、Y114、及び幅Y115、Y116と共に狭く(細く)する形状とすればよい。また、この構成の代わりに、幅Y111またはY112を狭く(細く)した形状としてもよい。欠陥画素を修復する際に、前者の構成より後者の構成を採用することにより、配線などを切断する箇所が1箇所でよいため好ましい。また、幅Y103、Y104、Y107、及び幅Y105、Y106、Y108は、それぞれ3μm以下とすることが好ましい。

10

【0210】

上述したような形状の発光素子101の一方の電極1361、配線1371、活性層1372、配線1351、配線1352を有する表示装置は、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥を容易に修正することができる。

【0211】

(実施の形態14)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

20

【0212】

図40に表示装置の画素部における1画素の一部に相当するレイアウトを示す。図40は、画素電極と電源線との接続関係を示す上面図である。また、図40に示す上面図を等価回路に表すと、図14に相当し、画素電極と電源線との間において、発光素子の一方の電極に接続されたトランジスタ1405と、当該トランジスタと接続された2つのトランジスタ1406、1407とを少なくとも有する構成を示している。

30

【0213】

図40は、活性層1468を有するトランジスタ1406のソースまたはドレインの一方及び活性層1469を有するトランジスタ1407のソースまたはドレインの一方が配線1465を介して互いに接続されている。また、配線1465は、活性層1464を有するトランジスタ1405のソースまたはドレインの一方に接続されている。また、トランジスタ1405のソースまたはドレインの他方は、配線1462を介して発光素子101の一方の電極1461(画素電極)に接続されている。また、トランジスタ1406のソースまたはドレインの他方は、配線1451に接続され、トランジスタ1407のソースまたはドレインの他方は、配線1452に接続されている。

30

【0214】

本実施の形態では、実施の形態13で図39を用いて説明したように、幅Y126、Y127、Y128の少なくとも一つ、及び幅Y129、Y130、Y131の少なくとも一つを狭く(細く)した形状としている。このとき、幅Y126、Y127、Y128の少なくとも一つ、及び幅Y129、Y130、Y131の少なくとも一つは、3μm以下とすることが好ましい。

40

【0215】

また、幅Y126、Y127、Y128の少なくとも一つ、及び幅Y129、Y130、Y131の少なくとも一つを狭く(細く)する形状とする代わりに、幅Y121、Y122、Y123、Y124、Y125の少なくとも一つを狭く(細く)した形状としてもよい。欠陥画素を修復する際に、前者の構成より後者の構成を採用することにより、配線などを切断する箇所が1箇所でよいため好ましい。また、このとき幅Y121、Y122、Y123、Y124、Y125は、3μm以下とすることが好ましい。

【0216】

上述したような形状の発光素子101の一方の電極1461、配線1462、活性層1

50

464、配線1465、活性層1468、活性層1469、配線1451、配線1452を有する表示装置は、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥を容易に修正することができる。

【0217】

(実施の形態15)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

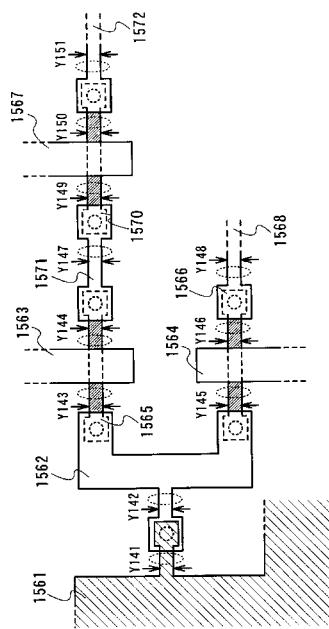

【0218】

図41に表示装置の画素部における1画素の一部に相当するレイアウトを示す。図41は、画素電極と電源線との接続関係を示す上面図である。また、図41に示す上面図を等価回路に表すと、図15に相当し、画素電極と電源線との間にいて、直列に接続されたトランジスタ1506、1507と、トランジスタ1508とが発光素子の一方の電極に接続された構成を示している。

【0219】

発光素子の一方の電極1561は、配線1562を介してトランジスタ1506の活性層1565(ソースまたはドレインの一方)及びトランジスタ1508の活性層1566(ソースまたはドレインの一方)に接続されている。また、トランジスタ1506のソースまたはドレインの他方は、配線1571を介してトランジスタ1507の活性層1570(ソースまたはドレインの一方)に接続されている。また、トランジスタ1507のソースまたはドレインの他方は、配線1572に接続されている。また、トランジスタ1508のソースまたはドレインの他方は、配線1568に接続されている。

【0220】

本実施の形態では、幅Y143、Y144、Y147、Y149、Y150、Y151の少なくとも一つ、及び幅Y145、Y146、Y148の少なくとも一つを狭く(細く)した形状としている。このとき、幅Y143、Y144、Y147、Y149、Y150、Y151の少なくとも一つ、及び幅Y145、Y146、Y148の少なくとも一つは、3μm以下とすることが好ましい。

【0221】

また、幅Y143、Y144、Y147、Y149、Y150、Y151の少なくとも一つ、及び幅Y145、Y146、Y148の少なくとも一つを狭く(細く)する形状とする代わりに、幅Y141、Y142の少なくとも一つを狭く(細く)した形状としてもよい。欠陥画素を修復する際に、前者の構成より後者の構成を採用することにより、配線などを切断する箇所が1箇所でよいため好ましい。また、このとき幅Y141、Y142は、3μm以下とすることが好ましい。

【0222】

上述したような形状の発光素子101の一方の電極1561、配線1562、活性層1565、活性層1566、配線1567、配線1568、活性層1570、配線1571を有する表示装置は、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥を容易に修正することができる。

【0223】

(実施の形態16)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

【0224】

図42(A)に表示装置の画素部における1画素の一部に相当するレイアウトを示す。図42(A)は、画素電極(発光素子の有する一対の電極のうちの一方の電極)と電源線との接続関係を示す上面図であり、図42(B)は、図42(A)においてA-A'方向に切断したときの断面図である。また、図42(A)に示す上面図を等価回路に表すと図12に相当し、図36(A)、図37(A)と同様に、画素電極(発光素子の有する一対の電極のうちの一方の電極)と電源線との間に、直列に接続された2つのトランジスタを

10

20

30

40

50

少なくとも有する構成を示している。

【0225】

画素電極4201は、配線4202を介して、活性層4204を有するトランジスタ1204のソースまたはドレインの一方に接続されている。また、トランジスタ1204のソースまたはドレインの他方は、配線4205を介して活性層4206を有するトランジスタ1205のソースまたはドレインの一方に接続されている。また、トランジスタ1205のソースまたはドレインの他方は、配線4207に接続されている。なお、図42(B)において、4208は13族元素(または15族元素)を含有する半導体膜を示しており、図42(A)においては配線4202、配線4205、配線4207の下に配置されているため、図示されない。また、ゲート配線4203の下には基板が存在するが、本図面では図示していない。

10

【0226】

本実施の形態では、上面から見て、画素電極4201及び活性層4204と重ならない配線4202の領域の幅Y161を狭く(細く)した形状としている。この幅Y161は、3μm以下とすることが好ましい。

【0227】

また、幅Y161を狭く(細く)する形状とする代わりに、活性層4204及び活性層4206と重ならない配線4205の領域の幅Y162を狭く(細く)した形状としてもよい。この幅Y162は、3μm以下とすることが好ましい。また、幅Y161、Y162を狭く(細く)する形状とする代わりに、活性層4206と重ならない配線4207との幅Y163を狭く(細く)した形状としてもよい。この幅Y163は、3μm以下とすることが好ましい。なお、幅Y161、Y162、Y163は、共に狭くした形状としてもよいが、少なくともいずれか一つを狭く(細く)した形状とすればよい。

20

【0228】

上述したような形状の配線4202、配線4205、または配線4207を有する表示装置は、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥を容易に修正することができる。

【0229】

(実施の形態17)

本実施の形態では、欠陥画素を簡便に修復できる表示装置の画素部の別の構成について説明する。

30

【0230】

図43(A)に表示装置の画素部における1画素の一部に相当するレイアウトを示す。図43(A)は、画素電極(発光素子の有する一对の電極のうちの一方の電極)と電源線との接続関係を示す上面図であり、図43(B)は、図43(A)においてA-A'方向に切断したときの断面図である。また、図43(A)に示す上面図を等価回路に表すと図12に相当し、図42(A)と同様に、画素電極(発光素子の有する一对の電極のうちの一方の電極)と電源線との間に、直列に接続された2つのトランジスタを少なくとも有する構成を示している。

40

【0231】

実施の形態16で説明した図42(A)においては、13族元素(または15族元素)を含有する半導体膜4208と重ならない領域の活性層(チャネル形成領域に相当する)が一部エッチングされており、配線4202の上に重なるように画素電極4201が設けられた構造である。これに対し、図43(A)は、チャネル形成領域と重ならない領域の活性層の上を覆うように保護膜4209が設けられており、画素電極4201の上に重なるように配線4202が設けられた構造であり、この点で図42(A)と相違するが、それ以外の構成については同じである。すなわち、本実施の形態では、上面から見て、配線4202の幅Y161、配線4205の幅Y162、または配線4207の幅Y163の少なくともいずれか一つを狭く(細く)した形状とすればよい。この幅Y161、Y162、Y163は、3μm以下とすることが好ましい。なお、幅Y161、Y162、Y1

50

63は、共に狭くした形状としてもよい。

【0232】

上述したような形状の配線4202、配線4205、または配線4207を有する表示装置は、どの画素において欠陥画素が生じても、他の画素に影響を与えることなく欠陥を容易に修正することができる。

【実施例1】

【0233】

本実施例では、欠陥画素を簡便に修復することが可能な表示装置の構成について説明する。なお、実施の形態2においては、図1を用いて1画素の構成例を説明したので、本実施例では図1とは違う構造を有する画素の構成例について説明する。

10

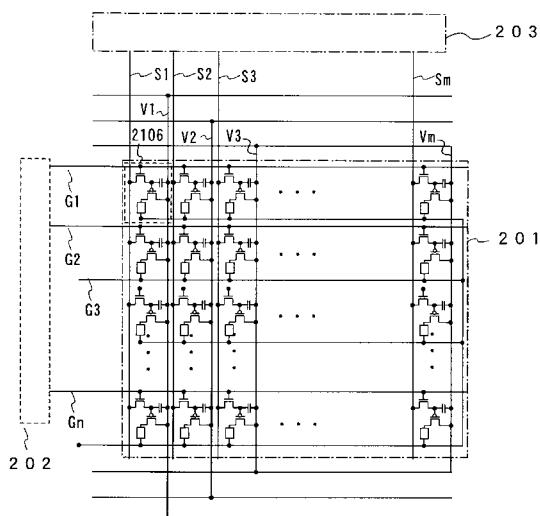

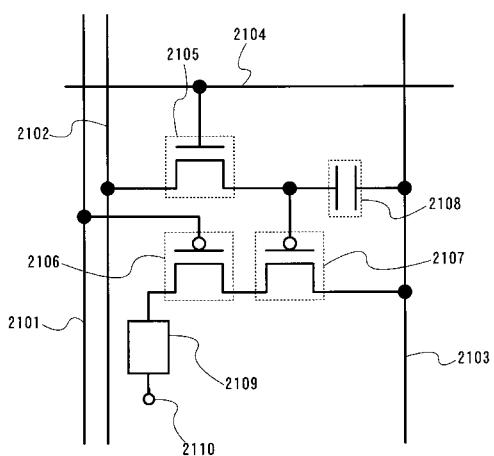

【0234】

図21に表示装置の画素部における1画素分の等価回路図の一例を示す。各画素には、第1のトランジスタ2105、第2のトランジスタ2106、第3のトランジスタ2107、コンデンサ2108、発光素子2109、発光素子2109の一方の電極2110が設けられている。発光素子2109の一方の電極2110は、陽極であってもよいし、陰極であってもよい。

【0235】

第1のトランジスタ2105は、ゲート電極がゲート信号線2104（走査線）に接続され、ソース領域またはドレイン領域の一方が第1のソース信号線2102（データ線）に、他方が第3のトランジスタ2107のゲート電極及びコンデンサ2108の一方の電極にそれぞれ接続されている。また、第2のトランジスタ2106は、ゲート電極が第2のソース信号線2101に接続され、ソース領域またはドレイン領域の一方が発光素子2109の他方の電極に、他方が第3のトランジスタ2107のソース領域またはドレイン領域の一方にそれぞれ接続されている。また、第3のトランジスタ2107は、ソース領域またはドレイン領域の他方が電源線2103に接続されている。また、コンデンサ2108の他方の電極は電源線2103に接続されている。

20

【0236】

コンデンサ2108は、第3のトランジスタ2107のゲート電位を保持する役目をしている。このため、図21においては、第3のトランジスタ2107のゲート電極と電源線2103との間にコンデンサ2108が接続されているが、この構成に限定されない。すなわち、第3のトランジスタ2107のゲート電位を保持できるようにコンデンサ2108は設けられていればよい。また、第3のトランジスタ2107のゲート容量などを用いて第3のトランジスタ2107のゲート電位を保持できる場合は、コンデンサ2108を設けない構成とすることもできる。

30

【0237】

なお、実施の形態2で説明したように、第1～第3のトランジスタ2105～2107は図21の構成に限定されるものではない。すなわち、第1～第3のトランジスタ2105～2107は、それぞれNチャネル型、Pチャネル型のどちらでもよい、また、各トランジスタの活性層は、それぞれ非晶質でもよいし、結晶性を有していてもよい。また、各トランジスタの活性層は、それぞれLDD構造を有していてもよいし、GOLD構造を有していてもよい。また、各トランジスタの構造は、それぞれ順スタガ型、逆スタガ型のどちらでもよい。また、各トランジスタの構造は、それぞれトップゲート型、ボトムゲート型のどちらでもよい。また、各トランジスタのゲート電極は、それぞれチャネル形成領域の上下の両方にあってもよいし、チャネル形成領域の上方または下方の一方に複数のゲート電極があってもよい。

40

【0238】

図21において本発明を実施するためには、発光素子2109の他方の電極（第2のトランジスタ2106のソース領域またはドレイン領域の一方に接続されている側の電極）と電源線2103との間ににおいて電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子2109の他方の電極と電源線2103との間ににおいて電流の流れる経

50

路は、上述した図12の構成と同じであるので、ここでは詳細な説明を省略する。

【0239】

また、本発明では、欠陥画素を簡便に修復することができるようするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

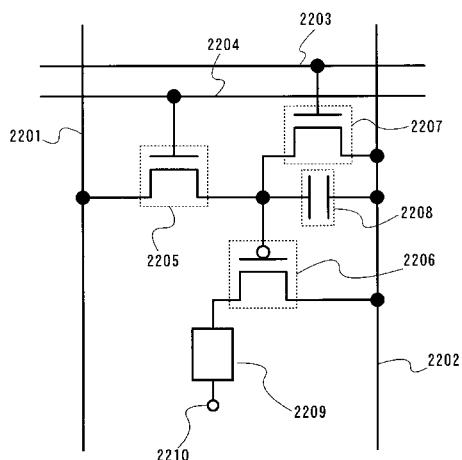

【0240】

次に、図22に表示装置の画素部における1画素分の等価回路図の別の一例を示す。各画素には、第1のトランジスタ2205、第2のトランジスタ2206、第3のトランジスタ2207、コンデンサ2208、発光素子2209、発光素子2209の一方の電極2210が設けられている。発光素子2209の一方の電極2210は、陽極であってもよいし、陰極であってもよい。

10

【0241】

第1のトランジスタ2205は、ゲート電極が第1のゲート信号線2204に接続され、ソース領域またはドレイン領域の一方が第1のソース信号線2201(データ線)に、他方が第2のトランジスタ2206のゲート電極、第3のトランジスタ2207のソース領域またはドレイン領域の一方、及びコンデンサ2208の一方の電極にそれぞれ接続されている。また、第2のトランジスタ2206は、ソース領域またはドレイン領域の一方が発光素子2209の他方の電極に、他方が電源線2202にそれぞれ接続されている。また、第3のトランジスタ2207は、ゲート電極が第2のゲート信号線2203に接続され、ソース領域またはドレイン領域の他方が電源線2202に接続されている。また、コンデンサ2208の他方の電極は電源線2202に接続されている。

20

【0242】

図22において本発明を実施するためには、発光素子2209の他方の電極(第2のトランジスタ2206のソース領域またはドレイン領域の一方に接続されている側の電極)と電源線2202との間ににおいて電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子2209の他方の電極と電源線2202との間ににおいて電流の流れる経路は、上述した図11の構成と同じであるので、ここでは詳細な説明を省略する。

30

【0243】

また、本発明では、欠陥画素を簡便に修復することができるようするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

40

【0244】

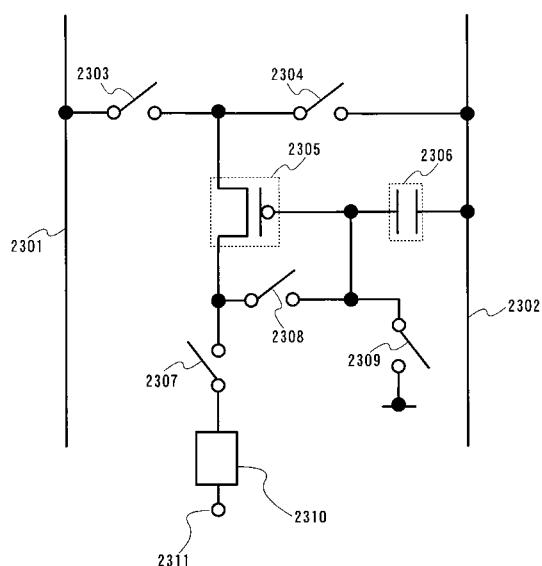

次に、図23に表示装置の画素部における1画素分の等価回路図の別の一例を示す。各画素には、第1のスイッチ2303、第2のスイッチ2304、トランジスタ2305、コンデンサ2306、第3のスイッチ2307、第4のスイッチ2308、第5のスイッチ2309、発光素子2310、発光素子2310の一方の電極2311が設けられている。発光素子2310の一方の電極2311は、陽極であってもよいし、陰極であってもよい。

50

【0245】

トランジスタ2305は、ゲート電極がコンデンサ2306の一方の電極、第4のスイッチ2308の一方の端子、及び第5のスイッチ2309の一方の端子に接続され、ソース領域またはドレイン領域の一方が第1のスイッチ2303の一方の端子、及び第2のスイッチ2304の一方の端子に、他方が第3のスイッチ2307の一方の端子、及び第4のスイッチ2308の他方の端子に接続されている。また、第1のスイッチ2303の他方の端子はソース信号線2301に接続され、第2のスイッチ2304の他方の端子は電源線2302に接続されている。また、コンデンサ2306の他方の電極は電源線2302に接続されている。また、第3のスイッチ2307の他方の端子は、発光素子2310の他方の電極に接続されている。

50

## 【0246】

図23において本発明を実施するためには、発光素子2310の他方の電極（第3のスイッチ2307の他方の端子に接続されている側の電極）と電源線2302との間において電流の流れる経路のうち、少なくとも一部を断線させればよい。

## 【0247】

また、本発明では、欠陥画素を簡便に修復することができるようとするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

## 【0248】

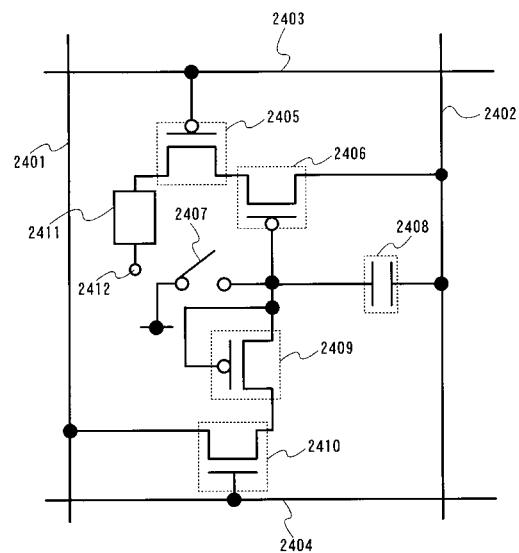

次に、図24に表示装置の画素部における1画素分の等価回路図の別の一例を示す。各画素には、第1のトランジスタ2405、第2のトランジスタ2406、スイッチ2407、コンデンサ2408、第3のトランジスタ2409、第4のトランジスタ2410、発光素子2411、発光素子2411の一方の電極2412が設けられている。発光素子2411の一方の電極2412は、陽極であってもよいし、陰極であってもよい。

10

## 【0249】

第1のトランジスタ2405は、ゲート電極が第1のゲート信号線2403に接続され、ソース領域またはドレイン領域の一方が発光素子2411の他方の電極に、他方が第2のトランジスタ2406のソース領域またはドレイン領域の一方に接続されている。また、第2のトランジスタ2406は、ゲート電極がスイッチ2407の一方の端子、コンデンサ2408の一方の電極、並びに第3のトランジスタ2409のソース領域またはドレイン領域の一方及びゲート電極に接続され、ソース領域またはドレイン領域の他方が電源線2402に接続されている。また、コンデンサ2408の他方の電極は、電源線2402に接続されている。また、第3のトランジスタ2409は、ソース領域またはドレイン領域の他方が第4のトランジスタ2410のソース領域またはドレイン領域の一方に接続されている。また、第4のトランジスタ2410は、ゲート電極が第2のゲート信号線2404に接続され、ソース領域またはドレイン領域の他方がソース信号線2401に接続されている。

20

## 【0250】

図24において本発明を実施するためには、発光素子2411の他方の電極と電源線2402との間において電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子2411の他方の電極と電源線2402との間において電流の流れる経路は、上述した図12の構成と同じであるので、ここでは詳細な説明を省略する。

30

## 【0251】

また、本発明では、欠陥画素を簡便に修復することができるようとするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

## 【0252】

次に、図25に表示装置の画素部における1画素分の等価回路図の別の一例を示す。図25に示す構成は、図24において設けられていたスイッチ2407の代わりに、第5のトランジスタ2413が設けられた構成となっている。

40

## 【0253】

第5のトランジスタ2413は、ゲート電極が当該第5のトランジスタ2413のソース領域またはドレイン領域の一方及び第4のトランジスタ2410のソース領域またはドレイン領域の一方に接続され、ソース領域またはドレイン領域の他方が第3のトランジスタ2409のソース領域またはドレイン領域の一方に接続されている。

## 【0254】

図25において本発明を実施するためには、発光素子2411の他方の電極と電源線2402との間において電流の流れる経路のうち、少なくとも一部を断線させればよい。発

50

光素子 2411 の他方の電極と電源線 2402 との間において電流の流れる経路は、上述した図 12 の構成と同じであるので、ここでは詳細な説明を省略する。

【0255】

また、本発明では、欠陥画素を簡便に修復することができるようにするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態 6 ~ 9 で説明した方法を用いればよいので、ここでは説明を省略する。

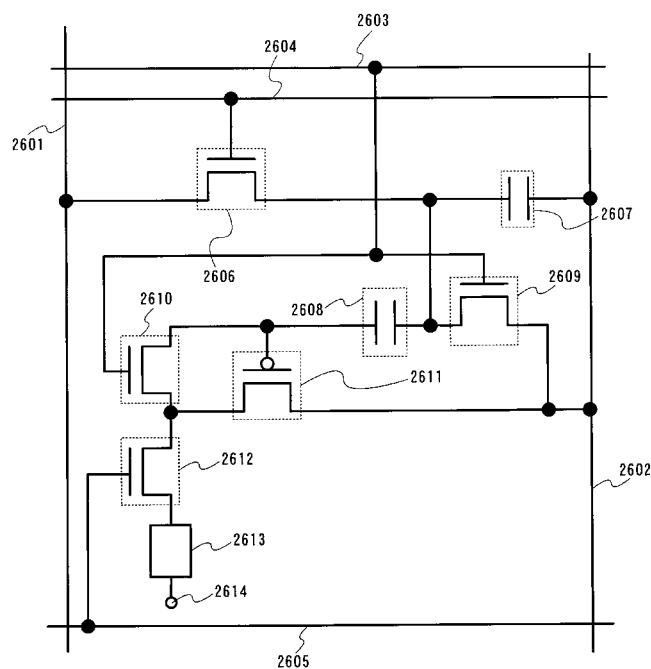

【0256】

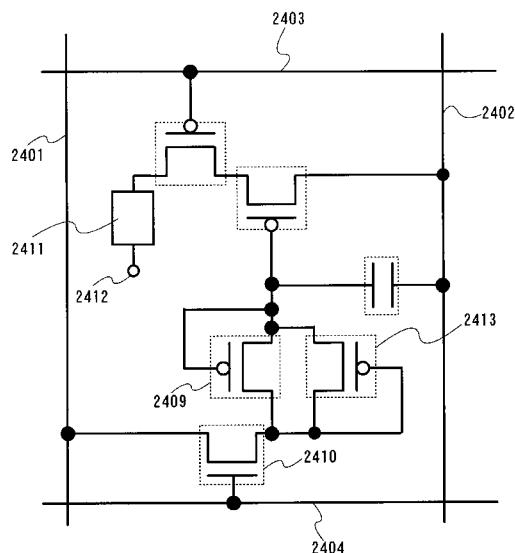

次に、図 26 に表示装置の画素部における 1 画素分の等価回路図の別の一例を示す。各画素には、第 1 のトランジスタ 2606、第 1 のコンデンサ 2607、第 2 のコンデンサ 2608、第 2 のトランジスタ 2609、第 3 のトランジスタ 2610、第 4 のトランジスタ 2611、第 5 のトランジスタ 2612、発光素子 2613、発光素子 2613 の一方の電極 2614 が設けられている。発光素子 2613 の一方の電極 2614 は、陽極であってもよいし、陰極であってもよい。

10

【0257】

第 1 のトランジスタ 2606 は、ゲート電極が第 2 のゲート信号線 2604 に接続され、ソース領域またはドレイン領域の一方がソース信号線 2601 に、他方が第 1 のコンデンサ 2607 の一方の電極、第 2 のコンデンサ 2608 の一方の電極、及び第 2 のトランジスタ 2609 のソース領域またはドレイン領域の一方に接続されている。また、第 1 のコンデンサ 2607 の他方の電極は電源線 2602 に接続されている。また、第 2 のコンデンサ 2608 の他方の電極は、第 3 のトランジスタ 2610 のソース領域またはドレイン領域の一方及び第 4 のトランジスタ 2611 のゲート電極に接続されている。また、第 2 のトランジスタ 2609 は、ゲート電極が第 1 のゲート信号線 2603、及び第 3 のトランジスタ 2610 のゲート電極に接続され、ソース領域またはドレイン領域の他方が電源線 2602、及び第 4 のトランジスタ 2611 のソース領域またはドレイン領域の一方に接続されている。また、第 3 のトランジスタ 2610 は、ソース領域またはドレイン領域の他方が電源線 2602、第 4 のトランジスタ 2611 のソース領域またはドレイン領域の他方、及び第 5 のトランジスタ 2612 のソース領域またはドレイン領域の一方に接続されている。また、第 5 のトランジスタ 2612 は、ゲート電極が第 3 のゲート信号線 2605 に接続され、ソース領域またはドレイン領域の他方が発光素子 2613 の他方の電極に接続されている。

20

30

【0258】

図 26 において本発明を実施するためには、発光素子 2613 の他方の電極と電源線 2602 との間において電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子 2613 の他方の電極と電源線 2602 との間において電流の流れる経路は、上述した図 12 の構成と同じであるので、ここでは詳細な説明を省略する。

40

【0259】

また、本発明では、欠陥画素を簡便に修復することができるようにするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態 6 ~ 9 で説明した方法を用いればよいので、ここでは説明を省略する。

【0260】

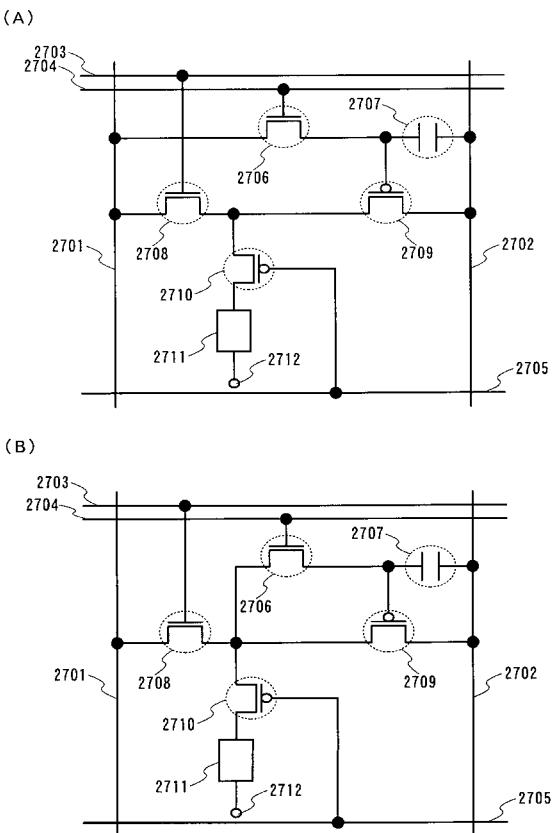

次に、図 27 (A) に表示装置の画素部における 1 画素分の等価回路図の別の一例を示す。各画素には、第 1 のトランジスタ 2706、第 1 のコンデンサ 2707、第 2 のトランジスタ 2708、第 3 のトランジスタ 2709、第 4 のトランジスタ 2710、発光素子 2711、発光素子 2711 の一方の電極 2712 が設けられている。発光素子 2711 の一方の電極 2712 は、陽極であってもよいし、陰極であってもよい。

【0261】

第 1 のトランジスタ 2706 は、ゲート電極が第 2 のゲート信号線 2704 に接続され、ソース領域またはドレイン領域の一方がソース信号線 2701 に、他方が第 1 のコンデ

50

ンサ 2707 の一方の電極、及び第 3 のトランジスタ 2709 のゲート電極に接続されている。また、第 1 のコンデンサ 2707 の他方の電極は電源線 2702 に接続されている。また、第 2 のトランジスタ 2708 は、ゲート電極が第 1 のゲート信号線 2703 に接続され、ソース領域またはドレイン領域の一方がソース信号線 2701 に、他方が第 3 のトランジスタ 2709 のソース領域またはドレイン領域の一方、及び第 4 のトランジスタ 2710 のソース領域またはドレイン領域の一方に接続されている。また、第 3 のトランジスタ 2709 は、ソース領域またはドレイン領域の他方が電源線 2702 に接続されている。また、第 4 のトランジスタ 2710 は、ゲート電極が第 3 のゲート信号線 2705 に接続され、ソース領域またはドレイン領域の他方が発光素子 2711 の他方の電極に接続されている。

10

## 【0262】

次に、図 27 (B) について説明する。図 27 (A) において第 1 のトランジスタ 2706 のソース領域またはドレイン領域の一方がソース信号線 2701 に接続されていたのに対し、図 27 (B) では、第 1 のトランジスタ 2706 のソース領域またはドレイン領域の一方が第 2 のトランジスタ 2708 のソース領域またはドレイン領域の他方、第 3 のトランジスタ 2709 のソース領域またはドレイン領域の一方、及び第 4 のトランジスタ 2710 のソース領域またはドレイン領域の一方に接続されている点で図 27 (B) は図 27 (A) と相違し、これ以外の構成については同じである。

## 【0263】

図 27 (A)、(B) において本発明を実施するためには、発光素子 2711 の他方の電極と電源線 2702 との間ににおいて電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子 2711 の他方の電極と電源線 2702 との間ににおいて電流の流れる経路は、上述した図 12 の構成と同じであるので、ここでは詳細な説明を省略する。

20

## 【0264】

また、本発明では、欠陥画素を簡便に修復することができるようにするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態 6 ~ 9 で説明した方法を用いればよいので、ここでは説明を省略する。

## 【0265】

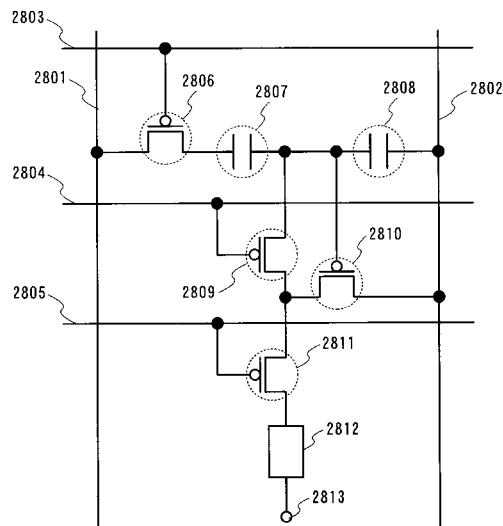

次に、図 28 に表示装置の画素部における 1 画素分の等価回路図の別の一例を示す。各画素には、第 1 のトランジスタ 2806、第 1 のコンデンサ 2807、第 2 のコンデンサ 2808、第 2 のトランジスタ 2809、第 3 のトランジスタ 2810、第 4 のトランジスタ 2811、発光素子 2812、発光素子 2812 の一方の電極 2813 が設けられている。発光素子 2812 の一方の電極 2813 は、陽極であってもよいし、陰極であってもよい。

30

## 【0266】

第 1 のトランジスタ 2806 は、ゲート電極が第 1 のゲート信号線 2803 に接続され、ソース領域またはドレイン領域の一方がソース信号線 2801 に、他方が第 1 のコンデンサ 2807 の一方の電極に接続されている。また、第 1 のコンデンサ 2807 の他方の電極は、第 2 のコンデンサ 2808 の一方の電極、第 2 のトランジスタ 2809 のソース領域またはドレイン領域の一方、及び第 3 のトランジスタ 2810 のゲート電極に接続されている。また、第 2 のコンデンサ 2808 の他方の電極は、電源線 2802 に接続されている。また、第 2 のトランジスタ 2809 は、ゲート電極が第 2 のゲート信号線 2804 に接続され、ソース領域またはドレイン領域の他方が第 3 のトランジスタ 2810 のソース領域またはドレイン領域の一方、及び第 4 のトランジスタ 2811 のソース領域またはドレイン領域の一方に接続されている。また、第 3 のトランジスタ 2810 は、ソース領域またはドレイン領域の他方が電源線 2802 に接続されている。また、第 4 のトランジスタ 2811 は、ゲート電極が第 3 のゲート信号線 2805 に接続され、ソース領域またはドレイン領域の他方が発光素子 2812 の他方の電極に接続されている。

40

## 【0267】

50

図28において本発明を実施するためには、発光素子2812の他方の電極と電源線2802との間ににおいて電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子2812の他方の電極と電源線2802との間ににおいて電流の流れる経路は、上述した図12の構成と同じであるので、ここでは詳細な説明を省略する。

【0268】

また、本発明では、欠陥画素を簡便に修復することができるようにするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

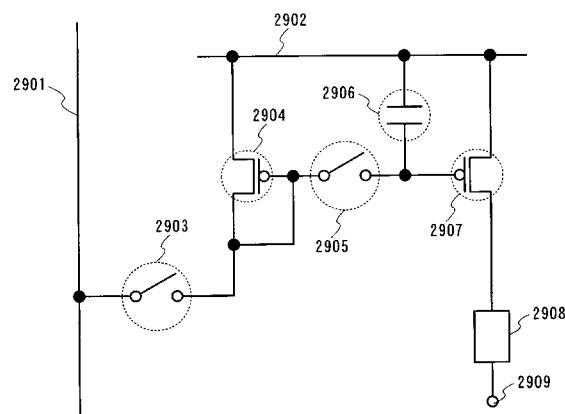

【0269】

次に、図29に表示装置の画素部における1画素分の等価回路図の別の一例を示す。各画素には、第1のスイッチ2903、第1のトランジスタ2904、第2のスイッチ2905、コンデンサ2906、第2のトランジスタ2907、発光素子2908、発光素子2908の一方の電極2909が設けられている。発光素子2908の一方の電極2909は、陽極であってもよいし、陰極であってもよい。

10

【0270】

第1のスイッチ2903は、一方の端子がソース信号線2901に接続され、他方の端子が第1のトランジスタ2904のソース領域またはドレイン領域の一方、ゲート電極、及び第2のスイッチ2905の一方の端子に接続されている。また、第1のトランジスタ2904は、ソース領域またはドレイン領域の他方が電源線2902に接続されている。また、第2のスイッチ2905の他方の端子は、コンデンサ2906の一方の電極、及び第2のトランジスタ2907のゲート電極に接続されている。また、コンデンサ2906の他方の電極は、電源線2902に接続されている。また、第2のトランジスタ2907は、ソース領域またはドレイン領域の一方が電源線2902に接続され、他方が発光素子2908の他方の電極に接続されている。

20

【0271】

図29において本発明を実施するためには、発光素子2908の他方の電極と電源線2902との間ににおいて電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子2908の他方の電極と電源線2902との間ににおいて電流の流れる経路は、上述した図11の構成と同じであるので、ここでは詳細な説明を省略する。

30

【0272】

また、本発明では、欠陥画素を簡便に修復することができるようにするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

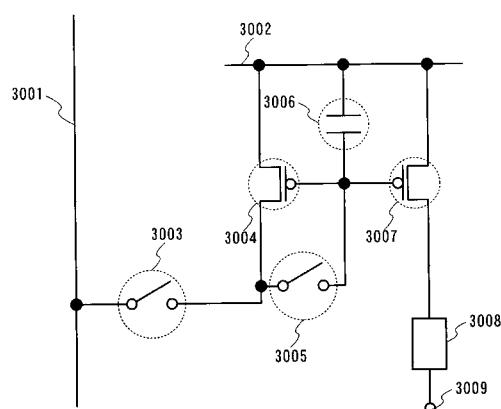

【0273】

次に、図30に表示装置の画素部における1画素分の等価回路図の別の一例を示す。各画素には、第1のスイッチ3003、第1のトランジスタ3004、第2のスイッチ3005、コンデンサ3006、第2のトランジスタ3007、発光素子3008、発光素子3008の一方の電極3009が設けられている。発光素子3008の一方の電極3009は、陽極であってもよいし、陰極であってもよい。

40

【0274】

第1のスイッチ3003は、一方の端子がソース信号線3001に接続され、他方の端子が第1のトランジスタ3004のソース領域またはドレイン領域の一方、及び第2のスイッチ3005の一方の端子に接続されている。また、第1のトランジスタ3004は、ゲート電極が第2のスイッチ3005の他方の端子、コンデンサ3006の一方の電極、及び第2のトランジスタ3007のゲート電極に接続され、ソース領域またはドレイン領域の他方が電源線3002に接続されている。また、コンデンサ3006の他方の電極は、電源線3002に接続されている。また、第2のトランジスタ3007は、ソース領域またはドレイン領域の一方が電源線3002に接続され、他方が発光素子3008の他方

50

の電極に接続されている。

【0275】

図30において本発明を実施するためには、発光素子3008の他方の電極と電源線3002との間ににおいて電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子3008の他方の電極と電源線3002との間ににおいて電流の流れる経路は、上述した図11の構成と同じであるので、ここでは詳細な説明を省略する。

【0276】

また、本発明では、欠陥画素を簡便に修復することができるようとするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

10

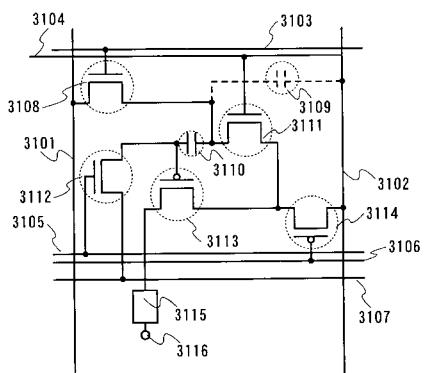

【0277】

次に、図31に表示装置の画素部における1画素分の等価回路図の別の一例を示す。各画素には、第1のトランジスタ3108、第1のコンデンサ3109、第2のコンデンサ3110、第2のトランジスタ3111、第3のトランジスタ3112、第4のトランジスタ3113、第5のトランジスタ3114、発光素子3115、発光素子3115の一方の電極3116が設けられている。発光素子3115の一方の電極3116は、陽極であってもよいし、陰極であってもよい。

【0278】

第1のトランジスタ3108は、ゲート電極が第1のゲート信号線3103に接続され、ソース領域またはドレイン領域の一方がソース信号線3101に、他方が第1のコンデンサ3109の一方の電極、第2のコンデンサ3110の一方の電極、及び第2のトランジスタ3111のソース領域またはドレイン領域の一方に接続されている。また、第1のコンデンサ3109の他方の電極は電源線3102に接続されている。また、第2のコンデンサ3110の他方の電極は、第3のトランジスタ3112のソース領域またはドレイン領域の一方、及び第4のトランジスタ3113のゲート電極に接続されている。また、第2のトランジスタ3111は、ゲート電極が第2のゲート信号線3104、ソース領域またはドレイン領域の他方が、第4のトランジスタ3113のソース領域またはドレイン領域の一方に接続されている。また、第3のトランジスタ3112は、ゲート電極が第3のゲート信号線3105に接続され、ソース領域またはドレイン領域の他方が初期化用の配線3107に接続されている。また、第4のトランジスタ3113は、ソース領域またはドレイン領域の他方が発光素子3115の他方の電極に接続されている。また、第5のトランジスタ3114は、ゲート電極が第4のゲート信号線3106に接続され、ソース領域またはドレイン領域の他方が電源線3102に接続されている。

20

30

【0279】

図31において本発明を実施するためには、発光素子3115の他方の電極と電源線3102との間ににおいて電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子3115の他方の電極と電源線3102との間ににおいて電流の流れる経路は、上述した図12の構成と同じであるので、ここでは詳細な説明を省略する。

40

【0280】

また、本発明では、欠陥画素を簡便に修復することができるようとするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

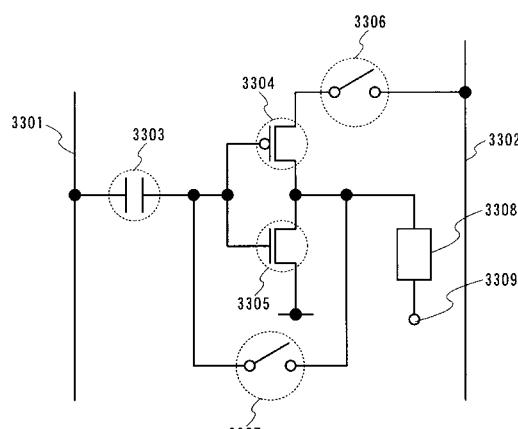

【0281】

次に、図32に表示装置の画素部における1画素分の等価回路図の別の一例を示す。各画素には、第1のコンデンサ3203、トランジスタ3204、第1のスイッチ3205、第2のスイッチ3206、発光素子3207、発光素子3207の一方の電極3208が設けられている。発光素子3207の一方の電極3208は、陽極であってもよいし、

50

陰極であってもよい。

【0282】

第1のコンデンサ3203は、一方の電極がソース信号線3201に接続され、他方の電極がトランジスタ3204のゲート電極、及び第1のスイッチ3205の一方の端子に接続されている。また、トランジスタ3204は、ソース領域またはドレイン領域の一方が電源線3202に接続され、他方が第1のスイッチ3205の他方の端子及び第2のスイッチ3206の一方の端子に接続されている。また、第2のスイッチ3206の他方の端子は、発光素子3207の他方の電極に接続されている。

【0283】

図32において本発明を実施するためには、発光素子3207の他方の電極と電源線3202との間ににおいて電流の流れる経路のうち、少なくとも一部を断線させればよい。

【0284】

また、本発明では、欠陥画素を簡便に修復することができるようとするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

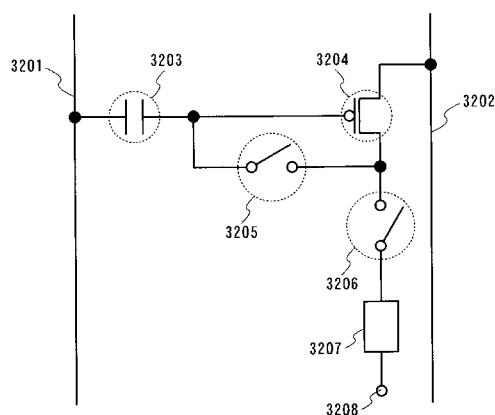

【0285】

次に、図33に表示装置の画素部における1画素分の等価回路図の別の一例を示す。各画素には、第1のコンデンサ3303、第1のトランジスタ3304、第2のトランジスタ3305、第1のスイッチ3306、第2のスイッチ3307、発光素子3308、発光素子3308の一方の電極3309が設けられている。発光素子3308の一方の電極3309は、陽極であってもよいし、陰極であってもよい。

【0286】

第1のコンデンサ3303は、一方の電極がソース信号線3301に接続され、他方の電極が第1のトランジスタ3304のゲート電極、第2のトランジスタ3305のゲート電極、及び第2のスイッチ3307の一方の端子に接続されている。また、第1のトランジスタ3304は、ソース領域またはドレイン領域の一方が第1のスイッチ3306の一方の端子に、他方が第2のトランジスタ3305のソース領域またはドレイン領域の一方、第2のスイッチ3307の他方の端子、及び発光素子3308の他方の電極に接続されている。また、第2のトランジスタ3305は、ソース領域またはドレイン領域の他方が低電源電位に接続されている。このように第1のトランジスタ3304、及び第2のトランジスタ3305はCMOSインバータ回路を構成している。また、第1のスイッチ3306の他方の端子は、電源線3302に接続されている。

【0287】

図33において本発明を実施するためには、発光素子3308の他方の電極と電源線3302との間ににおいて電流の流れる経路のうち、少なくとも一部を断線させればよい。

【0288】

また、本発明では、欠陥画素を簡便に修復することができるようとするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

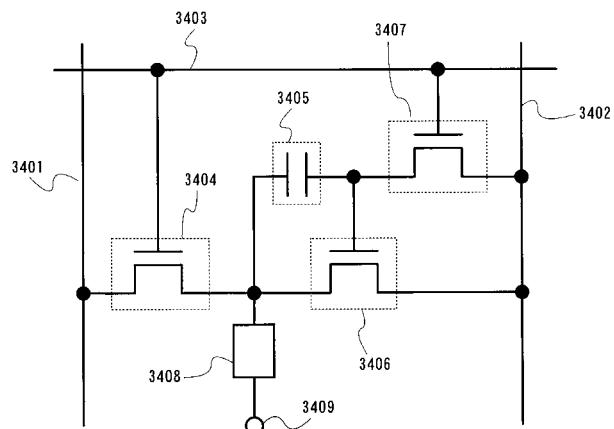

【0289】

次に、図34に表示装置の画素部における1画素分の等価回路図の別の一例を示す。各画素には、第1のトランジスタ3404、コンデンサ3405、第2のトランジスタ3406、第3のトランジスタ3407、発光素子3408、発光素子3408の一方の電極3409が設けられている。発光素子3408の一方の電極3409は、陽極であってもよいし、陰極であってもよい。

【0290】

第1のトランジスタ3404は、ゲート電極がゲート信号線3403に接続され、ソース領域またはドレイン領域の一方がソース信号線3401に、他方がコンデンサ3405

10

20

30

40

50

の一方の電極、第2のトランジスタ3406のソース領域またはドレイン領域の一方、及び発光素子3408の他方の電極に接続されている。また、コンデンサ3405の他方の電極は、第2のトランジスタ3406のゲート電極、及び第3のトランジスタ3407のソース領域またはドレイン領域の一方に接続されている。また、第2のトランジスタ3406は、ソース領域またはドレイン領域の他方が電源線3402に接続されている。また、第3のトランジスタ3407は、ゲート電極がゲート信号線3403に接続され、ソース領域またはドレイン領域の他方が電源線3402に接続されている。

【0291】

図34において本発明を実施するためには、発光素子3408の他方の電極と電源線3402との間において電流の流れる経路のうち、少なくとも一部を断線させればよい。発光素子3408の他方の電極と電源線3402との間において電流の流れる経路は、上述した図11の構成と同じであるので、ここでは詳細な説明を省略する。

10

【0292】

また、本発明では、欠陥画素を簡便に修復することができるようとするため、断線させる領域に相当する配線の幅を狭くする構成とする。断線させる領域に相当する配線の幅を狭くする具体的な構成例としては、実施の形態6～9で説明した方法を用いればよいので、ここでは説明を省略する。

【0293】

本実施例で説明した図面は、あくまで一例である。すなわち、トランジスタの極性や図面の構成に限定されるものではなく、Nチャネル型、Pチャネル型のどちらでも構わない。

20

【実施例2】

【0294】

本発明の表示装置は様々な電子機器の表示部に用いることができる。特に薄型、軽量が要求されるモバイル機器には本発明の表示装置を用いることが望ましい。

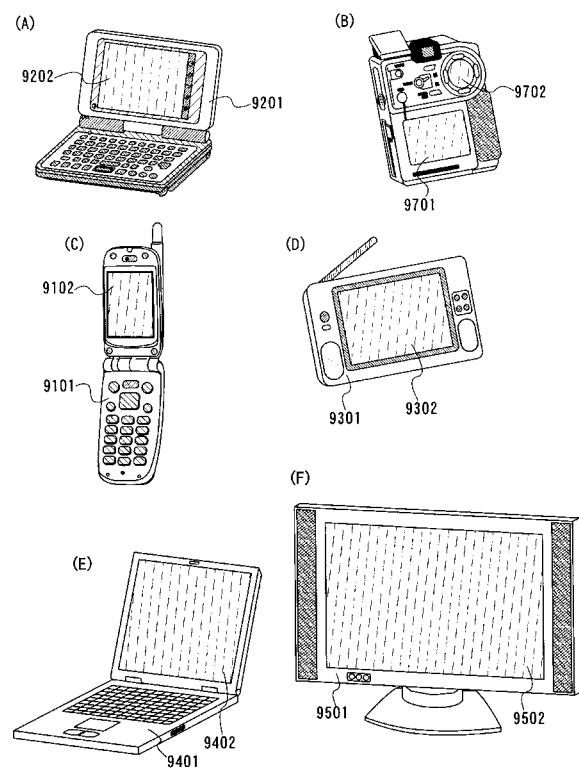

【0295】

上記実施の形態及び上記実施例に示される表示装置を筐体に組み込んだ電子機器として、テレビジョン装置（単にTV、テレビ、又はテレビジョン受信機ともよぶ。）、カメラ（ビデオカメラやデジタルカメラ等）、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話機、携帯型のゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはDVD（d i g i t a l v e r s a t i l e d i s c）やHD DVD（H i g h D e f i n i t i o n D V D）、ブルーレイディスク（B l u r a y（登録商標）Disk）等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）、その他表示部を有する電化製品などが挙げられる。電子機器の具体例を図8、図10に示す。

30

【0296】

図8（A）に示す携帯情報端末は、本体9201、表示部9202等を含んでいる。表示部9202は、実施形態1～9で示すものを適用することができる。本発明の一である表示装置を用いることにより、点欠ではあるものの輝点がなく、画面全体の画質不良が低減された、表示品位に優れた携帯情報端末を歩留まり良く安価に提供することができる。

40

【0297】

図8（B）に示すデジタルビデオカメラは、表示部9701、表示部9702等を含んでいる。表示部9701は、実施形態1～9で示すものを適用することができる。本発明の一である表示装置を用いることにより、点欠ではあるものの輝点がなく、画面全体の画質不良が低減された、表示品位に優れたデジタルビデオカメラを歩留まり良く安価に提供することができる。

【0298】

図8（C）に示す携帯端末は、本体9101、表示部9102等を含んでいる。表示部9102は、実施形態1～9で示すものを適用することができる。本発明の一である表示

50

装置を用いることにより、点欠ではあるものの輝点がなく、画面全体の画質不良が低減された、表示品位に優れた携帯端末を歩留まり良く安価に提供することができる。

【0299】

図8(D)に示す携帯型のテレビジョン装置は、本体9301、表示部9302等を含んでいる。表示部9302は、実施形態1~9で示すものを適用することができる。本発明の一である表示装置を用いることにより、点欠ではあるものの輝点がなく、画面全体の画質不良が低減された、表示品位に優れた携帯型のテレビジョン装置を歩留まり良く安価に提供することができる。このようなテレビジョン装置は携帯電話機などの携帯端末に搭載する小型のものから、持ち運びをすることができる中型のもの、また、大型のもの(例えば40インチ以上)まで、幅広く適用することができる。

10

【0300】

図8(E)に示す携帯型のコンピュータは、本体9401、表示部9402等を含んでいる。表示部9402は、実施形態1~9で示すものを適用することができる。本発明の一である表示装置を用いることにより、点欠ではあるものの輝点がなく、画面全体の画質不良が低減された、表示品位に優れた携帯型のコンピュータを歩留まり良く安価に提供することができる。

20

【0301】

図8(F)に示すテレビジョン装置は、本体9501、表示部9502等を含んでいる。表示部9502は、実施形態1~9で示すものを適用することができる。本発明の一である表示装置を用いることにより、点欠ではあるものの輝点がなく、画面全体の画質不良が低減された、表示品位に優れたテレビジョン装置を歩留まり良く安価に提供することができる。

20

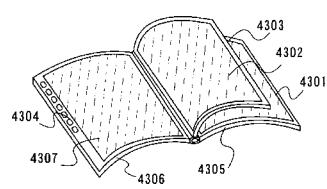

【0302】

図10に示す電子ブックは、両面表示型パネル4303を搭載した例である。第1の筐体4305は第1の表示部4301を有し、第2の筐体4306は操作ボタン4304及び第2の表示部4307を有し、両面表示型パネル4303は、第1の表示面、及び第1の表示面の裏面に相当する第2の表示面4302を有し、両面表示型パネル4303は、第1の筐体4305と第2の筐体4306の間に挿入されている。各表示部は、実施形態1~9で示すものを適用することができる。

30

【0303】

両面表示型パネル4303を挿入した電子ブックの使い方の例としては、第1の表示部4301及び第2の表示面4302で文章を読み、第2の表示部4307及び第1の表示面で図を参照するのは便利である。このとき、両面表示型パネル4303は、第1の表示面と第2の表示面4302を同時に違う画面を表示することはできないため、第1の表示面と第2の表示面4302を動かしたときに、第1の表示面の表示から第2の表示面の表示に切り替わるものとする。

30

【0304】

また、第1の表示部4301から第1の表示面を読んで、次のページ、両面表示型パネルをめくり始めた時に、ある角度で第2の表示面及び第2の表示部4307は次のページの表示を行い、また、第2の表示面4302及び第2の表示部4307を使い終わり、両面表示型パネルをめくり始めると、ある角度で第1の表示面及び第1の表示部4301が次のページを表示する。これにより、画面の切り替わりを目に見えないようにし、視覚的な違和感等を抑えることが可能となる。また、違和感を更に低減するために、可撓性基板に両面射出型パネルを設けるとよい。本発明の一である表示装置を用いることにより、点欠ではあるものの輝点がなく、画面全体の画質不良が低減された、表示品位に優れた電子ブックを歩留まり良く安価に提供することができる。

40

【0305】

上記に挙げた電子機器において、二次電池を用いているものは、表示装置の消費電力を削減した分、電子機器の使用時間を長持ちさせることができ、二次電池を充電する時間を短くすることができる。

50

## 【0306】

なお、上述した電子機器の他に、フロント型若しくはリア型のプロジェクターに用いることも可能である。

## 【0307】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。

## 【符号の説明】

## 【0308】

101 発光素子

102 駆動用のトランジスタ

103 スイッチング用トランジスタ

104 コンデンサ

105 電源線

106 ソース信号線

107 ゲート信号線

108 発光素子の他方の電極（陰極）に接続された配線

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

【図 15】

【図 16】

【図 17】

【図 18】

【図 19】

【図 2 0】

【図 2 1】

【図 2 2】

【図 2 3】

【図24】

【図25】

【図26】

【図27】

【図 2 8】

【図 2 9】

【図 3 0】

【図 3 1】

【図 3 3】

【図 3 2】

【図34】

【図35】

【図36】

【図37】

【 図 3 8 】

【 図 3 9 】

### 【図41】

【 図 4 0 】

【 図 4 2 】

【図43】

## 【手続補正書】

【提出日】平成29年5月1日(2017.5.1)

## 【手続補正2】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

## 【特許請求の範囲】

## 【請求項1】

プラスチック基板の上方に、第1の配線、第2の配線、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第4のトランジスタ、第5のトランジスタ、第6のトランジスタ、及び発光素子を有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記第1の配線と電気的に接続され、