(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4160032号

(P4160032)

(45) 発行日 平成20年10月1日(2008.10.1)

(24) 登録日 平成20年7月25日(2008.7.25)

(51) Int.CI.

F 1

**G09G 3/30 (2006.01)**

**G09G 3/20 (2006.01)**

**H01L 51/50 (2006.01)**

GO9G 3/30 J

GO9G 3/30 K

GO9G 3/20 621F

GO9G 3/20 624B

GO9G 3/20 641A

請求項の数 14 (全 37 頁) 最終頁に続く

(21) 出願番号

特願2004-254615 (P2004-254615)

(22) 出願日

平成16年9月1日(2004.9.1)

(65) 公開番号

特開2006-71919 (P2006-71919A)

(43) 公開日

平成18年3月16日(2006.3.16)

審査請求日

平成17年7月12日(2005.7.12)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 110000338

特許業務法人原謙三國際特許事務所

(74) 代理人 100080034

弁理士 原 謙三

(74) 代理人 100113701

弁理士 木島 隆一

(74) 代理人 100116241

弁理士 金子 一郎

(72) 発明者 沼尾 孝次

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】表示装置およびその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表示光源としての電流駆動型の電気光学素子と、電流制御端子と基準電位端子との間に印加される電圧により制御される出力電流を電流出力端子から上記電気光学素子に駆動電流として供給する駆動用トランジスタとが、マトリックス状に設けられた各画素に配置され、上記駆動電流が、データ配線から上記各画素に供給される、上記電気光学素子の点灯または消灯を示すデジタルの表示データに対応する表示装置において、

上記駆動用トランジスタと第1スイッチ用トランジスタと上記電気光学素子とが直列に接続され、

上記駆動用トランジスタの上記電流制御端子に第1コンデンサの一方端子が接続され、

上記駆動用トランジスタの上記電流制御端子と上記電流出力端子との間に第2スイッチ用トランジスタが接続され、

上記第2スイッチ用トランジスタがON状態であるとともに上記第1スイッチ用トランジスタがOFF状態であり、上記データ配線から上記各画素の上記表示データに対応する電位であって、上記表示データが点灯を示すものである場合には上記駆動用トランジスタをON状態とする電位が、また、上記表示データが消灯を示すものである場合には上記駆動用トランジスタをOFF状態とする電位が、上記駆動用トランジスタの上記電流制御端子に伝達される表示データ付与期間と、

上記表示データ付与期間の後に続く第1期間であって、上記第2スイッチ用トランジスタがON状態であるとともに上記第1スイッチ用トランジスタがOFF状態であり、上記

10

20

データ配線から上記電流制御端子への上記電位の伝達が遮断される第1期間とを経る動作を行い、

上記動作を行った後の第2期間において、上記第1コンデンサの他方端子の電位または、上記駆動用トランジスタの上記基準電位端子の電位が変化することにより、上記駆動用トランジスタの出力電流が設定されることを特徴とする表示装置。

【請求項2】

上記第1コンデンサの上記他方端子は第1配線に接続されていることを特徴とする請求項1に記載の表示装置。

【請求項3】

上記第2期間に上記第1配線の電位が変化して、上記駆動用トランジスタがOFF状態からON状態に変化する、または、OFF状態を維持することにより、上記駆動電流の有無が決定されることを特徴とする請求項2に記載の表示装置。 10

【請求項4】

上記駆動用トランジスタの上記電流出力端子と上記データ配線との間に第3スイッチ用トランジスタが接続されていることを特徴とする請求項1から3までのいずれか1項に記載の表示装置。

【請求項5】

上記表示データ付与期間に上記第3スイッチ用トランジスタがON状態となることを特徴とする請求項4に記載の表示装置。

【請求項6】

上記駆動用トランジスタの上記電流制御端子と上記データ配線との間に第4スイッチ用トランジスタが接続されていることを特徴とする請求項1から3までのいずれか1項に記載の表示装置。 20

【請求項7】

上記駆動用トランジスタの上記電流出力端子と上記データ配線とは第2コンデンサを介して接続されていることを特徴とする請求項1から3までのいずれか1項に記載の表示装置。

【請求項8】

上記駆動用トランジスタの上記基準電位端子と上記データ配線との間に第5スイッチ用トランジスタが接続され、 30

上記駆動用トランジスタの上記基準電位端子と、上記駆動用トランジスタの出力電流を生成する電源の電位を与える電源配線との間に、第6スイッチ用トランジスタが接続されていることを特徴とする請求項1に記載の表示装置。

【請求項9】

上記第1コンデンサの上記他方端子と、上記駆動用トランジスタの出力電流を生成する電源の電位を与える電源配線との間に、第3コンデンサが接続され、

上記第1コンデンサの上記他方端子と上記データ配線との間に第7スイッチ用トランジスタが接続されていることを特徴とする請求項1に記載の表示装置。

【請求項10】

上記第1コンデンサの上記他方端子と所定の電位を与える第2配線との間に第8スイッチ用トランジスタが接続され、 40

上記第1コンデンサの上記他方端子と上記データ配線との間に第7スイッチ用トランジスタが接続されていることを特徴とする請求項1に記載の表示装置。

【請求項11】

表示光源としての電流駆動型の電気光学素子と、電流制御端子と基準電位端子との間に印加される電圧により制御される出力電流を電流出力端子から上記電気光学素子に駆動電流として供給する駆動用トランジスタとが、マトリックス状に設けられた各画素に配置され、上記駆動電流が、データ配線から上記各画素に供給される、上記電気光学素子の点灯または消灯を示すデジタルの表示データに対応する表示装置において、

上記駆動用トランジスタと第1スイッチ用トランジスタと上記電気光学素子とが直列に 50

接続され、

上記駆動用トランジスタの上記電流制御端子に第1コンデンサの一方端子が接続され、

上記駆動用トランジスタの上記電流制御端子と上記電流出力端子との間に第2スイッチ用トランジスタが接続され、

上記駆動用トランジスタの上記電流制御端子と上記データ配線との間に第4スイッチ用トランジスタが接続され、

上記データ配線から上記各画素の上記表示データに対応する電位であって、上記表示データが点灯を示すものである場合には上記駆動用トランジスタをON状態とする電位が、また、上記表示データが消灯を示すものである場合には上記駆動用トランジスタをOFF状態とする電位が、上記駆動用トランジスタの上記電流制御端子に与えられて、上記第1コンデンサに、対応する電荷が保持された状態から始まる、あるいは、対応する電荷を保持する動作と同時に行われる第1期間において、上記第2スイッチ用トランジスタがON状態となり、上記第1スイッチ用トランジスタがOFF状態となり、

第2期間において、上記第1コンデンサの他方端子の電位または、上記駆動用トランジスタの上記基準電位端子の電位が変化することにより、上記駆動用トランジスタの出力電流が設定されることを特徴とする表示装置。

【請求項12】

表示光源としての電流駆動型の電気光学素子と、電流制御端子と基準電位端子との間に印加される電圧により制御される出力電流を電流出力端子から上記電気光学素子に駆動電流として供給する駆動用トランジスタとが、マトリックス状に設けられた各画素に配置され、上記駆動電流が、データ配線から上記各画素に供給される、上記電気光学素子の点灯または消灯を示すデジタルの表示データに対応する表示装置において、

上記駆動用トランジスタと第1スイッチ用トランジスタと上記電気光学素子とが直列に接続され、

上記駆動用トランジスタの上記電流制御端子に第1コンデンサの一方端子が接続され、

上記駆動用トランジスタの上記電流制御端子と上記電流出力端子との間に第2スイッチ用トランジスタが接続され、

上記駆動用トランジスタの上記電流出力端子と上記データ配線とは第2コンデンサを介して接続され、

上記データ配線から上記各画素の上記表示データに対応する電位であって、上記表示データが点灯を示すものである場合には上記駆動用トランジスタをON状態とする電位が、また、上記表示データが消灯を示すものである場合には上記駆動用トランジスタをOFF状態とする電位が、上記駆動用トランジスタの上記電流制御端子に与えられて、上記第1コンデンサに、対応する電荷が保持された状態から始まる、あるいは、対応する電荷を保持する動作と同時に行われる第1期間において、上記第2スイッチ用トランジスタがON状態となり、上記第1スイッチ用トランジスタがOFF状態となり、

第2期間において、上記第1コンデンサの他方端子の電位または、上記駆動用トランジスタの上記基準電位端子の電位が変化することにより、上記駆動用トランジスタの出力電流が設定されることを特徴とする表示装置。

【請求項13】

上記第1コンデンサの上記他方端子は第1配線に接続されていることを特徴とする請求項11または12に記載の表示装置。

【請求項14】

表示光源としての電流駆動型の電気光学素子と、電流制御端子と基準電位端子との間に印加される電圧により制御される出力電流を電流出力端子から上記電気光学素子に駆動電流として供給する駆動用トランジスタとが、マトリックス状に設けられた各画素に配置され、上記駆動電流が、データ配線から上記各画素に供給される、上記電気光学素子の点灯または消灯を示すデジタルの表示データに対応する表示装置において、

上記駆動用トランジスタと第1スイッチ用トランジスタと上記電気光学素子とが直列に接続され、

10

20

30

40

50

上記駆動用トランジスタの上記電流制御端子に第1コンデンサの一方端子が接続され、上記駆動用トランジスタの上記電流制御端子と上記電流出力端子との間に第2スイッチ用トランジスタが接続された表示装置の駆動方法であって、

上記第2スイッチ用トランジスタがON状態であるとともに上記第1スイッチ用トランジスタがOFF状態であり、上記データ配線から上記各画素の上記表示データに対応する電位であって、上記表示データが点灯を示すものである場合には上記駆動用トランジスタをON状態とする電位が、また、上記表示データが消灯を示すものである場合には上記駆動用トランジスタをOFF状態とする電位が、上記駆動用トランジスタの上記電流制御端子に伝達される表示データ付与期間と、

上記表示データ付与期間の後に続く第1期間であって、上記第2スイッチ用トランジスタがON状態であるとともに上記第1スイッチ用トランジスタがOFF状態であり、上記データ配線から上記電流制御端子への上記電位の伝達が遮断される第1期間とを経る動作を行い、

上記動作を行った後の第2期間において、上記第1コンデンサの他方端子の電位または、上記駆動用トランジスタの上記基準電位端子電位を変化させることにより、上記駆動用トランジスタの出力電流を設定することを特徴とする表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機EL(Electro Luminescence)ディスプレイやFED(Field Emission Display)等の電流駆動型の電気光学素子を用いた表示装置およびその駆動方法に関するものである。

【背景技術】

【0002】

近年、有機ELディスプレイやFED等の電流駆動発光素子の研究開発が活発に行われている。特に有機ELディスプレイは、低電圧・低消費電力で発光可能なディスプレイとして、携帯電話やPDA(Personal Digital Assistants)などの携帯機器用として注目されている。

【0003】

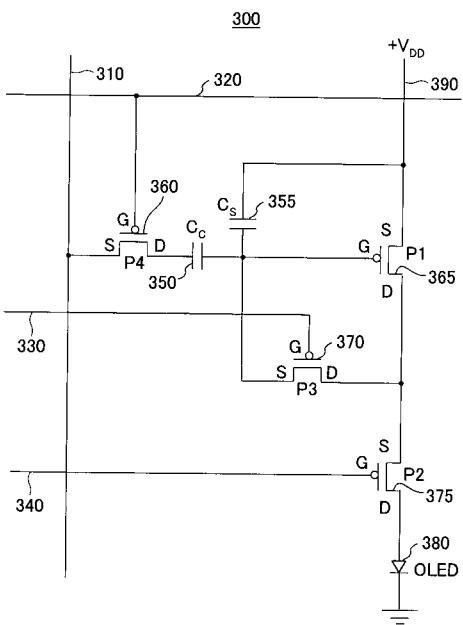

この有機ELディスプレイの電流駆動画素回路構成として、特許文献1(特表2002-514320号公報)に示された回路構成を図25に示す。

【0004】

図25に示す画素回路300は、4つのp型TFT(Thin Film Transistor)360, 365, 370, 375と2つのコンデンサ350, 355と、有機EL(OLED)380とから構成される。有機EL380は電流駆動型の電気光学素子であり、表示光源となる。電源ライン390から共通陰極(GNDライン)へ至る経路にはTFT365, 375、有機EL380がこの順で直列に接続されている。駆動用TFT(駆動用トランジスタ)365のゲート端子(電流制御端子)からデータライン310へ至る経路にはコンデンサ350とスイッチ用TFT360とがこの順で直列に接続されている。また、駆動用TFT365のゲート端子とドレイン端子(電流出力端子)との間にはスイッチ用TFT370が接続され、駆動用TFT365のゲート端子とソース端子(基準電位端子)との間にはコンデンサ355が接続されている。これらTFT360, 370, 375のゲート端子には順にセレクトライン320、オートゼロライン330、照明ライン340が接続されている。

【0005】

この画素回路300では、第1期間にオートゼロライン330及び照明ライン340がLOWとなり、スイッチ用TFT370及び375がON状態となり、駆動用TFT365のドレイン端子とゲート端子とが同電位となる。このとき、駆動用TFT365がON状態となり、駆動用TFT365からOLED380に向け電流が流れる。

【0006】

10

20

30

40

50

またこのとき、データライン 310 へ基準電圧を入力し、セレクトライン 320 を Low としてコンデンサ 350 の他方端子 (TFT360 側端子) を基準電圧としておく。

【0007】

次に第2期間となり、照明ライン 340 を High として、TFT375 を OFF 状態とする。

【0008】

このことにより、駆動用 TFT365 のゲート電位は徐々に高くなり、駆動用 TFT365 の閾値電圧 (-Vth) に対応した値 (+VDD - Vth) となったとき駆動用 TFT365 は OFF 状態となる。

【0009】

次に第3期間となり、オートゼロライン 330 を High として、スイッチ用 TFT370 を OFF 状態とする。このことにより、コンデンサ 350 には、そのゲート電位と基準電位との差が記憶される。

【0010】

即ち、駆動用 TFT365 のゲート電位は、データライン 310 の電位が基準電位のとき閾値電圧 (-Vth) に対応した値 (+VDD - Vth) となる。そして、データライン 310 の電位がその基準電位から変化すれば、駆動用 TFT365 の閾値電圧に關係なく、その電位変化に対応した電流が駆動用 TFT365 に流れよう制御される。

【0011】

そこで、そのような所望の電位変化をデータライン 310 に与え、セレクトラインをハイ状態とし、スイッチ用 TFT360 を OFF 状態して、この駆動用 TFT365 のゲート端子電位を維持し、画素の選択期間を終了する。

【0012】

このように、図 25 に示す画素回路を用いれば、駆動用 TFT365 の閾値電圧のばらつきを補償し、駆動用 TFT365 のゲート端子へその閾値電圧を補償した電位 (所望の電位 - 閾値電圧) を与えることができる。

【0013】

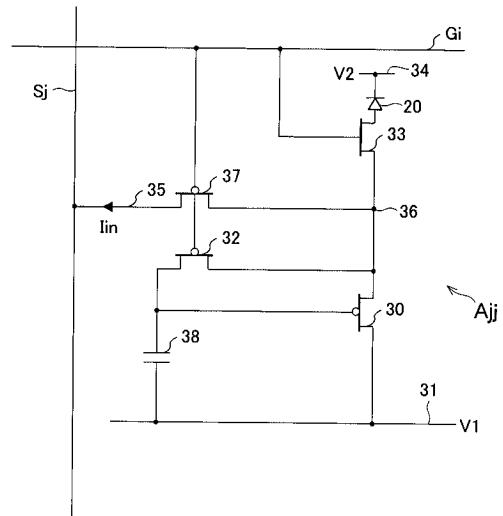

また、有機 EL ディスプレイの別の電流駆動画素回路構成として、特許文献 2 (特表 2003-529805 号公報) に示された回路構成を図 26 に示す。

【0014】

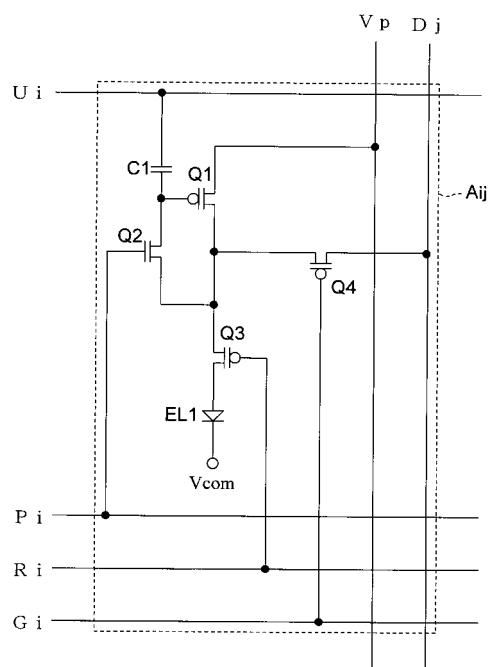

図 26 に示す画素回路 Aij は、3 つの p 型 TFT30, 32, 37 と 1 つの n 型 TFT33 と 1 つのコンデンサ 38 及び有機 EL (OLED) 20 とから構成される。有機 EL 20 は電流駆動型の電気光学素子であり、表示光源となる。電源ライン 31 から共通陰極 (GND ライン) 34 に至る経路の間には TFT30, 33, 有機 EL 20 がこの順で直列に接続されている。駆動用 TFT30 のゲート端子 (電流制御端子) とドレイン端子 (電流出力端子) との間にはスイッチ用 TFT32 が配置され、駆動用 TFT30 のゲート端子とソース端子 (基準電位端子) との間にはコンデンサ 38 が配置されている。駆動用 TFT30 のドレイン端子とソース配線 Sj との間にはスイッチ用 TFT37 が接続されている。これら TFT32, 37, 33 のゲート端子にはゲート配線 Gi が配置されている。

【0015】

この構成では、ゲート配線 Gi が Low となる間 (選択期間)、スイッチ用 TFT33 が OFF 状態となり、スイッチ用 TFT32, 37 が ON 状態となる。この結果、電源ライン 31 から駆動用 TFT30 およびスイッチ用 TFT37 を介してソース配線 Sj へ電流が流れる。このときの電流値をソース配線 Sj に繋がる図示しないソースドライバ回路の電流源で制御すれば、駆動用 TFT30 の出力電流値がソースドライバ回路で規定された電流値となるよう、駆動用 TFT30 のゲート電圧を設定できる。

【0016】

その後、ゲート配線 Gi を High とすることで、TFT32, 37 が OFF 状態となり駆動用 TFT30 のゲート電圧を保持する。また、TFT33 が ON 状態となり、上記

10

20

30

40

50

選択期間に設定された電流値が駆動用 TFT30 から有機 EL (OLED) 20 へ出力される。

【0017】

このように、図 26 に示す画素回路を用いれば、駆動用 TFT30 の閾値電圧のばらつきや移動度のばらつきによらず、駆動用 TFT30 の出力電流値が上記ソースドライバ回路の電流源から与えられた電流値となるよう、駆動用 TFT30 のゲート電位を設定することができる。

【特許文献 1】特表 2002-514320 号公報 (国際公開日: 1998 年 10 月 29 日)

【特許文献 2】特表 2003-529805 号公報 (国際公開日: 2001 年 10 月 11 日)

10

【特許文献 3】特開平 9-127906 号公報 (公開日: 1997 年 9 月 16 日)

【非特許文献 1】“4.0-in. TFT-OLED Displays and a Novel Digital Driving Method” (SID'00 Digest, pp.924-927、半導体エネルギー研究所)

【非特許文献 2】“Continuous Grain Silicon Technology and Its Applications for Active Matrix Display” (AM-LCD 2000, pp.25-28、半導体エネルギー研究所)

【非特許文献 3】“Polymer Light-Emitting Diodes for use in Flat panel Display” (AM-LCD '01, pp.211-214、半導体エネルギー研究所)

【発明の開示】

【発明が解決しようとする課題】

20

【0018】

上記のように図 25 に示した画素回路構成を用いれば、駆動用 TFT365 の閾値電圧のばらつきを補償することができる。しかし、図 25 の画素回路構成では、駆動用 TFT365 が ON 状態から OFF 状態に変移するまでに数十  $\mu$ s の時間が必要であり、その間データライン 310 に基準電位を保持しなければならず、1 画素当たりの選択期間が長くなり、その分、表示できる画素数が少なくなると言う課題がある。

【0019】

また、図 26 に示した画素回路構成では、駆動用 TFT30 の閾値電圧のばらつきと移動度のばらつきとを補償することができる。しかし、上記課題がより顕著に発生する。

【0020】

30

即ち、図 26 の画素回路でもソース配線  $S_j$  に浮遊容量が存在する。そして、駆動用 TFT30 からソースドライバ回路へ所望の電流が流れよう制御するので、その電流値が少ないと、上記浮遊容量を充電するだけでも数百  $\mu$ s 以上必要となる。

【0021】

この結果、画素当たりの選択期間が長くなり、その分、表示できる画素数が少なくなると言う課題がある。

【0022】

本発明は上記課題を解決する為のものであり、その目的は、駆動用トランジスタの閾値電圧のばらつきを補償しながら、1 画素当たりの選択期間の長さを短くすることのできる表示装置およびその駆動方法を実現することにある。

40

【課題を解決するための手段】

【0023】

本発明の表示装置は、上記課題を解決するために、表示光源としての電流駆動型の電気光学素子と、電流制御端子と基準電位端子との間に印加される電圧により制御される出力電流を電流出力端子から上記電気光学素子に駆動電流として供給する駆動用トランジスタとが、マトリックス状に設けられた各画素に配置され、上記駆動電流が、データ配線から上記各画素に供給される、上記電気光学素子の点灯または消灯を示すデジタルの表示データに対応する表示装置において、上記駆動用トランジスタと第 1 スイッチ用トランジスタと上記電気光学素子とが直列に接続され、上記駆動用トランジスタの上記電流制御端子に第 1 コンデンサの一方端子が接続され、上記駆動用トランジスタの上記電流制御端子と上

50

記電流出力端子との間に第2スイッチ用トランジスタが接続され、上記第2スイッチ用トランジスタがON状態であるとともに上記第1スイッチ用トランジスタがOFF状態であり、上記データ配線から上記各画素の上記表示データに対応する電位であって、上記表示データが点灯を示すものである場合には上記駆動用トランジスタをON状態とする電位が、また、上記表示データが消灯を示すものである場合には上記駆動用トランジスタをOFF状態とする電位が、上記駆動用トランジスタの上記電流制御端子に伝達される表示データ付与期間と、上記表示データ付与期間の後に続く第1期間であって、上記第2スイッチ用トランジスタがON状態であるとともに上記第1スイッチ用トランジスタがOFF状態であり、上記データ配線から上記電流制御端子への上記電位の伝達が遮断される第1期間とを経る動作を行い、上記動作を行った後の第2期間において、上記第1コンデンサの他方端子の電位または、上記駆動用トランジスタの上記基準電位端子の電位が変化することにより、上記駆動用トランジスタの出力電流が設定されることを特徴としている。

本発明の表示装置は、上記課題を解決するために、表示光源としての電流駆動型の電気光学素子と、電流制御端子と基準電位端子との間に印加される電圧により制御される出力電流を電流出力端子から上記電気光学素子に駆動電流として供給する駆動用トランジスタとが、マトリックス状に設けられた各画素に配置され、上記駆動電流が、データ配線から上記各画素に供給される、上記電気光学素子の点灯または消灯を示すデジタルの表示データに対応する表示装置において、上記駆動用トランジスタと第1スイッチ用トランジスタと上記電気光学素子とが直列に接続され、上記駆動用トランジスタの上記電流制御端子に第1コンデンサの一方端子が接続され、上記駆動用トランジスタの上記電流制御端子と上記電流出力端子との間に第2スイッチ用トランジスタが接続され、上記データ配線から上記各画素の上記表示データに対応する電位であって、上記表示データが点灯を示すものである場合には上記駆動用トランジスタをON状態とする電位が、また、上記表示データが消灯を示すものである場合には上記駆動用トランジスタをOFF状態とする電位が、上記駆動用トランジスタの上記電流制御端子に与えられて、上記第1コンデンサに、対応する電荷が保持された状態から始まる、あるいは、対応する電荷を保持する動作と同時に行われる第1期間において、上記第2スイッチ用トランジスタがON状態となり、上記第1スイッチ用トランジスタがOFF状態となり、第2期間において、上記第1コンデンサの他方端子の電位または、上記駆動用トランジスタの上記基準電位端子の電位が変化することにより、上記駆動用トランジスタの出力電流が設定されることを特徴としている。

#### 【0024】

上記の発明によれば、各画素の表示データに対応する電位が第1期間の前あるいは同時に駆動用トランジスタの電流制御端子に与えられる。そして、第1期間にON状態とした駆動用トランジスタの閾値電圧を補償することにより、その駆動用トランジスタの電流制御端子の電位が駆動用トランジスタの基準電位端子の電位Vsより閾値電圧Vthだけ大きい状態となる。また、OFF状態とした駆動用トランジスタでは、閾値電圧が補償できないが、元々OFF状態は閾値電圧に依存しないので問題ない。そして、第2期間でその駆動用トランジスタの電流制御端子の電位または駆動用トランジスタの基準電位端子の電位を変化させることで、駆動用トランジスタの出力電流を閾値電圧に関わらず所望の電流値に設定できる。

#### 【0025】

データ配線は、少なくとも、各画素の表示データに対応する電位が駆動用トランジスタの電流制御端子に与えられて、第1コンデンサに対応する電荷が保持される動作が完了するまで画素に接続されればよい。従って、各画素は、駆動用トランジスタの閾値電圧補償期間において、データ配線を占有する必要がない。この結果、駆動用トランジスタの閾値電圧のばらつきを補償しながら、1画素当たりの選択期間の長さを短くすることができる表示装置を実現することができるという効果を奏する。

#### 【0026】

本発明の表示装置は、上記課題を解決するために、上記第1コンデンサの上記他方端子は第1配線に接続されていることを特徴としている。また、上記第2期間に上記第1配線

10

20

30

40

50

の電位が変化して、上記駆動用トランジスタがOFF状態からON状態に変化する、または、OFF状態を維持することにより、上記駆動電流の有無が決定されてもよい。

【0027】

上記の発明によれば、第1コンデンサの他方端子に第1配線を接続し、第2期間でその第1配線の電位を変化させることで、駆動用トランジスタの電流制御端子の電位を変化させ、駆動用トランジスタの出力電流を所望の値に設定することができるという効果を奏する。

【0028】

本発明の表示装置は、上記課題を解決するために、上記駆動用トランジスタの上記電流出力端子と上記データ配線との間に第3スイッチ用トランジスタが接続されていることを特徴としている。また、上記表示データ付与期間に上記第3スイッチ用トランジスタがON状態となつてもよい。

10

【0029】

上記の発明によれば、第1期間において、第1スイッチ用トランジスタをOFF状態としてから、第2スイッチ用トランジスタをON状態とし、更に第3スイッチ用トランジスタをON状態とできる。このとき、第3スイッチ用トランジスタを通して駆動用トランジスタの電流出力端子へ電位Vdaを与える。この電位Vdaを制御することで、上記第1期間において、電気光学素子へ電流を流さなくても、駆動用トランジスタのON/OFF状態を制御できるという効果を奏する。

【0030】

20

例えば、駆動用トランジスタがp型で、基準電位端子電位をVsとするとき、上記電位Vdaが駆動用トランジスタの最小閾値電圧-Vth(min)に対し、

$$Vs - Vth(min) < Vda \quad \dots \text{ (条件1)}$$

であれば、駆動用トランジスタ(Q1)はその閾値電圧に依らずOFF状態となる。

【0031】

逆に、上記電位Vdaが駆動用トランジスタ(Q1)の最大閾値電圧-Vth(max)に対し、

$$Vs - Vth(max) > Vda \quad \dots \text{ (条件2)}$$

であれば駆動用トランジスタはその閾値電圧に依らずON状態となる。

【0032】

30

その後、第3スイッチ用トランジスタをOFF状態とする。このとき、条件1では、駆動用トランジスタはOFF状態となり、駆動用トランジスタの電流制御端子の電位はこの電位Vdaのままとなる。条件2では、駆動用トランジスタがON状態となり、駆動用トランジスタの電流制御端子の電位はVs-Vthとなる。

【0033】

そして、第2期間でその駆動用トランジスタの電流制御端子の電位または駆動用トランジスタの基準電位端子の電位を変化させることで、駆動用トランジスタの電流制御端子の電位がVs-Vthとなった駆動用トランジスタを、その閾値電圧に依らず一定の電流が流れる状態とすることができます。

【0034】

40

また、この電位変化が電位Vsから電位Vs-Vxに変化するとした場合、

$$Vs - Vth(min) < Vda - Vx$$

であれば、駆動用トランジスタの電流制御端子の電位がVdaである駆動用トランジスタの出力状態をOFF状態のままですることができる。

【0035】

本発明の表示装置は、上記課題を解決するために、上記駆動用トランジスタの上記電流制御端子と上記データ配線との間に第4スイッチ用トランジスタが接続されていることを特徴としている。

【0036】

上記の発明によれば、第1期間において、第1スイッチ用トランジスタをOFF状態と

50

してから、第4スイッチ用トランジスタをON状態にできる。そして、第1期間の最初に第4スイッチ用トランジスタを通して駆動用トランジスタの電流出力端子へ電位Vdaを与える。この電位Vdaを制御することで、上記第1期間において、電気光学素子へ電流を流さなくても、駆動用トランジスタのON/OFF状態を制御できるという効果を奏する。

【0037】

本発明の表示装置は、上記課題を解決するために、上記駆動用トランジスタの上記電流出力端子と上記データ配線とは第2コンデンサを介して接続されていることを特徴としている。

【0038】

上記の発明によれば、第1期間において、第2スイッチ用トランジスタをON状態としてから、第1スイッチ用トランジスタをOFF状態とする。このため、駆動用トランジスタは一端ON状態となり、電気光学素子へ向け電流が流れ、その後、駆動用トランジスタがOFF状態となる。

【0039】

その後、第2スイッチ用トランジスタをOFF状態とする直前に、データ配線の電位をHigh電位とすることで、駆動用トランジスタの電流制御端子は閾値電位Vs-Vthより大きな電位となり、駆動用トランジスタの電流制御端子にOFF電位が保持される。

【0040】

逆に、第2スイッチ用トランジスタをOFF状態とする直前に、データ配線の電位をLow電位のままとすることで、駆動用トランジスタの電流制御端子は閾値電位Vs-Vthのままとなる。

【0041】

その後、第2スイッチ用トランジスタをOFF状態として、この電位を保持することで、駆動用トランジスタのON/OFF状態を制御できるという効果を奏する。また、このON状態は駆動用トランジスタのその閾値電圧に依らず一定の電流を与える状態とができるという効果を奏する。

【0042】

なお、第2コンデンサと直列にスイッチ用トランジスタを配置すれば、そのスイッチ用トランジスタをOFF状態とすることで、データ配線に繋がる容量を小さくできる。このため、第2期間における、ソースドライバ回路の負荷を減らし、データ配線の電位変化速度を早くできるので好ましい。

【0043】

本発明の表示装置は、上記課題を解決するために、上記駆動用トランジスタの上記基準電位端子と上記データ配線との間に第5スイッチ用トランジスタが接続され、上記駆動用トランジスタの上記基準電位端子と、上記駆動用トランジスタの出力電流を生成する電源の電位を与える電源配線との間に、第6スイッチ用トランジスタが接続されていることを特徴としている。

【0044】

上記の発明によれば、第1期間に駆動用トランジスタの電流制御端子の電位がデータ配線の電位より閾値電位Vthだけ大きい（または小さい）状態となる。そして、第2期間において、駆動用トランジスタの基準電位端子の電位を変化させ、駆動用トランジスタの出力電流を所望の電流値に設定できるという効果を奏する。

【0045】

本発明の表示装置は、上記課題を解決するために、上記第1コンデンサの上記他方端子と、上記駆動用トランジスタの出力電流を生成する電源の電位を与える電源配線との間に、第3コンデンサが接続され、上記第1コンデンサの上記他方端子と上記データ配線との間に第7スイッチ用トランジスタが接続されていることを特徴としている。

【0046】

上記の発明によれば、第1期間に駆動用トランジスタの電流制御端子の電位が駆動用ト

10

20

30

40

50

ランジスタの基準電位端子の電位  $V_s$  より閾値電位  $V_{th}$  だけ大きい（または小さい）状態となる。そして、第2期間において、上記第1コンデンサの他方端子電位を変化させ、駆動用トランジスタの出力電流を所望の電流値に設定できるという効果を奏する。

【0047】

本発明の表示装置は、上記課題を解決するために、上記第1コンデンサの上記他方端子と所定の電位を与える第2配線との間に第8スイッチ用トランジスタが接続され、上記第1コンデンサの上記他方端子と上記データ配線との間に第7スイッチ用トランジスタが接続されていることを特徴としている。

【0048】

上記の発明によれば、第1期間に駆動用トランジスタの電流制御端子の電位が駆動用トランジスタの基準電位端子の電位  $V_s$  より閾値電位  $V_{th}$  だけ大きい（または小さい）状態となる。そして、第2期間において、上記第1コンデンサの他方端子電位を変化させ、駆動用トランジスタの出力電流を所望の電流値に設定できるという効果を奏する。

10

【0049】

また、第2配線の電位を固定することもできるし、RGB各色で共通化することもできる。

【0050】

本発明の表示装置の駆動方法は、上記課題を解決するために、表示光源としての電流駆動型の電気光学素子と、電流制御端子と基準電位端子との間に印加される電圧により制御される出力電流を電流出力端子から上記電気光学素子に駆動電流として供給する駆動用トランジスタとが、マトリックス状に設けられた各画素に配置され、上記駆動電流が、データ配線から上記各画素に供給される、上記電気光学素子の点灯または消灯を示すデジタルの表示データに対応する表示装置において、上記駆動用トランジスタと第1スイッチ用トランジスタと上記電気光学素子とが直列に接続され、上記駆動用トランジスタの上記電流制御端子に第1コンデンサの一方端子が接続され、上記駆動用トランジスタの上記電流制御端子と上記電流出力端子との間に第2スイッチ用トランジスタが接続された表示装置の駆動方法であって、上記データ配線から上記各画素の上記表示データに対応する電位であつて、上記表示データが点灯を示すものである場合には上記駆動用トランジスタをON状態とする電位を、また、上記表示データが消灯を示すものである場合には上記駆動用トランジスタをOFF状態とする電位を、上記駆動用トランジスタの上記電流制御端子に与えて、上記第1コンデンサに、対応する電荷を保持させた状態から始まる、あるいは、対応する電荷を保持する動作と同時に第1期間において、上記第2スイッチ用トランジスタをON状態とし、上記第1スイッチ用トランジスタをOFF状態とし、第2期間において、上記第1コンデンサの他方端子の電位または、上記駆動用トランジスタの上記基準電位端子電位を変化させることにより、上記駆動用トランジスタの出力電流を設定することを特徴としている。

20

【0051】

上記の発明によれば、各画素は、駆動用トランジスタの閾値電圧補償期間において、データ配線を占有する必要がない。この結果、駆動用トランジスタの閾値電圧のばらつきを補償しながら、1画素当たりの選択期間の長さを短くすることのできる表示装置の駆動方法を実現することができるという効果を奏する。

30

【発明の効果】

【0052】

本発明の表示装置は、以上のように、上記駆動用トランジスタと第1スイッチ用トランジスタと上記電気光学素子とが直列に接続され、上記駆動用トランジスタの上記電流制御端子に第1コンデンサの一方端子が接続され、上記駆動用トランジスタの上記電流制御端子と上記電流出力端子との間に第2スイッチ用トランジスタが接続され、上記データ配線から上記各画素の表示データに対応する電位が上記駆動用トランジスタの上記電流制御端子に与えられて、上記第1コンデンサに、対応する電荷が保持された状態から始まる、あるいは、対応する電荷を保持する動作と同時に行われる第1期間において、上記第2スイ

40

50

ツチ用トランジスタがON状態となり、上記第1スイッチ用トランジスタがOFF状態となることにより、上記駆動用トランジスタの閾値電圧が補償され、第2期間において、上記第1コンデンサの他方端子の電位または、上記駆動用トランジスタの上記基準電位端子の電位が変化することにより、上記駆動用トランジスタの出力電流が設定される。

【0053】

それゆえ、駆動用トランジスタの閾値電圧のばらつきを補償しながら、1画素当たりの選択期間の長さを短くすることのできる表示装置を実現することができるという効果を奏する。

【発明を実施するための最良の形態】

【0054】

本発明の実施の形態について図1ないし図24に基づいて説明すれば、以下の通りである。

10

【0055】

本発明に用いられるスイッチング素子は低温ポリシリコン TFT や CG (Continuous Grain)シリコン TFT などで構成できるが、本実施の形態では CGシリコン TFT を用いることとする。

【0056】

ここで、CGシリコン TFT の構成は、例えば非特許文献1に発表されており、CGシリコン TFT の製造プロセスは、例えば非特許文献2に発表されている。すなわち、CGシリコン TFT の構成およびその製造プロセスは何れも公知であるため、ここではその詳細な説明は省略する。

20

【0057】

また、本実施の形態で用いる電気光学素子である有機EL素子についても、その構成は、例えば非特許文献3に発表されており公知であるため、ここではその詳細な説明は省略する。

【0058】

〔実施の形態1〕

本実施の形態では、本発明の表示装置の第1の例について説明する。

【0059】

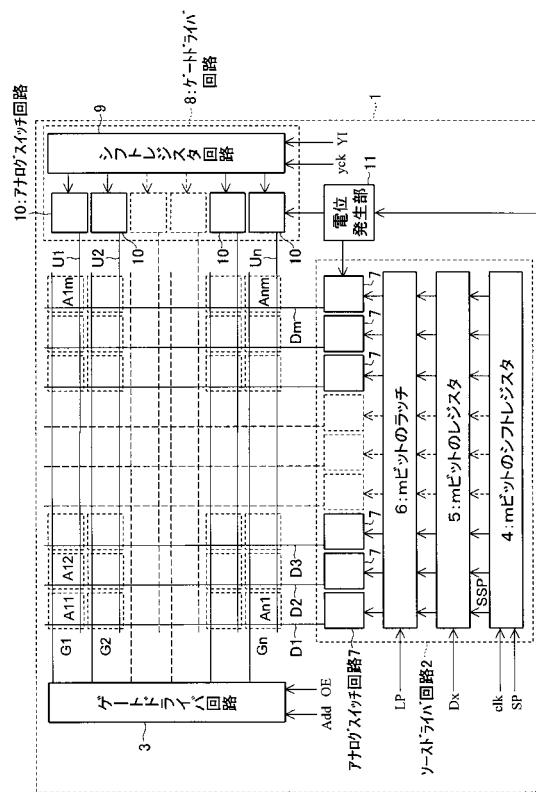

本実施の形態の表示装置1は、図2に示すように、画素回路A<sub>i</sub>j (i = 1 ~ n, j = 1 ~ m)をマトリックス状に配置し、その配線制御回路としてゲートドライバ回路3, 8、ソースドライバ回路2を配置し、その内部電圧発生回路として電位発生部11を有している。

30

【0060】

各画素回路A<sub>i</sub>jは、データ配線D<sub>j</sub>とゲート配線G<sub>i</sub>とが交差する領域に対応して配置されている。また、上記ソースドライバ回路2は、mビットのシフトレジスタ4、mビットのレジスタ5、mビットのラッチ6、及び、m個のアナログスイッチ回路7...から構成される。

【0061】

上記ソースドライバ回路2においては、mビットのシフトレジスタ4の先頭のレジスタへスタートパルスS<sub>P</sub>が入力され、そのスタートパルスS<sub>P</sub>がクロックc<sub>1</sub>kでシフトレジスタ4内を転送され、同時にレジスタ5にタイミングパルスS<sub>SP</sub>として出力される。mビットのレジスタ5は、シフトレジスタ4から送られてくるタイミングパルスS<sub>SP</sub>により、入力された1ビットのデータD<sub>x</sub>を対応するデータ配線D<sub>j</sub>の位置に保持する。ラッチ6ではこの保持されたmビットのデータをラッチパルスL<sub>P</sub>のタイミングで取り込み、アナログスイッチ回路7へ出力する。アナログスイッチ回路7では、入力されたデータに対応する電位V<sub>H</sub>, V<sub>L</sub>を電位発生部11から選択しデータ配線D<sub>j</sub>へ出力する。

40

【0062】

また、ゲートドライバ回路3は図示しないデコーダ回路とバッファ回路とから構成され、入力されたアドレスA<sub>d</sub>dをデコーダ回路でデコードし、制御信号O<sub>E</sub>で制御されたタ

50

イミングでバッファを通して、対応したゲート配線  $G_i$  へ出力する。

【0063】

ゲートドライバ回路 8 はシフトレジスタ回路 9 とアナログスイッチ回路 10... とから構成され、入力された制御信号  $Y_i$  等をシフトレジスタ回路 9 の先頭に入力し、クロック  $y_{ck}$  でシフトレジスタ回路 9 内を転送し、アナログスイッチ回路 10 や図示しないバッファ回路へ出力する。アナログスイッチ回路 10 は、入力されたデータに対応して、電位発生部 11 から電圧  $V_{cc}$  か電圧  $V_c$  を選択し電位配線  $U_i$  へ出力する。バッファ回路は入力されたデータを増幅し、対応した制御配線  $P_i$ ,  $R_i$  へ出力する。

【0064】

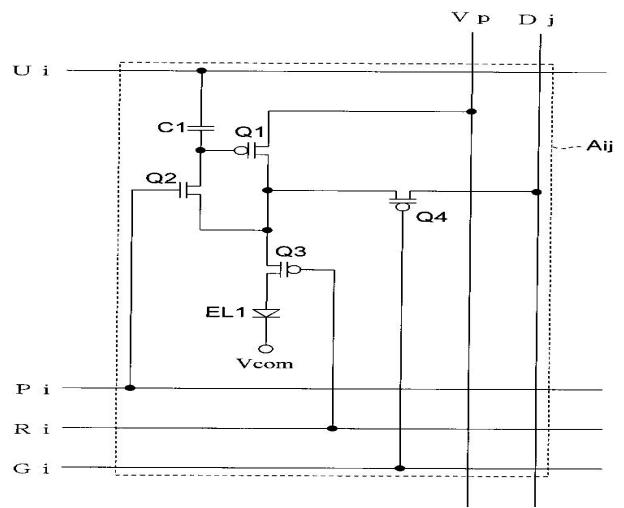

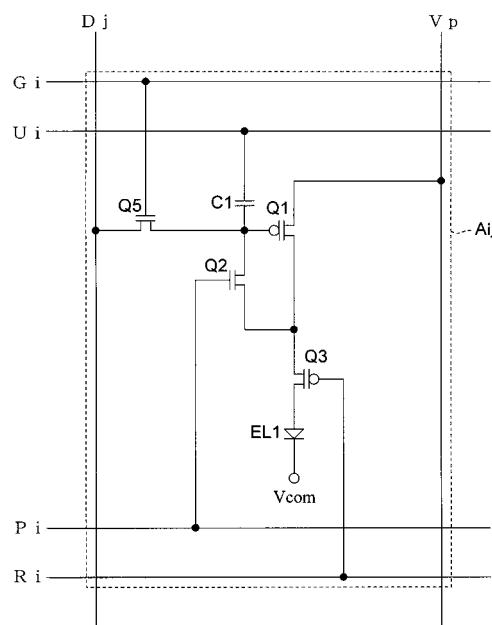

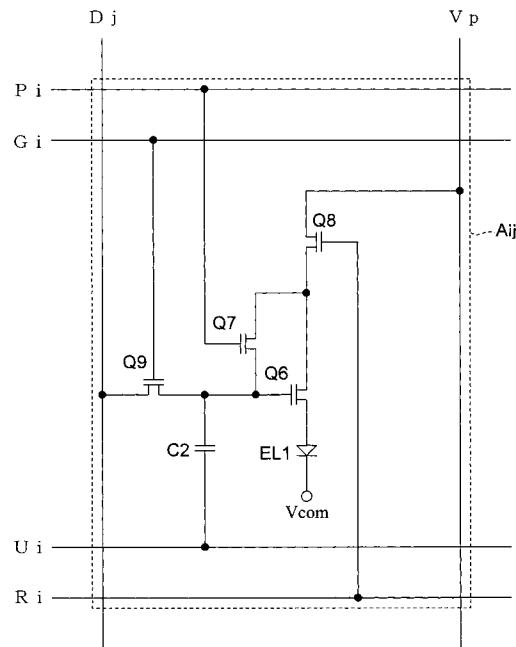

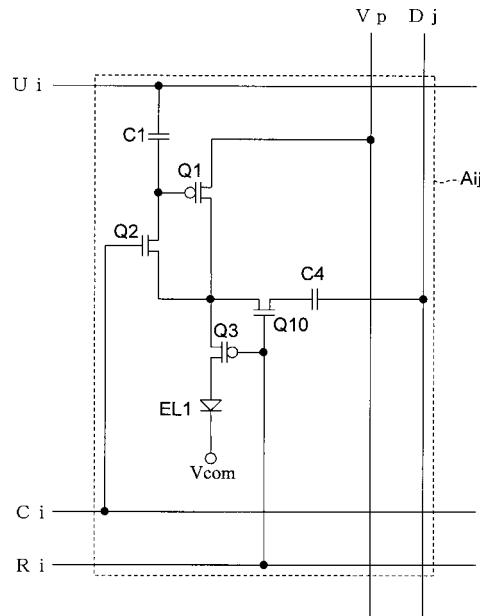

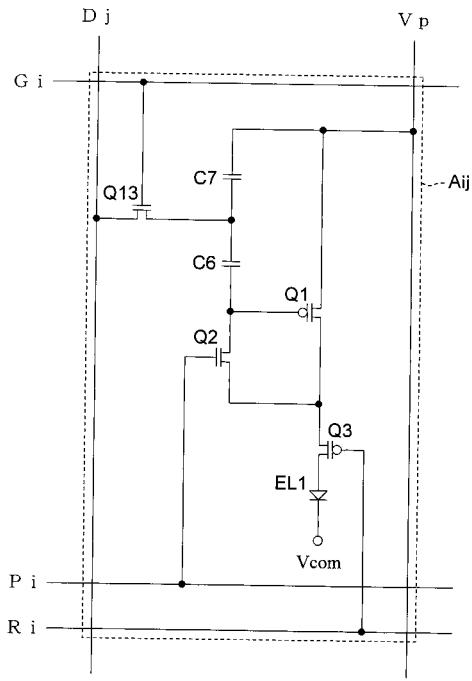

図 1 に、画素回路  $A_{ij}$  の構成を示す。

10

【0065】

この画素回路  $A_{ij}$  ではデータ配線  $D_j$  (第 2 配線) とゲート配線  $G_i$  が交差する付近に駆動用 TFT : Q1 (駆動用トランジスタ) と有機 EL : EL1 (電気光学素子) が配置されている。そして、電源配線  $V_p$  から共通配線  $V_{com}$  へ至る経路に駆動用 TFT : Q1 とスイッチ用 TFT : Q3 (第 1 スイッチ用トランジスタ) と有機 EL : EL1 とがこの順で直列に接続されている。有機 EL : EL1 は電流駆動型の電気光学素子であり、表示光源となる。

【0066】

駆動用 TFT : Q1 のゲート端子 (電流制御端子) にはコンデンサ C1 (第 1 コンデンサ) の一方端子が接続され、駆動用 TFT : Q1 のゲート端子とドレイン端子 (電流出力端子)との間にはスイッチ用 TFT : Q2 (第 2 スイッチ用トランジスタ) が接続されている。駆動用 TFT : Q1 は、ゲート端子とソース端子との間に印加される電圧により出力電流が制御される駆動用トランジスタである。なお、ドレイン端子は駆動用 TFT が n 型の場合は電流が流入する側の端子となるが、この場合も有機 EL 素子の駆動電流を駆動用 TFT が決定しているので、そのドレイン端子を電流出力端子と称する。

20

【0067】

また、コンデンサ C1 の他方端子には電位配線  $U_i$  (第 1 配線) が接続され、駆動用 TFT : Q1 のドレイン端子 (電流出力端子) とデータ配線  $D_j$  との間にはスイッチ用 TFT : Q4 (第 3 スイッチ用トランジスタ) が接続されている。

【0068】

30

各スイッチ用 TFT : Q2, Q3, Q4 のゲート端子には順に制御配線  $P_i$ 、制御配線  $R_i$ 、ゲート配線  $G_i$  が接続されている。

【0069】

なお、駆動用 TFT : Q1, スイッチ用 TFT : Q3, Q4 は p 型 TFT であり、スイッチ用 TFT : Q2 は n 型 TFT である。

【0070】

この画素回路構成では、駆動用 TFT : Q1 が取りうる状態は ON 状態および OFF 状態である。このため、本実施の形態では時間分割階調表示を用いることにする。

【0071】

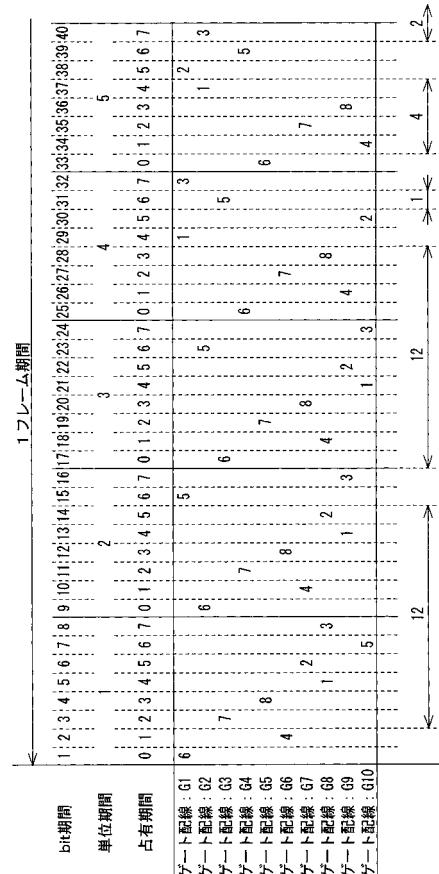

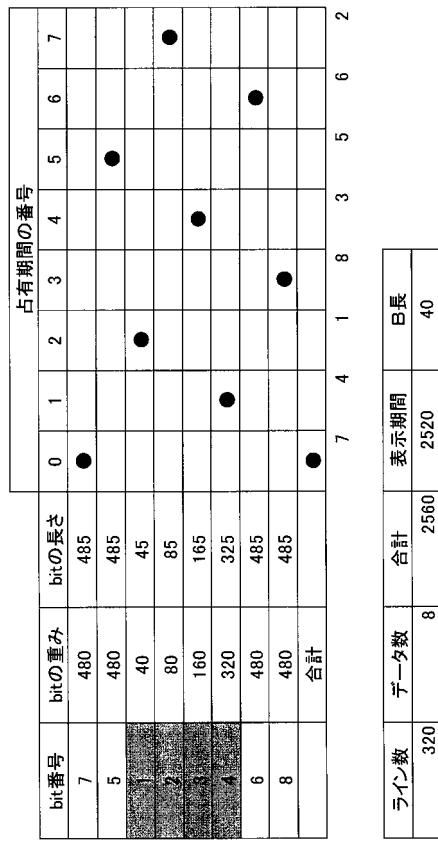

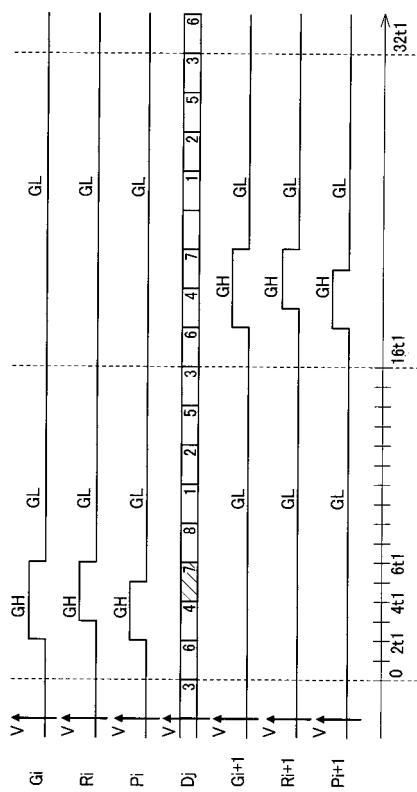

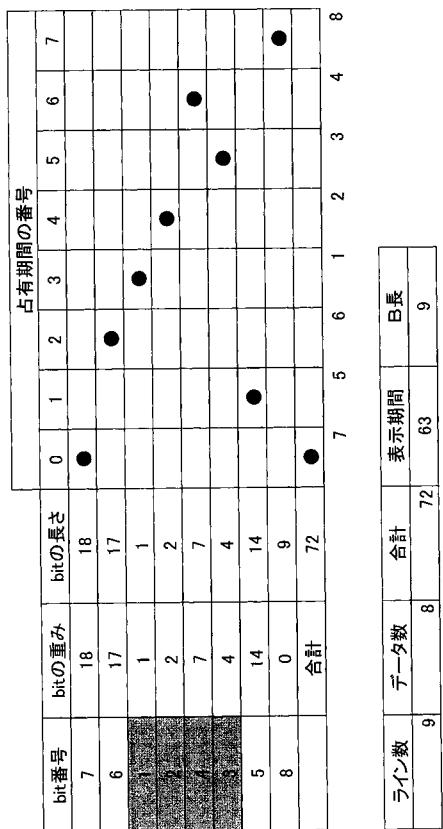

この時間分割階調表示方法の例として特許文献 3 等があるが、ここでは図 3 に示す時間配列を用いることにする。

40

【0072】

図 3 の時間配列は、各画素回路  $A_{ij}$  に 1 フレーム期間に時系列でどのように 1, 0 のデータを供給するかを表したものである。画素回路  $A_{ij}$  は 1 フレーム期間に 8 ビットからなるデータを 1 ビットずつ時系列でソースドライバ回路 2 から供給される。「bit 番号」および「bit の重み」の欄から分かるように、各 bit1 ~ bit8 の重みは 1 : 2 : 4 : 8 : 12 : 12 : 12 : 12 となっている。この各重みは点灯 / 消灯期間の長さを表しており、発光強度を一定にして点灯期間が合計でどのような長さとするかによって 1 フレーム期間に感じる画素の明るさを変えるようにしている。これらの bit の重みを用いると、重み 12 を 0 個用いたときに重み 1, 2, 4, 8 により 0 ~ 15 が表現でき、

50

重み 12 を 1 個用いたときに 12 ~ 27 が表現でき、12 を 2 個用いたときに 24 ~ 39 が表現でき、12 を 3 個用いたときに 36 ~ 51 が表現でき、12 を 4 個用いたときに 48 ~ 63 が表現でき、全部で 0 ~ 63 の 64 階調表示が可能になる。

#### 【0073】

この 64 階調表示を、各画素で表示する順番を「占有期間の番号」が重ならないように 12 : 12 : 1 : 4 : 2 : 8 : 12 : 12 とする。すなわち画素回路 Aij に供給する「bit 番号」の順番を 6 5 1 3 2 4 8 7 となるよう並べ替えて行う。これはこれら「占有期間の番号」に対応する「bit の重み」に更に非表示期間（ブランкиング期間）を加えた「bit の長さ」が、欄のように 14 : 14 : 3 : 6 : 4 : 10 : 15 : 14 とし、0 / 8 の余り 0、14 / 8 の余り 6、(14 + 14) / 8 の余り 4、(14 + 14 + 3) / 8 の余り 7、・・・等が互いに重ならないようにするためである。従って、1 フレーム期間は、bit の長さの合計  $14 + 14 + 3 + 6 + 4 + 10 + 15 + 14 = 80$  となる。bit の長さ 1 を 1 bit 期間とすると、1 フレーム期間は 80 bit 期間となる。また、1 bit 期間は、画素回路 Aij に 1 bit 分のデータを設定するために、データ配線 Dj にデータに対応した電位を出力する期間である。

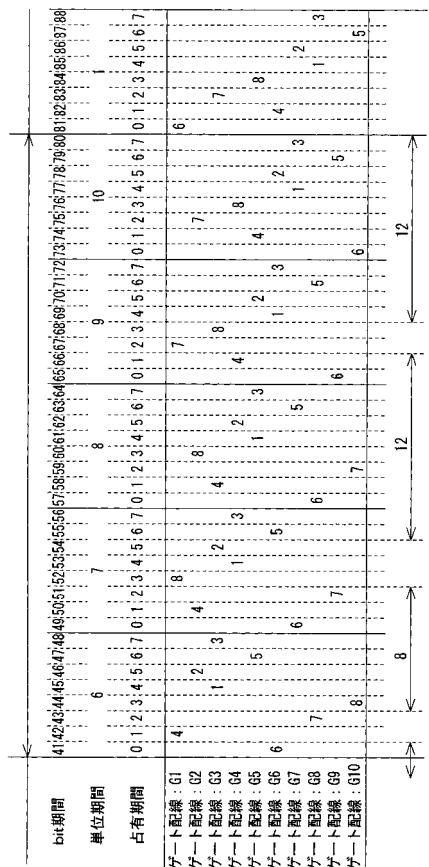

#### 【0074】

これをライン数（ゲート配線 Gi の数）が 10 である場合で考え、あるデータ配線 Dj に、各 bit 期間にどのゲート配線 Gi につながる画素用の何 bit 目のデータを供給するかを図 4 および図 5 に示す。図 4 は 1 フレーム期間の前半部分のデータ供給を表し、図 5 は 1 フレーム期間の後半部分のデータ供給を表す。

#### 【0075】

図 4 および図 5 において、ゲート配線 G1 の欄は、あるデータ配線 Dj のゲート配線 G1 につながる画素 A1j に時系列でどのように bit データを供給するのかを表している。この画素 A1j には、第 1 bit 期間で bit 6 のデータが供給され、14 bit 期間後の第 15 bit 期間で bit 5 のデータが供給され、さらに 14 bit 期間後の第 29 bit 期間で bit 1 のデータが供給され、さらに 3 bit 期間後の第 32 bit 期間で bit 3 のデータが供給され、さらに 6 bit 期間後の第 38 bit 期間で bit 2 のデータが供給され、さらに 4 bit 期間後の第 42 bit 期間で bit 4 のデータが供給され、さらに 10 bit 期間後の第 52 bit 期間で bit 8 のデータが供給され、さらに 15 bit 期間後の第 67 bit 期間で bit 7 のデータが供給される。そして、さらに 14 bit 期間後の第 81 bit 期間で最初の第 1 bit 期間に戻り、bit 6 のデータをデータ配線 Dj に供給する。

#### 【0076】

なお、ゲート配線 G1 によって選択される画素 A1j について、図 4 および図 5 の最下部に、bit の長さのうちブランкиング期間を除いた bit の重みに対応する期間、すなわちその画素 A1j が点灯しうる期間を示してある。このように、bit 番号 6, 5, 1, 3, 2, 4, 7 の各 bit の長さの最初の 2 bit 期間、および、bit 番号 8 の bit の長さの最初の 3 bit 期間はブランкиング期間とする。これは他のゲート配線でも同様である。

#### 【0077】

上記データ配線 Dj につながる画素のうち次のゲート配線 Gi + 1 につながる画素には、ゲート配線 Gi に対応する bit データの供給タイミングを 8 bit 期間遅らせたタイミングでデータ配線 Dj に供給する。例えばゲート配線 G2 の欄には、上記ゲート配線 G1 の bit データの供給タイミングを 8 bit 期間遅らせてデータ配線 Dj に供給することが示されている。このように各ゲート配線 Gi に bit データを供給するタイミングを作っていくと、同じデータ配線 Dj に対して、第 1 bit 期間にゲート配線 G1 につながる画素 A1j への bit 6 のデータを供給し、第 2 bit 期間にゲート配線 G6 につながる画素 A6j への bit 4 のデータを供給し、第 3 bit 期間にゲート配線 G3 につながる画素 A3j への bit 7 のデータを供給する、といったようにデータ供給が行われる。

#### 【0078】

10

20

30

40

50

このように、各ゲート配線  $G_i$  に対応する  $bit$  データは、同じデータ配線  $D_j$  に、互いにタイミングが重なることなく供給される。また、同じデータ配線  $D_j$  に対し、各  $bit$  期間にはいずれかのゲート配線  $G_i$  に対応する  $bit$  データが供給される。

#### 【0079】

そこで、図4および図5の1フレーム期間に相当する80bit期間を8bit期間毎にまとめてグループ化し、各グループに順に単位期間1~10という記号を割り当てる。また、各単位期間内の8つのbit期間に順に占有期間0~7という記号を割り当てる。そうすると、bit6, 5, 1, 3, 2, 4, 8, 7は順に必ず占有期間0, 6, 4, 7, 5, 1, 3, 2に出現する。

#### 【0080】

そこで、上記対応を、各bitを縦軸、占有期間を横軸にして、対応するところに『』で記すことにより示すと、図3の「bitの長さ」対「占有期間の番号」のようになる。

#### 【0081】

なお、上記時間配列では、各bitの長さが各bitの重みより大きくなっている。この期間の差は、後述する図6のタイミングチャートに示すように、電位配線  $U_i$  を  $V_{cc}$  等にして、強制的に駆動用TFT:Q1をOFF状態とするプランキング期間で埋めることにする。プランキング期間は各bitの全占有期間の最初に設けられる。

#### 【0082】

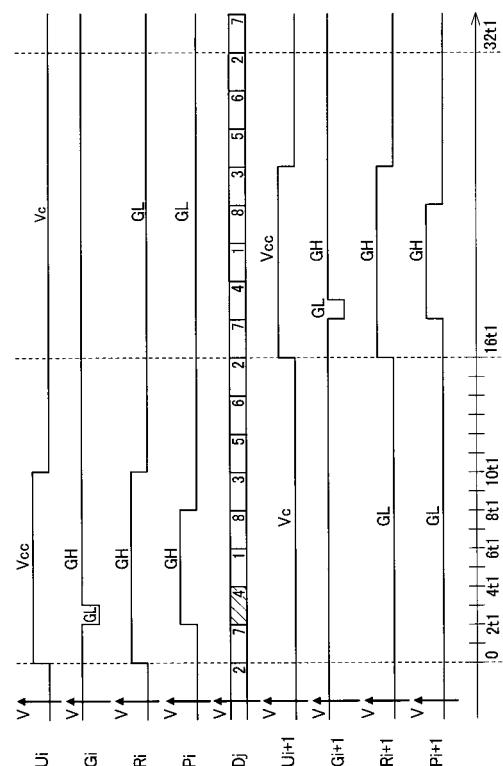

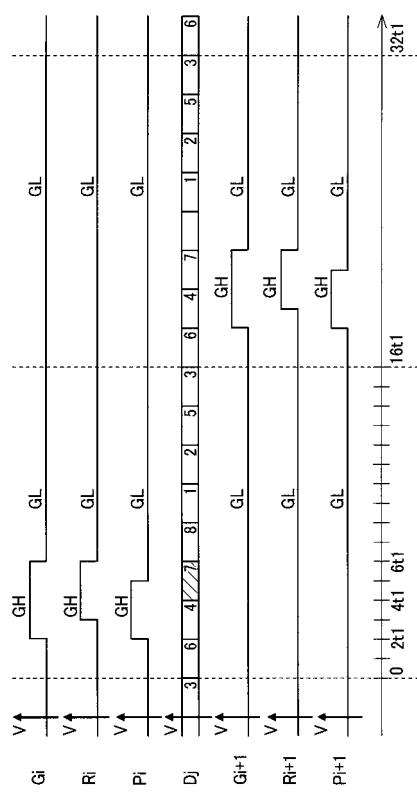

以下、図1の画素回路  $A_{ij}$  の動作を、このプランキング期間を含め図6に示すタイミングチャートを用いて説明する。

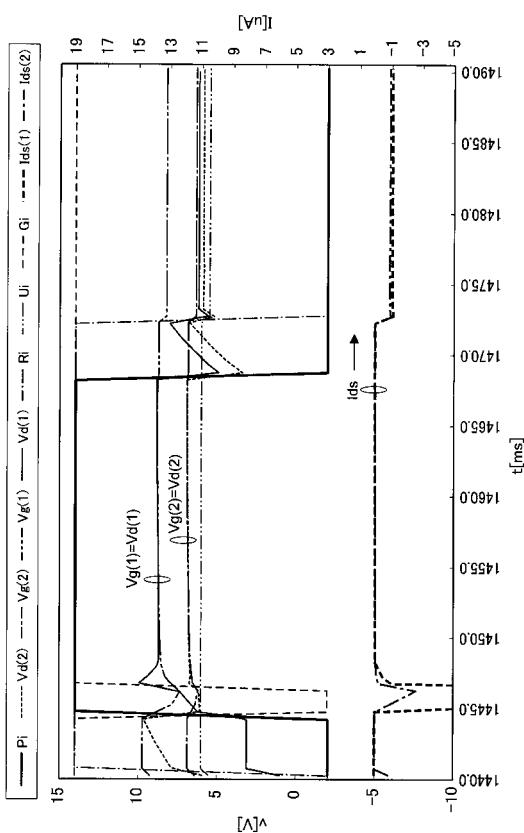

#### 【0083】

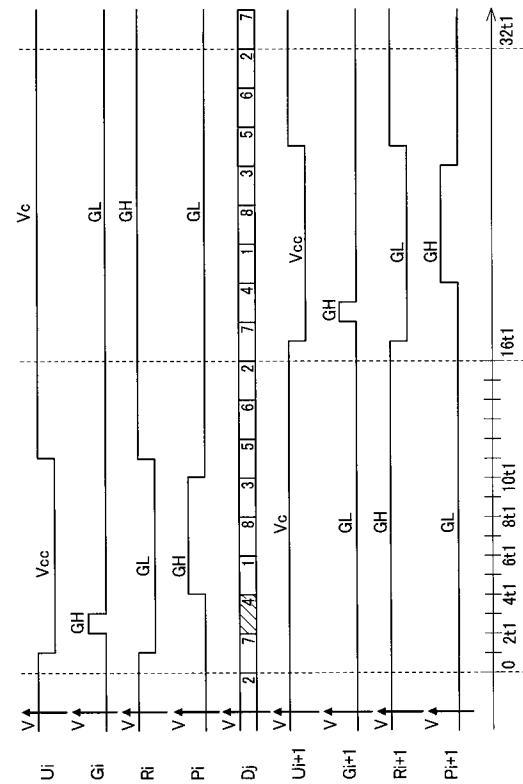

図6において  $U_i, G_i, R_i, P_i$  は画素回路  $A_{ij}$  に対応し、 $U_{i+1}, G_{i+1}, R_{i+1}, P_{i+1}$  は画素回路  $A_{i+1,j}$  に対応する。 $D_j$  はデータ配線  $D_j$  に供給するbit1~8のデータを示している。また、t1分の期間は1bit期間の2分の1である。

#### 【0084】

時刻  $4t_1 \sim 6t_1$  の期間は画素回路  $A_{ij}$  に bit7 のデータを設定する bit 期間であり、時刻  $4t_1 \sim 8t_1$  の期間はプランキング期間である。

#### 【0085】

時刻  $4t_1$  において、電位配線  $U_i$  を電位  $V_{cc}$  としてプランキング期間を開始する。そして、制御配線  $R_i$  を High (GH) として、スイッチ用TFT:Q3をOFF状態とする。また、制御配線  $P_i$  を High (GH) として、スイッチ用TFT:Q2をON状態とする。また、ゲート配線  $G_i$  を Low (GL) として、スイッチ用TFT:Q4をON状態とする。

#### 【0086】

このとき、データ配線  $D_j$  に与える電位を  $V_L$  とすれば駆動用TFT:Q1はゲート電位が低くなつてON状態となり、 $V_H$  とすれば駆動用TFT:Q1はゲート電位が高くなつてOFF状態となる。

#### 【0087】

即ち、電源配線  $V_p$  の電位を  $V_p$ 、駆動用TFT:Q1の閾値電圧の絶対値がばらつきの最大（絶対値が最大）で  $V_{th}(max)$ 、ばらつきの最小（絶対値が最小）で  $V_{th}(min)$  であるとして、

$$V_L < V_p - V_{th}(max)$$

$$V_H > V_p - V_{th}(min)$$

とする。

#### 【0088】

これにより、例えば、データ配線  $D_j$  に電位  $V_L$  を与えると、スイッチ用TFT:Q2, Q4がON状態であるので、駆動用TFT:Q1のゲート電位も  $V_L$  となる。このため、駆動用TFT:Q1はその閾値電圧  $V_{th}$  がばらつきのどこにあってもON状態となる

10

20

30

40

50

。逆に、データ配線  $D_j$  に電位  $V_H$  を与えると、駆動用 TFT : Q1 のゲート電位も  $V_H$  となる。このため、駆動用 TFT : Q1 はその閾値電位  $V_{th}$  がばらつきのどこにあっても OFF 状態となる。

【0089】

その後、時刻  $5t_1$  でゲート配線  $G_i$  を High (GH) として、スイッチ用 TFT : Q4 を OFF 状態とする。

【0090】

次に、時刻  $5t_1 \sim 7t_1$  の期間は、駆動用 TFT : Q1 の閾値補償期間（第1期間）となる。時刻  $5t_1$  で駆動用 TFT : Q1 が ON 状態である場合、すなわちデータ配線  $D_j$  が電位  $V_L$  である場合、閾値補償期間に電源配線  $V_p$  から駆動用 TFT : Q1 のドレインを介して駆動用 TFT : Q1 のゲートおよびコンデンサ C1 の一方端子に電流が流れ込むため、駆動用 TFT : Q1 のゲート電位は  $V_p - V_{th}$  まで上昇して OFF 状態となる（以下、状態  $V_L$  と称する）。一方、時刻  $5t_1$  で駆動用 TFT : Q1 が OFF 状態である場合、すなわちデータ配線  $D_j$  が電位  $V_H$  である場合、閾値補償期間に駆動用 TFT : Q1 のゲート電位は  $V_H$  のままとなる（以下、状態  $V_H$  と称する）。

【0091】

その後、時刻  $7t_1$  で制御配線  $P_i$  を Low (GL) として、スイッチ用 TFT : Q2 を OFF 状態とし、駆動用 TFT : Q1 の閾値補償期間を終了する。これにより、コンデンサ C1 の電荷、従って駆動用 TFT : Q1 のゲート・ソース間電圧が保持される。従って、駆動用 TFT : Q1 のゲート電位は閾値補償期間に状態  $V_L$  となった場合には電位  $V_p - V_{th}$  に保持され、閾値補償期間に状態  $V_H$  となった場合には電位  $V_H$  に保持される。本実施の形態では、第1期間としての閾値補償期間は、データ配線  $D_j$  から各画素の表示データに対応する電位が駆動用 TFT Q1 のゲート端子に与えられて、コンデンサ C1 に、対応する電荷が保持された状態から始まる。

【0092】

そして、時刻  $8t_1$  で制御配線  $R_i$  を Low (GL) として、スイッチ用 TFT : Q3 を ON 状態とし、電位配線  $U_i$  の電位を  $V_c$  ( $V_c < V_{cc}$ ) に変化させ、ブランкиング期間を終了する。時刻  $8t_1$  以降は第2期間である。

【0093】

このとき、電位配線  $U_i$  は  $V_{cc} - V_c$  だけ電位が下降するので、閾値補償期間に状態  $V_H$  となった場合には、電位が  $V_H$  であった駆動用 TFT : Q1 のゲート電位、すなわちコンデンサ C1 の一方端子の電位は  $V_H - (V_{cc} - V_c)$  に変化する。従って、

$$V_H - (V_{cc} - V_c) > V_p - V_{th} \text{ (min)}$$

としておけば、状態  $V_H$  の駆動用 TFT : Q1 は OFF 状態のままとなる。一方、閾値補償期間に状態  $V_L$  となった場合の駆動用 TFT : Q1 のゲート電位は

$$V_p - V_{th} - (V_{cc} - V_c)$$

となり、駆動用 TFT : Q1 の閾値状態から  $V_{cc} - V_c$  という一定電圧だけ低い電位となる。従って、駆動用 TFT : Q1 は、その閾値電圧  $V_{th}$  に依らず一定電流が流れる状態となる。

【0094】

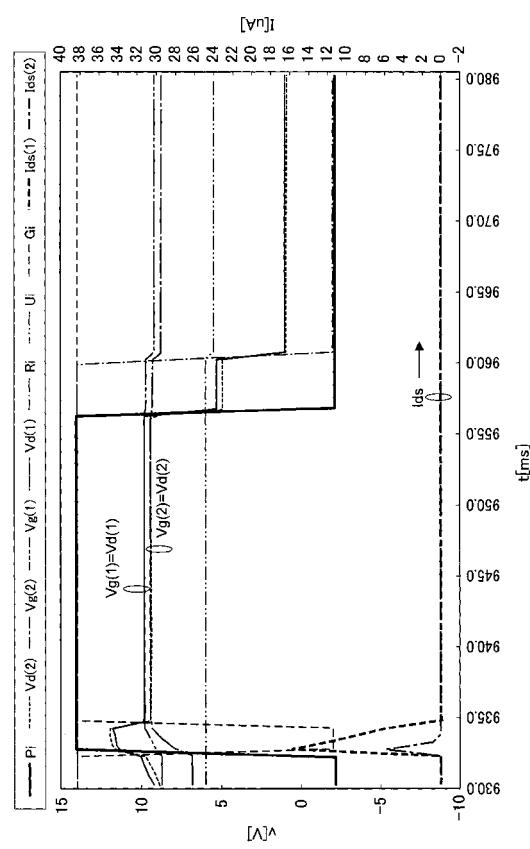

そこで、閾値補償期間に状態  $V_L$  となる場合の駆動用 TFT : Q1 のゲート電位  $V_g$ 、ドレイン電位  $V_d$ 、ソース・ドレイン間電流  $I_{ds}$  をシミュレーションした結果を図7に示す。なお、電圧および電流の符号に付されている(1)は、閾値  $V_{th}$  が最小 ( $V_{th} \text{ (min)}$ ) で移動度  $\mu$  が最大である場合に対応し、(2)は、閾値  $V_{th}$  が最大 ( $V_{th} \text{ (max)}$ ) で移動度  $\mu$  が最小である場合に対応する。また、図7の電圧の立ち上がりおよび立ち下がりタイミングは図6と一致しておらず、制御配線  $R_i$  が High (GH) となってから制御配線  $P_i$  が High (GH)、ゲート配線  $G_i$  が Low (GL) となっているが、これはスイッチ用 TFT : Q3 を先に OFF 状態としたものであり、図6と本質的には差はない。

【0095】

10

20

30

40

50

図 7 のシミュレーション結果から判るとおり、制御配線  $R_i$  を  $L_o w (G L)$  として、電位配線  $U_i$  を  $V_c$  とした後、駆動用  $TFT:Q1$  のソース・ドレン間電流  $I_{ds}$  は、その閾値電圧に依らず（移動度の影響を残し）ほぼ一定となる。

【0096】

なお、このとき駆動用  $TFT:Q1$  を流れる電流は、電位  $V_{cc}$  と電位  $V_c$  との差の二乗に比例する。

【0097】

そこで、表示装置の点灯画素数が多くなるほど、電位  $V_{cc}$  が低くなるよう、電位  $V_c$  を電源配線  $V_p$  から得るようにする。そして、表示装置外の電源と電源配線  $V_p$  との間に抵抗等を配置し、表示装置の点灯画素数が多くなるほど電位  $V_{cc}$  が低くなるようにする。一方、電位  $V_c$  についてはロジック電源から抵抗分圧等により作製し、常時一定の電位となるようにする。10

【0098】

のことにより、本実施の形態の画素回路のような構成では、表示画素数が少ないほど白色表示の輝度が上がるピーク輝度を実現できる。

【0099】

また、状態  $V_H$  とした駆動用  $TFT:Q1$  のゲート電位  $V_g$ 、ドレン電位  $V_d$ 、ソース・ドレン間電流  $I_{ds}$  をシミュレーションした結果を図 8 に示す。なお、電圧および電流の符号に付されている（1）は、閾値  $V_{th}$  が最小 ( $V_{th} (min)$ ) で移動度  $\mu$  が最大である場合に対応し、（2）は、閾値  $V_{th}$  が最大 ( $V_{th} (max)$ ) で移動度  $\mu$  が最小である場合に対応する。また、図 8 の電圧の立ち上がりおよび立ち下がりタイミングは図 6 と一致しているが、これも図 7 と同様に、図 6 と本質的には差はない。20

【0100】

図 8 のシミュレーション結果から判るとおり、制御配線  $R_i$  を  $L_o w (G L)$  として、電位配線  $U_i$  を  $V_c$  とした後でも、駆動用  $TFT:Q1$  のソース・ドレン間電流  $I_{ds}$  は 0 である。

【0101】

以上、本実施の形態によれば、図 6 のタイミングチャートから明らかなように、プランニング期間である時刻  $4t_1 \sim 8t_1$  の期間のうち、データ配線  $D_j$  に画素回路  $A_{ij}$  に対応する  $b_{it7}$  のデータを与える時間（選択期間）は時刻  $4t_1 \sim 6t_1$  で済む。データ配線  $D_j$  には時刻  $4t_1$  から時刻  $6t_1$  まで第 7 ビットの電圧を出力する期間が割り当てられるが、実際、データ配線  $D_j$  の電圧を画素回路  $A_{ij}$  に用いているのは、ゲート配線  $G_i$  が  $L_o w$  である時刻  $4t_1$  から時刻  $5t_1$  までである。時刻  $6t_1$  から時刻  $8t_1$  までは他のゲート電極  $G_i$  につながる画素回路  $A_{ij}$  の第 8 ビットの電圧をデータ配線  $D_j$  に出力する期間に割り当てられる。そして、このプランニング期間を自在に伸ばしても、選択期間は  $2t_1$  の期間のまま変化することはない。30

【0102】

このように本実施の形態では、プランニング期間のうち一部の時間だけを選択期間とするので、より多くのゲート配線  $G_i$  を駆動でき、大容量化が可能となる。

【0103】

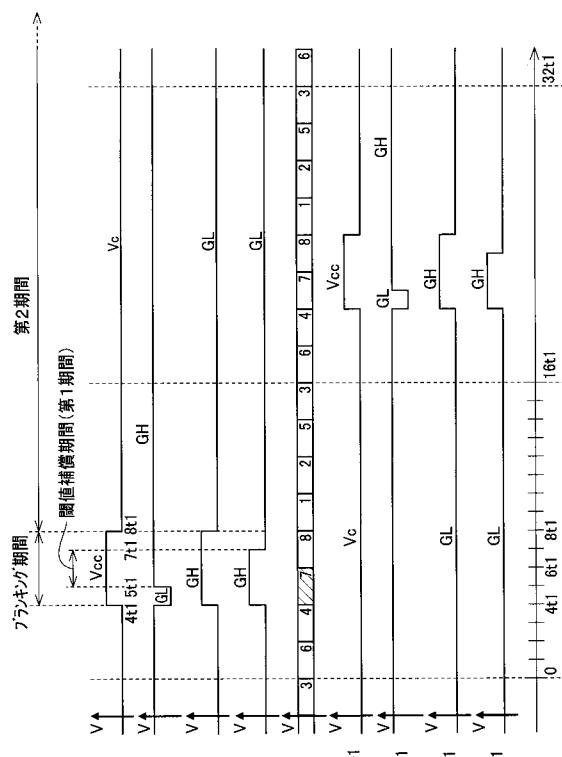

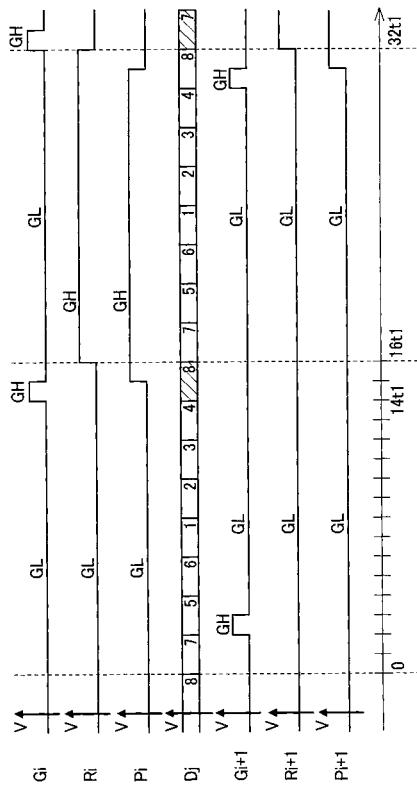

ところで、図 3 で示した時間配列は、図 4 及び図 5 のタイミングチャートを示すためにゲート配線数を 10 本とした例についてのものである。しかし、実際には図 9 に示すようにゲート配線数 320 本の QVGA (縦型) の表示を行う。40

【0104】

図 9 に示す時間配列では各  $b_{it}$  の長さを各  $b_{it}$  の重みより 5  $b_{it}$  期間分長くしている。これは、図 10 のタイミングチャートに示すように、各  $b_{it}$  当たりプランニング期間が 5  $b_{it}$  期間あることを示している。

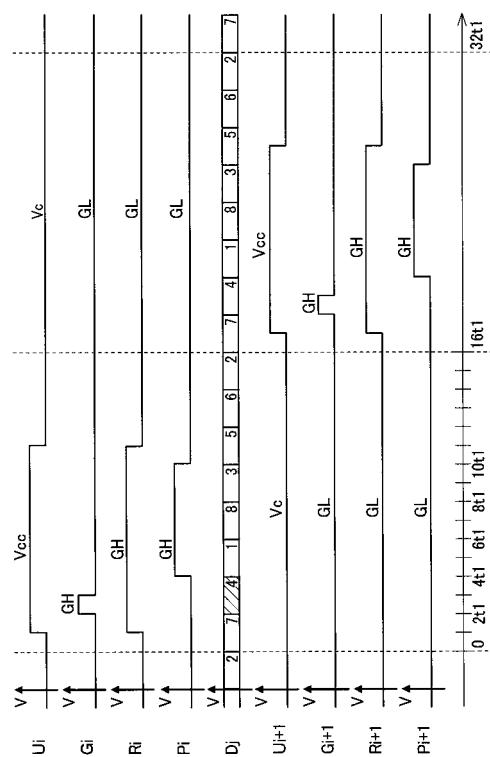

【0105】

このプランニング期間が 5 選択期間である例を図 10 に示す。図 10 のタイミングチャートでは、時刻 0 において、電位配線  $U_i$  を電位  $V_{cc}$  として駆動用  $TFT:Q1$  のゲー50

ト電位をOFF電位とし、プランキング期間を開始する。そして、同時に制御配線R<sub>i</sub>をHigh(GH)として、スイッチ用TFT:Q3をOFF状態とする。

【0106】

その後、時刻2t1において、制御配線P<sub>i</sub>をHigh(GH)として、スイッチ用TFT:Q2をON状態とする。また、同時にゲート配線G<sub>i</sub>をLow(GL)として、スイッチ用TFT:Q4をON状態とする。そして、同時にデータ配線D<sub>j</sub>から所望の電位(図10では第4bitの電位)を駆動用TFT:Q1のゲート端子に与え、時刻3t1にてゲート配線G<sub>i</sub>をHigh(GH)として、スイッチ用TFT:Q4をOFF状態とする。

【0107】

その後、時刻8t1で制御配線P<sub>i</sub>をLow(GL)として、スイッチ用TFT:Q2をOFF状態とする。このことにより、駆動用TFT:Q1のゲート電位はV<sub>p</sub>-V<sub>th</sub>の状態(状態VL)かVHの状態(状態VH)で保持される。

【0108】

そして、時刻10t1で制御配線R<sub>i</sub>をLow(GL)として、スイッチ用TFT:Q3をON状態とし、同時に電位配線U<sub>i</sub>の電位をV<sub>c</sub>に変化させる。

【0109】

このことにより、電位配線U<sub>i</sub>を電位V<sub>c</sub>とした後、状態VLとした駆動用TFT:Q1を流れる電流は、その閾値電圧に依らずほぼ一定となる。

【0110】

また、電位配線U<sub>i</sub>を電位V<sub>c</sub>とした後、状態VHとした駆動用TFT:Q1を流れる電流は0となる。

【0111】

本実施の形態では、データ配線D<sub>j</sub>は、少なくとも、各画素の表示データに対応する電位が駆動用TFT(駆動用トランジスタ):Q1のゲート端子に与えられて、コンデンサ(第1コンデンサ)C1に対応する電荷が保持される動作が完了するまで画素に接続されていればよい。従って、各画素は、駆動用TFT(駆動用トランジスタ):Q1の閾値電圧補償期間において、データ配線を占有する必要がない。このように、本実施の形態ではプランキング期間を選択期間の長さとは無関係に長くできるので、より多くのゲート配線G<sub>i</sub>を駆動でき、大容量化が可能となる。このことは、以下の実施の形態でも同様である。

【0112】

〔実施の形態2〕

本実施の形態では、本発明の表示装置の第2の例について説明する。

【0113】

本実施の形態に係る表示装置1も、図2に示す構成は同じであるので、その説明は省略する。

【0114】

図11に、本実施の形態に係る画素回路A<sub>i</sub>jの構成を示す。

【0115】

この画素回路A<sub>i</sub>jは、図1の画素回路A<sub>i</sub>jの構成からスイッチ用TFT:Q4(第3スイッチ用トランジスタ)を外し、代わりに、駆動用TFT:Q1(駆動用トランジスタ)のゲート端子(電流制御端子)とデータ配線D<sub>j</sub>との間にn型のスイッチ用TFT:Q5(第4スイッチ用トランジスタ)が配置されたものである。その他は、図1の画素回路A<sub>i</sub>jと同様なので、ここではそれ以上の説明は省略する。

【0116】

以下、この画素回路A<sub>i</sub>jの動作を図12のタイミングチャートを用いて説明する。

【0117】

図12においてU<sub>i</sub>, G<sub>i</sub>, R<sub>i</sub>, P<sub>i</sub>は画素回路A<sub>i</sub>jに対応し、U<sub>i</sub>+1, G<sub>i</sub>+1, R<sub>i</sub>+1, P<sub>i</sub>+1は画素回路A<sub>i</sub>+1jに対応する。D<sub>j</sub>はデータ配線D<sub>j</sub>に供給

10

20

30

40

50

する第1bit～第8bitのデータを示している。

【0118】

図12のタイミングチャートでは、ランキング期間は、制御配線R<sub>i</sub>がHighとなる、または電位配線U<sub>i</sub>がVccとなる、時刻t<sub>1</sub>～11t<sub>1</sub>の期間である。また、閾値補償期間（第1期間）は、制御配線P<sub>i</sub>がHighとなる、時刻4t<sub>1</sub>～10t<sub>1</sub>の期間である。また、時刻2t<sub>1</sub>～4t<sub>1</sub>の期間は画素回路A<sub>ij</sub>に第4bitのデータを設定する選択期間である。

【0119】

時刻t<sub>1</sub>において、電位配線U<sub>i</sub>を電位Vccとして駆動用TFT:Q1のゲート電位をOFF電位とし、同時に、制御配線R<sub>i</sub>をHigh(GH)として、スイッチ用TFT:Q3をOFF状態とする。

10

【0120】

その後、時刻2t<sub>1</sub>～3t<sub>1</sub>の期間に、ゲート配線G<sub>i</sub>をHigh(GH)として、スイッチ用TFT:Q5をON状態とする。そしてこのとき、データ配線D<sub>j</sub>から与える電位をVLとするか、VHとするかにより、駆動用TFT:Q1をON状態にするか、OFF状態にするかを設定する。

【0121】

即ち、電源配線Vpの電位をVp、駆動用TFT:Q1の閾値電圧の絶対値がばらつきの最大（絶対値が最大）でVth(max)、ばらつきの最小（絶対値が最小）でVth(min)であるとして、

20

$$\begin{aligned} VL &< Vp - Vth(max) \\ VH &> Vp - Vth(min) \end{aligned}$$

とする。

【0122】

例えば、データ配線D<sub>j</sub>から与える電位をVLとすると、駆動用TFT:Q1のゲート電位はVLとなる。このため、駆動用TFT:Q1はその閾値電圧Vthに依らずON状態となる。逆に、データ配線D<sub>j</sub>から与える電位をVHとすると、駆動用TFT:Q1のゲート電位はVHとなる。このため、駆動用TFT:Q1はその閾値電圧Vthに依らずOFF状態となる。

【0123】

30

その後、時刻4t<sub>1</sub>において制御配線P<sub>i</sub>をHigh(GH)として、スイッチ用TFT:Q2をON状態とする。このことにより、ON状態の駆動用TFT:Q1のゲート電位はVp - Vthに変化する。一方、OFF状態の駆動用TFT:Q1のゲート電位はVHのままとなる。

【0124】

その後、時刻10t<sub>1</sub>で制御配線P<sub>i</sub>をLow(GL)として、スイッチ用TFT:Q2をOFF状態とする。このことにより、駆動用TFT:Q1のゲート電位はVp - Vthの状態（状態VL）かVHの状態（状態VH）で保持される。

【0125】

そして、時刻11t<sub>1</sub>で制御配線R<sub>i</sub>をLow(GL)として、スイッチ用TFT:Q3をON状態とし、電位配線U<sub>i</sub>の電位をVcに変化させる。

40

【0126】

このとき、

$$VH - (Vcc - Vc) > Vp - Vth(min)$$

としておけば、状態VHの駆動用TFT:Q1はOFF状態のままとなる。一方、状態VLの駆動用TFT:Q1のゲート電位は

$$Vp - Vth - (Vcc - Vc)$$

となり、駆動用TFT:Q1の閾値電圧Vthに依らず駆動用TFT:Q1に一定電流が流れる状態となる。

【0127】

50

このように、本実施の形態によれば、図12のタイミングチャートから明らかなように、プランキング期間のうち、データ配線D<sub>j</sub>に所望の電位V<sub>H</sub> / V<sub>L</sub>を与える時間（選択期間）は、閾値補償期間が時刻4t<sub>1</sub>～10t<sub>1</sub>の期間であるのに対し、時刻2t<sub>1</sub>～4t<sub>1</sub>の期間で済む。そして、このプランキング期間を自在に伸ばしても、選択期間は2t<sub>1</sub>の期間のままで済ませられる。本実施の形態では、第1期間としての閾値補償期間は、データ配線D<sub>j</sub>から各画素の表示データに対応する電位が駆動用TFTQ1のゲート端子に与えられて、コンデンサC1に、対応する電荷が保持された状態から始まる。時刻11t<sub>1</sub>以降は第2期間となる。

## 【0128】

このように本実施の形態によれば、プランキング期間のうち一部の時間だけを選択期間とするので、より多くのゲート配線G<sub>i</sub>を駆動でき、大容量化が可能となる。 10

## 【0129】

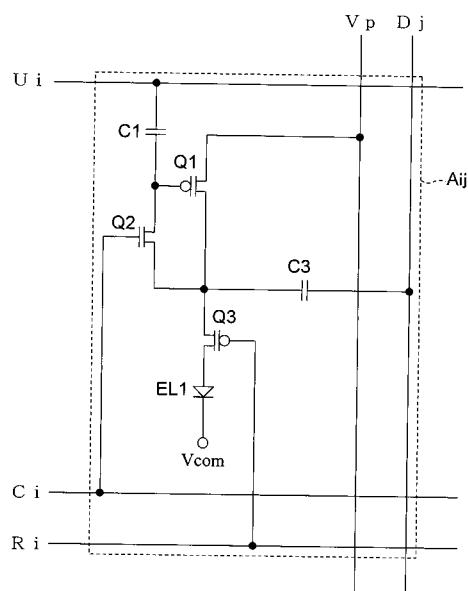

次に、図13に、駆動用TFTをn型の駆動用TFT:Q6とする場合の画素回路A<sub>i</sub><sub>j</sub>の構成を示しておく。

## 【0130】

図13では、電源配線V<sub>p</sub>と共通電極V<sub>com</sub>との間に、第1スイッチ用TFT:Q8（第1スイッチ用トランジスタ）と駆動用TFT:Q6（駆動用トランジスタ）と有機EL:EL1（電気光学素子）がこの順で直列に接続されている。また、駆動用TFT:Q6のゲート端子（電流制御端子）にはコンデンサC2（第1コンデンサ）の一方端子が接続され、駆動用TFT:Q6のゲート端子とドレイン端子（電流出力端子）との間にはスイッチ用TFT:Q7（第2スイッチ用トランジスタ）が接続されている。 20

## 【0131】

コンデンサC2の他方端子は電位配線U<sub>i</sub>（第1配線）に接続され、駆動用TFT:Q6（駆動用トランジスタ）のゲート端子（電流制御端子）とデータ配線D<sub>j</sub>との間にスイッチ用TFT:Q9（第4スイッチ用トランジスタ）が接続されている。各スイッチ用TFT:Q7, Q8, Q9のゲート端子は順に制御配線P<sub>i</sub>、制御配線R<sub>i</sub>、ゲート配線G<sub>i</sub>に接続されている。

## 【0132】

なお、駆動用TFT:Q6およびスイッチ用TFT:Q7, Q8, Q9はn型TFTである。 30

## 【0133】

図14に、この画素回路A<sub>i</sub><sub>j</sub>のタイミングチャートを示す。

## 【0134】

図14のタイミングチャートでは、駆動用TFT:Q6がn型であることから、V<sub>cc</sub> < V<sub>c</sub>となる。また、信号配線R<sub>i</sub>の極性が図12とは反対となるが、これは、図13の画素回路構成では制御配線R<sub>i</sub>に繋がるスイッチ用TFT:Q8（第1スイッチ用トランジスタ）がn型であるからである。

## 【0135】

それ以外、図14のタイミングチャートは図12のタイミングチャートと等しいので、ここでは説明は省略する。 40

## 【0136】

このように、本実施の形態は、駆動用TFTがp型の場合だけでなく、n型の場合にも成り立つ。

## 【0137】

〔実施の形態3〕

本実施の形態では、本発明の表示装置の第3の例について説明する。

## 【0138】

本実施の形態に係る表示装置1も、図2に示す構成は同じであるので、その説明は省略する。

## 【0139】

10

20

30

40

50

図15に、本実施の形態に係る画素回路A<sub>i</sub>jの構成を示す。

【0140】

この画素回路A<sub>i</sub>jは、図1の画素回路A<sub>i</sub>jの構成からスイッチ用TFT:Q4(第3スイッチ用トランジスタ)を外し、代わりに、駆動用TFT:Q1(駆動用トランジスタ)のドレイン端子(電流出力端子)とデータ配線D<sub>j</sub>との間にコンデンサC3(第2コンデンサ)を接続したものとなっている。また、スイッチ用TFT:Q4のゲート電圧を制御するためのゲート配線G<sub>i</sub>も外してある。その他は、図1の画素回路A<sub>i</sub>jと同様なので、ここではそれ以上の説明は省略する。

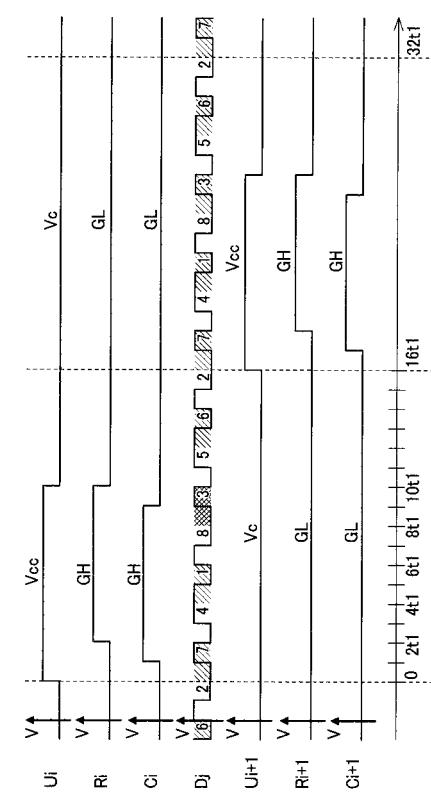

【0141】

以下、この画素回路A<sub>i</sub>jの動作を図16のタイミングチャートを用いて説明する。

10

【0142】

図16においてU<sub>i</sub>, R<sub>i</sub>, C<sub>i</sub>は画素回路A<sub>i</sub>jに対応し、U<sub>i+1</sub>, R<sub>i+1</sub>, C<sub>i+1</sub>は画素回路A<sub>i+1</sub>jに対応する。D<sub>j</sub>はデータ配線D<sub>j</sub>に供給する第1bit~第8bitのデータを示している。

【0143】

図16のタイミングチャートでは、ブランкиング期間は、電位配線U<sub>i</sub>が電位V<sub>cc</sub>となる、時刻0~10t<sub>1</sub>の期間である。また、閾値補償期間(第1期間)は、後述の説明から分かるように時刻8t<sub>1</sub>~9t<sub>1</sub>の期間である。また、時刻8t<sub>1</sub>~10t<sub>1</sub>の期間は画素回路A<sub>i</sub>jに第3bitのデータを設定する選択期間である。

【0144】

データ配線D<sub>j</sub>に供給されるbitデータは、OFF状態に対応するデータである場合には2t<sub>1</sub>分の選択期間の前半でV<sub>H</sub>、後半でV<sub>L</sub>となり、ON状態に対応するデータである場合には選択期間の前半でV<sub>L</sub>、後半でV<sub>H</sub>となる。

20

【0145】

時刻8t<sub>1</sub>~10t<sub>1</sub>の選択期間に先立ち、時刻0において、電位配線U<sub>i</sub>を電位V<sub>cc</sub>として駆動用TFT:Q1のゲート電位をOFF電位とする。そして、時刻t<sub>1</sub>において、制御配線C<sub>i</sub>をHigh(GH)として、スイッチ用TFT:Q2をON状態とする。このとき、制御配線R<sub>i</sub>はLow(GL)のままなので、スイッチ用TFT:Q3はON状態である。この結果、駆動用TFT:Q1のゲート電位が低下し、駆動用TFT:Q1はON状態となる。

30

【0146】

その後、時刻2t<sub>1</sub>において、制御配線R<sub>i</sub>がHigh(GH)となるので、スイッチ用TFT:Q3がOFF状態となる。その後、データ配線D<sub>j</sub>が電位V<sub>L</sub>となる毎に、駆動用TFT:Q1のゲート電位が、コンデンサC3を通して変化する。その結果、駆動用TFT:Q1の閾値電圧をV<sub>th</sub>とすると、駆動用TFT:Q1のゲート電位はV<sub>p</sub>-V<sub>th</sub>となる。

【0147】

そこで、時刻9t<sub>1</sub>において制御信号C<sub>i</sub>をLow(GL)としてスイッチ用TFT:Q2をOFF状態とする。このとき、この直前に、データ配線D<sub>j</sub>の電位がV<sub>L</sub>(第3bitのデータがONとなるデータ)であれば、駆動用TFT:Q2のゲート電位はV<sub>p</sub>-V<sub>th</sub>となる。データ配線D<sub>j</sub>の電位がV<sub>H</sub>(第3bitのデータがOFFとなるデータ)であれば、駆動用TFT:Q2のゲート電位はV<sub>p</sub>-V<sub>th</sub>+(V<sub>H</sub>-V<sub>L</sub>)となる。

40

【0148】

その後、時刻10t<sub>1</sub>において、電位配線U<sub>i</sub>の電位をV<sub>cc</sub>からV<sub>c</sub>へ変化させ、駆動用TFT:Q1のゲート電位を設定する。このため、時刻9t<sub>1</sub>においてデータ配線D<sub>j</sub>の電位がV<sub>L</sub>のとき、駆動用TFT:Q1のゲート電位は時刻10t<sub>1</sub>においてV<sub>p</sub>-V<sub>th</sub>-V<sub>cc</sub>+V<sub>c</sub>となり、駆動用TFT:Q1はON状態となる。一方、時刻9t<sub>1</sub>においてデータ配線D<sub>j</sub>の電位がV<sub>H</sub>のとき、駆動用TFT:Q1のゲート電位は時刻10t<sub>1</sub>においてV<sub>p</sub>-V<sub>th</sub>+(V<sub>H</sub>-V<sub>L</sub>)-V<sub>cc</sub>+V<sub>c</sub>となる。そこで、V<sub>H</sub>-V<sub>L</sub>>V<sub>cc</sub>-V<sub>c</sub>とすれば、駆動用TFT:Q1はOFF状態となる。

50

## 【0149】

このことにより、時刻  $10t_1$  において電位配線  $U_i$  の電位を  $V_{cc}$  から  $V_c$  へ変化させることで、時刻間  $9t_1$  においてデータ配線  $D_j$  の電位が  $V_L$  の場合の駆動用  $TFT:Q_1$  は、時刻  $10t_1$  において  $ON$  状態となる。また、時刻  $9t_1$  においてデータ配線  $D_j$  の電位が  $V_H$  の場合の駆動用  $TFT:Q_1$  は、時刻  $10t_1$  において  $OFF$  状態となる。

## 【0150】

そして、時刻  $9t_1$  において、データ配線  $D_j$  の電位が  $V_L$  の場合、駆動用  $TFT:Q_1$  の出力電流は駆動用  $TFT:Q_1$  の閾値電圧のばらつきに依らず一定となる。

## 【0151】

このように、本実施の形態によれば、図15の画素回路  $A_{ij}$  を用いることにより、ブランкиング期間である時刻  $0 \sim 10t_1$  の期間のうち、データ配線  $D_j$  に所望の電位  $V_H$  /  $V_L$  を与える時間（選択期間）は時刻  $8t_1 \sim 10t_1$  の  $2t_1$  分で済む。そして、このブランкиング期間を自在に伸ばしても、選択期間は  $2t_1$  の期間のままで済ませられる。本実施の形態では、第1期間としての閾値補償期間は、データ配線  $D_j$  から各画素の表示データに対応する電位が駆動用  $TFT:Q_1$  のゲート端子に与えられて、コンデンサ  $C_1$  に、対応する電荷が保持される動作と同時（時刻  $8t_1 \sim 9t_1$ ）に行われる。時刻  $10t_1$  以降は第2期間となる。

## 【0152】

このように本実施の形態によれば、ブランкиング期間のうち一部の期間だけを選択期間とするので、より多くのゲート配線  $G_i$  を駆動でき、大容量化が可能となる。

## 【0153】

次に、図17に駆動用  $TFT:Q_1$  のドレイン端子（電流出力端子）とデータ配線  $D_j$ （第2の配線）の間にコンデンサ  $C_4$ （第2コンデンサ）とスイッチ用  $TFT:Q_{10}$ （第8スイッチ用トランジスタ）とを接続した回路構成を示す。

## 【0154】

データ配線  $D_j$ （第2の配線）に設けたコンデンサ  $C_4$ （第2コンデンサ）の容量が大きいときはデータ配線  $D_j$  の配線容量が増えて、波形が歪みやすくなり、選択期間内に波形が立ち上がらなくなる可能性がある。従って、それを防ぐために、コンデンサ  $C_4$ （第2コンデンサ）と直列にスイッチ用  $TFT:Q_{10}$ （第8スイッチ用トランジスタ）を接続し、制御配線  $R_i$  が  $LOW$  となっている間にコンデンサ  $C_4$  と駆動用  $TFT:Q_1$  との接続を絶つのが有効である。スイッチ用  $TFT:Q_{10}$  が  $OFF$  になると、コンデンサ  $C_4$  と駆動用  $TFT:Q_1$  との間の接続が絶たれるので、コンデンサ  $C_4$  の端子の1つがオープンになって、コンデンサ  $C_4$  の容量はデータ配線  $D_j$  の配線容量として働くなくなる。

## 【0155】

この図17に対応するタイミングチャートは図16と同じであるので、ここではその説明を省略する。

## 【0156】

## 〔実施の形態4〕

本実施の形態では、本発明の表示装置の第4の例について説明する。

## 【0157】

本実施の形態に係る表示装置1も、図2に示す構成は同じであるので、その説明は省略する。

## 【0158】

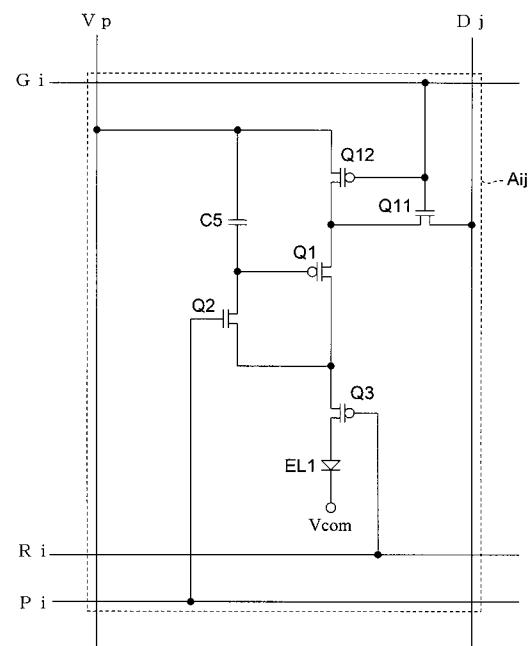

図18に、本実施の形態に係る画素回路  $A_{ij}$  の構成を示す。

## 【0159】

この画素回路  $A_{ij}$  は、データ配線  $D_j$  とゲート配線  $G_i$  とが交差する付近に駆動用  $TFT:Q_1$ （駆動用トランジスタ）と有機EL：EL1（電気光学素子）とが配置されたものである。そして、電源配線  $V_p$  と共通配線  $V_{com}$ との間に、スイッチ用  $TFT:Q$

10

20

30

40

50

12 (第6スイッチ用トランジスタ)と、駆動用TFT:Q1と、スイッチ用TFT:Q3 (第1スイッチ用トランジスタ)と有機EL:EL1とがこの順で直列に接続されている。

#### 【0160】

駆動用TFT:Q1のゲート端子 (電流制御端子) と電源配線Vpとの間にはコンデンサC5 (第1コンデンサ) が接続されている。また、駆動用TFT:Q1のゲート端子とドレイン端子 (電流出力端子)との間にはスイッチ用TFT:Q2 (第2スイッチ用トランジスタ) が接続されている。また、駆動用TFT:Q1のソース端子 (基準電位端子) とデータ配線Djとの間にスイッチ用TFT:Q11 (第5スイッチ用トランジスタ) が接続されている。

10

#### 【0161】

各スイッチ用TFT:Q2, Q3のゲート端子は順に制御配線Pi, R<sub>i</sub>に接続され、スイッチ用TFT:Q11, Q12のゲート端子はゲート配線Giに接続されている。

#### 【0162】

なお、駆動用TFT:Q1およびスイッチ用TFT:Q3, Q12はp型TFTであり、スイッチ用TFT:Q2, Q11はn型TFTである。

#### 【0163】

以下、この画素回路Ai jの動作を図19のタイミングチャートを用いて説明する。

#### 【0164】

図19においてGi, Ri, Piは画素回路Ai jに対応し、Gi+1, Ri+1, Pi+1は画素回路Ai+1 jに対応する。Djはデータ配線Djに供給する第1bit～第8bitのデータを示している。

20

#### 【0165】

図19のタイミングチャートでは、ブランкиング期間は、制御配線RiがHighとなる、時刻3t1～6t1の期間である。あるいは、ゲート配線GiがHighとなる、時刻2t1～6t1の期間をブランкиング期間とすることもできる。また、閾値補償期間 (第1期間)は、後述の説明から分かるように、時刻4t1～5t1の期間である。また、時刻4t1～6t1の期間は画素回路Ai jに第7bitのデータを設定する選択期間である。

#### 【0166】

30

時刻2t1において、ゲート配線GiをHigh (GH) としてスイッチ用TFT:Q12をOFF状態として、スイッチ用TFT:Q11をON状態とする。また、同時に制御配線PiをHigh (GH) として、スイッチ用TFT:Q2をON状態とする。制御配線Riは時刻3t1までLow (GL) のままなので、駆動用TFT:Q1のゲート電位は低下し、駆動用TFT:Q1はON状態となる。そして、データ配線Djからスイッチ用TFT:Q11、駆動用TFT:Q1、スイッチ用TFT:Q3を通して有機EL:EL1へ電流が流れる。

#### 【0167】

その後、時刻3t1において、制御配線RiがHigh (GH) となるので、スイッチ用TFT:Q3がOFF状態となる。そして、第7bitのデータがデータ配線Djに与えられ始める時刻4t1から、時刻5t1において制御配線PiがLow (GL) となつてスイッチ用TFT:Q2がOFFとなるまで、駆動用TFT:Q1の閾値補償期間が続く。この閾値補償期間の最後にデータ配線Djに与えられる電位をVdaとすると、駆動用TFT:Q1のゲート電位はVda - Vthとなる。そして、この駆動用TFT:Q1のゲート電位が、時刻5t1において制御配線PiがLow (GL) となることで、保持される。

40

#### 【0168】

その後、時刻6t1において、ゲート配線GiをLow (GL) としてスイッチ用TFT:Q11をOFF状態として、スイッチ用TFT:Q12をON状態とする。この結果、駆動用TFT:Q1のソース端子電位は電位Vdaから電位Vpに変化する。一方、駆

50

動用 T F T : Q 1 のゲート電位は  $V_{d\alpha} - V_{th}$  から変化しない。

【 0 1 6 9 】

その結果、選択期間である時刻  $4t_1 \sim 6t_1$  の期間においてデータ配線  $D_j$  に供給する電位  $V_{da}$  と電源配線  $V_p$  の電位  $V_p$  との間に

$$V_p > V_{da}$$

の関係があれば、駆動用 T F T : Q 1 のゲート・ソース間電圧  $V_{ds}$  の絶対値が  $V_p - V_{da}$  だけ大きくなるので、駆動用 T F T : Q 1 は ON 状態となる。

【 0 1 7 0 】

逆に、

$$V_p < V_{da}$$

10

であれば、駆動用 T F T : Q 1 のゲート・ソース間電圧  $V_{ds}$  の絶対値が  $V_{da} - V_p$  だけ小さくなるので、駆動用 T F T : Q 1 は OFF 状態となる。

【 0 1 7 1 】

その結果、上記 ON 状態となった駆動用 T F T : Q 1 を流れる電流は、その閾値電圧  $V_{th}$  に依らず一定となる。本実施の形態では、第 1 期間としての閾値補償期間は、データ配線  $D_j$  から各画素の表示データに対応する電位が駆動用 T F T Q 1 のゲート端子に与えられて、コンデンサ C 1 に、対応する電荷が保持される動作と同時（時刻  $4t_1 \sim 5t_1$ ）に行われる。時刻  $6t_1$  以降は第 2 期間となる。

【 0 1 7 2 】

以上のように、本実施の形態によれば、また、上記ブランкиング期間のうち一部の時間だけ選択期間とするので、より多くのゲート配線  $G_i$  を駆動でき、大容量化が可能となる。

20

【 0 1 7 3 】

〔 実施の形態 5 〕

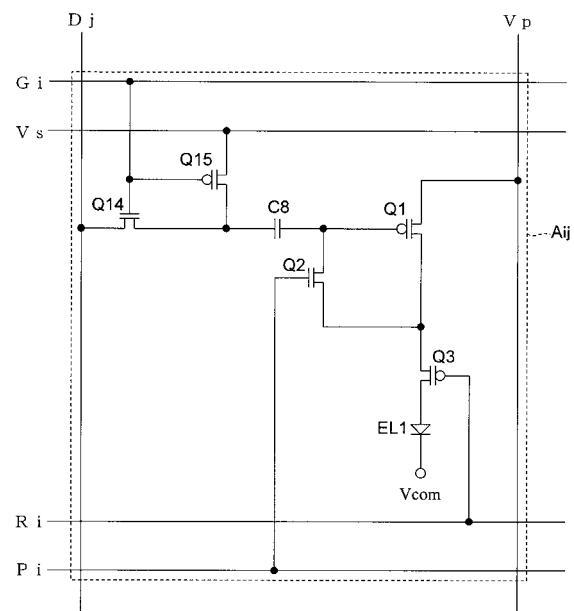

本実施の形態では、本発明の表示装置の第 5 の例について説明する。

【 0 1 7 4 】

本実施の形態に係る表示装置 1 も、図 2 に示す構成は同じであるので、その説明は省略する。

【 0 1 7 5 】

図 2 に、本実施の形態に係る画素回路  $A_{ij}$  の構成を示す。

30

【 0 1 7 6 】

この画素回路  $A_{ij}$  でも、データ配線  $D_j$  とゲート配線  $G_i$  とが交差する付近に駆動用 T F T : Q 1 (駆動用トランジスタ) と有機 E L : E L 1 (電気光学素子) とが配置されている。

【 0 1 7 7 】

そして、電源配線  $V_p$  と共通配線  $V_{com}$  との間に駆動用 T F T : Q 1 と、スイッチ用 T F T : Q 3 (第 1 スイッチ用トランジスタ) と、有機 E L : E L 1 とがこの順で直列に接続されている。

【 0 1 7 8 】

駆動用 T F T : Q 1 のゲート端子 (電流制御端子) にはコンデンサ C 8 (第 1 コンデンサ) の一方端子が接続され、そのコンデンサ C 8 の他方端子と電位配線  $V_s$  (第 2 配線) との間にはスイッチ用 T F T : Q 1 5 (第 8 スイッチ用トランジスタ) が接続されている。また、コンデンサ C 8 の他方端子とデータ配線  $D_j$  との間にスイッチ用 T F T : Q 1 4 (第 7 スイッチ用トランジスタ) が接続されている。

40

【 0 1 7 9 】

駆動用 T F T : Q 1 のゲート端子とドレイン端子 (電流出力端子) の間にスイッチ用 T F T : Q 2 (第 2 スイッチ用トランジスタ) が接続されている。

【 0 1 8 0 】

各スイッチ用 T F T : Q 2, Q 3 ゲート端子は、順に制御配線  $P_i, R_i$  に接続され、スイッチ用 T F T : Q 1 4, 1 5 のゲート端子はゲート配線  $G_i$  に接続されている。

50

## 【0181】

この、駆動用 TFT : Q1, スイッチ用 TFT : Q3, Q15 は p 型 TFT であり、スイッチ用 TFT : Q2, Q14 は n 型 TFT である。

## 【0182】

以下、この画素回路  $A_{ij}$  の動作を図 21 のタイミングチャートを用いて説明する。

## 【0183】

図 26 において  $G_i$ ,  $R_i$ ,  $P_i$  は画素回路  $A_{ij}$  に対応し、 $G_{i+1}$ ,  $R_{i+1}$ ,  $P_{i+1}$  は画素回路  $A_{i+1,j}$  に対応する。 $D_j$  はデータ配線  $D_j$  に供給する第 1 bit ~ 第 8 bit のデータを示している。

## 【0184】

図 21 のタイミングチャートでは、ブランкиング期間は、制御配線  $R_i$  が High となる、時刻  $3t_1 \sim 6t_1$  の期間である。あるいは、ゲート配線  $G_i$  が High となる、時刻  $2t_1 \sim 6t_1$  の期間をブランкиング期間とすることもできる。また、閾値補償期間（第 1 期間）は、後述の説明から分かるように、時刻  $4t_1 \sim 5t_1$  の期間である。また、時刻  $4t_1 \sim 6t_1$  の期間は画素回路  $A_{ij}$  に第 7 bit のデータを設定する選択期間である。

10

## 【0185】

時刻  $2t_1$  において、ゲート配線  $G_i$  を High (GH) としてスイッチ用 TFT : Q15 を OFF 状態として、スイッチ用 TFT : Q14 を ON 状態とする。また、同時に制御配線  $P_i$  を High (GH) として、スイッチ用 TFT : Q2 を ON 状態とする。制御配線  $R_i$  は時刻  $3t_1$  まで Low (GL) のままなので、駆動用 TFT : Q1 のゲート電位は低下し、駆動用 TFT : Q1 は ON 状態となる。そして、電源配線  $V_p$  から駆動用 TFT : Q1、スイッチ用 TFT : Q3 を通して有機 EL : EL1 へ電流が流れる。

20

## 【0186】

その後、時刻  $3t_1$  において、制御配線  $R_i$  が High (GH) となるので、スイッチ用 TFT : Q3 が OFF 状態となる。そして、第 7 bit のデータがデータ配線  $D_j$  に与えられ始める時刻  $4t_1$  から、時間  $5t_1$  において制御配線  $P_i$  が Low (GL) となってスイッチ用 TFT : Q2 が OFF となるまで、駆動用 TFT : Q1 の閾値補償期間が続く。

## 【0187】

30

この閾値補償期間の最後にデータ配線  $D_j$  に与えられる電位を  $V_{da}$  とすると、駆動用 TFT : Q1 のゲート電位は  $V_p - V_{th}$  となる。そして、コンデンサ C8 の両端に溜まる電荷は  $V_{da} - (V_p - V_{th})$  となる。

## 【0188】

そして、この駆動用 TFT : Q1 のゲート電位が、時刻  $5t_1$  において制御配線  $P_i$  が Low (GL) となることで、保持される。

## 【0189】

その後、時刻  $6t_1$  において、ゲート配線  $G_i$  を Low (GL) としてスイッチ用 TFT : Q14 を OFF 状態として、スイッチ用 TFT : Q15 を ON 状態とする。

## 【0190】

40

この結果、コンデンサ C8 の他方端子電位は電位  $V_{da}$  から  $V_s$  に変化する。

## 【0191】

その結果、選択期間である時刻  $4t_1 \sim 6t_1$  の期間においてデータ配線  $D_j$  に供給する電圧  $V_{da}$  と電位配線  $V_s$  の電位  $V_s$  との間に、

$$V_s < V_{da}$$

の関係があれば、駆動用 TFT : Q1 のゲート・ソース間電圧  $V_{ds}$  の絶対値が大きくなるので、駆動用 TFT : Q1 は ON 状態となる。

## 【0192】

逆に、

$$V_s > V_{da}$$

50

であれば、駆動用 T F T : Q 1 のゲート・ソース間電圧  $V_{ds}$  の絶対値が小さくなるので、駆動用 T F T : Q 1 は OFF 状態となる。

【0193】

その結果、上記 ON 状態となった駆動用 T F T : Q 1 を流れる電流は、その閾値電圧  $V_{th}$  に依らず一定となる。本実施の形態では、第 1 期間としての閾値補償期間は、データ配線 D<sub>j</sub> から各画素の表示データに対応する電位が駆動用 T F T Q 1 のゲート端子に与えられて、コンデンサ C 1 に、対応する電荷が保持される動作と同時（時刻 4 t<sub>1</sub> ~ 5 t<sub>1</sub>）に行われる。時刻 6 t<sub>1</sub> 以降は第 2 期間となる。

【0194】

また、上記プランキング期間のうち一部の時間だけ選択期間とするので、より多くのゲート配線 G<sub>i</sub> を駆動でき、大容量化が可能となる。 10

【0195】

〔実施の形態 6〕

本実施の形態では、本発明の表示装置の第 6 の例について説明する。

【0196】

本実施の形態に係る表示装置 1 も、図 2 に示す構成は同じであるので、その説明は省略する。

【0197】

図 2 に、本実施の形態に係る画素回路 A<sub>i</sub> j の構成を示す。

【0198】

この画素回路 A<sub>i</sub> j でも、データ配線 D<sub>j</sub> とゲート配線 G<sub>i</sub> とが交差する付近に駆動用 T F T : Q 1（駆動用トランジスタ）と有機 E L : E L 1（電気光学素子）とが配置されている。そして、電源配線 V<sub>p</sub> と共通配線 V<sub>com</sub> との間に駆動用 T F T : Q 1 と、スイッチ用 T F T : Q 3（第 1 スイッチ用トランジスタ）と、有機 E L : E L 1 とがこの順で直列に接続されている。 20

【0199】

駆動用 T F T : Q 1 のゲート端子（電流制御端子）にはコンデンサ C 6（第 1 コンデンサ）の一方端子が接続され、そのコンデンサ C 6 の他方端子と電源配線 V<sub>p</sub> との間にはコンデンサ C 7（第 3 コンデンサ）が接続されている。また、コンデンサ C 6 の他方端子とデータ配線 D<sub>j</sub> との間にスイッチ用 T F T : Q 1 3（第 7 スイッチ用トランジスタ）が接続されている。駆動用 T F T : Q 1 のゲート端子とドレイン端子（電流出力端子）との間にはスイッチ用 T F T : Q 2（第 2 スイッチ用トランジスタ）が接続されている。 30

【0200】

各スイッチ用 T F T : Q 2, Q 3, Q 1 3 のゲート端子は、順に制御配線 P<sub>i</sub>、制御配線 R<sub>i</sub>、ゲート配線 G<sub>i</sub> に接続されている。

【0201】

また、駆動用 T F T : Q 1 およびスイッチ用 T F T : Q 3 は p 型 T F T であり、スイッチ用 T F T : Q 2, Q 1 3 は n 型 T F T である。

【0202】

なお、この画素回路構成で用いる時間分割階調表示は、図 2 に示す時間配列とする。即ち、第 1 b<sub>1</sub> t ~ 第 8 b<sub>1</sub> t の各重みは 1 : 2 : 4 : 7 : 14 : 17 : 18 : 0 とする。この 64 階調表示を、各画素で表示する順番を b<sub>1</sub> t 重みが 18 : 17 : 1 : 2 : 7 : 4 : 14 : 0 となるよう並べ替える。そして、最後の重み 0 の第 8 b<sub>1</sub> t のデータは全期間をプランキング期間とし、長さを 9 b<sub>1</sub> t 期間とする。第 1 b<sub>1</sub> t ~ 第 7 b<sub>1</sub> t にはプランキング期間は存在しない。 40

【0203】

以下、この画素回路 A<sub>i</sub> j の動作を図 2 4 のタイミングチャートを用いて説明する。

【0204】

図 2 4 において G<sub>i</sub>, R<sub>i</sub>, P<sub>i</sub> は画素回路 A<sub>i</sub> j に対応し、G<sub>i</sub> + 1, R<sub>i</sub> + 1, P<sub>i</sub> + 1 は画素回路 A<sub>i</sub> + 1 j に対応する。D<sub>j</sub> はデータ配線 D<sub>j</sub> に供給する第 1 b<sub>1</sub> t ~ 50

第 8 bit のデータを示している。

【 0 2 0 5 】

時刻 14t1 ~ 16t1 の期間は画素回路 Aij に第 8 bit のデータを設定する選択期間である。時刻 14t1 ~ 15t1 にかけて、ゲート配線 Gi を High (GH) としてスイッチ用 TFT : Q13 を ON 状態として、データ配線 Dj より電位 Vx を入力する。その後、時刻 15t1 において制御配線 Pi を High (GH) としてスイッチ用 TFT : Q2 を ON 状態とし、この電位 Vx に対応する電荷をコンデンサ C6, C7 に保持させる。制御配線 Ri は時刻 16t1 まで Low (GL) のままで、駆動用 TFT : Q1 のドレイン電位は低下する。駆動用 TFT : Q1 のドレイン端子とゲート端子とはスイッチ用 TFT : Q2 で短絡されているので、駆動用 TFT : Q1 のゲート電位も低下し、駆動用 TFT : Q1 は ON 状態となる。そして、電源配線 Vp から駆動用 TFT : Q1 およびスイッチ用 TFT : Q3 を通して有機 EL : EL1 へ電流が流れる。

【 0 2 0 6 】

その後、時刻 16t1 において、制御配線 Ri を High (GH) とし、スイッチ用 TFT : Q3 を OFF 状態とする。そして、時刻 31t1 で制御配線 Pi を Low とする迄、この状態を保持する。

【 0 2 0 7 】

この結果、電源配線 Vp の電位を Vp、駆動用 TFT : Q1 の閾値電圧を Vth とする、駆動用 TFT : Q1 のゲート電位は Vp - Vth となる。

【 0 2 0 8 】

そして、時刻 31t1 において、制御配線 Pi を Low (GL) として、この駆動用 TFT : Q1 のゲート電位 Vp - Vth を保持する。

【 0 2 0 9 】

本実施の形態では、上記コンデンサ C6 の両端の電位差を設定するために、この全期間がブランкиング期間である第 8 bit データが必要である。

【 0 2 1 0 】

即ち、第 8 bit データとして VH を用い、コンデンサ C7 の両端の電位差を Vp - VH に設定する（図 24 では時刻 14t1 ~ 15t1 の間がこの設定期間になる）。そして、図 24 に示すように、その後、時刻 15t1 ~ 31t1 の間（この長さはブランкиング期間以内なら適当でも良い）、制御配線 Pi をハイとして、スイッチ用 TFT : Q2 をオンさせることで、駆動用 TFT : Q1 の閾値補償を行う。その結果、コンデンサ C6 の両端の電位差は VH - (Vp - Vth) となる。

【 0 2 1 1 】

このように、他の bit のデータ書き込みにブランкиング期間がないため、この第 8 bit データ表示期間（時刻 14t1 ~ 32t1 の期間）をブランкиング期間として用い、駆動用 TFT : Q1 の閾値補償を行うのがこの実施の形態である。

【 0 2 1 2 】

次に、時刻 32t1 において、制御配線 Ri を Low (GL) としてスイッチ用 TFT : Q3 を ON 状態とする。また、時刻 32t1 ~ 33t1 にかけ、ゲート配線 Gi を High (GH) として、スイッチ用 TFT : Q13 を ON として、データ配線 Dj よりコンデンサ C6, C7 へ第 7 bit に対応した電位 Vda を与える。

【 0 2 1 3 】

この電位 Vda と先に与えた電位 Vx との間に、

$$Vx > Vda$$

の関係があれば、駆動用 TFT : Q1 のゲート・ソース間電圧 Vgs の絶対値が大きくなり、駆動用 TFT : Q1 は ON 状態となる。

【 0 2 1 4 】

逆に、

$$Vx < Vda$$

であれば、駆動用 TFT : Q1 のゲート・ソース間電圧 Vgs の絶対値が小さくなるので

10

20

30

40

50

、駆動用 T F T : Q 1 は O F F 状態となる。

【 0 2 1 5 】

第 1 b i t ~ 第 7 b i t の表示について詳述すれば以下の通りである。

【 0 2 1 6 】

図 2 4 にあるように、ゲート配線 G i が H i g h のとき、スイッチ用 T F T : Q 1 3 が O N になって、コンデンサ C 7 の電位を V H か V L に置き換える。

【 0 2 1 7 】

このとき、コンデンサ C 6 の電荷は変化しないので、V H ( オフ ) のとき駆動用 T F T : Q 1 のゲート電位は V p - V t h ( V t h > 0 ) となる。即ち、このときのコンデンサ C 6 の両端の電位は V H - ( V p - V t h ) となる。V L ( オン ) のとき駆動用 T F T : Q 1 のゲート電位は V p - V t h - V H + V L ( V t h > 0 ) となる。 10

【 0 2 1 8 】

V H > V L であるから、駆動用 T F T : Q 1 のゲート電位は V p - V t h より低い電圧 ( 即ちオン電圧 ) になる。

【 0 2 1 9 】

このようにゲート配線 G i が H i g h の時のデータ配線 D j の電位により、駆動用 T F T : Q 1 のゲート電位が設定される。

【 0 2 2 0 】

本実施の形態では、第 1 期間としての閾値補償期間は、データ配線 D j から各画素の表示データに対応する電位が第 8 b i t のデータの電位で代用されて駆動用 T F T Q 1 のゲート端子に与えられて、コンデンサ C 1 に、対応する電荷が保持された状態から始まる。 20 第 2 期間は、第 1 b i t ~ 第 7 b i t のそれぞれについてゲート配線 G i が H i g h になる時刻以降の期間 ( 図 2 4 の第 7 b i t では時刻 3 2 t 1 以降の期間 ) となる。

【 0 2 2 1 】

このように本実施の形態によれば、閾値補償期間のうち一部の時間だけ選択期間とするので、より多くのゲート配線 G i を駆動でき、大容量化が可能となる。このように、本発明の効果は明らかである。

【 0 2 2 2 】

以上、各実施の形態について述べた。

【 0 2 2 3 】

以上のように本発明の表示装置およびその駆動方法によれば、各画素は、駆動用トランジスタ ( Q 1 ) の閾値電圧補償期間において、データ配線 ( データ配線 D j ) を占有する必要がない。このため、1 画素当たりの選択期間を短くでき、表示できる画素数を増やすことができる。 30

【 0 2 2 4 】

特に、1 フレームに複数回、駆動用トランジスタ ( Q 1 ) の出力状態を切り替えて時間分割階調表示を行う場合、駆動用トランジスタ ( Q 1 ) の出力状態を設定するためにデータ配線 ( データ配線 D j ) を占有できる時間 ( 選択期間 ) を短くする必要がある。

【 0 2 2 5 】

例えば、8 b i t 階調の場合、Q V G A を表示するためには、1 回当たりのデータ配線 ( データ配線 D j ) の占有時間は 40

$$1 / ( 60 \times 320 \times 8 ) = 6.5 \mu s$$

以下に収める必要がある。ここで、「 60 」は 1 秒当たりのフレーム数、「 320 」は図 9 の 320 ライン、「 8 」は図 4 の 1 単位時間の占有時間数である。

【 0 2 2 6 】

しかし、従来例で示した画素回路構成及びその駆動方法では、1 回当たりのデータ配線 ( データ配線 D j ) を占有時間が数十  $\mu s$  必要であり、Q V G A 表示はできないことになる。

【 0 2 2 7 】

一方、本発明を用いれば、1 回当たりのデータ配線 ( データ配線 D j ) を数  $\mu s$  以下に 50

収められるので、Q V G A表示も可能となる。

【0228】

このように、本発明を用いれば、表示パネルの大容量化が可能となるので、その効果は明らかである。

【産業上の利用可能性】

【0229】

本発明は、電流駆動型の電気光学素子を用いる表示装置に広く適用することができる。

【図面の簡単な説明】

【0230】

【図1】本発明の実施の形態1に係る表示装置における画素回路構成を示す回路図である

10

。

【図2】本発明の表示装置の構成を示す回路ブロック図である。

【図3】本発明の実施の形態1～5に係る表示装置の第1の時間配列を示す図である。

【図4】図3の時間配列における1フレーム期間のデータ信号を示す前半部分のタイミング図である。

【図5】図3の時間配列における1フレーム期間のデータ信号を示す後半部分のタイミング図である。

【図6】図4の画素回路の動作タイミングを示す第1の波形図である。

【図7】図4の画素回路において、駆動用TFTのゲート電位V<sub>g</sub>、ドレイン電位V<sub>d</sub>およびソース・ドレイン間電流I<sub>d</sub>の変化をシミュレーションした結果を示す第1のグラフである。

20

【図8】図4の画素回路において、駆動用TFTのゲート電位V<sub>g</sub>、ドレイン電位V<sub>d</sub>およびソース・ドレイン間電流I<sub>d</sub>の変化をシミュレーションした結果を示す第2のグラフである。

【図9】本発明の実施の形態1～5に係る表示装置の第2の時間配列を示す図である。

【図10】図4の画素回路の動作タイミングを示す第2の波形図である。

【図11】本発明の実施の形態2に係る表示装置における画素回路構成を示す回路図である。

【図12】図11の画素回路及び駆動回路の動作タイミングを示す波形図である。

【図13】本発明の実施の形態2に係る表示装置における変形例の画素回路構成を示す回路図である。

30

【図14】図13の画素回路及び駆動回路の動作タイミングを示す波形図である。

【図15】本発明の実施の形態3に係る表示装置における画素回路構成を示す回路図である。

【図16】図15の画素回路及び駆動回路の動作タイミングを示す波形図である。

【図17】本発明の実施の形態3に係る表示装置における変形例の画素回路構成を示す回路図である。

【図18】本発明の実施の形態4に係る表示装置における画素回路構成を示す回路図である。

【図19】図18の画素回路及び駆動回路の動作タイミングを示す波形図である。

40

【図20】本発明の実施の形態5に係る表示装置における画素回路構成を示す回路図である。

【図21】図20の画素回路及び駆動回路の動作タイミングを示す波形図である。

【図22】本発明の実施の形態6に係る表示装置における画素回路構成を示す回路図である。

【図23】本発明の実施の形態6に係る表示装置の時間配列を示す図である。

【図24】図22の画素回路構成の動作タイミングを示す波形図である。

【図25】従来の表示装置における画素回路の第1の構成例を示す回路図である。

【図26】従来の表示装置における画素回路の第2の構成例を示す回路図である。

【符号の説明】

50

【 0 2 3 1 】

|       |                                 |    |

|-------|---------------------------------|----|

| Q 1   | 駆動用 T F T ( 駆動用トランジスタ )         |    |

| Q 2   | スイッチ用 T F T ( 第 2 スイッチ用トランジスタ ) |    |

| Q 3   | スイッチ用 T F T ( 第 1 スイッチ用トランジスタ ) |    |

| Q 4   | スイッチ用 T F T ( 第 3 スイッチ用トランジスタ ) |    |

| Q 5   | スイッチ用 T F T ( 第 5 スイッチ用トランジスタ ) |    |

| Q 6   | 駆動用 T F T ( 駆動用トランジスタ )         |    |

| Q 7   | スイッチ用 T F T ( 第 2 スイッチ用トランジスタ ) |    |

| Q 8   | スイッチ用 T F T ( 第 1 スイッチ用トランジスタ ) |    |

| Q 9   | スイッチ用 T F T ( 第 4 スイッチ用トランジスタ ) | 10 |

| Q 1 1 | スイッチ用 T F T ( 第 5 スイッチ用トランジスタ ) |    |

| Q 1 2 | スイッチ用 T F T ( 第 6 スイッチ用トランジスタ ) |    |

| Q 1 3 | スイッチ用 T F T ( 第 7 スイッチ用トランジスタ ) |    |

| Q 1 4 | スイッチ用 T F T ( 第 7 スイッチ用トランジスタ ) |    |

| Q 1 5 | スイッチ用 T F T ( 第 8 スイッチ用トランジスタ ) |    |

| C 1   | コンデンサ ( 第 1 コンデンサ )             |    |

| C 3   | コンデンサ ( 第 2 コンデンサ )             |    |

| C 4   | コンデンサ ( 第 2 コンデンサ )             |    |

| C 5   | コンデンサ ( 第 1 コンデンサ )             |    |

| C 6   | コンデンサ ( 第 1 コンデンサ )             | 20 |

| C 7   | コンデンサ ( 第 3 コンデンサ )             |    |

| E L 1 | 有機 E L ( 電気光学素子 )               |    |

| D j   | データ配線                           |    |

| U i   | 電位配線 ( 第 1 配線 )                 |    |

| V p   | 電源配線                            |    |

| V s   | 電位配線 ( 第 2 配線 )                 |    |

【図1】

【図2】

【図3】

|       |        | 占有期間の番号 |    |    |    |    |    |    |    |    |

|-------|--------|---------|----|----|----|----|----|----|----|----|

| bit番号 | bitの重み | bitの長さ  | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

| 6     | 12     | 14      |    |    |    |    |    |    |    |    |

| 5     | 12     | 14      |    |    |    |    |    |    |    |    |

| 4     | 1      | 3       |    |    |    |    |    |    |    |    |

| 3     | 4      | 6       |    |    |    |    |    |    |    |    |

| 2     | 2      | 4       |    |    |    |    |    |    |    |    |

| 1     | 8      | 10      |    |    |    |    |    |    |    |    |

| 0     | 8      | 12      |    |    |    |    |    |    |    |    |

| 合計    | 12     | 14      |    |    |    |    |    |    |    |    |

| ライン数  | データ数   | 合計      | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

| 10    | 8      | 80      | 63 | 63 | 63 | 63 | 63 | 63 | 63 | 63 |

|       |        |         | 17 | 17 | 17 | 17 | 17 | 17 | 17 | 17 |

【図4】

【図5】

【図7】

【 四 6 】

【 四 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2-1】

【図2-2】

【図2-3】

【図2-4】

### 【図25】

【図26】

---

フロントページの続き

(51)Int.Cl.

F I

H 05B 33/14

A

審査官 福村 拓

(56)参考文献 特開2004-226960 (JP, A)

特開2004-341351 (JP, A)

特開2005-031630 (JP, A)

特開2004-133240 (JP, A)

特表2006-503327 (JP, A)

特開2003-295824 (JP, A)

特開2002-006808 (JP, A)

特開2006-048041 (JP, A)

特開2006-058800 (JP, A)

特開2005-099247 (JP, A)

特開2005-326828 (JP, A)

特開2003-195809 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 3 0

G 09 G 3 / 2 0

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP4160032B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2008-10-01 |

| 申请号            | JP2004254615                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2004-09-01 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 沼尾孝次                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 沼尾 孝次                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H01L51/50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0842 G09G2300/0852 G09G2300/0861 G09G2300/0866 G09G2300/0876 G09G2320/043                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09G3/30.J G09G3/30.K G09G3/20.621.F G09G3/20.624.B G09G3/20.641.A H05B33/14.A G09G3/3225 G09G3/3266 G09G3/3275 G09G3/3283 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 3K007/AB17 3K007/BA06 3K007/DB03 3K007/GA00 3K007/GA04 3K107/AA01 3K107/BB01 3K107/CC33 3K107/EE03 3K107/HH00 3K107/HH04 3K107/HH05 5C080/AA06 5C080/BB05 5C080/DD08 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 5C380/AA01 5C380/AB06 5C380/AB24 5C380/AB34 5C380/AC11 5C380/AC12 5C380/BA19 5C380/BA38 5C380/BA39 5C380/BB02 5C380/BB23 5C380/CA04 5C380/CA08 5C380/CA12 5C380/CA13 5C380/CA14 5C380/CA33 5C380/CA53 5C380/CB04 5C380/CB14 5C380/CB16 5C380/CB17 5C380/CB19 5C380/CB26 5C380/CB31 5C380/CC04 5C380/CC12 5C380/CC21 5C380/CC26 5C380/CC33 5C380/CC35 5C380/CC39 5C380/CC42 5C380/CC62 5C380/CC63 5C380/CC64 5C380/CD014 5C380/CD015 5C380/CD023 5C380/CD024 5C380/CE04 5C380/CF07 5C380/CF09 5C380/CF41 5C380/CF48 5C380/CF51 5C380/CF64 5C380/DA06 5C380/DA09 5C380/DA20 5C380/DA32 5C380/DA49 5C380/DA57 |         |            |

| 代理人(译)         | 木岛隆一<br>金子 一郎                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 审查员(译)         | 福村 拓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | JP2006071919A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

## 摘要(译)

提供一种显示装置及其驱动方法，能够缩短每个像素的选择周期，同时补偿驱动晶体管的阈值电压的变化。在像素电路Aij中，将电位布线Ui的电位设定为电位Vcc，将栅极布线Gi设定为低，将控制布线Ri设定为高，将控制布线Pi设定为高，以使驱动TFT：Q1的栅极端子设定为数据布线Dj的电位。。然后，将栅极布线Gi设置为“高”以补偿驱动TFT Q1的阈值电压。此后，电容器C1的电压，即驱动TFT的栅极和源极之间的电压随着控制布线Pi的电位设置为低而电位布线Ui被设置为电位Vc而改变，并且控制布线Ri被设置为低以使驱动电流流向有机EL：EL。点域1